特開2003-140182

(P2003-140182A)

(43)公開日 平成15年5月14日(2003.5.14)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I            | テマコード(参考)       |

|--------------------------|------|----------------|-----------------|

| G 0 2 F 1/1345           |      | G 0 2 F 1/1345 | 2 H 0 9 2       |

| 1/133                    | 550  | 1/133          | 2 H 0 9 3       |

| G 0 9 F 9/00             | 348  | G 0 9 F 9/00   | 348 Z 5 C 0 0 6 |

| G 0 9 G 3/20             | 621  | G 0 9 G 3/20   | 621 M 5 C 0 8 0 |

|                          | 623  |                | 623 B 5 G 4 3 5 |

審査請求 未請求 請求項の数 220L(全 20数) 最終頁に続く

(21)出願番号 特願2002-164813(P2002-164813)

(22)出願日 平成14年6月5日(2002.6.5)

(31)優先権主張番号 2001-068397

(32)優先日 平成13年11月3日(2001.11.3)

(33)優先権主張国 韓国(KR)

(71)出願人 501426046

エルジー・フィリップス エルシーデー

カンパニー, リミテッド

大韓民国 ソウル, ヨンドゥンポ-ク, ヨイ

ド-ドン 20

(72)発明者 リー ソク ウー

大韓民国 キョンサンブック-ド, クミ-シ

, ジンピュン-ドン, ナンバー642-3

(74)代理人 100064447

弁理士 岡部 正夫 (外10名)

最終頁に続く

(54)【発明の名称】 液晶表示装置のデータ駆動装置及び方法

(57)【要約】 (修正有)

【課題】 デジタル-アナログ変換部を時分割駆動して出力バッファ部と分離して集積化することで、デジタル-アナログ変換集積回路とテープ・キャリア・パッケージの数を減らす。

【解決手段】 データ駆動装置は、デジタル-アナログ変換集積回路と、デジタル-アナログ変換集積回路から供給される画素電圧信号をデータラインに信号緩衝させ出力する、nチャンネルの出力バッファの集積回路と、デジタル-アナログ変換集積回路及び出力バッファ集積回路を制御すると共に、デジタル-アナログ変換集積回路に供給する2nの画素データを出力バッファ集積回路に供給される順序に対応して再整列させて、n個ずつの画素データに構成される少なくとも2個の区間に時分割して供給するタイミング制御部とを具備しており、デジタル-アナログ変換集積回路はテープ・キャリアー・パッケージ上に実装され、出力集積回路は前記液晶パネル上に実装されている。

## 【特許請求の範囲】

【請求項1】 入力されたn個( nは正数)ずつの画素データを画素電圧信号に変換して少なくとも2分割して出力するデジタル-アナログ変換集積回路と、前記デジタル-アナログ変換集積回路から少なくとも2分割されて供給される画素電圧信号をそれぞれ入力してn個ずつのデータラインに信号緩衝させて出力する、前記デジタル-アナログ変換集積回路のそれぞれに少なくとも2個が共通に接続されたnチャンネルの出力バッファ集積回路と、前記デジタル-アナログ変換集積回路及び出力バッファ集積回路を制御すると共に前記デジタル-アナログ変換集積回路のそれぞれに供給する2n個の画素データを前記少なくとも2個の出力バッファ集積回路に供給される順序に対応して再整列させて、前記n個ずつの画素データに構成される少なくとも2個の区間に時分割して供給するタイミング制御部とを具備してなり、前記デジタル-アナログ変換集積回路は液晶パネルに接続されるテープ・キャリアー・パッケージ上に実装されており、前記出力バッファ集積回路は前記液晶パネル上に実装されていることを特徴とする液晶表示装置のデータ駆動装置。

【請求項2】 前記デジタル-アナログ変換集積回路のそれぞれは、前記タイミング制御部の制御に応答してサンプリング信号を順次的に出力するシフト・レジスタ部と、前記タイミング制御部と前記サンプリング信号に応答して前記タイミング制御部から入力されるn個の画素データを順次的にラッチして同時に出力するラッチ部と、入力ガンマ電圧を利用して前記n個の画素データを正極性及び負極性の画素電圧信号に同時に変換して、前記タイミング制御部の極性の制御信号に応答するn個の画素電圧信号を選択して、前記少なくとも2個の出力バッファ集積回路のそれぞれに供給するデジタル-アナログ変換部とを具備することを特徴とする請求項1記載の液晶表示装置のデータ駆動装置。

【請求項3】 前記出力バッファ集積回路のそれぞれは、前記デジタル-アナログ変換集積回路で出力されるn個の画素電圧信号のうちの1/2n個の画素電圧信号を入力して、前記タイミング制御部のソース入力イネーブル信号に応答してn個の出力ラインに選択的に供給するデマルチプレクサと、前記n個のデータラインに接続されて前記デマルチプレクサから1/2n個ずつ入力される画素電圧信号をホールディングしてn個の画素電圧信号がすべて入力されると信号緩衝させて出力する出力バッファ部とを具備することを特徴とする請求項1記載の液晶表示装置のデータ駆動装置。

【請求項4】 入力されたn個( nは正数)ずつの画素データを画素電圧信号に変換して、変換されたn個の画素電圧信号をk個( kは正数、k < n)ずつ時分割して出力するデジタル-アナログ変換集積回路と、前記デジタル-アナログ変換集積回路からk個ずつ供給される画素電圧信号をホールディングしてn個の画素電圧信号がすべて入力されると信号緩衝させてn個のデータラインに出力する、前記デジタル-アナログ変換集積回路のそれぞれに少なくとも2個が共通に接続された出力バッファの集積回路と、前記デジタル-アナログ変換集積回路及び出力バッファ集積回路のそれぞれを制御すると共に前記デジタル-アナログ変換集積回路に供給する画素データを、前記n個ずつの画素データに構成される少なく

素電圧信号をホールディングして2n個の画素電圧信号がすべて入力されると信号緩衝させて2n個のデータラインに同時に出力する2nチャンネルの出力バッファ集積回路と、前記デジタル-アナログ変換集積回路及び出力バッファ集積回路を制御すると共に前記デジタル-アナログ変換集積回路のそれぞれに供給する2n個の画素データを前記n個ずつ時分割して供給するタイミング制御部とを具備してなり、前記デジタル-アナログ変換集積回路は液晶パネルに接続されるテープ・キャリアー・パッケージ上に実装されており、前記出力バッファ集積回路は前記液晶パネル上に実装されていることを特徴とする液晶表示装置のデータ駆動装置。

【請求項5】 前記デジタル-アナログ変換集積回路のそれぞれは、前記タイミング制御部の制御に応答してサンプリング信号を順次的に出力するシフト・レジスタ部と、前記タイミング制御部の制御と前記サンプリング信号に応答して前記タイミング制御部から入力されるn個の画素データなどを順次的にラッチして同時に出力するラッチ部と、入力ガンマ電圧を利用して前記n個の画素データを正極性及び負極性の画素電圧信号に同時に変換して、前記タイミング制御部の極性の制御信号に応答するn個の画素電圧信号を選択すると同時に、前記タイミング制御部の選択制御信号に応答してそのn個の画素電圧信号を時分割してk個ずつ出力するデジタル-アナログ変換部とを具備することを特徴とする請求項4記載の液晶表示装置のデータ駆動装置。

【請求項6】 前記出力バッファ集積回路のそれぞれは、前記デジタル-アナログ変換集積回路で出力されるk個ずつの画素電圧信号を入力しての前記タイミング制御部のソース入力イネーブル信号に応答して2n個の出力ラインに選択的に供給するデマルチプレクサと、前記2n個のデータラインなどに接続されて前記デマルチプレクサからk個ずつ入力される画素電圧信号をホールディングして2n個の画素電圧信号がすべて入力されると信号緩衝させて出力する出力バッファ部とを具備することを特徴とする請求項4記載の液晶表示装置のデータ駆動装置。

【請求項7】 入力されたn個( nは正数)ずつの画素データを画素電圧信号に変換して、変換されたn個の画素電圧信号をk個( kは正数、k < n)ずつ時分割して出力するデジタル-アナログ変換集積回路と、前記デジタル-アナログ変換集積回路からk個ずつ供給される画素電圧信号をホールディングしてn個の画素電圧信号がすべて入力されると信号緩衝させてn個のデータラインに出力する、前記デジタル-アナログ変換集積回路のそれぞれに少なくとも2個が共通に接続された出力バッファの集積回路と、前記デジタル-アナログ変換集積回路及び出力バッファ集積回路のそれぞれを制御すると共に前記デジタル-アナログ変換集積回路に供給する画素データを、前記n個ずつの画素データに構成される少なく

とも2個の区間に時分割して供給するタイミング制御部とを具備してなり、前記デジタル-アナログ変換集積回路は液晶パネルに接続されるテープ・キャリア・パッケージ上に実装されており、前記出力バッファ集積回路は前記液晶パネル上に実装されていることを特徴とする液晶表示装置のデータ駆動装置。

【請求項8】 前記デジタル-アナログ変換集積回路のそれぞれは、前記タイミング制御部の制御に応答してサンプリング信号を順次的に出力するシフト・レジスタ部と、前記タイミング制御部の制御と前記サンプリング信号に応答して前記タイミング制御部から入力されるn個の画素データなどを順次的にラッチして同時に出力するラッチ部と、入力ガンマ電圧を利用して前記n個の画素データを正極性及び負極性の画素電圧信号に同時に変換して、前記タイミング制御部の極性の制御信号に応答するn個の画素電圧信号を選択すると同時に、前記タイミング制御部の第1選択制御信号に応答してそのn個の画素電圧信号を時分割してk個ずつ出力するデジタル-アナログ変換部と、前記タイミング制御部からの第2選択信号に応答して前記k個ずつ順次的に出力される画素電圧信号を前記少なくとも2個の出力バッファ集積回路に選択的に出力するデマルチプレクサとを具備することを特徴とする請求項7記載の液晶表示装置のデータ駆動装置。

【請求項9】 前記選択制御信号は、前記n個の画素電圧信号を前記k個ずつの画素電圧信号に時分割する回数に相当するビット数を有することを特徴とする請求項8記載の液晶表示装置のデータ駆動装置。

【請求項10】 前記デジタル-アナログ変換集積回路のそれぞれは、前記タイミング制御部の制御に応答してサンプリング信号を順次的に出力するシフト・レジスタ部と、前記タイミング制御部の制御と前記サンプリング信号に応答して前記タイミング制御部から入力されるn個の画素データを順次的にラッチして同時に出力するラッチ部と、入力ガンマ電圧を利用して前記n個の画素データを正極性及び負極性の画素電圧信号に同時に変換して、前記タイミング制御部の極性の制御信号に応答するn個の画素電圧信号を選択して出力するデジタル-アナログ変換部と、前記n個の画素電圧信号を前記タイミング制御部の第1選択制御信号に応答して少なくとも2個の出力段に選択的に出力するデマルチプレクサと、前記少なくとも2個の出力段のそれぞれに接続されて前記n個の画素電圧信号を前記タイミング制御部からの第2選択信号に応答して前記k個ずつ時分割して出力する少なくとも2個のデマルチプレクサとを具備することを特徴とする請求項7記載の液晶表示装置のデータ駆動装置。

【請求項11】 前記第1選択制御信号は前記ラッチ部の出力を制御する出力イネーブル信号の周期毎に選択制御信号の論理状態が反転されて、前記第2選択制御信号は前記n個の画素電圧信号を前記k個ずつの画素電圧信

(3)

4

号に時分割する回数に相当するビット数を有することを特徴とする請求項10記載の液晶表示装置のデータ駆動装置。

【請求項12】 前記出力バッファ集積回路のそれぞれは、前記デジタル-アナログ集積回路で出力されるk個ずつの画素電圧信号を入力して前記タイミング制御部のソース入力イネーブル信号に応答してn個の出力ラインに選択的に供給するデマルチプレクサと、前記n個のデータラインに接続されて前記デマルチプレクサからk個ずつ入力される画素電圧信号をホールディングしてn個の画素電圧信号がすべて入力されると信号緩衝させ出力する出力バッファ部とを具備することを特徴とする請求項7記載の液晶表示装置のデータ駆動装置。

【請求項13】 前記ソース入力イネーブル信号は、前記n個の画素電圧信号を前記k個ずつ画素電圧信号に時分割する回数に相当するビット数を有することを特徴とする請求項12記載の液晶表示装置のデータ駆動装置。

【請求項14】 前記出力バッファ部は前記n個のデータラインにそれぞれ接続されるn個の出力バッファセルで構成されており、前記出力バッファセルそれぞれに直列接続されて入力された画素電圧信号を信号緩衝する第1電圧の追従機と、前記第1電圧追従機の入力段及び出力段の中のいずれか一つに接続されて前記画素電圧信号をホールディングするホールディング手段と、前記タイミング制御部からの出力イネーブル信号に応答して前記ホールディングされた画素電圧信号を出力するスイッチング手段と、前記スイッチング手段から出力される画素電圧信号を信号緩衝して出力する第2電圧追従機とを具備することを特徴とする請求項12記載の液晶表示装置のデータ駆動装置。

【請求項15】 前記デジタル-アナログ変換集積回路のそれぞれは、前記デジタル-アナログ変換集積回路の構成要素のそれぞれに前記タイミング制御部からの制御信号と画素データを中継して供給する信号制御部と、入力ガンマ基準電圧を細分化して前記ガンマ電圧を発生するガンマの電圧部とを更に具備することを特徴とする請求項7記載の液晶表示装置のデータ駆動装置。

【請求項16】 前記タイミング制御部は、前記画素データをオド画素データの電送ラインとイブン画素データの電送ラインを通して前記デジタル-アナログ変換集積回路のそれぞれに供給して、前記タイミング制御部から前記デジタル-アナログ変換集積回路に供給される制御信号と画素データの周波数が少なくとも2倍以上増加されていることを特徴とする請求項7記載の液晶表示装置のデータ駆動装置。

【請求項17】 前記デジタル-アナログ変換集積回路は第1及び第2ブロックに分けられており、前記タイミング制御部は、前記画素データを第1オド画素データの電送ラインと第1イブン画素データの電送ラインを通して前記第1ブロックに含まれるデジタル-アナログ変換

集積回路に供給し、また、前記画素データを第2オド画素データの電送ラインと第2イブン画素データの電送ラインを通して前記第2ブロックに含まれるデジタル-アナログ変換集積回路に供給することを特徴とする請求項7記載の液晶表示装置のデータ駆動装置。

【請求項18】前記デジタル-アナログ変換集積回路が奇数個である場合において、それらの中の一つのデジタル-アナログ変換集積回路は前記第1及び第2オド画素データの電送ラインのうちのいずれか一つに接続された第1入力ポートと前記第1及び第2イブン画素データの電送ラインのうちのいずれか一つに接続された第2入力ポートとを具備しており、前記第1及び第2入力ポートは独立的に駆動されることを特徴とする請求項17記載の液晶表示装置のデータ駆動装置。

【請求項19】液晶パネルに配置されたデータラインを駆動するためのデータ駆動装置の駆動方法において、前記データ駆動装置は、タイミング制御部に接続されたデジタル-アナログ変換集積回路と、n個(nは正数)ずつのデータラインに接続された出力バッファの集積回路で構成されており、前記タイミング制御部で入力された画素データを再整列して前記デジタル-アナログ変換集積回路のそれぞれに入力されたn個の画素データを画素電圧信号に変換して、変換された画素電圧信号を1/2n個ずつ分割して前記2個の出力バッファの集積回路のそれぞれに出力する段階と、前記出力バッファの集積回路のそれぞれに1/2n個ずつ供給される画素電圧信号をホールディングする段階と、前記タイミング制御部で前記デジタル-アナログ変換集積回路のそれぞれに残りのn個の画素データを供給する段階と、前記デジタル-アナログ変換集積回路のそれぞれで入力された残りのn個の画素データをアナログ形態である画素電圧信号に変換して、変換された画素電圧信号を1/2n個ずつ分割して前記2個の出力バッファの集積回路のそれぞれに出力する段階と、前記出力バッファの集積回路で1/2個ずつ供給される画素電圧信号を前記段階でホールディングされた画素電圧信号と共に信号緩衝させて前記データラインに同時に供給する段階とを含むことを特徴とする液晶表示装置のデータ駆動方法。

【請求項20】液晶パネルに配置されたデータラインを駆動するためのデータ駆動装置の駆動方法において、前記データ駆動装置は、タイミング制御部に接続されたデジタル-アナログ変換集積回路と、前記デジタル-アナログ変換集積回路のそれぞれに接続されると共に2n個(nは正数)ずつのデータラインに接続された出力バッファの集積回路で構成されており、前記タイミング制御部により前記デジタル-アナログ変換集積回路のそれぞれに2n個の画素データのうちのn個の画素データを供給する段階と、前記デジタル-アナログ変換集積回路のそれぞれに入力されたn個の画素データを画素電圧信号に変換して、変換された画素電圧信号をk個(kは正

\*数、 $k < n$ )ずつ分割して該当する出力バッファの集積回路に出力する段階と、前記出力バッファの集積回路のそれぞれでk個ずつ供給される画素電圧信号を順次的にホールディングしてn個の画素電圧信号をホールディングする段階と、前記タイミング制御部で前記デジタル-アナログ変換集積回路のそれぞれに残りのn個の画素データを供給する段階と、前記デジタル-アナログ変換集積回路のそれぞれに入力された残りのn個の画素データをアナログ形態である画素電圧信号に変換して、変換された画素電圧信号をk個ずつ分割して該当する出力バッファの集積回路に出力する段階と、前記出力バッファの集積回路のそれぞれにk個ずつ供給される画素電圧信号をホールディングして、n個の画素電圧信号が入力される前記段階でホールディングされたn個の画素電圧信号と共に信号緩衝させて前記2n個のデータラインに同時に供給する段階とを含むことを特徴とする液晶表示装置のデータ駆動方法。

【請求項21】前記タイミング制御部は、前記画素データをオド画素データの電送ラインとイブン画素データの電送ラインを通して前記デジタル-アナログ変換集積回路のそれぞれに供給して、前記タイミング制御部から前記デジタル-アナログ変換集積回路に供給される制御信号と画素データの周波数が少なくとも2倍以上増加されていることを特徴とする請求項20記載の液晶表示装置のデータ駆動方法。

【請求項22】前記デジタル-アナログ変換集積回路は第1及び第2ブロックに分けられており、前記タイミング制御部は、第1オド画素データの電送ラインと第1イブン画素データの電送ラインを通して画素データを前記第1ブロックに含まれるデジタル-アナログ変換集積回路に供給し、第2オド画素データの電送ラインと第2イブン画素データの電送ラインを通して画素データを前記第2ブロックに含まれるデジタル-アナログ変換集積回路に供給することを特徴とする請求項20記載の液晶表示装置のデータ駆動方法。

#### 【発明の詳細な説明】

##### 【0001】

【発明の属する技術分野】本発明は液晶表示装置に関するもので、特にデジタル-アナログ変換部を時分割駆動して出力バッファ部と分離して集積化することで、デジタル-アナログ変換集積回路とテープ・キャリア・パッケージの数を減らすことができるようした液晶表示装置のデータの駆動装置及び方法に関するものである。

##### 【0002】

【従来の技術】一般的に、液晶表示装置は電界を利用して液晶の光透過率を調節することで画像を表示する。このために液晶表示装置は、液晶セルがマトリックス形態で配列された液晶パネルと、この液晶パネルを駆動するための駆動回路とを具備する。液晶パネルには複数のデータラインと複数のデータラインが交差して配列されて

おり、そのゲートラインとデータラインが交差して設けられる領域に液晶セルが位置する。この液晶パネルには、液晶セルのそれぞれに電界を印加するための画素電極と共に共通電極が設けられる。画素電極のそれぞれは、スイッチング素子である薄膜トランジスタ(TFT)のソース及びドレイン端子などを経由してデータラインのうちのいずれか一つに接続される。薄膜トランジスタのゲート端子は、画素電圧信号が1ライン分ずつの画素電極に印加されるようにするゲートラインのうちのいずれか一つに接続される。駆動回路は、ゲートラインを駆動するためのゲート駆動装置と、データラインを駆動するためのデータ駆動装置と、共通電極を駆動するための共通電圧発生部とを具備する。ゲート駆動装置は走査信号をゲートラインに順次的に供給して液晶パネル上の液晶セルを1ライン分ずつ順次的に駆動する。データ駆動装置は、ゲートラインのうちのいずれか一つにゲート信号が供給される毎にデータラインのそれぞれに画素電圧信号を供給する。共通電圧発生部は、共通電極に共通電圧信号を供給する。これにより液晶表示装置は、液晶セル別に画素電圧信号により画素電極と共に電極の間に印加される電界により光透過率を調節することで画像を表示する。データ駆動装置とゲート駆動装置は、多数個の集積回路(以下「IC」という)に集積化される。集積化されたデータ駆動ICとゲート駆動ICのそれぞれはテープ・キャリア・パッケージ(以下「TCP」という)上に実装されてTAB(テープ・オートメ-テッド・ボンディング)方式で液晶パネルに接続されるか、COG(チップ・オン・グラス)方式で液晶パネル上に実装される。

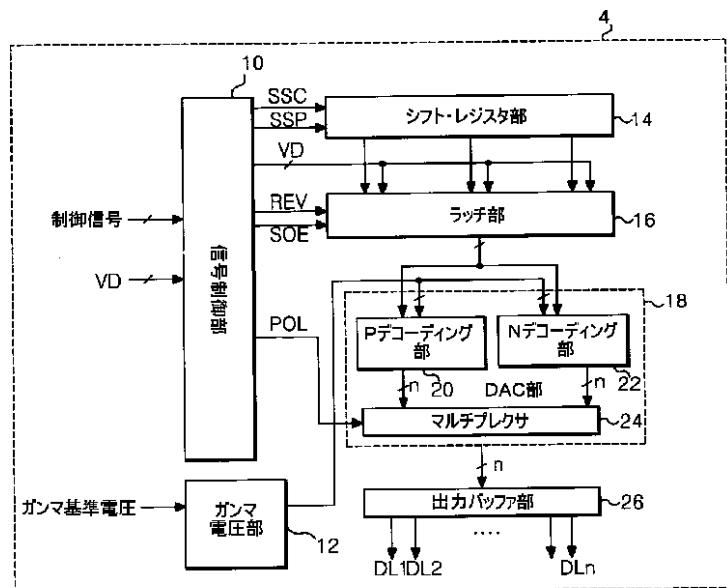

【0003】図1は従来の液晶表示装置のデータ駆動ブロックを概略的に図示したもので、データ駆動ブロックは、TCP(6)を通して液晶パネル(2)と接続された複数のデータ駆動IC(4)と、TCP(6)を通してデータ駆動IC(4)と接続されたデータ印刷回路基板(以下印刷回路基板を「PCB」という)(8)とを具備する。

【0004】データPCB(8)は、タイミング制御部(図示しない)から供給される各種の制御信号及びデータ信号とパワー部(図示しない)からの駆動電圧信号を入力してデータ駆動IC(4)に中継する役割をする。TCP(6)は、液晶パネル(2)の上段部に設けられたデータパッドと電気的に接続されると共に、データPCB(8)に設けられた出力パッドと電気的に接続される。データ駆動IC(4)は、デジタル信号である画素データ信号をアナログ信号である画素電圧信号に変換して液晶パネル(2)上のデータラインに供給する。

【0005】このために、データ駆動IC(4)のそれぞれは、図2に図示されたように順次的にサンプリング信号を供給するシフト・レジスタ部(14)と、サンプリング信号に応答して画素データ(VD)を順次的にラ

ッチして同時に outputするラッチ部(16)と、ラッチ部(16)からの画素データ(VD)を画素電圧信号に変換するデジタル-アナログ変換部(以下、DAC部といふ)(18)と、DAC部(18)からの画素電圧信号を緩衝して出力する出力バッファ部(26)とを具備する。また、データ駆動IC(4)は、タイミング制御部(図示しない)から供給される各種の制御信号と画素データ(VD)とを中継する信号制御部(10)と、DAC部(18)で必要とする正極性及び負極性のガンマ電圧を供給するガンマ電圧部(12)とを更に具備する。このような構成を有するデータ駆動IC(4)のそれぞれは、n個ずつのデータライン(DL1乃至DLn)を駆動する。

【0006】信号制御部(10)は、タイミング制御部(図示しない)からの各種の制御信号(SSP、SSC、SOE、REV、POLなど)と画素データ(VD)が所定の構成要素に出力されるように制御する。

【0007】ガンマ電圧部(12)は、ガンマ基準電圧の発生部(図示しない)から入力される多数のガンマ基準電圧をグレイ別に細分化して出力する。シフト・レジスタ部(14)に含まれたn/6個のシフト・レジスタは、信号制御部(10)からのソース・スタート・パルス(SSP)をソース・サンプリング・クロック信号(SSC)により順次的にシフトさせてサンプリング信号として出力する。

【0008】ラッチ部(16)は、シフト・レジスタ部(14)からのサンプリング信号に応答して信号制御部(10)からの画素データ(VD)を一定の単位ずつ順次的にサンプリングしてラッチする。このためにラッチ部は、n個の画素データ(VD)をラッチするためにn個のラッチで構成されており、そのラッチのそれぞれは、画素データ(VD)のビット数(3ビットまたは6ビット)に対応する大きさを有する。特にタイミング制御部(図示しない)は、伝送周波数を減らすために画素データ(VD)をイブン画素データ(VDeven)とオド画素データ(VDodd)に分けて、それぞれの伝送ラインを通して同時に outputする。ここで、イブン画素データ(VDeven)とオド画素データ(VDodd)のそれぞれは、赤(R)、緑(G)、青(B)の画素データを含む。これによりラッチ部(16)は、サンプリング信号毎に信号制御部(10)を経由して供給されるイブン画素データ(VDeven)とオド画素データ(VDodd)、即ち6個の画素データを同時にラッチする。続いて、ラッチ部(16)は、信号制御部(10)からのソース出力イネーブル信号(SOE)に応答してラッチされたn個の画素データ(VD)を同時に outputする。この場合、ラッチ部(16)は、データ反転の選択信号(REV)に応答してトランジションのビット数が減るように改造された画素データ(VD)を復元させて出力する。これはタイミング制御部でデータ電送の際に電磁気的干渉

を防ぐためである。

(EMI)を最小化するために、トランジションされるビット数が基準値を超える画素データ(VD)はトランジションのビット数が減るように変造して供給するためである。

【0009】D A C部(18)は、ラッチ部(16)からの画素データ(VD)を同時に正極及び負極性の画素電圧信号に変換して出力する。このために、D A C部(18)はラッチ部(16)に共通接続されたPデコーディング部(20)及びNデコーディング部(22)と、Pデコーディング部(20)及びNデコーディング部(22)の出力信号を選択するためのマルチブレクサ(24)とを具備する。Pデコーディング部(20)に含まれるn個のPデコーダは、ラッチ部(16)から同時に入力されるn個の画素データをガンマ電圧部(12)からの正極性のガンマ電圧を利用して正極性の画素電圧信号に変換する。Nデコーディング部(22)に含まれるn個のNデコーダは、ラッチ部(16)から同時に入力されるn個の画素データをガンマ電圧部(12)からの負極性のガンマ電圧を利用して負極性の画素電圧信号に変換する。マルチブレクサ(24)は、信号制御部(10)からの極性制御信号(POL)に応答してPデコーディング部(20)からの正極性の画素電圧信号またはNデコーディング部(22)からの負極性の画素電圧信号を選択して出力する。

【0010】出力バッファ部(26)に含まれるn個の出力バッファは、n個のデータライン(D1乃至Dn)に直列にそれぞれ接続された電圧追従機で構成される。このような出力バッファはD A C部(18)からの画素電圧信号を信号緩衝してデータライン(DL1乃至DLn)に供給する。

【0011】このように従来のデータ駆動I C(4)のそれぞれは、n個のデータライン(DL1乃至DLn)を駆動するために、n個ずつのラッチと2n個のデコーダを含まなければならない。この結果、従来のデータ駆動C(4)は、その構成が複雑で製造単価が相対的に高い短所を有する。

### 【0012】

【発明が解決しようとする課題】従って本発明の目的は、D A C部を時分割駆動して出力バッファ部を分離して液晶パネルの上に実装することにより、でD A C・I C及びT C Pの数を減らすことができる液晶表示装置のデータ駆動装置及び方法を提供することである。

### 【0013】

【課題を解決するための手段】前記目的を達成するため、本発明の一つ特徴による液晶表示装置のデータ駆動装置は、入力されたn個(nは正数)ずつの画素データを画素電圧信号に変換して少なくとも2分割して出するデジタル-アナログ変換集積回路と、デジタル-アナログ変換集積回路から少なくとも2分割されて供給される画素電圧信号をそれぞれ入力してn個ずつのデータラ

インに信号緩衝させて出力する、前記デジタル-アナログ変換集積回路のそれぞれに少なくとも2個が共通に接続されたnチャンネルの出力バッファ集積回路と、デジタル-アナログ変換集積回路及び出力バッファの集積回路を制御すると共に前記デジタル-アナログ変換集積回路のそれぞれに供給する2n個の画素データを前記少なくとも2個の出力バッファの集積回路に供給される順序に対応して再整列させて、n個ずつの画素データに構成される少なくとも2個の区間に時分割して供給するタイミング制御部とを具備しており、前記デジタル-アナログ変換集積回路は液晶パネルに接続されるテーブ・キャリアー・パッケージ上に実装されており、前記出力集積回路は前記液晶パネル上に実装されている。

【0014】ここで、前記デジタル-アナログ変換集積回路のそれぞれは、前記タイミング制御部の制御に応答してサンプリング信号を順次的に出力するシフト・レジスタ部と、タイミング制御部と前記サンプリング信号に応答して前記タイミング制御部から入力されるn個の画素データを順次的にラッチして同時に出力するラッチ部と、入力ガンマ電圧を利用して前記n個の画素データを正極性及び負極性の画素電圧信号に同時に変換して、前記タイミング制御部の極性の制御信号に応答するn個の画素電圧信号を選択して前記少なくとも2個の出力バッファ集積回路のそれぞれに供給するデジタル-アナログ変換部とを具備することを特徴とする。

【0015】そして、出力バッファ集積回路のそれぞれは、前記デジタル-アナログの変換集積回路で出力されるn個の画素電圧信号のうちの1/2n個の画素電圧信号を入力して前記タイミング制御部のソース入力インターブル信号に応答してn個の出力ラインに選択的に供給するデマルチブレクサと、前記n個のデータラインに接続されてデマルチブレックサから1/2n個ずつ入力される画素電圧信号をホールディングしてn個の画素電圧信号がすべて入力されると信号緩衝させて出力する出力バッファ部とを具備することを特徴とする。

【0016】本発明の異なる特徴による液晶表示装置のデータ駆動装置は、入力されたn個(nは正数)ずつの画素データを画素電圧信号に変換して、変換されたn個の画素電圧信号をk個(kは正数、k < n)ずつ時分割して出力するデジタル-アナログ変換集積回路と、デジタル-アナログ変換集積回路からk個ずつ供給される画素電圧信号をホールディングして2n個の画素電圧信号がすべて入力されると信号緩衝させて2n個のデータラインに同時に出力する2nチャンネルの出力バッファの集積回路と、デジタル-アナログ変換集積回路及び出力バッファの集積回路を制御すると共に前記デジタル-アナログ変換集積回路のそれぞれに供給する2n個の画素データを前記n個ずつ時分割して供給するタイミング制御部とを具備しており、デジタル-アナログ変換集積回路は液晶パネルに接続されるテーブ・キャリア・パッケ

ージ上に実装されており、出力バッファの集積回路は前記液晶パネル上に実装されている。

【0017】ここで、デジタル-アナログ変換集積回路のそれぞれは、前記タイミング制御部の制御に応答してサンプリング信号を順次的に出力するシフト・レジスタ部と、タイミング制御部の制御とサンプリング信号に応答してタイミング制御部から入力されるn個の画素データを順次的にラッチして同時に出力するラッチ部と、入力ガンマ電圧を利用してn個の画素データを正極性及び負極性の画素電圧信号に同時に変換して、タイミング制御部の極性の制御信号に応答するn個の画素電圧信号を選択すると同時に、タイミング制御部の選択制御信号に応答してそのn個の画素電圧信号を時分割してk個ずつ出力するデジタル-アナログ変換部とを具備することを特徴とする。

【0018】そして、出力バッファ集積回路のそれぞれは、デジタル-アナログ変換集積回路で出力されるk個ずつの画素電圧信号を入力してタイミング制御部のソース入力イネーブル信号に応答して2n個の出力ラインに選択的に供給するデマルチプレクサと、2n個のデータラインに接続されて前記デマルチプレクサからk個ずつ入力される画素電圧信号をホールディングして2n個の画素電圧信号がすべて入力されると信号緩衝させて出力する出力バッファ部とを具備することを特徴とする。

【0019】本発明のまた異なる特徴による液晶表示装置のデータ駆動装置は、入力されたn個(nは正数)ずつの画素データを画素電圧信号に変換して変換されたn個の画素電圧信号をk個(kは正数、k < n)ずつ時分割して出力するデジタル-アナログの変換の集積回路と、デジタル-アナログ変換集積回路からk個ずつ供給される画素電圧信号をホールディングしてn個の画素電圧信号がすべて入力されると信号緩衝させてn個のデータラインに出力して、デジタル-アナログ変換集積回路のそれぞれに少なくとも2個が共通に接続された出力バッファの集積回路と、デジタル-アナログ変換集積回路及び出力バッファの集積回路のそれぞれを制御すると共にデジタル-アナログ変換集積回路に供給する画素データを前記n個ずつの画素データに構成される少なくとも2個の区間に時分割して供給するタイミング制御部とを具備しており、デジタル-アナログ変換集積回路は液晶パネルに接続されるテーブ・キャリア・パッケージ上に実装されており、出力バッファの集積回路は前記液晶パネル上に実装されている。

【0020】ここで、デジタル-アナログ変換集積回路のそれぞれは、タイミング制御部の制御に応答してサンプリング信号を順次的に出力するシフト・レジスタ部と、タイミング制御部の制御とサンプリング信号に応答してタイミング制御部から入力されるn個の画素データを順次的にラッチして同時に出力するラッチ部と、入力ガンマ電圧を利用してn個の画素データを正極性及び負

極性の画素電圧信号に同時に変換して、タイミング制御部の極性の制御信号に応答するn個の画素電圧信号を選択すると同時に、タイミング制御部の第1選択制御信号に応答してそのn個の画素電圧信号を時分割してk個ずつ出力するデジタル-アナログ変換部と、前記タイミング制御部からの第2選択信号に応答して前記k個ずつ順次的に出力される画素電圧信号を前記少なくとも2個の出力バッファの集積回路に選択的に出力するデマルチプレクサとを具備することを特徴とする。

【0021】特に、選択制御信号はn個の画素電圧信号をk個ずつの画素電圧信号に時分割する回数に相当するビット数を有することを特徴とする。

【0022】そして、デジタル-アナログ変換集積回路のそれぞれは、タイミング制御部の制御に応答してサンプリング信号を順次的に出力するシフト・レジスタ部と、タイミング制御部の制御とサンプリング信号に応答してタイミング制御部から入力されるn個の画素データを順次的にラッチして同時に出力するラッチ部と、入力ガンマ電圧を利用してn個の画素データを正極性及び負極性の画素電圧信号に同時に変換して、タイミング制御部の極性の制御信号に応答するn個の画素電圧信号を選択して出力するデジタル-アナログ変換部と、前記n個の画素電圧信号をタイミング制御部の第1選択制御信号に応答して少なくとも2個の出力段に選択的に出力するデマルチプレクサと、少なくとも2個の出力段のそれぞれに接続されて前記n個の画素電圧信号をタイミング制御部からの第2選択信号に応答して前記k個ずつ時分割して出力する少なくとも2個のデマルチプレクサとを具備することを特徴とする。

【0023】特に、第1選択制御信号は、前記ラッチ部の出力を制御する出力イネーブル信号の周期毎に選択制御信号の論理状態が反転されて、第2選択制御信号は前記n個の画素電圧信号を前記k個ずつの画素電圧信号に時分割する回数に相当するビット数を有することを特徴とする。

【0024】そして、出力バッファ集積回路のそれぞれは、デジタル-アナログ集積回路で出力されるk個ずつの画素電圧信号を入力してタイミング制御部のソース入力イネーブル信号に応答してn個の出力ラインに選択的に供給するデマルチプレクサと、n個のデータラインに接続されてデマルチプレクサからk個ずつ入力される画素電圧信号をホールディングしてn個の画素電圧信号がすべて入力されると信号緩衝させて出力する出力バッファ部とを具備することを特徴とする。

【0025】ここで、ソース入力イネーブル信号は前記n個の画素電圧信号をk個ずつ画素電圧信号に時分割する回数に相当するビット数を有することを特徴とする。

【0026】そして、出力バッファ部は、n個のデータラインにそれぞれ接続されるn個の出力バッファセルで構成されており、出力バッファセルのそれぞれは、直列

接続されて入力された画素電圧信号を信号緩衝する第1電圧追従機と、第1電圧追従機の入力段及び出力段の中のいずれか一つに接続されて画素電圧信号をホールディングするホールディング手段と、タイミング制御部からの出力イネーブル信号に応答してホールディングされた画素電圧信号を出力するスイッチング手段と、スイッチング手段から出力される画素電圧信号を信号緩衝して出力する第2電圧追従機とを具備することを特徴とする。

【0027】また、デジタル - アナログ変換集積回路のそれぞれは、前記デジタル - アナログ変換集積回路の構成要素のそれぞれに前記タイミング制御部からの制御信号と画素データを中継して供給する信号制御部と、入力ガンマの基準電圧を細分化してガンマ電圧を発生するガンマ電圧部とを更に具備することを特徴とする。

【0028】特に、タイミング制御部は、前記画素データをオド画素データの電送ラインとイブン画素データの電送ラインを通して前記デジタル-アナログの変換集積回路のそれぞれに供給して、タイミング制御部からデジタル-アナログ変換集積回路に供給される制御信号と画素データの周波数が少なくとも2倍以上増加されていることを特徴とする。

【0029】これとは異なり、デジタル - アナログ変換集積回路を第1及び第2ブロックに分けて、タイミング制御部は画素データを第1オド画素データの電送ラインと第1イブン画素データの電送ラインを通して第1ブロックに含まれるデジタル - アナログ変換集積回路に供給して、画素データを第2オド画素データの電送ラインと第2イブン画素データの電送ラインを通して第2ブロックに含まれるデジタル - アナログ変換集積回路に供給することを特徴とする。

【0030】本発明の一つの特徴による液晶表示装置のデータ駆動方法は、液晶パネルに配置されたデータラインを駆動するためのデータ駆動装置の駆動方法において、データ駆動装置は、タイミング制御部に接続されたデジタル - アナログ変換集積回路と、 $n$  個 ( $n$  は正数) ずつのデータラインに接続された出力バッファの集積回路で構成されており、タイミング制御部で入力された画素データを再整列してデジタル - アナログ変換集積回路のそれぞれで入力された  $n$  個の画素データを画素電圧信号に変換して、変換された画素電圧信号を  $1/2 n$  個ずつ分割して 2 個の出力バッファの集積回路のそれぞれに output する段階と、出力バッファの集積回路のそれぞれで  $1/2 n$  個ずつ供給される画素電圧信号をホールディングする段階と、前記タイミング制御部でデジタル - アナログ変換集積回路などのそれに残りの  $n$  個の画素データを供給する段階と、デジタル - アナログ変換集積回路のそれぞれで入力された残りの  $n$  個の画素データをアナログ形態である画素電圧信号に変換して、変換された画素電圧信号を  $1/2 n$  個ずつ分割して 2 個の出力バッファの集積回路のそれぞれに出力する段階と、出力バッ

ファの集積回路のそれぞれで 1 / 2 個ずつ供給される画素電圧信号を前記段階でホールディングされた画素電圧信号と共に信号緩衝させてデータラインに同時に供給する段階を含む。

【0031】本発明の異なる特徴による液晶表示装置のデータ駆動方法は、液晶パネルに配置されたデータラインを駆動するためのデータ駆動装置の駆動方法において、データ駆動装置は、タイミング制御部に接続されたデジタル-アナログ変換集積回路と、デジタル-アナログ変換集積回路のそれぞれに接続されると共に $2n$ 個( $n$ は正数)ずつのデータラインに接続された出力バッファの集積回路で構成されて、タイミング制御部でデジタル-アナログ変換集積回路のそれぞれに $2n$ 個の画素データのうちの $n$ 個の画素データを供給する段階と、デジタル-アナログ変換集積回路のそれぞれで入力された $n$ 個の画素データを画素電圧信号に変換して、変換された画素電圧信号を $k$ 個( $k$ は正数、 $k < n$ )ずつ分割して該当する出力バッファ集積回路に出力する段階と、前記出力バッファの集積回路のそれぞれで $k$ 個ずつ供給される画素電圧信号を順次的にホールディングして $n$ 個の画素電圧信号をホールディングする段階と、タイミング制御部で前記デジタル-アナログ変換集積回路のそれに残りの $n$ 個の画素データを供給する段階と、デジタル-アナログ変換集積回路のそれぞれで入力された残りの $n$ 個の画素データをアナログ形態である画素電圧信号に変換して、変換された画素電圧信号を $k$ 個ずつ分割して該当する出力バッファの集積回路に出力する段階と、出力バッファ集積回路のそれぞれで $k$ 個ずつ供給される画素電圧信号をホールディングして $n$ 個の画素電圧信号が入力される段階でホールディングされた $n$ 個の画素電圧信号と共に信号緩衝させて $2n$ 個のデータラインに同時に供給する段階とを含む。

【 0 0 3 2 】

【作用】本発明による液晶表示装置のデータ駆動装置及び方法では、D A C 部を時分割駆動して出力バッファを分離して液晶パネルの上に実装することで、D A C・I C 及びT C P の数を半分に減らすことができるようになるので、製造単価を節減することができる。また、本発明による液晶表示装置のデータ駆動装置及び方法によると、データ駆動I C で出力バッファ部を分離してD A C 機能だけをさせるようにすることで駆動I C の構成がより簡素化されて製造効率を向上させることができる。更に、本発明による液晶表示装置のデータ駆動装置及び方法によるとデータ駆動I C がD A C・I C と出力バッファI C に分離されて集積化することでI C の精密度を向上させることができるので、I C の駆動信頼性を向上させることができる。

【 0 0 3 3 】

【発明の実施態様】以下、図3乃至図11を参照して本発明の好ましい実施例について説明する。

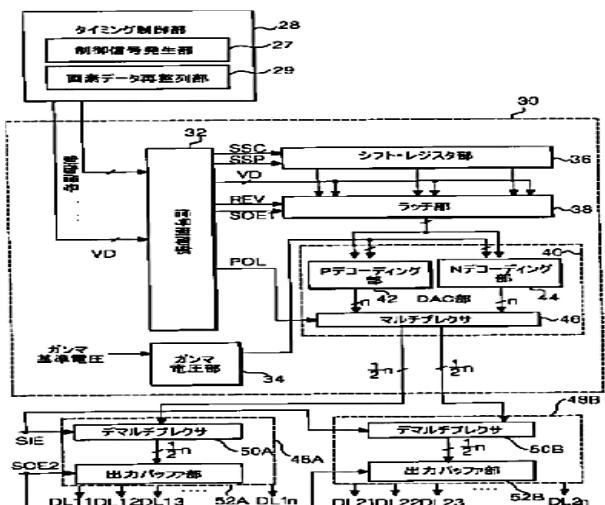

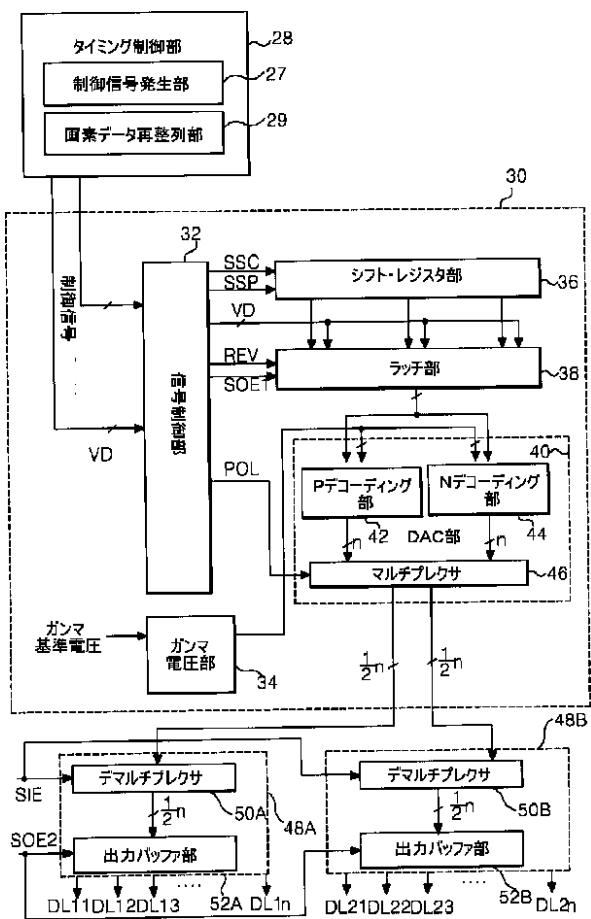

【0034】図3は本発明の第1実施例による液晶表示装置のデータ駆動ユニットの構成を図示したブロック図である。

【0035】図3でタイミング制御部(28)に接続されたデータ駆動ユニットは、大きくDAC機能をするDAC手段と出力バッファリング機能をするバッファリング手段に分離されて別途のチップに集積化される。換言すると、もう一度言って、データ駆動ユニットは、一つのDAC・IC(30)と少なくとも2個の出力バッファIC(48A、48B)に分離されて構成される。ここでは一つのDAC・IC(30)に第1及び第2出力バッファIC(48A、48B)が共通に接続された場合を例えて説明する。これによりDAC・IC(30)は2個の区間に時分割されてDAC機能を遂行することでn個ずつの出力チャンネルを有する第1及び第2出力バッファIC(48A、48B)を通して2n個のデータライン(DL11乃至DL1n、DL21乃至DL2n)を駆動する。

【0036】タイミング制御部(28)は、データの駆動ユニットを制御するための各種の制御信号と画素データ(VD)を供給する。このためにタイミング制御部(28)は、制御信号発生部(27)と画素データ再整列部(29)とを具備する。

【0037】制御信号発生部(27)は、外部から入力される垂直及び水平の同期信号とドットクロック信号を利用してデータユニットを制御するための各種の制御信号(SSP、SSC、SOE1、REV、POL、SIE、SOE2など)を発生する。

【0038】画素データ再整列部(29)は、2n個のデータライン(DL11乃至DL1n、DL21乃至DL2n)に供給される2n個の画素データ(VD)の整列順序を再整列した後、n個ずつ時分割して順次的に供給する。例えば、画素データ再整列部(29)は、n個ずつ供給される画素データ(VD)に第1及び第2出力バッファIC(48A)に供給される画素データが1/2n個ずつ含まれるように再整列して供給する。また、画素データ再整列部(29)は、伝送周波数を減らすために画素データ(VD)をイブン画素データ(VDeven)とオド画素データ(VDodd)に分けてそれぞれの伝送ラインを通して同時に供給する。ここで、イブン画素データ(VDeven)とオド画素データ(VDodd)のそれぞれは赤(R)、緑(G)、青(B)画素データを含む。特に、画素データ再整列部(29)は、データ電送の際に電磁気的干渉(EMI)を最小化するために、トランジションされるビット数が基準値を超えた場合は、画素データ(VD)はトランジションのビット数を減らすように変造して供給する。

【0039】DAC・IC(30)には、2n個のデータライン(DL11乃至DL1n、DL21乃至DL2n)に供給される2n個の画素データがn個ずつ時分割

されて入力される。DAC・IC(30)は先に入力されたn個の画素データをアナログ信号である画素電圧信号に変換する。そしてDAC・IC(30)は、アナログ信号に変換されたn個の画素電圧信号を更に1/2n個ずつ物理的に分割して第1及び第2出力バッファIC(50)に同時に供給する。続いてDAC・IC(30)は次に入力された残りのn個の画素データに対して前記のようなDAC動作を繰り返す。

【0040】このために、DAC・IC(30)は、順次的なサンプリング信号を供給するシフト・レジスタ部(36)と、サンプリング信号に応答して画素データ(VD)を順次的にラッチして同時に出力するラッチ部(38)と、ラッチ部(38)からの画素データ(VD)を画素電圧信号に変換するDAC部(40)とを具備する。また、DAC・IC(30)は、タイミング制御部(28)から供給される制御信号と画素データ(VD)を中継する信号制御部(32)と、DAC部(40)に必要とする正極性及び負極性のガンマ電圧を供給するガンマ電圧部(34)とを更に具備する。

【0041】信号制御部(32)は、タイミング制御部(28)からの各種制御信号(SSP、SSC、SOE、REV、POLなど)と画素データ(VD)を該当する構成要素に出力するように制御する。

【0042】ガンマ電圧部(34)は、ガンマ基準電圧の発生部(図示しない)から入力される多数個のガンマ基準電圧をグレイ別に細分化して出力する。

【0043】シフト・レジスタ部(36)に含まれるn/6つのシフト・レジスタは、信号制御部(32)からのソース・スタート・パルス(SSP)をソース・サンプリング・クロック信号(SSC)により順次的にシフトさせてサンプリング信号に出力する。

【0044】ラッチ部(38)は、シフト・レジスタ部(36)からのサンプリング信号に応答して信号の制御部(32)からの画素データ(VD)を一定単位ずつ順次的にサンプリングしてラッチする。このために、ラッチ部(38)はn個の画素データ(VD)をラッチするためにn個のラッチで構成されており、そのラッチのそれぞれは画素データ(VD)のビット数(3ビットまたは6ビット)に対応する大きさを有する。このようなラッチ部(38)は、サンプリング信号毎に信号制御部(32)を経由して供給されるイブン画素データ(VDeven)とオド画素データ(VDodd)、即ち、6個の画素データを同時にラッチする。続いて、ラッチ部(38)は、信号制御部(32)からの第1ソース出力イネーブル信号(SOE1)に応答してラッチされたn個の画素データ(VD)を同時に出力する。この場合、ラッチ部(32)は、データ反転選択信号(REV)に応答してトランジションビット数を減らすように変造された画素データ(VD)を復元させて出力する。

【0045】DAC部(40)は、ラッチ部(38)か

らのn個の画素データ(VD)を同時に正極性及び負極性の画素電圧信号に変換して極性制御信号(POL)に応答して正極性及び負極性の画素電圧信号を選択的に出力する。このために、DAC部(40)は、ラッチ部(38)に共通接続されたPデコーディング部(42)及びNデコーディング部(44)と、Pデコーディング部(42)及びNデコーディング部(44)の出力信号を選択するためのマルチブレクサ(46)とを具備する。

【0046】Pデコーディング部(42)に含まれるn個のPデコーダは、ラッチ部(38)から同時に入力されるn個の画素データを、ガンマ電圧部(34)からの正極性のガンマ電圧を利用して正極性の画素電圧信号に変換する。Nデコーディング部(44)に含まれるn個のNデコーダは、ラッチ部(38)から同時に入力されるn個の画素データをガンマ電圧部(34)からの負極性のガンマ電圧を利用して負極性の画素電圧信号に変換する。マルチブレクサ(46)は、信号制御部(32)からの極性制御信号(POL)に応答してPデコーディング部(42)からの正極性の画素電圧信号またはNデコーディング部(44)からの負極性の画素電圧信号を選択してn個の画素電圧信号を出力する。

【0047】出力バッファ部(26)に含まれるn個の出力バッファは、n個のデータライン(DL1乃至DLn)に直列にそれぞれ接続された電圧追従機で構成される。このような出力バッファは、DAC部(40)からの画素電圧信号を信号緩衝してデータライン(DL1乃至DLn)に供給する。特に、マルチブレクサ(46)は、出力チャンネルのうちの1/2n個の出力チャンネルは、第1出力バッファIC(48A)に接続されおり、残りの1/2n個の出力チャンネルは第2出力バッファIC(48B)に接続されている。これにより、マルチブレクサ(46)で出力されるn個の画素電圧信号は、1/2n個ずつ分離して第1及び第2出力バッファIC(48A、48B)に同時に供給される。

【0048】第1及び第2出力バッファIC(48A、48B)のそれぞれは、DAC・IC(30)から1/2n個ずつ入力される画素電圧信号をサンプリングした後、ホールディングしてn個のデータライン(DL11乃至DL1n、DL21乃至DL2n)に同時に出力する。このために、第1及び第2出力バッファIC(48A、48B)のそれぞれは、マルチブレクサ(50Aまたは50B)と出力バッファ部(52Aまたは52B)で構成される。

【0049】マルチブレクサ(50Aまたは50B)のそれぞれは、DAC・IC(30)から同時に入力される1/2n個ずつの画素電圧信号をタイミング制御部(28)から供給されるソース入力イネーブルに応答して出力バッファ部(52A、52B)に含まれるn個の出力バッファセルに選択的に供給する。

10 【0050】出力バッファ部(52A、52B)のそれぞれは、マルチブレクサ(50Aまたは50B)のそれから供給される1/2n個ずつの画素電圧信号を順次的に入力してホールディングさせる。このように、出力バッファ部(52A、52B)のそれに1/2n個ずつ入力されたn個の画素電圧信号がすべて入力されてホールディングされると、タイミング制御部(28)からの第2ソース出力イネーブル信号(SEO2)に応答してホールディングされたn個の画素電圧信号を同時に該当するデータライン(DL11乃至DL1n、DL21乃至DL2n)に供給する。このような出力バッファ部(52A、52B)のそれぞれは、該当するデータライン(DL11乃至DL1n、DL21乃至DL2n)に一对一に接続されるn個の出力バッファセルで構成される。

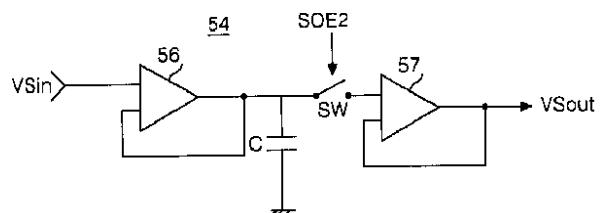

20 【0051】図4に図示されたように、出力バッファセル(54)のそれぞれは、入力画素電圧信号(VSin)を緩衝して出力する第1電圧追従機(56)と、第1電圧追従機(56)からの画素電圧信号をホールディングするためのキャパシティ(C)と、タイミング制御部(38)からのソース出力イネーブル信号(SEO2)に応答してホールディングされた画素電圧信号を出力するスイッチング素子(SW)と、スイッチング素子(SW)に接続されて画素電圧信号を信号緩衝して出力の画素電圧信号(VSout)に出力するための第2電圧追従機(57)で構成される。ここで、キャパシティは、第1電圧追従機(56)の出力段と基底電圧源の間に接続するか第1電圧追従機(56)の入力段と基底電圧源の間に接続することができる。

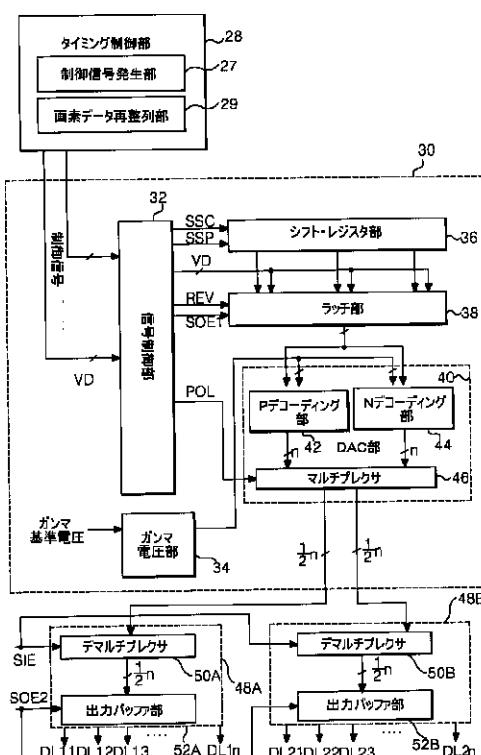

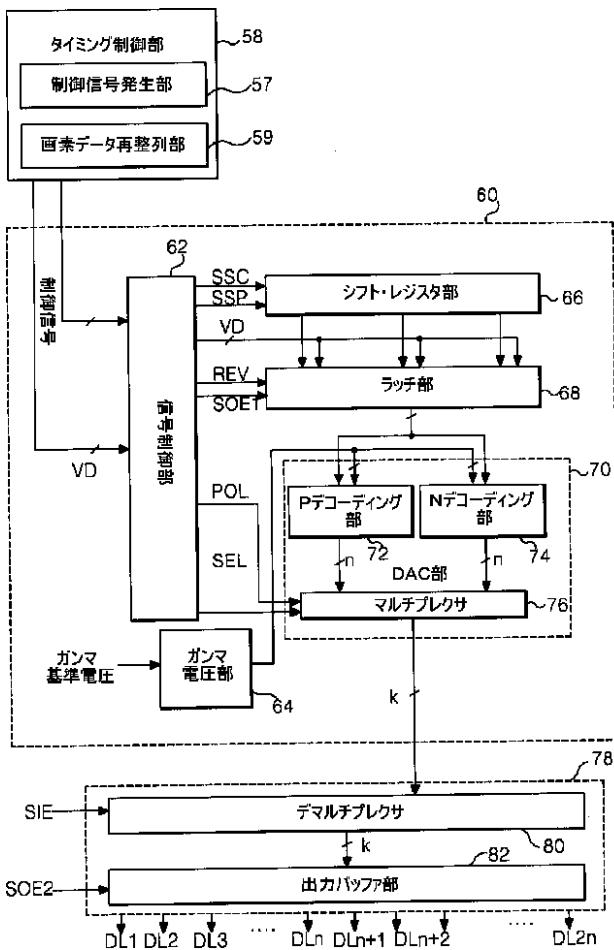

30 【0052】図5は、本発明の第2実施例による液晶表示装置のデータ駆動ユニットの構成を図示したブロック図である。図5でタイミング制御部(58)に接続されたデータ駆動ユニットは、図3に図示されたデータユニットと対比して大きく異なる点は出力バッファIC(78)が2n出力チャンネルを有することである。

【0053】タイミング制御部(58)は、データ駆動ユニットを制御するための各種の制御信号と画素データ(VD)とを供給する。このために、タイミング制御部(58)は制御信号発生部(57)と画素データ再整列部(59)とを具備する。

【0054】制御信号発生部(57)は、外部から入力される垂直及び水平の同期信号とドットクロック信号を利用してデータ駆動ユニットを制御するための各種の制御信号(SSP、SSC、SOE1、REV、POL、SIE、SOE2など)を発生する。

【0055】画素データ再整列部(59)は、2n個のデータライン(DL11乃至DL1n、DL21乃至DL2n)に供給される2n個の画素データ(VD)を時分割して順次的に供給する。また、画素データ再整列部(59)は、伝送周波数を減らすために画素データ(VD)

D) をイブン画素データ (V D even) とオド画素データ (V D odd) に分けて、それぞれの伝送ラインを通して同時に output する。ここで、イブン画素データ (V D even) とオド画素データ (V D odd) のそれぞれは、赤 (R)、緑 (G)、青 (B) 画素データを含む。特に、画素データ再整列部 (59) は、データ電送の際に電磁気的干渉 (EMI) を最小化するために、トランジションされるビット数が基準値を超えた場合は、画素データ (V D) はトランジションのビット数を減らすように変造して出力する。

【0056】D A C · I C (60) には、2n 個のデータライン (D L 1 1 乃至 D L 1 n, D L 2 1 乃至 D L 2 n) に供給される 2n 個の画素データが n 個ずつ時分割されて入力される。D A C · I C (60) は、先に入力された n 個の画素データをアナログ信号である画素電圧信号に変換する。そして、D A C · I C (60) は、アナログ信号に変換された n 個の画素電圧信号を更に 1/2n 個ずつ物理的に分割して第 1 及び第 2 出力バッファ I C (78) に同時に供給する。続いて、D A C · I C (60) は、次に入力された残りの n 個の画素データに 20 対して前記のような D A C 動作を繰り返す。

【0057】このために、D A C · I C (60) は、順次的なサンプリング信号を供給するシフト・レジスタ部 (66) と、サンプリング信号に応答して画素データ (V D) を順次的にラッチして同時に output するラッチ部 (68) と、ラッチ部 (68) からの画素データ (V D) を画素電圧信号に変換する D A C 部 (70) とを具備する。また、D A C · I C (60) はタイミング制御部 (58) から供給される制御信号と画素データ (V D) とを中継する信号制御部 (62) と、D A C 部 (70) に必要とする正極性及び負極性のガンマ電圧を供給するガンマ電圧部 (64) とを更に具備する。

【0058】信号制御部 (62) は、タイミング制御部 (58) からの各種制御信号 (S S P, S S C, S O E, R E V, P O L など) と画素データ (V D) を該当する構成要素で出力するように制御する。

【0059】ガンマ電圧部 (64) は、ガンマ基準電圧の発生部 (図示しない) から入力される多数個のガンマ基準電圧をグレイ別に細分化して出力する。

【0060】シフト・レジスタ部 (66) に含まれる n/6 つのシフト・レジスタは、信号制御部 (62) からのソース・スタート・パルス (S S P) をソース・サンプリング・クロック信号 (S S C) により順次的にシフトさせてサンプリング信号として出力する。

【0061】ラッチ部 (68) は、シフト・レジスタ部 (66) からのサンプリング信号に応答して、信号制御部 (62) からの画素データ (V D) を一定単位ずつ順次的にサンプリングしてラッチする。このためにラッチ部 (68) は、n 個の画素データ (V D) をラッチするために n 個のラッチで構成されており、そのラッチのそ 50

れぞれは、画素データ (V D) のビット数 (3 ビットまたは 6 ビット) に対応する大きさを有する。このようなラッチ部 (38) は、サンプリング信号毎に信号制御部 (62) を経由して供給されるイブン画素データ (V D even) とオド画素データ (V D odd)、即ち、6 個の画素データを同時にラッチする。続いて、ラッチ部 (68) は、信号制御部 (62) からの第 1 ソース出力イネーブル信号 (S O E 1) に応答してラッチされた n 個の画素データ (V D) を同時に output する。この場合、ラッチ部 (62) は、データ反転選択信号 (R E V) に応答してトランジションビット数を減らすように変造された画素データ (V D) を復元させて出力する。

【0062】D A C 部 (70) は、ラッチ部 (68) からの n 個の画素データ (V D) を同時に正極及び負極性の画素電圧信号に変換して、極性制御信号 (P O L) に応答して正極性及び負極性の画素電圧信号を選択的に出力する。このために、D A C 部 (70) は、ラッチ部 (68) に共通接続された P デコーディング部 (72) 及び N デコーディング部 (74) と、P デコーディング部 (72) 及び N デコーディング部 (74) の出力信号を選択するためのマルチプレクサ (76) とを具備する。

【0063】P デコーディング部 (72) に含まれる n 個の P デコーダは、ラッチ部 (68) から同時に入力される n 個の画素データをガンマ電圧部 (64) からの正極性のガンマ電圧を利用して正極性の画素電圧信号に変換する。N デコーディング部 (74) に含まれる n 個の N デコーダは、ラッチ部 (68) から同時に入力される n 個の画素データをガンマ電圧部 (64) からの負極性のガンマ電圧を利用して負極性の画素電圧信号に変換する。マルチプレクサ (76) は、信号制御部 (62) からの極性制御信号 (P O L) に応答して P デコーディング部 (72) からの正極性の画素電圧信号または N デコーディング部 (74) からの負極性の画素電圧信号を選択すると同時に、選択制御信号 (S E L) に応答して n 個の画素電圧信号を k 個ずつ分けて出力する。この場合、選択制御信号 (S E L) のビット数は、n 個の画素電圧信号を分割する回数 (j) により定められる。例えば、n 個の画素電圧信号を 8 (j = 8) 分割して出力する場合に、選択制御信号 (S E L) は 3 ビットに構成されると十分である。このように、D A C 部 (70) は、n 個ずつの画素データを画素電圧信号に変換して n 個の画素電圧信号をそれより小さい k 個ずつ時分割して出力する。

【0064】出力バッファ I C (78) は D A C · I C (60) から k 個ずつ入力される画素電圧信号をサンプリングした後、ホールディングして 2n 個のデータライン (D L 1 乃至 D L 2 n) のうち n 個のデータラインに同時に output する。このような出力バッファ I C (78) は、デマルチプレクサ (80) と出力バッファ部 (8

2)とを具備する。

【0065】デマルチプレクサ(80)は、マルチプレクサ(76)からk個ずつ入力される画素電圧信号を、タイミング制御部(58)から供給されるソース入力イネーブル(SIE)に応答して、出力バッファ部(82)に含まれる2n個の出力バッファセルのうちのn個の出力バッファセルにk個ずつ選択的に供給する。この場合、ソース入力イネーブル(SIE)もまた、前記選択制御信号(SEL)と同時にn個の画素電圧信号が分割された回数(j)に相当するビット数を有する。

【0066】出力バッファ部(82)は、図5に示されたような構成を有して2n個のデータライン(DL1乃至DL2n)に一対一に接続される2n個の出力バッファセルとを具備する。このように出力バッファ部(82)は、デマルチプレクサ(80)から供給されるk個ずつの画素電圧信号を順次的に入力してn個の画素電圧信号がホールディングされるようにする。このようなn個の画素電圧信号のそれをホールディングしているn個の出力バッファセルは、前述したDAC変換動作を繰り返して残りのn個の出力バッファセルに残りのn個の画素電圧信号がすべて入力されるまでホールディング状態を維持する。そして、出力バッファ部(82)にk個ずつ入力された2n個の画素電圧信号がすべて入力されてホールディングされると、タイミング制御部(58)からの第2ソース出力イネーブル信号(SEO2)に応答してホールディングされた2n個の画素電圧信号を2n個のデータライン(DL1乃至DL2n)に同時に供給する。

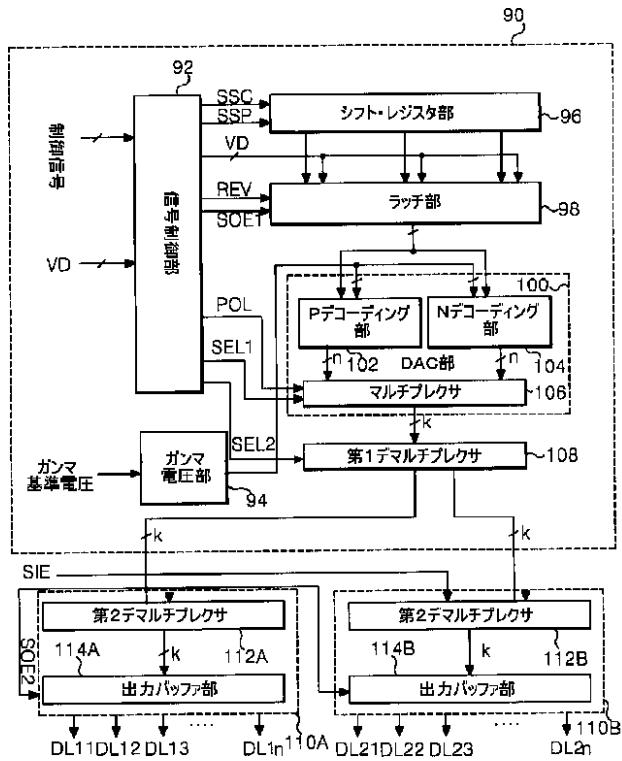

【0067】図6は、本発明の第3実施例による液晶表示装置のデータ駆動ユニットの構成を示したブロック図である。図6に示されたデータ駆動ユニットは、図3に示されたデータ駆動ユニットと対比してDAC·IC(90)の出力段に第1出力バッファIC(110A)と第2出力バッファIC(110B)を順次的に駆動するための第1デマルチプレクサ(108)が更に追加されたことを除いては同一の構成要素を具备する。そして、図6に示されたデータユニットは、図5に示されたタイミング制御部(58)のような制御方式で制御される。

【0068】タイミング制御部(58)は、データ駆動ユニットを制御するための各種の制御信号と画素データ(VD)を供給する。このためにタイミング制御部(58)は、制御信号発生部(57)と画素データ再整列部(59)とを具备する。

【0069】制御信号発生部(57)は、外部から入力される垂直及び水平の同期信号とドットクロック信号を利用してデータユニットを制御するための各種の制御信号(SSP、SSC、SOE1、REV、POL、SIE、SOE2など)を発生する。

【0070】画素データ再整列部(59)は、2n個の

データライン(DL11乃至DL1n、DL21乃至DL2n)に供給される2n個の画素データ(VD)を時分割して順次的に供給する。また、画素データ再整列部(59)は、伝送周波数を減らすために画素データ(VD)をイブン画素データ(VDeven)とオド画素データ(VDodd)に分けて、それぞれの传送ラインを通して同時に outputする。ここで、イブン画素データ(VDeven)とオド画素データ(VDodd)のそれぞれは、赤(R)、緑(G)、青(B)画素データを含む。特に、10画素データ再整列部(59)は、データ電送の際に電磁気的干渉(EMI)を最小化するために、トランジションされるビット数が基準値を超えた場合は、画素データ(VD)はトランジションのビット数を減らすように変造して出力する。

【0071】DAC·IC(90)には、2n個のデータライン(DL11乃至DL1n、DL21乃至DL2n)に供給される2n個の画素データがn個ずつ時分割されて入力される。DAC·IC(90)は、先に入力されたn個の画素データをアナログ信号である画素電圧信号に変換する。そしてDAC·IC(90)は、アナログ信号に変換されたn個の画素電圧信号をまたk個(<n>ずつ分割して第1及び第2出力バッファIC(110A、110B)に選択的に供給する。

【0072】このために、DAC·IC(90)は、順次的なサンプリング信号を供給するシフト·レジスタ部(66)と、サンプリング信号に応答して画素データ(VD)を順次的にラッチして同時に出力するラッチ部(98)と、ラッチ部(98)からの画素データ(VD)を画素電圧信号に変換するDAC部(100)と、DAC(100)からの画素電圧信号を2個の出力バッファIC(110A、110B)に選択的に供給する第1デマルチプレクサ(108)とを具备する。また、DAC·IC(90)は、タイミング制御部(58)から供給される各種の制御信号と画素データ(VD)を中継する信号制御部(92)と、DAC部(100)に必要とする正極性及び負極性のガンマ電圧を供給するガンマ電圧部(94)とを更に具备する。

【0073】信号制御部(92)は、タイミング制御部(58)からの各種の制御信号(CLK、SSP、SSC、SOE、REV、POL、SEL1、SEL2など)と画素データ(VD)を該当する構成要素に出力するように制御される。

【0074】ガンマ電圧部(94)は、ガンマ基準電圧の発生部(図示しない)から入力される多数個のガンマ基準電圧をグレイ別に細分化して出力する。

【0075】シフト·レジスタ部(96)に含まれるn/6個のシフト·レジスタは、信号制御部(92)からのソース·スタート·パルス(SSP)をソース·サンプリング·クロック信号(SSC)により順次的にシフトさせサンプリング信号として出力する。

【0076】ラッチ部(98)は、シフト・レジスタ部(96)からのサンプリング信号に応答して、信号制御部(92)からの画素データ(VD)を一定単位ずつ順次的にサンプリングしてラッチする。このためにラッチ部(98)は、n個の画素データ(VD)をラッチするためにn個のラッチで構成されており、そのラッチのそれぞれは、画素データ(VD)のビット数(3ビットまたは6ビット)に対応する大きさを有する。このようなラッチ部(98)は、サンプリング信号毎に信号制御部(92)を経由して供給されるイブン画素データ(VD even)とオド画素データ(VD odd)、即ち、6個の画素データを同時にラッチする。続いて、ラッチ部(98)は、信号制御部(92)からの第1ソース出力イネーブル信号(SOE1)に応答してラッチされたn個の画素データ(VD)を同時に出力する。この場合、ラッチ部(98)はデータ反転選択信号(REV)に応答してトランジションビット数を減らすように変造された画素データ(VD)を復元させて出力する。

【0077】DAC部(100)は、ラッチ部(98)からのn個の画素データ(VD)を同時に正極及び負極性の画素電圧信号に変換して、極性制御信号(POL)に応答して正極性及び負極性の画素電圧信号を選択的に出力する。このために、DAC部(100)は、ラッチ部(98)に共通接続されたPデコーディング部(102)及びNデコーディング部(104)と、Pデコーディング部(102)及びNデコーディング部(104)の出力信号を選択するためのマルチプレクサ(106)とを具備する。

【0078】Pデコーディング部(102)に含まれるn個のPデコーダは、ラッチ部(98)から同時に入力されるn個の画素データをガンマ電圧部(94)からの正極性のガンマ電圧を利用して正極性の画素電圧信号に変換する。Nデコーディング部(104)に含まれるn個のNデコーダは、ラッチ部(98)から同時に入力されるn個の画素データをガンマ電圧部(94)からの負極性のガンマ電圧を利用して負極性の画素電圧信号に変換する。マルチプレクサ(106)は、信号制御部(92)からの極性制御信号(POL)に応答して、Pデコーダ(102)からの正極性の画素電圧信号またはNデコーダ(104)からの負極性の画素電圧信号を選択すると同時に、第1選択制御信号(SEL1)に応答してn個の画素電圧信号をk個ずつ分けて出力する。この場合、第1選択制御信号(SEL1)のビット数は、n個の画素電圧信号を分割する回数(j)により定められる。例えば、n個の画素電圧信号を8(j=8)分割して出力する場合に、第1選択制御信号(SEL1)は3ビットに構成されると十分である。このように、DAC部(100)は、n個ずつの画素データを画素電圧信号に変換して、n個の画素電圧信号をそれより小さいk個ずつ時分割して出力する。

10

【0079】第1マルチプレクサ(108)は、マルチプレクサ(106)からk個ずつ入力される画素電圧信号を、信号制御部(92)から入力される第2選択制御信号(SEL2)に応答して、第1出力バッファIC(110A)または第2出力バッファIC(110B)に出力する。この場合、第2選択制御信号(SEL2)もn個の画素電圧信号が分割された回数(j)により定められるので、前記第1選択制御信号(SEL1)と同一のビット数を有する。

【0080】第1及び第2出力バッファIC(110A、110B)のそれぞれは、DAC・IC(90)からk個ずつ入力される画素電圧信号をサンプリングした後、ホールディングしてn個のデータライン(DL11乃至DL1nまたはDL21乃至DL2n)に同時に出力する。このために、第1及び第2出力バッファIC(110A、110B)のそれぞれは、第2マルチプレクサ(112Aまたは112B)と出力バッファ部(114A、114B)で構成される。

【0081】第2マルチプレクサ(112Aまたは112B)のそれぞれは、第1マルチプレクサ(108)からk個ずつ入力される画素電圧信号を、タイミング制御部(58)から供給されるソース入力イネーブル(SIE)に応答して出力バッファ部(114A、114B)に含まれるn個の出力バッファセルに選択的に供給する。

【0082】出力バッファ部(114A、114B)のそれぞれは、該当するデータライン(DL11乃至DL1nまたはDL21乃至DL2n)に一对一に接続されており、図4に示されたような構成を有するn個の出力バッファセルで構成される。このように、出力バッファ部(114A、114B)のそれぞれは、マルチプレクサ(112A、112B)のそれから供給されるk個ずつの画素電圧信号を順次的に入力してホールディングさせる。このように出力バッファ部(114A、114B)のそれぞれにk個ずつ入力されたn個の画素電圧信号がすべて入力されてホールディングされると、タイミング制御部(58)からの第2ソース出力イネーブル信号(SEO2)に応答してホールディングされたn個の画素電圧信号を同時に該当するデータライン(DL1乃至DL2n)に供給する。

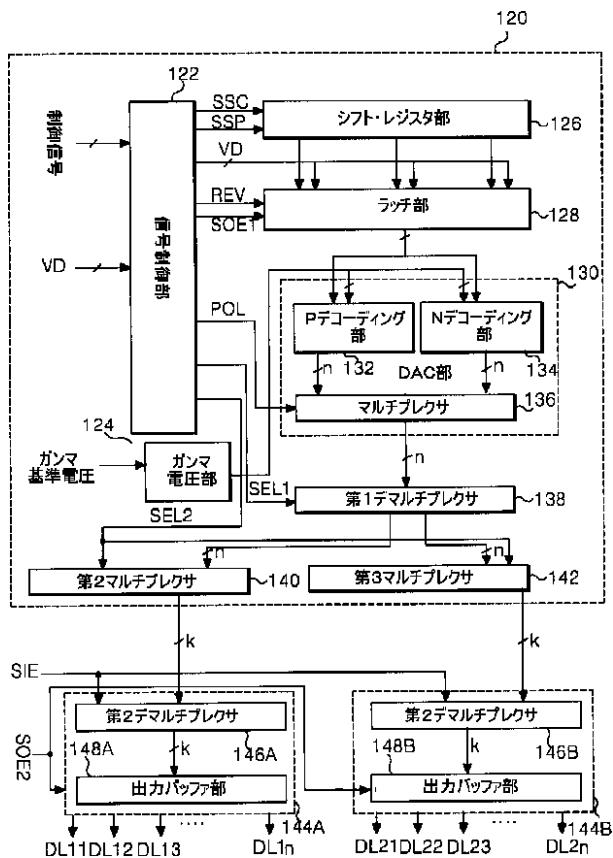

【0083】図7は、本発明の第4実施例による液晶表示装置のデータ駆動ユニットの構成を示したブロック図である。図7に示されたデータ駆動ユニットは、図6に示されたデータ駆動ユニットと対比して図6のマルチプレクサ(106)が有するn個の画素電圧信号の分割機能を遂行するための2個のマルチプレクサ(140、142)が追加されたことを除いては同一の構成要素を具备する。そして、図7に示されたデータユニットは、図5に示されたタイミング制御部(58)のような制御方式で制御される。

50

【0084】タイミング制御部(58)は、データ駆動ユニットを制御するための各種の制御信号と画素データ(VD)を供給する。このためにタイミング制御部(58)は、制御信号発生部(57)と画素データ再整列部(59)とを具備する。

【0085】制御信号発生部(57)は、外部から入力される垂直及び水平の同期信号とドットクロック信号を利用してデータユニットを制御するための各種の制御信号(SSP、SSC、SOE1、REV、POL、SIE、SOE2など)を発生する。

【0086】画素データ再整列部(59)は、2n個のデータライン(DL11乃至DL1n、DL21乃至DL2n)に供給される2n個の画素データ(VD)を時分割して順次的に供給する。また、画素データ再整列部(59)は、伝送周波数を減らすために画素データ(VD)をイブン画素データ(VDeven)とオド画素データ(VDodd)に分けてそれぞれの伝送ラインを通して同時に output する。ここで、イブン画素データ(VDeven)とオド画素データ(VDodd)のそれぞれは赤(R)、緑(G)、青(B)画素データを含む。特に、画素データ再整列部(59)は、データ電送の際に電磁気的干渉(EMI)を最小化するために、トランジションされるビット数が基準値を超える場合は、画素データ(VD)はトランジションのビット数を減らすように変造して出力する。

【0087】DAC・IC(120)には、2n個のデータライン(DL11乃至DL1n、DL21乃至DL2n)に供給される2n個の画素データがn個ずつ時分割されて入力される。DAC・IC(120)は、入力されたn個の画素データをアナログ信号である画素電圧信号に変換する。そしてDAC・IC(120)は、アナログ信号に変換されたn個の画素電圧信号をまたk個(<n)ずつ分割して第1及び第2出力バッファIC(144A、144B)に選択的に供給する。

【0088】このために、DAC・IC(120)は、順次的にサンプリング信号を供給するシフト・レジスタ部(126)と、サンプリング信号に応答して画素データ(VD)を順次的にラッチして同時に output するラッチ部(128)と、ラッチ部(128)からの画素データ(VD)を画素電圧信号に変換するDAC部(130)と、DAC部(130)からの画素電圧信号を2個のマルチプレクサ(140、142)に選択的に供給する第1マルチプレクサ(138)からの画素電圧信号を、時分割して第1及び第2出力バッファIC(144A、144B)のそれぞれに供給する第2及び第3マルチプレクサ(140、142)とを具備する。また、DAC・IC(120)は、タイミング制御部(58)から供給される各種の制御信号と画素データ(VD)を中継する信号制御部(122)と、DAC部(130)に必要とする正極性及び負極性のガンマ電圧を供給するガンマ

電圧部(124)とを更に具備する。

【0089】信号制御部(122)は、タイミング制御部(58)からの各種制御信号(CLK、SSP、SSC、SOE、REV、POL、SEL1、SEL2など)と画素データ(VD)を該当する構成要素に出力するように制御される。

【0090】ガンマ電圧部(124)は、ガンマ基準電圧の発生部(図示しない)から入力される多数個のガンマ基準電圧をグレイ別に細分化して出力する。

10 【0091】シフト・レジスタ部(126)に含まれるn/6つのシフト・レジスタは、信号制御部(122)からのソース・スタート・パルス(SSP)をソース・サンプリング・クロック信号(SSC)により順次的にシフトさせてサンプリング信号に出力する。

【0092】ラッチ部(128)は、シフト・レジスタ部(126)からのサンプリング信号に応答して、信号制御部(122)からの画素データ(VD)を一定単位ずつ順次的にサンプリングしてラッチする。このためにラッチ部(128)は、n個の画素データ(VD)をラッチするためのn個のラッチで構成されており、そのラッチのそれぞれは、画素データ(VD)のビット数(3ビットまたは6ビット)に対応する大きさを有する。このようなラッチ部(128)は、サンプリング信号毎に信号制御部(122)を経由して供給されるイブン画素データ(VDeven)とオド画素データ(VDodd)、即ち、6個の画素データを同時にラッチする。続いて、ラッチ部(128)は、信号制御部(122)からの第1ソース出力イネーブル信号(SOE1)に応答してラッチされたn個の画素データ(VD)を同時に output する。この場合、ラッチ部(128)は、データ反転選択信号(REV)に応答してトランジションビット数を減らすように変造された画素データ(VD)を復元させて出力する。

【0093】DAC部(130)は、ラッチ部(128)からのn個の画素データ(VD)を同時に正極及び負極性の画素電圧信号に変換して、極性制御信号(POL)に応答して正極性及び負極性の画素電圧信号を選択的に出力する。このために、DAC部(130)は、ラッチ部(128)に共通接続されたPデコーディング部(132)及びNデコーディング部(134)と、Pデコーディング部(132)及びNデコーディング部(134)の出力信号を選択するための第1マルチプレクサ(136)とを具備する。

【0094】Pデコーディング部(132)に含まれるn個のPデコーダは、ラッチ部(128)から同時に input されるn個の画素データをガンマ電圧部(124)からの正極性のガンマ電圧を利用して正極性の画素電圧信号に変換する。Nデコーディング部(134)に含まれるn個のNデコーダは、ラッチ部(128)から同時に input されるn個の画素データをガンマ電圧部(124)

からの負極性のガンマ電圧を利用して負極性の画素電圧信号に変換する。第1マルチブレクサ(136)は、信号制御部(122)からの極性制御信号(POL)に応答してPコーディング部(132)からの正極性の画素電圧信号またはNコーディング部(134)からの負極性の画素電圧信号を選択して出力する。

【0095】第1デマルチブレクサ(138)は、第1マルチブレクサ(136)から入力されるn個の画素電圧信号を、信号制御部(122)から入力される第1選択制御信号(SEL1)に応答して第2及び第3マルチブレクサ(140、142)に選択的に出力する。第1選択制御信号(SEL1)は、ラッチ部(128)に供給されるソース入力イネーブル信号(SOE)の一周期毎に論理値が反転されることで、n個ずつの画素電圧信号が2個の第2マルチブレクサ(140、142)に選択的に出力される。

【0096】第2及び第3マルチブレクサ(140、142)のそれぞれは、第1デマルチブレクサ(138)からn個ずつ供給される画素電圧信号を、信号制御部(122)から第2選択制御信号(SEL2)に応答してk個ずつ分けて出力する。この場合、第2選択制御信号(SEL2)のビット数は、n個の画素電圧信号を分割する回数(j)により定められる。例えば、n個の画素電圧信号を8(j=8)分割して出力する場合に、第2選択制御信号(SEL2)は3ビットで構成されると十分である。

【0097】第1及び第2出力バッファIC(144A、144B)のそれぞれは、DAC·IC(120)の第2及び第3マルチブレクサ(140、142)のそれからk個ずつ入力される画素電圧信号をサンプリングした後、ホールディングしてn個のデータライン(DL11乃至DL1nまたはDL21乃至DL2n)に同時に出力する。このために、第1及び第2出力バッファIC(144A、144B)のそれぞれは、第2デマルチブレクサ(146Aまたは146B)と出力バッファ部(144A、144B)で構成される。

【0098】第2デマルチブレクサ(146Aまたは146B)のそれぞれは、第2及び第3デマルチブレクサ(140、142)のそれからk個ずつ入力される画素電圧信号を、タイミング制御部(58)から供給されるソース入力イネーブル(SIE)に応答して出力バッファ部(144A、144B)に含まれるn個の出力バッファセルに選択的に供給する。

【0099】出力バッファ部(144A、144B)のそれぞれは、該当するデータライン(DL11乃至DL1nまたはDL21乃至DL2n)に一対一に接続された図4に示されたような構成を有するn個の出力バッファセルで構成される。このように、出力バッファ部(144A、144B)のそれぞれは、デマルチブレクサ(146A、146B)のそれから供給されるk個

ずつの画素電圧信号を順次的に入力してホールディングさせる。このように出力バッファ部(144A、144B)のそれぞれにk個ずつ入力されたn個の画素電圧信号がすべて入力されてホールディングされると、タイミング制御部(58)からの第2ソース出力イネーブル信号(SEO2)に応答してホールディングされたn個の画素電圧信号を同時に該当するデータライン(DL1乃至DL2n)に供給する。

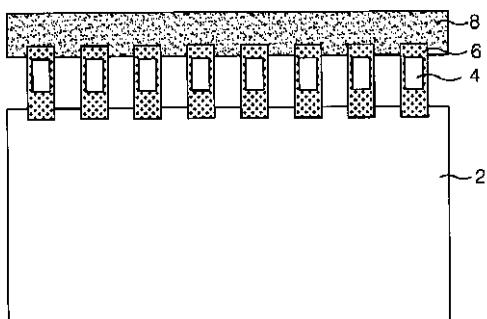

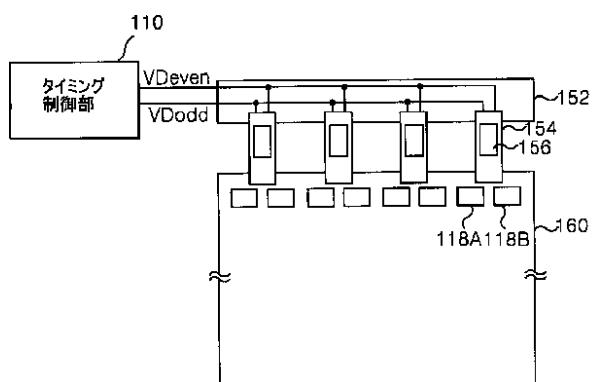

【0100】以上、説明したように、本発明の実施例によるデータ駆動ユニットは、DAC·ICと出力バッファICに分離されて集積化される。そして、一つのDAC·ICが時分割駆動されて、そのDAC·ICにnチャンネルを有する少なくとも2個の出力バッファICが共通接続されるか2nチャンネルを有する出力バッファICが接続されることで、DAC·IC数を1/2に減らすことができる。更にこのように必要な個数が減ったDAC·ICは、TCP上に実装し、出力バッファICはCOG型に液晶パネル上に実装することでTCPの個数を従来より1/2に減らすことができる。

【0101】詳細に説明すると、図8に示されたように、DAC·IC(156)はTCP(154)上に、出力バッファIC(118A、118B)は液晶パネル(160)上に分離されて実装されている。図8は時分割駆動されるDAC·IC(156)のそれと2個の出力バッファIC(118A、118B)が共通接続された場合を示した液晶表示装置のデータ駆動装置を示す。

【0102】出力バッファIC(118A、118B)は液晶パネル(160)上にCOG型に実装される。DAC·IC(156)が実装されたTCP(154)は、液晶パネル(160)の上段部に設けられたパッドなどを通して出力バッファIC(118A、118B)と電気的に接続されると共にデータPCB(152)に設けられた出力パッドなどと電気的に接続される。データPCB(152)はタイミング制御部(110)から供給される各種の制御信号と画素データ信号をDAC·IC(156)に伝送する役割をする。

【0103】タイミング制御部(110)は、伝送周波数を減らせるために画素データ(VD)をイブン画素データ(VD even)とオド画素データ(VD odd)に分けてそれぞれの伝送ラインを通して出力する。そして、タイミング制御部(110)は、イブン画素データ(VD even)とオド画素データ(VD odd)を多数個のDAC·ICなど(156)に順次的に供給する。ここで、出力バッファIC(118A、118B)のそれぞれがn個の出力チャンネルを有する場合、タイミング制御部(110)はDAC·IC(156)のそれと2n個の画素データをn個ずつ時分割して供給する。これにより、DAC·IC(156)のそれぞれは、1水平周期の内にn個ずつ2回DAC機能を遂行しなければなら

ないので、従来に比べて2倍の速度で駆動されるべきである。このために、タイミング制御部(110)は、DAC・IC(156)のそれぞれに供給する各種の制御信号(SSC、SSP、SSC、SOE、REV、POLなど)及び画素データ(VD)が従来に比べて2倍の周波数で供給される。このようにTCP(154)上には、時分割駆動されるDAC・IC(156)だけが実装されることで、そのDAC・IC(156)と共にTCP(154)の個数を半分に減らすことができるので、その分製造単価を低くすることができます。

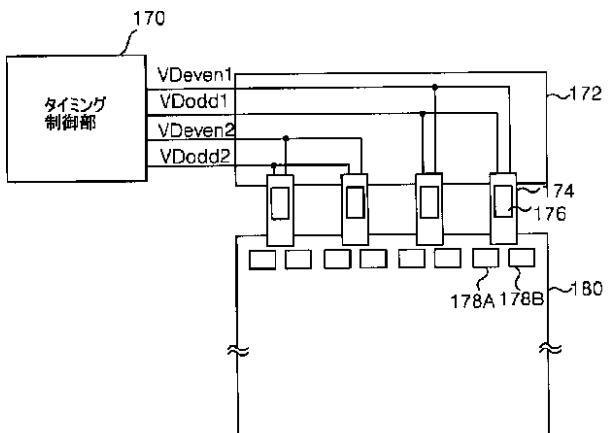

【0104】これとは異なり、時分割駆動されるDAC・ICの駆動周波数を2倍に増加させないためには、図9に示されたようにタイミング制御部(170)からDAC・IC(176)に画素データを供給する伝送ラインを物理的に分離する。換言すると、タイミング制御部(170)からの画素データを伝送するための伝送ラインは、第1イブン画素データ(VDeven1)伝送ライン、第1オド画素データ(VDodd1)伝送ライン、第2イブン画素データ(VDeven2)伝送ライン、そして第2オド画素データ(VDodd2)伝送ラインに分離される。ここで、第1イブン画素データ(VDeven1)伝送ライン及び第1オド画素データ(VDodd1)伝送ラインは、4個のDAC・IC(174)のうちの2個のDAC・IC(174)に接続されて、第2イブン画素データ(VDeven2)伝送ライン及び第2オド画素データ(VDodd2)伝送ラインは残りの2個のDAC・IC(174)に接続される。このように、データ電送ラインを2倍に追加してDAC・IC(174)に分離して接続させることで、2個のDAC・IC(174)に画素データ(VD)をラッチする時間の間に4個のDAC・IC(174)に画素データ(VD)をラッチすることができる。タイミング制御部(17)は、このような画素データラッチ時間の短縮のためにDAC・IC(176)が時分割駆動されても、図8に示された液晶表示装置のデータ駆動装置の駆動周波数の増加なしに既存と同一の駆動周波数にてDAC・IC(176)を駆動することができる。

【0105】DAC・IC(176)が実装されたTCP(174)のそれぞれに2個ずつ共通に接続される出力バッファIC(178A、178B)は、液晶パネル(180)上にCGO型に実装される。TCP(174)は、液晶パネル(180)の上段部に設けられたパッドを通して出力バッファIC(178A、178B)と電気的に接続されると共に、データPCB(172)に設けられた出力パッドと電気的に接続される。データPCB(172)は、タイミング制御部(170)から供給される各種の制御信号と画素データ信号をDAC・IC(176)に伝送する役割をする。

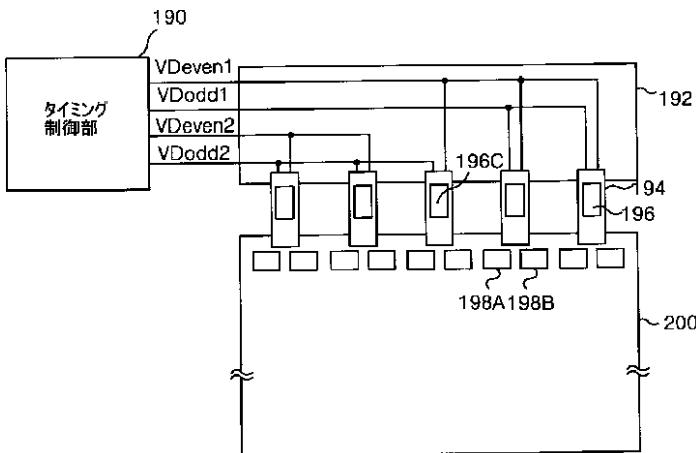

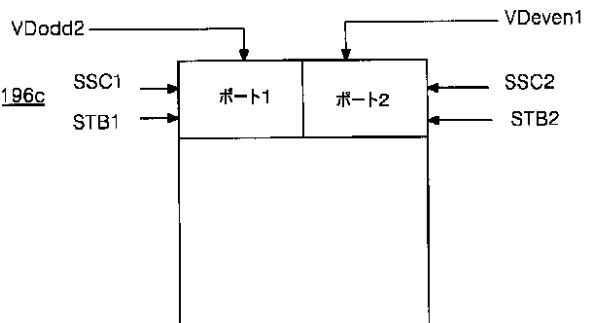

【0106】一方、図10に示されたように、DAC・IC(196)の個数が従来対比の奇数個、例えば5個

に減る場合に、図9のようにデータ電送ラインを分離するためには、その5個のDAC・IC(196)のうちの中央に位置する一つのDAC・IC(195C)はポート1とポート2のそれぞれを通して画素データを入力しなければならない。

【0107】例えば、液晶パネル(200)がSXGAモード(1280\*1204)である場合に、480チャンネルのデータ駆動ICを使用する場合には、8個のデータ駆動ICを必要とし、384チャンネルのデータ駆動ICを使用する場合には10個のデータ駆動IC出力バッファICを必要とする。このようなデータ駆動ICをDAC・ICと出力バッファICに分離してDAC・ICを時分割駆動することで、DAC・ICの個数を半分に減らすことができる。本発明では、4個の480チャンネルDAC・ICまたは5個の384チャンネルのDAC・ICが必要になる。ここで、4個の480チャンネルを使用するDAC・ICを使用する場合に駆動周波数の増加を防止するためには、図9に示されたように、データ電送ラインを2分してDAC・ICを2個ずつ分離駆動する。しかし、480チャンネルのDAC・ICは384チャンネルのDAC・ICより製造単価が高い短所を有する。

【0108】これにより、5個の384チャンネルのDAC・ICを使用する場合にデータ電送ラインを2分して駆動周波数の増加を防止するためには、5個のDAC・ICのうちの一つのDAC・IC(195C)は、データ入力ポートが独立的に駆動されるポート1とポート2で構成されるべきである。図10を参照すると、5個のDAC・IC(196、196C)のうちの第1及び第2DAC・IC(196)は、第2イブン画素データ(VDeven2)伝送ライン及び第2オド画素データ(VDodd2)伝送ラインに共通に接続されて、第4及び第5DAC・IC(196)は、第1イブン画素データ(VDeven1)伝送ライン及び第1オド画素データ(VDodd1)伝送ラインに共通に接続される。特に、第3DAC・IC(196C)は、画素データの入力のため図11に示されたように、独立的に駆動されるポート1とポート2とを具備する。ポート1は第2イブン画素データ(VDeven2)伝送ラインに接続されて、ポート2は第1イブン画素データ(VDeven1)伝送ラインに接続される。ポート1は、タイミング制御部(190)から供給される第1ソース・サンプリング・クロック(SSC1)と第1ストロブネイブル信号(STB1)に応答して、第2オド画素データ(VDodd2)伝送ラインを通して入力されるオド画素データなどを入力する。ポート2は、タイミング制御部(190)から供給される第2ソース・サンプリング・クロック(SSC2)と第2ストロブネイブル信号(STB2)に応答して、第1イブン画素データ(VDeven1)伝送ラインを通して入力されるイブン画素データを入力する。

【0109】このように、奇数個のD A C · I C ( 1 9 6 、 1 9 6 C ) を 2 分されたデータ電送ラインに分離して接続させることで、2.5個のD A C · I C に画素データ ( V D ) をラッチする時間の間に、5個のD A C · I C ( 1 9 6 、 1 9 6 C ) に画素データ ( V D ) をラッチすることができる。タイミング制御部 ( 1 9 0 ) は、このような画素データのラッチ時間を短縮のためにD A C · I C ( 1 9 6 、 1 9 6 C ) が時分割駆動されても、図8に示された液晶表示装置のデータ駆動装置の駆動周波数の増加なしに既存と同一の駆動周波数にてD A C · I C ( 1 9 6 、 1 9 6 C ) を駆動することができる。

【0110】このようなD A C · I C ( 1 9 6 、 1 9 6 C ) が実装されたT C P ( 1 9 4 ) のそれぞれに2個ずつ共通に接続される出力バッファ I C ( 1 9 8 A 、 1 9 8 B ) は、液晶パネル ( 2 0 0 ) 上にC G O型に実装される。T C P ( 1 9 4 ) は、液晶パネル ( 2 0 0 ) の上段部に設けられたパッドを通して出力バッファ I C ( 1 9 8 A 、 1 9 8 B ) と電気的に接続されると共に、データP C B ( 1 9 2 ) に設けられた出力パッドと電気的に接続される。データP C B ( 1 9 2 ) は、タイミング制御部 ( 1 9 0 ) から供給される各種の制御信号と画素データ信号をD A C · I C ( 1 9 6 、 1 9 6 C ) に伝送する役割をする。

#### 【0111】

【発明の効果】上述したように、本発明による液晶表示装置のデータ駆動装置及び方法では、D A C部を時分割駆動して出力バッファ部を分離して液晶パネル上に実装することで、D A C · I C部及びT C Pの数を半分に減らすことができるので製造単価を節減することができる。また、本発明による液晶表示装置のデータ駆動装置及び方法によると、データ駆動 I C で出力バッファ部を分離してD A C機能だけをすることによって、ドライバ I C の構成がより簡素化され製造効率を向上させることができる。更に、本発明による液晶表示装置のデータ駆動装置及び方法によると、データ駆動 I C がD A C · I C と出力バッファ I C に分離されて集積化されることで、I C の精密度を向上させることができるので I C の駆動信頼性を向上させることができる。

【0112】以上説明した内容を通して、当業者であれば本発明の技術思想を逸脱しない範囲で多様な変更及び修正の可能である。従って、本発明の技術的な範囲は明細書の詳細な説明に記載された内容に限らず特許請求の範囲によって定めなければならない。

#### 【図面の簡単な説明】

【図1】従来の液晶表示装置のデータ駆動装置を概略的に図示した画面である。

【図2】図1に示されたデータ駆動装置の集積回路の詳細な構成を示したブロック図である。

【図3】本発明の第1実施例による液晶表示装置のデータ駆動ユニットを図示したブロック図である。

【図4】図3に示された出力バッファ部に含まれる出力バッファセルの詳細な構成を示した図面である。

【図5】本発明の第2実施例による液晶表示装置のデータ駆動ユニットを示したブロック図である。

【図6】本発明の第3実施例による液晶表示装置のデータ駆動ユニットを示したブロック図である。

【図7】本発明の第4実施例による液晶表示装置のデータ駆動ユニットを示したブロック図である。

【図8】本発明によるデータ駆動ユニットを含む液晶表示装置のデータ駆動装置を概略的に示した図面である。

【図9】本発明によるデータ駆動ユニットを含む異なる液晶表示装置のデータ駆動装置を概略的に示した図面である。

【図10】本発明によるデータ駆動ユニットを含む更に異なる液晶表示装置のデータ駆動装置を概略的に示した図面である。

【図11】図10に示された第3デジタル・アナログ変換集積回路のメカニズムを説明するための図面である。

#### 【符号の説明】

2、160、180、200：液晶パネル

4：データ駆動集積回路 ( I C )

6、154、174、194：テープ・キャリア・パッケージ ( T C P )

8、152、172、192：データ印刷回路基板 ( P C B )

10、32、62、92、122：信号制御部

12、34、64、94、124：ガンマ電圧部

14、36、66、96、126：シフト・レジスタ部

16、38、68、98、128：ラッチ部

18、40、70、100、130：デジタル-アナログ変換 ( D A C ) 部

20、42、72、102、132：Pデコーディング部

22、44、74、104、134：Nデコーディング部

24、46、76、106、136：マルチブレクサ ( M U X )

26、52A、52B、82、114A、114B、148A、148B：出力バッファ部

28、58、150：タイミング制御部

29、59：ビデオデータ整列部

30、60、90、120、156、176、196、196C：デジタル-アナログ変換集積回路

48A、48B、78、110A、110B、144A、144B、158A、158B、178A、178B、198A、198B：出力バッファ集積回路

50A、50B、80、108、112A、112B、146A、146B：デマルチブレクサ ( D E M U X )

54：出力バッファセル

56、57：バッファ

【図1】

【図2】

【図3】

【図4】

【図8】

【図5】

【図9】

【図6】

〔义 7 〕

【図10】

### 【図11】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

## 識別記号

F I

G 0 9 G 3/20

### テ-マコ-ト (参考)

680

3 / 36

(72)発明者 ソン ジン キョン

大韓民国 キョンサンブック - ド, クミ -

シ, ジンピュン - ドン, イニュイジグ 82

ビー 2 エル, シンソン ヴィラ, ナンバー

303

F ターム(参考) 2H092 GA59 JA24 NA25

2H093 NA16 NA32 NA43 NC02 NC15

NC16 NC22 NC23 NC24 NC26

NC29 NC34 ND40 ND54

5C006 AA16 AC11 AC26 AF43 AF46

AF71 AF83 BB16 BC02 BC12

BC23 BC24 BF03 BF04 BF11

BF24 BF25 BF27 BF49 EB06

FA32 FA43 FA51

5C080 AA10 BB05 DD12 DD23 DD25

DD28 EE29 FF11 JJ02 JJ03

5G435 AA17 BB12 EE40

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置的数据驱动装置和方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP2003140182A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2003-05-14 |

| 申请号            | JP2002164813                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2002-06-05 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | Eruji.菲利普斯杜天公司,有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | リーソクウ<br>ソンジンキョン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | リーソクウ<br>ソンジンキョン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G02F1/1345 G02F1/133 G09F9/00 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| CPC分类号         | G09G3/3688 G09G3/3614 G09G2310/027 G09G2310/0281 G09G2310/0297 G09G2320/0276<br>G09G2330/06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G02F1/1345 G02F1/133.550 G09F9/00.348.Z G09G3/20.621.M G09G3/20.623.B G09G3/20.623.F<br>G09G3/20.623.W G09G3/20.680.G G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 2H092/GA59 2H092/JA24 2H092/NA25 2H093/NA16 2H093/NA32 2H093/NA43 2H093/NC02 2H093<br>/NC15 2H093/NC16 2H093/NC22 2H093/NC23 2H093/NC24 2H093/NC26 2H093/NC29 2H093/NC34<br>2H093/ND40 2H093/ND54 5C006/AA16 5C006/AC11 5C006/AC26 5C006/AF43 5C006/AF46 5C006<br>/AF71 5C006/AF83 5C006/BB16 5C006/BC02 5C006/BC12 5C006/BC23 5C006/BC24 5C006/BF03<br>5C006/BF04 5C006/BF11 5C006/BF24 5C006/BF25 5C006/BF27 5C006/BF49 5C006/EB06 5C006<br>/FA32 5C006/FA43 5C006/FA51 5C080/AA10 5C080/BB05 5C080/DD12 5C080/DD23 5C080/DD25<br>5C080/DD28 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5G435/AA17 5G435/BB12 5G435<br>/EE40 2H092/GA51 2H092/GA60 2H092/PA06 2H093/NC12 2H193/ZA04 2H193/ZC02 2H193/ZF02<br>2H193/ZF36 |         |            |

| 优先权            | 1020010068397 2001-11-03 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 其他公开文献         | JP4140755B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

## 摘要(译)

(带更正)通过时分驱动数模转换单元并将其与输出缓冲单元分开集成,以减少数模转换集成电路和磁带载体封装的数量。数据驱动器包括:数模转换集成电路;以及n通道输出缓冲集成电路,其将从数模转换集成电路提供的像素电压信号缓冲并输出到数据线。控制数模转换集成电路和输出缓冲器集成电路,并根据提供给输出缓冲器集成电路的顺序重新排列提供给数模转换集成电路的2n像素数据。并且,一种用于时分地提供给由每个像素数据构成的至少两个部分的定时控制单元,将数字模拟转换集成电路安装在带载封装上,并且提供输出集成电路。被安装在液晶面板上。