(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3987280号

(P3987280)

(45) 発行日 平成19年10月3日(2007.10.3)

(24) 登録日 平成19年7月20日(2007.7.20)

(51) Int.CI.

F 1

|             |             |                  |             |             |             |

|-------------|-------------|------------------|-------------|-------------|-------------|

| <b>G09G</b> | <b>3/36</b> | <b>(2006.01)</b> | <b>G09G</b> | <b>3/36</b> |             |

| <b>G09G</b> | <b>3/20</b> | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b> | <b>622E</b> |

|             |             |                  | <b>G09G</b> | <b>3/20</b> | <b>660Q</b> |

請求項の数 3 (全 22 頁)

|              |                               |           |                                               |

|--------------|-------------------------------|-----------|-----------------------------------------------|

| (21) 出願番号    | 特願2000-401601 (P2000-401601)  | (73) 特許権者 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (22) 出願日     | 平成12年12月28日 (2000.12.28)      | (74) 代理人  | 100095728<br>弁理士 上柳 雅善                        |

| (62) 分割の表示   | 特願平10-507829の分割               | (74) 代理人  | 100107076<br>弁理士 藤岡 英吉                        |

| 原出願日         | 平成9年11月10日 (1997.11.10)       | (74) 代理人  | 100107261<br>弁理士 須澤 修                         |

| (65) 公開番号    | 特開2001-242841 (P2001-242841A) | (72) 発明者  | 石井 賢哉<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内        |

| (43) 公開日     | 平成13年9月7日 (2001.9.7)          |           |                                               |

| 審査請求日        | 平成13年1月29日 (2001.1.29)        |           |                                               |

| 審判番号         | 不服2004-13688 (P2004-13688/J1) |           |                                               |

| 審判請求日        | 平成16年7月1日 (2004.7.1)          |           |                                               |

| (31) 優先権主張番号 | 特願平8-296546                   |           |                                               |

| (32) 優先日     | 平成8年11月10日 (1996.11.10)       |           |                                               |

| (33) 優先権主張国  | 日本国 (JP)                      |           |                                               |

最終頁に続く

(54) 【発明の名称】 液晶パネルの駆動装置、液晶装置及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1方向に配列されており画像信号が供給される複数の信号線と、前記第1方向に交わる第2方向に配列されており走査信号が順次供給される複数の走査線と、マトリクス状に設けられており前記複数の信号線及び前記複数の走査線から夫々供給される前記画像信号及び前記走査信号により夫々駆動される複数の画素部とを備えた液晶パネルを、画素マトリクスの上下の全域を画像表示領域にする表示モードと画素マトリクスの上下の一定幅領域を非画像表示領域にする表示モードとに切り換えて駆動する液晶パネルの駆動装置であって、

前記複数の走査線に対して垂直走査を行うシフトレジスタと、

10

前記画素マトリクスの上下の一定幅領域を非画像表示領域にする表示モードを示すモード切り換え信号に応じて、前記シフトレジスタにスタートパルスを出力すると共に、前記シフトレジスタから出力されたエンドパルスに基づいて前記一定幅領域を非画像表示領域にするための信号を出力するモード切換回路と、

前記一定幅領域に対応する複数の前記走査線の夫々に接続された複数の論理和回路と、を備え、

前記複数の論理和回路は夫々、前記モード切換回路から出力された前記一定幅領域を非画像表示領域にするための信号と前記シフトレジスタの出力との論理和を前記一定幅領域に対応する複数の前記走査線に供給し、

前記複数の論理和回路に接続された前記複数の走査線に対応する前記複数の画素に所定

20

レベルの画像信号が一斉に供給されることを特徴とする液晶パネルの駆動装置。

【請求項 2】

請求項 1 に記載の液晶パネルの駆動装置を備えたことを特徴とする液晶装置。

【請求項 3】

請求項 2 に記載の液晶装置を備えたことを特徴とする電子機器。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、トランジスタ駆動、MIM (Metal Insulator Metal) 駆動等によるマトリクス駆動方式の液晶パネルの駆動装置、並びにこれを用いた液晶装置及び電子機器の技術分野に関し、特に、画像信号の種類に応じて相異なるアスペクト比(横対縦の比)の画像を表示可能とするように液晶パネルを駆動する駆動装置、並びにこれを用いた液晶装置及び電子機器の技術分野に関する。 10

【0002】

【従来の技術】

近年のテレビ放送のワイド画面化やコンピューター等の表示仕様との共用等の市場の要求により、液晶装置も異なる複数の表示仕様に対応していかなければならない。しかしながら、従来のドットマトリクス型液晶装置では、アスペクト比の異なる複数の表示仕様に対応する際に発生する映像が表示されない非画像表示領域の処理が課題であった。例えば、近年のハイビジョン規格、NTSC (National Television System Committee) ワイド画面規格等に基づくアスペクト比 16 : 9 の画面を持つドットマトリクス型液晶装置において内包する形で従来の NTSC 規格、PAL (Phase Alteration Line) 規格等に基づくアスペクト比 4 : 3 の表示を行おうとした場合、画像表示領域の左右には非画像表示領域が発生する。この非画像表示領域には通常黒表示がなされるが、通常のシフトレジスタの駆動で黒表示を行っては各水平帰線区間の時間内で当該非画像表示領域における画素電極全ての水平走査を行い表示することはできない。従って、ラインメモリ等の外部記憶装置により水平走査周波数の調整をするか、非画像表示領域のみシフトレジスタを画像表示領域よりも 1.5 から 2 倍と高い周波数で駆動するといった手法が用いられていた。 20

【0003】

逆に、例えば従来の NTSC 規格等に基づくアスペクト比 4 : 3 の画面を持つドットマトリクス型液晶装置において内包する形で、ハイビジョン規格等に基づくアスペクト比 16 : 9 の表示を行おうとした場合、画像表示領域の上下には非画像表示領域が発生する。この非画像表示領域には、やはり通常黒表示がなされるが、この場合にも、外部記憶装置により垂直走査周波数の調整をするか、非画像表示領域のみシフトレジスタを画像表示領域よりも高い周波数で駆動するといった手法が用いられていた。 30

【0004】

また、特開平 9 - 154086 号公報には、左右の非画像表示領域に副映像信号処理部からの信号が同時に表示されるように水平走査を制御する装置を備えた表示装置が開示されている。この技術によれば、左右の非画像表示領域において同時に走査を行うことにより、この領域を走査するための時間が半分で済むとされている。 40

【0005】

【発明が解決しようとする課題】

しかしながら、前述したようにシフトレジスタを画像表示領域よりも高い周波数で駆動する方式を用いて非画像表示領域の黒表示を行った場合、シフトレジスタに高い特性が必要となり、また、当該非画像表示領域において画素の選択時間が短くなるために十分なコントラスト比が得られない等の問題点がある。更に、駆動周波数が高くなることで、消費電力が増加するという問題もある。他方、前述したラインメモリ等の外部記憶装置による方式では、コストの増加を招くばかりでなく、周辺回路の設計や動作制御がより複雑なものになるという問題がある。 50

**【0006】**

更に前述した特開平9-154086号公報に開示された技術によれば、左右の非画像表示領域において同時に走査を行うために、副映像信号処理部、映像信号切換装置等の複雑な回路をドライバ回路に組み込まねばならず装置構成及び制御の複雑化を招いてしまう。更に、左右の非画像表示領域に黒表示するためには、左右を別々に走査する場合と比較して尚、約二分の一の走査時間が必要とされてしまう。

**【0007】**

そこで本発明は、比較的簡易な構成を用いて非画像表示領域に適宜黒表示でき、各種のアスペクト比の画像を表示可能な液晶パネルの駆動装置、並びに該駆動装置を備えた液晶装置及び電子機器を提供することを技術的課題とする。

10

**【0008】****【課題を解決するための手段】**

本発明の液晶パネルの駆動装置は上述の技術的課題を解決するために、第1方向に配列されており画像信号が供給される複数の信号線と、前記第1方向に交わる第2方向に配列されており走査信号が順次供給される複数の走査線と、マトリクス状に設けられており前記複数の信号線及び前記複数の走査線から夫々供給される前記画像信号及び前記走査信号により夫々駆動される複数の画素部とを備えた液晶パネルを、画素マトリクスの上下の全域を画像表示領域にする表示モードと画素マトリクスの上下の一定幅領域を非画像表示領域にする表示モードとに切り換えて駆動する液晶パネルの駆動装置であって、前記複数の走査線に対して垂直走査を行うシフトレジスタと、前記画素マトリクスの上下の一定幅領域を非画像表示領域にする表示モードを示すモード切り換え信号に応じて、前記シフトレジスタにスタートパルスを出力すると共に、前記シフトレジスタから出力されたエンドパルスに基づいて前記一定幅領域を非画像表示領域にするための信号を出力するモード切換回路と、前記一定幅領域に対応する複数の前記走査線の夫々に接続された複数の論理回路と、を備え、前記複数の論理回路は夫々、前記モード切換回路から出力された前記一定幅領域を非画像表示領域にするための信号と前記シフトレジスタの出力との論理和を前記一定幅領域に対応する複数の前記走査線に供給し、前記複数の論理回路に接続された前記複数の走査線に対応する前記複数の画素に所定レベルの画像信号が一斉に供給されることを特徴とする。

20

**【0022】**

30

本発明の液晶装置は、上述の液晶パネルの駆動装置を備えることを特徴とする。

**【0023】**

本発明の液晶装置によれば、以上説明した本発明の液晶装置の駆動装置を備えているので、比較的簡易な構成を用いて非画像表示領域に適宜黒表示しながら、各種のアスペクト比の画像を表示できる。

**【0024】**

本発明の電子機器は、上述の液晶装置を備えたことを特徴とする。

**【0025】**

本発明の電子機器によれば、本発明の液晶装置を備えているので、比較的簡易な構成を用いて画面上に各種のアスペクト比の画像を表示可能な、液晶プロジェクタ、パーソナルコンピュータ、ページャ等の様々な電子機器を実現可能となる。

40

**【0032】****【発明の実施の形態】**

以下、本発明を実施するための最良の形態について実施例毎に順に図面に基づいて説明する。

**【0033】****(第1実施例)**

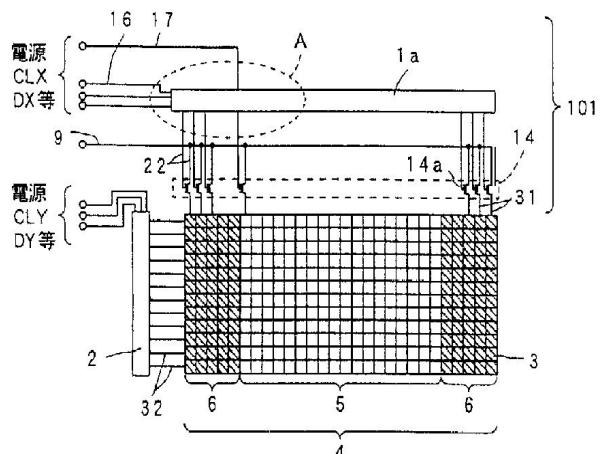

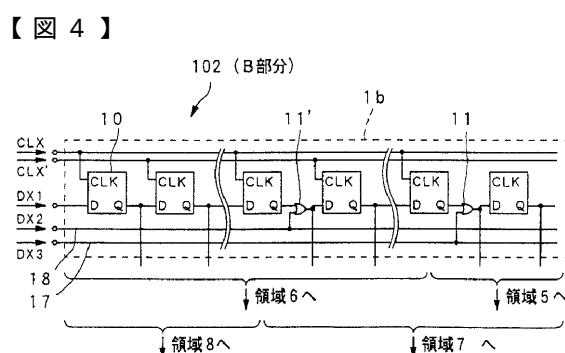

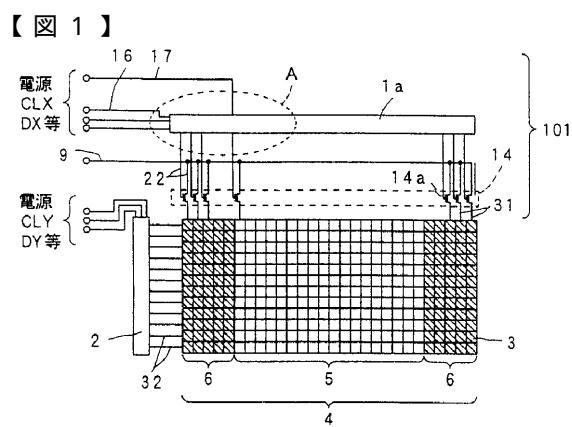

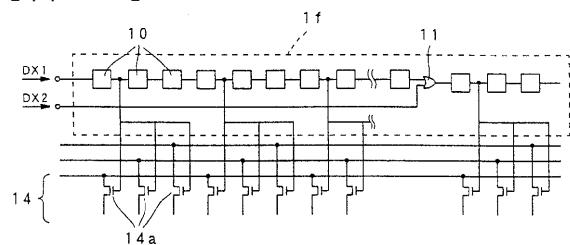

先ず第1実施例について図1及び図2を参照して説明する。図1は、第1実施例にかかる液晶装置の回路ブロック図であり、図2は、図1のA部分の拡大図である。

**【0034】**

50

図1において、液晶装置は、Xシフトレジスタ(Xドライバ回路)1aと、Yシフトレジスタ(Yドライバ回路)2と、画素マトリクス3とを備えて構成されている。更に、液晶装置は、サンプリング回路14を備えており、Xシフトレジスタ1a、サンプリング回路14及び後述の各種配線(9、16、17、22等)から画像信号供給装置101が構成されている。

#### 【0035】

Xシフトレジスタ1aは、図2に示すように、水平走査を行うために、一連のフリップフロップ10がX方向に直列に配列されて構成されている。より具体的には、Xシフトレジスタ1aは、水平走査スタート信号DX1が配線16を介して供給されると、図で左端のフリップフロップ10が、X側の基準クロック信号であるクロック信号CLX(及び、その反転クロック信号CLX')に基づく転送信号の生成を開始し、この初段から転送信号が出力されると共に、次段のフリップフロップ10に転送信号が転送されることにより次段のフリップフロップ10がクロック信号CLXに基づいて転送信号を生成する。そして、このような動作が繰り返されることにより、転送信号がXシフトレジスタ1aの各段から順次出力されると共に次段へ転送されるように構成されている。10

#### 【0036】

図1において、Yシフトレジスタ2は、垂直走査を行うために、一連のフリップフロップがY方向に直列に配列されて構成されている。より具体的には、Yシフトレジスタ2は、垂直走査スタート信号DYが供給されると、上端のフリップフロップが、Y例の基準クロック信号であるクロック信号CLY(及び、その反転クロック信号CLY')に基づく転送信号の生成を開始し、この初段から転送信号が対応する走査線32に出力されると共に、次段のフリップフロップに転送信号が転送されることにより次段のフリップフロップがクロック信号CLYに基づいて転送信号を生成する。そして、このような動作が繰り返されることにより、転送信号がYシフトレジスタ2の各段から走査信号として走査線32に順次出力されると共に次段へ転送されるように構成されている。20

#### 【0037】

サンプリング回路14は、TFT14aを各信号線31毎に備える。入力画像信号線9は、各TFT14aのソース電極に接続されている。Xシフトレジスタ1aの各段から順次出力される転送信号がサンプリング回路駆動信号として供給されるサンプリング回路駆動信号線22は、各TFT14aのゲート電極に接続されている。そして、サンプリング回路14は、入力画像信号線9を介して画像信号が入力されると、これをサンプリングし、Xシフトレジスタ1aからサンプリング回路駆動信号線22を介してサンプリング回路駆動信号が入力されると、サンプリングされた画像信号を、信号線31毎に順次印加する。30

#### 【0038】

以上の説明では、説明を分かり易くするために、Xシフトレジスタ1aとサンプリング回路14とは、線順次で(即ち、信号線31一本ずつ)画像信号を供給する場合について説明したが、例えば、複数の入力画像信号線9を介して、多相展開された画像信号を信号線31に供給するように構成してもよい。即ち、隣接する複数の信号線31に接続される複数のTFT14aを同時に選択し、複数の信号線31からなるグループ毎に順次転送していく方式を採用してもよい。この同時選択する信号線31の数(即ち、相展開数)としては、例えば、3、6、9、12、...本などの3の倍数であれば、カラー画像表示の際の3色毎の走査には比較的相性がよいが、それ以外の本数でもよい。一般には、サンプリング回路14を構成するTFT14aの書き込み特性が良ければ、比較的小さい相展開数(例えば、5相以下)とされ、画像信号の周波数が高ければ、比較的大きな相展開数(例えば、7相以上)とされる。この際、少なくとも画像信号の相展開数だけ、入力画像信号線9が必要なことは言うまでもない。40

#### 【0039】

また、画像信号を多相展開して、複数の入力画像信号線9を設ける構成とした場合、Xシフトレジスタ1aの各段から出力される転送信号をサンプリングに用いずに、複数段おきの転送信号をサンプリングに用いることが出来る(後述の図19参照)。この場合、サン50

プリング回路 14 の TFT 14 a は複数個が同時に導通状態とされる。

#### 【0040】

図において、画素マトリクス 3 は、アスペクト比 16 : 9 を有し（即ち、NTSC ワイド規格に基づいており）、画素マトリクス 3 を構成する各画素には薄膜トランジスタ（TFT）、二端子型非線形素子（例えば、MIM 素子等）などのスイッチング素子と、これに接続された画素電極と、画素電極に印加された電荷を保持する保持容量とが配置される。そして、一方で、入力画陥信号線 9 を介して供給される画像信号が、Xシフトレジスタ 1 a により駆動されるサンプリング回路 14 を介して、各信号線 31 から各画素に供給される。他方で、Yシフトレジスタ 2 から発せられた走査信号が、各走査線 32 から各画素に供給される。本実施例では、各画素のスイッチング素子が TFT から構成されているものとして以下説明を続ける。この場合、一方で、Xシフトレジスタ 1 a により信号線 31 に順次画像信号が供給され、他方で、Yシフトレジスタ 2 により走査線 32 に順次走査信号が供給され、走査信号がゲートに供給された TFT が導通状態とされて、信号線 31 に供給されている画像信号を画素電極及び保持容量に印加する。但し、各画素のスイッチング素子を、例えば MIM 素子から構成する場合には、対向基板側に配線されて対向電極として機能する信号線 31 及び走査線 32 の一方と、MIM アレイ基板側に配線された信号線 31 及び走査線 32 の他方に MIM 素子を介して接続された画素電極とにより、画像信号と走査信号との電位差に基づく電圧が液晶に印加される。10

#### 【0041】

ここで通常、16 : 9 のアスペクト比の画像表示を行う際には、Xシフトレジスタ 1 a を左端から右端へ順次に走査することによりサンプリング回路 14 の各 TFT 14 a を順次開閉し、導通した TFT 14 a を介して画像信号が画像入力信号線 9 から各信号線 31 に供給され、各信号線 31 に接続されるスイッチング素子（TFT）を介して対応する画素電極に画像信号を書込む。Xシフトレジスタ 1 a でのシフト走査（水平走査）が右端へ達したところで 1 行の表示が終了し、水平帰線区間内で Xシフトレジスタ 1 a はリセットされ、シフトレジスタ 2 でのシフト走査（垂直走査）が次段に送られ、Xシフトレジスタ 1 a により再び左端より水平走査を開始する。これを表示行数分ずなわち、垂直走査回路である Yシフトレジスタ 2 の段数分繰り返すことによりアスペクト比 16 : 9 の画像表示領域 4 に 1 フレームの表示が行われる。20

#### 【0042】

ところが、アスペクト比 4 : 3 の表示を従来の手法で行おうとすれば NTSC においては Xシフトレジスタ 1 a の約 8 分の 6 (= (4 / 3) / (16 / 9)) にあたる画像表示領域 5 を 53 μsec で走査するのに対し、Xシフトレジスタ 1 a の約 8 分の 2 にあたる非画像表示領域 6 を約 10 分の 2 の時間である水平帰線区間の 11 μsec 内に走査しきらなければならない（図 1 参照）。したがって、非画像表示領域 6 の走査周波数は画像表示領域 5 よりも高い周波数とならざるをえない。30

#### 【0043】

この問題を解決すべく本実施例では特に、Xシフトレジスタ 1 a 内のフリップフロップ 10 間に、図 2 に示すように、論理和回路 11 を挿入することにより、シフトレジスタ 1 a の末端（左端のフリップフロップ 10）以外の部分より走査を開始できるように構成されている。より具体的には、一方で、配線 16 を介して水平走査スタート信号 DX 1 が Xシフトレジスタ 1 a に入力された場合には、左端のフリップフロップ 10 による転送信号の生成が開始され、論理和回路 11 は、その左側にあるフリップフロップ 10 から転送される転送信号をその右側にあるフリップフロップ 10 にそのまま転送する。従って、転送動作が論理和回路 11 により妨げられることはない。他方で、配線 17 を介して水平走査スタート信号 DX 2 が Xシフトレジスタ 1 a に入力された場合には、論理和回路 11 を介して水平走査スタート信号 DX 2 を受ける論理回路 11 の右側にあるフリップフロップ 10 から転送信号の生成が開始される。この場合には、論理和回路 11 の左側にあるフリップフロップ 10 には、転送信号や水平走査スタート信号 DX 1 が入力されないために、転送動作が行われることはない。40

## 【0044】

このように、本実施例の液晶装置においては、アスペクト比4:3の表示を行うためには、Xシフトレジスタ1aのうちサンプリングのための転送信号を出力する総有効段数のおよそ8分の1段目に相当するフリップフロップ10の入力側に挿入された論理和回路11にアスペクト比4:3表示時の水平走査スタート信号DX2を配線17を介して印加し、この論理和回路11の出力を受けた次段より走査を開始するように構成されている。これにより、Xシフトレジスタ1aの走査開始側の8分の1は走査されないので、水平帰線区間の $11\mu\text{sec}$ 内に走査しなければならない非画像表示領域6に対応するXシフトレジスタ1aの段数は半分となり、2倍の走査時間が確保される。従って、非画像表示領域6の走査を画像表示領域5と同一の走査周波数で駆動することが可能となる。

10

## 【0045】

以上の様に第1実施例によれば、NTSCワイド規格に基づくアスペクト比16:9の画面を持つ液晶装置において、比較的簡単な構成を用いてワイド画面表示も通常画面表示も選択的に行うことが可能となり、従来必要であったラインメモリ倍速動作等による外部回路への負担と消費電力を軽減するとともに、液晶装置の素子特性に要求される能力も従来と同様の水準でよいため、安価に高機能な表示装置が実現される。更に、第1実施例においてXシフトレジスタ1aを双方向走査可能なシフトレジスタとして構成することにより、合計4個所の走査開始位置を指定可能とすることもでき、左右反転時等におけるアスペクト比の変更も容易である。

## 【0046】

20

また、Xシフトレジスタ1aは、一系列のシフトレジスタとして説明されてきたが、複数系列のシフトレジスタとして構成し（後述の図18参照）、複数系列のシフトレジスタからサンプリング回路14の駆動信号を順番に出力させてもよいことは言うまでもない。

## 【0047】

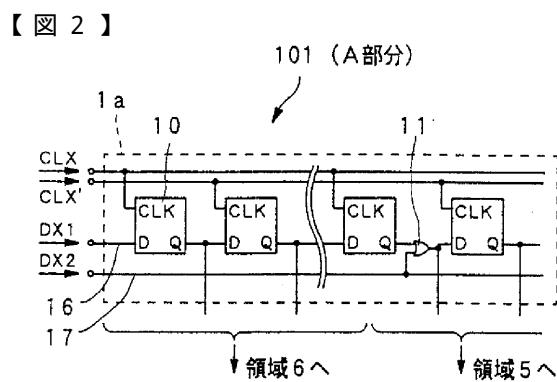

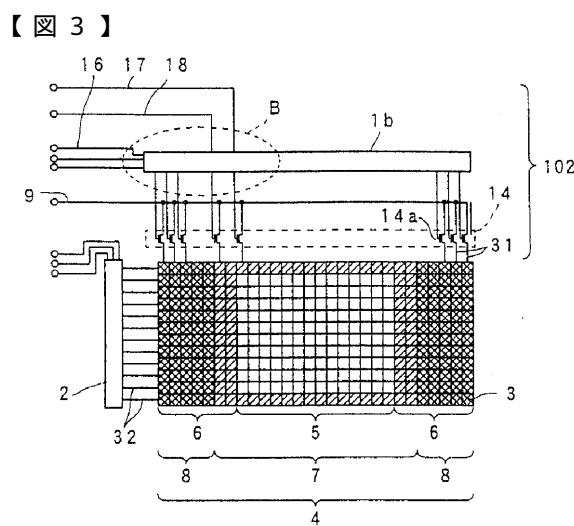

## (第2実施例)

次に第2実施例について図3及び図4を参照して説明する。図3は、第2実施例にかかる液晶装置の回路ブロック図であり、図4は、図3のB部分の拡大図である。尚、図3及び図4において図1及び図2に示した第1実施例の場合と同じ構成要素には同一の参照符号を付し、その説明は省略する。

## 【0048】

30

図3及び図4で示される液晶装置は、第1実施例の液晶装置に、水平走査スタート信号を挿入する論理和回路をさらに1つ追加した構成となっている。

## 【0049】

より具体的には、図3に示すように、第2実施例における液晶装置は、Xシフトレジスタ1b、サンプリング回路14及び各種配線（9、16、17、18等）から構成された画像信号供給装置102を備えている。そして、図4に示すように、Xシフトレジスタ1bは、配線17から水平走査スタートパルスDX2が供給される論理和回路11に加えて、配線18から水平走査スタートパルスDX3が供給される論理和回路11'を備えて構成されている。従って、Xシフトレジスタ1bは、合計三個所（左端のフリップフロップ10、論理和回路11'の右側のフリップフロップ10及び論理和回路11の右側のフリップフロップ10）から転送信号の発生を開始できる。

40

## 【0050】

従って、図3に示す液晶装置は、これら3個所から水平走査を開始できる。ここで、第2実施例の液晶装置は水平方向に427列、垂直方向に260行の正方形の画素マトリクス3を有し、アスペクト比16:9の表示を行う際には、Xシフトレジスタ1bを末端（左端）から水平走査し、画像表示領域の上下20行ずつ計40行の表示を黒表示とすることで、 $427 : 240 = 16 : 9$ のアスペクト比を有する画像表示領域4に表示を行う。また、アスペクト比4:3の画像表示領域5に表示を行うときには、Xシフトレジスタ1bを非画像表示領域6以後の53列目から320列分だけ水平走査して有効な画像表示を行うようにし、垂直方向については、画像表示領域の上下20行ずつ計40行の表示を黒表

50

示とすることで、 $320 : 240 = 4 : 3$  のNTSC表示を行うことが可能である。さらに、垂直方向を230行すべて使い、Xシフトレジスタ1bを新たに追加された第三の走査開始位置（論理和回路11'に対応する位置）である40列目より347列分だけ水平走査して有効な画像表示を行うようにして、PAL非画像表示領域8部分の水平走査をスキップし、 $247 : 260 = 4 : 3$  のPAL画像表示領域7を構成することにより、PAL表示を行うことが可能である。

#### 【0051】

このように第2実施例によれば、走査開始位置を三個以上設けることにより、ワイド表示とNTSC、PALのような異なる表示モードへも容易に対応することが可能となる。更に、第2実施例においてXシフトレジスタ1bを双方向走査可能なシフトレジスタとして構成することにより、合計6個所の走査開始位置を指定可能とすることで、左右反転時等においてもアスペクト比の変更も容易である。10

#### 【0052】

また、Xシフトレジスタ1bは、一系列のシフトレジスタとして説明されてきたが、複数系列のシフトレジスタとして構成し（後述の図18参照）、複数系列のシフトレジスタからサンプリング回路14の駆動信号を順番に出力させてもよいことは言うまでもない。

#### 【0053】

##### （第3実施例）

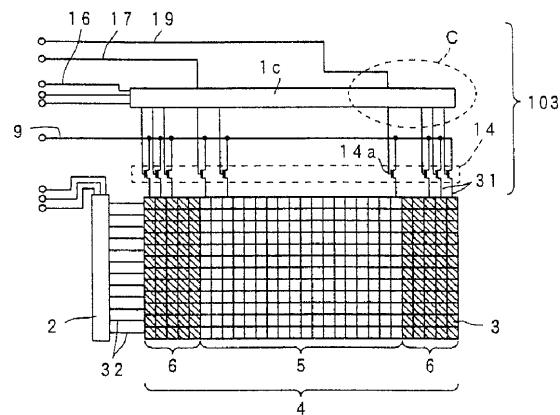

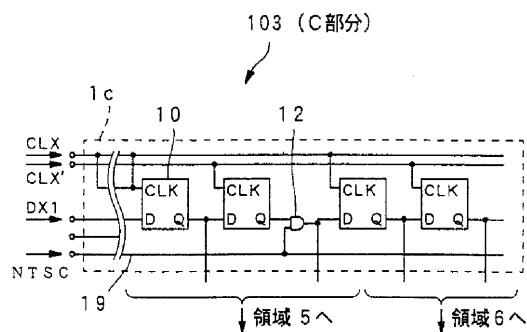

次に第3実施例について図5及び図6を参照して説明する。図5は、第3実施例にかかる液晶装置の回路ブロック図であり、図6は、図5のC部分の拡大図である。尚、図5及び図6において図1及び図2に示した第1実施例の場合と同じ構成要素には同一の参照符号を付し、その説明は省略する。20

#### 【0054】

図5及び図6で示される液晶装置は、第1実施例の液晶装置に、水平走査を所定位置で停止するための論理積回路を追加した構成となっている。

#### 【0055】

より具体的には、図5に示すように、第3実施例における液晶装置は、Xシフトレジスタ1c、サンプリング回路14及び各種配線（9、16、17、19等）から構成された画像信号供給装置103を備えている。そして、図6に示すように、Xシフトレジスタ1cは、配線19からNTSC信号が供給される論理積回路12を備えて構成されている。従って、Xシフトレジスタ1cは、例えば論理積回路12の前段（左側）にあるフリップフロップ10が転送信号を出力するタイミングに合わせてローレベルに変化するNTSC信号を供給することにより、この転送信号を次段（右側）のフリップフロップ10に転送されないようにできる。或いは、このようなNTSC信号を供給しないことにより又は前段にあるフリップフロップ10が転送信号を出力するタイミングに合わせてハイレベルに変化するNTSC信号を供給することにより、この論理積回路12を介して転送信号を次段のフリップフロップ10に転送できる。従って、NTSC信号のレベルを制御することにより、論理積回路12を挿入した位置を水平走査の停止位置としたり、或いは、論理積回路12を挿入した位置を超えて最後（右端）まで水平走査することが可能となる。30

#### 【0056】

従って、図5に示す液晶装置は、2個所から水平走査を開始できると共に2個所で水平走査を序止できる。ここで、第3実施例の液晶装置はアスペクト比16:9の画像表示領域4を有し、アスペクト比4:3の画像表示領域5の走査終了位置にあたる所定の段、すなわち、Xシフトレジスタ1cのうちサンプリングのための転送信号を出力する総有効段数のおよそ8分の7（ $\{1 + (4/3) / (16/9)\} / 2$ 段目に論理積回路12を挿入した回路構成となっている。従って、アスペクト比16:9の画像表示領域4において、アスペクト比4:3の表示を行うときには、4:3画像表示領域5の終了位置にあたるフリップフロップ10の出力（右側）に挿入された論理積回路12を用いて水平走査を停止させ、無駄なXシフトレジスタ1cの走査動作を省略することが可能である。40

#### 【0057】

このように第3実施例によれば、非画素表示領域6に対応するXシフトレジスタ1cの8分の2を走査しなくてよいので、この部分に要する無駄な走査時間が節約され、外部回路への負担を大幅に軽減するとともに、消費電力の低減を実現できる。

#### 【0058】

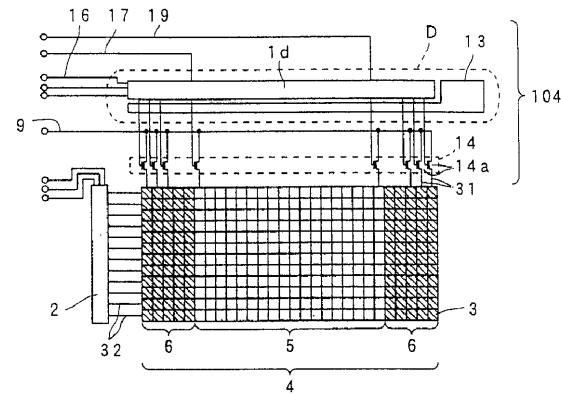

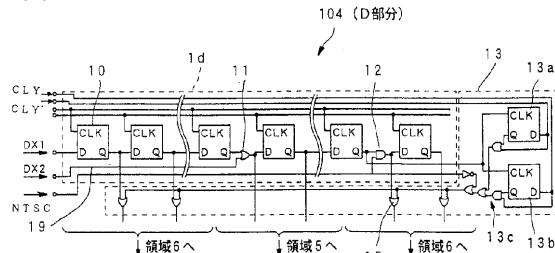

##### (第4実施例)

次に第4実施例について図7から図10を参照して説明する。図7は、第4実施例にかかる液晶装置の回路ブロック図であり、図8は、図7のC部分の拡大図である。また、図9及び図10は第4実施例における各種信号のタイミングチャートである。尚、図7及び図8において図5及び図6に示した第3実施例の場合と同じ構成要素には同一の参照符号を付し、その説明は省略する。

10

#### 【0059】

図7及び図8で示される液晶装置は、第3実施例の液晶装置に対し、非画像表示領域6に黒表示を行う回路（以下SB（サイドブラック）回路と呼ぶ）を附加した構造となっている。

#### 【0060】

より具体的には、図7に示すように、第4実施例における液晶装置は、Xシフトレジスタ1d、サンプリング回路14及び各種配線（9、16、17、19等）並びにSB回路13から構成された画像信号供給装置104を備えている。そして、図8に示すように、SB回路13は、Xシフトレジスタ1dにおける水平走査開始用の論理和回路11の左側にあるフリップフロップ10の出力信号線及び論理積回路12（水平走査停止用）の右側にあるフリップフロップ10の出力信号線に夫々接続された複数の論理和回路15と、水平走査停止用の論理積回路122の前段（左側）にあるフリップフロップ10からの転送信号をクロック入力とする一対のフリップフロップ13a及び13bと、これらのフリップフロップ13a及び13bの出力並びに配線19を介して供給されるNTSC信号により複数の論理積回路15を介して同時にサンプリング回路駆動信号をサンプリング回路14に供給する論理回路部13cとを備えて構成されている。

20

#### 【0061】

前述の第3実施例の液晶装置は、非画像表示領域6の画素電極は電圧が印加されない状態であるので、ノーマリー・ホワイトモード等の液晶モードを使用する場合、この部分が明るく表示されるため、画像部分の表示品位が損なわれ、これらの液晶モードには不向きであるという問題がある。

30

#### 【0062】

しかし、第4実施例では、上述のようにXシフトレジスタ1dに同期されたSB回路13を附加することによりこの問題は解決される。即ち、第4実施例によれば、アスペクト比4:3の画像表示時には、Xシフトレジスタ1dの画像表示領域5の最終段に当たるフリップフロップ10の出力をトリガーとして、SB回路13が作動することで非画像表示領域6に対応するサンプリング回路14のTFT14aを、論理和回路15により一斉に導通状態とし、配線9から供給される黒表示信号を一斉に書き込むことが可能となるのである。

#### 【0063】

40

Xシフトレジスタを複数系列設け、順番にサンプリング回路14の駆動信号を出力させる場合には（後述の図18参照）、複数系列シフトレジスタの最終駆動信号を出力するフリップフロップ10を最終段として、SB回路13をトリガーすればよい。

#### 【0064】

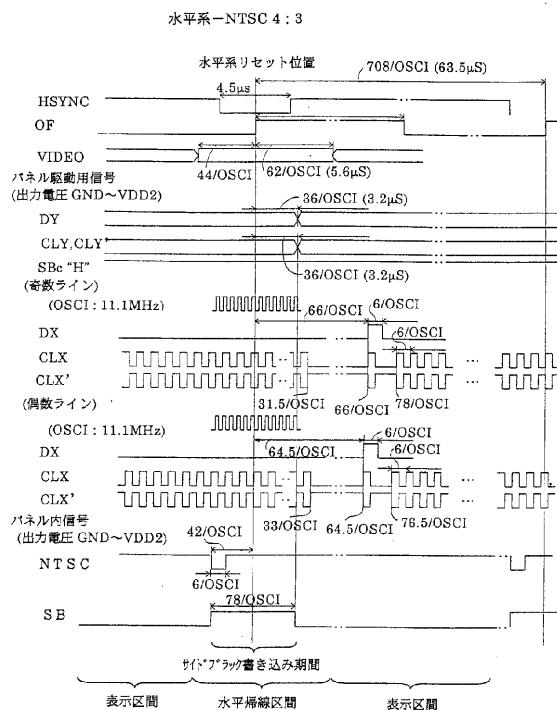

次に、以上の如く構成された第4実施例の動作について図9及び図10のタイミングチャートを参照して、説明する。尚、水平走査の開始にかかるタイミングについては、第1から第3実施例の場合も同様であり、水平走査の停止にかかるタイミングについては、第3実施例の場合も同様である。

#### 【0065】

先ず、図9を参照して、図7及び図8に示したNTSCワイド規格に基づくアスペクト比

50

16:9の画面を持つ液晶装置において、NTSC規格に基づくアスペクト比4:3の画像を表示する際の動作について説明する。

#### 【0066】

図9に示すように、テレビチューナ、ビデオプレーヤ等の画像信号源から、画像信号処理IC等の外部画像信号処理回路に、708/OSCI(基準発信周波数) = 63.5 μsec毎に4.5 μsec幅の水平同期信号HSYNが入力され、水平系リセット位置でハイレベルとなるOF信号が入力され、実際の表示に係る有効な画像信号が各水平走査区間(水平表示区間+水平帰線区間)毎に水平系リセット位置より44/OSCI前に終了すると共に62/OSCI(=5.6 μsec)後に開始する画像信号VIDEOが入力される。

10

#### 【0067】

すると、これらに対応して外部画像信号処理回路から、パネル駆動用信号として、Yシフトレジスタ2に対し、水平系リセット位置より36/OSCI = 3.2 μsec後に、垂直走査スタート信号DY及びクロック信号CLY(及びその反転クロック信号CLY')が入力される。また、SB(サイドブラック)書き込みを行う旨を示すハイレベルのサイドブラック制御用の信号SBCが入力される。

#### 【0068】

更に、奇数ラインからなる(NTSC規格では、263本の走査線からなる)フィールドに対する水平走査の場合には、Xシフトレジスタ1aに、水平系リセット位置より66/OSCI後に、パルス幅6/OSCIを有する水平走査スタート信号DXが入力され、このパルスに同期した周期6/OSCIのクロック信号CLX(及びその反転クロック信号CLX')が入力される。偶数ラインからなる(262本の走査線からなる)フィールドに対する水平走査の場合には、Xシフトレジスタ1aに、水平系リセット位置より64.5/OSCI後に、パルス幅6/OSCIを有する水平走査スタート信号DXが入力され、このパルス信号に同期した周期6/OSCIのクロック信号CLX(及びその反転クロック信号CLX')が入力される。尚、この場合の基準発振周波数OSCIは、11.1MHzである。

20

#### 【0069】

そして、これらのパネル駆動用信号に基づいて、Xシフトレジスタ1aは、サンプリング回路14を駆動するが、特にこの場合には、サイドブラック制御用の信号SBCがハイレベルとされているので、配線17を介して論理回路11に対し水平走査スタート信号DXが(図2に示した信号DX2として)入力される。このため、水平走査は、この論理回路11の右側にあるフリップフロップ10から開始され、これに対応する信号線31に接続された画素列から画像信号VIDEOによる画像表示が行われる。即ち、画像表示領域5における有効な画像表示が行われる。

30

#### 【0070】

そして、外部画像信号処理回路から水平系リセット位置よりも42/OSCI前に、パルス幅6/OSCIを有するNTSC信号が入力され、このNTSC信号の立ち下がり時点から、水平帰線区間内の78/OSCIの時間は、サイドブラック書き込み期間としてサイドブラック書き込み用の信号SBがハイレベルとされる。このため、信号SBがハイレベルの間には、論理回路11の左側にあるフリップフロップ10及び論理積回路12の右側にあるフリップフロップ10に対応する信号線31に接続された画素列では、入力画像信号線9から供給される黒レベルの画像信号VIDEOによる黒表示が行われる。即ち、非画像表示領域6における黒表示が行われる。

40

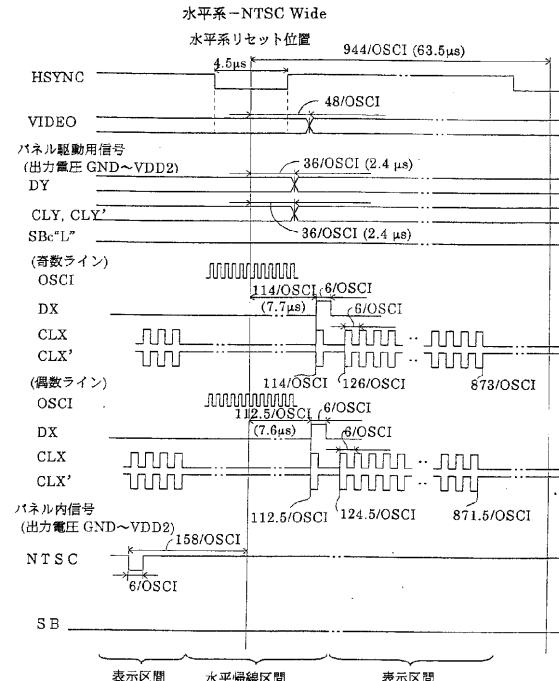

#### 【0071】

次に、図10を参照して、図1に示したNTSCワイド規格に基づくアスペクト比16:9の画面を持つ液晶装置において、NTSCワイド規格に基づくアスペクト比16:9の画像を表示する際の動作について説明する。尚、この場合には、画素マトリクス3の全域(即ち、画顔表示領域4)に、画像信号に基づく有効な画像を表示すればよく、左右に黒表示をする特別な制御は必要ない。

50

**【0072】**

図10に示すように、画像信号源から、外部画像信号処理回路に、944 / OSC1毎に4.5 μsec幅の水平同期信号HSYNが入力され、各水平走査期間毎に水平系リセット位置より48 / OSC1後に開始する画像信号VIDEOが入力される。

**【0073】**

すると、これらに対応して外部画像信号処理回路から、パネル駆動用信号として、Yシフトレジスタ2に対し、水平系リセット位置より36 / OSC1後に、垂直走査スタート信号DY及びクロック信号CLY(及びその反転クロック信号CLY')が入力される。また、SB(サイドブラック)書き込みを行わない旨を示すローレベルのサイドブラック制御用の信号SBCが入力される。

10

**【0074】**

更に、奇数ラインからなるフィールドに対する水平走査の場合には、Xシフトレジスタ1aに、水平系リセット位置より114 / OSC1後に、パルス幅6 / OSC1を有する水平走査スタート信号DXが入力され、このパルス信号に同期した周期6 / OSC1のクロック信号CLX(及びその反転クロック信号CLX')が入力される。偶数ラインからなるフィールドに対する水平走査の場合には、Xシフトレジスタ1aに、水平系リセット位置より112.5 / OSC1後に、パルス幅6 / OSC1を有する水平走査スタート信号DXが入力され、このパルス信号に同期した周期6 / OSC1のクロック信号CLX(及びその反転クロック信号CLX')が入力される。尚、この場合の基準発振周波数OSC1も、11.1MHzである。

20

**【0075】**

そして、これらのパネル駆動用信号に基づいて、Xシフトレジスタ1aは、サンプリング回路14を駆動するが、特にこの場合には、信号SBCがローレベルとされているので、配線16を介して水平走査スタート信号DXが(図2に示した信号DX1として)入力される。このため、水平走査は、左端にあるフリップフロップ10から開始され、これに対する信号線31に接続された画素列から画像信号VIDEOによる画像表示が行われる。即ち、画像表示領域4における有効な画像表示が行われる。

**【0076】**

この場合、外部画像信号処理回路から水平系リセット位置よりも158 / OSC1前に、パルス幅6 / OSC1を有するNTSC信号が入力されるが、サイドブラック書き込み用の信号SBは常にローレベルとされ、サイドブラックにおける黒表示が行われることはない。

30

**【0077】**

以上詳細に説明したように第4実施例によれば、SB回路13は、水平帰線区間の大部分を画素への書き込み時間として動作するため、十分に長い書き込み動作が実現され、非常に高いコントラスト比の要求される電気見切り枠の表示が可能となる。

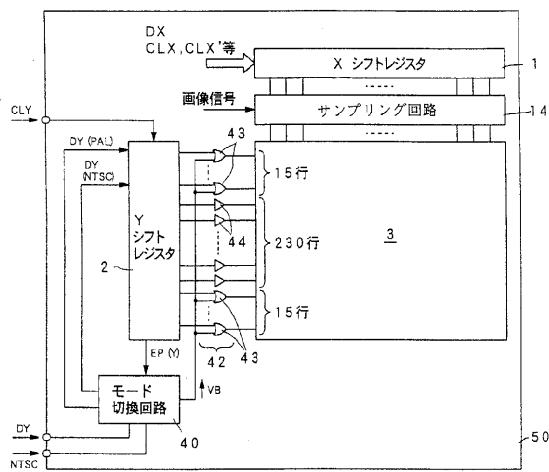

**【0078】****(第5実施例)**

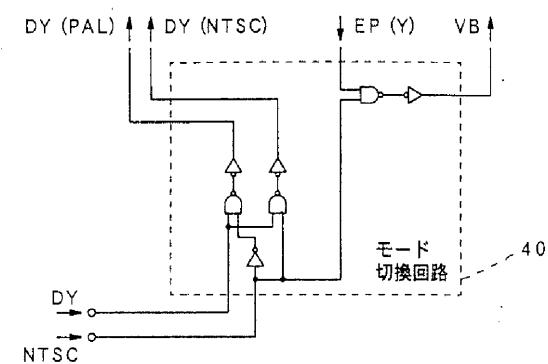

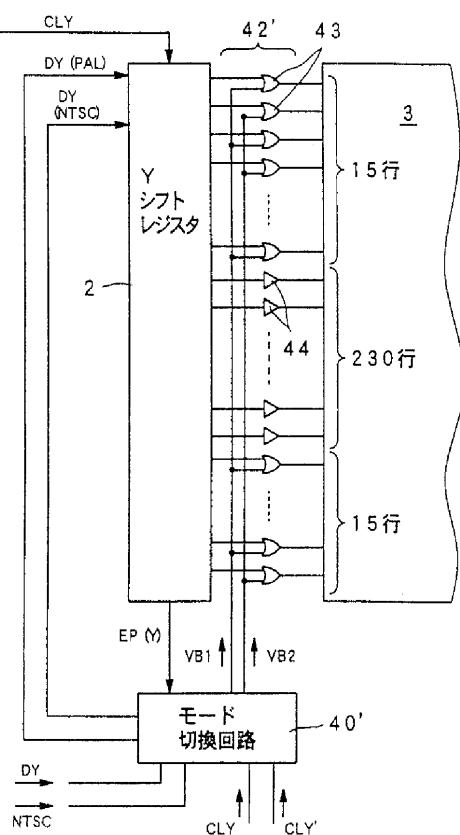

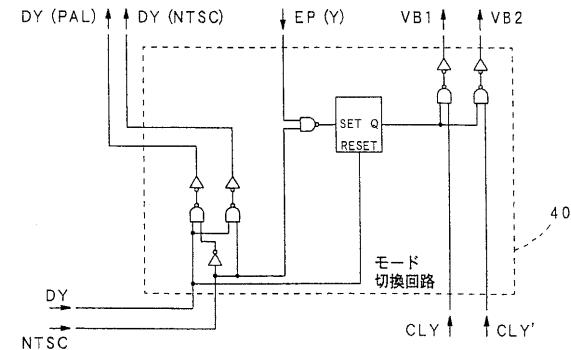

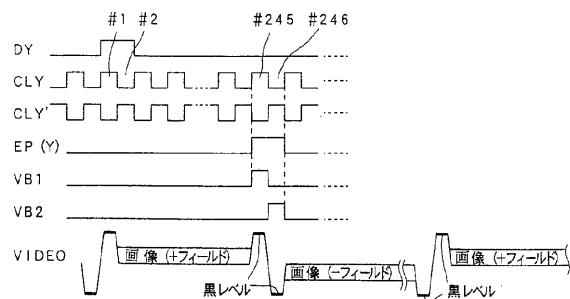

次に第5実施例について図11から図13を参照して説明する。図11は、第5実施例にかかる液晶装置の回路ブロック図であり、図12は、図11のモード切換回路の回路ブロック図であり、図13は、第5実施例における各種信号のタイミングチャートである。尚、図11において図1に示した第1実施例の場合と同じ構成要素には同一の参照符号を付し、その説明は省略する。

40

**【0079】**

図11において、液晶装置は、TFTアレイ基板50上に形成された画素マトリクス3、Xシフトレジスタ1(第1から第4実施例のXシフトレジスタ1a～1dのいずれか一つ)、サンプリング回路14及びYシフトレジスタ2に加えて、画素マトリクス3の上下の全域を画像表示領域にする表示モードと画素マトリクス3の上下の一定幅領域を非画像表示領域にする表示モードとを切り換えるためのモード切換回路40並びに、複数の論理回路43及びバッファ44を含む論理回路分42を備えて構成されている。

50

**【0080】**

本実施例では、画素マトリクス3のアスペクト比は4：3であり、モード切り換えとしては、PAL表示モード（アスペクト比4：3）とNTSCワイド表示モード（アスペクト比16：9）とを切り換える場合について説明する。即ち、PAL表示モードの際には、上下の全領域を画換表示領域とし、NTSCワイド表示モードの場合には、画面内の上下の一定幅領域を非画像表示領域とする場合について説明する。

**【0081】**

図12に示すように、モード切換回路40には、外部画像信号処理回路から、垂直走査スタート信号DYに加えて、クロックモード切り換え信号として、ハイレベルでNTSCワイド表示モードであることを示すと共にローレベルでPAL表示モードであることを示すNTSC信号が入力される。すると、NTSC信号のレベルに応じてNTSCワイド表示用のスタートパルスDY(NTSC)又はPAL表示用のスタートパルスDY(PAL)がモード切換回路40からYシフトレジスタ2に出力される。Yシフトレジスタ2では、NTSCワイド用のスタートパルスDY(NTSC)が入力されると、上から16行目と下から16行目との間に位置する中央の230行の走査線について垂直走査を行い、PAL表示用のスタートパルスDY(PAL)が入力されると、上から下までの260行の全走査線について垂直走査を行うように構成されている。

10

**【0082】**

モード切換回路40は、更にYシフトレジスタ2からエンドパルス信号EP(Y)が入力されると、NTSC信号がハイレベルの場合には、上下の15行をブラックにするための信号V3をこれらの行に対応する走査線に夫々接続された論理和回路43に出力するよう構成されている。従って、この場合には、論理和回路43を介して信号VBを受ける画素マトリクス3の上下の15行は、これらの行に対応する黒レベルの画像信号VIDEOを信号線に供給することにより、常に黒表示とされる。他方、モード切換回路40は、NTSC信号がローレベルの場合には、信号VBを出力しない。従って、この場合には、画素マトリクス3の上下の15行は、黒表示とされることなく、PAL規格に基づく有効な画面表示が行われる。

20

**【0083】**

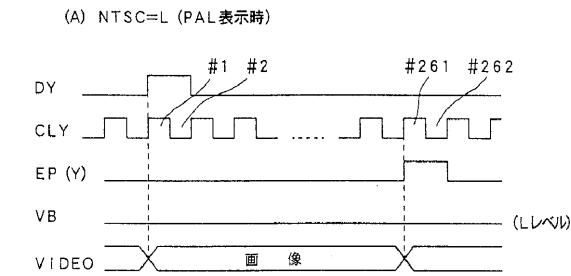

次に、以上の如く構成された第5実施例の動作について図13のタイミングチャートを参照して、説明する。

30

**【0084】**

先ず、図13(A)を参照して、NTSC信号がローレベル（即ち、PAL表示モード）の場合について説明する。

**【0085】**

図13(A)に示すように、この場合には、垂直走査スタート信号DYが入力されると、クロック#1から#260の間に、水平走査が260行について行われた後、エンドパルス信号EP(Y)が出力されるが、信号VBは常にローレベルにあるので、特に上下に黒表示が行われることではなく、この260行の水平走査の間中、画像信号VIDEOが供給されて、PAL規格に基づいて画素マトリクス3の全面にアスペクト比4：3の画像が表示される。

40

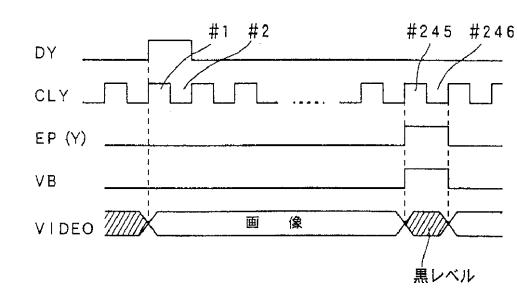

**【0086】**

次に、図13(B)を参照して、NTSC信号がハイレベル（即ち、NTSCワイド表示モードの場合）の場合について説明する。

**【0087】**

図13(B)に示すように、この場合には、垂直走査スタート信号DYが入力されると、クロック#1から#245の間、水平走査が245行について行われた後、エンドパルス信号EP(Y)が出力される。すると、モード切換回路40からは信号VBが出力され、この信号VBは、論理和回路43を夫々介して上下15行にある各画素のTFTに供給されて、これらのTFTが一斉に導通状態とされる。従って、上下15行で黒レベルの画像信号VIDEOによる黒表示を行いつつ中央の245行で画像信号VIDEOによる有効な表示が行われる。

**【0088】**

50

このように第5実施例によれば、表示画面のサイズと表示画像のサイズとが合わない場合に、画素マトリクスの上下にも黒表示を行うことができ、よって、左右左右に黒表示を行うことにより画素マトリクス3からなる一定サイズの表示画面上に所望のサイズの画像を表示できるので大変便利である。

#### 【0089】

尚、Yシフトレジスタ2は、同一の回路を走査線の左右に設けて両端側から同一走査線を駆動してもよい。また、Yシフトレジスタ2を2分割し、走査線の左右端に分けて配置し、左側Yシフトレジスタからの走査線駆動と右側Yシフトレジスタからの走査線駆動とが交互になるように構成してもよいことは言うまでもない。これらの場合、非画像表示領域に対応する各々のYシフトレジスタの出力に対して論理和回路43が挿入される。

10

#### 【0090】

##### (第6実施例)

次に第6実施例について図14から図16を参照して説明する。図14は、第5実施例にかかる液晶装置の要部回路ブロック図であり、図15は、図11のモード切換回路の回路ブロック図であり、図16は、第6実施例における各種信号のタイミングチャートである。尚、図14において図1に示した第1実施例の場合と同じ構成要素には同一の参照符号を付し、その説明は省略する。

#### 【0091】

第5実施例では、一つの信号VBを用いて、画素マトリクス3の上下の一定幅の領域で黒表示を行ったが、第6実施例では、上下を黒表示するための2つの位相が異なる信号VB1及びVB2信号を用いる。

20

#### 【0092】

一般に液晶の劣化を防止するためには液晶を交流駆動する必要があるが、交流駆動方式の代表的なものとして、一フィールド毎（或いはフレーム毎）に画像信号の極性を反転させるフィールド反転駆動方式がある。更に、表示画像のフリッカの防止にも役立つ交流駆動方式として、一走査線毎に（一行毎に）画像信号の極性を反転させる1H反転駆動方式がある。そこで、第6実施例は、このフィールド反転駆動方式や1H反転駆動方式により画素マトリクスの上下の黒表示をも好適に行うことができる液晶装置を提供するものである。

#### 【0093】

より具体的には図14において、液晶装置は、図示しない第1から第4実施例におけるXシフトレジスタ1a、1b、1c又は1d及びサンプリング回路14を備えており、画素マトリクス3及びYシフトレジスタ2に加えて、画素マトリクス3の全域を画像表示領域にする表示モードと画素マトリクス3の上下の一定幅の領域を非画像表示領域にする表示モードとを切り換えるためのモード切換回路40'並びに、複数の論理和回路43を含む論理回路分42'を備えて構成されている。

30

#### 【0094】

本実施例では、第5実施例の場合と同様に、画素マトリクス3のアスペクト比は4:3であり、モード切り換えとしては、PAL表示モードとNTSCワイド表示モードとを切り換える場合について説明する。

#### 【0095】

40

図15に示すように、モード切換回路40'には、策5実施例の場合と同様に水平走査スタート信号DYに加えて、NTSC信号が入力され、NTSC信号のレベルに応じてスタートパルスDY(NTSC)又はスタートパルスDY(PAL)がYシフトレジスタ2に出力される。

#### 【0096】

ここで、モード切換回路40'は、Yシフトレジスタ2からエンドパルス信号EP(Y)が入力されると、NTSC信号がハイレベルの場合には、上下を黒表示するための信号VB1及びVB2を、上下15行の走査線に夫々接続された論理和回路43に夫々一つおきに出力するよう接続されている。特に、モード切換回路40'には、クロック信号CLY(及びその反転クロックCLY')が入力されており、このクロック信号CLYの半周期だけ信号VB1及びVB2は位相が相互にずれている。従って、この場合には、論理和回路43を介して信号VB1

50

又はV B 2 を受ける画素マトリクス3の上下の15行は、これらの行に対応する画像信号V I D E Oを、1フィールド又はフレーム毎牟1走査線毎に極性の反転した黒レベルの電圧が液晶に印加されるように信号線に供給することにより、常に黒表示とされる。他方、モード切換回路40'は、NTSC信号がローレベルの場合には、信号VB1又はV B 2 出力しない。従って、この場合には、画素マトリクス3の上下の15行は、黒表示とされることなく、PAL規格に基づく有効な画面表示が行われる。

#### 【0097】

次に、以上の如く構成された第6実施例の動作について図16のタイミングチャートを参照して、説明する。尚、NTSC信号がローレベル（即ち、PAL表示モード）の場合については、信号V B 1 及びV B 2 は出力されず、結果として図13(A)で説明した第5実施例の場合と同様であるので、その説明は省略する。以下、NTSC信号がハイレベル（即ち、NTSCワイド表示モードの場合）の場合について説明する。

10

#### 【0098】

図16に示すように、この場合には、垂直走査スタート信号DYが入力されると、クロック#1から#245の間、水平走査が245行について行われた後、エンドパルス信号EP(Y)が出力される。すると、モード切換回路40'からはエンドパルス信号EP(Y)の前半の半周期にハイレベルの信号VB1が outputされ、更に、エンドパルス信号EP(Y)の後半の半周期にハイレベルの信号VB2が出力される。これらの信号VB1及びVB2は、論理和回路43を介して上下15行にある各画素のTFTに供給されて、これらのTFTが一斉に導通状態とされる。従って、画素マトリクスの上下15行で、フィールド毎や走査線毎に極「生反転する黒レベル」の画像信号V I D E Oによる黒表示を行いつつ、中央の245行で、やはりフィールド又はフレーム毎や走査線毎に液晶印加電圧の極性が反転する画像信号V I D E Oによる有効な表示が行われる。ここに液晶印加電圧とは、画素電極と、これに対向する基板に配置される対向電極（共通電極）との差電圧に基づきそれらの間に挟持される液晶部分に印加される電圧である。

20

#### 【0099】

尚、Yシフトレジスタ2は、同一の回路を走査線の左右に設けて両端側から同一走査線を駆動してもよい。また、Yシフトレジスタ2を2分割し、走査線の左右端に分けて配置し、左側Yシフトレジスタからの走査線駆動と右側Yシフトレジスタからの走査線駆動とが交互になるように構成してもよいことは言うまでもない。これらの場合、非画像表示領域に対応する各々のYシフトレジスタの出力に対して論理和回路43が挿入される。

30

#### 【0100】

以上のように第6実施例によれば、画素マトリクス3の上下に黒表示を行うことができるのみならず、この上下の非画像表示領域においても、フィールド又はフレーム反転駆動方式や1H反転駆動方式を用いて黒表示を行うようにしたので、この部分における直流駆動による液晶の劣化を有効に防そことができ、特に走査線毎に反転する1H反転駆動方式を挽和した場合には表示画像のフリッカを防止できるので、実践上大変有利である。

#### 【0101】

なお、以上の実施例においては、XシフトレジスタやYシフトレジスタのシフトスタートを途中段からスタートできるようにした実施例、Xシフトレジスタを途中段でシフト停止できるようにした実施例、黒表示をフィールド反転駆動方式や1H反転駆動方式により行う実施例等を説明したが、これらを本発明の主旨に反しない範囲で、組合わせて実施し、画素マトリクスの左右上下の任意の位置において途中からシフトスタートし途中でシフト停止するようにしてもよいし、フィールド又はフレーム反転駆動方式や1H反転駆動方式以外の交流駆動方式で左右上下の非画像表示領域における黒表示を行うようにしてもよい。更に任意のn行毎にハイレベルのV B 信号を割り当てるように構成してもよい。

40

#### 【0102】

以上の各実施例では、絶縁性基板上に形成されたTFTを有する液晶パネルを前提に説明したが、半導体基板とガラス基板とにより液晶を挟持する反射型液晶パネルの場合には、TFTで形成した素子は、半導体基板に形成されたMOSトランジスタに置き換えて構成すること

50

が出来る。

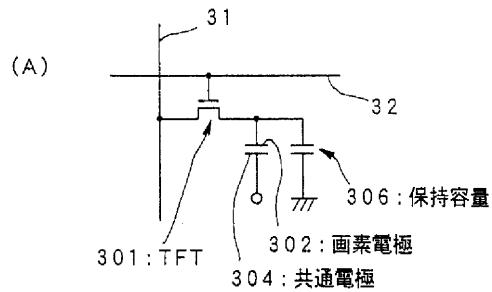

#### 【0103】

以上の各実施例では、各画素におけるスイッチング素子をTFTで構成した場合について説明したが、各実施例において、各画素におけるスイッチング素子をMIM素子で構成してもよい。図17(A)に示すようにスイッチング素子をTFT301で構成する場合には、信号線31にTFT301のソース(又はドレイン)が接続され、走査線32にTFT301のゲートが接続される。そして、TFT301のドレイン(又はソース)には、画素電極302が接続されており、対向基板に設けられた共通電極304は、この画素電極302に液晶を介して対向配置されている。そして、この画素電極302と並列に保持容量306が設けられている。他方、図17(B)に示すようにスイッチング素子をMIM素子401で構成する場合には、信号線31にMIM素子401の一方の端子が接続され、更にMIM素子401の他方の端子には画素電極402が接続される。そして、走査線32はその一部が画素電極402と液晶を介して対向する対向電極404とされる。

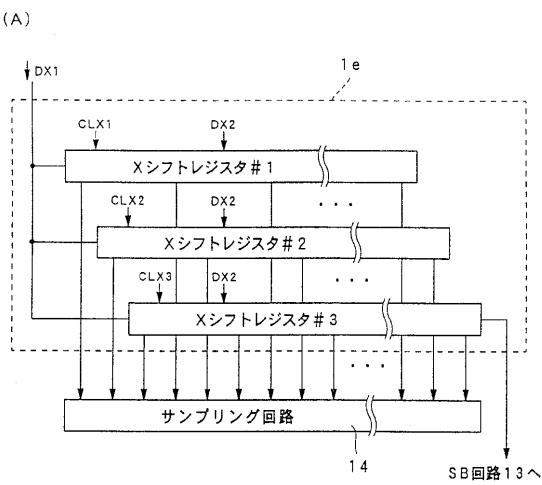

#### 【0104】

以上の各実施例では、Xシフトレジスタは、一系列のシフトレジスタとして説明されてきたが、各実施例のXシフトレジスタを、図18(A)に示すように、3つのXシフトレジスタ#1、Xシフトレジスタ#2及びXシフトレジスタ#3を含む複数系列のシフトレジスタ1eとして構成してもよい。この場合、図18(B)に示すように、位相が相互にずれたクロック信号CLX1、CLX2及びCLX3が各シフトレジスタ#1、#2及び#3のクロック信号として夫々用いられ、複数系列のシフトレジスタ1eからは、これら3つのシフトレジスタから出力される、クロック信号の位相ずれに対応して位相がずれた3種類の転送信号が順次出力され、3種類の転送信号のタイミングにより順次サンプリングが行われる。なお、複数系列のシフトレジスタとして構成した場合、転送開始及び停止の制御は、各シフトレジスタの画像表示領域の開始位置に対応するフリップフロップ10の転送信号入力端と終了位置に対応するフリップフロップ10の転送信号出力端とに、以上の各実施例にて説明したのと同様な構成の論理回路を挿入して行うことができる。

#### 【0105】

更に、以上の各実施例では、Xシフトレジスタの各段(各フリップフロップ)から出力される転送信号が、サンプリング回路駆動信号としてXシフトレジスタからその外部へ出力されるように構成されているが、図19に示すように、複数段おきに出力される転送信号をXシフトレジスタからその外部へサンプリング回路駆動信号として出力するように各実施例のXシフトレジスタを構成してもよい。図19においては、相隣接する3つのフリップフロップ10は、2つおきに転送信号をXシフトレジスタ1fからサンプリング回路14へ出力するように、且つ他のフリップフロップ10から出力される転送信号はXシフトレジスタ1fからその外部へ出力されることなく次段へ転送されるように構成されている。

#### 【0106】

##### (その他の実施例)

次に、以上詳細に説明した液晶装置を備えた電子機器の実施例について図9から図13を参照して説明する。

#### 【0107】

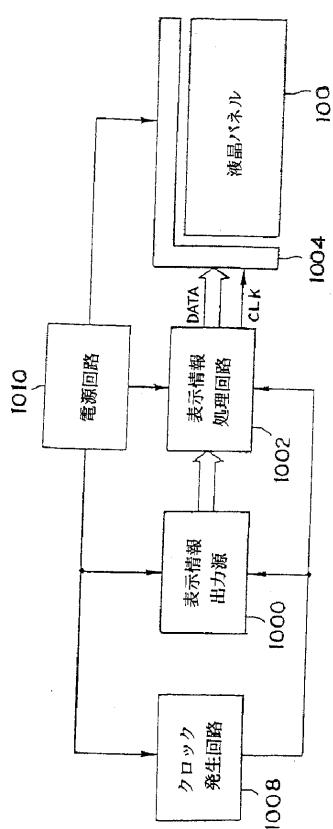

先ず図20に、第1から第6実施例に示した液晶装置を備えた電子機器の実施例の概略構成を示す。

#### 【0108】

図20において、電子機器は、表示情報出力源1000、表示情報処理回路1002、駆動回路1004、液晶パネル100、クロック発生回路1008並びに電源回路1010を備えて構成されている。表示情報出力源1000は、ROM(Read Only Memory)、RAM(Random Access Memory)、光ディスク装置などのメモリ、テレビ信号を同調して出力する同調回路等を含み、クロック発生回路1008からのクロック信号に基づいて、所定フォーマットの画像信号などの表示情報を表示情報処理回路1002に出力する。表示情報処理回路1002は、増幅・極性反転回路、相展開回路、ローテーション回路、ガンマ補正回路、クランプ回路等の周知の各種処理

10

20

30

40

50

回路を含んで構成されており、クロック信号に基づいて入力された表示情報からデジタル信号を順次生成し、クロック信号CLXと共に駆動回路1004に出力する。駆動回路1004は、液晶パネル100を駆動する。電源回路1010は、上述の各回路に所定電源を供給する。尚、液晶パネル100を構成するTFTアレイ基板の上に、駆動回路1004を搭載してもよく、これに加えて表示情報処理回路1002を搭載してもよい。

#### 【0109】

次に図21から図24に、一このように構成された電子機器の実施例を夫々示す。

#### 【0110】

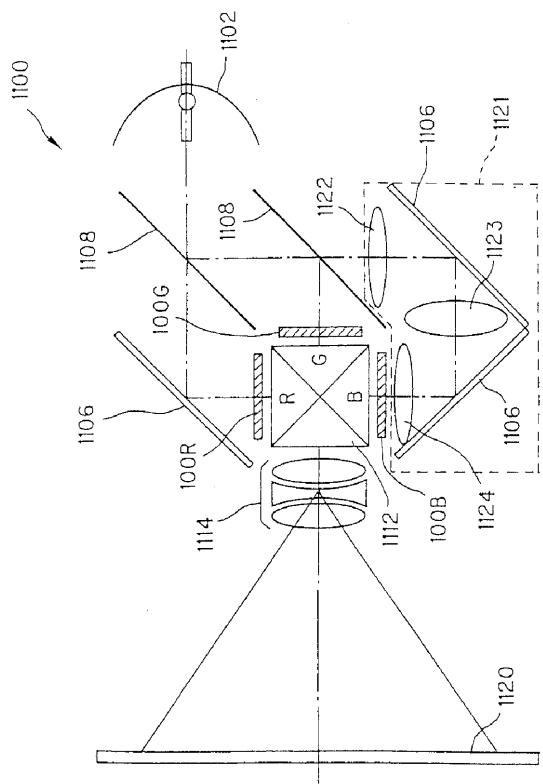

図21において、電子機器の一例たる液晶プロジェクタ1100は、上述した駆動回路1004がTFTアレイ基板上に搭載された液晶パネル100を含む液晶モジュールを3個用意し、夫々RGB用のライトバルブ100R、100G及び100Bとして用いたプロジェクタとして構成されている。液晶プロジェクタ1100では、メタルハライドランプ等の白色光源のランプユニット1102から投写光が発せられると、3枚のミラー1106及び2枚のダイクロイックミラー1108によって、RGBの3原色に対応する光成分R、G、Bに分けられ、各色に対応するライトバルブ100R、100G及び100Bに夫々導かれる。この際特にB光は、長い光路による光損失を防ぐために、入射レンズ1122、リレーレンズ1123及び出射レンズ1124からなるリレーレンズ系1121を通して導かれる。そして、ライトバルブ100R、100G及び100Bにより夫々変調された3原色に対応する光成分は、ダイクロイックプリズム1112により再度合成された後、投写レンズ1114を通してスクリーン1120にカラー画像として投写される。

#### 【0111】

本実施例においては特に、遮光層を各画素のTFTの下側（投写光の出射側）にも設けておけば、当該液晶パネル100からの入射光に基づく液晶プロジェクタ内の投写光学系による反射光、入射光が通過する際のTFTアレイ基板の表面からの反射光、他の液晶パネルから出射した後にダイクロイックプリズム1112を突き抜けてくる入射光の一部（R光及びG光の一部）等が、戻り光としてTFTアレイ基板の側から入射しても、画素電極のスイッチング用のTFT等のチャネルに対する遮光を十分に行うことができる。この場合、小型化に適したプリズムを投写光学系に用いても、各液晶パネルのTFTアレイ基板とプリズムとの間ににおいて、戻り光防止用のARフィルムを貼り付けたり、偏光板にAR被膜処理を施したりすることが不要となるので、構成を小型且つ簡易化する上で大変有利である。

#### 【0112】

図22において、電子機器の他の実施例たるマルチメディア対応のラップトップ型のパソコンコンピュータ（PC）1200は、上述した液晶パネル100がトップカバーケース内に備えられており、更にCPU、メモリ、モデム等を収容すると共にキーボード1202が組み込まれた本体1204を備えている。

#### 【0113】

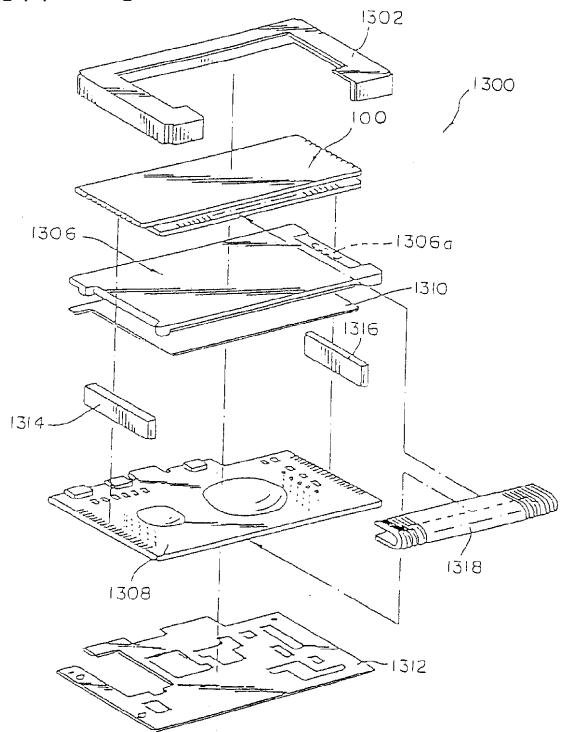

図23において、電子機器の他の実施例たるページャ1300は、金属フレーム1302内に前述の駆動回路1004がTFTアレイ基板上に搭載されて液晶モジュールをなす液晶パネル100が、バックライト1306aを含むライトガイド1306、回路基板1308、第1及び第2のシールド板1310及び1312、二つの弹性導電体1314及び1316、並びにフィルムキャリアテープ1318と共に収容されている。この例の場合、前述の表示情報処理回路1002（図20参照）は、回路基板1308に搭載してもよく、液晶パネル100のTFTアレイ基板上に搭載してもよい。更に、前述の駆動回路1004を回路基板1308上に搭載することも可能である。

#### 【0114】

尚、図23に示す例はページャであるので、回路基板1308等が設けられている。しかしながら、駆動回路1004を更に表示情報処理回路1002を搭載して液晶モジュールをなす液晶パネル100の場合には、金属フレーム1302内に液晶パネル100を固定したものを液晶装置として、或いはこれに加えてライトガイド1306を組み込んだバックライト式の液晶装置として、生産、販売、使用等することも可能である。

#### 【0115】

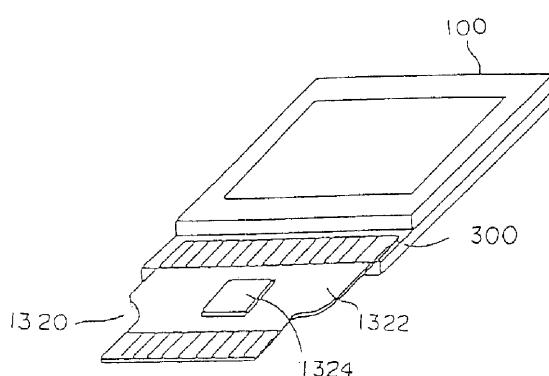

また図24に示すように、駆動回路1004や表示情報処理回路1002を搭載しない液晶パネル10

10

20

30

40

50

0の場合には、駆動回路1004や表示情報処理回路1002を含むIC1324がポリイミドテープ1322上に実装されたTCP(Tape Carrier Package)1320に、TFTアレイ基板300の周辺部に設けられた異方性導電フィルムを介して物理的且つ電気的に接続して、液晶装置として、生産、販売、使用等することも可能である。

#### 【0116】

以上図21から図24を参照して説明した電子機器の他にも、液晶テレビ、ビューファインダ型又はモニタ直視型のビデオテープレコーダ、カーナビゲーション装置、電子手帳、電卓、ワードプロセッサ、エンジニアリング・ワークステーション(EWS)、携帯電話、テレビ電話、POS端末、タッチパネルを備えた装置等などが図20に示した電子機器の例として挙げられる。

10

#### 【0117】

以上説明したように、本実施例によれば、比較的簡易な構成を用いて非画像表示領域に適宜黒表示でき、各種のアスペクト比の画俊を表示可能な液晶装置を備えた各種の電子機器を実現できる。

#### 【図面の簡単な説明】

【図1】本発明を実施するための最良の形態における第1実施例の回路ブロック図。

【図2】図1のA部分の拡大回路ブロック図。

【図3】本発明を実施するための最良の形態における第2実施例の回路ブロック図。

【図4】図3のB部分の拡大回路ブロック図。

【図5】本発明を実施するための最良の形態における第3実施例の回路ブロック図。

20

【図6】図5のC部分の拡大回路ブロック図。

【図7】本発明を実施するための最良の形態における第4実施例の回路ブロック図。

【図8】図7のD部分の拡大回路ブロック図。

【図9】第4実施例において、アスペクト比16:9(NTSCワイド規格)の画面に対し、アスペクト比4:3(NTSC規格)の画像を表示する際の各種信号の出力タイミングチャート。

【図10】第4実施例において、アスペクト比16:9の画面に対し、アスペクト比16:9の画像を表示する際の各種信号の出力タイミングチャート。

【図11】本発明を実施するための最良の形態における第5実施例の回路ブロック図。

【図12】図11のモード切換回路の回路ブロック図。

30

【図13】(A)は、第5実施例において、アスペクト比4:3の画面に対し、アスペクト比4:3(PAL規格)の画像を表示する際の各種信号の出力タイミングチャートであり、(B)は、第5実施例において、アスペクト比4:3の画面に対し、アスペクト比16:9(NTSCワイド規格)の画像を表示する際の各種信号の出力タイミングチャート。

【図14】本発明を実施するための最良の形態における第6実施例の回路ブロック図。

【図15】図14のモード切換回路の回路ブロック図。

【図16】第6実施例において、アスペクト比4:3の画面に対し、アスペクト比16:9の画像を表示する際の各種信号の出力タイミングチャート。

【図17】(A)は、スイッチング素子をTFTから構成した場合の画素部の回路図であり、(B)は、スイッチング素子をMIM素子から構成した場合の画素部の回路図。

40

【図18】各実施例に適用可能な複数系列のXシフトレジスタの概略ブロック図。

【図19】は、各実施例に適用可能な複数段おきに転送信号をサンプリング回路駆動信号として出力するXシフトレジスタの概略ブロック図。

【図20】本発明による電子機器の実施例の概略構成を示すブロック図。

【図21】電子機器の一例としての液晶プロジェクタを示す断面図。

【図22】電子機器の他の例としてのパーソナルコンピュータを示す正面図。

【図23】電子機器の一例としてのページヤを示す分解斜視図。

【図24】電子機器の一例としてのTCPを用いた液晶装置を示す斜視図。

【符号の説明】

50

- 1 a . Xシフトレジスタ

1 b . Xシフトレジスタ

1 c . Xシフトレジスタ

1 d . Xシフトレジスタ

2 . Yシフトレジスタ

3 . 画素マトリクス

4 . 画像表示領域

5 . 画像表示領域

6 . 非画像表示領域

10 . フリップフロップ

11 . 論理和回路

12 . 論理積回路

13 . S B回路

14 . サンプリング回路

15 . 論理和回路

10

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図14】

【図13】

(B) NTSC=H (NTSCワイド表示時)

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図 2 1】

【図 2 2】

【図 2 3】

【図 2 4】

---

フロントページの続き

合議体

審判長 瀧 廣往

審判官 小川 浩史

審判官 中村 直行

(56)参考文献 特開平6 - 202595 (JP, A)

特開平4 - 165329 (JP, A)

特開平3 - 131182 (JP, A)

特開昭61 - 56327 (JP, A)

特開平9 - 9180 (JP, A)

特開平9 - 212139 (JP, A)

特開平4 - 34591 (JP, A)

特開平7 - 36406 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G3/20-3/38

|                |                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶面板的驱动装置，液晶装置和电子设备                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP3987280B2</a>                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2007-10-03 |

| 申请号            | JP2000401601                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2000-12-28 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 当前申请(专利权)人(译)  | 精工爱普生公司                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| [标]发明人         | 石井賢哉                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 发明人            | 石井 賢哉                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133 H04N5/66                                                                                                                                                                                                                                                                                                                                                               |         |            |

| CPC分类号         | G09G3/3685 G09G3/20 G09G3/3648 G09G3/367 G09G3/3674 G09G3/3677 G09G3/3688 G09G2310 /0232 G09G2340/0442 G09G2340/0464 G09G2340/0471 G09G2340/0478 G09G2340/0485 G09G2360 /02                                                                                                                                                                                                                        |         |            |

| F1分类号          | G09G3/36 G09G3/20.622.E G09G3/20.660.Q G02F1/133.550 G09G3/20.623.H G09G3/20.650.G G09G3/20.660.E H04N5/66.102.B                                                                                                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA33 2H093/NC16 2H093/NC22 2H093/NC23 2H093/ND04 2H093/ND10 2H093 /ND39 2H193/ZC15 5C006/AF36 5C006/BB16 5C006/BB17 5C006/BC03 5C006/BC11 5C006/BF03 5C006/BF26 5C006/FA05 5C006/FA41 5C058/AA06 5C058/BA01 5C058/BA22 5C058/BB25 5C080 /AA10 5C080/BB05 5C080/DD21 5C080/DD22 5C080/EE19 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C080/KK02 5C080/KK43 |         |            |

| 代理人(译)         | 须泽 修                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 助理审查员(译)       | 小川博 中村直之                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 优先权            | 1996296546 1996-11-10 JP                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 其他公开文献         | <a href="#">JP2001242841A</a>                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                          |         |            |

## 摘要(译)

要解决的问题：提供一种液晶面板的驱动装置，其能够通过使用简单的配置在非图像显示区域中根据需要显示黑色，并显示各种宽高比的图像。解决方案：OR电路11和AND电路12布置在对应于区域5的触发器和对应于区域6的触发器之间。以这种方式，当区域6被制成非显示区域时，DX1固定为低电平，传输时钟输入DX2。当区域6成为显示区域时，传输时钟输入DX1，DX2固定为低。

【图1】