(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-189762

(P2006-189762A)

(43) 公開日 平成18年7月20日(2006.7.20)

| (51) Int.CI.                 | F 1                          | テーマコード (参考)         |

|------------------------------|------------------------------|---------------------|

| <b>G09G 3/36 (2006.01)</b>   | GO9G 3/36                    | 2H092               |

| <b>G02F 1/133 (2006.01)</b>  | GO2F 1/133 550               | 2H093               |

| <b>G02F 1/1345 (2006.01)</b> | GO2F 1/1345                  | 5C006               |

| <b>G02F 1/1368 (2006.01)</b> | GO2F 1/1368                  | 5C080               |

| <b>G09G 3/20 (2006.01)</b>   | GO9G 3/20 622E               |                     |

|                              | 審査請求 有 請求項の数 34 O L (全 22 頁) | 最終頁に続く              |

| (21) 出願番号                    | 特願2005-183225 (P2005-183225) | (71) 出願人 501426046  |

| (22) 出願日                     | 平成17年6月23日 (2005.6.23)       | エルジー・フィリップス エルシーテー  |

| (31) 優先権主張番号                 | 2004-113684                  | カンパニー、リミテッド         |

| (32) 優先日                     | 平成16年12月28日 (2004.12.28)     | 大韓民国 ソウル、ヨンドゥンポーク、ヨ |

| (33) 優先権主張国                  | 韓国 (KR)                      | イドードン 20            |

|                              |                              | (74) 代理人 100064447  |

|                              |                              | 弁理士 岡部 正夫           |

|                              |                              | (74) 代理人 100085176  |

|                              |                              | 弁理士 加藤 伸晃           |

|                              |                              | (74) 代理人 100106703  |

|                              |                              | 弁理士 産形 和央           |

|                              |                              | (74) 代理人 100094112  |

|                              |                              | 弁理士 岡部 謙            |

|                              |                              | (74) 代理人 100096943  |

|                              |                              | 弁理士 白井 伸一           |

|                              |                              | 最終頁に続く              |

(54) 【発明の名称】平板表示装置用シフトレジスト

## (57) 【要約】

【課題】本発明は、非晶質薄膜トランジスタの駆動の熱化現象を除去して安定された出力を提供するゲート駆動用シフトレジストに係り、より詳しくは、第1駆動電源及び第2駆動電源が各々入力を受けて交差駆動される液晶表示装置ゲート駆動用シフトレジストに関する。

【解決手段】持続されるバイアスの印加によって特性の変化が誘発されないように、ペアで駆動トランジスタを構成して、駆動と非駆動休止区間が反復されるようにすることと同時に、非駆動休止期間には、逆バイアスまたは、基底電源に当たるバイアスを印加することによって、駆動区間の間、トランジスタに印加されたバイアスストレスを相殺させて、素子の安定化による回路の正常駆動及び寿命延長効果を導出する長所がある。

【選択図】図 8

## 【特許請求の範囲】

## 【請求項 1】

以前ステージの出力信号が入力されQノードに連結されて、自己のゲート電極が自分のドレイン電極に連結されるダイオード構造の第1薄膜トランジスタと；

前記Qノードと供給電源端間に連結され、次のステージの出力信号によって開閉の可否が決定される第2薄膜トランジスタと；

第1駆動電源端と第1QBノード間に連結されて、自己のゲート電極が自己的ドレイン電極に連結されるダイオード構造の第3-1薄膜トランジスタと；

第2駆動電源端と第2QBノード間に連結されて、自己のゲート電極が自己的ドレイン電極に連結されるダイオード構造の第3-2薄膜トランジスタと；

第1クロック入力端と当ステージの信号出力端間に連結されて、前記Qノードの電圧によって開閉の可否が決定される第4薄膜トランジスタと；

前記第1QBノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第5-1薄膜トランジスタと；

前記第2QBノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第5-2薄膜トランジスタと；

前記第1QBノードと供給電源端間に連結され、前記第2駆動電源端の出力によって開閉の可否が決定される第6-1薄膜トランジスタと；

前記第2QBノードと供給電源端間に連結され、前記第1駆動電源端の出力によって開閉の可否が決定される第6-2薄膜トランジスタと；

前記Qノードと供給電源端間に連結され、前記第1QBノードの電圧によって開閉の可否が決定される第7-1薄膜トランジスタと；

前記Qノードと供給電源端間に連結され、前記第2QBノードの電圧によって開閉の可否が決定される第7-2薄膜トランジスタと；

前記当ステージの信号出力端と供給電源端間に連結され、前記第1QBノードの電圧によって開閉の可否が決定される第8-1薄膜トランジスタと；前記当ステージの信号出力端と供給電源端間に連結され、前記第2QBノードの電圧によって開閉の可否が決定される第8-2薄膜トランジスタとを含む前記当ステージを構成する平板表示装置用駆動回路のシフトレジスト。

## 【請求項 2】

前記第1駆動電源及び第2駆動電源は、同一な周期を有して、位相が相互に反対のパルスであることを特徴とする請求項1に記載の平板表示装置用駆動回路のシフトレジスト。

## 【請求項 3】

前記パルスの周期は、1フレーム駆動周期以上であることを特徴とする請求項2に記載の平板表示装置用駆動回路のシフトレジスト。

## 【請求項 4】

前記各トランジスタは、Nタイプの非晶質シリコン薄膜トランジスタであることを特徴とする請求項1に記載の平板表示装置用駆動回路のシフトレジスト。

## 【請求項 5】

前記シフトレジストの1番目のステージのための前記以前ステージの出力信号は、スタート信号であることを特徴とする請求項1に記載の平板表示装置用駆動回路のシフトレジスト。

## 【請求項 6】

前記供給電源端は、接地電圧または、ローレベル電圧を有することを特徴とする請求項1に記載の平板表示装置用駆動回路のシフトレジスト。

## 【請求項 7】

以前ステージの出力信号を入力してQノードに連結されて、自己のゲート電極が自己的ドレイン電極に連結されるダイオード構造の第1薄膜トランジスタと；

前記Qノードと供給電源端間に連結され、次のステージの出力信号によって開閉の可否が決定される第2薄膜トランジスタと；

10

20

30

40

50

第1駆動電源端と第1QBノード間に連結されて、自己のゲート電極が自己のドレイン電極に連結されるダイオード構造の第3-11薄膜トランジスタと；

前記第1駆動電源端と第1QBノード間に連結されて、第1ノードの電圧によって開閉の可否が決定される第3-12薄膜トランジスタと；

前記第1ノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第3-13薄膜トランジスタと；

前記第1ノードと供給電源端間に連結され、前記以前ステージの出力信号によって開閉の可否が決定される第3-14薄膜トランジスタと；

第2駆動電源端と第2QBノード間に連結され、自己のゲート電極が自己のドレイン電極に連結されるダイオード構造の第3-21薄膜トランジスタと；

前記第2駆動電源端と第2QBノード間に連結され、第2ノードの電圧によって開閉の可否が決定される第3-22薄膜トランジスタと；

前記第2ノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第3-23薄膜トランジスタと；

前記第2ノードと供給電源端間に連結され、前記以前ステージの出力によって開閉の可否が決定される第3-24薄膜トランジスタと；

第1クロック入力端と当ステージの信号出力端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第4薄膜トランジスタと；

前記第1QBノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第5-1薄膜トランジスタと；

前記第2QBノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第5-2薄膜トランジスタと；

前記第1QBノードと供給電源端間に連結され、前記以前ステージの出力によって開閉の可否が決定される第6-1薄膜トランジスタと；

前記第2QBノードと供給電源端間に連結され、前記以前ステージの出力によって開閉の可否が決定される第6-2薄膜トランジスタと；

前記Qノードと供給電源端間に連結され、前記第1QBノードの電圧によって開閉の可否が決定される第7-1薄膜トランジスタと；

前記Qノードと供給電源端間に連結され、前記第2QBノードの電圧によって開閉の可否が決定される第7-2薄膜トランジスタと；

前記当ステージの信号出力端と供給電源端間に連結され、前記第1QBノードの電圧によって開閉の可否が決定される第8-1薄膜トランジスタと；

前記当ステージの信号出力端と供給電源端間に連結され、前記第2QBノードの電圧によって開閉の可否が決定される第8-2薄膜トランジスタとを含む前記当ステージを構成する平板表示装置用駆動回路のシフトレジスト。

#### 【請求項8】

前記第1駆動電源及び第2駆動電源は、同一な周期を有して、位相が相互に反対のパルスであることを特徴とする請求項7に記載の平板表示装置用駆動回路のシフトレジスト。

#### 【請求項9】

前記パルスの周期は、1フレーム駆動周期以上であることを特徴とする請求項8に記載の平板表示装置用駆動回路のシフトレジスト。

#### 【請求項10】

前記各トランジスタは、Nタイプの非晶質シリコン薄膜トランジスタであることを特徴とする請求項7に記載の平板表示装置用駆動回路のシフトレジスト。

#### 【請求項11】

前記シフトレジストの1番目のステージのための前記以前ステージの出力信号は、スタート信号であることを特徴とする請求項7に記載の平板表示装置用駆動回路のシフトレジスト。

#### 【請求項12】

前記供給電源端は、接地電圧または、ローレベル電圧を有することを特徴とする請求項

10

20

30

40

50

7に記載の平板表示装置用駆動回路のシフトレジスト。

**【請求項 1 3】**

以前ステージの出力信号を入力してQノードに連結されて、自己のゲート電極が自己のドレイン電極に連結されるダイオード構造の第1薄膜トランジスタと；

前記Qノードと供給電源端間に連結され、次のステージの出力信号によって開閉の可否が決定される第2薄膜トランジスタと；

第1駆動電源端と第1QBノード間に連結され、自己のゲート電極が自己のドレイン電極に連結されるダイオード構造の第3-11薄膜トランジスタと；

前記第1駆動電源端と第1QBノード間に連結されて、第1ノードの電圧によって開閉の可否が決定される第3-12薄膜トランジスタと；

前記第1ノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第3-13薄膜トランジスタと；

前記第1ノードと供給電源端間に連結され、第2駆動電源端の出力によって開閉の可否が決定される第3-14薄膜トランジスタと；

前記第2駆動電源端と第2QBノード間に連結され、自己のゲート電極が自己のドレイン電極に連結されるダイオード構造の第3-21薄膜トランジスタと；

前記第2駆動電源端と第2QBノード間に連結され、第2ノードの電圧によって開閉の可否が決定される第3-22薄膜トランジスタと；

前記第2ノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第3-23薄膜トランジスタと；

前記第2ノードと供給電源端間に連結され、前記第2駆動電源端の出力によって開閉の可否が決定される第3-24薄膜トランジスタと；

第1クロック入力端と当ステージの信号出力端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第4薄膜トランジスタと；

前記第1QBノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第5-1薄膜トランジスタと；

前記第2QBノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第5-2薄膜トランジスタと；

前記第1QBノードと供給電源端間に連結され、前記以前ステージの出力によって開閉の可否が決定される第6-1薄膜トランジスタと；

前記第2QBノードと供給電源端間に連結され、前記以前ステージの出力によって開閉の可否が決定される第6-2薄膜トランジスタと；

前記Qノードと供給電源端間に連結され、前記第1QBノードの電圧によって開閉の可否が決定される第7-1薄膜トランジスタと；

前記Qノードと供給電源端間に連結され、前記第2QBノードの電圧によって開閉の可否が決定される第7-2薄膜トランジスタと；

前記当ステージの信号出力端と供給電源端間に連結され、前記第1QBノードの電圧によって開閉の可否が決定される第8-1薄膜トランジスタと；

前記当ステージの信号出力端と供給電源端間に連結され、前記第2QBノードの電圧によって開閉の可否が決定される第8-2薄膜トランジスタとを含む前記当ステージを構成する平板表示装置用駆動回路のシフトレジスト。

**【請求項 1 4】**

前記第1駆動電源及び第2駆動電源は、同一な周期を有して、位相が相互に反対のパルスであることを特徴とする請求項13に記載の平板表示装置用駆動回路のシフトレジスト。

**【請求項 1 5】**

前記パルスの周期は、1フレーム駆動周期以上であることを特徴とする請求項14に記載の平板表示装置用駆動回路のシフトレジスト。

**【請求項 1 6】**

前記各トランジスタは、Nタイプの非晶質シリコン薄膜トランジスタであることを特徴

10

20

30

40

50

とする請求項 13 に記載の平板表示装置用駆動回路のシフトレジスト。

【請求項 17】

前記シフトレジストの 1 番目のステージのための前記以前ステージの出力信号は、スタート信号であるとを特徴とする請求項 13 記載の平板表示装置用駆動回路のシフトレジスト。

【請求項 18】

前記供給電源端は、接地電圧または、ローレベル電圧を有することを特徴とする請求項 13 に記載の平板表示装置用駆動回路のシフトレジスト。

【請求項 19】

スタート信号によって Q ノードを充電する第 1 薄膜トランジスタと； 10

次のステージの出力信号によって Q ノードを充電する第 2 薄膜トランジスタと；

前記 Q ノードの電圧によって当ステージの出力電圧を増加させるプルアップ駆動部と；

奇数番目のフレームに、QB-o ノードの電圧によって前記当ステージの出力電圧を減少させる第 1 プルダウン駆動部と；

偶数番目のフレームに、QB-e ノードの電圧によって前記当ステージの出力電圧を減少させる第 2 プルダウン駆動部と；

前記 QB-o ノードに連結され、自己のゲート電極と自己のドレイン電極が相互に連結されて、第 1 駆動電圧が印加される第 3-1 薄膜トランジスタと；

前記 QB-e ノードに連結され、自己のゲート電極と自己のドレイン電極が相互に連結されて、第 2 駆動電圧が印加される第 3-2 薄膜トランジスタとを含む平板表示装置用駆動回路の多数のシフトレジストステージ。 20

【請求項 20】

前記スタート信号は、以前ステージの出力電圧を含むことを特徴とする請求項 19 に記載の平板表示装置用駆動回路の多数のシフトレジストステージ。

【請求項 21】

前記第 1 駆動電圧は、前記奇数番目のフレームの間は、ハイレベルの電圧を有して、前記偶数番目のフレームの間は、ローレベルの電圧を有し、前記第 2 駆動電圧は、前記奇数番目のフレームの間、ローレベルの電圧を有して、前記偶数番目のフレームの間は、ハイレベルの電圧を有することを特徴とする請求項 19 に記載の平板表示装置用駆動回路の多数のシフトレジストステージ。 30

【請求項 22】

前記平板表示装置は、平板パネルと前記駆動回路で構成されて、前記多数のシフトレジストステージは、前記平板パネルに内臓されることを特徴とする請求項 19 に記載の平板表示装置用駆動回路の多数のシフトレジストステージ。

【請求項 23】

前記プルアップ駆動部は、前記 Q ノードの電圧によって開閉が決定される第 4 薄膜トランジスタを含むことを特徴とする請求項 19 に記載の平板表示装置用駆動回路の多数のシフトレジストステージ。

【請求項 24】

前記第 3-1 薄膜トランジスタと QB-o ノード間に連結される第 5-1 薄膜トランジスタと； 40

前記第 3-2 薄膜トランジスタと QB-e ノード間に連結される第 5-2 薄膜トランジスタと；

前記第 3-1 薄膜トランジスタに連結され、前記 Q ノードの電圧によって開閉が決定される第 6-1 薄膜トランジスタと；

前記第 3-2 薄膜トランジスタに連結され、前記 Q ノードの電圧によって開閉が決定される第 6-2 薄膜トランジスタと；

前記第 3-1 薄膜トランジスタに連結され、前記スタート信号によって開閉が決定される第 7-1 薄膜トランジスタと；

前記第 3-2 薄膜トランジスタに連結され、前記スタート信号によって開閉が決定され 50

る第7-2薄膜トランジスタとをさらに含むことを特徴とする請求項23に記載の平板表示装置用駆動回路の多数のシフトレジストステージ。

【請求項25】

前記第3-1薄膜トランジスタとQB-oノード間に連結される第5-1薄膜トランジスタと；

前記第3-2薄膜トランジスタとQB-eノード間に連結される第5-2薄膜トランジスタと；

前記第3-1薄膜トランジスタに連結され、前記Qノードの電圧によって開閉が決定される第6-1薄膜トランジスタと；

前記第3-2薄膜トランジスタに連結され、前記Qノードの電圧によって開閉が決定される第6-2薄膜トランジスタと；

前記第3-1薄膜トランジスタに連結され、前記第2駆動電圧によって開閉が決定される第7-1薄膜トランジスタと；

前記第3-2薄膜トランジスタに連結され、前記第1駆動電圧によって開閉が決定される第7-2薄膜トランジスタとをさらに含むことを特徴とする請求項16に記載の平板表示装置用駆動回路の多数のシフトレジストステージ。 10

【請求項26】

スタート信号端子に連結されたゲート電極及びドレイン電極を備えた第1薄膜トランジスタと；

第1駆動電圧端子に連結されたゲート電極及びドレイン電極を備えた第2薄膜トランジスタと； 20

第2駆動電圧端子に連結されたゲート電極及びドレイン電極を備えた第3薄膜トランジスタと；

クロック端子とシフトレジストステージの出力ノード間に連結され、自己のゲート電極が自己のソース電極と相互に連結された第4薄膜トランジスタとを含む平板表示装置用駆動回路のシフトレジストステージ。 30

【請求項27】

前記シフトレジストステージにおいて、前記第2薄膜トランジスタ及び第3薄膜トランジスタだけが、自己のドレイン電極等が前記第1駆動電圧及び第2駆動電圧に各自連結される薄膜トランジスタであることを特徴とする請求項26に記載の平板表示装置用駆動回路のシフトレジストステージ。 30

【請求項28】

前記第4薄膜トランジスタのゲート電極と供給電源間に連結され、次のステージの出力に連結されるゲート電極を備えた第5薄膜トランジスタをさらに含むことを特徴とする請求項26に記載の平板表示装置用駆動回路のシフトレジストステージ。

【請求項29】

前記供給電源は、接地電圧または、ローレベルの電圧を有することを特徴とする請求項28に記載の平板表示装置用駆動回路のシフトレジストステージ。

【請求項30】

前記シフトレジストステージにおいて、前記クロック端子だけが、前記薄膜トランジスタ等にクロック信号を供給する端子であることを特徴とする請求項26に記載の平板表示装置用駆動回路のシフトレジストステージ。 40

【請求項31】

前記第1駆動電圧端子に連結されて、前記第2薄膜トランジスタのソース電極に連結されるゲート電極を備えた第6薄膜トランジスタと、前記第2駆動電圧端子に連結されて、前記第3薄膜トランジスタのソース電極に連結されるゲート電極を備えた第7薄膜トランジスタをさらに含むことを特徴とする請求項26に記載の平板表示装置用駆動回路のシフトレジストステージ。

【請求項32】

前記第2薄膜トランジスタのソース電極と供給電源間に連結される第1薄膜トランジス 50

タペアと、前記第3薄膜トランジスタのソース電極と前記供給電源間に連結される第2薄膜トランジスタペアをさらに含み、前記第1薄膜トランジスタペアの1番目の薄膜トランジスタと、前記第2薄膜トランジスタペアの1番目の薄膜トランジスタは、前記第4薄膜トランジスタのゲート電極に連結される、ゲート電極を有して、前記第1薄膜トランジスタペアの2番目の薄膜トランジスタと、前記第2薄膜トランジスタペアの2番目の薄膜トランジスタは、前記スタート信号端子に連結されるゲート電極を有することを特徴とする請求項26に記載の平板表示装置用駆動回路のシフトレジストステージ。

### 【請求項33】

前記第2薄膜トランジスタのソース電極と供給電源間に連結される第1薄膜トランジスタペアと、前記第3薄膜トランジスタのソース電極と前記供給電源間に連結される第2薄膜トランジスタペアをさらに含み、前記第1薄膜トランジスタペアの1番目の薄膜トランジスタと、前記第2薄膜トランジスタペアの1番目の薄膜トランジスタは、前記第4薄膜トランジスタのゲート電極に連結される、ゲート電極を有して、前記第1薄膜トランジスタペアの2番目の薄膜トランジスタは、前記第1駆動電圧端子に連結されるゲート電極を有して、前記第2薄膜トランジスタペアの2番目の薄膜トランジスタは、前記第2駆動電圧端子に連結されるゲート電極を有することを特徴とする請求項26に記載の平板表示装置用駆動回路のシフトレジストステージ。 10

### 【請求項34】

前記平板表示装置は、平板パネルと前記駆動回路で構成されて、前記シフトレジストステージは、前記平板パネルに内臓されることを特徴とする請求項26に記載の平板表示装置用駆動回路のシフトレジストステージ。 20

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、平板表示装置に関し、より詳しくは、非晶質薄膜トランジスタ駆動による熱化現象を除去して安定された出力を提供するシフトレジストを含む平板表示装置用駆動回路に関する。 30

#### 【背景技術】

#### 【0002】

平板表示装置のうち、最も幅広く使用されている液晶表示装置は、液晶の特定な分子配列に電圧を印加して、他の分子配列に変換させて、このような分子配列により発光する液晶セルの複屈折性、旋光性、2色性及び光散乱の特性等の光学的性質の変化を、視覚変化に変換させて、液晶セルによる光の変調を利用したディスプレー装置として、通常の液晶表示装置は、液量パネル上の液晶セル等の光透過率を調節することによって、ビデオ信号に当たる画像を表示する。液晶パネル上の液晶セル等を駆動するために、液晶表示装置は、液晶パネル駆動回路を備える。 30

#### 【0003】

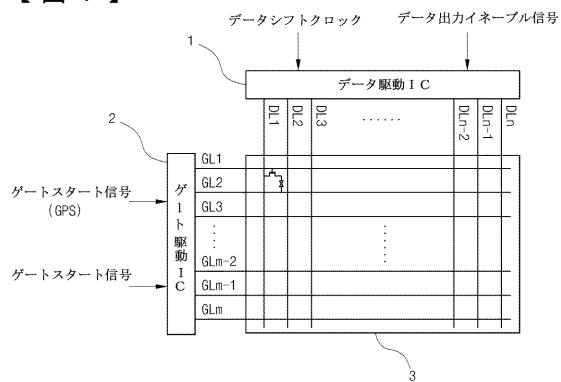

図1を参照すると、通常の能動マトリックス液晶表示装置は、液晶セル等が2枚の透明基板を間に、マトリックス状で配列されている液晶パネル3と、液晶パネル3上のデータ配線等(DL1ないしDLn)にデータを供給するためのデータ駆動IC(1)と、ゲート配線等(GL1ないしGLm)を順に駆動するためのゲート駆動IC(2)とを備える。液晶パネル3には、多数の液晶セル等と、これら液晶セル等各々に供給されるデータ信号をスイッチングする薄膜トランジスタ等(以下、TFTと称する。)が設けられている。 40

#### 【0004】

多数の液晶セル等は、データ配線等及びゲート配線等が交差する交差点に各々設けられると共に、薄膜トランジスタ等と前記交差点等に各々位置する。

#### 【0005】

データ駆動IC(1)は、シフトレジストとラッチを含み、データシフトクロックに応答してデータ信号をシフトさせて、データ出力イネーブル信号に応答して1ライン分のデータ信号をデータ配線等に同時に供給する。 50

## 【0006】

ゲート駆動 I C (2)は、各ゲート配線等を駆動するために、シフトレジストを含む多数のステージで構成され、ゲートスタート信号に応答してゲート配線等にゲート信号を順に印加する。

## 【0007】

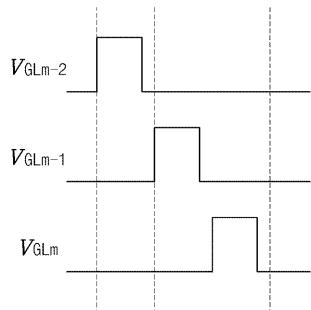

ゲートスタート信号がゲート駆動 I C (2)等に供給されると、ゲート駆動 I C (2)は、図2に示したように、液晶パネル上のm個のゲート配線等に、順にゲート信号(V G L m - 2、V G L m - 1、V G L m)を供給することによって、m個のゲート配線等が順に駆動される。すると、液晶パネル上のTFT等は、1ゲート配線分ずつ順序的に駆動され、1ゲート配線分ずつの液晶セル等にデータ信号等が順に駆動される。

10

## 【0008】

前述した構成において、ゲート駆動 I C (2)は、多数のシフトレジストによりゲート信号が順に出力されるが、非晶質シリコン(a-Si)トランジスタを利用するシフトレジストの場合、各々のトランジスタに長時間高い電圧が印加される時、熱化による特性の変化が発生する問題がある、以下、従来のシフトレジストを例えて、その問題を説明する。

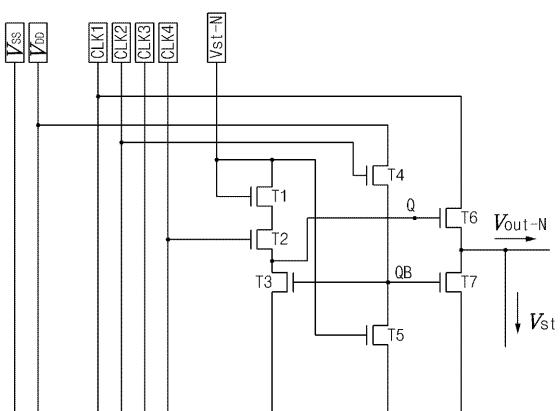

## 【0009】

図3は、従来の液晶表示装置用シフトレジストのn番目のステージを示した回路図であって、図4は、図3のシフトレジストの駆動のために印加して出力される信号等のタイミング図である。ここで例えた回路構成のトランジスタ素子は、N-タイプの非晶質シリコン(a-Si)薄膜トランジスタを利用して構成された。

20

## 【0010】

駆動を考慮すると、以前のステージ回路(N-1番目のステージ)の出力であるスタート信号(V s t - N)と、第4クロック(C L K 4)のハイレベル電圧の入力により、第1トランジスタ(T 1)及び第2トランジスタ(T 2)がオン(on)状態に転換され、Q-ノード(Q)が充電状態になる。

## 【0011】

ここで、前記スタート信号(V s t - N)と第4クロック(C L K 4)は、相互に同期された信号である。

## 【0012】

この時、前記Q-ノード(Q)は、ブートストラップ(bootstrap)され、電圧が上昇して、以後、第1クロック(C L K 1)が入力されると、第6トランジスタ(T 6)がオン(on)され、出力(V o u t - N)が発生する。この時の出力は、次のステージ回路(N+1番目のステージ)のスタート信号{V s t -(N+1)}で入力される。

30

## 【0013】

第2クロック(C L K 2)のハイレベル電圧が入力される時、第3トランジスタ(T 3)がオン(on)され、前記Q-ノード(Q)に充電されていた電荷が放電される。

## 【0014】

前述したような方式により動作されるシフトレジスト回路は、薄膜トランジスタ各々の役割によって、相互に異なるバイアスストレスを受けるが、このように、薄膜トランジスタに印加されるバイアスストレスは、閾値電圧の特性の変化を起こして、回路の動作の信頼性を低下させる。

40

## 【0015】

特に、図3に示した回路の構成では、Q B - ノード(Q B)によりプルダウン機能の素子として使用される第3トランジスタ(T 3)及び第7トランジスタ(T 7)は、1フレームの動作週期のうちで出力が発生される動作区間を除いた時間の間、持続的にバイアスストレスを受ける状態であるので、最も大きい特性の変化を起こす。従って、シフトレジスト回路の動作の信頼性の上昇のためには、Q B - ノード(Q B)の充電/放電によるオン/オフ状態によって発生する前記第3トランジスタ(T 3)及び第7トランジスタ(T 7)の特性の変化を最小化させなければならない。

## 【0016】

50

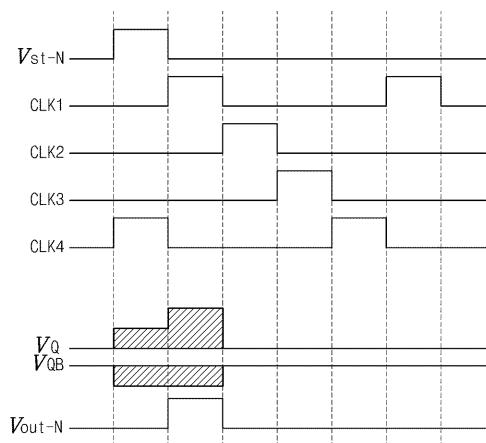

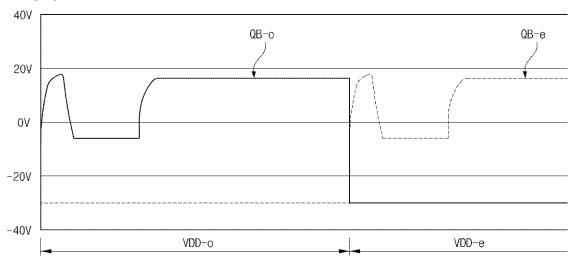

図5は、図3の单一駆動の第4トランジスタ(T4)に印加されるバイアスストレス状態をグラフに示した図面である。

#### 【0017】

図5の单一駆動による第4トランジスタ(T4)のゲート電極Gに、ハイレベルの電圧が印加される時、ドレイン電極D及びソース電極Sにも、各々ハイレベルの電圧が印加される。従って、ゲート電極Gとドレイン電極D及びソース電極S間に、電圧の差がほとんどなく、よって、第4トランジスタ(T4)は、ローバイアスストレスが印加される。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0018】

本発明は、前述したような問題を解決するために案出されており、交差駆動のためのデュアルプルダウン駆動部の構成のシフトレジストのステージで、熱化によるトランジスタの特性の変化を改善することを目的として、このために、新しく提案された非晶質シリコントランジスタを利用した液晶表示装置用シフトレジストのステージを提供して、駆動信頼性をさらに向上させる。

#### 【課題を解決するための手段】

#### 【0019】

前述したような目的を達成するために本発明は、以前ステージの出力信号が入力されQノードに連結されて、自己のゲート電極が自己的ドレイン電極に連結されるダイオード構造の第1薄膜トランジスタと；前記Qノードと供給電源端間に連結され、次のステージの出力信号によって開閉の可否が決定される第2薄膜トランジスタと；第1駆動電源端と第1QBノード間に連結されて、自己のゲート電極が自己的ドレイン電極に連結されるダイオード構造の第3-1薄膜トランジスタと；第2駆動電源端と第2QBノード間に連結されて、自己のゲート電極が自己的ドレイン電極に連結されるダイオード構造の第3-2薄膜トランジスタと；第1クロック入力端と当ステージの信号出力端間に連結されて、前記Qノードの電圧によって開閉の可否が決定される第4薄膜トランジスタと；前記第1QBノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第5-1薄膜トランジスタと；前記第2QBノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第5-2薄膜トランジスタと；前記第1QBノードと供給電源端間に連結され、前記第2駆動電源端の出力によって開閉の可否が決定される第6-1薄膜トランジスタと；前記第2QBノードと供給電源端間に連結され、前記第1駆動電源端の出力によって開閉の可否が決定される第6-2薄膜トランジスタと；前記Qノードと供給電源端間に連結され、前記第1QBノードの電圧によって開閉の可否が決定される第7-1薄膜トランジスタと；前記Qノードと供給電源端間に連結され、前記第2QBノードの電圧によって開閉の可否が決定される第7-2薄膜トランジスタと；前記当ステージの信号出力端と供給電源端間に連結され、前記第1QBノードの電圧によって開閉の可否が決定される第8-1薄膜トランジスタと；前記当ステージの信号出力端と供給電源端間に連結され、前記第2QBノードの電圧によって開閉の可否が決定される第8-2薄膜トランジスタとを含む前記当ステージを構成する平板表示装置用駆動回路のシフトレジストを提供する。

#### 【0020】

前記第1駆動電源及び第2駆動電源は、同一な周期を有して、位相が相互に反対のパルスであり、前記パルスの周期は、1フレーム駆動周期以上である。

#### 【0021】

また、前記各トランジスタは、Nタイプの非晶質シリコン薄膜トランジスタであることを特徴とする。

#### 【0022】

前記シフトレジストの1番目のステージのための前記以前ステージの出力信号は、スタート信号であって、前記供給電源端は、接地電圧または、ローレベル電圧を有する。

#### 【0023】

10

20

30

40

50

一方、本発明は、以前ステージの出力信号を入力してQノードに連結されて、自己のゲート電極が自己のドレイン電極に連結されるダイオード構造の第1薄膜トランジスタと；前記Qノードと供給電源端間に連結され、次のステージの出力信号によって開閉の可否が決定される第2薄膜トランジスタと；第1駆動電源端と第1QBノード間に連結されて、自己のゲート電極が自己のドレイン電極に連結されるダイオード構造の第3-11薄膜トランジスタと；前記第1駆動電源端と第1QBノード間に連結されて、第1ノードの電圧によって開閉の可否が決定される第3-12薄膜トランジスタと；前記第1ノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第3-13薄膜トランジスタと；前記第1ノードと供給電源端間に連結され、前記以前ステージの出力信号によって開閉の可否が決定される第3-14薄膜トランジスタと；第2駆動電源端と第2QBノード間に連結され、自己のゲート電極が自己のドレイン電極に連結されるダイオード構造の第3-21薄膜トランジスタと；前記第2駆動電源端と第2QBノード間に連結され、第2ノードの電圧によって開閉の可否が決定される第3-22薄膜トランジスタと；前記第2ノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第3-23薄膜トランジスタと；前記第2ノードと供給電源端間に連結され、前記以前ステージの出力によって開閉の可否が決定される第3-24薄膜トランジスタと；第1クロック入力端と当ステージの信号出力端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第4薄膜トランジスタと；前記第1QBノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第5-1薄膜トランジスタと；前記第2QBノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第5-2薄膜トランジスタと；前記第1QBノードと供給電源端間に連結され、前記以前ステージの出力によって開閉の可否が決定される第6-1薄膜トランジスタと；前記第2QBノードと供給電源端間に連結され、前記以前ステージの出力によって開閉の可否が決定される第6-2薄膜トランジスタと；前記Qノードと供給電源端間に連結され、前記第1QBノードの電圧によって開閉の可否が決定される第7-1薄膜トランジスタと；前記Qノードと供給電源端間に連結され、前記第2QBノードの電圧によって開閉の可否が決定される第7-2薄膜トランジスタと；前記当ステージの信号出力端と供給電源端間に連結され、前記第1QBノードの電圧によって開閉の可否が決定される第8-1薄膜トランジスタと；前記当ステージの信号出力端と供給電源端間に連結され、前記第2QBノードの電圧によって開閉の可否が決定される第8-2薄膜トランジスタとを含む前記当ステージを構成する平板表示装置用駆動回路のシフトレジストを提供する。

#### 【0024】

前記第1駆動電源及び第2駆動電源は、同一な周期を有して、位相が相互に反対のパルスであり、前記パルスの周期は、1フレーム駆動周期以上である。

#### 【0025】

また、前記各トランジスタは、Nタイプの非晶質シリコン薄膜トランジスタであることを特徴とする。

#### 【0026】

前記シフトレジストの1番目のステージのための前記以前ステージの出力信号は、スタート信号であって、前記供給電源端は、接地電圧または、ローレベル電圧を有する。

#### 【0027】

一方、本発明は、以前ステージの出力信号を入力してQノードに連結されて、自己のゲート電極が自己のドレイン電極に連結されるダイオード構造の第1薄膜トランジスタと；前記Qノードと供給電源端間に連結され、次のステージの出力信号によって開閉の可否が決定される第2薄膜トランジスタと；第1駆動電源端と第1QBノード間に連結され、自己のゲート電極が自己のドレイン電極に連結されるダイオード構造の第3-11薄膜トランジスタと；前記第1駆動電源端と第1QBノード間に連結されて、第1ノードの電圧によって開閉の可否が決定される第3-12薄膜トランジスタと；前記第1ノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第3-13薄膜トランジスタと；前記第1ノードと供給電源端間に連結され、第2駆動電源端の出力によ

10

20

30

40

50

って開閉の可否が決定される第3-14薄膜トランジスタと；前記第2駆動電源端と第2QBノード間に連結され、自己のゲート電極が自己のドレイン電極に連結されるダイオード構造の第3-21薄膜トランジスタと；前記第2駆動電源端と第2QBノード間に連結され、第2ノードの電圧によって開閉の可否が決定される第3-22薄膜トランジスタと；前記第2ノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第3-23薄膜トランジスタと；前記第2ノードと供給電源端間に連結され、前記第2駆動電源端の出力によって開閉の可否が決定される第3-24薄膜トランジスタと；第1クロック入力端と当ステージの信号出力端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第4薄膜トランジスタと；前記第1QBノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第5-1薄膜トランジスタと；前記第2QBノードと供給電源端間に連結され、前記Qノードの電圧によって開閉の可否が決定される第5-2薄膜トランジスタと；前記第1QBノードと供給電源端間に連結され、前記以前ステージの出力によって開閉の可否が決定される第6-1薄膜トランジスタと；前記第2QBノードと供給電源端間に連結され、前記以前ステージの出力によって開閉の可否が決定される第6-2薄膜トランジスタと；前記Qノードと供給電源端間に連結され、前記第1QBノードの電圧によって開閉の可否が決定される第7-1薄膜トランジスタと；前記Qノードと供給電源端間に連結され、前記第2QBノードの電圧によって開閉の可否が決定される第7-2薄膜トランジスタと；前記当ステージの信号出力端と供給電源端間に連結され、前記第1QBノードの電圧によって開閉の可否が決定される第8-1薄膜トランジスタと；前記当ステージの信号出力端と供給電源端間に連結され、前記第2QBノードの電圧によって開閉の可否が決定される第8-2薄膜トランジスタとを含む前記当ステージを構成する平板表示装置用駆動回路のシフトレジストを提供する。

10

20

## 【0028】

前記第1駆動電源及び第2駆動電源は、同一な周期を有して、位相が相互に反対のパルスであり、前記パルスの周期は、1フレーム駆動周期以上である。

## 【0029】

また、前記各トランジスタは、Nタイプの非晶質シリコン薄膜トランジスタであることを特徴とする。

## 【0030】

前記シフトレジストの1番目のステージのための前記以前ステージの出力信号は、スタート信号であって、前記供給電源端は、接地電圧または、ローレベル電圧を有する。

30

## 【0031】

一方、本発明は、スタート信号によってQノードを充電する第1薄膜トランジスタと；次のステージの出力信号によってQノードを充電する第2薄膜トランジスタと；前記Qノードの電圧によって当ステージの出力電圧を増加させるプルアップ駆動部と；奇数番目のフレームに、QB-oノードの電圧によって前記当ステージの出力電圧を減少させる第1プルダウン駆動部と；偶数番目のフレームに、QB-eノードの電圧によって前記当ステージの出力電圧を減少させる第2プルダウン駆動部と；前記QB-oノードに連結され、自己のゲート電極と自己のドレイン電極が相互に連結されて、第1駆動電圧が印加される第3-1薄膜トランジスタと；前記QB-eノードに連結され、自己のゲート電極と自己のドレイン電極が相互に連結されて、第2駆動電圧が印加される第3-2薄膜トランジスタとを含む平板表示装置用駆動回路の多数のシフトレジストステージを提供する。

40

## 【0032】

前記スタート信号は、以前ステージの出力電圧を含み、前記第1駆動電圧は、前記奇数番目のフレームの間は、ハイレベルの電圧を有して、前記偶数番目のフレームの間は、ローレベルの電圧を有し、前記第2駆動電圧は、前記奇数番目のフレームの間、ローレベルの電圧を有して、前記偶数番目のフレームの間は、ハイレベルの電圧を有する。

## 【0033】

前記平板表示装置は、平板パネルと前記駆動回路で構成されて、前記多数のシフトレジストステージは、前記平板パネルに内臓されることを特徴とする。

50

## 【0034】

前記プルアップ駆動部は、前記Qノードの電圧によって開閉が決定される第4薄膜トランジスタを含む。

## 【0035】

また、平板表示装置用駆動回路の多数のシフトレジストステージは、前記第3-1薄膜トランジスタとQB-oノード間に連結される第5-1薄膜トランジスタと；前記第3-2薄膜トランジスタとQB-eノード間に連結される第5-2薄膜トランジスタと；前記第3-1薄膜トランジスタに連結され、前記Qノードの電圧によって開閉が決定される第6-1薄膜トランジスタと；前記第3-2薄膜トランジスタに連結され、前記Qノードの電圧によって開閉が決定される第6-2薄膜トランジスタと；前記第3-1薄膜トランジスタに連結され、前記スタート信号によって開閉が決定される第7-1薄膜トランジスタと；前記第3-2薄膜トランジスタに連結され、前記スタート信号によって開閉が決定される第7-2薄膜トランジスタとをさらに含む。10

## 【0036】

なお、平板表示装置用駆動回路の多数のシフトレジストステージは、前記第3-1薄膜トランジスタとQB-oノード間に連結される第5-1薄膜トランジスタと；前記第3-2薄膜トランジスタとQB-eノード間に連結される第5-2薄膜トランジスタと；前記第3-1薄膜トランジスタに連結され、前記Qノードの電圧によって開閉が決定される第6-1薄膜トランジスタと；前記第3-2薄膜トランジスタに連結され、前記Qノードの電圧によって開閉が決定される第6-2薄膜トランジスタと；前記第3-1薄膜トランジスタに連結され、前記第2駆動電圧によって開閉が決定される第7-1薄膜トランジスタと；前記第3-2薄膜トランジスタに連結され、前記第1駆動電圧によって開閉が決定される第7-2薄膜トランジスタとをさらに含む。20

## 【0037】

一方、本発明は、スタート信号端子に連結されたゲート電極及びドレイン電極を備えた第1薄膜トランジスタと；第1駆動電圧端子に連結されたゲート電極及びドレイン電極を備えた第2薄膜トランジスタと；第2駆動電圧端子に連結されたゲート電極及びドレイン電極を備えた第3薄膜トランジスタと；クロック端子とシフトレジストステージの出力ノード間に連結され、自己のゲート電極が自己のソース電極と相互に連結された第4薄膜トランジスタとを含む平板表示装置用駆動回路のシフトレジストステージを提供する。30

## 【0038】

前記シフトレジストステージにおいて、前記第2薄膜トランジスタ及び第3薄膜トランジスタだけが、自己のドレイン電極等が前記第1駆動電圧及び第2駆動電圧に各々連結される薄膜トランジスタである。

## 【0039】

平板表示装置用駆動回路のシフトレジストステージは、前記第4薄膜トランジスタのゲート電極と供給電源間に連結され、次のステージの出力に連結されるゲート電極を備えた第5薄膜トランジスタをさらに含む。

## 【0040】

前記供給電源は、接地電圧または、ローレベルの電圧を有することを特徴とする。40

## 【0041】

また、前記シフトレジストステージにおいて、前記クロック端子だけが、前記薄膜トランジスタ等にクロック信号を供給する端子である。

## 【0042】

平板表示装置用駆動回路のシフトレジストステージは、前記第1駆動電圧端子に連結されて、前記第2薄膜トランジスタのソース電極に連結されるゲート電極を備えた第6薄膜トランジスタと、前記第2駆動電圧端子に連結されて、前記第3薄膜トランジスタのソース電極に連結されるゲート電極を備えた第7薄膜トランジスタをさらに含む。

## 【0043】

なお、平板表示装置用駆動回路のシフトレジストステージは、前記第2薄膜トランジス50

タのソース電極と供給電源間に連結される第1薄膜トランジスタペアと、前記第3薄膜トランジスタのソース電極と前記供給電源間に連結される第2薄膜トランジスタペアをさらに含み、前記第1薄膜トランジスタペアの1番目の薄膜トランジスタと、前記第2薄膜トランジスタペアの1番目の薄膜トランジスタは、前記第4薄膜トランジスタのゲート電極に連結される、ゲート電極を有して、前記第1薄膜トランジスタペアの2番目の薄膜トランジスタと、前記第2薄膜トランジスタペアの2番目の薄膜トランジスタは、前記スタート信号端子に連結されるゲート電極を有する。

#### 【0044】

また、平板表示装置用駆動回路のシフトレジストステージは、前記第2薄膜トランジスタのソース電極と供給電源間に連結される第1薄膜トランジスタペアと、前記第3薄膜トランジスタのソース電極と前記供給電源間に連結される第2薄膜トランジスタペアをさらに含み、前記第1薄膜トランジスタペアの1番目の薄膜トランジスタと、前記第2薄膜トランジスタペアの1番目の薄膜トランジスタは、前記第4薄膜トランジスタのゲート電極に連結される、ゲート電極を有して、前記第1薄膜トランジスタペアの2番目の薄膜トランジスタは、前記第1駆動電圧端子に連結されるゲート電極を有して、前記第2薄膜トランジスタペアの2番目の薄膜トランジスタは、前記第2駆動電圧端子に連結されるゲート電極を有する。

#### 【0045】

前記平板表示装置は、平板パネルと前記駆動回路で構成されて、前記シフトレジストステージは、前記平板パネルに内臓されることを特徴とする。

#### 【0046】

以下、添付された図面を参照して、本発明による平板表示装置用シフトレジスト各々の実施例を説明する。

#### 【発明の効果】

#### 【0047】

本発明による液晶表示装置用シフトレジストは、ステージの非晶質シリコン薄膜トランジスタ、特に、プルダウン駆動部トランジスタだけではなく、プルダウン駆動部トランジスタの駆動を制御するトランジスタで発生されるバイアスによる素子の特性の変化を最小化させる。

#### 【0048】

すなわち、持続されるハイバイアスの印加によって、特性の変化が誘発されないように、ペアでトランジスタを構成して、駆動と非駆動の休止区間が反復されることと同時に、非駆動の休止期間には、逆バイアスまたは、基底電源に当たるバイアスを印加することによって、駆動時、印加されたバイアスストレスを相殺させて、回路駆動を行う各非晶質シリコン薄膜トランジスタの素子安定化による回路の正常駆動及び寿命延長の効果がある。

#### 【実施例】

#### 【0049】

図6は、本発明による液晶表示装置用シフトレジストのn番目のステージを示した回路図であって、図7は、図6のシフトレジストのための信号等のタイミング図である。もちろん、シフトレジストの駆動のためのスタート信号とクロック信号は、第1従来技術に示された図4のタイミング図と同様である。

#### 【0050】

図6に示したように、シフトレジストのステージは、2つのプルダウン駆動分(T3o、T7o)(T3e、T7e)を適用して入力電源をフレーム別に交差させて駆動する方式であって、このようなステージが多数構成されたシフトレジストは、4つのクロック信号(CLK1～CLK4)と3つの直流電源(VDD-o、VDD-e、VSS)及びスタート信号(Vst-M)を利用して駆動される。

#### 【0051】

ここで、パネルの奇数番目のフレームの動作時に印加される第1駆動電源(VDD-o)とパネルの偶数番目のフレームの動作時に印加される第2駆動電源(VDD-e)は、相互

10

20

30

40

50

に位相が反対の直流電源であって、各電源のパルス持続時間は、1フレーム時間以上である。

#### 【0052】

動作を察すると、図7のタイミング図に示したように、液晶表示パネルの奇数番目のフレーム駆動の場合、前記第1駆動電源(VDD-o)でハイレベルの電圧が入力されて、前記第2駆動電源(VDD-e)には、ローレベルの電圧が入力される。よって、奇数番目のフレームの駆動で、前記(QB-o)ノードには、ハイレベルの電圧が印加されて、前記(QB-e)ノードには、ローレベルの電圧が印加される。

#### 【0053】

以後、液晶表示パネルの偶数番目のフレームの駆動では、出力信号(Vout-N)の発生以後には、前記第2駆動電源(VDD-e)に、ハイレベルの電圧が印加されて、前記第1駆動電源(VDD-o)に、ローレベルの電圧が印加され、前記(QB-e)ノードにハイレベルの電圧が印加され、前記(QB-o)ノードに、ローレベルの電圧が印加される。

#### 【0054】

以後の動作は、前述した第1従来技術と同様な方法によりフレーム別に反復されて行われるために、示されたシフトレジストのステージ回路のプルダウン駆動部を構成する各トランジスタ(T3o、T3e、T7o、T7e)に印加されるバイアスストレスは、奇数番目と偶数番目のフレームの反復によって、電圧レベルが反転して入力される第1駆動電源(VDD-o)及び第2駆動電源(VDD-e)により相殺される効果がある。

#### 【0055】

ところが、図6に示したように、シフトレジストのステージは、長時間の連続駆動を行う場合、第4トランジスタ(T4o、T4e)等の熱化による回路の誤動作が発生されて、前記第4トランジスタ(T4o、T4e)等の熱化による閾値電圧の特性の変化は、前記電源の交差駆動によるプルダウントランジスタの特性の変化を抑えるにも拘らず、前記各QB-ノード(QB-o、QB-e)に伝達される有効電圧を減少させる問題が発生する。

#### 【0056】

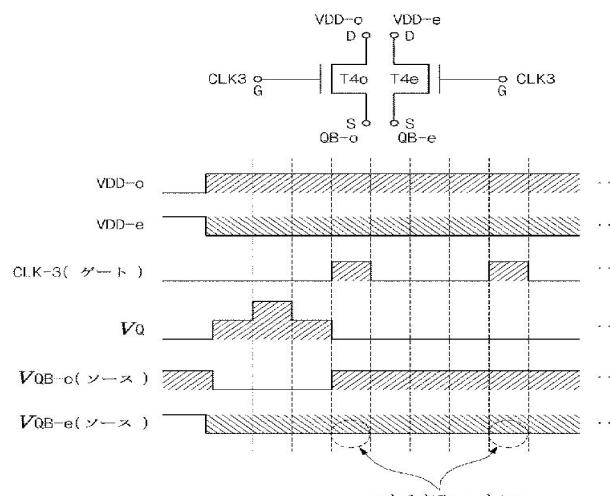

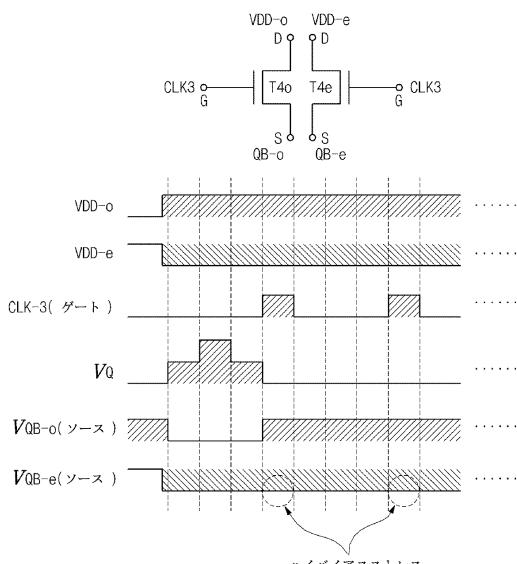

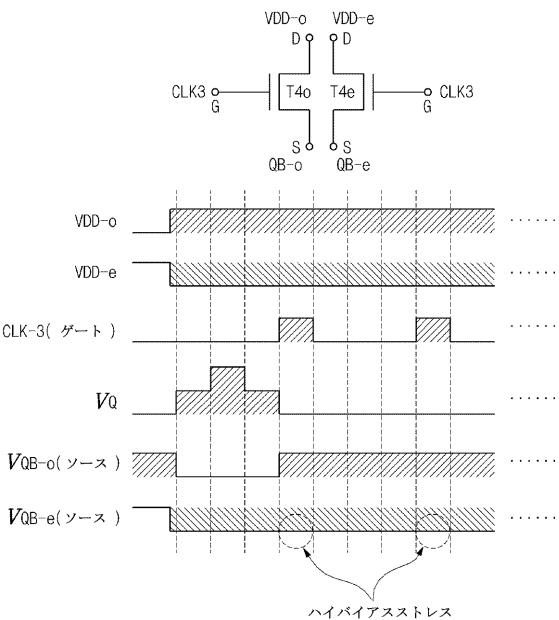

図8は、図6の交差駆動の第4トランジスタ(T4o、T4e)に印加されるバイアスストレス状態のグラフを示した図面である。

#### 【0057】

図8のような交差駆動において、第1駆動電源(VDD-o)と第2駆動電源(VDD-e)が各々ローレベルの電圧である場合、これに当たる各第4トランジスタ(T4o、T4e)のドレイン電極Dとソース電極Sに各々ローレベルの電圧が印加された状態になる。

#### 【0058】

以後、前記各第4トランジスタ(T4o、T4e)のゲート電極Gにハイレベルの電圧が印加される場合、前記各第4トランジスタ(T4o、T4e)には、ハイバイアスストレスが印加され特性の変化、すなわち、閾値電圧Vthの移動現象が現れる問題が発生する。

#### 【0059】

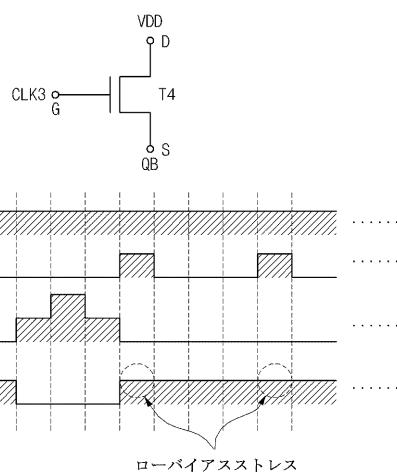

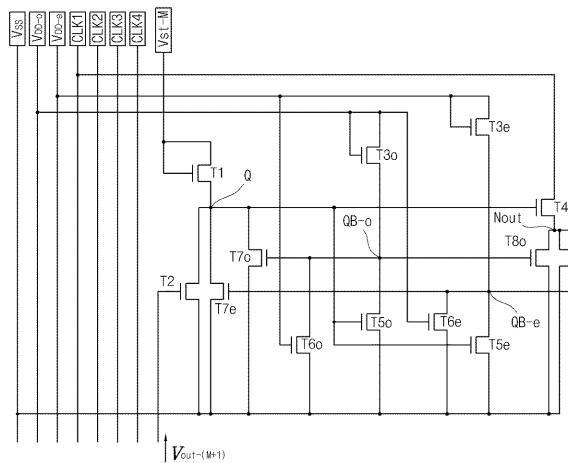

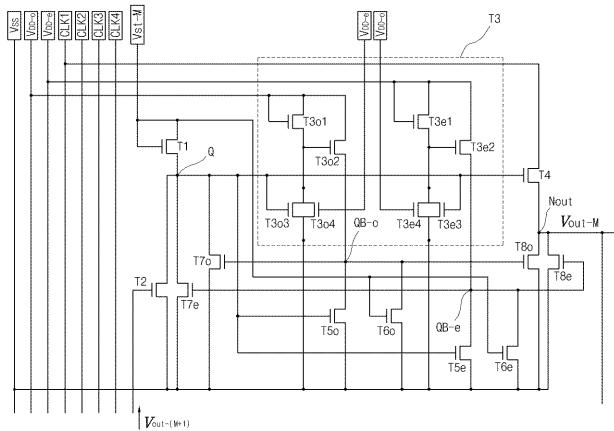

図9は、本発明の実施例1による液晶表示装置用シフトレジストのm番目のステージの図面である。

#### 【0060】

構造の特徴において、駆動回路を液晶表示パネルのフレーム別に交差駆動するための第1駆動電源(VDD-o)と第2駆動電源(VDD-e)が入力されて、ゲート信号出力端(Nout)からゲート駆動回路出力信号(Vout-M)を出力するための任意のクロック(CLK1)が入力される。回路の最初の駆動にためのスタート信号(Vst-M)は、以前ステージ(M-1番目のステージ)のゲート駆動回路出力信号(Vout-(M-1))が入力されて、ゲート駆動回路出力信号(Vout-N)の出力後Qノード(Q)の放電のための信号として、次のステージ(M+1番目のステージ)のゲート駆動回路出力信号(Vout-(M+1))が入力される構造である。前記第1駆動電源(VDD-o)と第2駆動電源(VDD-e)は、ハイレベルの電圧の印加時間がパネルの1フレーム駆動時間以上であって、同一な周期を有する反対の位相の電圧信号であり、前記クロックは、最小1フレーム駆動

10

20

30

40

50

時間の間、ハイレベルの電圧を維持する電圧信号である。

#### 【0061】

また、そのゲート電極とドレイン電極が相互に連結されるダイオード構造の第3トランジスタ群(T3o、T3e)は、奇数番目及び偶数番目の駆動フレーム順に交差入力される第1駆動電源(VDD-o)と第2駆動電源(VDD-e)の入力を受けて、ダイオード動作を行い、第1QBノード(QB-o)及び第2QBノード(QB-e)を放電させることによって、プルダウントランジスタ(T5o、T5e、T6o、T6e)に持続的なハイバイアスストレスが印加されることを防ぐための構造であって、入力される前記第1駆動電源(VDD-o)と第2駆動電源(VDD-e)は、ハイレベルの電圧及びローレベルの電圧がフレーム周期時間ごと反復して入力される。ここで、前記第1駆動電源(VDD-o)と第2駆動電源(VDD-e)のローレベルの電圧は、ハイレベルの電圧の反対の極性または、接地電圧VSSレベルを有する。

#### 【0062】

さらに、前記第3トランジスタ群(T3o、T3e)の動作により第1QBノード(QB-o)及び第2QBノード(QB-e)に印加されるハイレベルの電圧をローレベルの電圧に転換するために、第5トランジスタ群(T5o、T5e)及び第6トランジスタ群(T6o、T6e)が各々構成される。ここで、各トランジスタは、非晶質シリコン薄膜トランジスタ(a-Si TFT)であって、全てNタイプで構成される。

#### 【0063】

このような構造の特徴を有する本発明の実施例1によるステージの動作をは下記のようである。ここで、回路の動作のためのスタート信号及びクロック信号は、図4に示したように入力される。

#### 【0064】

液晶表示パネルの奇数番目のフレーム駆動の場合、第1駆動電源(VDD-o)は、ハイレベルの電圧を有して、第2駆動電源(VDD-e)は、ローレベルの電圧を有するために、以前ステージのゲート駆動回路出力信号をスタート信号として入力を受ける第1トランジスタ(T1)は、オン(on)状態になり、Qノード(Q)を充電する。この時、第3-1トランジスタ(T3o)の、そのゲート電極とドレイン電極が相互に連結されたダイオード構造によって第1QBノード(QB-o)は、ハイレベルの電圧になる。

#### 【0065】

以後、前記第1クロック(CLK1)が印加されると、Qノード(Q)は、ブーストトラップにより電圧がさらに上昇して、よって、前記第4トランジスタ(T4)をオン(on)させてゲート駆動回路出力信号(Vout-M)を出力する。この時のゲート駆動回路出力信号は、次のステージのスタート信号として入力されて、次のステージのゲート駆動回路出力信号が第2トランジスタ(T2)に入力されると、Qノード(Q)が可放電され、ゲート駆動回路出力信号の出力は中止される。

#### 【0066】

パネルの偶数番目のフレーム駆動の場合、第1駆動電源(VDD-o)は、ローレベルの電圧を有して、第2駆動電源(VDD-e)は、ハイレベルの電圧を有するために、以前フレームの駆動で前記第3-1トランジスタ(T3o)によりハイレベルの電圧が印加された第1QBノード(QB-o)は、第6-1トランジスタ(T6o)により放電されローレベルの電圧に転換されるので、第7-1トランジスタ(T7o)及び第8-1トランジスタ群(T8o)には、逆レベルバイアスにより継続的にハイバイアスストレスが印加されない。

#### 【0067】

また、前記第3-1トランジスタ(T3o)も、電圧レベルの転換による逆バイアスストレスの印加によって特性の変化が抑えられて、素子の安定化及び寿命向上の効果が発生する。

#### 【0068】

さらに、以前ステージのゲート駆動回路出力信号(Vout-(M-1))をスタート信号として入力を受けた第1トランジスタ(T1)は、オン(on)状態になってQノード(Q)を

10

20

30

40

50

充電する。

【0069】

以後、前記第1クロック(CLK1)が印加されると、Qノードは、ポートストラップにより電圧がさらに上昇して、よって、前記第4トランジスタ(T4)をオン(on)させてゲート駆動回路出力信号(Vout-M)を出力する。

【0070】

この時のゲート駆動回路出力信号(Vout-M)は、次のステージのスタート信号として入力されて、次のステージのゲート駆動回路出力信号(Vout-(M+1))が第2トランジスタ(T2)に入力されると、Qノードは、放電される。

【0071】

パネルの奇数番目のフレーム駆動の場合、第1駆動電源(VDD-o)は、ハイレベルの電圧に、第2駆動電源(VDD-e)は、ローレベルの電圧に転換されて、以前フレームの駆動で前記第3-2トランジスタ(T3e)によりハイレベルの電圧が印加された第2QBノード(QB-e)は、第6-2トランジスタ(T6e)により放電されて、ローレベルの電圧に転換されるので、第7-2トランジスタ(T7e)及び第8-2トランジスタ(T8e)は、逆レベルバイアスにより継続的にハイバイアスストレスが印加されない。

【0072】

また、前記第3-2トランジスタ(T3e)も、電圧レベルの転換による逆バイアスの印加によって特性の変化が抑えられて、素子の安定化及び寿命向上の効果が発生する。

【0073】

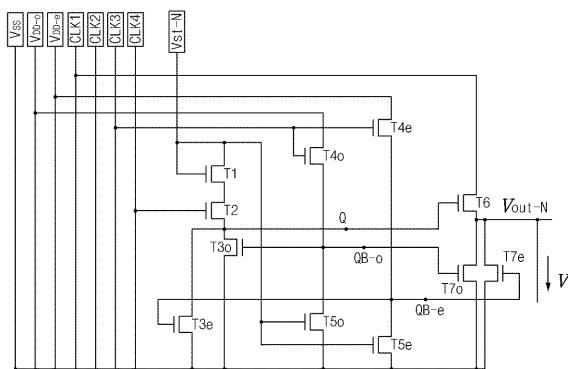

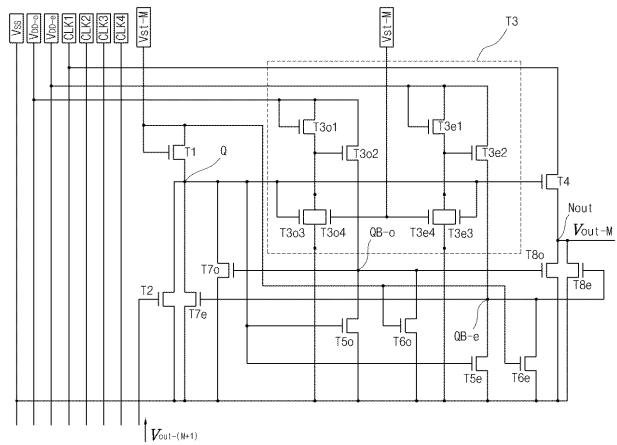

図10は、本発明の実施例2による液晶表示装置用シフトレジストのm番目のステージの図面である。

【0074】

構造の特徴において、回路を液晶表示パネルのフレーム別に交差駆動するための第1駆動電源(VDD-o)と第2駆動電源(VDD-e)が入力されて、ゲート信号出力端(Nout)からゲート駆動回路出力信号(Vout-M)を出力するための任意のクロック(CLK1)が入力される。回路の最初の駆動のためのスタート信号(Vst-M)は、以前ステージ(M-1番目のステージ)のゲート駆動回路出力信号(Vout-(M-1))が入力されて、ゲート駆動回路出力信号(Vout-N)の出力後Qノード(Q)の放電のための信号として、次のステージ(M+1番目のステージ)のゲート駆動回路出力信号(Vout-(M+1))が入力される構造である。前記第1駆動電源(VDD-o)と第2駆動電源(VDD-e)は、ハイレベルの電圧の印加時間がパネルの1フレーム駆動時間以上であって、同一な周期を有する反対の位相の信号であり、前記クロックは、最小1フレーム駆動時間の間、ハイレベルの電圧を維持する信号である。また、前記第1駆動電源(VDD-o)と第2駆動電源(VDD-e)のローレベルの電圧は、ハイレベルの電圧の反対の極性または、接地電圧VSSレベルを有する。

【0075】

さらに、液晶表示パネルの奇数番目及び偶数番目の駆動フレーム別に交差入力される第1駆動電源(VDD-o)と第2駆動電源(VDD-e)の入力を受けて、以前ステージのゲート駆動回路出力信号(Vout-(M-1))を開始信号(Vst-M)として入力を受けて動作されるインバーター構造の第3トランジスタ群(T3o1~T3o4、T3e1~T3e4)の駆動により第1QBノード(QB-o)及び第2QBノード(QB-e)に連結されたブルダウントランジスタのハイバイアスストレスを低減させる構造である。また、前記第1駆動電源(VDD-o)と第2駆動電源(VDD-e)は、ハイレベルの電圧及びローレベルの電圧の信号がフレームの駆動周期を有して交差して入力される。

【0076】

以下、液晶表示パネルの奇数番目のフレーム駆動での回路の動作を説明する。

【0077】

第1駆動電源(VDD-o)は、ハイレベルの電圧が引火されて、第2駆動電源(VDD-e)は、ローレベルの電圧が印加され、以前ステージのゲート駆動回路出力信号(Vou

10

20

30

40

50

$t - (M - 1)$ )をスタート信号( $V_{start} - M$ )として入力を受ける第1トランジスタ( $T_1$ )は、オン( $on$ )状態になり、 $Q$ ノード( $Q$ )を充電する。

#### 【0078】

この時、第5-1トランジスタ( $T_{5o}$ )と第6-1トランジスタ( $T_{6o}$ )により第1QBノード( $QB-o$ )は、放電され、ローレベルの電圧が印加された状態になると同時に、第3トランジスタ群( $T_3$ )の第3-13トランジスタ( $T_{3o3}$ )がオン( $on$ )され第3-12トランジスタ( $T_{3o2}$ )のゲート電極に印加される電圧をローレベルの電圧状態に転換させオフ( $off$ )させる。従って、第1QBノード( $QB-o$ )は、充電されてない状態になる。

#### 【0079】

以後、前記第1クロック( $CLK_1$ )が第4トランジスタ( $T_4$ )に印加されると、 $Q$ ノード( $Q$ )は、ブーストストラップにより電圧がさらに上昇して、よって、前記第4トランジスタ( $T_4$ )のゲートをオン( $on$ )させてゲート駆動回路出力信号( $V_{out} - M$ )を出力する。この時のゲート駆動回路出力信号は、次のステージのスタート信号として入力されて、次のステージのゲート駆動回路出力信号( $V_{out} - (M + 1)$ )が第2トランジスタ( $T_2$ )に入力されると、 $Q$ ノード( $Q$ )は、放電され、ゲート駆動回路出力信号( $V_{out} - M$ )の出力は中止される。

#### 【0080】

前記 $Q$ ノード( $Q$ )の放電により前記第3-13トランジスタ( $T_{3o3}$ )がオフ( $off$ )されて、そのゲート電極とドレイン電極が相互に連結されたダイオード構造の第3-11トランジスタ( $T_{3o1}$ )によって、第3-12トランジスタ( $T_{3o2}$ )がオン( $on$ )状態に転換され第1QBノード( $QB-o$ )は、さらに充電される。

#### 【0081】

一方、液晶表示パネルの偶数番目のフレーム駆動での回路の動作を説明する。

#### 【0082】

第1駆動電源( $V_{DD-o}$ )は、ローレベルの電圧を有して、第2駆動電源( $V_{DD-e}$ )は、ハイレベルの電圧が入力されて、以前ステージのゲート駆動回路出力信号( $V_{DD} - (M - 1)$ )をスタート信号( $V_{start} - M$ )として入力を受ける 第1トランジスタ( $T_1$ )は、オン( $on$ )状態になって $Q$ ノード( $Q$ )を充電する。

#### 【0083】

この時、第5-2トランジスタ( $T_{5e}$ )と第6-2トランジスタ( $T_{6e}$ )により第2QBノード( $QB-e$ )は、放電され、ローレベルの電圧が印加された状態になると同時に、第3トランジスタ群( $T_3$ )の第3-23トランジスタ( $T_{3e3}$ )がオン( $on$ )されて、第3-22トランジスタ( $T_{3e2}$ )のゲート電極にローレベルの電圧が印加されるように転換してオフ( $off$ )させる。従って、第2QBノード( $QB-e$ )は、充電されてない状態になる。

#### 【0084】

以後、前記第1クロック( $CLK_1$ )が第4トランジスタ( $T_4$ )に印加されると、 $Q$ ノード( $Q$ )は、ブーストストラップにより電圧がさらに上昇して、よって、前記第4トランジスタ( $T_4$ )のゲートをオン( $on$ )させゲート駆動回路出力信号( $V_{out} - M$ )を出力する。この時のゲート駆動回路出力信号( $V_{out} - M$ )は、次のステージのスタート信号として入力されて、次のステージのゲート駆動回路出力信号( $V_{out} - (M + 1)$ )が第2トランジスタ( $T_2$ )に入力されると、 $Q$ ノード( $Q$ )は、放電され、ゲート駆動回路出力信号( $V_{out} - M$ )の出力は中止される。

#### 【0085】

前記 $Q$ ノード( $Q$ )の放電により前記第3-23トランジスタ( $T_{3e3}$ )がオフ( $off$ )されて、そのゲート電極とドレイン電極が相互に連結されたダイオード構造の第3-21トランジスタ( $T_{3e1}$ )によって、第3-22トランジスタ( $T_{3e2}$ )がオン( $on$ )状態に転換され第2QBノード( $QB-e$ )は、さらに充電される。

#### 【0086】

10

20

30

40

50

前述したように、図9の実施例2の回路は、液晶表示装置駆動による奇数番目及び偶数番目のフレーム別に印加される第1駆動電源(VDD-o)及び第2駆動電源(VDD-e)によって第1QBノード(QB-o)及び第2QBノード(QB-o)に各々逆バイアスが印加されて、第3トランジスタ群(T3)も電圧レベルの転換による逆バイアス印加によって特性の変化が抑えられて、トランジスタ素子の安定化及び寿命向上の効果が発生する。

#### 【0087】

図11は、本発明の実施例3による液晶表示装置用シフトレジストのm番目のステージの図面である。

#### 【0088】

図示された実施例3の回路は、前述した図9の実施例2の回路と、その駆動原理が同様であって、特に、本実施例3のシフトレジストステージでは、駆動電源の電圧が変化される時、第3-24トランジスタ(T3o4)による第1QBノード(QB-o)及び第2QBノード(QB-o)のリセットのための信号として、第3-14トランジスタ(T3o4)には、第2駆動電源(VDD-e)を、第3-24トランジスタ(T3e4)には、第1駆動電源(VDD-o)を印加する特徴がある。また、実施例によって構成された各トランジスタは、非晶質シリコン薄膜トランジスタであって、さらに、前記各トランジスタは、Nタイプである。

#### 【0089】

なお、液晶表示装置駆動の奇数番目及び偶数番目の駆動フレーム別に交差入力される第1駆動電源(VDD-o)及び第2駆動電源(VDD-e)の入力を受けて駆動されるインバータ構造の第3トランジスタ群(T3)の駆動によって第1QBノード(QB-o)及び第2QBノード(QB-o)に連結されたプルダウントランジスタのハイバイアスストレスを低減させると共に、第3トランジスタ群(T3)も電圧レベルの転換による逆バイアスの印加によって特性の変化が抑えられて、トランジスタ素子の安定化及び寿命向上の効果が導出できる構造である。

#### 【0090】

以上では説明の便宜上、液晶表示装置の駆動回路を例えているが、本発明による駆動回路を有機電界発光素子ELD、電界効果表示装置FED等の平板表示装置に適用できることは言うまでもない。

#### 【図面の簡単な説明】

#### 【0091】

【図1】通常の能動マトリックス液晶表示装置の構成を示した図である。

【図2】図1による液晶表示装置の駆動のためのゲート信号を示した図である。

【図3】従来の液晶表示装置用シフトレジストのn番目のステージを示した回路図である。

【図4】図3のシフトレジストのための信号等のタイミング図である。

【図5】図3の単一構造による第4トランジスタに印加されるバイアスストレス状態を示した図である。

【図6】本発明による液晶表示装置用シフトレジストのn番目のステージを示した回路図である。

【図7】図6のシフトレジストのための信号等のタイミング図である。

【図8】図6の交差駆動による第4トランジスタ群に印加されるバイアスストレス状態を示した図である。

【図9】本発明の実施例1による液晶表示装置用シフトレジストのm番目のステージを示した図である。

【図10】本発明の実施例2による液晶表示装置用シフトレジストのm番目のステージを示した図である。

【図11】本発明の実施例3による液晶表示装置用シフトレジストのm番目のステージを示した図である。

10

20

30

40

50

## 【符号の説明】

## 【0092】

VDD-o、VDD-e : 奇数番目及び偶数番目のフレーム別印加電源

CLK1 ~ CLK4 : 第1ないし第4クロック信号

Vst-M : スタート信号

Vout : ゲート駆動回路の出力信号

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図7】

【 四 9 】

【 図 1 0 】

【 図 1 1 】

## フロントページの続き

| (51)Int.Cl.          | F I           | テーマコード(参考) |

|----------------------|---------------|------------|

| <b>G 1 1 C 19/00</b> | G 0 9 G 3/20  | 6 7 0 K    |

| <b>G 1 1 C 19/28</b> | G 1 1 C 19/00 | G          |

|                      | G 1 1 C 19/00 | J          |

|                      | G 1 1 C 19/28 | D          |

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100128657

弁理士 三山 勝巳

(72)発明者 ユン スヨン

大韓民国 4 1 2 - 2 2 2 キョンギド コヤンシ トギャング ヘンシン 2 ドン ムウォンメウル 1 0 ダンジ ソワン アパート 1 0 1 0 ドン 8 0 2 ホ

(72)発明者 チャン ヨンホ

大韓民国 4 6 3 - 0 3 0 キョンギド ソンナムシ ブンダング ブンダンドン セトビヨルメウルサムブ アパート 4 1 4 - 8 0 6

(72)発明者 キム ビン

大韓民国 1 5 8 - 0 5 5 ソウル ヤンチョンゲ モクトン モクトン 4 ダンジ アパート 4 0 8 ドン 2 0 0 3 ホ

(72)発明者 ムン スファン

大韓民国 7 3 0 - 1 2 0 キョンサンブット クミシ サンモドン ウバンシンセゲタウン 1 0 5 ドン 9 0 1 ホ

F ターム(参考) 2H092 GA59 JA24 KA05 KA07 NA24 PA06

2H093 NA16 NC09 NC22 NC34 ND47 ND48

5C006 AF75 BB16 BC03 BC06 BC20 BF03 BF34 BF42

5C080 AA06 AA10 AA18 BB05 DD29 FF11 JJ02 JJ03 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于平板显示器的移位抗蚀剂                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 公开(公告)号        | <a href="#">JP2006189762A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2006-07-20 |

| 申请号            | JP2005183225                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2005-06-23 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | Eruji. 菲利普斯杜天公司，有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| [标]发明人         | ユンスヨン<br>チャンヨンホ<br>キムビン<br>ムンスファン                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 发明人            | ユンスヨン<br>チャンヨンホ<br>キムビン<br>ムンスファン                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G02F1/1345 G02F1/1368 G09G3/20 G11C19/00 G11C19/28                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| CPC分类号         | G11C19/28 G11C19/00                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G02F1/1345 G02F1/1368 G09G3/20.622.E G09G3/20.670.K G11C19/00.G<br>G11C19/00.J G11C19/28.D G11C19/00 G11C19/28.230                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 2H092/GA59 2H092/JA24 2H092/KA05 2H092/KA07 2H092/NA24 2H092/PA06 2H093/NA16 2H093/<br>/NC09 2H093/NC22 2H093/NC34 2H093/ND47 2H093/ND48 5C006/AF75 5C006/BB16 5C006/BC03<br>5C006/BC06 5C006/BC20 5C006/BF03 5C006/BF34 5C006/BF42 5C080/AA06 5C080/AA10 5C080<br>/AA18 5C080/BB05 5C080/DD29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 2H192/AA24<br>2H192/FB03 2H192/GD61 2H193/ZA04 5B074/AA01 5B074/AA02 5B074/AA03 5B074/CA01 5B074<br>/DB01 5B074/DB02 |         |            |

| 代理人(译)         | 白井伸一<br>朝日伸光                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 优先权            | 1020040113684 2004-12-28 KR                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 其他公开文献         | <a href="#">JP4225508B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

## 摘要(译)

栅极驱动移位抗蚀剂技术领域本发明涉及通过去除非晶薄膜晶体管的驱动的热现象来提供稳定输出的栅极驱动移位抗蚀剂，更具体地，涉及第一驱动电源和第二驱动电源。本发明涉及一种用于驱动液晶显示装置的移位抗蚀剂，该液晶显示装置响应于输入而被驱动交叉。驱动晶体管被配置为一对，使得重复驱动和非驱动暂停，使得通过施加持续偏置不会引起特性的改变，并且同时是非驱动暂停。此外，通过施加反向偏压或撞击基极电源的偏压，在驱动部分期间消除施加到晶体管的偏置应力，以通过元件稳定化导出电路的正常驱动和寿命延长效应。有一个优点。

[选择图]图8