(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-171793

(P2006-171793A)

(43) 公開日 平成18年6月29日(2006.6.29)

(51) Int.CI.

G02F 1/1345 (2006.01)

G02F 1/1368 (2006.01)

F 1

G02F 1/1345

G02F 1/1368

テーマコード(参考)

2 H 0 9 2

審査請求 有 請求項の数 14 O L (全 14 頁)

(21) 出願番号 特願2006-63669 (P2006-63669)

(22) 出願日 平成18年3月9日 (2006.3.9)

(62) 分割の表示 特願平10-256211の分割

原出願日 平成10年9月10日 (1998.9.10)

(31) 優先権主張番号 1997-47248

(32) 優先日 平成9年9月12日 (1997.9.12)

(33) 優先権主張国 韓国(KR)

(71) 出願人 599127667

エルジー フィリップス エルシーティー

カンパニー リミテッド

大韓民国 ソウル, ヨンドンポーク,

ヨイドードン 20

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100096943

弁理士 白井 伸一

(74) 代理人 100101498

弁理士 越智 隆夫

(74) 代理人 100096688

弁理士 本宮 照久

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】共通駆動回路として機能する従来の第3ドライブ回路を使用せずに、共通電圧の降下及び時間遅延による影響を防止する。共通電圧信号の時間遅延により発生する歪みを計算して補償する。

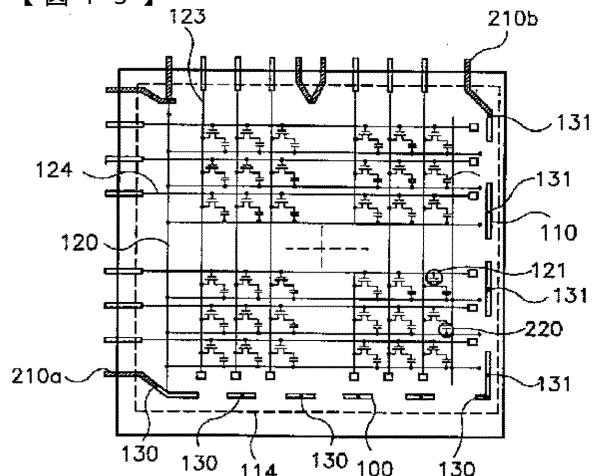

【解決手段】スキャン配線124と、データ配線123と、薄膜トランジスタ121と、画素電極150と、スキャン配線124と平行に表示領域の外側部に配置された單一共通配線100と、單一共通配線100に設けられた第1連結端子130とを含む。共通線100は、シルバードット130及び131を通して共通電極114に接続している。第2共通パッド210bは第1共通パッド210aに接続されず、入力共通電圧及び出力共通電圧を検出することはなら妨害を受けないので、第2共通パッド210bに印加される共通電圧の波形を計算することができる。表示領域の中心部で生じる共通電圧波形の歪みあるいは共通電圧の降下電圧の量を正確に計算することができる。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

マトリクス状に配列された複数の能動素子及び画素電極と、前記能動素子に接続されたデータ配線及びスキャン配線と、前記マトリクス状配列の行方向又は列方向に沿って表示領域縁の一方の側に配置された第1共通配線(100)とを含む第1基板と、

前記画素電極と対向する共通電極(114)を含む第2基板とを備える液晶表示装置において、

前記共通電極に共通電位を供給するために、前記第1共通配線は第1パッド(図5-210a又は図8-210b)に接続されそして少なくとも表示領域の左・右又は上・下の箇所で前記共通電極に接続され、

表示領域の前記第1共通配線の配置されていない側の箇所に、前記共通電極に接続しているが前記共通配線に接続されていない第2パッド(図5-210b、図8-210a)を有しており、及び

前記共通電圧が前記第1パッド又は前記第2パッドに印加されたとき、前記第1パッドと前記第2パッドとの間の電圧差に基いて、前記共通電極内で発生される電圧降下または遅延量が測定されるよう構成された液晶表示装置。

**【請求項 2】**

前記第1共通配線は、前記表示領域の底面に設置されていることを特徴とする、請求項1記載の液晶表示装置。

**【請求項 3】**

前記第1共通配線は、前記表示領域の右側に設置されていることを特徴とする、請求項1記載の液晶表示装置。

**【請求項 4】**

前記共通電極と前記第1共通配線を接続するために、前記第1共通配線に設置された少なくとも一つの連結部材を含むことを特徴とする、請求項1記載の液晶表示装置。

**【請求項 5】**

前記連結部材のうちの少なくともいずれかが、シルバードットであることを特徴とする、請求項4記載の液晶表示装置。

**【請求項 6】**

前記第1共通配線(図9-100)と分離形成されて、前記第2パッド(図9-210b)に接続された第2共通配線(図9-110)を含むことを特徴とする請求項1記載の液晶表示装置。

**【請求項 7】**

前記第1共通配線は前記画面領域の底面に沿って配置され、前記第2共通配線は前記画面領域の右側に沿って配置されたことを特徴とする、請求項6記載の液晶表示装置。

**【請求項 8】**

前記第2共通配線は、前記第2共通配線を前記共通電極に連結するための複数の連結端子を含むことを特徴とする、請求項6記載の液晶表示装置。

**【請求項 9】**

前記第1共通配線は、前記データ配線と略平行に延長されることを特徴とする、請求項6記載の液晶表示装置。

**【請求項 10】**

前記第2共通配線は、前記スキャン配線と略平行に延長されることを特徴とする、請求項6記載の液晶表示装置。

**【請求項 11】**

前記第1共通配線は、共通電極に接続された互いに分離形成された少なくとも二つのセグメントから構成されることを特徴とする、請求項6記載の液晶表示装置。

**【請求項 12】**

前記第1共通配線のセグメント上に少なくとも一つのシルバードットを含むことを特徴とする、請求項11記載の液晶表示装置。

10

20

30

40

50

**【請求項 1 3】**

前記第2共通配線は、共通電極に接続された互いに分離形成された少なくとも二つのセグメントから構成されることを特徴とする、請求項6記載の液晶表示装置。

**【請求項 1 4】**

前記第2共通配線のセグメント上に少なくとも一つのシルバードットを含むことを特徴とする、請求項13記載の液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、共通電圧の印加時に遅延時間のために生ずる共通電圧の歪みを発見することが出来る液晶表示装置の構造に関する。特に、本発明は、共通ドライブ装置を必要とせずに、そのような歪みが補正されるように共通電圧の歪みの量を検出できるように構成された共通配線を含む液晶表示装置に関する。

**【背景技術】****【0002】**

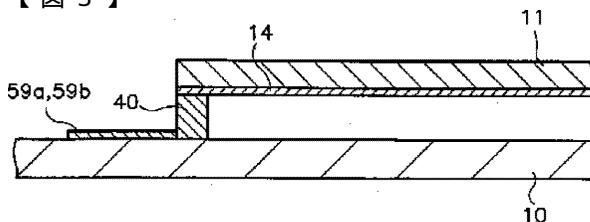

図1に示すように従来の液晶表示装置は、上板11と下板10の二つの透明基板と、前記上板11と前記下板10との間に注入される液晶15を含む。前記下板10上には複数個のスキャン配線24と複数個のデータ配線23が互いに直交するように形成されており、前記スキャン配線24と前記データ配線23の交差部には薄膜トランジスタ21と画素電極20が形成されている。前記薄膜トランジスタ21はゲート電極25、ソース電極27及びドレイン電極29から構成されている。各々の前記ゲート電極25は前記一つのスキャン配線24に連結されており、各々の前記ソース電極27は前記一つのデータ配線23に連結されており、又各々の前記ドレイン電極29は各々の画素電極20に連結されている。図1には図示しないが、前記スキャン配線24の一端はスキャン駆動ICの出力電極に連結されており、各々の前記データ配線23の一端はデータ駆動ICの出力電極に連結されている。追加に前記下板10には外部装置から印加された共通信号が流れる共通配線の一部を形成することが出来る。

**【0003】**

図1に示すように、前記上板11は共通電極14及びカラーフィルター13から構成されている。前記カラーフィルター13は、赤(Red)、緑(Green)、青(Blue)の三つのフィルターから構成されており、前記下板10の前記画素電極20に対向される位置に形成されている。前記共通電極14は前記カラーフィルター13上に形成されている。一般に前記共通電極14は、前記上板11の主表面の一つを覆う一体物で形成されている。又は、データ配線23、もしくはスキャン配線24に沿って配列された線状の複数個で形成される場合もある。

**【0004】**

又、前記上板10及び前記下板10の間に注入された前記液晶物質15の分子配列方向は、前記画素電極20と前記共通電極14の間の電圧差によって変化される。前記スキャン配線24にスキャン電圧が印加される時、前記薄膜トランジスタ21は前記ゲート電極25に印加された電圧によって導通(on)される。この際、前記データ配線23に印加されたデータ電圧は前記ドレイン電極29に連結された前記画素電極20に前記データ電圧が印加されるように前記薄膜トランジスタ21のソース電極27からドレイン電極29に送られる。従って、前記共通電極14と前記画素電極20間に電圧差が発生する。液晶物質の分子配列方向の変化によって前記液晶表示装置が表示装置として機能することになる。

**【0005】**

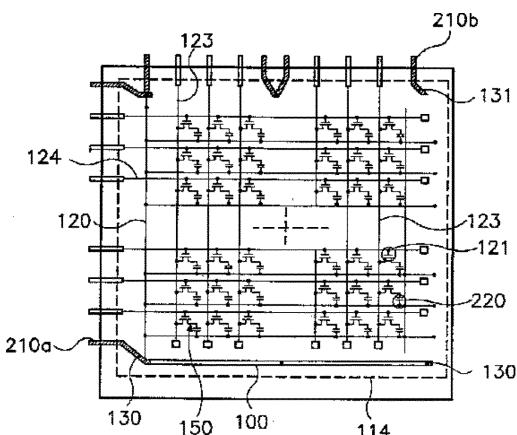

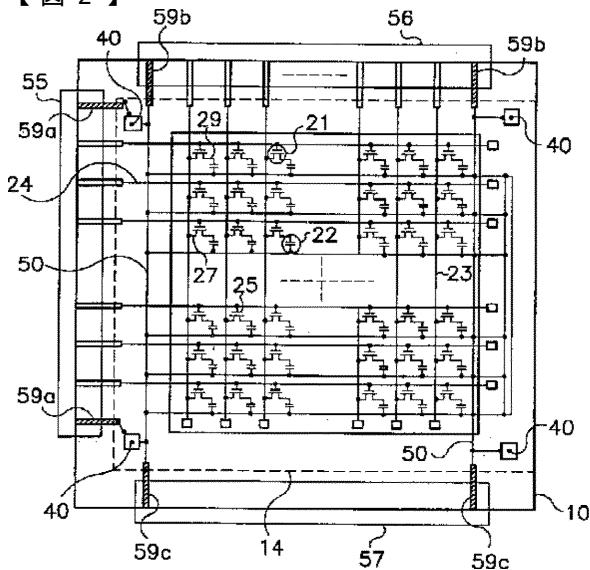

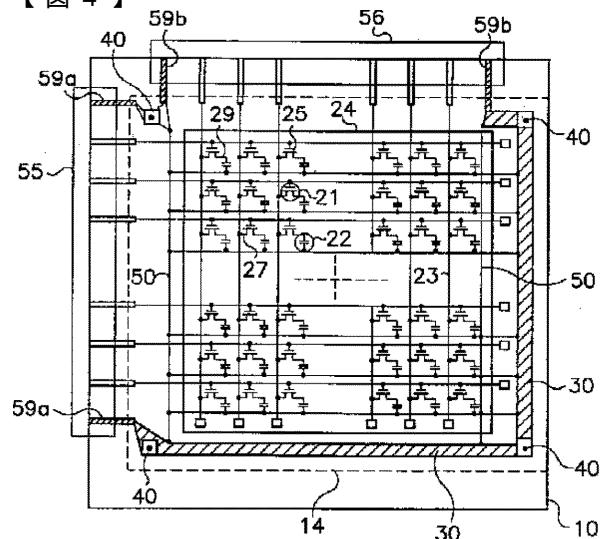

図2及び図3は、液晶表示装置においての共通電極の従来構造を示す。図2及び図3を参照し、前記スキャンドライバIC55の前記共通パッド59a、59b及び前記データドライバIC56は、前記上板11上に形成された前記共通電極14に、前記下板10のための共通電圧を印加する。前記共通電圧が前記シルバードット(Ag dot)40を通して前記共通電極14に供給されるようにシルバードット40は、前記共通電極14とスキャンドライバIC共通パッド59a及びデータドライバIC共通パッド59bが接触する前記下板10の4隅部に各々位置されている。

10

20

30

40

50

## 【0006】

前述した従来の液晶表示装置において、前記シルバードットの近くに位置した前記共通電極14の一部で発生される共通電圧の波形は、前記シルバードットの遠くに位置した前記共通電極14の一部で発生する共通電圧の波形と違う（以下、この明細書において、この違いを「共通電圧の歪み」あるいは「歪曲」と表現する）。前記波形の差は、前記共通電極14の抵抗によって前記共通電圧の信号が遅延するために発生する信号遅延による。従つて、前記共通電極14を制御するための第3ドライブIC57を設置する必要がある。

## 【0007】

第3駆動回路57を使用せずに前記問題点を解決するための、図4に示した米国特許No.5,311,342の液晶表示装置では、延長された共通線30は、LCDのマトリックス表示部の2つの近接する側面部に沿って連続的に形成されている。延長された共通電極線30は、図4のマトリックス部の下左隅に位置するスキャンパッド部から図3のマトリックス部の上右隅に位置するデータパッド部へ連続的に延びるマトリックス表示部を囲み、スキャンパッド部及びデータパッド部が互いに接続されるようしている。下パネル10に形成された共通線30と、図3の点線の正方形で示された上パネル11に形成された共通電極14は、シルバードット40を通して互いに接続されている。加えて、共通線とは分離して形成された導電性配線50は、共通電圧の時間遅れを減少させるために、共通電極14に接続されている。

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0008】

しかしながら、米国特許第5,311,342に記述された構造は、図4のマトリックス部の下左隅に位置するスキャンドライバIC共通パッド59aから図4のマトリックス部の上右隅に位置するデータドライバIC共通パッド59bへ延長された共通線により引き起こされる問題が生じる。共通線30がデータパッド部とスキャンパッド部の間に連続的に延びているために、表示領域の中心の共通電圧の遅延時間の正確な量を検出することができない。そのため、時間遅延から生じる共通電圧の降下電圧の量を計算することができない。降下電圧を計算できないので、降下電圧を補償及び補正する方法がない。これらの問題のために、図4に示される装置により表示される画像にフリッカが発生したり、図4の装置に表示される画像のコントラスト及び輝度が均一でなくなったりする。

## 【0009】

従つて、前記共通電極の縁部分と中央部分から発生する信号遅延を正確に把握することが出来る共通電圧配線の構造が必要である。

## 【0010】

本発明は、従来の共通駆動回路として機能する第3ドライブ回路を使用せずに、共通電圧の歪曲量、又は時間遅延を防止するための液晶表示装置を提供することを目的とする。

## 【0011】

又、本発明は、前記共通配線に印加された共通電圧の歪曲を補償し、共通配線と共に電極で共通電圧信号の時間遅延から発生する共通電圧の歪曲量を計算するために配列された液晶表示装置を提供することを目的とする。

## 【課題を解決するための手段】

## 【0012】

上記課題を解決するために、本発明に係る液晶表示装置は、マトリクス状に配列された複数の能動素子及び画素電極と、前記能動素子に接続されたデータ配線及びスキャン配線と、前記マトリクスの略中央部で共通電圧信号の電圧降下あるいは遅延の少なくともいずれかを測定するための单一共通配線とを含む第1基板と、前記画素電極と対向する共通電極を含む第2基板とを備える液晶表示装置において、前記共通電極に共通電位を供給するために、前記单一共通配線は少なくとも前記共通電極の端子のうちの少なくとも1つに接続されていることを特徴とする。

## 【0013】

10

20

30

40

50

また、この発明に係る液晶表示装置は、マトリクス状に配列された複数の能動素子及び画素電極と、前記能動素子に接続されたデータ配線及びスキャン配線と、前記画素電極を含む液晶表示領域の4つの側のたかだか1つに沿って延長され、前記マトリクスの略中央部で共通電圧信号の電圧降下あるいは遅延の少なくともいずれかを測定するための单一共通配線と、前記单一共通配線上に設けられた少なくとも1つの連結部材とを含む下板と、前記連結部材を通して前記单一共通配線に接続される共通電極を含む上板とを備えるものである。

#### 【0014】

また、この発明に係る液晶表示装置は、マトリクス状に配列された複数の能動素子及び画素電極と、前記能動素子に接続されたデータ配線及びスキャン配線と、前記画素電極を含む液晶表示領域を囲むように設けられた第1共通配線及び第2共通配線と、前記第1共通配線及び第2共通配線上に設けられた複数の連結部材とを含む下板と、前記複数の連結部材を通して前記第1共通配線及び前記第2共通配線に接続される共通電極を含む上板とを備え、前記マトリクスの略中央部で生じる共通電圧信号の電圧降下あるいは遅延の少なくともいずれかを測定するために、前記第1共通配線及び前記第2共通配線は互いに離隔して設けられることを特徴とする。

#### 【発明を実施するための最良の形態】

#### 【0015】

#### 実施の形態1.

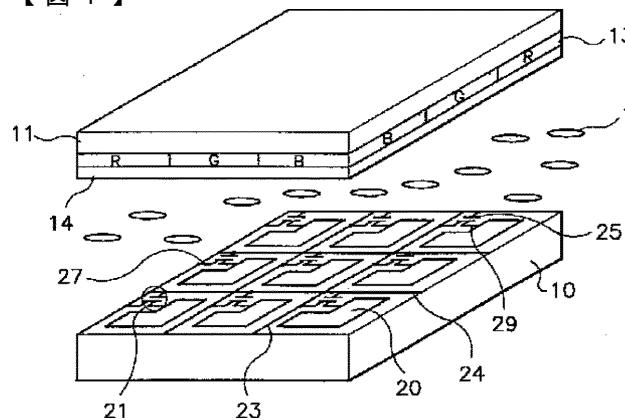

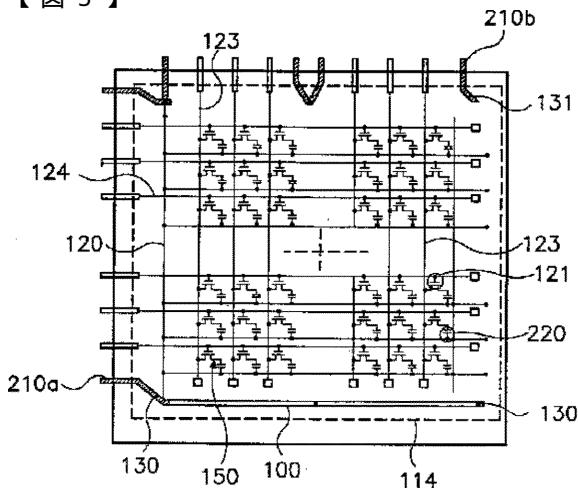

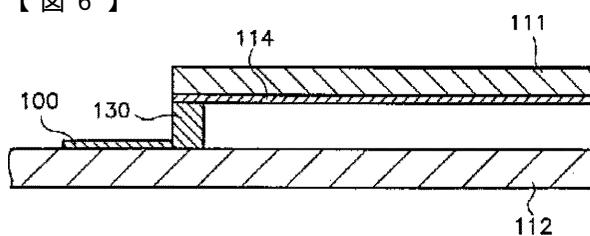

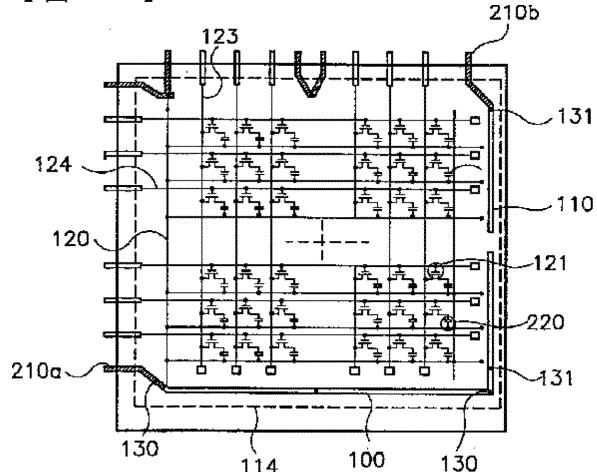

本発明の構造を図5R>5及び図6を用いて次の如く詳しく説明する。

10

20

30

本発明の実施の形態1は、複数個のスキャン配線124と複数個のデータ配線123とを含み、前記スキャン配線124と前記データ配線123との各々交差点で形成されている薄膜トランジスタ121と画素電極150を有する表示領域を含む。又本実施の形態は、前記スキャン配線124と平行に前記表示領域の外側部に配置された单一共通配線100を加えて含む。図5に示すように、前記单一共通配線100は、前記表示領域の底面に配置され、前記表示領域の下左隅部に位置した第1共通パッド210aに連結されている。追加に、前記单一共通配線100に沿った一部に、好ましくはシルバードットから構成される第1連結端子130が配置されている。第2連結パッド210bは前記表示領域の上右隅部に位置されるが、前記单一共通配線100には連結されていない。図6に示すように、下板112上に形成された共通線100は、シルバードット130及び131を通して前記上板111に形成された共通電極114に接続している。

#### 【0017】

前記单一共通配線100は、下左隅の第1連結端子130から、表示領域の下側に沿って、第1連結端子130が位置するその下右隅へ延長される。電圧信号の歪曲を減らすために前記信号共通配線100に沿って前記第1連結端子は幾つでも形成することが出来る。図5に示すように、前記信号共通配線100は前記表示領域の右側に沿って延長されない。

#### 【0018】

共通電極114は、従来の画素電極14の同様に前記上板に形成されている。前記共通電極114は、前記单一共通配線100を通して前記表示領域の下右隅部に形成された前記第1連結端子130に連結されている。又、前記共通電極114は、共通電圧を供給するために前記第1共通パッド210a及び第2共通パッド210bに連結されている。前記共通電極114は、入力する共通電圧信号の遅延時間を減らすために形成されている導電配線120に連結されている。

40

#### 【0019】

前記液晶表示装置が最終的に製品として組み立てられる前、前記第1共通パッド210aを通して前記单一共通配線100に共通電圧が印加される。そして、前記共通電圧が前記共通電極114に印加され、最終に前記第2連結端子131を通して前記第2共通パッド210bに印加される。

#### 【0020】

50

図5に示すように、前記单一共通配線100の構造及び配列に関して、前記单一共通配線100は、前記表示領域の右側に沿って延長されず、又前記表示領域の上右側に位置された前記第2共通パッド210bに延長されない。このような配列の結果、共通線が第1及び第2の間に連続的に延びて共通パッドを互いに接続した先行技術とは異なり、第2共通パッド210bは第1共通パッド210aに接続されず、これにより、入力共通電圧及び出力共通電圧を検出することはなんら妨害を受けないので、第2共通パッド210bに印加される共通電圧の波形は、計算することができる。従って、図5に示すような本発明の実施の形態での入力共通電圧を検出する第1共通パッド及び出力共通電圧を検出する第2共通パッドを使うことにより、表示領域の中心部で生じる共通電圧波形の歪みあるいは共通電圧の降下電圧の量を正確に計算することができる。このため、検出され計算された正確な共通電圧の歪みの量に対する補償のための装置は、導電性配線120に接続できるとともに、共通電圧歪みに対する補償する電圧の補正量を供給するために適用することができる。

10

20

30

40

50

## 【0021】

従って、図5に示す前記单一共通配線100は、図4に示す従来装置の問題点を解決し、さらに従来に第3駆動回路として機能した第3ドライブ回路の要求をなくし、前記单一共通配線100により前記第1共通パッド210aに印加された共通電圧及び第2共通パッド210bに印加された出力共通電圧を検出することができ、印加される及び計算される出力共通電圧の間の相違を許容し、共通電極114に接続される導電性線120を介して共通電極に補償電圧を供給することにより、共通電圧の歪みを除去できる。このようなに歪曲電圧を正確に又容易に無くすことが出来るため、図5に示すような配列及び構造を有し、单一共通配線が形成された液晶表示装置はフリッカを減らし、均一な表示コントラスト及び明るさを得ることが出来る。

## 【0022】

図5に示すように本実施の形態は、共通構造上に保持容量を有する。本実施の形態は、ゲート構造上に保持容量の配列を有することも出来る。図7は、ゲート構造上の保持上に单一共通配線100を有する液晶表示装置を示す。

## 【0023】

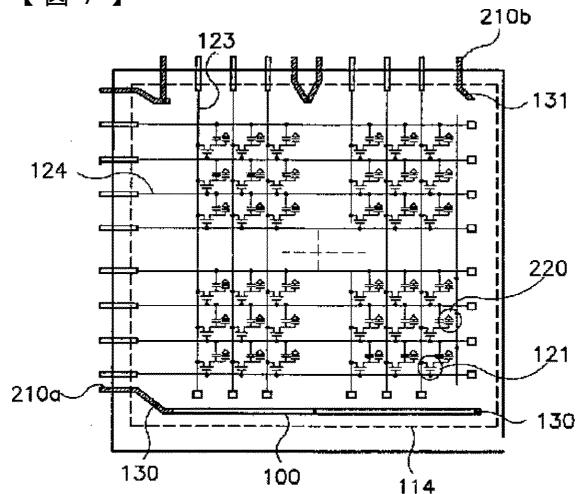

実施の形態2～8

又、本発明の他の実施の形態について、図8～図15を参照して以下に説明する。図8～図15に示す各々の実施の形態は、図5に示したような効果と同一な効果が得られる。又これらの実施の形態は、液晶表示装置の共通構造上の保持、又はゲート構造上の保持に適用することも出来る。本実施の形態には、共通構造上の保持について説明したが、ゲート構造上の保持に適用することもできる。

## 【0024】

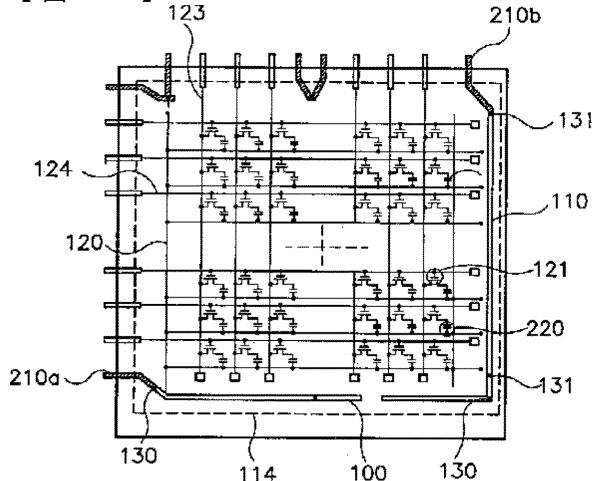

実施の形態2

図8は実施の形態2を示す。実施の形態2は、单一共通配線だけを含む。然し、図6～図15に示す実施の形態の目的のために図4に示す前記单一共通配線100は、第1共通配線100として説明し、図8に示す单一共通配線110は第2共通配線110として以後に説明する。

## 【0025】

図5に示す前記実施の形態1の第1共通配線100と図8に示す前記実施の形態2の第2共通配線110との差異点は、前記第2共通配線110が前記表示領域の右側に位置され、又前記第2共通パッド210bに連結されていることである。前記第2共通パッド210bは、それに沿って配置された複数の連結端子131を含む。

## 【0026】

図8に示すように前記第2共通配線110は、前記表示領域の右側に沿って第2共通パッド210bから延長されるが、前記表示領域の底面からは延長されない。前記第1共通パッド210aは、单一第1連結端子130を含み、図5の実施の形態1に示すように前記表示領域の底面に沿っては延長されていない。

## 【0027】

図8の実施の形態2では、表示領域の中央部での共通電圧の歪み量が計算できて前述のように補償できるように、第1共通パッド210aは入力共通電圧を検出するために使うことができ、第2共通パッド210bは出力共通電圧を検出するように使うことができる。

#### 【0028】

单一共通線のみを含むこれら実施の形態により、より正確で信頼できる電圧降下の計算ができるので、図5-図7及び図8に示された実施の形態で示された单一共通線は、図9-図15に示される実施の形態と比較される点を指摘しておく。

#### 【0029】

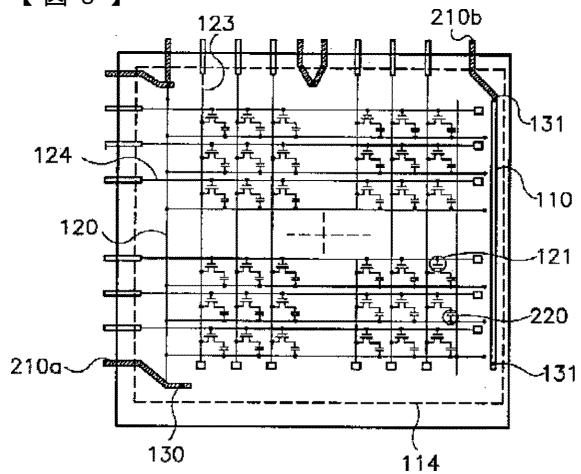

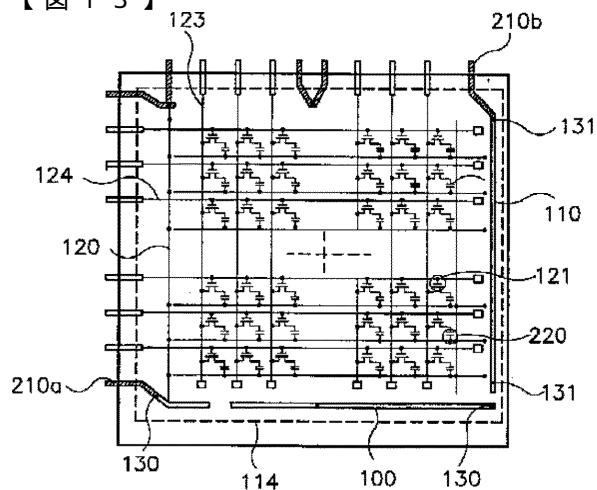

##### 実施の形態3.

図9は、他の実施の形態を示す。図9に示すように、前記第1共通配線100は、前記表示領域の底面に位置されている。又、本実施の形態は、前記データ配線123と平行に表示領域の外側部に配置された第2共通配線110を含む。前記第2共通配線110は、図9に示すように前記表示領域の右部に沿って形成されている。

#### 【0030】

図9に示すように前記第1共通配線100及び前記第2共通配線110は、各々分離して形成され、連続に形成されてない。前記第1共通配線100と前記第2共通配線110間の分離は、図9に示すように、前記二つの共通配線100、110間の空間の形態で前記表示領域の下右隅部にある。前記空間は、第1共通線100及び第2共通線110が連続して形成され、あるいは接続されることがないように形成されなければならず、これにより表示領域のほぼ中央部で生じる電圧降下の計測ができる。前記第1共通配線100及び前記第2共通配線110の配列及び構造の結果、前記表示領域の下左隅部に位置された前記第1共通パッド210aで印加された入力電圧を測定することが出来、又前記表示領域の上右隅部に位置された前記第2共通パッド210bで印加された出力電圧の結果を測定することが出来る。前記測定された二つの電圧間の差により、前記表示領域のほぼ中央部に発生する電圧降下を正確に測定することができる。前述のように、電圧降下は補償することが出来る。

#### 【0031】

図9及び図5-図15に示すように共通電極114は、従来の共通電極14と同様に上板に配置されている。前記共通電極114は前記第1共通配線100を通して前記第1連結端子130に連結され、又前記第2共通配線110を通して前記第2連結端子131に連結されている。本実施の形態は、前記共通電極114に連結された導電配線120を加えて構成することが出来、又前記実施の形態1に記述した効果を得ることが可能である。

#### 【0032】

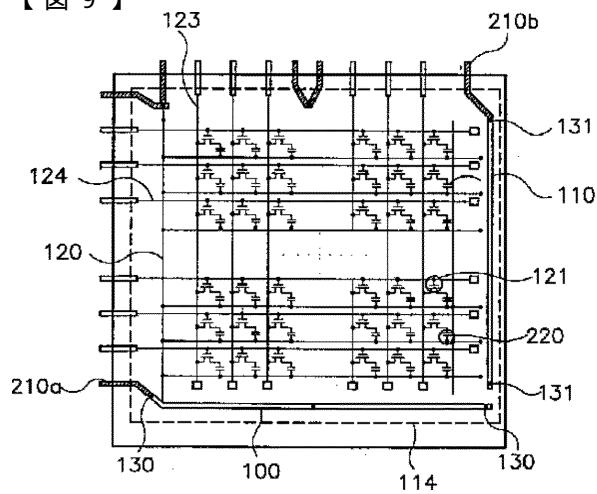

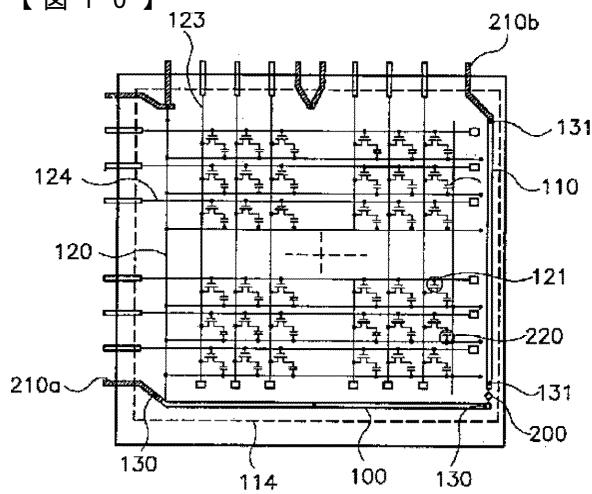

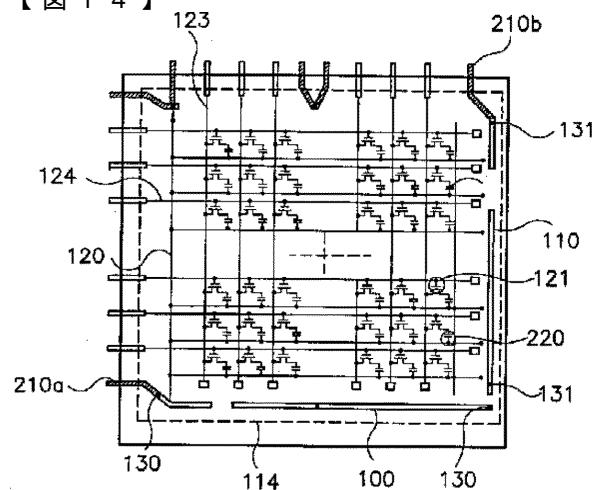

##### 実施の形態4.

図10は、図9の実施の形態から派生された他の実施の形態を示す。図10に示すように本実施の形態4は、前記第1共通配線100及び前記第2共通配線110に連結された静電気防止回路200を加えて構成される。前記静電気防止回路200は、前記配線100、110間で高い電圧差が発生する時だけに前記第1共通配線100及び前記第2共通配線110に電気的に連結される。前記配線100、110間で電圧差が低い時、若しくは静電気が無い場合には、前記第1共通配線100及び前記第2共通配線110に電気的に分離されている。

#### 【0033】

##### 実施の形態5.

図11の実施の形態5は、図9に示す実施の形態より様々な前記第1共通配線100及び前記第2共通配線110の配列及び構造示す。本実施の形態は、前記第2共通配線110が占める領域は減られ、又前記第1共通配線100が占める領域は前記表示領域の右側に沿って延長し、又底面に沿って延長して増加された。然し、前記第1、第2共通配線100、110は、表示領域の中央部で発生する共通電圧の歪曲の正確な量を計算するために、前記第2共通パッド210bで測定するための出力電圧及び前記第1共通パッド210aで測定するための入力電圧のための空間のため、連結されていなく、分離されている。

#### 【0034】

10

20

30

40

50

実施の形態 6 .

又、図12に示すように実施の形態6には前記第2共通配線110の領域は延長されることが出来、又前記第1共通配線100の領域を減らすことが出来る。従って本実施の形態には、前記第1共通配線100は表示領域の底面だけに沿って延長されており、前記第2共通配線110は表示領域の右部に沿って延長されると共に表示領域の底面にも沿って延長されている。然し、前記第1，第2共通配線100、110は、表示領域の中央部で発生する共通電圧の歪曲の正確な量を計算するために、前記第2共通パッド210bで測定するための出力電圧及び前記第1共通パッド210aで測定するための入力電圧のための空間のため、連結されていなく、分離されている。

## 【0035】

従って、図11及び図12に示すように前記第1共通配線100及び前記第2共通配線110の形状は、前述したように電圧降下を正確に計算し、補償するために前記第1共通配線を所望のとおり長くすることが出来る。

## 【0036】

実施の形態 7 .

又、本発明の実施の形態7は、図13に示すように少なくとも二つの領域で分離され、又独立したセグメントから構成される前記第1共通配線100を含む。あるいは、図14に示すように少なくとも二つの領域で分離され、又独立したセグメントから構成される前記第2共通配線110を含むことも出来る。図示しないが、前記第1共通配線100及び前記第2共通配線110を少なくとも二つの領域で分離し、独立したセグメントで構成することも出来る。

## 【0037】

実施の形態 8 .

又、あるいは、図15に示すように実施の形態8は、複数個で分離され、又独立のセグメントから前記第1共通配線100及び前記第2共通配線110を構成することも出来る。図15には図示しないが、前記第1共通配線100及び前記第2共通配線110中の一つは複数個で分離され、又独立のセグメントから構成することが出来、前記第1共通配線100及び前記第2共通配線110中の他の一つは単一の独立的セグメントで構成することが出来る。

## 【0038】

前述の如く本発明の液晶表示装置は、單一共通配線、又は独立的に分離された第1、第2共通配線を有し、前記第1共通配線は共通電圧を印加するための第1パッドを含み、前記共通電圧を検査するための第2パッドを含む第2共通配線を提供する。前記單一共通配線、又は独立的に分離形成された第1、第2共通配線の配列及び構造の結果、入力及び出力共通電圧は正確に検出され、これらの間の差が正確に計算され、表示領域のほぼ中心部に存在する電圧歪みを補正するための補償電圧を供給することができる。従って、本発明による実施の形態は、従来の装置で使用された第3駆動回路の要求を無くし、共通電極に連結された導電配線を通して前記共通電極に補償電圧を印加して計算することにより、前記共通電圧の歪曲を解決することが出来る。その結果、本発明による実施の形態は、フリッカを無くし、コントラスト及び明るさのような、表示品質の均一性を獲得することが可能である。

## 【図面の簡単な説明】

## 【0039】

【図1】従来の一般的な液晶表示装置の構造を示す斜視図。

【図2】従来の液晶表示装置の共通電極とドライバIC共通電極及びシルバードット(Ag dot)を示す平面図。

【図3】従来の液晶表示装置の共通電極とドライバIC共通電極及びシルバードット(Ag dot)を示す断面図。

## 【図4】従来の液晶表示装置の構造を示す平面図。

【図5】本発明の液晶表示装置において、單一共通配線だけを含み、共通構造上の保持容量を有する実施の形態1を示す平面図。

10

20

30

40

50

【図6】図5の本発明の実施の形態1の断面図。

【図7】本発明の液晶表示装置において、单一共通配線だけを含み、ゲート構造上の保持容量を有する実施の形態1を示す平面図。

【図8】本発明の液晶表示装置において、单一共通配線を含む実施の形態2を示す平面図。

【図9】本発明の液晶表示装置において、各々分離された第1共通電圧配線と第2共通電圧配線を含む実施の形態3を示す平面図。

【図10】本発明の液晶表示装置において、各々分離された第1共通電圧配線と第2共通電圧配線及びそれらに連結された静電気防止回路を含む実施の形態4を示す平面図。

【図11】本発明の液晶表示装置において、各々分離された第1共通電圧配線と第2共通電圧配線を含む実施の形態5を示す平面図。

【図12】本発明の液晶表示装置において、各々分離された第1共通電圧配線と第2共通電圧配線を含む実施の形態6を示す平面図。

【図13】本発明の液晶表示装置において、分離された二領域から構成される第1共通電圧配線を含む実施の形態7を示す平面図。

【図14】本発明の液晶表示装置において、分離された二領域から構成される第2共通電圧配線を含む実施の形態8を示す平面図。

【図15】本発明の液晶表示装置において、複数の違うセグメントから構成される第1共通電圧配線と第2共通電圧配線を含む実施の形態8を示す平面図。

【符号の説明】

【0040】

10 下板

11 上板

12 偏光板

13 カラーフィルター

14 共通電極

15 液晶

20 画素電極

21 薄膜トランジスタ

23 データ配線

24 スキャン配線

30 共通電圧配線

40 シルバードット(Ag dot)

50、120 導電性配線

100 第1共通電圧配線

110 第2共通電圧配線

130 第1共通電圧配線のシルバードット

131 第2共通電圧配線のシルバードット

134 出力パットのシルバードット

200 静電気防止回路

210 出力パット

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(74)代理人 100104352

弁理士 朝日 伸光

(72)発明者 宋 寅徳

大韓民国 京機道安養市 東安区 虎渓洞 533番地 エルジー電子株式会社 第1研究団地 L

C D研究所内

F ターム(参考) 2H092 GA37 GA38 HA14 JA24 JB77 MA56 NA25 PA06

|                |                                                                                                                                                |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2006171793A</a>                                                                                                                  | 公开(公告)日 | 2006-06-29 |

| 申请号            | JP2006063669                                                                                                                                   | 申请日     | 2006-03-09 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | Eruji飞利浦杜迪股份有限公司                                                                                                                               |         |            |

| [标]发明人         | 宋寅德                                                                                                                                            |         |            |

| 发明人            | 宋寅德                                                                                                                                            |         |            |

| IPC分类号         | G02F1/1345 G02F1/1368 G02F1/13 G02F1/136 G02F1/1362 G09F9/30 G09G3/36                                                                          |         |            |

| CPC分类号         | G09G3/3655 G02F1/1345 G02F1/1362 G09G3/3648 G09G2320/0223                                                                                      |         |            |

| FI分类号          | G02F1/1345 G02F1/1368                                                                                                                          |         |            |

| F-TERM分类号      | 2H092/GA37 2H092/GA38 2H092/HA14 2H092/JA24 2H092/JB77 2H092/MA56 2H092/NA25 2H092/PA06 2H192/AA24 2H192/DA12 2H192/EA43 2H192/FA22 2H192/FA24 |         |            |

| 代理人(译)         | 白井伸一<br>朝日伸光                                                                                                                                   |         |            |

| 优先权            | 1019970047248 1997-09-12 KR                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                      |         |            |

### 摘要(译)

要解决的问题：为了防止公共电压的下降和时间延迟的影响而不使用在现有技术中用作公共驱动电路的第三驱动电路，并且计算和补偿由公共电压的时间延迟引起的失真信号。ZSOLUTION：该液晶显示器包括扫描线124，数据线123，薄膜晶体管121，像素电极150，设置在与扫描线124平行的显示区域外部的单个公共线100，以及设置在其上的第一连接端子130。公共线100通过银点130,131连接到公共电极114。可以计算施加在第二公共焊盘210上的公共电压的波形，因为第二公共焊盘210b未连接因此，对于第一公共焊盘210a，输入公共电压和输出公共电压的检测没有障碍。因此，可以精确地计算公共电压波形的失真或者在显示区域的中心部分中出现的公共电压的下降电压的量。Z