(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-48051

(P2006-48051A)

(43) 公開日 平成18年2月16日(2006.2.16)

| (51) Int.CI.                 | F 1         | テーマコード (参考) |

|------------------------------|-------------|-------------|

| <b>G02F 1/133 (2006.01)</b>  | G02F 1/133  | 550 2H092   |

| <b>G02F 1/1368 (2006.01)</b> | G02F 1/1368 | 550 2H093   |

| <b>G09F 9/30 (2006.01)</b>   | G09F 9/30   | 338 5C006   |

| <b>G09G 3/20 (2006.01)</b>   | G09G 3/20   | 624B 5C080  |

| <b>G09G 3/36 (2006.01)</b>   | G09G 3/36   | 5C094       |

審査請求 未請求 請求項の数 16 O L (全 13 頁)

(21) 出願番号 特願2005-225847 (P2005-225847)

(22) 出願日 平成17年8月3日 (2005.8.3)

(31) 優先権主張番号 10-2004-0061066

(32) 優先日 平成16年8月3日 (2004.8.3)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区梅灘洞416

416, Maetan-dong, Yeongtong-gu, Suwon-si

Gyeonggi-do, Republic

of Korea

(74) 代理人 100072349

弁理士 八田 幹雄

(74) 代理人 100110995

弁理士 奈良 泰男

(74) 代理人 100114649

弁理士 宇谷 勝幸

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】開口率を減少することなくゲート線と画素の間の結合を改善することができる液晶表示装置を提供する。

【解決手段】本発明による液晶表示装置は、スイッチング素子Qを備え、画素行と画素列で配列されている複数の画素  $P_{i,u,j-1}, P_{i,u,j}$ 、スイッチング素子Qに連結されており、スイッチング素子Qを導通させるゲートオン電圧を伝達する複数対の第1及び第2ゲート線  $G_{1,up} - G_{n,down}$  と、スイッチング素子Qに連結されている複数のデータ線  $D_0 - D_m$  と、を含み、各対の第1及び第2ゲート線  $G_{1,up} - G_{n,down}$  は、隣接した二つの画素行の間に配置されていて一つの画素行のスイッチング素子Qに連結されている。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

スイッチング素子を備え、画素行と画素列で配列されている複数の画素と、前記スイッチング素子に連結されており、前記スイッチング素子を導通させるゲートオン電圧を伝達する複数対の第1及び第2ゲート線と、前記スイッチング素子に連結されている複数のデータ線と、を含み、前記各対の第1及び第2ゲート線は、隣接した二つの画素行の間に配置されていて、当該隣接した二つの画素行の一の画素行のスイッチング素子に連結されている液晶表示装置。

10

**【請求項 2】**

前記第1ゲート線は、前記第2ゲート線よりも前記一の画素行に近く位置して、前記第2ゲート線よりも先に前記ゲートオン電圧を印加される、請求項1に記載の液晶表示装置。

**【請求項 3】**

前記データ線は、互いに隣接した二つの画素列のスイッチング素子に連結されている、請求項1に記載の液晶表示装置。

**【請求項 4】**

前記隣接した二つの画素列は、前記データ線を中心に互いに反対側に位置する、請求項3に記載の液晶表示装置。

20

**【請求項 5】**

一つの画素列にある隣接した二つの画素は、前記第1及び第2ゲート線に各々連結されている、請求項3に記載の液晶表示装置。

**【請求項 6】**

前記隣接した二つの画素列は、前記データ線を中心に同じ方向に位置する、請求項3に記載の液晶表示装置。

**【請求項 7】**

一つの画素列にある隣接した二つの画素は、互いに異なる前記データ線に各々連結されている、請求項6に記載の液晶表示装置。

30

**【請求項 8】**

前記データ線は、二つの画素列毎に一つずつ配置されている、請求項3に記載の液晶表示装置。

**【請求項 9】**

前記第2ゲート線は、前記第1ゲート線よりも前記一の画素行から遠くに位置し、前記第2ゲート線と連結する前記一の画素行のスイッチング素子は、前記第1ゲート線と前記第2ゲート線との間に伸びた分枝線を介して前記データ線と連結される、請求項1に記載の液晶表示装置。

**【請求項 10】**

前記第1ゲート線と連結されている第1ゲート駆動部と、前記第2ゲート線と連結されている第2ゲート駆動部と、をさらに含む、請求項1に記載の液晶表示装置。

40

**【請求項 11】**

隣接した前記ゲート線がゲートオン電圧を印加される時間は互いに一部重複する、請求項1に記載の液晶表示装置。

**【請求項 12】**

前記液晶表示装置は、列反転または行反転を実行する、請求項1に記載の液晶表示装置。

**【請求項 13】**

画素行と画素列で配列されている複数の画素と、前記各画素と連結されている複数のスイッチング素子と、二つの画素列毎に一つずつ配置されている複数のデータ線と、

50

隣接した二つの画素行の間に各々位置する複数対の第1及び第2ゲート線と、

を含み、

一対の前記画素は、隣接した二つの前記データ線と隣接した二対の前記第1及び第2ゲート線とで画定される領域に位置し、一対の第1及び第2ゲート線は、前記隣接した二つの画素行の一の画素行のスイッチング素子に連結されている、表示装置。

#### 【請求項14】

前記複数対の第1及び第2ゲート線において、前記第1ゲート線は前記第2ゲート線よりも前記一の画素行に近く位置する、請求項13に記載の表示装置。

#### 【請求項15】

前記一対の画素において各画素のスイッチング素子は、同一の第1または第2ゲート線と連結されており、10

前記一対の画素において各画素のスイッチング素子は、前記隣接した二つのデータ線のうち当該スイッチング素子が連結されている画素に近い方のデータ線と連結されており、

前記一対の画素と連結されている第1または第2ゲート線は各画素行に沿って交代する、請求項13に記載の表示装置。10

#### 【請求項16】

前記一対の画素のスイッチング素子は、当該一対の画素の一側及び他側にあるデータ線のうち同一のデータ線に連結されており、

前記一対の画素に連結されているデータ線は各画素行に沿って交代し、

前記一対の画素が連結されたデータ線に近く位置する前記一対の画素の一の画素のスイッチング素子は、前記第1ゲート線と連結されており、20

前記一対の画素が連結されたデータ線から遠くに位置する前記一対の画素の他の画素のスイッチング素子は、前記第2ゲート線に連結されている、請求項13に記載の表示装置。20

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、液晶表示装置に関する。

#### 【背景技術】

#### 【0002】

アクティブマトリクス型( active matrix )液晶表示装置及びアクティブマトリクス型有機発光表示装置などのアクティブ表示装置は、マトリクス状(行列状)に配列されていて、スイッチング素子を含む複数の画素と、スイッチング素子に信号を伝達するためのゲート線及びデータ線などの複数の信号線を含む。画素のスイッチング素子は、ゲート線からのゲート信号に応答して、データ線からのデータ信号を選択的に画素に伝達する。液晶表示装置の画素はデータ信号によって入射光の透過率を調節し、有機発光表示装置の画素はデータ信号によって発光輝度を調節する。30

#### 【0003】

また、表示装置は、ゲート信号を生成してゲート線に印加するゲート駆動部と、データ信号をデータ線に印加するデータ駆動部と、を備える。40

#### 【0004】

ゲート駆動部とデータ駆動部は、複数の駆動集積回路チップで構成することが普通であるが、このようなチップの数をできれば減少させることができることが生産費用を減らすのに重要な要素である。特に、データ駆動集積回路チップは、ゲート駆動回路チップに比べて値段が高いためにより一層その数を減らす必要がある。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0005】

本発明が解決しようとする技術的課題は、開口率を減少させることなくゲート線と画素との間の結合を改善して液晶表示装置の画質を向上することである。50

**【 0 0 0 6 】**

本発明の他の技術的課題は、駆動回路チップの数を減らし、液晶表示装置の製造費用を減らすことである。

**【 課題を解決するための手段 】****【 0 0 0 7 】**

このような技術的課題を解決するための本発明の液晶表示装置は、スイッチング素子を備える複数の画素と、前記スイッチング素子に連結されていて、前記スイッチング素子を導通させるゲートオン電圧を伝達する複数対の第1及び第2ゲート線と、前記スイッチング素子に連結されていてデータ電圧を伝達する複数のデータ線と、を含み、前記各対の第1及び第2ゲート線は、隣接した二つの画素行の間に位置し、前記隣接した二つの画素行の一つの画素行のスイッチング素子に連結されている。10

**【 0 0 0 8 】**

前記第1ゲート線は、前記第2ゲート線よりも前記一の画素行に近く、前記第2ゲート線よりも先にゲートオン電圧の印加を受けることができる。前記データ線の各々は、隣接した二つの画素列のスイッチング素子に連結されていることが好ましい。

**【 0 0 0 9 】**

隣接した二つの画素列は、一つのデータ線に対して互いに反対側に連結されることが好ましく、一つの画素列において二つの隣接した画素は、それぞれ第1及び第2ゲート線に連結されることが好ましい。

**【 0 0 1 0 】**

二つの隣接した画素列は、一つのデータ線に対して同じ側に配置されることが好ましく、一つの画素列において隣接した二つの画素は、互いに異なるデータ線に連結されることが好ましい。20

**【 0 0 1 1 】**

前記第2ゲート線は、第1ゲート線よりも前記画素列から遠くに位置することが好ましく、前記第2ゲート線と連結する前記一の画素列のスイッチング素子は、第1ゲート線と第2ゲート線との間に伸びた分枝線を介して前記データ線と連結されることが好ましい。

**【 0 0 1 2 】**

前記表示装置は、前記第1ゲート線に連結された第1ゲート駆動部、及び前記第2ゲート線に連結されている第2ゲート駆動部をさらに含むことができる。30

**【 0 0 1 3 】**

二つの隣接したゲート線は、少なくとも部分的にゲートオン電圧を同時に印加されることができる。

**【 0 0 1 4 】**

前記表示装置は、列反転または行反転を実行することが好ましい。

**【 発明の効果 】****【 0 0 1 5 】**

本発明によれば、開口率を減少させることなくゲート線と画素PXの間の干渉を改善することができ、液晶表示装置の画質を向上させることができる。

**【 発明を実施するための最良の形態 】****【 0 0 1 6 】**

添付した図面を参照して、本発明の実施の形態に対して本発明の属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。

**【 0 0 1 7 】**

図面では、複数の層及び領域を明確に表現するために厚さを拡大して示した。明細書の全体にわたって類似な部分については同一符号を付けた。層、膜、領域、及び板などの部分が他の部分“上に”あるとする時、これは他の部分の“すぐ上に”ある場合だけでなく、その中間に他の部分がある場合も含む。反対に、ある部分が他の部分の“すぐ上に”あるとする時には、中間に他の部分がないことを意味する。

**【 0 0 1 8 】**

10

20

30

40

50

次に、本発明の実施の形態による液晶表示装置について添付した図面を参照して詳細に説明する。

【0019】

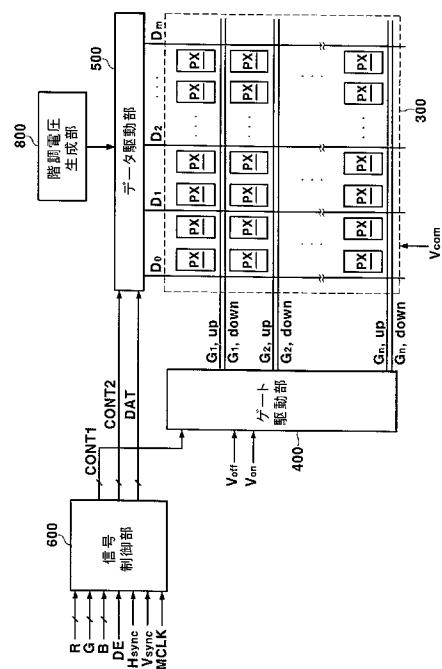

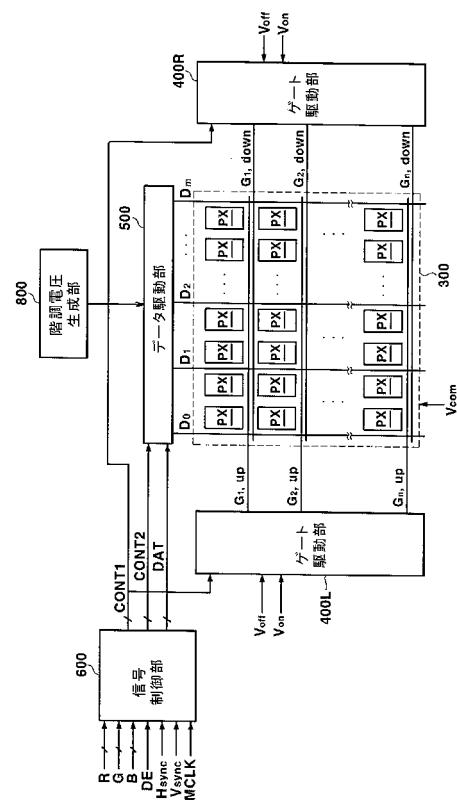

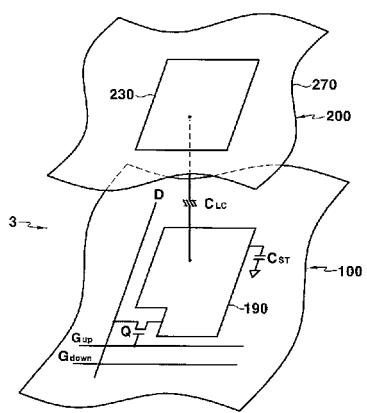

図1は、本発明の一実施の形態による液晶表示装置のブロック図であり、図2は、本発明の他の実施の形態による液晶表示装置のブロック図である。また、図3は、本発明の一実施の形態による液晶表示装置の一つの画素に対する等価回路図である。

【0020】

図1及び図2を参考にすれば、本発明の一実施の形態による液晶表示装置は、液晶表示板組立体300と、これに連結された一つまたは二つのゲート駆動部400, 400L, 400Rと、データ駆動部500と、データ駆動部500に連結された階調電圧生成部800と、これらを制御する信号制御部600と、を含む。

10

【0021】

液晶表示板組立体300は、図1及び図2に示した等価回路から見る時、複数の表示信号線 $G_1, up - G_n, down, D_0 - D_m$ と、これらに連結されていて、ほぼ行列形態に配列された複数の画素PXを含む。一方、液晶表示板組立体300を構造的に見れば、図3に示したように、互いに対向する下部及び上部表示板100, 200と、それらの間の液晶層3を含む。

【0022】

表示信号線 $G_1, up - G_n, down, D_0 - D_m$ は、ゲート信号（“走査信号”とも言う）を伝達する複数のゲート線 $G_1, up - G_n, down$ とデータ信号を伝達するデータ線 $D_0 - D_m$ を含む。ゲート線 $G_1, up - G_n, down$ ( $G_1 - G_{2n}$ )は、行方向へ伸びて互いに平行であり、データ線 $D_0 - D_m$ は、列方向へ伸びて互いに平行である。

20

【0023】

図3を参考にすれば、各画素PXは、表示信号線 $G_1, up - G_n, down, D_0 - D_m$ に連結されたスイッチング素子Qと、これらに連結された液晶キャパシタ $C_{LC}$ 及びストレージキャパシタ $C_{ST}$ と、を含む。なお、ストレージキャパシタ $C_{ST}$ は、必要に応じて省略することができる。

【0024】

薄膜トランジスタなどのスイッチング素子Qは、下部表示板100に備えられていて、三端子素子としてその制御端子または入力端子は、各々ゲート線 $G_1, up - G_n, down$ またはデータ線 $D_0 - D_m$ に連結されており、出力端子は、液晶キャパシタ $C_{LC}$ 及びストレージキャパシタ $C_{ST}$ に連結されている。

30

【0025】

液晶キャパシタ $C_{LC}$ は、下部表示板100の画素電極190と上部表示板200の共通電極270を二つの端子にして、二つの電極190, 270の間の液晶層3は、誘電体として機能する。画素電極190は、スイッチング素子Qに連結され、共通電極270は、上部表示板200の前面に形成されていて、共通電圧 $V_{com}$ を印加される。図3とは違って、共通電極270が下部表示板100に備わる場合もあり、この時には、二つの電極190, 270のうちの少なくとも一つが線状または棒形に作られる。

40

【0026】

ストレージキャパシタ $C_{ST}$ は、下部表示板100に備えた別個の信号線（図示せず）と画素電極190が重なって作られ、この別個の信号線には共通電圧 $V_{com}$ などの決められた電圧が印加される。しかし、ストレージキャパシタ $C_{ST}$ は、画素電極190が絶縁体を媒介としてすぐ上のゲート線と重なって作られることがある。

【0027】

一方、色表示を実現するためには、各画素が三原色のうちの各色を固有の幾何学的位置に表示し（空間分割）、または、各画素が時間によって交互に三原色を表示するように（時間分割）して、これら三原色の空間的、時間的組み合わせによって所望の色相が認識されるようとする。図3は、空間分割の一例として、各画素が画素電極190に対応する領

50

域に三原色のうちの一つを表示する色フィルター 230 を備えることを示している。図 3 とは違って色フィルター 230 は、下部表示板 100 の画素電極 190 上または下に形成することもできる。色フィルター 230 の色相は、赤色、緑色、及び青色などの三原色のうちの一つであることができ、本明細書では画素が現す色相によって各画素を赤色、緑色、及び青色画素という。

#### 【0028】

液晶表示板組立体 300 の二つの表示板 100, 200 のうちの少なくとも一つ表示板の外側面には、光を偏光させる偏光子（図示せず）が取付けられている。また、偏光子と表示板 100, 200 の間には、液晶の屈折率異方性を補償する少なくとも一つの補償板（図示せず）が介在されることができる。10

#### 【0029】

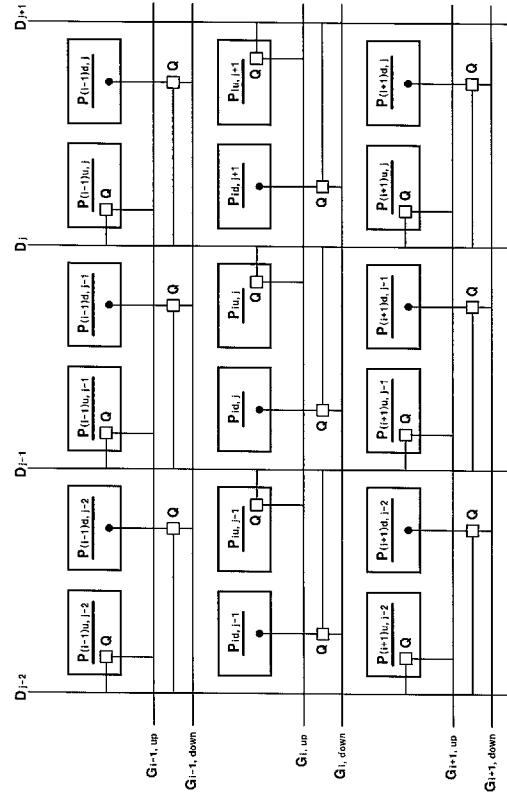

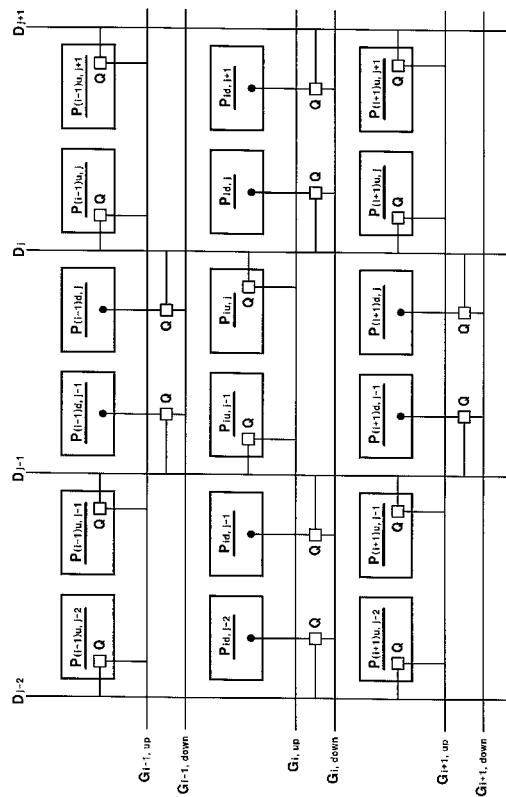

以下、本発明の一つの実施の形態によるゲート線、データ線、及び画素の配置に対して、図 4 及び図 5 を参照して詳細に説明する。

#### 【0030】

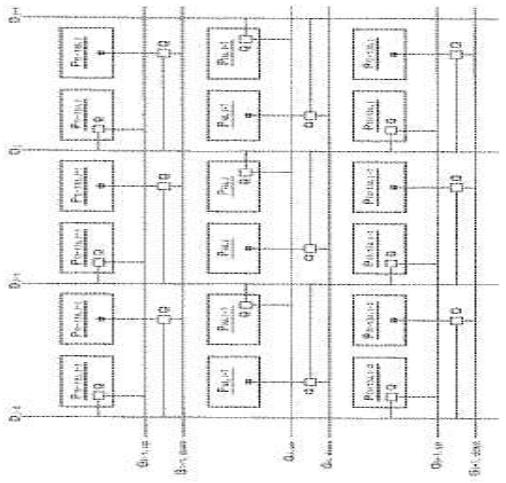

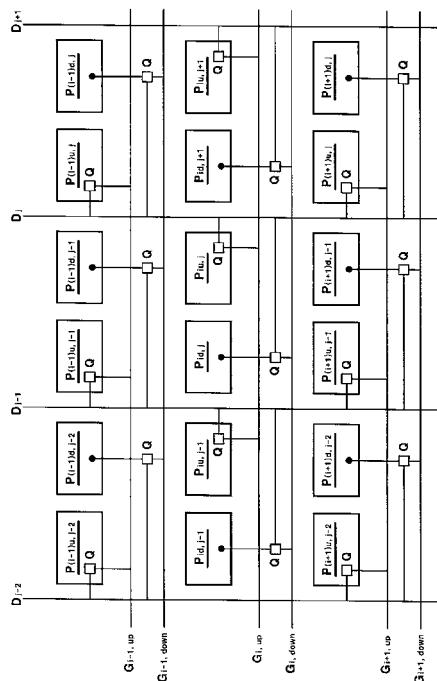

図 4 及び図 5 は、本発明の実施の形態による液晶表示装置の画素及び信号線の空間的な配列を示した図面である。

#### 【0031】

図 4 及び図 5 に図示したように、隣接した二つの行の画素 PX の間に一对の上部及び下部ゲート線（第 1 及び第 2 ゲート線）が配置されていて、二つの列の画素 PX 当り一つずつデータ線が配置されている。したがって、各画素行において、隣接した一对の隣接データ線の間には、一对の左側及び右側の画素電極が配置されている。20

#### 【0032】

前述したように、各画素 PX は、スイッチング素子 Q を通じて一つのゲート線及び一つのデータ線に連結されている。図 4 及び図 5 で、各画素 PX は  $P_{g, d}$  に表記したが、ここで g は当該画素に連結されたゲート線を示し、d は当該画素に連結されたデータ線を示す。例えば、図 4 で左下の角部の画素 PX は  $P_{(i+1), u, j-2}$  に示し、これはその画素 PX がゲート線 ( $G_{i+1, up}$ ) とデータ線 ( $D_{j-2}$ ) に連結されていることを意味する。図 4 の場合には、二つのデータ線の間に位置した一对の画素 PX が互いに異なるゲート線に連結されており、同一なデータ線に連結されている。

#### 【0033】

データ線に対する画素の連結は、画素行に沿って交互に配列される。例えば、一つの画素行において、一对の画素（以下、画素対と称する）の二つの画素全ては、その画素対のすぐ左側に位置したデータ線と連結されており、その画素行のすぐ下とすぐ上の画素行にある画素対は、全て右側に位置したデータ線に連結されている。30

#### 【0034】

ゲート線に対する画素の連結は次の通りである。同一のデータ線に連結される各画素対において、データ線に近い画素は、すぐ下に位置した一对のゲート線のうちの上側ゲート線に連結されており、データ線から遠い画素は、すぐ下に位置した一对のゲート線のうちの下側ゲート線に連結されている。

#### 【0035】

例えば、i 番目画素行において、隣接した二つのデータ線  $D_{j-1}, D_j$  の間に位置した一对の画素  $P_{i, u, j}, P_{i, d, j}$  は、全て右側データ線  $D_j$  に連結されており、データ線  $D_j$  に近い右側画素  $P_{i, u, j}$  は、下に位置した一对のゲート線  $G_{i, up}, G_{i, down}$  のうちの上側ゲート線  $G_{i, up}$  に連結されており、データ線  $D_j$  から遠い左側画素  $P_{i, d, j}$  は、下側のゲート線  $G_{i, down}$  に連結されている。しかし、i 番目画素行に隣接した (i-1) 番目及び (i+1) 番目画素行の場合、隣接した二つのデータ線の間に位置した一对の画素 PX のうちのデータ線に近い左側画素 PX は、下に位置した一对のゲート線のうちの上側ゲート線に連結されており、データ線から遠い左側画素 PX は、下側のゲート線に連結されている所は i 番目画素行と同一であるが、二つの画素 PX 共に左側データ線  $D_{j-1}$  に連結されている所は異なる。図 4 に示したように、連結され40

たデータ線に近い画素  $P_X$  は上部ゲート線に連結されており、連結されたデータ線から遠い画素  $P_X$  は下部ゲート線に連結されている。

#### 【0036】

これとは違って、図 5 の場合には、隣接した二つのデータ線の間に位置した一対の画素  $P_X$  が同一なゲート線に連結されており、互いに異なるデータ線に連結されている。画素対の画素は近いデータ線に連結されている。つまり、画素対において、左側画素はその画素対のすぐ左側に位置したデータ線と連結されており、右側画素はその画素対のすぐ右側に位置したデータ線と連結されている。ゲート線に対する連結は次のような方式で交互に行われる。すぐ下に位置した一対のゲート線のうちの上側ゲート線と連結される、一つの画素対に対し、その画素対のすぐ下、上、左側、及び右側に位置した各画素対は下側ゲート線と連結される。例えば、隣接した二つのデータ線  $D_{j-1}, D_j$  の間に位置した一対の画素  $P_{i_u, j-1}, P_{i_u, j}$  は、全て下に位置した一対のゲート線  $G_{i_u, up}, G_{i_u, down}$  のうちの上側ゲート線  $G_{i_u, up}$  に連結されており、左側画素電極  $P_{i_u, j-1}$  は、隣接した左側データ線  $D_{j-1}$  に、右側画素  $P_{i_u, j}$  は、隣接した右側データ線  $D_j$  に連結されている。しかし、一対の画素  $P_{i_u, j-1}, P_{i_u, j}$  のすぐ上、下、左側、または右側にある隣接した画素対において、同一の二つのデータ線の間に位置した二つの画素  $P_X$  に対し、二つの画素  $P_X$  は共に下側ゲートに連結されている。

#### 【0037】

上記の隣接した 4 対の画素電極の場合、左側画素電極は、隣接した左側データ線に、右側画素電極は、隣接した右側データ線に連結されている所は同一であるが、二つの画素電極が全て下側ゲートに連結されている所が異なる。

#### 【0038】

このように配置すれば、データ線  $D_0 - D_m$  の数を画素の列数の半分に減らすことができる。その代わりに、ゲート線  $G_{1, up} - G_{n, down}$  の数が画素の行数の 2 倍となる。

#### 【0039】

また、図 4 及び図 5 で一対のゲート線のうち、下側に位置したゲート線と連結されるスイッチング素子と連結されるデータ線は、二つのゲート線の間に分枝線を出して伸びる。

#### 【0040】

さらに、図 1 及び図 2 を参考にすれば、階調電圧生成部 800 は、画素の透過率に関する二組の複数階調電圧を生成する。二組のうちの一組は、共通電圧  $V_{com}$  に対して正の値を有して、他の一組は負の値を有する。

#### 【0041】

ゲート駆動部 400, 400L, 400R は、ゲート線  $G_{1, up} - G_{n, down}$  に連結されて外部からのゲートオン電圧  $V_{on}$  とゲートオフ電圧  $V_{off}$  の組み合わせからなるゲート信号をゲート線  $G_{1, up} - G_{n, down}$  に印加する。図 1 の場合、液晶表示板組立体 300 の左側に一つだけ備えられていて、図 2 の場合、液晶表示板組立体 300 の左側と右側に一つずつ一対が備えて隣接した二つの画素列の間に位置したゲート線対において上側ゲート線は左側ゲート駆動部 400L に、下側ゲート線は右側ゲート駆動部 400R に連結されている。しかし、その逆に連結されることはもちろんである。

#### 【0042】

データ駆動部 500 は、液晶表示板組立体 300 のデータ線  $D_1 - D_m$  に連結されて階調電圧生成部 800 からの階調電圧を選択してデータ信号として画素に印加する。

#### 【0043】

ゲート駆動部 400, 400L, 400R とデータ駆動部 500 は、複数の集積回路チップの形態で液晶表示板組立体 300 上に直接装着することもでき、可撓性印刷回路膜上に T C P ( 図示せず ) 方式で液晶表示板組立体 300 上に取付けることもできる。しかし、ゲート駆動部 400, 400L, 400R 及びデータ駆動部 500 、特にゲート駆動部 400, 400L, 400R の場合、ゲート線  $G_{1, up} - G_{n, down}$  、データ線  $D$

10

20

30

40

50

$D_0 - D_m$  及びスイッチング素子 Q と共に液晶表示板組立体 300 に集積されることもできる。

#### 【0044】

信号制御部 600 は、ゲート駆動部 400, 400L, 400R 及びデータ駆動部 500 などの動作を制御する。

#### 【0045】

以下、このような液晶表示装置の動作について詳細に説明する。

#### 【0046】

信号制御部 600 は、外部のグラフィック制御機（図示せず）から入力映像信号 R, G, B 及びその表示を制御する入力制御信号、例えば、垂直同期信号 V sync と水平同期信号 H sync、メインクロック MCLK、及びデータタイミング信号 DE などを供与される。

10

#### 【0047】

信号制御部 600 は、入力映像信号 R, G, B と入力制御信号に基づいて映像信号 R, G, B を液晶表示板組立体 300 の動作条件に合うように適切に処理して、ゲート制御信号 CONT 1 及びデータ制御信号 CONT 2 などを生成した後、ゲート制御信号 CONT 1 をゲート駆動部 400, 400L, 400R に送出し、データ制御信号 CONT 2 と処理した映像信号 DAT を、データ駆動部 500 に送出する。ここで映像信号 R, G, B の処理は、図 4 及び図 5 に示した液晶表示板組立体の画素配列に合わせて映像データ R, G, B を再配列する動作を含む。

20

#### 【0048】

ゲート制御信号 CONT 1 は、走査開始を指示する走査開始信号 STV、及びゲートオン電圧 Von の出力時期を制御する少なくとも一つのクロック信号を含む。ゲート制御信号 CONT 1 は、ゲートオン電圧 Von の持続時間を限定する出力タイミング信号 OE をさらに含むことができる。データ制御信号 CONT 2 は、映像データ DAT の伝送開始を知らせる水平同期開始信号 STH とデータ線  $D_0 - D_m$  に当該データ電圧を印加させるコード信号 LOAD、共通電圧 Vcom に対するデータ電圧の極性（以下、“共通電圧に対するデータ電圧の極性”を縮めて“データ電圧の極性”という）を反転させる反転信号 RVS 及びデータクロック信号 HCLK などを含む。

30

#### 【0049】

データ駆動部 500 は、信号制御部 600 から受け取るデータ制御信号 CONT 2 によって一つの行の画素に対応する映像データ DAT を順次に受信して、階調電圧生成部 800 からの階調電圧のうちの各映像データ DAT に対応する階調電圧を選択することによって、映像データ DAT を当該データ電圧に変換した後、これを当該データ線  $D_0 - D_m$  に印加する。

30

#### 【0050】

ゲート駆動部 400, 400L, 400R は、信号制御部 600 からのゲート制御信号 CONT 1 によってゲートオン電圧 Von をゲート線  $G_{1, up} - G_{n, down}$  に印加して、このゲート線  $G_{1, up} - G_{n, down}$  に連結されたスイッチング素子 Q を導通させて、それによってデータ線  $D_0 - D_m$  に印加されたデータ電圧が導通したスイッチング素子 Q を通じて当該画素に印加される。

40

#### 【0051】

画素に印加されたデータ電圧と共通電圧 Vcom の差は、液晶キャパシタ  $C_{LC}$  の充電電圧、つまり、画素電圧として現れる。液晶分子は、画素電圧の大きさによってその配列を変化させ、そのため液晶層 3 を通過する光の偏光が変化する。このような偏光の変化は、表示板 100, 200 に取付けられた偏光子（図示せず）によって光の透過率変化に現れる。

#### 【0052】

与えられた時間を単位にしてゲート駆動部 400, 400L, 400R とデータ駆動部 500 は、同一な走査動作を繰り返す。データ線の数が画素の列数と同一な一般的な液晶

50

表示装置の場合、このような時間を通常 1 水平周期といい、1 H と表示するが、本実施の形態の場合には、ゲート線  $G_{1, \text{up}} - G_{n, \text{down}}$  の数が従来の液晶表示装置の 2 倍であるので、一つの画素行の走査にかかる時間は、 $1 / 2 H$  にすべきである。しかし、隣接する二つのゲート線に  $1 / 2 H$  ほどゲートオン電圧  $V_{on}$  を重なるように印加すれば、従来の液晶表示装置とほとんど同一に一つのゲート線にゲートオン電圧  $V_{on}$  を印加する時間を  $1 H$  にして十分な充電時間を確保できる。

#### 【0053】

このような方式で、1 フレームの間全てのゲート線  $G_1 - G_{2n}$  に対して順次にゲートオン電圧  $V_{on}$  を印加して、全ての画素にデータ電圧を印加する。1 フレームが終われば次のフレームが始まって各画素に印加されるデータ電圧の極性が直前フレームでの極性と反対になるようにデータ駆動部 500 に印加される反転信号  $RVS$  の状態が制御される（“フレーム反転”）。この時、1 フレーム内でも反転信号  $RVS$  の特性によって一つのデータ線を通じて流れるデータ電圧の極性が変わることができ（例：行反転、点反転）、あるいは、一つの画素行に印加されるデータ電圧の極性も互いに異なることができる（例：列反転、点反転）。

#### 【0054】

一方、図 4 及び図 5 を再び見れば、二つの画素行の間に位置した一対のゲート線、例えば、図面符号  $G_{i, \text{up}}$  と  $G_{i, \text{down}}$  に示したゲート線のうちの上側にあるゲート線  $G_{i, \text{up}}$  が先にゲートオン電圧  $V_{on}$  を印加されて、下側にあるゲート線  $G_{i, \text{down}}$  が後ほどゲートオン電圧  $V_{on}$  を印加される。

#### 【0055】

ところが、後ほどゲートオン電圧  $V_{on}$  を印加される下側ゲート線  $G_{i, \text{down}}$  は、直前に電圧を印加される画素  $PX$  とは上側ゲート線  $G_{i, \text{up}}$  を間に置いており、距離上にも離れているために、下側ゲート線  $G_{i, \text{down}}$  にゲートオン電圧  $V_{on}$  が印加されて電磁気場が発生しても画素  $PX$  に至ると電磁気場自体の強さが非常に減るだけでなく、電磁気場が上側ゲート線  $G_{i, \text{up}}$  によって遮蔽されて画素  $PX$  に与える影響が非常に減る。

#### 【0056】

また、図 5 の場合には、隣接した二つのデータ線の間の二つの画素  $PX$  が同一なゲート線に連結されて同時に充電されるので、充電時期が異なる場合に発生する二つの画素  $PX$  の間の干渉が減る。

#### 【0057】

このように一つの行の画素  $PX$  を上側と下側のうちの何れか一方、特に下側に位置したゲート線とスイッチング素子を通じて連結することによって、開口率が減少することなくゲート線と画素  $PX$  の間の干渉を改善することができ、液晶表示装置の画質を向上させることができる。

#### 【0058】

本発明はまた、有機発光表示装置など他の表示装置にも適用できる。

#### 【0059】

以上で、本発明の好ましい実施の形態について詳細に説明したが、本発明の権利範囲はこれに限定されず、次の請求範囲で定義している本発明の基本概念を利用した当業者の多様な変形及び改良形態も本発明の権利範囲に属することである。

#### 【図面の簡単な説明】

#### 【0060】

【図 1】本発明の一実施の形態による液晶表示装置のブロック図である。

【図 2】本発明の他の実施の形態による液晶表示装置のブロック図である。

【図 3】本発明の一実施の形態による液晶表示装置の一つの画素に対する等価回路図である。

【図 4】本発明の一実施の形態による液晶表示装置の画素の空間的になっている配列を示した図である。

10

20

30

40

50

【図5】本発明の他の実施の形態による液晶表示装置の画素の空間的になっている配列を示した図である。

【符号の説明】

【0061】

|                                                       |             |    |

|-------------------------------------------------------|-------------|----|

| 3                                                     | 液晶層、        |    |

| 1 0 0                                                 | 下部表示板、      |    |

| 2 0 0                                                 | 上部表示板、      |    |

| 1 9 0                                                 | 画素電極、       |    |

| 2 3 0                                                 | 色フィルター、     | 10 |

| 2 7 0                                                 | 共通電極、       |    |

| 3 0 0                                                 | 液晶表示板組立体、   |    |

| 4 0 0 , 4 0 0 L , 4 0 0 R                             | ゲート駆動部、     |    |

| 5 0 0                                                 | データ駆動部、     |    |

| 6 0 0                                                 | 信号制御部、      |    |

| 8 0 0                                                 | 階調電圧生成部、    |    |

| C <sub>L</sub> C                                      | 液晶キャパシタ、    |    |

| C <sub>S</sub> T                                      | ストレージキャパシタ、 |    |

| C O N T 1                                             | ゲート制御信号、    | 20 |

| C O N T 2                                             | データ制御信号、    |    |

| C P V                                                 | ゲートクロック信号、  |    |

| D <sub>0</sub> - D <sub>m</sub>                       | データ線、       |    |

| D A T                                                 | 映像データ、      |    |

| D E                                                   | データイネーブル信号、 |    |

| G <sub>1</sub> , u p - G <sub>n</sub> , d o w n       | ゲート線、       |    |

| H C L K                                               | データクロック信号、  |    |

| H s y n c                                             | 水平同期信号、     |    |

| M C L K                                               | メーンクロック、    |    |

| O E                                                   | 出力イネーブル信号、  |    |

| P X , P <sub>i u , j - 1</sub> , P <sub>i u , j</sub> | 画素、         | 30 |

| Q                                                     | スイッチング素子、   |    |

| R , G , B                                             | 入力映像信号、     |    |

| R V S                                                 | 反転信号、       |    |

| S T H                                                 | 水平同期開始信号、   |    |

| S T V                                                 | 走査開始信号、     |    |

| V c o m                                               | 共通電圧、       |    |

| V o f f                                               | ゲートオフ電圧、    |    |

| V o n                                                 | ゲートオン電圧、    |    |

| V s y n c                                             | 垂直同期信号。     |    |

【図1】

【図2】

【図3】

【図4】

【 図 5 】

---

フロントページの続き

(72)発明者 金 聖 萬

大韓民国ソウル特別市松坡区新川洞 ザンミアパート30棟508号

(72)発明者 李 鍾 煥

大韓民国京畿道安養市東安区達安洞 セッピヨルアパート602棟1705号

(72)発明者 李 成 榮

大韓民国ソウル特別市陽川区新月7洞331-54番地 ソンイルビラ ガ棟302号

(72)発明者 許 命 九

大韓民国京畿道安養市東安区冠陽2洞 インドクウォン三星アパート102棟1004号

(72)発明者 文 勝 煥

大韓民国京畿道龍仁市上 けん 洞 マンヒョンマウル現代アイパーク6次アパート205棟1504号

(72)発明者 孔 香 植

大韓民国京畿道水原市靈通区靈通洞 シンナムシルシンウォンアパート644棟304号

(72)発明者 宋 長 根

大韓民国ソウル特別市江南区大峙2洞 ミドアアパート110棟304号

F ターム(参考) 2H092 GA11 JA24 JB22 JB31 NA07 NA25 PA11

2H093 NA16 NA32 NA33 NA51 NC09 NC10 NC11 NC12 ND22 ND54

ND60 NE03

5C006 AC27 BB16 BC02 BC03 BC06 BC20 FA41 FA54

5C080 AA06 AA10 BB05 DD03 DD22 DD27 DD28 FF11 JJ02

5C094 AA02 AA44 BA03 BA27 BA43 CA19 EA04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP2006048051A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 公开(公告)日 | 2006-02-16 |

| 申请号            | JP2005225847                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2005-08-03 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 金聖萬<br>李鍾煥<br>李成榮<br>許命九<br>文勝煥<br>孔香植<br>宋長根                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | 金 聖 萬<br>李 鍾 煥<br>李 成 榮<br>許 命 九<br>文 勝 煥<br>孔 香 植<br>宋 長 根                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G02F1/133 G02F1/1368 G09F9/30 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| CPC分类号         | G09G3/3648 G09G3/3225 G09G3/3266 G09G2300/0426 G09G2300/0465                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G02F1/133.550 G02F1/1368 G09F9/30.338 G09G3/20.624.B G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 2H092/GA11 2H092/JA24 2H092/JB22 2H092/JB31 2H092/NA07 2H092/NA25 2H092/PA11 2H093 /NA16 2H093/NA32 2H093/NA33 2H093/NA51 2H093/NC09 2H093/NC10 2H093/NC11 2H093/NC12 2H093/ND22 2H093/ND54 2H093/ND60 2H093/NE03 5C006/AC27 5C006/BB16 5C006/BC02 5C006 /BC03 5C006/BC06 5C006/BC20 5C006/FA41 5C006/FA54 5C080/AA06 5C080/AA10 5C080/BB05 5C080/DD03 5C080/DD22 5C080/DD27 5C080/DD28 5C080/FF11 5C080/JJ02 5C094/AA02 5C094 /AA44 5C094/BA03 5C094/BA27 5C094/BA43 5C094/CA19 5C094/EA04 2H192/AA24 2H192/BC24 2H192/CC62 2H192/DA12 2H192/DA73 2H192/EA42 2H193/ZA04 2H193/ZA08 2H193/ZA19 2H193 /ZC02 2H193/ZC15 2H193/ZD21 2H193/ZF22 2H193/ZF24 2H193/ZF36 2H193/ZP03 |         |            |

| 代理人(译)         | 宇谷 胜幸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 优先权            | 1020040061066 2004-08-03 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 其他公开文献         | JP4758704B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

**摘要(译)**

解决的问题：提供一种能够在不减小开口率的情况下改善栅极线与像素之间的耦合的液晶显示装置。根据本发明的液晶显示装置包括开关元件Q，并且布置在像素行和像素列中的多个像素Pi<sub>u</sub>, j-1, P<sub>i u</sub>, j连接到开关元件Q，用于传输用于导通开关元件Q的栅极导通电压的多对第一和第二栅极线G<sub>1</sub>, 向上-G<sub>n</sub>, 向下和连接至开关元件Q的多条数据线D<sub>0-D</sub>。米，并且每对的第一和第二栅极线G<sub>1</sub>, 向上-G<sub>n</sub>, 向下 布置在两个相邻的像素行之间，并且包括一个像素行的开关元件Q。链接到。[选择图]图4