(19)日本国特許庁( J P )

(12) 公開特許公報 ( A ) (11)特許出願公開番号

特開2001 - 281625

(P2001 - 281625A)

(43)公開日 平成13年10月10日(2001.10.10)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I            | テマコード*(参考)      |

|--------------------------|------|----------------|-----------------|

| G 0 2 F 1/133            | 550  | G 0 2 F 1/133  | 550 2 H 0 9 3   |

| G 0 9 G 3/20             | 641  | G 0 9 G 3/20   | 641 E 5 C 0 0 6 |

|                          |      |                | 641 R 5 C 0 5 8 |

| 3/36                     |      | 3/36           | 5 C 0 8 0       |

| H 0 4 N 5/66             | 102  | H 0 4 N 5/66   | 102 B           |

|                          |      | 審査請求 未請求 請求項の数 | 160 L (全 9 数)   |

(21)出願番号 特願2000 - 90283(P2000 - 90283)

(22)出願日 平成12年3月29日(2000.3.29)

(71)出願人 000002185

ソニー株式会社

東京都品川区北品川6丁目7番35号

(72)発明者 池田 裕幸

東京都品川区北品川6丁目7番35号 ソニー

株式会社内

(74)代理人 100092336

弁理士 鈴木 晴敏

最終頁に続く

(54)【発明の名称】 液晶表示装置及びその駆動方法

(57)【要約】

【課題】 アクティブマトリクス型液晶表示装置における動画表示の画質改善を目的とする。

【解決手段】 液晶表示装置は、行列状に配された液晶画素LCと、所定の周期で繰り返すフレーム毎に液晶画素LCの各行を順次走査する行駆動回路1と、順次走査に同期して各液晶画素LCに画像信号を書き込む列駆動回路3とを備えている。行駆動回路1は、フレーム1を先行のサブフレーム1及び後続のサブフレーム2に分割し、先行のサブフレーム1で順次走査を行った後、再び後続のサブフレーム2で順次走査を行う。列駆動回路3は、先行のサブフレーム1の線順次走査に同期して、当該フレーム1に割り当てられた正規の画像信号を各液晶画素LCに書き込み、後続のサブフレーム2の線順次走査に同期して、次のフレーム2に割り当てられた画像信号と当該フレーム1に割り当てられた画像信号とを演算して求めた画質調整用の画像信号を各液晶画素LCに書き込む。

## 【特許請求の範囲】

【請求項1】 行列状に配された液晶画素と、所定の周期で繰り返すフレーム毎に液晶画素の各行を順次走査する行駆動回路と、該順次走査に同期して各液晶画素に画像信号を書き込む列駆動回路とを備えた液晶表示装置の駆動方法において、

前記行駆動回路は、一フレームを先行のサブフレーム及び後続のサブフレームに分割し、先行のサブフレームで該順次走査を行った後、再び後続のサブフレームで該順次走査を行い、

前記列駆動回路は、先行のサブフレームの線順次走査に同期して、当該フレームに割り当てられた正規の画像信号を各液晶画素に書き込み、後続のサブフレームの線順次走査に同期して、次のフレームに割り当てられた画像信号と当該フレームに割り当てられた画像信号とを演算して求めた画質調整用の画像信号を各液晶画素に書き込むことを特徴とする液晶表示装置の駆動方法。

【請求項2】 前記列駆動回路は、次のフレームに割り当てられた画像信号と当該フレームに割り当てられた画像信号とを演算して両者を平均化した画質調整用の画像信号を各液晶画素に書き込むことを特徴とする請求項1記載の液晶表示装置の駆動方法。

【請求項3】 前記列駆動回路は、応答時間が10msec以下の液晶画素に画像信号を書き込むことを特徴とする請求項1記載の液晶表示装置の駆動方法。

【請求項4】 行列状に配された液晶画素と、所定の周期で繰り返すフレーム毎に液晶画素の各行を順次走査する行駆動回路と、該順次走査に同期して各液晶画素に画像信号を書き込む列駆動回路とを備えた液晶表示装置の駆動方法において、

前記行駆動回路は、一フレームを先行のサブフレーム及び後続のサブフレームに分割し、先行のサブフレームで該順次走査を行った後、再び後続のサブフレームで該順次走査を行い、

前記列駆動回路は、先行のサブフレームの線順次走査に同期して、当該フレームに割り当てられた正規の画像信号を各液晶画素に書き込み、後続のサブフレームの線順次走査に同期して、当該フレームに割り当てられた画像信号を割り引き演算して求めた画質調整用の画像信号を各液晶画素に書き込むことを特徴とする液晶表示装置の駆動方法。

【請求項5】 前記列駆動回路は、当該フレームに割り当てられた画像信号を半分に割り引き演算して求めた画質調整用の画像信号を各液晶画素に書き込むことを特徴とする請求項4記載の液晶表示装置の駆動方法。

【請求項6】 前記列駆動回路は、応答時間が10msec以下の液晶画素に画像信号を書き込むことを特徴とする請求項4記載の液晶表示装置の駆動方法。

【請求項7】 行列状に配された液晶画素と、所定の周期で繰り返すフレーム毎に液晶画素の各行を順次走査す

る行駆動回路と、該順次走査に同期して各液晶画素に画像信号を書き込む列駆動回路とを備えた液晶表示装置の駆動方法において、

前記行駆動回路は、一フレームを先行のサブフレーム及び後続のサブフレームに分割し、先行のサブフレームで該順次走査を行った後、再び後続のサブフレームで該順次走査を行い、

前記列駆動回路は、先行のサブフレームの線順次走査に同期して、当該フレームに割り当てられた正規の画像信号を各液晶画素に書き込み、後続のサブフレームの線順次走査に同期して、一律に中間調を表わす画質調整用の画像信号を各液晶画素に書き込むことを特徴とする液晶表示装置の駆動方法。

【請求項8】 前記列駆動回路は、応答時間が10msec以下の液晶画素に画像信号を書き込むことを特徴とする請求項7記載の液晶表示装置の駆動方法。

【請求項9】 行列状に配された液晶画素と、所定の周期で繰り返すフレーム毎に液晶画素の各行を順次走査する行駆動回路と、該順次走査に同期して各液晶画素に画像信号を書き込む列駆動回路とを備えた液晶表示装置において、

前記行駆動回路は、一フレームを先行のサブフレーム及び後続のサブフレームに分割し、先行のサブフレームで該順次走査を行った後、再び後続のサブフレームで該順次走査を行い、

前記列駆動回路は、先行のサブフレームの線順次走査に同期して、当該フレームに割り当てられた正規の画像信号を各液晶画素に書き込み、後続のサブフレームの線順次走査に同期して、次のフレームに割り当てられた画像信号と当該フレームに割り当てられた画像信号とを演算して求めた画質調整用の画像信号を各液晶画素に書き込むことを特徴とする液晶表示装置。

【請求項10】 前記列駆動回路は、次のフレームに割り当てられた画像信号と当該フレームに割り当てられた画像信号とを演算して両者を平均化した画質調整用の画像信号を各液晶画素に書き込むことを特徴とする請求項9記載の液晶表示装置。

【請求項11】 各液晶画素は、書き込まれた画像信号に対する応答時間が10msec以下であることを特徴とする請求項9記載の液晶表示装置。

【請求項12】 行列状に配された液晶画素と、所定の周期で繰り返すフレーム毎に液晶画素の各行を順次走査する行駆動回路と、該順次走査に同期して各液晶画素に画像信号を書き込む列駆動回路とを備えた液晶表示装置において、

前記行駆動回路は、一フレームを先行のサブフレーム及び後続のサブフレームに分割し、先行のサブフレームで該順次走査を行った後、再び後続のサブフレームで該順次走査を行い、

前記列駆動回路は、先行のサブフレームの線順次走査に

同期して、当該フレームに割り当てられた正規の画像信号を各液晶画素に書き込み、後続のサブフレームの線順次走査に同期して、当該フレームに割り当てられた画像信号を割り引き演算して求めた画質調整用の画像信号を各液晶画素に書き込むことを特徴とする液晶表示装置。

【請求項13】前記列駆動回路は、当該フレームに割り当てられた画像信号を半分に割り引き演算して求めた画質調整用の画像信号を各液晶画素に書き込むことを特徴とする請求項12記載の液晶表示装置。

【請求項14】各液晶画素は、書き込まれた画像信号に対する応答時間が10msec以下であることを特徴とする請求項12記載の液晶表示装置。10

【請求項15】行列状に配された液晶画素と、所定の周期で繰り返すフレーム毎に液晶画素の各行を順次走査する行駆動回路と、該順次走査に同期して各液晶画素に画像信号を書き込む列駆動回路とを備えた液晶表示装置において、

前記行駆動回路は、一フレームを先行のサブフレーム及び後続のサブフレームに分割し、先行のサブフレームで該順次走査を行った後、再び後続のサブフレームで該順次走査を行い、

20

前記列駆動回路は、先行のサブフレームの線順次走査に同期して、当該フレームに割り当てられた正規の画像信号を各液晶画素に書き込み、後続のサブフレームの線順次走査に同期して、一律に中間調を表わす画質調整用の画像信号を各液晶画素に書き込むことを特徴とする液晶表示装置。

【請求項16】各液晶画素は、書き込まれた画像信号に対する応答時間が10msec以下であることを特徴とする請求項15記載の液晶表示装置。30

#### 【発明の詳細な説明】

##### 【0001】

【発明の属する技術分野】本発明はアクティブラトリックス型の液晶表示装置及びその駆動方法に関する。より詳しくは、動画品質の改善を目的とした駆動技術に関する。

##### 【0002】

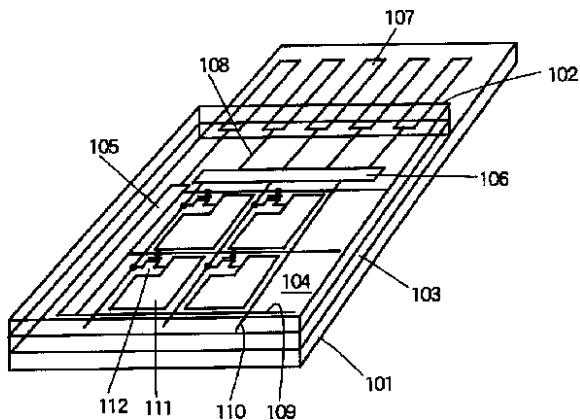

【従来の技術】図8は、アクティブラトリックス型液晶表示装置の一般的な構成を示す斜視図である。図示するように、従来の表示装置は一対の絶縁基板101, 102と両者の間に保持された液晶103とを備えたパネル構造を有する。下側の絶縁基板101には画素アレイ部104と駆動回路部とが集積形成されている。駆動回路部は行駆動回路105と列駆動回路106とに分かれている。又、絶縁基板101の周辺部上端には外部接続用の端子部107が形成されている。端子部107は配線108を介して行駆動回路105及び列駆動回路106に接続している。画素アレイ部104には行状のゲート配線109と列状の信号配線110が形成されている。両配線の交差部には画素電極111とこれを駆動する薄膜50

トランジスタ112が形成されている。薄膜トランジスタ112のゲート電極は対応するゲート配線109に接続され、ドレイン領域は対応する画素電極111に接続され、ソース領域は対応する信号配線110に接続している。ゲート配線109は行駆動回路105に接続する一方、信号配線110は列駆動回路106に接続している。

【0003】上述したアクティブラトリックス型の液晶表示装置(液晶ディスプレイ)はデバイス、プロセス、生産における技術の進歩により、20インチ級の大型化も可能になり、画質の面でも高輝度化及び高精細化が進んでいる。又、液晶ディスプレイの欠点とされていた視野角の問題、即ち一定以上のコントラストが得られる視野角の範囲がCRTに比べて狭く、中間調において局部的にネガポジ反転する問題も、液晶分子を基板面内方向の電界でスイッチングする技術(イン・プレーン・スイッチング)や、液晶配向方向の分割と垂直配向技術の組み合わせ(マルチブル・バーティカル・アライメント)や位相差補償フィルムの技術により、実用上問題ないレベルにまで改善が図られている。又、生産技術の進歩により、コストダウンも急速に進み、これらを背景に今や20インチクラスの液晶テレビも実用化されつつある。これらの技術により、液晶ディスプレイの画質は静止画に関する限りCRTを凌駕するまでになっている。

##### 【0004】

【発明が解決しようとする課題】にも関わらず、液晶ディスプレイにはまだ致命的とも言える欠点がある。それは、動画の画質である。動画像の輪郭がぼやけることや、画像がもやつく、極端には野球中継の画面でピッチャーの投げた球が尾を引くなどの問題がある。この内、野球ボールの尾が引く様な極端な現象は、液晶材料の進歩により改善が図られている。定量的には、液晶が電界により水平に寝た状態から立ち上がる時間と、零電界で再び立ち下がる時間を合わせた時間(応答時間)は30msec程度までに改善されている。現在、フレーム周期が30Hzで駆動される液晶ディスプレイにおいて、一つのフレームが表示される時間33.3msecの初めの部分で、液晶分子が立ち上がるか或いは立ち下がるかの反応をしており、液晶分子は十分フレーム周期に追従可能なまで応答性が改善されている。

【0005】しかしながら、それでも動画像は輪郭がぼやけるなどの欠陥が残っている。この欠陥は、更に応答時間の短い液晶材料、配向技術によつても改善できない。この欠陥の根本原因は、アクティブラトリックス型液晶ディスプレイの基本原理に根ざしており、1997年のインターナショナル・ディスプレイ・リサーチ・カンファレンス(IDRC)において、論文「Improving the Moving-Image Quality of TFT-LCDs」に報告されている。

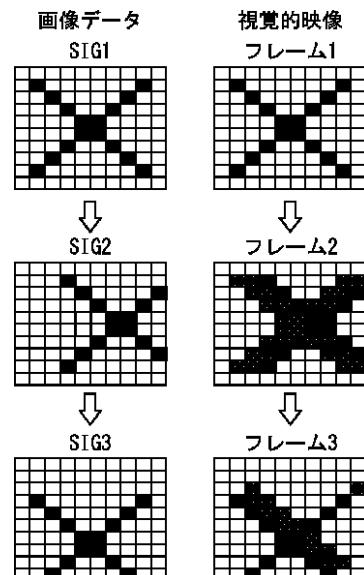

【0006】図9は、従来のアクティブラトリックス型液

液晶ディスプレイの動画像に関する問題を模式化して表わしている。図9の左側は各フレームに割り当てられる画像データを表わし、右側は実際の視覚的映像を表わしている。フレーム1の画像データS I G 1は例えば文字Xを表わしている。次のフレーム2では画像データS I G 2は僅かに右側に移動した文字Xを表わしている。次のフレーム3では、画像データS I G 3は逆に左下に移動する文字Xを表わしている。これに対し、実際人間の目に視覚される映像は、フレーム1からフレーム2に移る際に残像（影）が生じ、フレーム2からフレーム3に移る際にも残像が生じている。この様に、従来のアクティブマトリクス型液晶ディスプレイでは、残像により輪郭がぼやけるなどの欠陥が残されている。

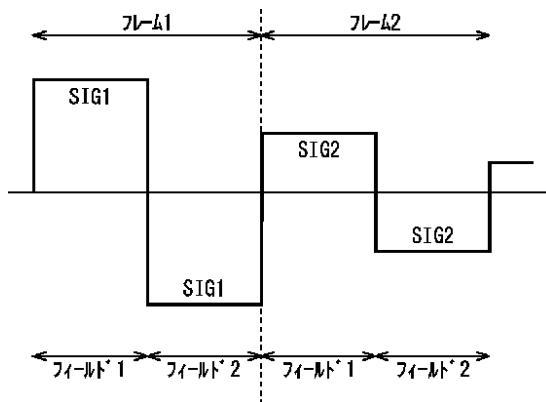

【0007】図10は、図9に示した従来のアクティブマトリクス型液晶ディスプレイの駆動方法を模式的に表わした波形図である。一般に、液晶ディスプレイは交流駆動されている。この為、フレーム1はフィールド1とフィールド2に分かれておりインターレース駆動される。フレーム1では画像信号S I G 1がフィールド1及びフィールド2に亘って液晶画素に書き込まれる。次のフレーム2では画像信号S I G 2が同じくフィールド1及びフィールド2に亘って書き込まれる。アクティブマトリクス駆動では、各液晶画素に書き込まれた画像信号は当該フレーム中はそのまま保持されている。次のフレームに至ると瞬間に画像データが書き換えられる。即ち、フレーム1とフレーム2の間で画像データが突然切り換えるので、残像現象が生じることになる。フレーム1で白が書き込まれていた液晶画素がフレーム2で突然黒に書き換えられると、フレームの切換時点で人間の目は残像を感じてしまう。

【0008】CRTにおいては表示画像はμsecオーダで輝度が減衰するのに対し、液晶ディスプレイでは一フレームの間画像を表示し続ける保持型の表示原理となっている。この為、液晶材料の応答性を究極まで改善しても、動画の輪郭に沿った液晶画素はフレームの切り換わる直前まで画像を表示している為、これが人間の目の残像効果と相まって、次のフレームでもそこに像が表示されているかの如く感知する。これが、アクティブマトリクス型液晶ディスプレイの動画の画質欠陥の根本原因である。

【0009】この解決策として、上記に挙げた論文では、「OCBモード」と呼ばれる応答時間が5msec程度の液晶技術を前提として、人間の目で感ずる残像を断ち切る技術を導入することで、動画質の改善を図っている。具体的には、透過型の液晶ディスプレイにおいて、バックライトを一フレームの間に点滅させて、一フレームの前半で画像を表示する一方、一フレームの後半はあたかもCRT輝度が減衰するかの如くに、バックライトを消灯する方法を採用している。しかしながら、この方法には次の様な問題がある。一つは、バックライト

10

20

30

40

50

が点滅する為に、平均輝度が低下し、画面が暗くなると同時にコントラストが低下する。又、バックライトを間欠駆動する為、コスト及び消費電力が上昇する。更には、近年急速に普及している反射型の液晶ディスプレイには適用できない問題がある。このうち、バックライトの消費電力の課題及び反射型への適用の課題を改善したものに、1998年のソサイアティ オブ インターナショナル、ディスプレイの論文 "A Novel Wide-Viewing-Angle Motion-Picture LCD" があるが、輝度及びコントラスト低下の課題は改善に至っていない。

#### 【0010】

【課題を解決するための手段】上述した従来の技術の課題に鑑み、本発明はアクティブマトリクス型液晶表示装置における動画表示の画質改善を目的とする。この目的を達成する為に以下の手段を講じた。即ち、本発明は、行列状に配された液晶画素と、所定の周期で繰り返すフレーム毎に液晶画素の各行を順次走査する行駆動回路と、該順次走査に同期して各液晶画素に画像信号を書き込む列駆動回路とを備えた液晶表示装置の駆動方法において、前記行駆動回路は、一フレームを先行のサブフレーム及び後続のサブフレームに分割し、先行のサブフレームで該順次走査を行った後、再び後続のサブフレームで該順次走査を行い、前記列駆動回路は、先行のサブフレームの線順次走査に同期して、当該フレームに割り当てられた正規の画像信号を各液晶画素に書き込み、後続のサブフレームの線順次走査に同期して、次のフレームに割り当てられた画像信号と当該フレームに割り当てられた画像信号とを演算して求めた画質調整用の画像信号を各液晶画素に書き込むことを特徴とする。好ましくは、前記列駆動回路は、次のフレームに割り当てられた画像信号と当該フレームに割り当てられた画像信号とを演算して両者を平均化した画質調整用の画像信号を各液晶画素に書き込む。又、前記列駆動回路は、応答時間が10msec以下の液晶画素に画像信号を書き込む。

【0011】又本発明は、行列状に配された液晶画素と、所定の周期で繰り返すフレーム毎に液晶画素の各行を順次走査する行駆動回路と、該順次走査に同期して各液晶画素に画像信号を書き込む列駆動回路とを備えた液晶表示装置の駆動方法において、前記行駆動回路は、一フレームを先行のサブフレーム及び後続のサブフレームに分割し、先行のサブフレームで該順次走査を行った後、再び後続のサブフレームで該順次走査を行い、前記列駆動回路は、先行のサブフレームの線順次走査に同期して、当該フレームに割り当てられた正規の画像信号を各液晶画素に書き込み、後続のサブフレームの線順次走査に同期して、当該フレームに割り当てられた画像信号を割り引き演算して求めた画質調整用の画像信号を各液晶画素に書き込むことを特徴とする。好ましくは、前記列駆動回路は、当該フレームに割り当てられた画像信号

を半分に割り引き演算して求めた画質調整用の画像信号を各液晶画素に書き込む。又、前記列駆動回路は、応答時間が10msec以下の液晶画素に画像信号を書き込む。

【0012】更に本発明は、行列状に配された液晶画素と、所定の周期で繰り返すフレーム毎に液晶画素の各行を順次走査する行駆動回路と、該順次走査に同期して各液晶画素に画像信号を書き込む列駆動回路とを備えた液晶表示装置の駆動方法において、前記行駆動回路は、一フレームを先行のサブフレーム及び後続のサブフレームに分割し、先行のサブフレームで該順次走査を行った後、再び後続のサブフレームで該順次走査を行い、前記列駆動回路は、先行のサブフレームの線順次走査に同期して、当該フレームに割り当てられた正規の画像信号を各液晶画素に書き込み、後続のサブフレームの線順次走査に同期して、一律に中間調を表わす画質調整用の画像信号を各液晶画素に書き込むことを特徴とする。好ましくは、前記列駆動回路は、応答時間が10msec以下の液晶画素に画像信号を書き込む。

【0013】本発明によれば、一フレームを先行のサブフレームと後続のサブフレームに分割している。先行のサブフレームでは、正規の画像信号を各液晶画素に書き込む。これに対し、後続のサブフレームでは正規の画像信号ではなく画質調整用の画像信号を各液晶画素に書き込む。この画質調整用の画像信号は先のフレームと次のフレームとの間の切換時点で生じていた残像現象を遮断する為に導入されたものである。従来の様に後続のサブフレームを完全な黒表示とするのではなく、当該フレーム及び/又は次のフレームの画像データと相關のある画像データを用いることで、必要な輝度を確保している。

#### 【0014】

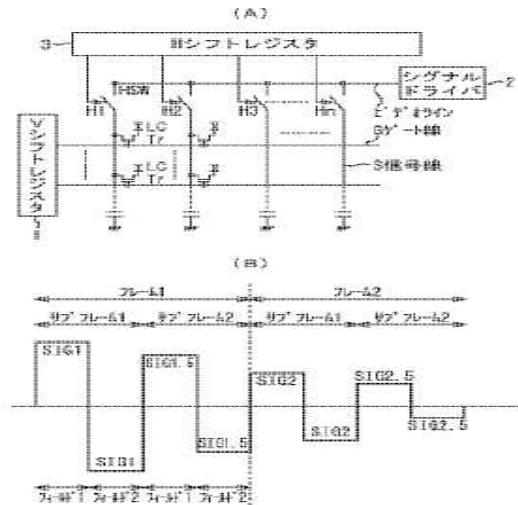

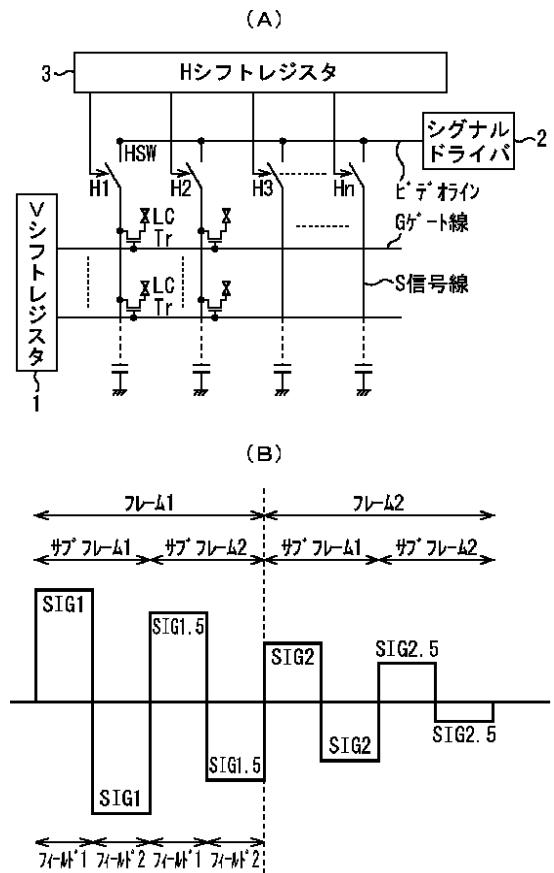

【発明の実施の形態】以下図面を参照して本発明の実施の形態を詳細に説明する。図1は本発明に係る液晶表示装置及びその駆動方法を示す模式図の一例である。

(A)に示す様に、本液晶表示装置は基本的に、行列状に配された液晶画素LCと、所定の周期で繰り返すフレーム毎に液晶画素LCの各行を順次走査する行駆動回路(Vシフトレジスタ1)と、この順次走査に同期して各液晶画素LCに画像信号を書き込む列駆動回路(シグナルドライバ2及びHシフトレジスタ3)とを備えている。具体的には、本アクティブラマトリクス型の液晶表示装置は、行状のゲート線Gと、列状の信号線Sと、両者の各交差部に配された行列状の液晶画素LCとを有している。個々の液晶画素LCは薄膜トランジスタTrにより駆動される。Vシフトレジスタ1は各ゲート線Gをフレーム毎に最初の行から最後の行まで線順次走査する。これにより、一水平期間(1H)毎に一行分の液晶画素LCを選択する。Hシフトレジスタ3は1H内で画像信号を各信号線Sに順次サンプリングし、選択された一行分の液晶画素LCに点順次で画像信号の書き込みを行な

う。この点順次書き込みを最初の一行分から最後の一行分まで行なって、一フレーム分の画像信号を各液晶画素LCに書き込む。具体的には、各信号線Sは水平スイッチHSWを介してビデオラインに接続されシグナルドライバ2から画像信号の供給を受ける一方、Hシフトレジスタ3は順次水平サンプリングパルスH1,H2,H3,...,Hnを出力し各水平スイッチHSWの開閉制御を行なう。

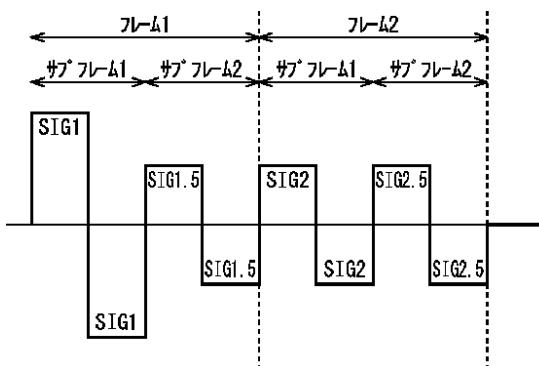

【0015】続いて(B)を参照して、本液晶表示装置の駆動方法を説明する。まずVシフトレジスタ1は、一フレームを先行のサブフレーム及び後続のサブフレームに分割し、先行のサブフレームで順次走査を行なった後、再び後続のサブフレームで順次走査を行なう。図示の例では、フレーム1を先行のサブフレーム1及び後続のサブフレーム2に分割し、サブフレーム1で一回目の順次走査を行なった後、後続のサブフレーム2で二回目の順次走査を行なう。同様に、次のフレーム2もサブフレーム1とサブフレーム2に分割されており、各サブフレームで線順次走査を実行する。尚、各サブフレームはフィールド1とフィールド2に分かれており、従来例と同様にインターレース駆動を行なっている。本実施形態では各フレームを2個のサブフレームに分割しているが、これを3個以上のサブフレームに分割しても構わない。一方、Hシフトレジスタ3は、先行のサブフレーム1の線順次走査に同期して、当該フレーム1に割り当てられた正規の画像信号SIG1を各液晶画素に書き込み、後続のサブフレーム2の線順次走査に同期して、次のフレーム2に割り当てられた画像信号SIG2と当該フレーム1に割り当てられた画像信号SIG1とを演算して求めた画質調整用の画像信号SIG1.5を各液晶画素に書き込む。尚、画像信号SIG1、SIG1.5、SIG2などはシグナルドライバ2で作成され、ビデオラインを介して液晶画素側に送られる。Vシフトレジスタ1、Hシフトレジスタ3、シグナルドライバ2などの周辺回路は、液晶画素の形成された基板に一体的に形成されるか、もしくは別IC部品として接続される。本実施形態では、シグナルドライバ2は、次のフレーム2に割り当てられた画像信号SIG2と当該フレーム1に割り当てられた画像信号SIG1とを演算して両者を平均化した画質調整用の画像信号SIG1.5を各液晶画素LCに書き込んでいる。この駆動方法を実現する為には、Vシフトレジスタ1及びHシフトレジスタ3の走査速度を従来に比べ2倍とすればよい。又、シグナルドライバ2に先のフレームと次のフレームとの間の画像信号の演算を行なう為に、一画面分(一フレーム分)の画像信号情報を記憶しておくフレームメモリを組み込んでおけばよい。

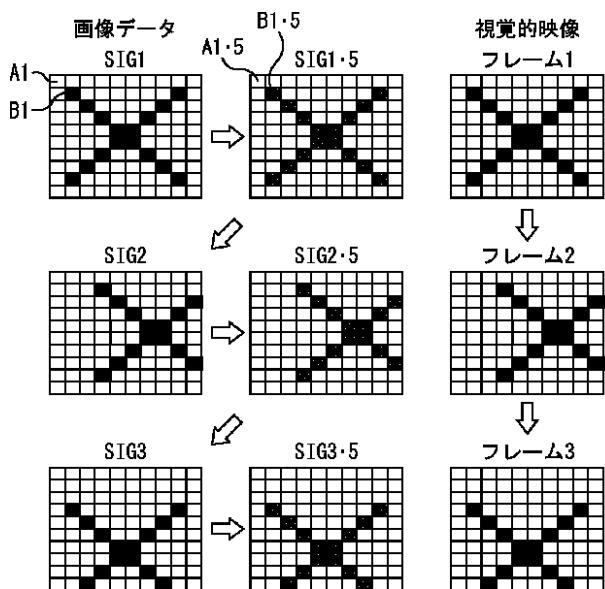

【0016】図2は、図1に示した駆動方法を模式化して表わしたものである。図中、左側の部分はフレーム1～フレーム3に割り当てられた画像データSIG1～S

I G 3 をビットマップとして表わしたものである。理解を容易にする為、このビットマップデータは図9に示したビットマップデータと同じものを使っている。図中右側の部分はフレーム1からフレーム3に亘って実際に人間の目が視覚する映像を表わしている。図9に示した従来例と比較すれば明らかな様に、残像現象は表われていない。その理由は、図の中央部分に示す様に、各フレームの後半サブフレームで、残像を遮断する画像調整用の画像信号を挿入しているからである。例えば、フレーム1の前半サブフレームでは画像データS I G 1が書き込まれ、フレーム2の前半サブフレームでは画像データS I G 2が書き込まれ、両サブフレームの間に位置するフレーム1の後半サブフレームでは、S I G 1とS I G 2を平均化した画像データS I G 1 . 5が書き込まれる。例えば、画面の左上角の液晶画素Aに着目する。フレーム1における画素AのデータをA 1とし、フレーム2における画素AのデータをA 2とすると、フレーム1の後半サブフレームで画素Aに書き込まれるデータA 1 . 5はA 1とA 2の平均値となる。図示の例では、A 1 , A 2共に白レベルであるのでA 1 . 5は白レベルである。即ち、フレーム1とフレーム2で画像データが変化しない画素は、フレーム1の後半のサブフレームでもそのまま当該データが書き込まれる。換言すると、静止している部分はそのままであるので、従来と同様に優れた静止画像の画質が得られる。一方、画素Aの右下に位置する画素Bに着目すると、フレーム1では黒(B 1)であり、フレーム2では白(B 2)に切り換わっている。従って、フレーム1の後半サブフレームで画素Bに書き込まれる画像データB 1 . 5はB 1とB 2の中間の灰色となる。この様に、先のフレームと次のフレームの両者に相關した画像データを挿入することで、人間の残像現象を緩和している。尚、図示の例はノーマリホワイトモードを例に取って説明したものであるが、ノーマリブラックモードでも適用可能である。本発明は、透過型でも反射型でも適用可能である。透過型に適用した場合、視認される動画特性が向上するのは勿論、白表示は白表示のままの輝度の低下もない。又、動画部分でも画像信号の電位に変化のない例えは黒表示の部分は黒表示のままである為、コントラストの低下も生じない。

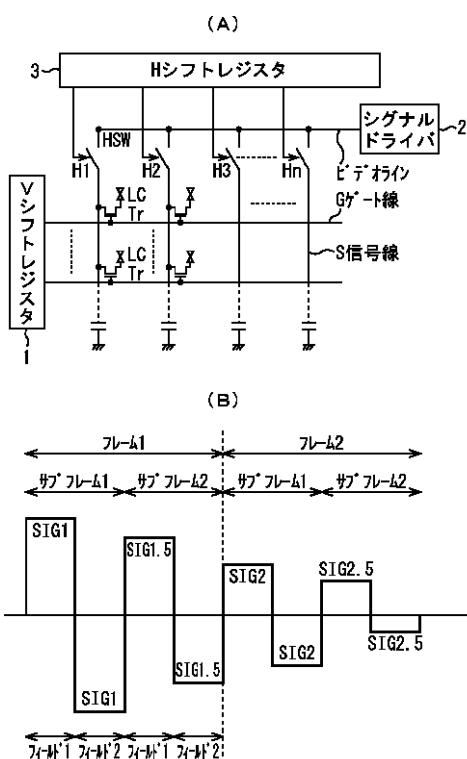

【0017】本発明では、一つのフレームを2以上のサブフレームに分割して駆動する為、液晶画素は高速応答性が要求される。この為、図1に示した実施形態では応答時間が10msec以下の液晶画素を用いている。具体的には、図3に示す様に、O C B モード(Optic ally Compensated Birefringence mode)の液晶パネルを用いている。(A)に示す様に、このO C B モードは対向する電極10, 20の間に挟み込む液晶30が、ねじれずにしかも各電極面で逆方向にプレチルト角0を有する様に配列され、液晶層中央部で液晶分子30cが電極に垂直にな

る様な配置になっているモード(ベント配列)で、液晶層の上半分と下半分が常時対称な形状になっている。このモードは電極10, 20間に一定の電圧が印加された状態で生じるものであり、電圧無印加状態では、(B)に示す様に液晶層中央部の液晶分子30cが電極に対して平行になる所謂スプレー配列に戻る。O C B モードは上記の様に液晶分子配列が層を中心に対照的である為に視角を傾けても視角特性は対称となり、更に二軸の位相差板で補償することにより、視角依存性がない表示が得られる。又、ネマティック液晶のねじれ配向を利用したTN方式やSTN方式に比べ、ベント配向を利用したO C B モードは電界に対する応答時間が短くなっている、高速応答性に特徴がある。

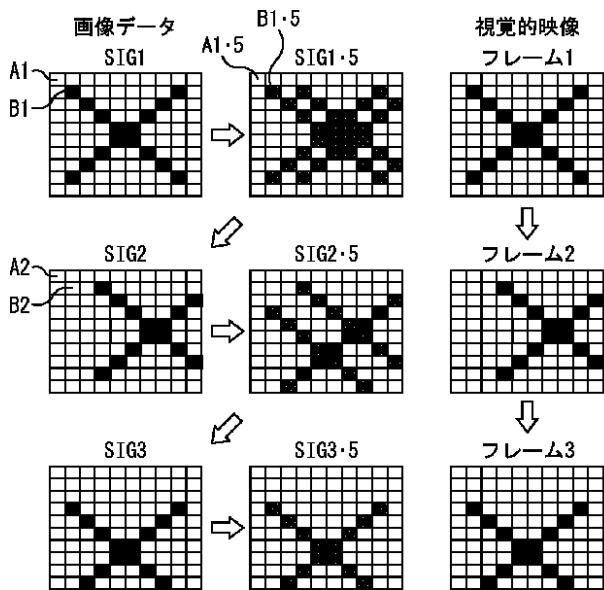

【0018】図4は、本発明に係る液晶表示装置の駆動方法の他の実施形態の一例を示す模式図である。理解を容易にする為、図2に示した先の実施形態と同様なフォームで記載している。即ち、図の左側部分は、フレーム1～フレーム3の各前半サブフレームで書き込まれる画像データS I G 1～S I G 3をビットマップデータで表わしたものである。又、右側部分は、フレーム1からフレーム3に亘って実際に視認される映像を模式的に表わしたものである。図示の様に、残像は緩和されている。図の中央部分は、フレーム1～フレーム3の各後半サブフレームに挿入される画像データS I G 1 . 5、S I G 2 . 5及びS I G 3 . 5をビットマップデータで表わしたものである。本実施形態では、当該フレームに割り当てられた画像信号を割引演算して求めた画質調整用の画像信号を各液晶画素に書き込んでいる。例えば、画面の左上角に位置する画素Aに着目すると、フレーム1ではその画像データA 1は白(零電位)である。この為フレーム1の後半サブフレームで画素Aに書き込まれるべき画像データA 1 . 5はA 1を所定の割合で割り引いたものであるが、元々A 1 = 0であるので、A 1 . 5も0である。画素Aの右下に位置する画素Bに着目すると、フレーム1におけるデータB 1は黒を表わしており、ノーマリホワイトモードでは最高電位レベルである。これを所定の割合で割り引いてフレーム1の後半サブフレームに書き込むべき画像データB 1 . 5を得ている。黒レベルを半分に割り引けば灰レベルの画像データB 1 . 5が得られる。一般に、割引率は0.5～0.75程度に設定するとよい。この様に、当該フレームの画像データを所定の割合で割り引いた画像データを後半サブフレームに挿入することで、残像現象を緩和することが可能である。

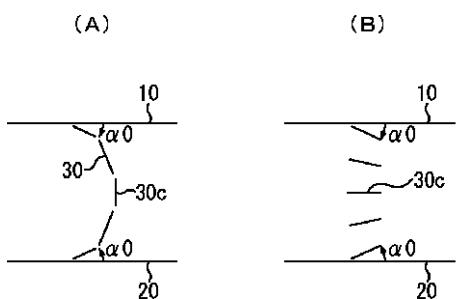

【0019】図5は、図4に示した実施形態に用いられる画像信号を示す模式的な波形図である。フレーム1の前半サブフレーム1では正規の画像信号S I G 1が2フィールドに亘って書き込まれ、後半サブフレーム2ではS I G 1を所定の割合で割り引いた画像信号S I G 1 . 5が2フィールドに亘って書き込まれる。次のフレーム

2でも同様に、前半サブフレーム1で正規の画像信号SIG2が書き込まれ、後半サブフレーム2では正規の画像信号SIG2を例えれば半分に割り引いた画像信号SIG2.5が各画素に書き込まれる。

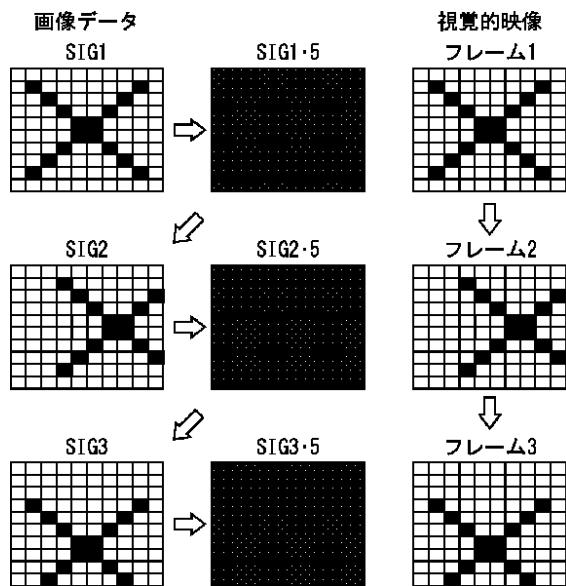

**【0020】**図6は、本発明に係る液晶表示装置の駆動方法の別の実施形態の一例を示す模式図である。理解を容易にする為、図2及び図4に示した先の実施形態と同様のフォームを用いている。本実施形態では、各フレームの前半サブフレームでは正規の画像データを書き込む一方、後半サブフレームでは一律に中間調を表わす画質調整用の画像信号を各液晶画素に書き込んでいる。本駆動方法は、図2及び図4に示した先の実施形態と異なり、画像信号の演算が必要でない為、フィールドメモリを要しない。図6に示した例はノーマリホワイトモードであるが、ノーマリブラックモードにも適用可能である。各フレーム間の残像現象を断ち切る為には、各フレームの後半サブフレームで完全な黒表示を画面全体に亘って書き込んだ方が効果的である。しかしながら、黒データを書き込むと時間軸で平均化した場合画面の明るさが足らなくなる場合がある。そこで、本実施形態では各フレームの後半サブフレームで黒データではなく中間調のデータを各液晶画素に一律に書き込む様にしている。

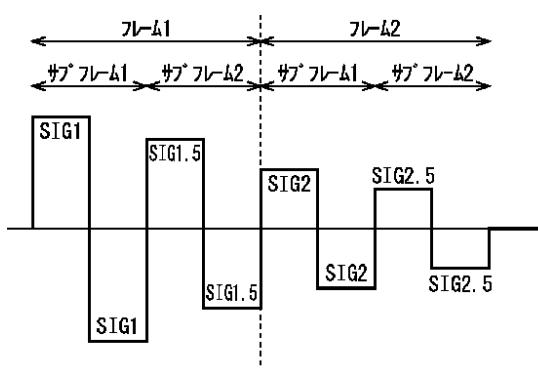

**【0021】**図7は、図6に示した駆動方法に使われる画像信号を模式的に表わした波形図である。フレーム1の前半サブフレーム1では正規の画像信号SIG1を2フィールドに亘って書き込み、後半サブフレーム2では各液晶画素に対して一律に所定の中間調信号電圧を表わす画像信号SIG1.5を書き込む。次のフレーム2でも同様に、前半サブフレーム1で正規の画像信号SIG2を書き込み、次の後半サブフレーム2で中間調を表わす画質調整用の画像信号を一律に書き込む。

#### 【0022】

**【発明の効果】**以上説明したように、本発明によれば、一フレームを複数のサブフレームに分割し、先頭以外の\*

\*サブフレームで書き込む画像信号を、当該フレームの画像信号電位又は次のフレームの画像信号電位の値の演算により求めることで、或いは少なくとも先頭以外のサブフレームの画像信号電位を一律中間調電位としてことで、アクティブマトリクス型液晶表示装置における動画像の画質を改善することが可能である。特に、当該フレームと次のフレームとの間でフレーム間演算を行なって画像信号を決める場合は、平均輝度を低下させることなく、動画像のコントラストを低下させることもない優れた表示特性を得ることが可能である。

#### 【図面の簡単な説明】

**【図1】**本発明に係る液晶表示装置及びその駆動方法を示す模式図である。

**【図2】**本発明に係る液晶表示装置の駆動方法の実施形態を示す模式図である。

**【図3】**本発明に係る液晶表示装置の一例を示す模式図である。

**【図4】**本発明に係る液晶表示装置の駆動方法の他の実施形態を示す模式図である。

**【図5】**本発明に係る液晶表示装置の駆動方法の他の実施形態を示す波形図である。

**【図6】**本発明に係る液晶表示装置の駆動方法の別の実施形態を示す模式図である。

**【図7】**本発明に係る液晶表示装置の駆動方法の別の実施形態を示す波形図である。

**【図8】**従来の液晶表示装置の一例を示す斜視図である。

**【図9】**従来の液晶表示装置の動作説明に供する模式図である。

**【図10】**従来の液晶表示装置の動作説明に供する波形図である。

#### 【符号の説明】

1・・・Vシフトレジスタ、2・・・シグナルドライバ、3・・・Hシフトレジスタ、LC・・・液晶画素

【図3】

【図5】

【図1】

【図4】

【図2】

【図6】

【図7】

【図8】

【図10】

【図9】

フロントページの続き

F ターム(参考) 2H093 NA33 NA43 NC02 NC22 NC29

NC34 ND04 ND06 ND08 ND32

5C006 AA01 AA14 AF44 BB16 BF03

FA29

5C058 AA08 AB03 BA03 BA08 BB13

BB16

5C080 AA10 BB05 DD05 DD06 EE19

EE29 FF11 JJ02 JJ04 JJ05

JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2001281625A</a>                                                                                                                                                                                                                                                                                                                                                                               | 公开(公告)日 | 2001-10-10 |

| 申请号            | JP2000090283                                                                                                                                                                                                                                                                                                                                                                                                | 申请日     | 2000-03-29 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 池田裕幸                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 池田 裕幸                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G02F1/133 G09F9/30 G09F9/35 G09G3/20 G09G3/36 H04N5/66                                                                                                                                                                                                                                                                                                                                                      |         |            |

| CPC分类号         | G09G3/3648 G09G2300/0491 G09G2320/0257 G09G2320/0261                                                                                                                                                                                                                                                                                                                                                        |         |            |

| FI分类号          | G02F1/133.550 G09G3/20.641.E G09G3/20.641.R G09G3/36 H04N5/66.102.B                                                                                                                                                                                                                                                                                                                                         |         |            |

| F-TERM分类号      | 2H093/NA33 2H093/NA43 2H093/NC02 2H093/NC22 2H093/NC29 2H093/NC34 2H093/ND04 2H093/ND06 2H093/ND08 2H093/ND32 5C006/AA01 5C006/AA14 5C006/AF44 5C006/BB16 5C006/BF03 5C006/FA29 5C058/AA08 5C058/AB03 5C058/BA03 5C058/BA08 5C058/BB13 5C058/BB16 5C080/AA10 5C080/BB05 5C080/DD05 5C080/DD06 5C080/EE19 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ04 5C080/JJ05 5C080/JJ06 2H193/ZA04 2H193/ZC15 2H193/ZF02 |         |            |

| 其他公开文献         | <a href="#">JP4240743B2</a>                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

### 摘要(译)

本发明的目的是提高有源矩阵液晶显示装置中的运动图像显示的图像质量。 液晶显示装置包括以行和列排列的液晶像素LC，针对以预定周期重复的每一帧依次扫描液晶像素LC的每一行的行驱动电路1以及与顺序扫描同步的行驱动电路1。 提供了用于将图像信号写入到液晶像素LC的列驱动电路3。 行驱动电路1将帧1划分为前一子帧1和后一子帧2，在前一子帧1中执行顺序扫描，然后再次在后一子帧2中执行顺序扫描。 列驱动电路3与前一子帧1的行顺序扫描同步地将分配给帧1的普通图像信号写入每个液晶像素LC，并与后一子帧2的行顺序扫描同步。 然后，通过计算分配给下一帧2的图像信号和分配给帧1的图像信号而获得的用于图像质量调节的图像信号被写入每个液晶像素LC中。