(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-334216

(P2004-334216A)

(43) 公開日 平成16年11月25日(2004.11.25)

(51) Int.Cl.<sup>7</sup>

**G02F** 1/1343

**G02F** 1/133

**G02F** 1/1345

**G02F** 1/1368

**H01L** 29/786

F 1

G02F 1/1343

G02F 1/133 505

G02F 1/133 550

G02F 1/1345

G02F 1/1368

H01L 29/786

テーマコード(参考)

2H092

2H093

5F110

審査請求 未請求 請求項の数 10 O L (全 17 頁) 最終頁に続く

|              |                              |          |                                                                |

|--------------|------------------------------|----------|----------------------------------------------------------------|

| (21) 出願番号    | 特願2004-137754 (P2004-137754) | (71) 出願人 | 390019839<br>三星電子株式会社<br>大韓民国京畿道水原市靈通区梅灘洞 416                  |

| (22) 出願日     | 平成16年5月6日 (2004.5.6)         | (74) 代理人 | 100094145<br>弁理士 小野 由己男                                        |

| (31) 優先権主張番号 | 2003-028650                  | (74) 代理人 | 100106367<br>弁理士 稲積 朋子                                         |

| (32) 優先日     | 平成15年5月6日 (2003.5.6)         | (72) 発明者 | 金 煙 傑<br>大韓民国京畿道龍仁市駒城面普亭里 116<br>1番地珍山マウル三星5次アパート 505<br>棟206号 |

| (33) 優先権主張国  | 韓国 (KR)                      | (72) 発明者 | 全 珍<br>大韓民国京畿道安養市東安区葛山洞セムマ<br>ウル双龍アパート 202 棟602号               |

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【要約】

【課題】 表示特性を向上させることができる液晶表示装置を提供する。

## 【解決手段】

液晶表示パネルには第1ゲートライン、第2ゲートライン及び第1データラインに連結された第1画素、第1ゲートラインと第1データラインに連結された第2画素及び第2データラインと第1ゲートラインに連結された第3画素で構成された複数の画素群が具備される。第1ゲート駆動部は第1ゲートラインに第1ゲート駆動信号を出し、第2ゲート駆動部は第2ゲートラインに第2ゲート駆動信号を出す。データ駆動部は映像信号を発生して第1及び第2データラインに提供する。従って、液晶表示装置の表示特性を向上させることができ、液晶表示パネルに形成されたデータラインの数を減少させることができる。

## 【選択図】

図2

**【特許請求の範囲】****【請求項 1】**

第1ゲートラインと、前記第1ゲートラインと隣接した第2ゲートライン及び第1データラインに連結された第1画素と、前記第1ゲートラインと前記第1データラインに連結された第2画素と、前記第1データラインと隣接する第2データラインと前記第1ゲートラインに連結された第3画素と、を含んで構成される多数の画素群が具備された表示パネルと、

前記第1ゲートラインに第1ゲート駆動信号を提供するための第1ゲート駆動部と、

前記第2ゲートラインに第2ゲート駆動信号を提供するための第2ゲート駆動部と、

映像信号を発生して前記第1データライン及び第2データラインに提供するためのデータ駆動部と、

10

を含むことを特徴とする表示装置。

**【請求項 2】**

前記第1画素は、

第1画素電極と、

前記第2ゲートラインに連結されたゲート電極、前記第1データラインに連結されたソース電極、及びドレーン電極を有する第1トランジスタと、

前記第1ゲートラインに連結されたゲート電極、前記第1トランジスタのドレーン電極に連結されたソース電極、及び前記第1画素電極と結合されたドレーン電極を有する第2トランジスタと、

20

を含むことを特徴とする請求項1記載の表示装置。

**【請求項 3】**

前記第1ゲート駆動信号は、前記第1ゲートラインに連結された以前端の前記第1画素及び第2画素を駆動するための第1区間、前記第1ゲートラインに連結された現在端の前記第1画素乃至第3画素を駆動するための第2区間を有し、

前記第2ゲート駆動信号は、前記第2ゲートラインに連結された以前端の前記第1画素及び第2画素を駆動するための第3区間、及び前記第2ゲートラインに連結された現在端の前記第1画素乃至第3画素を駆動するための第4区間を有することを特徴とする請求項2記載の表示装置。

30

**【請求項 4】**

前記第2画素は、

第2画素電極と、

前記第1ゲートラインに連結されたゲート電極、前記第1データラインに連結されたソース電極、及びドレーン電極を有する第3トランジスタと、

前記第1ゲートラインに連結されたゲート電極、前記第3トランジスタのドレーン電極に連結されたソース電極、及び前記第2画素電極と結合されたドレーン電極を有する第4トランジスタと、を含むことを特徴とする請求項2記載の表示装置。

40

**【請求項 5】**

前記第1区間及び第3区間は、前記第1トランジスタをターンオンさせて前記第1画素電極に前記映像信号を出力するための第5区間、及び前記第1トランジスタをターンオフさせて前記第2画素電極に前記映像信号を出力するための第6区間で構成されることを特徴とする請求項4記載の表示装置。

**【請求項 6】**

前記第3画素は、

第3画素電極と、

前記第1ゲートラインに連結されたゲート電極、前記第2データラインに連結されたソース電極、及びドレーン電極を有する第5トランジスタと、

前記第1ゲートラインに連結されたゲート電極、前記第5トランジスタのドレーン電極に連結されたソース電極、及び前記第3画素電極と結合されたドレーン電極を有する第6トランジスタと、

50

を含むことを特徴とする請求項 2 記載の表示装置。

【請求項 7】

前記表示パネルは、前記第 1 画素乃至第 3 画素にそれぞれ対応する R ( R e d ) 、 G ( G r e e n ) 、 B ( B l u e ) 色画素を更に含むことを特徴とする請求項 1 記載の表示装置。

【請求項 8】

前記第 1 ゲート駆動部は、

第 1 クロック信号の入力を受けるクロック信号端子と、前記第 1 クロック信号を前記第 1 ゲート駆動信号として出力する第 1 出力端子と、前記第 1 クロック信号を第 1 ステージ駆動信号として出力する第 2 出力端子と、以前端の第 2 出力端子から出力された前記第 1 ステージ駆動信号の入力を受ける入力端子と、次端の第 2 出力端子から出力された前記第 1 ステージ駆動信号の入力を受ける制御端子と、を含んで構成されることを特徴とする請求項 1 記載の表示装置。10

【請求項 9】

前記第 2 ゲート駆動部は、

第 2 クロック信号の入力を受けるクロック信号端子と、前記第 2 クロック信号を前記第 1 ゲート駆動信号として出力する第 1 出力端子と、前記第 1 クロック信号を第 1 ステージ駆動信号として出力する第 2 出力端子と、以前端の第 2 出力端子から出力された前記第 1 ステージ駆動信号の入力を受ける入力端子と、次端の第 2 出力端子から出力された前記第 1 ステージ駆動信号の入力を受ける制御端子と、を含んで構成された複数のステージが従属的に連結されたシフトレジストで構成されることを特徴とする請求項 1 記載の表示装置。20

【請求項 10】

前記表示パネルは、表示領域と、

前記表示領域の周辺に形成された第 1 、第 2 及び第 3 周辺領域と、を含み、

前記第 1 ゲート駆動部は前記第 1 周辺領域に集積されて形成され、

前記第 2 ゲート駆動部は前記第 2 周辺領域に集積されて形成されることを特徴とする請求項 1 記載の表示装置。

【発明の詳細な説明】

【技術分野】

30

【0001】

本発明は表示装置に関し、より詳細には表示特性を向上させることができ、データラインの数を減少させることができる表示装置に関する。

【背景技術】

【0002】

一般に、液晶表示装置は映像を表示するための液晶表示パネルを具備する。液晶表示パネルは、表示領域と、表示領域の周辺に形成された第 1 乃至第 3 周辺領域とで構成される。表示領域には、第 1 方向に延伸された複数のゲートラインと、第 1 方向と直交する第 2 方向に延伸された複数のデータラインと、が具備される。それぞれのゲートライン及びデータラインには薄膜トランジスタが連結される。40

【0003】

最近、液晶表示パネルのサイズが漸次増加することにより、表示領域に形成されるデータライン及びゲートラインの数も漸次増加される。このように、ゲートラインの数が増加されることにより、液晶表示装置の前記第 1 及び第 2 周辺領域にそれぞれ第 1 及び第 2 ゲート駆動部を具備する構造が採用されている。即ち、前記第 1 ゲート駆動部は複数のゲートラインのうち奇数番目ゲートラインに第 1 ゲート駆動信号を順次出し、前記第 2 ゲート駆動部は複数のゲートラインのうち偶数番目のゲートラインに第 2 ゲート駆動信号を順次出力する。

このように、液晶表示装置は、前記複数のゲートラインを駆動するために第 1 及び第 2 ゲート駆動部を第 1 及び第 2 周辺領域にそれぞれ設けることで、ゲートラインに印加され

50

る信号が遅延する現象を防止することができる。

【発明の開示】

【発明が解決しようとする課題】

【0004】

一方、第3周辺領域には、複数のデータラインに映像信号を出力するためのデータ駆動チップが実装される。このとき、前記データ駆動チップに連結された複数のデータラインの数が増加されるに従い、前記データ駆動チップに掛かる負荷が増加して映像信号が遅延する現象が発生する。このような信号遅延現象は、液晶表示装置の表示特性を低下させる要因として作用する。

【0005】

従って、本発明は表示特性を向上させるための表示装置を提供する。

【課題を解決するための手段】

【0006】

本発明による表示装置は第1ゲートライン、前記第1ゲートラインと隣接する第2ゲートライン及び第1データラインに連結された第1画素、前記第1ゲートラインと前記第1データラインに連結された第2画素及び前記第1データラインと隣接する第2データラインと前記第1ゲートラインに連結された第3画素で構成された複数の画素群が具備された表示パネルを含む。

【0007】

第1ゲート駆動部は前記第1ゲートラインに第1ゲート駆動信号を出力し、第2ゲート駆動部は前記第2ゲートラインに第2ゲート駆動信号を出力する。データ駆動部は映像信号を発生して前記第1及び第2データラインに提供する。

【0008】

このような表示装置によると、前記表示パネルには複数の画素群が具備され、前記複数の画素群はR、G、B色画素パターン通りに反復できるよう第1乃至第3画素からなる。また、前記第1及び第2画素は一つのデータラインに共通的に連結される。従って、表示装置の表示特性を向上させるだけではなく、表示パネルに形成されたデータラインの数を減少させることができる。

【0009】

前記第1画素は、以下の要素を含むことが好ましい。

- ・第1画素電極、

- ・前記第2ゲートラインに連結されたゲート電極、前記第1データラインに連結されたソース電極、及びドレーン電極を有する第1トランジスタ、

- ・前記第1ゲートラインに連結されたゲート電極、前記第1トランジスタのドレーン電極に連結されたソース電極、及び前記第1画素電極と結合されたドレーン電極を有する第2トランジスタ。

【0010】

前記第1ゲート駆動信号は、前記第1ゲートラインに連結された以前端の前記第1画素及び第2画素を駆動するための第1区間、前記第1ゲートラインに連結された現在端の前記第1画素乃至第3画素を駆動するための第2区間を有していることが好適である。同様に、前記第2ゲート駆動信号は、前記第2ゲートラインに連結された以前端の前記第1画素及び第2画素を駆動するための第3区間、及び前記第2ゲートラインに連結された現在端の前記第1画素乃至第3画素を駆動するための第4区間を有することが好適である。

【0011】

前記第2画素は、以下の要素を含むことが好ましい。

- ・第2画素電極、

- ・前記第1ゲートラインに連結されたゲート電極、前記第1データラインに連結されたソース電極、及びドレーン電極を有する第3トランジスタ、

- ・前記第1ゲートラインに連結されたゲート電極、前記第3トランジスタのドレーン電極に連結されたソース電極、及び前記第2画素電極と結合されたドレーン電極を有する第4

10

20

30

40

50

トランジスタ。

【0012】

前記第1区間及び第3区間は、前記第1トランジスタをターンオンさせて前記第1画素電極に前記映像信号を出力するための第5区間、及び前記第1トランジスタをターンオフさせて前記第2画素電極に前記映像信号を出力するための第6区間で構成されることが好適である。

【0013】

前記第3画素は、以下の要素を含むことが好ましい。

- ・第3画素電極、

- ・前記第1ゲートラインに連結されたゲート電極、前記第2データラインに連結されたソース電極、及びドレーン電極を有する第5トランジスタ、10

- ・前記第1ゲートラインに連結されたゲート電極、前記第5トランジスタのドレーン電極に連結されたソース電極、及び前記第3画素電極と結合されたドレーン電極を有する第6トランジスタ。

【0014】

前記表示パネルは、前記第1画素乃至第3画素にそれぞれ対応するR(Red)、G(Green)、B(Blue)色画素を更に含むことが好適である。

【0015】

前記第1ゲート駆動部は、好ましくは以下の要素を含んで構成された複数のステージが従属的に連結されたシフトレジストで構成される。20

- ・第1クロック信号の入力を受けるクロック信号端子、

- ・前記第1クロック信号を前記第1ゲート駆動信号として出力する第1出力端子、

- ・前記第1クロック信号を第1ステージ駆動信号として出力する第2出力端子、

- ・以前端の第2出力端子から出力された前記第1ステージ駆動信号の入力を受ける入力端子、

- ・次端の第2出力端子から出力された前記第1ステージ駆動信号の入力を受ける制御端子。

【0016】

同様に、前記第2ゲート駆動部は、以下の要素を含むことが好ましい。

- ・第2クロック信号の入力を受けるクロック信号端子、30

- ・前記第2クロック信号を前記第1ゲート駆動信号として出力する第1出力端子、

- ・前記第1クロック信号を第1ステージ駆動信号として出力する第2出力端子、

- ・以前端の第2出力端子から出力された前記第1ステージ駆動信号の入力を受ける入力端子、

- ・次端の第2出力端子から出力された前記第1ステージ駆動信号の入力を受ける制御端子。

【0017】

前記表示パネルは、表示領域と、前記表示領域の周辺に形成された第1、第2及び第3周辺領域と、を含んでいいるとよい。このとき、前記第1ゲート駆動部は前記第1周辺領域に集積されて形成され、前記第2ゲート駆動部は前記第2周辺領域に集積されて形成されることが好ましい。40

【発明を実施するための最良の形態】

【0018】

以下、図面を参照して本発明の望ましい一実施例をより詳細に説明する。

【0019】

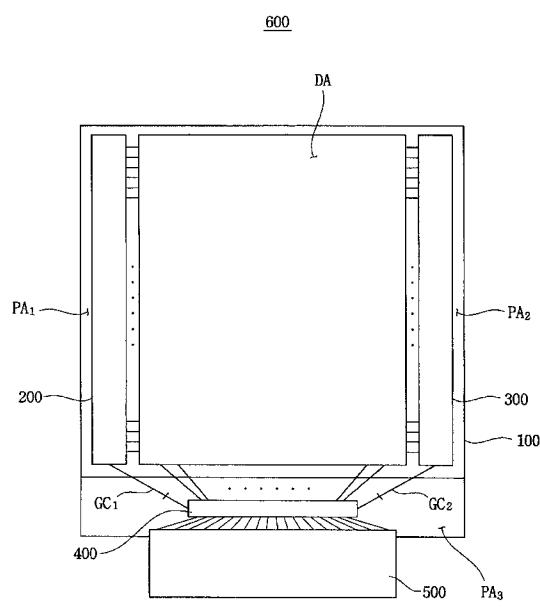

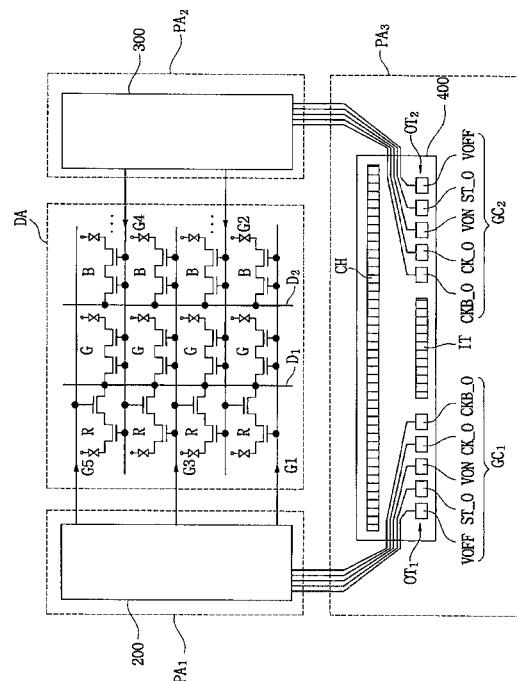

図1は本発明の一実施例による液晶表示装置を示す平面図である。

【0020】

図1に示すように、本発明の一実施例による液晶表示装置600は映像を表示するための表示領域DA、前記表示領域DAの周辺に形成された第1乃至第3周辺領域PA1、PA2、PA3を有する液晶表示パネル100を含む。第1ゲート駆動部200は前記第1

周辺領域 P A 1 に具備され、第 2 ゲート駆動部 3 0 0 は前記第 2 周辺領域 P A 2 に具備される。一方、前記第 3 周辺領域 P A 3 には統合チップ 4 0 0 が実装される。

### 【 0 0 2 1 】

前記液晶表示パネル 1 0 0 の前記第 3 周辺領域 P A 3 にはフレキシブル回路基板 5 0 0 が付着されている。前記フレキシブル回路基板 5 0 0 は、前記液晶表示パネル 1 0 0 の外部に具備される装置から各種信号の入力を受けて前記統合チップ 4 0 0 に提供する。前記統合チップ 4 0 0 は前記各種信号を変換して前記第 1 及び第 2 ゲート駆動部 2 0 0 , 3 0 0 の駆動を制御するための第 1 及び第 2 制御信号 G C 1 、 G C 2 を出力する。前記第 1 ゲート駆動部 2 0 0 は、前記第 1 制御信号 G C 1 により駆動され、前記表示領域 D A に複数の第 1 ゲート駆動信号を出力する。前記第 2 ゲート駆動部 3 0 0 は、前記第 2 制御信号 G C 2 によって駆動され、前記表示領域 D A に複数の第 2 ゲート駆動信号を出力する。また、前記統合チップ 4 0 0 は前記表示領域 D A に映像信号を出力する。

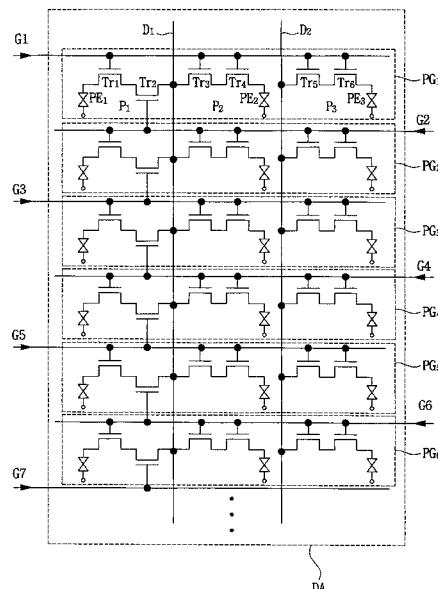

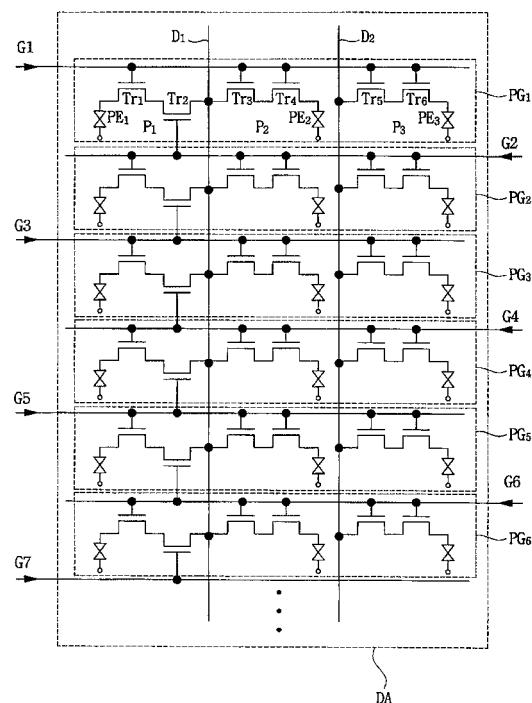

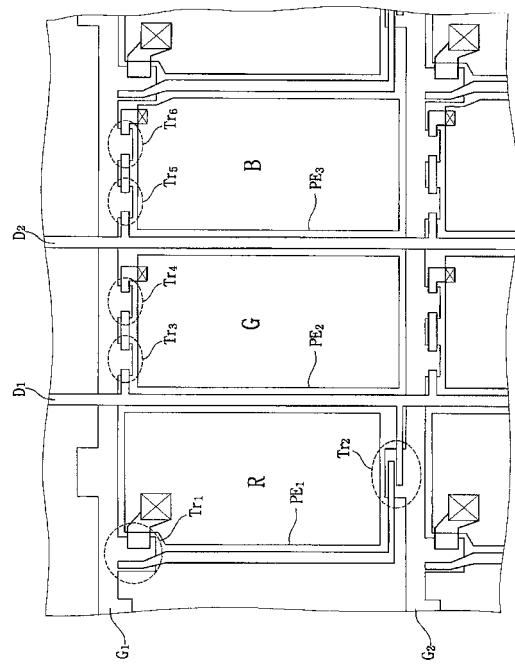

図 2 は図 1 に示された表示領域の内部構成を具体的に示す図面である。図 3 は図 1 に示された第 1 及び第 2 ゲート駆動部の内部構成を具体的に示す図面である。図 4 は図 2 に示された表示領域の構成を具体的に示すレイアウト図面である。表示領域 D A には複数の画素群 P G 1 、 P G 2 、 P G 3 、 P G 4 、 P G 5 、 P G 6 · · · が形成される。ここで、前記複数の画素群 P G 1 、 P G 2 、 P G 3 、 P G 4 、 P G 5 、 P G 6 · · · のそれぞれは同一の構造を有する。従って、前記複数の画素群 P G 1 、 P G 2 、 P G 3 、 P G 4 、 P G 5 、 P G 6 · · · のうちの一つである第 1 画素群 P G 1 に対して説明することで、複数の画素群 P G 1 、 P G 2 、 P G 3 、 P G 4 、 P G 5 、 P G 6 · · · に対する説明に代る。

図 2 及び図 4 に示すように、第 1 画素群 P G 1 は第 1 及び第 2 ゲートライン ( G 1 、 G 2 ) 、第 1 及び第 2 データライン ( D 1 、 D 2 ) 、第 1 乃至第 3 画素 ( P 1 、 P 2 、 P 3 ) を含む。前記第 1 ゲートライン G 1 は第 1 方向 A 1 に延伸され、前記第 2 ゲートライン G 2 は前記第 1 ゲートライン G 1 と絶縁された状態で前記第 1 方向 A 1 に延伸される。前記第 1 データライン D 1 は前記第 1 方向 A 1 と直交する第 2 方向 A 2 に延伸され、前記第 2 データライン D 2 は前記第 1 データライン D 1 と絶縁された状態で前記第 2 方向 A 2 に延伸される。

前記第 1 乃至第 3 画素 P 1 ~ P 3 はレッド、グリーン、ブルー色画素にそれぞれ対応する。前記第 1 画素 P 1 は、前記第 1 データライン D 1 、前記第 1 及び第 2 ゲートライン G 1 、 G 2 に連結されている。前記第 2 画素 P 2 は、前記第 1 ゲートライン G 1 及び第 1 データライン D 1 に連結されている。前記第 3 画素 P 3 は、前記第 1 ゲートライン G 1 及び第 2 データライン D 2 に連結される。

### 【 0 0 2 2 】

前記第 1 画素 P 1 は、第 1 薄膜トランジスタ（以下、TFT と称する）( T r 1 ) 、第 2 TFT ( T r 2 ) 及び第 1 画素電極 P E 1 で構成される。前記第 2 TFT ( T r 2 ) は、前記第 2 ゲートライン G 2 に連結されたゲート電極、前記第 1 データライン D 1 に連結されたソース電極及び前記第 1 TFT ( T r 1 ) に連結されたドレーン電極を有する。また、前記第 1 TFT ( T r 1 ) は、前記第 1 ゲートライン G 1 に連結されたゲート電極、前記第 2 TFT ( T r 2 ) のドレーン電極と連結されたソース電極及び前記第 1 画素電極 P E 1 に結合されたドレーン電極を有する。

一方、前記第 2 画素 P 2 は、第 3 TFT ( T r 3 ) 、第 4 TFT ( T r 4 ) 及び第 2 画素電極 P E 2 で構成される。前記第 3 TFT ( T r 3 ) は、前記第 1 ゲートライン G 1 に連結されたゲート電極、前記第 4 TFT ( T r 4 ) は、前記第 1 ゲートライン G 1 に連結されたソース電極及び前記第 4 画素電極 P E 2 に結合されたドレーン電極を有する。

前記第 3 画素 P 3 は、第 5 TFT ( T r 5 ) 、第 6 TFT ( T r 6 ) 及び第 3 画素電極 P E 3 で構成される。前記第 5 TFT ( T r 5 ) は、前記第 1 ゲートライン G 1 に連結さ

10

20

30

40

50

れたゲート電極、前記第2データラインD2に連結されたソース電極及び前記第6TFT(T<sub>r</sub>6)に連結されたドレーン電極を有する。また、前記第6TFT(T<sub>r</sub>6)は、前記第1ゲートラインG1に連結されたゲート電極、前記第5TFT(T<sub>r</sub>5)のドレーン電極に連結されたソース電極及び前記第3画素電極P<sub>E</sub>3に結合されたドレーン電極を有する。

前述した構造を有する第1画素群PG1が前記表示領域DA内に複数で形成されることで、前記表示領域DAには複数のゲートライン及び複数のデータラインが具備される。しかし、前記第1画素群PG1が含む第1乃至第3画素P1～P3それぞれに前記データラインが連結される従来の技術とは違って、図2に提示された本発明の一実施例では前記第1及び第2画素P1、P2に前記第1データラインD1が共通的に連結される。従って、前記第1画素群PG1内には2つのデータラインが具備される。それによって、前記表示領域DA内に具備される全体的な複数のデータラインの数を節減することができる。10

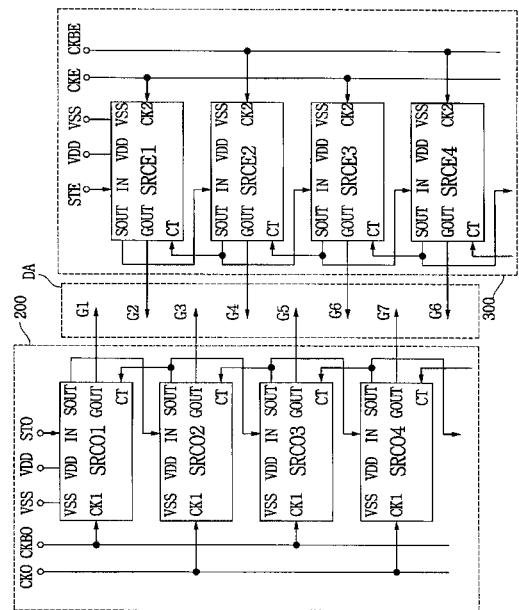

図3に示すように、第1ゲート駆動部200は、前記表示領域DA内に具備される複数のゲートラインのうち奇数番目ゲートラインG1、G3、G5、G7の第1端部に連結されて複数の第1ゲート駆動信号を提供する。第2ゲート駆動部300は、前記複数のゲートラインのうち偶数番目ゲートラインG2、G4、G6の第2端部に連結されて複数の第2ゲート駆動信号を提供する。

#### 【0024】

前記第1ゲート駆動部200は、互いに従属的に連結された複数のステージSRCO1～SRCO4で構成された第1シフトレジスタを含む。前記第1シフトレジスタの各ステージは、入力端子IN、第1出力端子SOUT、第2出力端子SO<sub>UT</sub>、制御端子CT、第1クロック信号端子CK1、駆動電源電圧端子VDD、アース電圧端子VSSを具備する。20

前記第1出力端子GOUTは、前記奇数番目ゲートラインG1、G3、G5、G7・・・の第1端部に連結されて前記奇数番目ゲートラインG1、G3、G5、G7・・・に順次前記複数の第1ゲート駆動信号を出力する。前記第2出力端子SO<sub>UT</sub>は、以前ステージの制御端子CT及び次ステージの入力端子INにそれぞれ連結され、前記第1ゲート駆動信号と同一の位相を有する第1ステージの駆動信号を出力する。一方、前記複数のステージのうち一番目のステージSRCO1の入力端子INには第1開示信号STOが提供される。30

#### 【0025】

前記第1クロック信号端子CK1には、第1クロック信号CKOまたは前記第1クロック信号CKOと異なる位相を有する第2クロック信号CKBOが提供される。例えば、第2クロック信号CKBOは、第1クロック信号CKOと反転された位相を有する。即ち、前記第1クロック信号CKOは前記複数のステージのうち偶数番目ステージSRCO2、SRCO4に提供され、前記第2クロック信号CKBOは前記複数のステージのうち奇数番目ステージSRCO1、SRCO3に提供される。前記駆動電圧端子VDD及びアース電圧端子VSSにはそれぞれ駆動電圧及びアース電圧が提供される。

前記第2ゲート駆動部300は、互いに従属的に連結された複数のステージSRCE1～SRCER4で構成された第2シフトレジスタを含む。前記第2シフトレジスタの各ステージは、入力端子IN、第1出力端子GOUT、第2出力端子SO<sub>UT</sub>、制御端子CT、第2クロック信号端子CK2、駆動電源電圧端子VDD、アース電圧端子VSSを具備する。40

前記第1出力端子GOUTは、前記偶数番目ゲートラインG2、G4、G6・・・の第2端部に連結され、前記偶数番目ゲートラインG2、G4、G6・・・に前記複数の第2ゲート駆動信号を順次出力する。前記第2出力端子SO<sub>UT</sub>は、以前ステージの制御端子CT及び次ステージの入力端子INにそれぞれ連結され、前記第2ゲート駆動信号と同一の位相を有する第2ステージ駆動信号を出力する。一方、前記複数のステージのうち一番目のステージSRCER1の入力端子には、第2開示信号STEが提供される。

#### 【0026】

10

20

30

40

50

前記第2クロック信号端子CK2には、第3クロック信号CKEまたは前記第3クロック信号CKEと異なる位相を有する第4クロック信号が提供される。例えば、第4クロック信号CKBEは、第3クロック信号CKEと反転された位相を有する。即ち、前記第3クロック信号CKEは、前記複数のステージのうち奇数番目ステージSRC E1、SRC E3に提供され、前記第4クロック信号CKBEは、前記複数のステージのうち偶数番目ステージSRC E2、SRC E4に提供される。前記駆動電圧端子VDD及びアース電圧端子VSSにはそれぞれ前記駆動電圧及びアース電圧が提供される。

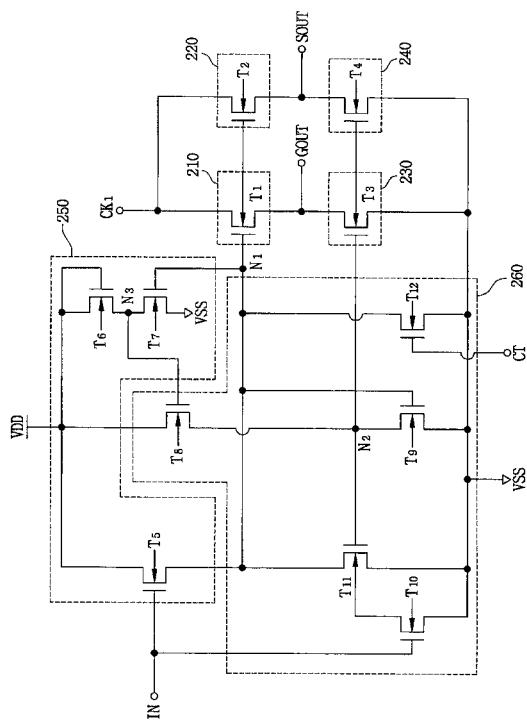

図5は、図3に提示された各ステージの内部構成を具体的に示す回路図である。但し、第1シフトレジスタの各ステージの内部構成を説明することで、これと類似する構成を有する第2シフトレジスタの各ステージの内部構成に対する説明を省略する。

10

#### 【0027】

図3及び図5に示すように、各ステージは第1プルアップ部210、第2プルアップ部220、第1プルダウン部230、第2プルダウン部240、プルアップ駆動部250及びプルダウン駆動部260を含む。

#### 【0028】

前記第1プルアップ部210は第1クロック信号端子CK1に提供される第1または第2クロック信号CKO、CKBOをゲート駆動信号として前記第1出力端子GOUTに出力し、前記第2プルアップ220は前記第1クロック信号端子CK1に提供される第1または第2クロック信号CKO、CKBOをステージ駆動信号として前記第2出力端子SOUTに出力する。

20

前記第1プルアップ210は、ゲート電極が第1ノードN1に連結され、ソース電極が前記第1クロック信号端子CK1に連結され、ドレーン電極が前記第1出力端子GOUTに連結された第1NMOSトランジスタT1で構成される。前記第2プルアップ部220は、ゲート電極が第1ノードN1に連結され、ソース電極が前記第1クロック信号端子CK1に連結され、ドレーン電極が前記第2出力端子SOUTに連結された第2NMOSトランジスタT2で構成される。

#### 【0029】

例えば、前記第1及び第2NMOSトランジスタT1、T2のチャンネル長さは3.5μmで固定される。例えば、前記第1NMOSトランジスタT1のチャンネル幅は1110μmで、前記第2NMOSトランジスタT2のチャンネル幅は前記第1NMOSトランジスタT1のチャンネル幅より約1/10倍小さい100μmである。

30

前記第1プルダウン部230は第1プルアップ部210がターンオフされて前記第1出力端子GOUTから出力される前記第1または第2クロック信号を放電させ、前記第2プルダウン部240は前記プルアップ部220がターンオフされた以後にターンオンされて前記第2出力端子SOUTから出力される前記第1及び第2クロック信号CKO、CKBOを放電させる。

#### 【0030】

前記第1プルダウン部230はゲート電極が第2ノードN2に連結され、ドレーン電極が前記第1出力端子GOUTに連結され、ソース電極がアース電圧端子VSSに連結された第3NMOSトランジスタT3で構成される。前記第2プルダウン部240はゲート電極が前記第2ノードN2に連結され、ドレーン電極が前記第2出力端子SOUTに連結され、ソース電極が前記アース電圧端子VSSに連結された第4NMOSトランジスタT4で構成される。

40

例えば、前記第3及び第4NMOSトランジスタT3、T4のチャンネル長さは3.5μmで固定される。例えば、前記第3NMOSトランジスタT3のチャンネル幅は2035μmで、前記第4NMOSトランジスタT4のチャンネル幅は前記第3NMOSトランジスタT3のチャンネル幅より約1/20倍小さい100μmである。

#### 【0031】

前記プルアップ駆動部250第5乃至第7NMOSトランジスタT5、T6、T7で構成されて前記第1及び第2プルアップ部351、352はターンオンさせるように制御す

50

る。

【0032】

前記第5N MOSトランジスタT5は、ゲート電極が前記入力端子INに連結され、ドレーン電極が駆動電圧端子VDDに連結され、ソース電極が第1ノードN1に連結される。前記第6N MOSトランジスタT6は、前記ゲート電極とドレーン電極が前記駆動電圧端子VDDに連結され、ソース電極が第3ノードN3に連結される。前記第7N MOSトランジスタT7はゲート電極が前記第1ノードN1に連結され、ドレーン電極が第3ノードN3に連結され、ソース電極がアース電圧端子VSSに連結される。

例えば、前記第5乃至第7N MOSトランジスタT5～T7のチャンネル長さは3.5μmで同一である。例えば、前記第5N MOSトランジスタT5のチャンネル幅は300μmであり、前記第6及び第7N MOSトランジスタT6、T7のチャンネル幅は50μmで互いに同一である。10

【0033】

前記プルダウン駆動部260は、第8及び第12N MOSトランジスタT8、T9、T10、T11、T12で構成されて前記第1及び第2プルアップ部210、220をターンオフさせ前記第1及び第2プルダウン部230、240をターンオンさせるように制御する。

【0034】

前記第8N MOSトランジスタT8はゲート電極が前記第3ノードN3に連結され、ドレーン電極が前記駆動電圧端子VDDに連結され、ソース電極が前記第2ノードN2に連結される。前記第9N MOSトランジスタT9はゲート電極が前記第1ノードN1に連結され、ドレーン電極が前記第2ノードN2に連結され、ソース電極が前記アース電圧端子VSSに連結される。前記第10N MOSトランジスタT10はゲート電極が前記入力端子INに連結され、ドレーン電極が前記第2ノードN2に連結され、ソース電極が前記アース電圧端子VSSに連結される。20

前記第11N MOSトランジスタT11はゲート電極が前記第2ノードN2に連結され、ドレーン電極が前記第1ノードN1に連結され、ソース電極が前記アース電圧端子VSSに連結される。前記第12N MOSトランジスタT12は、ゲート電極が前記制御端子CTに連結され、ドレーン電極が前記第1ノードN1に連結され、ソース電極が前記アース電圧端子VSSに連結される。30

【0035】

例えば、前記第8乃至第12N MOSトランジスタT8～T12のチャンネル長さは3.5μmで互いに同一である。例えば、前記第8及び第10N MOSトランジスタ(T8、T10)のチャンネル幅は100μmで互いに同一で、前記第9N MOSトランジスタT9のチャンネル幅は150μmである。また、前記第11N MOSトランジスタT11のチャンネル幅は100μmで、前記第12N MOSトランジスタT12のチャンネル幅は150μmである。

【0036】

前記入力端子INに、以前ステージの第2出力端子SOUTから出力された第1ステージ駆動信号が提供されると、前記第5N MOSトランジスタT5がターンオンされて前記第1ノードN1の電位が漸次上昇する。前記第1ノードN1の電位が上昇されることにより、前記第1N MOSトランジスタT1及び第2N MOSトランジスタT2がターンオンされて前記第1及び第2出力端子GOUT、SOUTには、第1ゲート駆動信号及び第1ステージ駆動信号がそれぞれ出力される。40

一方、前記第6N MOSトランジスタT6は、常にターンオン状態を維持している状態で、前記第1ノードN1の電位が上昇されることにより、前記第7N MOSトランジスタT7がターンオンされると、前記第3ノードN3の電位が下落される。

【0037】

前記第3ノードN3の電位が下落されることにより、前記第8N MOSトランジスタT8は、ターンオフ状態を維持する。従って、前記第2ノードN2には、前記駆動電圧VDD50

D が提供されない。又、前記第 9 NMOS トランジスタ T9 は、前記第 1 ノード N1 の電位が上昇する時にターンオンされて、前記第 2 ノード N2 の電位を前記アース電圧 VSS に維持させることにより、前記第 3 及び第 4 NMOS トランジスタ T3、T4 をターンオフさせる。

#### 【0038】

以後、前記制御端子 CT を通じて次端のステージの第 2 出力端子 SOUT から出力された第 1 ステージ駆動信号が提供されると、前記第 2 NMOS トランジスタ T12 がターンオンされて、前記第 1 ノード N1 の電位を前記アース電圧 VSS に放電させる。前記第 1 ノード N1 の電位が下落することにより、前記第 7 及び第 9 NMOS トランジスタ T7、T9 がターンオフされる。

10

#### 【0039】

従って、前記第 2 ノード N2 の電位が漸次上昇され、これにより、前記第 3 及び第 4 NMOS トランジスタ T3、T4 がターンオンされて、前記第 1 及び第 2 出力端子 GOUT、SOUT から出力された前記第 1 ゲート駆動信号をアース電圧 VSS に放電させる。

#### 【0040】

この際、前記第 10 及び第 11 NMOS トランジスタ T10、T11 は、前記第 2 ノード N2 の電位が上昇されるにつれターンオンされることにより、前記第 1 ノード N1 の電位を早く放電させる。このような過程を繰り返しながら、前記各ステージは、所定の区間の間、ハイ状態を維持する第 1 ゲート駆動信号及び第 1 ステージ駆動信号を出力する。

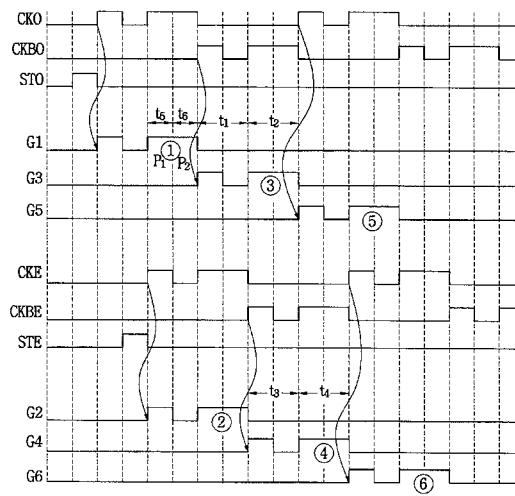

図 6 は、図 3 に図示された第 1 及び第 2 ゲート駆動部の出力波形図である。

20

#### 【0041】

図 2 乃至図 6 を参照すると、第 1 ゲート駆動部 200 の各ステージのうち、一番目ステージ SRCO1 の入力端子 IN に第 1 開示信号 STO が提供されると、前記各ステージ SRCO1 ~ SRCO4 には、第 1 又は第 2 クロック信号 CKO、CKBO、駆動電圧 VDD、及びアース電圧 VSS が印加される。

#### 【0042】

従って、前記入力端子 IN に、前記第 1 開示信号 STO が提供された後に、前記一番目ステージ SRCO1 がターンオンされながら、前記一番目ステージ SRCO1 の第 1 及び第 2 出力端子 GOUT、SOUT には、前記第 1 クロック信号 CKO が output される。前記第 1 クロック信号 CKO は、第 1 ゲートライン G1 に第 1 ゲート駆動信号として印加される。

30

#### 【0043】

その後、前記一番目ステージ SRCO1 がターンオフされる時点で、二番目ステージ SRCO2 がターンオンされて、前記二番目ステージ SRCO2 の第 1 及び第 2 出力端子 GOUT、SOUT では、前記第 2 クロック信号 CKBO が出力される。前記第 2 クロック信号 CKBO は、第 3 ゲートライン G3 に前記第 1 ゲート駆動信号として印加される。

#### 【0044】

次に、前記二番目ステージ SRCO2 がターンオフされる時点で三番目ステージ SRCO3 がターンオンされて、前記三番目ステージ SRCO3 の第 1 及び第 2 出力端子 GOUT、SOUT では、前記第 1 クロック信号 CKO が出力される。前記第 1 クロック信号 CKO は、第 5 ゲートライン G5 に前記第 1 ゲート駆動信号として印加される。

40

従って、前記第 1 ゲート駆動部 200 は、多数のゲートラインのうち、奇数番目ゲートライン G1、G3、G5 に順次前記第 1 ゲート駆動信号を出力することができる。

#### 【0045】

一方、第 2 ゲート駆動部 300 の各ステージのうち、一番目ステージ SRC E1 の入力端子 IN に第 2 開示信号 STE が提供されると、前記各ステージ SRC E1 ~ SRC E4 には、第 3 又は第 4 クロック信号 CKE、CKBE、駆動電圧 VDD、及びアース電圧 VSS が印加される。

#### 【0046】

従って、前記入力端子 IN に前記第 2 開示信号 STE が提供された以後に、前記一番目

50

ステージ S R C E 1 がターンオンされながら、前記一番目ステージ S R C E 1 の第 1 及び第 2 出力端子 G O U T 、 S O U T には、前記第 3 クロック信号 C K E が出力される。前記第 3 クロック信号 C K E は、第 2 ゲートライン G 2 に第 2 ゲート駆動信号として提供される。

#### 【 0 0 4 7 】

その後、前記一番目ステージ S R C E 1 がターンオフされる時点で、二番目ステージ S R C E 2 がターンオンされ、前記二番目ステージ S R C E 2 の第 1 及び第 2 出力端子 G O U T 、 S O U T では、前記第 4 クロック信号 C K B E が出力される。前記第 4 クロック信号 C K B E は、第 4 ゲートライン G 4 に前記第 2 ゲート駆動信号として提供される。

#### 【 0 0 4 8 】

次に、前記二番目ステージ S R C E 2 がターンオフされる時点で三番目ステージ S R C E 3 がターンオンされ、前記三番目ステージ S R C E 3 の第 1 及び第 2 出力端子 G O U T 、 S O U T では、前記第 3 クロック信号 C K E が出力される。前記第 3 クロック信号 C K E は、前記第 6 ゲートライン G 6 に前記第 2 ゲート駆動信号として提供される。

#### 【 0 0 4 9 】

従って、前記第 2 ゲート駆動部 3 0 0 は、多数のゲートラインのうち、偶数番目ゲートライン G 2 、 G 4 、 G 6 に順次前記第 2 ゲート駆動信号を出力することができる。

ここで、前記第 3 クロック信号 C K E は、前記第 1 クロック信号 C K O より 1 / 4 周期だけ遅延された位相を有し、前記第 4 クロック信号 C K B E は、前記第 2 クロック信号 C K B O より 1 / 4 周期だけ遅延された位相を有する。従って、前記奇数番目ゲートライン G 1 、 G 3 、 G 5 に印加される前記第 1 ゲート駆動信号も、前記偶数番目ゲートライン G 2 、 G 4 、 G 6 に印加される前記第 2 ゲート駆動信号と 1 / 4 周期だけ位相差が発生する。即ち、第 2 ゲートライン G 2 に印加される前記第 2 ゲート駆動信号が第 1 ゲートライン G 1 に印加される前記第 1 ゲート駆動信号より 1 / 4 周期だけ遅延される。

#### 【 0 0 5 0 】

前記第 1 画素 P 1 は、前記第 1 ゲートライン G 1 に連結された第 1 T F T ( T r 1 ) 、第 2 ゲートライン G 2 に連結された第 2 T F T ( T r 2 ) 、第 1 データライン D 1 及び前記第 1 T F T ( T r 1 ) に連結された第 1 画素電極 P E 1 で構成される。前記第 1 及び第 2 T F T ( T r 1 、 T r 2 ) が共にターンオンされる時、前記第 1 データライン D 1 から出力された映像信号が前記第 1 画素電極 P E 1 に印加されることができる。この際、前記第 1 及び第 2 T F T ( T r 1 、 T r 2 ) は、前記第 1 ゲートライン G 1 に印加された前記第 1 ゲート駆動信号と前記第 2 ゲートライン G 2 に印加される前記第 2 ゲート駆動信号とがそれぞれハイ状態を維持する時にターンオンされる。

#### 【 0 0 5 1 】

ここで、前記第 1 ゲート駆動信号は、前記奇数番目ゲートライン G 1 、 G 3 、 G 5 に連結された以前端の前記第 2 T F T ( T r 2 ) を駆動するための第 1 区間 t 1 、及び前記奇数番目ゲートライン G 1 、 G 3 、 G 5 に連結された現在端の前記第 1 T F T ( T r 1 ) を駆動するための第 2 区間 t 2 を有して発生される。又、前記第 2 ゲート駆動信号は、前記第 2 ゲートライン G 2 に連結された以前端の前記第 2 T F T ( T r 2 ) を駆動するための第 3 区間 t 3 及び前記第 2 ゲートライン G 2 に連結された現在端に前記第 1 T F T ( T r 1 ) を駆動するための第 4 区間 t 4 を有して発生される。

図 6 に示したように、前記第 1 ゲート駆動信号と前記第 2 ゲート駆動信号は、前記第 2 区間 t 2 と前記第 3 区間 t 3 が、互いにオーバーラップされるように発生される。前述したように、前記第 1 ゲート駆動信号は、前記第 2 区間 t 2 で前記第 1 T F T ( T r 1 ) をターンオンさせて、前記第 2 ゲート駆動信号は、前記第 3 区間 t 3 で前記第 2 T F T ( T r 2 ) をターンオンさせる。従って、前記第 1 データライン D 1 から出力された映像信号は、前記第 1 及び第 2 T F T ( T r 1 、 T r 2 ) を通過した後、前記第 1 画素電極 P E 1 に印加される。

#### 【 0 0 5 2 】

前記第 2 区間 t 2 は、前記第 1 データライン D 1 が前記第 1 画素 P 1 の前記第 1 画素電

10

20

30

40

50

極 P E 1 に映像信号を出力する第 5 区間  $t_5$ 、及び前記第 1 データライン D 1 が前記第 2 画素 P 2 の第 2 画素電極 P E 2 に映像信号を出力する第 6 区間  $t_6$  に区分される。即ち、前記第 5 区間  $t_5$  で前記第 1 TFT (Tr 1) がターンオンされるが、前記第 6 区間  $t_6$  では、前記第 2 ゲート駆動信号によって前記第 1 TFT (Tr 1) がターンオフ状態に変換される。従って、前記第 6 区間  $t_6$  で前記映像信号は、前記第 1 画素電極 P E 1 に提供されず、前記第 3 及び第 4 TFT (Tr 3、Tr 4) を通過した後、前記第 2 画素電極 P E 2 に提供される。

#### 【 0 0 5 3 】

このように、前記第 1 データライン D 1 に前記第 1 及び第 2 画素 P 1、P 2 が共通的に連結されても、前記第 1 データライン D 1 は、与えられた時間内に前記第 1 画素電極 P E 1 及び第 2 画素電極 P E 2 にそれぞれ映像信号を出力することができる。10

#### 【 0 0 5 4 】

これにより、前記奇数番目ゲートライン G 1、G 3、G 5 に連結された画素群と、偶数番目ゲートライン G 2、G 4、G 6 に連結された画素群が、互いに交互に駆動することができる。

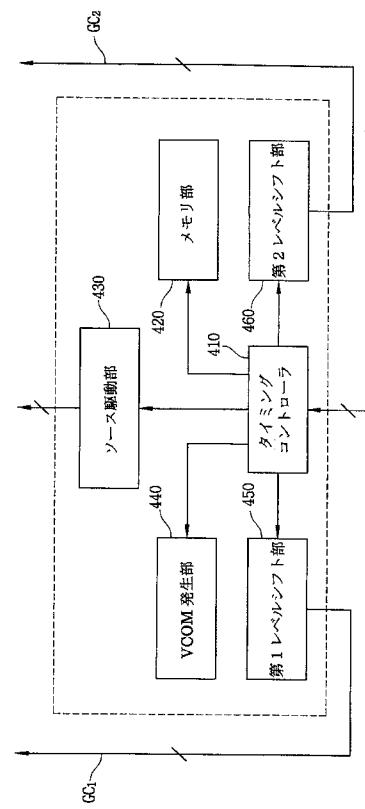

図 7 は、図 1 に図示された通合チップと、第 1 及び第 2 ゲート駆動部の連結関係を具体的に示した図であり、図 8 は、図 7 に図示された通合チップの内部ブロック図である。

#### 【 0 0 5 5 】

図 7 を参照すると、表示領域 D A には多数の画素群が具備され、第 1 及び第 2 周辺領域 P A 1、P A 2 には第 1 及び第 2 ゲート駆動部 2 0 0、3 0 0 がそれぞれ具備され、第 3 周辺領域 P A 3 には通合チップ 4 0 0 が実装される。前記通合チップ 4 0 0 は、外部から各種信号の入力を受ける入力端子 I T、前記表示領域 D A に具備された多数のデータラインに映像信号を出力するためのチャンネル端子 C H、前記第 1 ゲート駆動部 2 0 0 に第 1 制御信号 G C 1 を出力する第 1 出力端子 O T 1、及び前記第 2 ゲート駆動部 3 0 0 に第 2 制御信号 G C 2 を出力する第 2 出力端子 O T 2 で構成される。20

図 7 及び図 8 に示したように、前記通合チップ 4 0 0 は、タイミングコントローラ 4 1 0、メモリ部 4 2 0、ソース駆動部 4 3 0、共通電圧 V c o m 発生部 4 4 0、第 1 及び第 2 レベルシフト部 4 5 0、4 6 0 を含む。前記入力端子 I T を通じて各種信号が前記タイミングコントローラ 4 1 0 に提供される。ここで、前記タイミングコントローラ 4 1 0 は、外部映像信号及び外部制御信号の入力を受け、前記外部映像信号を前記メモリ部 4 2 0 に貯蔵する。一方、前記外部制御信号は、水平及び垂直同期信号、メインクロック信号、データイネイブル信号及びモード選択信号を含む。30

#### 【 0 0 5 6 】

又、前記タイミングコントローラ 4 1 0 は、前記第 1 レベルシフト部 4 5 0 に第 1 制御信号 G C 1 を提供し、前記第 2 レベルシフト部 4 6 0 に第 2 制御信号 G C 2 を提供する。この際、前記第 1 制御信号 G C 1 は、第 1 開示信号 S T O、第 1 クロック信号 C K O、第 2 クロック信号 C K B O、電源電圧 V S S、及び駆動電圧 V D D を含む。又、前記第 2 制御信号 G C 2 は、第 2 開示信号 S T E、第 3 クロック信号 C K E、第 4 クロック信号 C B K E、前記電源電圧 V S S、及び駆動電圧 V D D を含む。

前記タイミングコントローラ 4 1 0 は、前記メモリ部 4 2 0 に貯蔵された前記外部映像信号をブロック単位に出力して前記ソース駆動部 4 3 0 に提供する。40

#### 【 0 0 5 7 】

前記メモリ部 4 2 0 は、前記タイミングコントローラ 4 1 0 から提供された前記外部映像信号を一時的に貯蔵する。この際、前記メモリ部 4 2 0 は、前記外部映像信号をフレーム (frame) 又はライン (line) 単位に貯蔵する。

#### 【 0 0 5 8 】

前記ソース駆動部 4 3 0 は、前記メモリ部 4 2 0 から読み出されたブロック単位の前記外部映像信号の入力を受けて、アナログ信号に変換した後、ブロック単位に出力する。この際、前記ソース駆動部 4 3 0 の出力端子、即ち、前記チャンネル端子 C H は、複数のデータラインと連結され、前記多数のデータラインに前記アナログ映像信号を提供する。50

## 【0059】

前記第1レベルシフト部450は、前記タイミングコントローラ410から提供された前記第1制御信号G C 1の電圧レベルをシフティングして出力し、前記第2レベルシフト部460は、前記タイミングコントローラ410から提供された前記第2制御信号G C 2の電圧レベルをシフティングして出力する。従って、前記第1レベルシフト部450は、レベルがシフティングされた第1開示信号S T O、第1クロック信号C K O、第2クロック信号C K B O、アース電圧V S S、及び駆動電圧V D Dを出力する。又、前記第2レベルシフト部460は、レベルがシフティングされた第2開示信号S T E、第3クロック信号C K E、第4クロック信号C K B E、アース電圧V S S、及び駆動電圧V D Dを出力する。

10

## 【0060】

前記第1ゲート駆動部200は、レベルシフティングされた前記第1制御信号G C 1に応答して前記奇数番目ゲートラインG 1、G 3、G 5に第1ゲート駆動信号を順次出力し、前記第2ゲート駆動部300は、レベルシフティングされた前記第2制御信号G C 2に応答して、前記偶数番目ゲートラインG 2、G 4に第2ゲート駆動信号を順次出力する。

## 【0061】

前記共通電圧発生部440は、前記液晶層の電圧維持率を高めるために、液晶層と並列に形成された共通電極ライン(図示せず)に共通電圧V c o mを印加する。

## 【産業上の利用可能性】

## 【0062】

20

このような液晶表示装置によると、前記液晶表示パネルには多数の画素群が具備され、前記多数の画素群はR、G、B色画素パターンが反復されるように、第1乃至第3画素で構成される。従って、液晶表示装置の表示特性を向上させることができる。

## 【0063】

又、前記第1及び第2画素は、一つのデータラインに共通的に連結される。従って、前記データラインは、前記第1及び第2画素に連結されたゲートラインにゲート駆動信号が印加される時間を分割して前記第1画素及び第2画素に順次映像信号を出力する。その結果、液晶表示パネルに形成されたデータラインの数を減少させることができる。

## 【0064】

以上、本発明の実施例によって詳細に説明したが、本発明はこれに限定されず、本発明が属する技術分野において通常の知識を有するものであれば本発明の思想と精神を離れることなく、本発明を修正または変更できる。

30

## 【図面の簡単な説明】

## 【0065】

【図1】本発明の一実施例による液晶表示装置を示す平面図である。

【図2】図1に示された表示領域の内部構成を具体的に示す図である。

【図3】図1に示された第1及び第2ゲート駆動部の内部構成を具体的に示す図面である。

【図4】図2に示された表示領域の構成を具体的に示すレイアウト図面である。

40

【図5】図3に提示された各ステージの内部構成を具体的に示す回路図である。

【図6】図3に示された第1及び第2ゲート駆動部の出力波形図である。

【図7】図1に示された統合チップと第1と第2ゲート駆動部との連結関係を具体的に示す図面である。

【図8】図7に示された統合チップの内部ブロック図である。

## 【符号の説明】

## 【0066】

100 液晶表示パネル

200 第1ゲート駆動部

300 第2ゲート駆動部

400 統合チップ

50

5 0 0 フレキシブル回路基板

6 0 0 液晶表示装置

P G I 第 1 画素群

P 1 第 1 画素

P 2 第 2 画素

P 3 第 3 画素

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

H 01L 29/78 612C

H 01L 29/78 614

F ターム(参考) 2H092 GA20 GA24 GA32 HA02 HA06 JA24 JB21 NA25 PA06

2H093 NA16 NC09 NC11 NC34 ND37 ND50 NE03

5F110 AA01 AA28 BB02 GG28 GG29 NN72 NN78

【要約の続き】

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2004334216A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 公开(公告)日 | 2004-11-25 |

| 申请号            | JP2004137754                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 申请日     | 2004-05-06 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| [标]发明人         | 金炯傑<br>全珍                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 金炯傑<br>全珍                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号         | G02F1/133 G02F1/1343 G02F1/1345 G02F1/1362 G02F1/1368 G09G3/36 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| CPC分类号         | G02F1/136286 G09G3/20 G09G3/3648 G09G3/3659 G09G3/3677 G09G3/3688 G09G2300/0426 G09G2300/0814 G09G2310/0289 G09G2310/08 G11C19/28                                                                                                                                                                                                                                                                                                                                             |         |            |

| F1分类号          | G02F1/1343 G02F1/133.505 G02F1/133.550 G02F1/1345 G02F1/1368 H01L29/78.612.C H01L29/78.614 G11C19/00 G11C19/00.J G11C19/28.D G11C19/28.230                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 2H092/GA20 2H092/GA24 2H092/GA32 2H092/HA02 2H092/HA06 2H092/JA24 2H092/JB21 2H092/NA25 2H092/PA06 2H093/NA16 2H093/NC09 2H093/NC11 2H093/NC34 2H093/ND37 2H093/ND50 2H093/NE03 5F110/AA01 5F110/AA28 5F110/BB02 5F110/GG28 5F110/GG29 5F110/NN72 5F110/NN78 2H192/AA24 2H192/CB13 2H192/CC22 2H192/CC62 2H192/FA44 2H192/FA73 2H192/FB22 2H192/FB25 2H192/FB27 2H192/FB32 2H192/GD61 2H193/ZA04 2H193/ZA08 2H193/ZA19 2H193/ZF24 2H193/ZP03 5B074/AA10 5B074/CA01 5B074/EA01 |         |            |

| 优先权            | 1020030028650 2003-05-06 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 其他公开文献         | <a href="#">JP4630570B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

### 摘要(译)

提供一种能够改善显示特性的液晶显示装置。[解决方案] 液晶显示面板包括连接到第一栅极线，第二栅极线和第一数据线的第一像素，连接到第一栅极线和第一数据线的第二像素，第二数据线和连接到第一数据线的第二像素。提供多个像素组，每个像素组包括连接到一条栅极线的第三像素。第一栅极驱动器将第一栅极驱动信号输出至第一栅极线，第二栅极驱动器将第二栅极驱动信号输出至第二栅极线。数据驱动器产生视频信号，并将其提供给第一和第二数据线。因此，可以改善液晶显示装置的显示特性，并且可以减少形成在液晶显示面板上的数据线的数量。

[选择图] 图2