(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4668893号

(P4668893)

(45) 発行日 平成23年4月13日(2011.4.13)

(24) 登録日 平成23年1月21日(2011.1.21)

(51) Int.CI.

F 1

G02F 1/1368 (2006.01)

G02F 1/1368

H01L 29/786 (2006.01)

H01L 29/78 612D

H01L 21/336 (2006.01)

H01L 29/78 627C

請求項の数 19 (全 27 頁)

(21) 出願番号 特願2006-353326 (P2006-353326)

(22) 出願日 平成18年12月27日 (2006.12.27)

(65) 公開番号 特開2008-9372 (P2008-9372A)

(43) 公開日 平成20年1月17日 (2008.1.17)

審査請求日 平成18年12月27日 (2006.12.27)

(31) 優先権主張番号 10-2006-0059346

(32) 優先日 平成18年6月29日 (2006.6.29)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 501426046

エルジー ディスプレイ カンパニー リ

ミテッド

大韓民国 ソウル, ヨンドゥンパーク, ヨ

イドードン 20

(74) 代理人 100110423

弁理士 曽我 道治

(74) 代理人 100084010

弁理士 古川 秀利

(74) 代理人 100094695

弁理士 鈴木 憲七

(74) 代理人 100111648

弁理士 梶並 順

(74) 代理人 100147566

弁理士 上田 俊一

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲート配線と；

前記ゲート配線に連結されたゲート電極と；

前記ゲート配線及び前記ゲート電極上に位置するゲート絶縁膜と；

前記ゲート絶縁膜上に位置し、前記ゲート電極と重畳するアクティブ層と；

前記アクティブ層から延長されて、前記ゲート絶縁膜上に位置し、前記ゲート配線と重畳する半導体層と；

前記アクティブ層上に位置し、互いに離隔する第1及び第2オーミックコンタクト層と；

前記第1及び第2オーミックコンタクト層上にそれぞれ互いに離隔して位置することにより、前記アクティブ層の一部を露出させる第1ソース電極及び第1ドレイン電極と；

前記第1ソース電極及び第1ドレイン電極と前記アクティブ層の露出された一部上に位置し、前記第1ソース電極及び第1ドレイン電極それぞれを露出させる第1及び第2コンタクトホールを含み、前記ゲート配線及びゲート電極の側面を覆う保護膜と；

前記保護膜上に位置し、それぞれが透明導電性物質でなる第1層と不透明金属物質でなる第2層を含み、前記第1及び第2コンタクトホールを通じて前記第1ソース電極及び第1ドレイン電極と接触する第2ソース電極及び第2ドレイン電極と；

前記第2ソース電極の第1層及び第2層から延長されて、前記保護膜上に位置し、前記ゲート配線と交差して画素領域を定義するデータ配線と；

10

20

前記画素領域に位置して、前記第2ドレイン電極の第1層から延長されて、前記保護膜上に位置する画素電極と；

を含み、

前記ゲート絶縁膜は、前記ゲート配線及びゲート電極と同一の外郭を有し、

前記半導体層及びアクティブ層それぞれは、前記ゲート配線及びゲート電極と同一の外郭を有する

ことを特徴とする液晶表示装置。

【請求項2】

前記ゲート電極は、アクティブ層と平面的に同一な面積を有し完全に重畳することを特徴とする請求項1に記載の液晶表示装置。 10

【請求項3】

前記オームイックコンタクト層は、前記第1ソース電極及び前記第1ドレイン電極と同一の外郭を有することを特徴とする請求項1に記載の液晶表示装置。

【請求項4】

前記第1層は、インジウム-スズ-オキサイドITO、インジウム-ジンク-オキサイドIZO、インジウム-スズ-ジンク-オキサイドITZOの少なくとも一つを含み、前記第2層は、アルミニウムAl、アルミニウム合金AlNd、タンゲステンW、クロムCr、モリブデンMo、チタンTi、銅Cu、タンタルTaの少なくとも一つを含むことを特徴とする請求項1に記載の液晶表示装置。

【請求項5】 20

前記ゲート配線から延長されたゲートパッドと；

前記ゲートパッド上に位置して、前記第1層を有するゲートパッド電極と；

をさらに含むことを特徴とする請求項1に記載の液晶表示装置。

【請求項6】

前記データ配線の第1層から延長されたデータパッド電極をさらに含むことを特徴とする請求項1に記載の液晶表示装置。

【請求項7】

前記画素電極は、前記ゲート配線と重なることを特徴とする請求項1に記載の液晶表示装置。

【請求項8】 30

前記画素電極と重なる前記ゲート配線の部分は、前記画素領域へと突出されることを特徴とする請求項7に記載の液晶表示装置。

【請求項9】

前記アクティブ層は、純粋非晶質シリコンを含み、前記オームイックコンタクト層は、不純物非晶質シリコンを含むことを特徴とする請求項1に記載の液晶表示装置。

【請求項10】

第1マスクを使用して、基板上に、ゲート配線と、前記ゲート配線から延長されたゲートパッドと、ゲート電極と、前記ゲート配線及び前記ゲート電極上にゲート絶縁膜と、ゲート絶縁膜上に前記ゲート電極と重畳するアクティブ層と、前記ゲート絶縁膜上に前記ゲート配線と重畳する半導体層と、前記アクティブ層上に位置し、互いに離隔する第1及び第2オームイックコンタクト層と、前記第1及び第2オームイックコンタクト層上にそれぞれ位置して前記アクティブ層の一部を露出させる第1ソース電極及び第1ドレイン電極と、を形成する第1の段階と； 40

第2マスクを使用して、前記第1ソース電極と前記第1ドレイン電極との間の前記アクティブ層と前記ゲート配線及び前記ゲート電極の側面を覆い、前記第1ソース電極及び前記第1ドレイン電極を露出する第1及び第2コンタクトホールを含む保護膜を形成する第2の段階と；

第3マスクを使用して、前記第1ソース電極及び前記第1ドレイン電極に各々連結され、それぞれが透明導電性物質でなる第1層と不透明金属物質でなる第2層を含む第2ソース電極及び第2ドレイン電極と、前記第2ソース電極の第1及び第2層から延長されて前

記ゲート配線と交差して画素領域を定義するデータ配線と、前記データ配線から延長されたデータパッド電極と、前記画素領域に前記第2ドレイン電極の第1層から延長された画素電極を形成する第3の段階と；

を含み、

前記第1の段階は、

前記基板上に、第1導電層と、第1絶縁膜と、純粋非晶質シリコン層と、不純物非晶質シリコン層と、第2導電層を形成する段階と；

前記第1マスクを使用して、ゲート領域とスイッチング領域の一部に対応する第1部分と、前記スイッチング領域の一部の両側に対応して前記第1部分より厚い第2部分を有する第1フォトレジストパターンを前記第2導電層上に形成する段階と；

10

前記第1フォトレジストパターンを使用して、前記第2導電層と、不純物非晶質シリコン層と、純粋非晶質シリコン層と、第1絶縁膜と、第1導電層とをパターニングして、前記ゲート領域に前記ゲート配線とゲートパッドと半導体層とを形成し、前記スイッチング領域に前記ゲート電極及び前記アクティブ層を形成して、前記ゲート領域及び前記スイッチング領域に前記ゲート絶縁膜を形成する段階と；

前記第1フォトレジストパターンをアッシングして前記第1部分を除去する段階と；

アッシングされた前記第1フォトレジストパターンを使用して、パターニングされた前記第2導電層及び前記不純物非晶質シリコン層をパターニングし、前記第1ソース電極及び前記第1ドレイン電極と前記第1及び第2オーミックコントタクト層とを形成する段階と；

20

を含み、

前記ゲート配線、前記ゲートパッド及び前記ゲート電極は前記第1導電層でなり、前記ゲート絶縁膜は前記第1絶縁膜でなり、前記半導体層は前記純粋非晶質シリコン層でなり、前記アクティブ層は前記純粋非晶質シリコン層でなり、前記第1及び第2オーミックコントタクト層はそれぞれ前記不純物非晶質シリコン層でなり、前記第1ソース電極及び前記第1ドレイン電極はそれぞれ前記第2導電層でなり、

前記第3の段階は、

前記ゲートパッド電極を形成する段階を含むと共に；

前記保護膜上に、前記第1及び第2層を形成する段階と；

前記第3マスクを使用して、前記ゲートパッドの少なくとも一部とデータ領域の一端と前記画素領域とに対応する第1部分と、前記データ領域の他の部分に対応して前記第1部分より厚い第2部分を有して、前記第1ソース電極と前記第1ドレイン電極との間のアクティブ層を覆う保護膜の少なくとも一部を覆わないフォトレジストパターンを前記第2層上に形成する段階と；

30

前記フォトレジストパターンを使用して、前記第1及び第2層をパターニングして、前記第2ソース電極及び前記第2ドレイン電極と前記データ領域の他の部分とに前記データ配線を形成する段階と；

前記フォトレジストパターンをアッシングして前記第1部分を除去する段階と；

アッシングされた前記フォトレジストパターンを使用して、パターニングされた前記第2層をパターニングして、前記データ領域の一端に前記データパッド電極と前記画素電極と前記ゲートパッド電極とを形成する段階と；

40

を含むことを特徴とする液晶表示装置の製造方法。

### 【請求項11】

前記第1フォトレジストパターンを形成する段階は、

前記第2導電層上にフォトレジスト層を形成する段階と；

前記第1マスクの半透過部が前記スイッチング領域の一部に対応するようにして、かつ、前記第1マスクの遮断部が前記ゲート領域と前記スイッチング領域の一部との両側に対応するようにして、前記フォトレジスト層を露光する段階と；

露光された前記フォトレジスト層を現像する段階と；

を含むことを特徴とする請求項10に記載の液晶表示装置の製造方法。

50

## 【請求項 1 2】

前記第2の段階は、前記第1ソース電極及び前記第1ドレイン電極を有する基板上に第2絶縁膜を形成する段階と；

前記第2マスクを使用して、前記第1ソース電極及び前記第1ドレイン電極の一部に対応する第3部分と、前記第3部分より厚い第4部分を有して、前記ゲートパッドの少なくとも一部を覆わない第2フォトレジストパターンを前記第2絶縁膜上に形成する段階と；

前記第2フォトレジストパターンを使用して、前記第2絶縁膜と前記純粹非晶質シリコン層とゲート絶縁膜とをパターニングし、前記ゲートパッドの少なくとも一部を露出する段階と；

前記第2フォトレジストパターンをアッシングして前記第3部分を除去する段階と；

アッシングされた前記第2フォトレジストパターンを使用して、前記パターニングされた第2絶縁膜をパターニングし、前記第1及び第2コントакトホールを有する保護膜を形成する段階と；

をさらに含むことを特徴とする請求項1 0に記載の液晶表示装置の製造方法。

## 【請求項 1 3】

前記第2フォトレジストパターンを形成する段階は、

前記第2絶縁膜上にフォトレジスト層を形成する段階と；

前記第2マスクの透過部が前記ゲートパッドの少なくとも一部に対応するようにして、かつ、前記第2マスクの半透過部が前記第1ソース電極及び前記第1ドレイン電極の一部に対応するようにして、前記フォトレジスト層を露光する段階と；

露光された前記フォトレジスト層を現像する段階と；

を含むことを特徴とする請求項1 2に記載の液晶表示装置の製造方法。

## 【請求項 1 4】

前記データパッド電極は、前記データ配線の第1層から延長されることを特徴とする請求項1 0に記載の液晶表示装置の製造方法。

## 【請求項 1 5】

前記ゲートパッド上に、前記第1層を有するゲートパッド電極を形成する段階をさらに含むことを特徴とする請求項1 4に記載の液晶表示装置の製造方法。

## 【請求項 1 6】

前記第1層は、インジウム-スズ-オキサイドITO、インジウム-ジンク-オキサイドIZO、インジウム-スズ-ジンク-オキサイドITZOの少なくとも一つを含み、前記第2層は、アルミニウムAl、アルミニウム合金AlNd、タングステンW、クロムCr、モリブデンMo、チタンTi、銅Cu、タンタルTaの少なくとも一つを含むことを特徴とする請求項1 0に記載の液晶表示装置の製造方法。

## 【請求項 1 7】

前記フォトレジストパターンを形成する段階は、

前記第2層上にフォトレジスト層を形成する段階と；

前記第3マスクの半透過部が前記ゲートパッドの少なくとも一部と前記データ領域の一端と前記画素領域とに対応するようにして、かつ、前記第3マスクの遮断部が前記データ領域の他の部分に対応するようにして、かつ、前記第3マスクの透過部が前記第1ソース電極と前記第1ドレイン電極との間のアクティブ層を覆う保護膜の少なくとも一部に対応するようにして、前記フォトレジスト層を露光する段階と；

露光された前記フォトレジスト層を現像する段階と；

を含むことを特徴とする請求項1 0に記載の液晶表示装置の製造方法。

## 【請求項 1 8】

前記画素電極は、前記ゲート配線と重なることを特徴とする請求項1 0に記載の液晶表示装置の製造方法。

## 【請求項 1 9】

前記画素電極と重なる前記ゲート配線の部分は、前記画素領域へと突出されることを特徴とする請求項1 8に記載の液晶表示装置の製造方法。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、液晶表示装置及びその製造方法に関し、特に、液晶表示装置用アレイ基板の製作において、エッティング防止膜を含む薄膜トランジスタが構成された液晶表示装置用アレイ基板を3マスク工程によって製作可能にした技術に関するものである。

**【背景技術】****【0002】**

一般的な液晶表示装置の駆動原理は、液晶の光学的異方性と分極性質とを利用している。液晶は、構造が細く長いので、分子の配列において方向性を有しており、任意に液晶に電界を加えると、分子配列の配列方向を制御することができる。10

従って、液晶の分子配列方向を任意に調節すると、光学的異方性によって液晶の分子配列方向に光が屈折して画像情報を表現することができる。

**【0003】**

液晶表示装置は、共通電極が形成されたカラーフィルタ基板（上部基板）と、画素電極が形成されたアレイ基板（下部基板）と、これら両基板間に充填された液晶とにより構成される。このような液晶表示装置は、共通電極及び画素電極が上下に印加される電場により液晶を駆動する方式であって、透過率及び開口率等の特性が優れている。

現在では、薄膜トランジスタと薄膜トランジスタに連結された画素電極とが行列方式で配列された能動行列型の液晶表示装置（AM-LCD、以下、液晶表示装置と称する）が解像度及び動画像の具現能力が優れており、最も注目を浴びている。20

**【0004】**

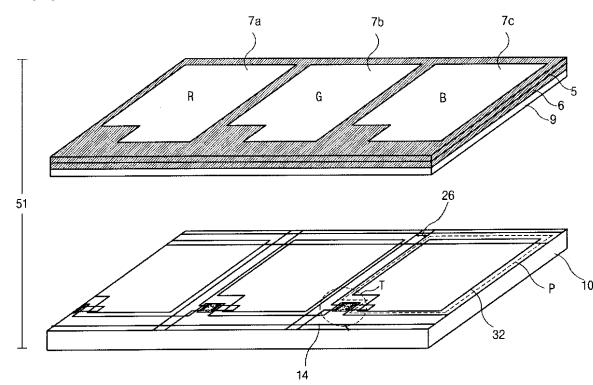

以下、図1を参照しながら、従来の液晶表示装置の構成について説明する。

図1は、一般的な液晶表示装置を概略的に示す斜視図である（例えば、特許文献1参照）。

図1において、液晶パネル51は、液晶層（図示せず）を間に有して相互に離隔して構成された第1基板5と第2基板10とにより構成されている。第2基板10と向かい合う第1基板5の一面には、ブラックマトリックス6と、赤色、緑色、青色のカラーフィルタ7a、7b、7cと、カラーフィルタ上に透明な共通電極9とが構成されている。

**【0005】**

第1基板5と向かい合う第2基板10には、多数の画素領域Pが定義されており、また、画素領域Pの一側に沿って延長して形成されたゲート配線14と、ゲート配線14が形成される画素領域Pの一側と、平行でない他側に沿って延長して形成されたデータ配線26とが構成されている。30

**【0006】**

図1の構成により、画素領域Pは、ゲート配線14とデータ配線26とが交差して定義され、両配線の交差地点には、薄膜トランジスタTが構成される。

画素領域Pには、薄膜トランジスタTと接触する透明な画素電極32が構成されており、画素電極32は、インジウム-スズ-オキサイドITO及びインジウム-ジンク-オキサイドIZOのように、光の透過率が比較的に優れた透明導電性金属で形成される。40

**【0007】**

上記のように構成された液晶表示装置用アレイ基板は、5～6マスク工程により製作される。以下、従来の液晶表示装置用アレイ基板の製作工程について、簡略的に紹介する。

ここでは、例えば5マスク工程について説明し、マスク工程のみを並べている。

**【0008】**

第1マスク工程：ゲート電極及びゲート配線（及びゲートパッド）の形成工程。

第2マスク工程：ゲート電極の上部のアクティブ層及びオーミックコンタクト層の形成工程。

第3マスク工程：データ配線（及びデータパッド）、ソース電極及びドレイン電極の形成工程。50

第4マスク工程：基板全面に保護膜を形成して、ドレイン電極を露出するコンタクトホールを形成する工程。

第5マスク工程：コンタクトホールを通じて接触する画素電極を形成する工程。

【0009】

以上の5マスク工程によって液晶表示装置用アレイ基板を製作することができる。

しかし、このように多数の工程によってアレイ基板が製作されるが、工程が多いほど不良が発生する確率が大きくなつて生産収率が低下するので、工程時間の増加と工程費用の上昇とによって製品の競争力が弱化される問題がある。

そこで、このような問題を解決するために、工程数を低減させた4マスク工程が提案されている。

10

【0010】

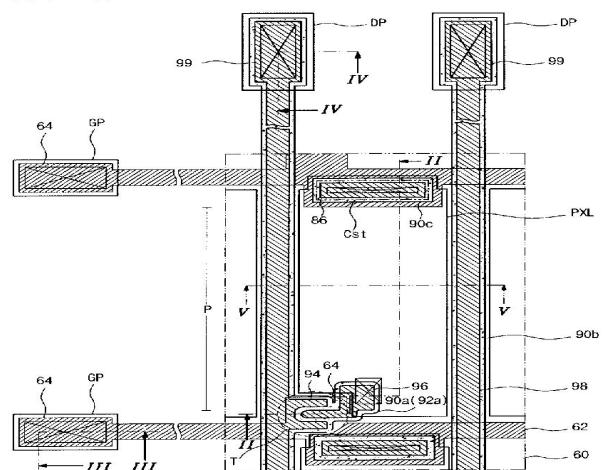

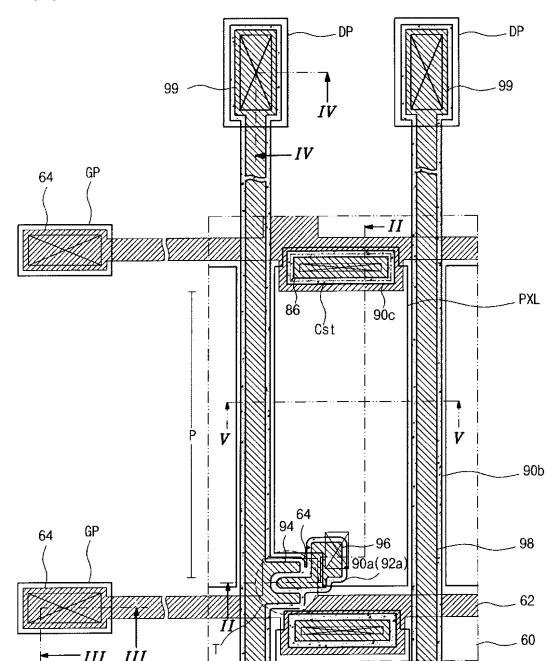

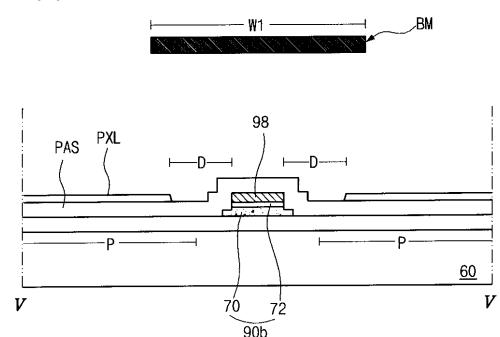

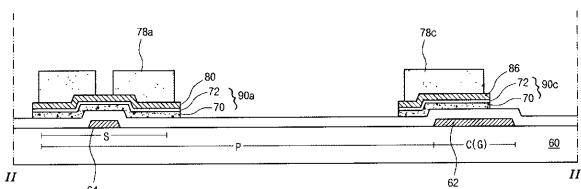

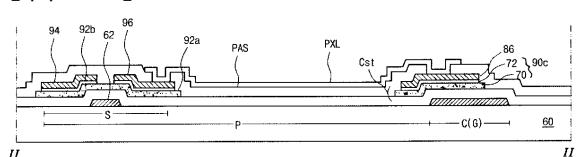

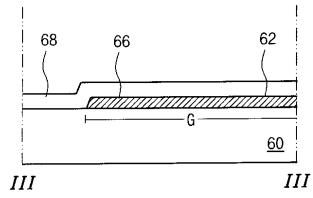

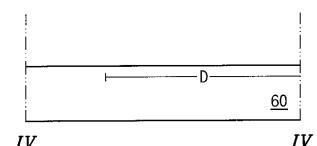

図2は、従来の4マスク工程によって製作した液晶表示装置用アレイ基板の一部を拡大して示す平面図である。

図2において、アレイ基板は、絶縁基板60上に一方向に延長されたゲート配線62と、ゲート配線62に交差して画素領域Pを定義するデータ配線98とを含む。

【0011】

ゲート配線62の一端にはゲートパッド電極64が構成され、データ配線98の一端にはデータパッド電極100が構成される。

ゲートパッド電極64及びデータパッド電極100の上部には、各々これと接触する透明なゲートパッド電極端子114と、データパッド電極端子116とが構成される。

20

【0012】

ゲート配線62とデータ配線98との交差地点には、ゲート配線62と接触するゲート電極64と、ゲート電極64の上部に位置した第1半導体層90aと、第1半導体層90aの上部に離隔され位置して、データ配線98に連結されたソース電極94と、ソース電極94から離隔されたドレイン電極96と、を含む薄膜トランジスタTが構成される。

【0013】

画素領域Pには、ドレイン電極96と接触する透明な画素電極PXLが構成される。また、ゲート配線62の一部上部には、画素電極PXLと接触するアイランド状のストレージ電極86が形成される。ゲート配線62の一部を第1電極として、ストレージ電極86を第2電極とし、これら両電極間に位置したゲート絶縁膜(図示せず)を誘電体としたストレージキャパシタCstが形成される。

30

【0014】

ここで、データ配線98の下部には、第1半導体層90aから延長された第2半導体層90bが構成されて、アイランド状のストレージ電極86の下部には、第3半導体層90cが形成される。

第1半導体層90aのアクティブ層92aの一部は、ゲート電極64によって遮られないで、バックライト等のような光に露出されて光電流(photocurrent)を発生する。このような光電流は、薄膜トランジスタの漏洩電流として機能する。

【0015】

また、データ配線98と下部の半導体層90bとが同一の工程でパターニングされるが、このパターニング時において、半導体層90bの下部層である純粋非晶質シリコン層70は、データ配線98の幅より広くパターニングされる。

40

これにより、純粋非晶質シリコン層70は、バックライトのような光に露出されて光電流を発生する。このように発生した光電流により、隣接した画素電極PXLとの間でカップリング(coupling)現象が発生して、液晶パネルの画面に波状ノイズ(wavy noise)が発生する問題がある。

【0016】

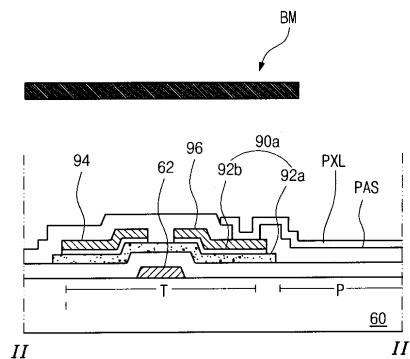

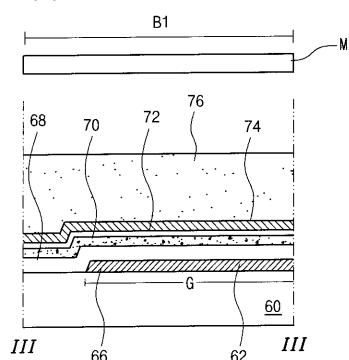

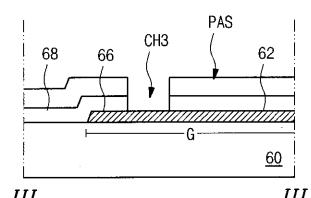

以下、図3A、図3Bを参照しながら、波状ノイズについて詳しく説明する。

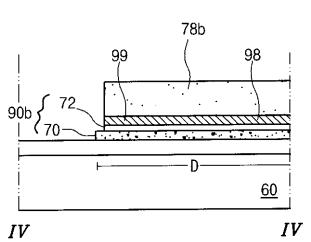

図3A、図3Bは、図2内のI—I'I'I線、V—V線に沿って切断した断面図である。

図3A、図3Bにおいて、従来の4マスク工程によって薄膜トランジスタアレイ基板6

50

0を製作すると、ソース電極94及びドレイン電極96の下部に第1半導体層90aが構成され、データ配線98の下部に第2半導体層90bが構成される。

#### 【0017】

ソース電極94及びドレイン電極96は、第1半導体層90a上に位置し、保護膜PA-Sは、ソース電極94及びドレイン電極96上に位置する。

第1半導体層90a及び第2半導体層90bは、純粋非晶質シリコン層(a-Si:H)70と、不純物を含む非晶質シリコン層(n+a-Si:H)72とに積層されて構成される。第1半導体層90aを構成する純粋非晶質シリコン層は、アクティブ層92aとして作用し、上部の不純物非晶質シリコン層は、オーミックコンタクト層92bとして作用する。

10

#### 【0018】

また、第1半導体層90aのアクティブ層92aの一部は、ゲート電極64によって遮られないので、バックライト等のような光に露出されて光電流を発生する。このような光電流は、薄膜トランジスタの漏洩電流として機能する。漏洩電流は、画素領域Pに充電された電圧を非正常に漏洩するようにして、薄膜トランジスタの動作を低下する原因となる。

#### 【0019】

また、データ配線98の下部に位置して、データ配線98の両側に突出された第2半導体層90bの純粋非晶質シリコン層70は、下部の光源に露出されて光電流を発生する。

また、下部の光源のちらつきによって、純粋非晶質シリコン層70は、微細に反応して活性化と非活性化状態とが繰り返されて、これによる光電流の変化が発生する。

20

このような光電流の変成成分は、隣接する画素電極PXLに流れる信号と共にカップリングされ、画素電極PXLに位置した液晶の動きを歪曲する。

これにより、液晶パネルの画面には、波状の細い線が示される波状ノイズが発生する。

また、データ配線98の下部に位置する純粋非晶質シリコン層70は、データ配線98の両側に各々約1.7μm程度突出される。

#### 【0020】

一般的に、データ配線98と画素電極PXLとは、アライン誤差を勘案して4.75μm程度の隔離距離を置いてパターニングされるが、上記突出部分を勘案すると、データ配線98と画素電極PXLとの隔離距離Dは、6.45μmになる。

30

すなわち、データ配線98の一側に突出された部分の長さだけ、画素電極PXLが遠くパターニングされて、この部分の光漏れを遮るブラックマトリックスBMの幅W1も広くなつて、開口領域が削減される問題がある。

#### 【0021】

また、上記波状ノイズが発生するデータ配線98と、その下部の第2半導体層90bと、漏洩電流が発生する薄膜トランジスタとの構造は、従来の汎用的な4マスク工程によって必然に発生する。以下、従来の4マスク工程について説明する。

#### 【0022】

ここでは、図4A～図4G、図5A～図5G、図6A～図6Gの工程図を参照しながら、従来の4マスク工程によってアレイ基板を製作する方法について説明する。

40

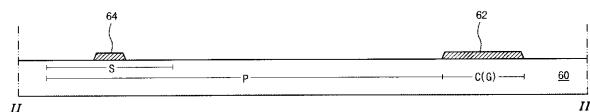

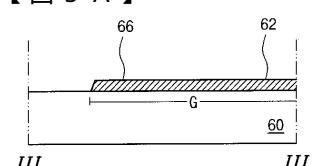

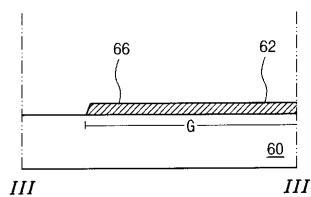

図4A～図4G、図5A～図5G、図6A～図6Gは、図2内のII-II線、III-III線、IV-IV線に沿つて切断した従来の工程断面図であり、工程順に示している。

#### 【0023】

図4A、図5A及び図6Aは、第1マスク工程を示している。

図4A、図5A及び図6Aにおいては、基板60上に、スイッチング領域Sを含む画素領域P、ゲート領域G、データ領域D及びストレージ領域Cを定義する。

ストレージ領域Cは、ゲート領域Gの一部に定義される。

#### 【0024】

また、多数の領域(S、P、G、D、C)が定義された基板60上に、一方向に延長さ

50

れて、一端にゲートパッド 6 6 を含むゲート配線 6 2 と、ゲート配線 6 2 に連結されて、スイッチング領域 S に位置するゲート電極 6 4 とを形成する。

【 0 0 2 5 】

ここで、ゲートパッド 6 6 及びゲート配線 6 2 とゲート電極 6 4 とは、アルミニウム A 1 、アルミニウム合金 A 1 N d 、タンゲステン W 、クロム C r 、モリブデン M o 等の単一金属や、アルミニウム A 1 / クロム C r ( または、モリブデン M o ) 等を含む導電性金属グループのうちから選択された一つまたはそれ以上の金属を蒸着することにより形成される。

【 0 0 2 6 】

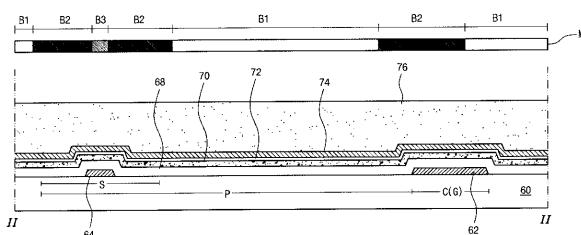

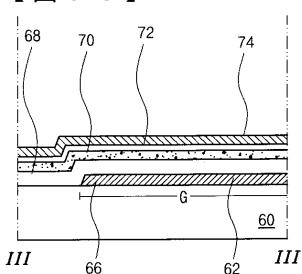

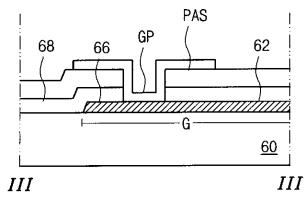

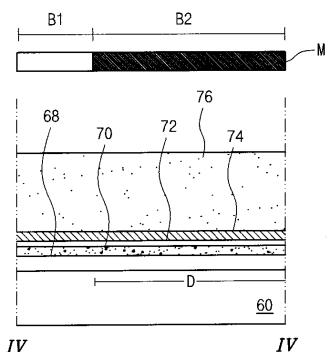

図 4 B ~ 図 4 E 、図 5 B ~ 図 5 E 、図 6 B ~ 図 6 E は、第 2 マスク工程を示している。

10

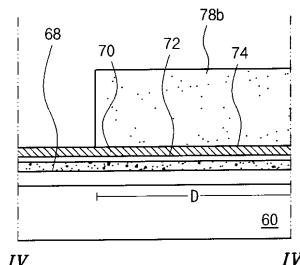

まず、図 4 B 、図 5 B 及び図 6 B においては、ゲート電極 6 4 及びゲートパッド 6 6 を含むゲート配線 6 2 が形成された基板 6 0 の全面に、ゲート絶縁膜 6 8 と、純粋非晶質シリコン層 ( a - S i : H ) 7 0 と、不純物を含む非晶質シリコン層 ( n + 、または、 P + a - S i : H ) 7 2 と、導電性金属層 7 4 とを形成する。

【 0 0 2 7 】

ゲート絶縁膜 6 8 は、窒化シリコン S i N X 、酸化シリコン S i O 2 等を含む無機絶縁物質、または場合によっては、ベンゾシクロブテン B C B 、アクリル系樹脂等を含む有機絶縁物質のうちから一つを蒸着して形成され、金属層 7 4 は、上記導電性金属グループのうちから選択された一つまたはそれ以上の物質を蒸着して形成される。

【 0 0 2 8 】

導電性金属層 7 4 が形成された基板 6 0 全面に、フォトレジストを塗布して感光層 7 6 を形成する。

20

感光層 7 6 の離隔された上部に、透過部 B 1 、遮断部 B 2 、半透過部 B 3 で構成されたマスク M を配置させる。

半透過部 B 3 は、マスク M にスリット状または半透過膜を形成して、光の強度を弱くしたり、または光の透過量を少なくしたりして、感光層を不完全露光させる機能を有する。

【 0 0 2 9 】

また、遮断部 B 2 は、光を完全に遮断する機能を有し、透過部 B 1 は、光を透過させ、光によって感光層 7 6 が完全な化学的变化、すなわち、完全露光させる機能を有する。

一方、スイッチング領域 S には、半透過部 B 3 を設けると共に、半透過部 B 3 の両側に遮断部 B 2 を配置させ、ストレージ領域 C には、遮断部 B 2 を配置させ、ゲート領域 G と交差する方向であるデータ領域 D には、遮断部 B 2 を配置させる。

30

以下、マスク M の上部に光を照射して、下部の感光層 7 6 を露光して現像する工程を行う。

【 0 0 3 0 】

続いて、図 4 C 、図 5 C 及び図 6 C においては、スイッチング領域 S とデータ領域 D とストレージ領域 C との上部に、パターニングされた第 1 ~ 第 3 感光パターン 7 8 a 、 7 8 b 、 7 8 c を形成する。

第 1 ~ 第 3 感光パターン 7 8 a 、 7 8 b 、 7 8 c の周辺に露出された金属層 7 4 と、その下部の不純物非晶質シリコン層 7 2 と、純粋非晶質シリコン層 7 0 とを除去する工程を行う。

40

【 0 0 3 1 】

この除去工程においては、金属層 7 4 の種類に応じて、金属層 7 4 及びその下部層 7 0 、 7 2 を同時に除去したり、金属層 7 4 を先にエッチングした後、乾式エッチング工程によって下部の純粋非晶質シリコン層 7 0 と不純物を含む非晶質シリコン層 7 2 を除去したりする。

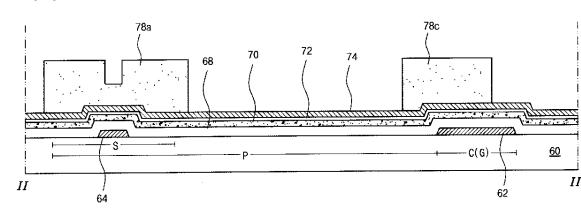

【 0 0 3 2 】

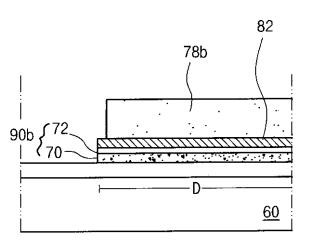

次に、上記除去工程が完了すると、図 4 D 、図 5 D 及び図 6 D において、第 1 ~ 第 3 感光パターン 7 8 a 、 7 8 b 、 7 8 c の下部に、第 1 金属パターン 8 0 と、第 1 金属パターン 8 0 から画素領域 P の一側に沿って延長された第 2 金属パターン 8 2 と、ストレージ領

50

域 C に対応したアイランド状の第 3 金属パターン 8 6 とが形成される。

【 0 0 3 3 】

この金属パターン形成工程においては、第 1 ~ 第 3 金属パターン 8 0 、 8 2 、 8 6 の下部に、純粋非晶質シリコン層 7 0 と不純物を含む非晶質シリコン層 7 2 とが存在しており、便宜上、第 1 金属パターン 8 0 の下部に構成されたのは第 1 半導体層 9 0 a 、第 2 金属パターン 8 2 の下部に構成されたのは第 2 半導体層 9 0 b 、第 3 金属パターン 8 6 の下部に構成されたのは第 3 半導体層 9 0 c とする。

【 0 0 3 4 】

また、第 1 感光パターン 7 8 a のうち、ゲート電極 6 4 の中心に対応して高さが低い部分を除去して、下部の金属パターン 8 0 を露出するためのアッシング工程を行う。

10

この結果、ゲート電極 6 4 の中心に対応する第 1 金属パターン 8 0 の一部が露出されて、第 1 ~ 第 3 感光パターン 7 8 a 、 7 8 b 、 7 8 c の周辺に、第 1 ~ 第 3 金属パターン 8 0 、 8 2 、 8 6 の周辺が同時に露出される。

アッシング工程の後、第 1 金属パターン 8 0 の露出された部分と、その下部の不純物非晶質シリコン層 7 2 とを除去する工程を行う。

【 0 0 3 5 】

次に、上記除去工程が完了すると、図 4 E 、図 5 E 及び図 6 E においては、ゲート電極 6 4 の上部に位置した第 1 半導体層 9 0 a のうち、下部層（純粋非晶質シリコン層）は、アクティブ層 9 2 a として機能し、アクティブ層 9 2 a の上部で、一部が除去されて離隔された上部層（不純物非晶質シリコン層）は、オーミックコンタクト層 9 2 b として機能する。

20

【 0 0 3 6 】

また、アクティブ層 9 2 a の上部のオーミックコンタクト層 9 2 b を除去しながら、下部のアクティブ層 9 2 a をオーバーエッチングして、アクティブ層 9 2 a の表面（アクティブチャンネル）に不純物が残らないようにする。

一方、オーミックコンタクト層 9 2 b の上部に位置して離隔された金属パターンは、各々、ソース電極 9 4 とドレイン電極 9 6 となる。

なお、ソース電極 9 4 と接触する第 2 金属パターン（図 5 C 内の 8 2 ）は、データ配線 9 8 であって、データ配線 9 8 の一端は、データパッド 9 9 である。

【 0 0 3 7 】

30

また、ストレージ領域 C に対応して形成されたアイランド状の第 3 金属パターン 8 6 は、ストレージ電極になる。

すなわち、ゲート配線 6 2 は、第 1 ストレージ電極の機能を有し、上部のストレージ電極 8 6 は、第 2 ストレージ電極の機能を有する。従って、ゲート配線 6 2 、その上部のゲート絶縁膜 6 8 、第 3 半導体階 9 0 c 、その上部のストレージ電極 8 6 は、補助容量部であるストレージキャパシタ C s t を構成する。以下、残留した感光パターン 7 8 a 、 7 8 b 、 7 8 c を除去することにより、第 2 マスク工程を完了する。

【 0 0 3 8 】

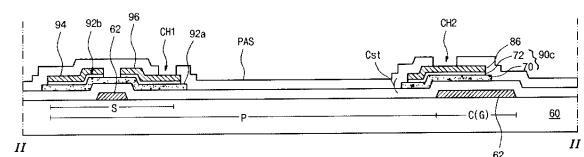

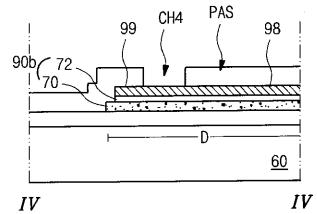

図 4 F 、図 5 F 及び図 6 F は、第 3 マスク工程を示している。

図 4 F 、図 5 F 及び図 6 F においては、ソース電極 9 4 及びドレイン電極 9 6 と、データパッド 9 9 を含むデータ配線 9 8 と、ストレージキャパシタ C s t とが構成された基板 6 0 の全面に、窒化シリコン Si NX または酸化シリコン Si O 2 を含む無機絶縁物質グループのうちから選択された一つを蒸着したり、または場合によって、ベンゾシクロブテン BCB 、アクリル系樹脂を含む有機絶縁物質グループのうちから選択された一つを塗布して、保護膜 P A S を形成する。

40

【 0 0 3 9 】

以下、保護膜 P A S をパターニングして、ドレイン電極 9 6 の一部を露出するドレインコンタクトホール C H 1 と、ストレージ電極 8 6 を露出するストレージコンタクトホール C H 2 と、ゲートパッド 6 6 の一部を露出するゲートパッドコンタクトホール C H 3 と、データパッド 9 9 の一部を露出するデータパッドコンタクトホール C H 4 とを形成する。

50

## 【0040】

図4G、図5G及び図6Gは、第4マスク工程を示している。

図4G、図5G及び図6Gに示においては、保護膜PASが形成された基板60全面に、インジウム-スズ-オキサイドITO、インジウム-ジンク-オキサイドIZOとインジウム-ジンク-オキサイドIZOを含む透明な導電性金属グループのうちから選択された一つを蒸着してパターニングし、ドレイン電極96及びストレージ電極86の両方と接触しながら画素領域Pに位置する画素電極PXLを形成すると同時に、ゲートパッド66と接触するゲートパッド電極GPと、データパッド99と接触するデータパッド電極DPとを形成する。

## 【0041】

10

このように、従来の4マスク工程により液晶表示装置用アレイ基板を製作する。

従来の4マスク工程によれば、既存の5マスク工程に比べて、画期的なほど生産費用を節減する効果及び工程時間を短縮する効果があり、また、工程時間の短縮によって不良発生確率も減少する。

【特許文献1】韓国公開特許第10-2001-0103431号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0042】

従来の液晶表示装置及びその製造方法では、上記4マスク工程によって製作された薄膜トランジスタアレイ基板が、データ配線の両側に半導体層が拡張されたの構造を有しているので、依然として画面に波状ノイズが発生するうえ、拡張された半導体層によって開口率が低下するという課題があった。

20

また、アクティブ層がゲート電極によって完全に遮られずに、薄膜トランジスタに漏洩電流が発生するという課題があった。さらに、オーバーエッ칭されることを考慮して、アクティブ層の厚さを厚く形成しているので、工程時間及び工程費用面で、工程収率が低下するという課題があった。

## 【0043】

本発明は、上記のような課題を解決するためになされたもので、画質及び開口率を向上させて、工程収率を高めることのできる液晶表示装置及びその製造方法を提供することを目的とする。

30

## 【課題を解決するための手段】

## 【0044】

本発明に係る液晶表示装置は、ゲート配線と；前記ゲート配線に連結されたゲート電極と；前記ゲート配線及び前記ゲート電極上に位置するゲート絶縁膜と；前記ゲート絶縁膜上に位置し、前記ゲート電極と重畳するアクティブ層と；前記アクティブ層から延長されて、前記ゲート絶縁膜上に位置し、前記ゲート配線と重畳する半導体層と；前記アクティブ層上に位置し、互いに離隔する第1及び第2オーミックコンタクト層と；前記第1及び第2オーミックコンタクト層上にそれぞれ互いに離隔して位置することにより、前記アクティブ層の一部を露出させる第1ソース電極及び第1ドレイン電極と；前記第1ソース電極及び第1ドレイン電極と前記アクティブ層の露出された一部上に位置し、前記第1ソース電極及び第1ドレイン電極それを露出させる第1及び第2コンタクトホールを含み、前記ゲート配線及びゲート電極の側面を覆う保護膜と；前記保護膜上に位置し、それが透明導電性物質でなる第1層と不透明金属物質でなる第2層を含み、前記第1及び第2コンタクトホールを通じて前記第1ソース電極及び第1ドレイン電極と接触する第2ソース電極及び第2ドレイン電極と；前記第2ソース電極の第1層及び第2層から延長されて、前記保護膜上に位置し、前記ゲート配線と交差して画素領域を定義するデータ配線と；前記画素領域に位置して、前記第2ドレイン電極の第1層から延長されて、前記保護膜上に位置する画素電極と；を含み、前記ゲート絶縁膜は、前記ゲート配線及びゲート電極と同一の外郭を有し、前記半導体層及びアクティブ層それぞれは、前記ゲート配線及びゲート電極と同一の外郭を有する。

40

50

また、本発明に係る液晶表示装置の製造方法は、第1マスクを使用して、基板上に、ゲート配線と、前記ゲート配線から延長されたゲートパッドと、ゲート電極と、前記ゲート配線及び前記ゲート電極上にゲート絶縁膜と、ゲート絶縁膜上に前記ゲート電極と重疊するアクティブ層と、前記ゲート絶縁膜上に前記ゲート配線と重疊する半導体層と、前記アクティブ層上に位置し、互いに離隔する第1及び第2オーミックコンタクト層と、前記第1及び第2オーミックコンタクト層上にそれぞれ位置して前記アクティブ層の一部を露出させる第1ソース電極及び第1ドレイン電極と、を形成する第1の段階と；第2マスクを使用して、前記第1ソース電極と前記第1ドレイン電極との間の前記アクティブ層と前記ゲート配線及び前記ゲート電極の側面を覆い、前記第1ソース電極及び前記第1ドレイン電極を露出する第1及び第2コンタクトホールを含む保護膜を形成する第2の段階と；第3マスクを使用して、前記第1ソース電極及び前記第1ドレイン電極に各々連結され、それぞれが透明導電性物質である第1層と不透明金属物質である第2層を含む第2ソース電極及び第2ドレイン電極と、前記第2ソース電極の第1及び第2層から延長されて前記ゲート配線と交差して画素領域を定義するデータ配線と、前記データ配線から延長されたデータパッド電極と、前記画素領域に前記第2ドレイン電極の第1層から延長された画素電極を形成する第3の段階と；を含み、前記第1の段階は、前記基板上に、第1導電層と、第1絶縁膜と、純粋非晶質シリコン層と、不純物非晶質シリコン層と、第2導電層を形成する段階と；前記第1マスクを使用して、ゲート領域とスイッチング領域の一部に対応する第1部分と、前記スイッチング領域の一部の両側に対応して前記第1部分より厚い第2部分を有する第1フォトレジストパターンを前記第2導電層上に形成する段階と；前記第1フォトレジストパターンを使用して、前記第2導電層と、不純物非晶質シリコン層と、純粋非晶質シリコン層と、第1絶縁膜と、第1導電層とをパターニングして、前記ゲート領域に前記ゲート配線とゲートパッドと半導体層とを形成し、前記スイッチング領域に前記ゲート電極及び前記アクティブ層を形成して、前記ゲート領域及び前記スイッチング領域に前記ゲート絶縁膜を形成する段階と；前記第1フォトレジストパターンをアッシングして前記第1部分を除去する段階と；アッシングされた前記第1フォトレジストパターンを使用して、パターニングされた前記第2導電層及び前記不純物非晶質シリコン層をパターニングし、前記第1ソース電極及び前記第1ドレイン電極と前記第1及び第2オーミックコンタクト層とを形成する段階と；を含み、前記ゲート配線、前記ゲートパッド及び前記ゲート電極は前記第1導電層であり、前記ゲート絶縁膜は前記第1絶縁膜であり、前記半導体層は前記純粋非晶質シリコン層であり、前記アクティブ層は前記純粋非晶質シリコン層であり、前記第1及び第2オーミックコンタクト層はそれぞれ前記不純物非晶質シリコン層であり、前記第1ソース電極及び前記第1ドレイン電極はそれぞれ前記第2導電層であり、前記第3の段階は、前記ゲートパッド電極を形成する段階を含むと共に；前記保護膜上に、前記第1及び第2層を形成する段階と；前記第3マスクを使用して、前記ゲートパッドの少なくとも一部とデータ領域の一端と前記画素領域とに対応する第1部分と、前記データ領域の他の部分に対応して前記第1部分より厚い第2部分を有して、前記第1ソース電極と前記第1ドレイン電極との間のアクティブ層を覆う保護膜の少なくとも一部を覆わないフォトレジストパターンを前記第2層上に形成する段階と；前記フォトレジストパターンを使用して、前記第1及び第2層をパターニングして、前記第2ソース電極及び前記第2ドレイン電極と前記データ領域の他の部分とに前記データ配線を形成する段階と；前記フォトレジストパターンをアッシングして前記第1部分を除去する段階と；アッシングされた前記フォトレジストパターンを使用して、パターニングされた前記第2層をパターニングして、前記データ領域の一端に前記データパッド電極と前記画素電極と前記ゲートパッド電極とを形成する段階と；を含む。

#### 【発明の効果】

#### 【0058】

本発明は、アレイ基板を3マスク工程で製作するので、工程単純化による工程時間の短縮及び工程費用の節減を実現し、生産収率を改善して、製品の競争力を高めることができる。

10

20

30

40

50

また、半導体層及びアクティブ層は、金属電極及び配線の外部に延長されないので、波状ノイズを改善して、開口率を高めることができる。

さらに、ゲート電極がアクティブ層を遮るので、薄膜トランジスタでの漏洩電流を改善することができる。

【発明を実施するための最良の形態】

【0059】

実施の形態1.

以下、添付した図面を参照しながら、本発明の実施の形態1について説明する。

本発明の実施の形態1においては、液晶表示装置用アレイ基板を3マスク工程で製作する。

10

図7は、本発明の実施の形態1に係る液晶表示装置用アレイ基板の一部を拡大して示す平面図である。

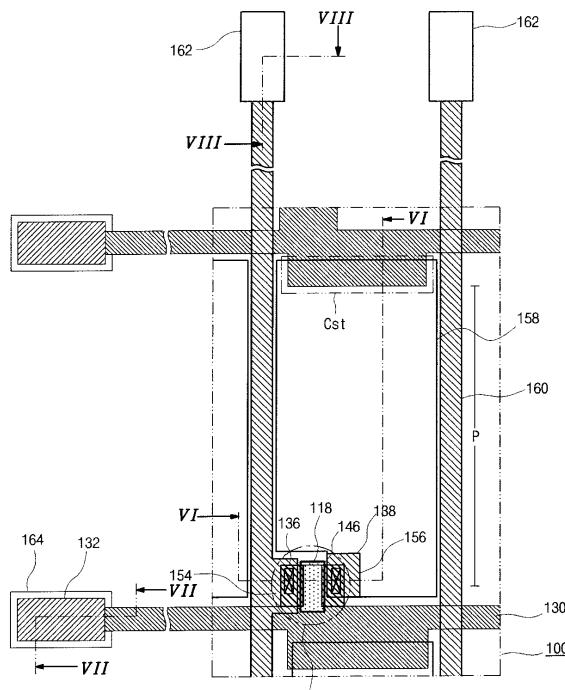

【0060】

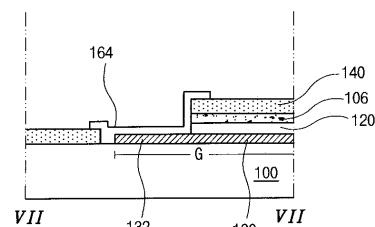

図7において、絶縁基板100上には、一方向に延長されて一端にゲートパッド132が構成されたゲート配線130と、ゲート配線130と交差して画素領域Pを定義すると共に、一端にデータパッド162を含むデータ配線160とが構成されている。

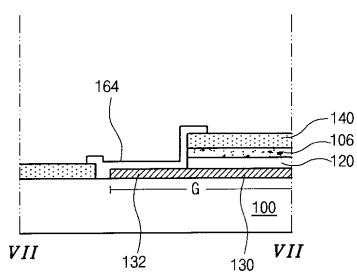

【0061】

ゲートパッド132は、上部に透明電極からなるゲートパッド電極164が構成されており、データパッド162は、それ自体が透明電極で構成されている。

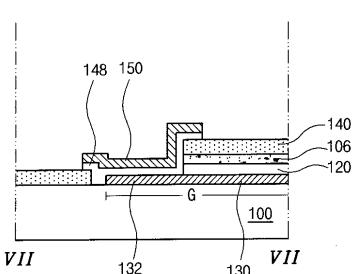

ゲート配線130とデータ配線160との交差地点には、ゲート電極118と、アクティブ層及びオーミックコンタクト層を含む第1半導体層と、オーミックコンタクト層に直接接触して互いに離隔された第1ソース電極136及び第1ドレイン電極138と、第1ソース電極136及び第1ドレイン電極138に接触する第2ソース電極154と、第2ドレイン電極156と、を含む薄膜トランジスタTが構成されている。

20

【0062】

薄膜トランジスタTの上部には、第1及び第2ソース電極136、154と、第1及び第2ドレイン電極136、156の離隔された間に露出されたアクティブ層(図示せず)を覆うエッチング防止膜146とが構成される。

画素領域Pには、第2ドレイン電極156に連結された透明な画素電極158が構成される。

30

【0063】

一方、画素領域Pを定義する部分のゲート配線130の上部には、これを第1ストレージ電極として、ゲート配線130の上部に延長された画素電極158の一部を第2ストレージ電極とするストレージキャパシタCstが構成される。ストレージキャパシタCstを構成するために、ゲート配線130は、画素領域Pへと突出されて画素電極158と重なる。

【0064】

上記構成は、3マスク工程によって製作されており、特に、アクティブ層(図示せず)は、データ配線160の下部に存在しないのみならず、配線の外側に露出されない。

【0065】

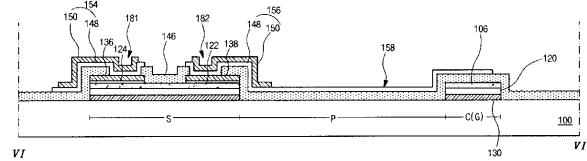

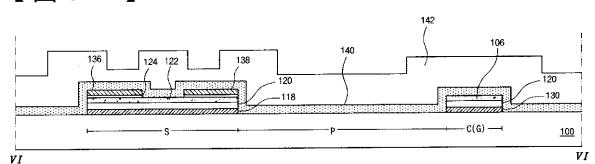

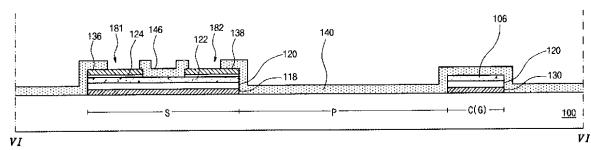

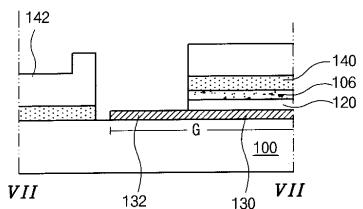

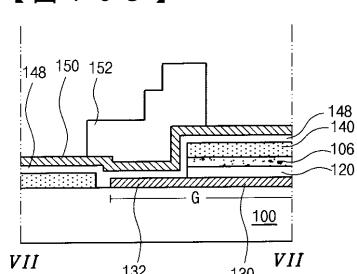

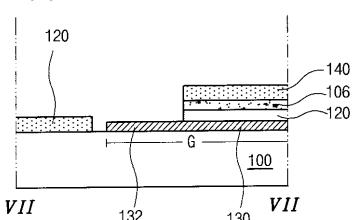

以下、図8A、図8B及び図8Cを参照しながら、本発明の実施の形態1に係る薄膜トランジスタアレイ基板の断面構成について説明する。

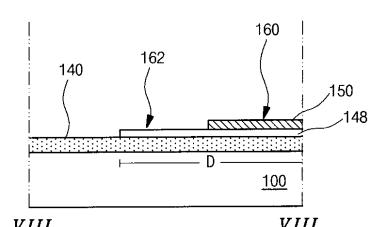

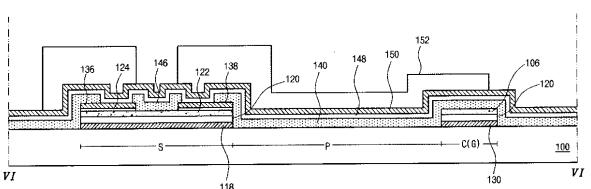

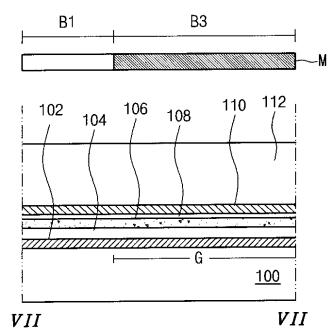

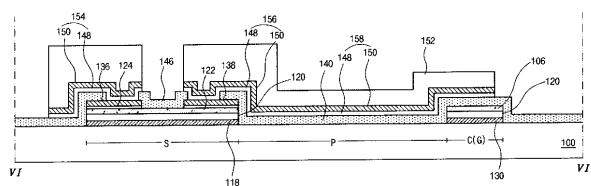

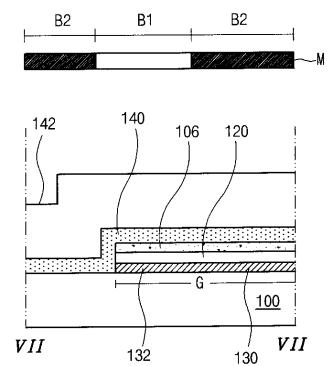

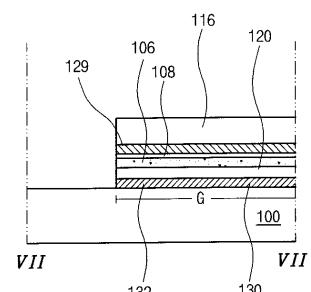

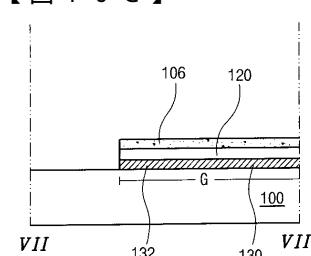

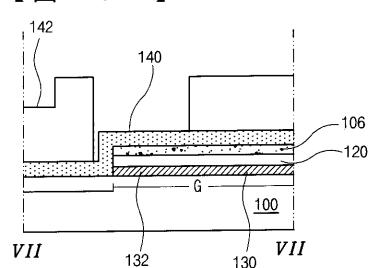

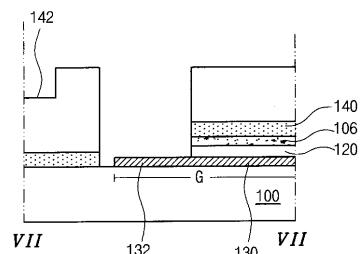

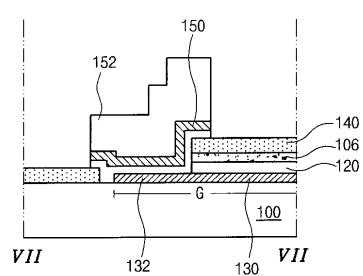

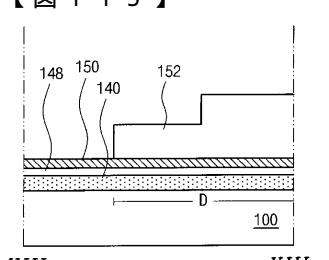

図8A、図8B及び図8Cは、各々、図7内のVII-VII線、VIII-VIII線、VIIII-VIIII線に沿って切断した断面図であり、それぞれ、スイッチング領域及び画素領域を切断した断面図と、ゲートパッドを切断した断面図と、データパッドを切断した断面図とを示している。

40

【0066】

図8A～図8Cにおいて、基板100は、多数の画素領域Pと、ゲート領域Gと、データ領域Dとにより定義される。また、ゲート領域Gの一部にストレージ領域Cが定義され、画素領域Pごとに、これに近接してスイッチング領域Sが定義される。

50

## 【0067】

スイッチング領域Sには、ゲート電極118と、アクティブ層122から離隔されたオーミックコンタクト層124を有する第1半導体層と、オーミックコンタクト層124と各々接触して互いに離隔された第1ソース電極136及び第1ドレイン電極138と、第1ソース電極136及び第1ドレイン電極138に各々接触する第2ソース電極154及び第2ドレイン電極156と、からなる薄膜トランジスタTが構成されている。

## 【0068】

第1ソース電極136及びその下部のオーミックコンタクト層124は、同一のアイランド状であり、第2ドレイン電極138及びその下部のオーミックコンタクト層124は、同一のアイランド状である。第1ソース電極136及び第1ドレイン電極138とオーミックコンタクト層124とは、ゲート電極の内部に位置する。 10

## 【0069】

ゲート電極118上には、ゲート絶縁膜120が配置される。エッティング防止膜146は、保護膜140のうち、第1ソース電極136及び第1ドレイン電極138の離隔された間に露出されたアクティブ層122を覆う部分を構成する。保護膜140は、第1ソース電極136及び第1ドレイン電極138を露出するための第1コンタクトホール181及び第2コンタクトホール182を有する。

## 【0070】

第2ソース電極154及び第2ドレイン電極156は、第1層としての透明金属層148と、第2層としての不透明金属層150とが積層された状態で構成される。 20

第2ソース電極156に連結されたデータ配線160は、画素領域Pの一側のデータ領域Dに構成される。データ配線160も、第1層148及び第2層150の積層構造で形成される。データパッド162は、データ配線160から延長された第1層148で構成される。

## 【0071】

画素領域Pに位置した画素電極158は、第2ドレイン電極156の第1層148から延長される。

また、ゲート配線130も、上部にゲート絶縁膜120及び第2半導体層106が構成される。第2半導体層106は、アクティブ層122から延長されている。ゲートパッド132の上部には、ゲートパッド電極164が配置される。ゲートパッド電極164は、第1層148により構成される。 30

## 【0072】

第1ソース電極136及び第1ドレイン電極138は、第2ソース電極154及び第2ドレイン電極156の下部の透明金属層148とオーミックコンタクト層124とのオミック接触のために形成される。

ゲート電極118及びゲート配線130の外郭と、アクティブ層及び第2半導体層106の外郭と、ゲート絶縁膜120の外郭とは、同一である。

## 【0073】

以上のように、半導体層及びアクティブ層は、金属電極及び配線の外部に延長された形態で構成されない。このような構成によって、従来の4マスク構造の代表的な問題として作用した波状ノイズ及び開口率の問題が改善される。また、ゲート電極がアクティブ層を遮るので、薄膜トランジスタでの漏洩電流も改善される。 40

上記構成は、本発明で提案した3マスク工程方法によって得ることができる。

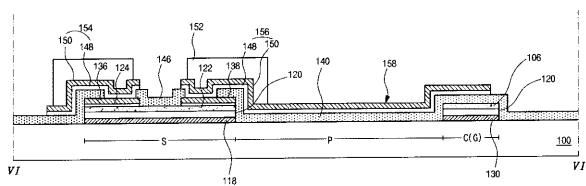

## 【0074】

以下、図9～図11を参照しながら、本発明の実施の形態1による3マスク工程によって液晶表示装置用アレイ基板を製作する方法について詳しく説明する。

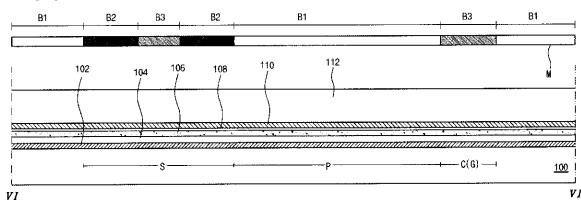

図9A～図9M、図10A～図10M及び図11A～図11Mは、図7内のV1-V1線、V1I-V1I線、V1II-V1II線に沿って切断した工程断面図であり、本発明の実施の形態1による工程順に示している。なお、図7内のV1-V1線は、薄膜トランジスタ及び画素領域の切断線であり、V1I-V1I線は、ゲートパッドの切断線である。 50

り、V I I I - V I I I 線は、データパッドの切断線である。

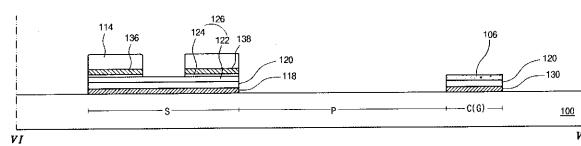

【0075】

図9A～図9C、図10A～図10C及び図11A～図11Cは、第1マスク工程を示している。

まず、図9A、図10A及び図11Aにおいて、基板100上に、スイッチング領域S、画素領域P、ゲート領域G、データ領域D及びストレージ領域Cを定義する。ストレージ領域Cは、ゲート領域Gの一部に定義される。

【0076】

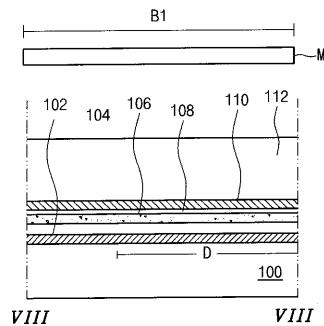

多数の領域S、P、G、D、Cが定義された基板100上に、第1導電層102と、第1絶縁膜104と、純粋非晶質シリコン層(a-Si:H)106と、不純物非晶質シリコン層(n+a-Si:H)108と、第2導電層110とを積層する。

10

また、第2導電層110の上部に、フォトレジストを塗布して感光層112を形成する。

。

【0077】

第1絶縁膜104は、窒化シリコンSiNX及び酸化シリコンSiO<sub>2</sub>を含む無機絶縁物質グループのうちから選択された一つまたは一つ以上の物質を蒸着して形成される。第1導電層102及び第2導電層110は、アルミニウムAl、アルミニウム合金AlNd、クロムCr、モリブデンMo、タンゲステンW、チタンTi、銅Cu、タンタルTa等を含む導電性金属グループのうちから選択された一つまたは一つ以上の金属を蒸着することにより形成される。

20

【0078】

ここで、第1導電層102としては、アルミニウムAlのような抵抗が低い金属を選択して形成し、選択された金属が化学的に弱いか、または、物理的に弱い場合には、これを保護するための別途の金属をさらに蒸着して形成する。

第2導電層110としては、モリブデンMoのように、乾式エッチングが可能な物質を使用する。

【0079】

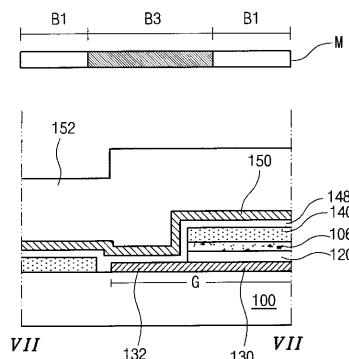

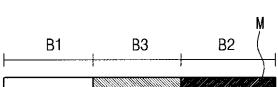

一方、感光層112を形成した後、感光層112が形成された基板100の離隔された上部に、透過部B1、遮断部B2及び半透過部B3で構成された第1マスクMを配置させる。

30

この際、スイッチング領域Sに対応して、半透過部B3を中心に両側に、遮断部B2を配置させる。ゲート領域(ストレージ領域Cを含む)Gに半透過部B3を配置させる。

【0080】

続いて、第1マスクMの上部から光を照射して下部の感光層112を露光する工程の後に、薬液を利用して現像する工程を行う。図9B、図10B及び図11Bに示すように、スイッチング領域Sには、中心部が低い高さで現像され段差を有する形状の第1感光パターン114が残って、ゲート領域Gには、元々の高さでパターニングされた第2感光パターン116が残る。従って、第1感光パターン114及び第2感光パターン116の周辺に第2導電層(図9A内の110)が露出される。

【0081】

第1感光パターン114及び第2感光パターン116の周辺に露出された第2導電層(図9A、図10A及び図11A内の110)と、その下部の不純物非晶質シリコン層(図9A、図10A、図11A内の108)と、純粋非晶質シリコン層(図9A、図10A及び図11A内の106)と、第1絶縁膜(図9A、図10A及び図11A内の104)と、第1導電層(図9A、図10A及び図11A内の102)を除去する工程を行う。

40

この際、第2導電層として乾式エッチング工程が可能な物質を使用した場合には、第2導電層及びその下部の不純物非晶質シリコン層と、純粋非晶質シリコン層及び第1絶縁膜とを同時に乾式エッチング方式で除去する。

一方、そうでない場合には、別途のエッチング方式を使用する。

【0082】

50

以後、第1導電層（図9A内の102）を除去する工程を行う。第1導電層（図9A内の102）がアルミニウムA1またはアルミニウム合金A1Ndで形成された場合、この工程は、一般的に、湿式エッチング工程によって除去されるので、上記工程とは別途の工程を行う。

【0083】

上記工程によって、スイッチング領域Sには、ゲート電極118、ゲート絶縁膜120、純粋非晶質シリコン層106及び不純物非晶質シリコン層108が積層された第1半導体層126と、ソース／ドレインパターン128とが残る。ゲート領域Gには、一端にゲートパッド132を含むゲート配線130と、ゲート絶縁膜120と導電パターン129とが残る。

10

【0084】

以下、第1感光パターン114の低い部分及び第2感光パターン116は、完全に除去するためのアッシング工程が施される。下部の露出されたソース／ドレインパターン128及び導電パターン129と、この下部の不純物非晶質シリコン層108とを除去する工程を行う。

【0085】

図9C、図10C及び図11Cに示すように、スイッチング領域Sには、アクティブ層122と、上部に離隔されたオーミックコンタクト層124と、離隔された第1ソース電極136及び第1ドレイン電極138が構成される。また、ゲート領域Gにおいては、導電パターン129と不純物非晶質シリコン層108が除去される。ゲート領域Gに残された純粋非晶質シリコン層106は、第2半導体層106に当たる。

20

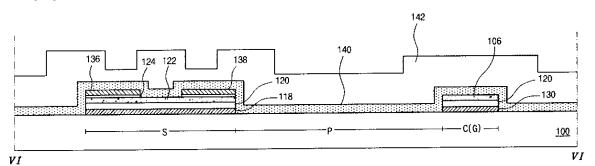

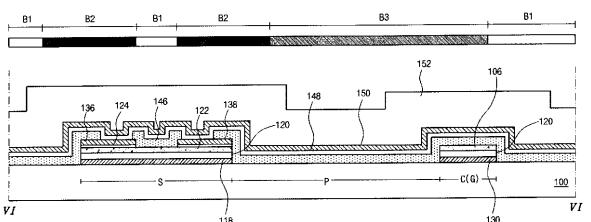

【0086】

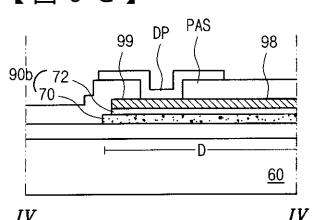

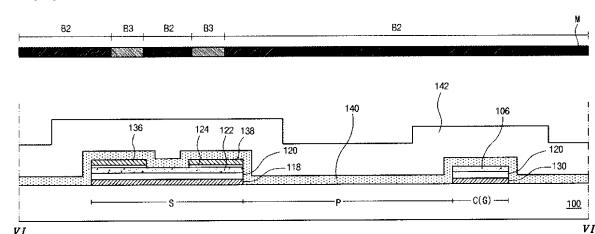

図9D～図9H、図10D～図10H及び図11D～図11Hは、第2マスク工程を工程順に示した工程断面図である。

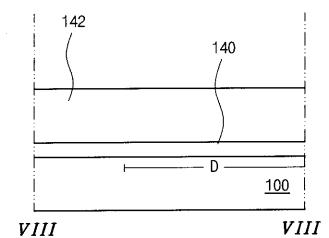

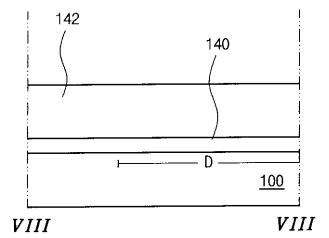

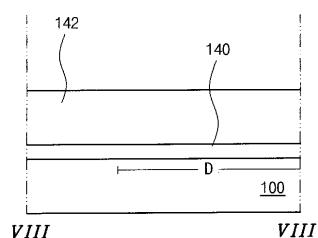

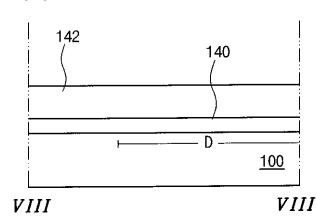

まず、図9D、図10D及び図11Dにおいて、第1ソース電極136及び第1ドレイン電極138が形成された基板100の全面に、無機絶縁物質グループのうちから選択された一つを蒸着して、第2絶縁膜140を形成する。

【0087】

第2絶縁膜140の上部に、フォトレジストを塗布して感光層142を形成する。

感光層142の離隔された上部に、透過部B1、遮断部B2及び半透過部B3で構成された第2マスクMを配置させる。

30

この際、スイッチング領域Sの第1ソース電極136及び第1ドレイン電極138の一部に対応して、半透過部B3を配置させる。また、ゲートパッド132に対応して透過部B1を配置させる。それ以外の領域には、遮断部B2を配置させる。

【0088】

続いて、第2マスクMの上部に光を照射して、下部の感光層142を露光し現像する工程を行う。

図9Eと図10Eと図11Eに示すように、感光層142においては、スイッチング領域Sの第1ソース電極136及び第1ドレイン電極138に対応した部分E1、E2は、低い高さで現像され、ゲートパッド132に対応した一部領域E3は、完全に除去されて、下部の第2絶縁膜140の一部が露出された状態（図10E参照）になる。

40

【0089】

続いて、ゲートパッド132に対応する上部の露出された第2絶縁膜140と、その下部の第2半導体層134と、その下部のゲート絶縁膜120とを完全に除去する工程を行う。

図9F、図10F及び図11Fに示すように、ゲート領域Gの端でゲートパッド132が露出された状態（図10F参照）になる。

【0090】

続いて、図9G、図10G及び図11Gに示すように、スイッチング領域Sに対応して、第1ソース電極136及び第1ドレイン電極138に対応した低い高さの感光層142

50

を除去するアッシング工程を行い、下部の第2絶縁膜140を露出する工程を行う。

【0091】

また、露出された部分の第2絶縁膜140を除去して、連続的に、感光層142を除去する工程を行う、図9Hと図10Hと図11Hに示したように、第1ソース電極136及び第1ドレイン電極138を各々露出するための第1コンタクトホール181及び第2コンタクトホール182が、第2絶縁膜140に形成される。

【0092】

第2絶縁膜140は、保護膜140に当たる。

また、保護膜140の一部は、第1ソース電極136と第1ドレイン電極138との離隔された間にに対応して、露出されたアクティブ層122を覆う。このような保護膜140部分は、エッチング防止膜146に当たる。

エッチング防止膜146は、アクティブ層122の表面の汚染または、以下の導電層を蒸着する際に、表面にダメージを与えるのを防ぐ機能を有する。

一方、スイッチング領域S及びゲートパッド132部分を除いた領域には、保護膜140が積層された状態で残っている。

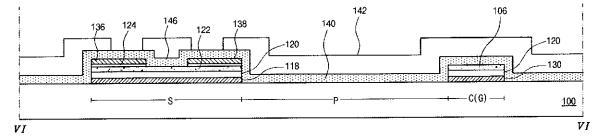

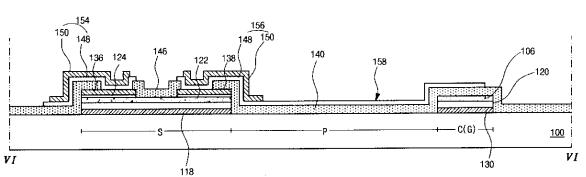

【0093】

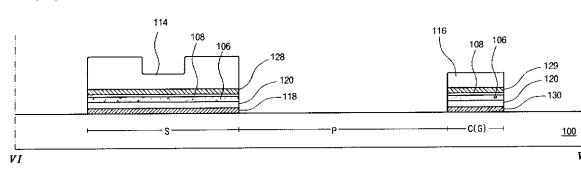

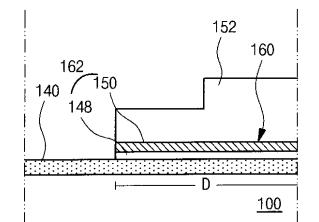

図9I～図9M、図10I～図10M及び図11I～図11Mは、第3マスク工程を工程順に示している。

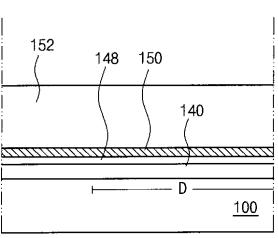

まず、図9I、図10I及び図11Iにおいて、スイッチング領域Sにエッチング防止膜146を形成し、ゲートパッド132が露出された基板100の全面に、第1層148及び第2層150を形成する。

【0094】

第1層148は、インジウム-スズ-オキサイドITO及びインジウム-ジンク-オキサイドIZOを含む透明な導電性金属グループのうちから選択された一つを蒸着して形成される。第2層150は、上部に導電性金属グループのうちから選択された一つまたは一つ以上の金属を蒸着することにより、不透明な導電性金属層150として形成される。

【0095】

第2層150の上部に、フォトレジストを塗布して感光層152を形成する。また、感光層152の離隔された上部に、透過部B1と遮断部B2と半透過部B3で構成されたマスクMを配置させる。

この際、スイッチング領域Sには、エッチング防止膜146に対応して透過部B1が位置し、透過部B1の両側に遮断部B2が位置する。また、画素領域P及びストレージ領域Cに対応して半透過部B3が位置する。ゲートパッド132に対応して半透過部B3が位置する。データ領域Dの端に対応して半透過部B3が位置する。半透過部B3が位置した領域を除いたデータ領域Dには、遮断部B2が位置する。それ以外の領域は、透過部B1が位置する。

【0096】

続いて、マスクMの上部に光を照射して下部の感光層152を露光した後、薬液を利用した現像工程を行う。

図9J、図10J及び図11Jに示すように、スイッチング領域Sに対応した部分は、エッチング防止膜146に対応した上部の第2層150を露出するように現像されて、画素領域P及びストレージ領域Cは、元々の高さより低くなった状態で現像される。

また、ゲートパッド132に対応した部分は、低い高さで現像される。

さらに、データ領域Dに対応する感光層152においては、データ領域Dの端に対応した部分は、低い高さで現像され、それ以外の領域は、元々の高さで残る。

【0097】

以下、感光層152の周辺に、第2層150が露出された状態になり、連続的に露出された第2層150及びその下部の第1層148を除去する工程を行う。

図9K、図10K及び図11Kに示すように、スイッチング領域Sに対応して、第1ソース電極136及び第1ドレイン電極138と接触する第2ソース電極154及び第2ド

10

20

30

40

50

レイン電極 156 を形成する。

【0098】

画素領域 P には、第 2 ドレイン電極 156 から延長された画素パターン 158 を形成する。

この際、第 2 ソース電極 154 及び第 2 ドレイン電極 156 と画素パターン 158 とは、第 1 層 148 及び第 2 層 150 の積層構造で形成される。

データ領域 D においても、第 2 ソース電極 154 と接触しながら一端にデータパッドパターン 162 を含む第 1 層 148 及び第 2 層 150 の積層構造のデータ配線 160 が形成される。ゲートパッド 132 の上部には、第 1 層 148 及び第 2 層 150 が積層された状態で残る。

10

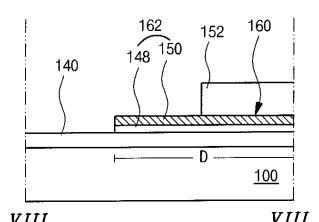

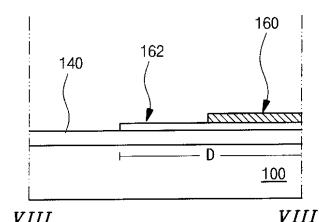

【0099】

以下、感光パターン 152 のうち、低い高さで現像された部分を除去するアッシング工程を行う。

図 9 L、図 10 L 及び図 11 L に示すように、画素パターン 158 と、データパッドパターン 162 の第 2 層 150 と、ゲートパッド 132 の上部の第 2 層 150 とを露出する。

【0100】

最後に、露出された第 2 層 150 のみを除去する工程を行う。

図 9 M、図 10 M 及び図 11 M に示すように、第 1 層 148 を有する画素電極 158 とデータパッド 162 とが形成されて、ゲートパッド 132 の上部には、第 1 層を有するゲートパッド電極 164 が形成される。

20

【0101】

以上のように、本発明の実施の形態 1 による 3 マスク工程によって液晶表示装置用アレイ基板を製造することができる。

一方、このようなアレイ基板と、これと向かい合う対応基板、例えば、カラーフィルタ基板を合着して、両基板間に液晶を注入して、液晶表示装置を製造することができる。

【図面の簡単な説明】

【0102】

【図 1】一般的な液晶表示装置を概略的に示した斜視図である。

【図 2】従来の液晶表示装置用アレイ基板の一部を拡大した平面図である。

30

【図 3 A】図 2 の I I - I I 線に沿って切断した断面図である。

【図 3 B】図 2 の V - V 線に沿って切断した断面図である。

【図 4 A】図 2 の I I - I I 線に沿って切断して、従来の工程順に示した工程断面図である。

【図 4 B】図 4 A に続く製造工程を示す断面図である。

【図 4 C】図 4 B に続く製造工程を示す断面図である。

【図 4 D】図 4 C に続く製造工程を示す断面図である。

【図 4 E】図 4 D に続く製造工程を示す断面図である。

【図 4 F】図 4 E に続く製造工程を示す断面図である。

【図 4 G】図 4 F に続く製造工程を示す断面図である。

40

【図 5 A】図 2 の I I I - I I I 線に沿って切断して、従来の工程順に示した工程断面図である。

【図 5 B】図 5 A に続く製造工程を示す断面図である。

【図 5 C】図 5 B に続く製造工程を示す断面図である。

【図 5 D】図 5 C に続く製造工程を示す断面図である。

【図 5 E】図 5 D に続く製造工程を示す断面図である。

【図 5 F】図 5 E に続く製造工程を示す断面図である。

【図 5 G】図 5 F に続く製造工程を示す断面図である。

【図 6 A】図 2 の I V - I V 線に沿って切断して、従来の工程順に示した工程断面図である。

50

- 【図 6 B】図 6 A に続く製造工程を示す断面図である。

- 【図 6 C】図 6 B に続く製造工程を示す断面図である。

- 【図 6 D】図 6 C に続く製造工程を示す断面図である。

- 【図 6 E】図 6 D に続く製造工程を示す断面図である。

- 【図 6 F】図 6 E に続く製造工程を示す断面図である。

- 【図 6 G】図 6 F に続く製造工程を示す断面図である。

- 【図 7】本発明の実施の形態 1 による液晶表示装置用アレイ基板の一部を拡大した平面図である。

- 【図 8 A】図 7 の V I - V I 線に沿って切断した断面図である。

- 【図 8 B】図 7 の V I I - V I I 線に沿って切断した断面図である。 10

- 【図 8 C】図 7 の V I I I - V I I I 線に沿って切断した断面図である。

- 【図 9 A】図 7 の V I - V I 線に沿って切断して、本発明の実施の形態 1 による工程順に示した工程断面図である。

- 【図 9 B】図 9 A に続く製造工程を示す断面図である。

- 【図 9 C】図 9 B に続く製造工程を示す断面図である。

- 【図 9 D】図 9 C に続く製造工程を示す断面図である。

- 【図 9 E】図 9 D に続く製造工程を示す断面図である。

- 【図 9 F】図 9 E に続く製造工程を示す断面図である。

- 【図 9 G】図 9 F に続く製造工程を示す断面図である。

- 【図 9 H】図 9 G に続く製造工程を示す断面図である。 20

- 【図 9 I】図 9 H に続く製造工程を示す断面図である。

- 【図 9 J】図 9 I に続く製造工程を示す断面図である。

- 【図 9 K】図 9 J に続く製造工程を示す断面図である。

- 【図 9 L】図 9 K に続く製造工程を示す断面図である。

- 【図 9 M】図 9 L に続く製造工程を示す断面図である。

- 【図 10 A】図 7 の V I I - V I I 線に沿って切断して、本発明の実施の形態 1 による工程順に示した工程断面図である。

- 【図 10 B】図 10 A に続く製造工程を示す断面図である。

- 【図 10 C】図 10 B に続く製造工程を示す断面図である。

- 【図 10 D】図 10 C に続く製造工程を示す断面図である。 30

- 【図 10 E】図 10 D に続く製造工程を示す断面図である。

- 【図 10 F】図 10 E に続く製造工程を示す断面図である。

- 【図 10 G】図 10 F に続く製造工程を示す断面図である。

- 【図 10 H】図 10 G に続く製造工程を示す断面図である。

- 【図 10 I】図 10 H に続く製造工程を示す断面図である。

- 【図 10 J】図 10 I に続く製造工程を示す断面図である。

- 【図 10 K】図 10 J に続く製造工程を示す断面図である。

- 【図 10 L】図 10 K に続く製造工程を示す断面図である。

- 【図 10 M】図 10 L に続く製造工程を示す断面図である。

- 【図 11 A】図 7 の V I I I - V I I I 線に沿って切断して、本発明の実施の形態 1 による工程順に示した工程断面図である。 40

- 【図 11 B】図 11 A に続く製造工程を示す断面図である。

- 【図 11 C】図 11 B に続く製造工程を示す断面図である。

- 【図 11 D】図 11 C に続く製造工程を示す断面図である。

- 【図 11 E】図 11 D に続く製造工程を示す断面図である。

- 【図 11 F】図 11 E に続く製造工程を示す断面図である。

- 【図 11 G】図 11 F に続く製造工程を示す断面図である。

- 【図 11 H】図 11 G に続く製造工程を示す断面図である。

- 【図 11 I】図 11 H に続く製造工程を示す断面図である。

- 【図 11 J】図 11 I に続く製造工程を示す断面図である。 50

【図11K】図11Jに続く製造工程を示す断面図である。

【図11L】図11Kに続く製造工程を示す断面図である。

【図11M】図11Lに続く製造工程を示す断面図である。

【符号の説明】

【0103】

100 基板、118 ゲート電極、120 ゲート絶縁膜、122 アクティブ層、

124 オーミックコンタクト層、130 ゲート配線、146 エッチング防止膜。

【図1】

【図2】

【図3A】

【図3B】

【図4A】

【図4A】

【図4B】

【図4C】

【図4D】

【図5B】

【図5C】

【図4F】

【図4G】

【図5A】

【図 5 D】

【図 5 G】

【図 5 E】

【図 6 A】

【図 5 F】

【図 6 B】

【図 6 C】

【図 6 F】

【図 6 D】

【図 6 G】

【図 6 E】

【図7】

【図8 A】

【図8 B】

【図8 C】

【図9 A】

【図9 D】

【図9 B】

【図9 E】

【図9 C】

【図9 F】

【図9 G】

【図9H】

【図9L】

【図9I】

【図9M】

【図9J】

【図10A】

【図9K】

【図10B】

【図10C】

【図10E】

【図 10 F】

【図 10 I】

【図 10 G】

【図 10 J】

【図 10 H】

【図 10 K】

【図 10 M】

【図 10 L】

【図 11 A】

【図 1 1 B】

【図 1 1 C】

【図 1 1 D】

【図 1 1 E】

【図 1 1 F】

【図 1 1 I】

【図 1 1 G】

【図 1 1 J】

【図 1 1 H】

【図 1 1 K】

VIII

VIII

【図 1 1 L】

VIII

VIII

【図 1 1 M】

VIII

VIII

---

フロントページの続き

(72)発明者 ドンヤン・キム

大韓民国、769-911、キョンブク、ウィソン・ゲン、ポンヤン・ミョン、プンニ 1-リ、

932-ビヨンジ

審査官 山口 裕之

(56)参考文献 特開2002-094064 (JP, A)

特開2005-108912 (JP, A)

特開2005-215278 (JP, A)

特開2004-004558 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1368

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP4668893B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2011-04-13 |

| 申请号            | JP2006353326                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 申请日     | 2006-12-27 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 申请(专利权)人(译)    | Eruji飞利浦杜迪股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 当前申请(专利权)人(译)  | Eruji显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | ドンヤンキム                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | ドンヤン・キム                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| IPC分类号         | G02F1/1368 H01L29/786 H01L21/336                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | H01L29/66765 G02F1/136209 G02F1/136227 G02F1/1368 G02F2001/136236 G02F2001/136295 H01L27/1214 H01L27/124 H01L27/1288                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G02F1/1368 H01L29/78.612.D H01L29/78.627.C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 2H092/GA43 2H092/JA26 2H092/JA29 2H092/JA34 2H092/JA38 2H092/JA42 2H092/JA44 2H092 /JA46 2H092/JA47 2H092/JB33 2H092/JB57 2H092/JB64 2H092/JB66 2H092/KB04 2H092/KB14 2H092/MA14 2H092/MA16 2H092/MA18 2H092/MA27 2H092/MA37 2H092/NA07 2H092/NA24 2H092 /NA27 2H192/AA24 2H192/BC31 2H192/CB05 2H192/CB71 2H192/DA02 2H192/EA04 2H192/FA65 2H192/HA44 2H192/HA47 5F110/AA06 5F110/AA16 5F110/AA30 5F110/BB01 5F110/CC07 5F110 /EE02 5F110/EE03 5F110/EE04 5F110/EE06 5F110/EE43 5F110/FF02 5F110/FF03 5F110/FF27 5F110/GG02 5F110/GG15 5F110/HK09 5F110/HK16 5F110/NN72 5F110/QQ01 |         |            |

| 代理人(译)         | 英年古河<br>Kajinami秩序<br>上田俊一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 审查员(译)         | 山口博之                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 优先权            | 1020060059346 2006-06-29 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 其他公开文献         | JP2008009372A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

**摘要(译)**

要解决的问题：为了获得一种液晶显示装置，其阵列基板（其中构成包括防蚀刻膜的薄膜晶体管）可以通过三种掩模工艺制造，并获得制造该液晶显示装置的方法。

**ŽSOLUTION**：液晶显示装置包括栅极线130和连接到栅极线的栅电极；栅电极和栅极线130上的栅极绝缘层120；栅极线130上方的栅极绝缘层120上的有源层122；有源层122上的欧姆接触层124；欧姆接触层124上的第一源极136和漏极138；第二源极和漏极154和156分别连接到第一源极136和漏极138；数据线从第二源电极154延伸并与栅极线130交叉以限定像素区域P；像素电极158位于像素区P中并从第二漏电极156延伸

【 図 2 】