**【特許請求の範囲】****【請求項 1】**

複数のゲートバスライン、当該ゲートバスラインに平行な複数の共通バスライン、および前記ゲートバスラインと前記共通バスラインに交差する複数のドレインバスラインを有する第1基板と、

所定間隔をあけて前記第1基板に対向して保持された第2基板と、

前記第1基板および前記第2基板の間に配置された液晶層と、

前記ゲートバスラインと前記ドレインバスラインによって画定されると共に、マトリックス状に配置された複数の画素領域とを備え、

前記画素領域の各々は、薄膜トランジスタと、当該薄膜トランジスタに電気的に接続された画素電極と、対応する前記共通バスラインに電気的に接続された共通電極とを備えており、

前記画素電極と前記共通電極との間に印加される前記第1基板の表面に略平行な電界により、前記画素領域の各々において前記液晶層の液晶分子を前記第1基板に平行な面内で回転させることによって表示を行う横電界方式のアクティブマトリックス型液晶表示装置において、

前記画素領域の各々には、当該画素領域を画定する前記ドレインバスラインに隣接し且つそれに沿って延在する遮光電極が設けられており、

前記遮光電極は、電気的に孤立していると共に、当該画素領域に対応する前記画素電極の前記ドレインバスラインに隣接して延在する部分と絶縁膜を挟んで重なっていることを特徴とする液晶表示装置。

**【請求項 2】**

複数のゲートバスライン、当該ゲートバスラインに平行な複数の共通バスライン、および前記ゲートバスラインと前記共通バスラインに交差する複数のドレインバスラインを有する第1基板と、

所定間隔をあけて前記第1基板に対向して保持された第2基板と、

前記第1基板および前記第2基板の間に配置された液晶層と、

前記ゲートバスラインと前記ドレインバスラインによって画定されると共に、マトリックス状に配置された複数の画素領域とを備え、

前記画素領域の各々は、薄膜トランジスタと、当該薄膜トランジスタに電気的に接続された画素電極と、対応する前記共通バスラインに電気的に接続された共通電極とを備えており、

前記画素電極と前記共通電極との間に印加される前記第1基板の表面に略平行な電界により、前記画素領域の各々において前記液晶層の液晶分子を前記第1基板に平行な面内で回転させることによって表示を行う横電界方式のアクティブマトリックス型液晶表示装置において、

前記画素領域の各々には、当該画素領域を画定する前記ドレインバスラインに隣接し且つそれに沿って延在する遮光電極が設けられており、

前記遮光電極は、当該画素領域に対応する前記画素電極の前記ドレインバスラインに隣接して延在する部分と部分的に重なっていると共に、当該画素領域内のいずれかの箇所において前記画素電極に電気的に接続されていることを特徴とする液晶表示装置。

**【請求項 3】**

前記遮光電極が、絶縁膜を挟んで前記ドレインバスラインとは異なる層に形成されている請求項1または2に記載の液晶表示装置。

**【請求項 4】**

前記画素電極の前記ドレインバスラインに隣接して延在する前記部分が、櫛歯状とされ、前記遮光電極が、前記ドレインバスラインに沿って延在する帯状とされている請求項1または2に記載の液晶表示装置。

**【請求項 5】**

前記画素電極が、前記ドレインバスラインに沿って延在する複数の櫛歯状部を有してい

10

20

30

40

50

ると共に、前記画素電極の外側にある2本の前記櫛歯状部が、それぞれ、当該画素領域を画定する2本の前記ドレインバスラインに隣接して延在する前記部分とされており、

前記遮光電極が帯状であって、2本の前記遮光電極が、当該画素領域を画定する2本の前記ドレインバスラインにそれぞれ沿って延在するように形成されている請求項1または2に記載の液晶表示装置。

#### 【請求項6】

前記画素領域の各々に対応して、前記ドレインバスラインが略V字状に屈曲せしめられており、それに対応して前記画素電極と前記共通電極が略V字状に屈曲せしめられている請求項1～5のいずれか1項に記載の液晶表示装置。

#### 【請求項7】

前記画素電極が、絶縁膜を挟んで前記ドレインバスラインとは異なる層に形成されている請求項1～6のいずれか1項に記載の液晶表示装置。

#### 【請求項8】

前記共通電極が前記画素電極と同じ層に形成されている請求項1～7のいずれか1項に記載の液晶表示装置。

#### 【請求項9】

前記画素電極および前記共通電極の少なくとも一方が、透明導電体により形成されている請求項1～8のいずれか1項に記載の液晶表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、液晶表示装置に関し、さらに言えば、横電界(In-Plane Switching、IPS)方式のアクティブマトリックス型液晶表示装置に関する。

##### 【背景技術】

##### 【0002】

一般に、液晶表示装置(LCD)は薄型軽量・低消費電力といった特徴を有する。特に、縦横のマトリックス状に配列した個々の画素を能動素子によって駆動するアクティブマトリックス型液晶表示装置(AM-LCD)は、高画質のフラットパネル・ディスプレイとして認知されており、中でも個々の画素をスイッチングする能動素子として薄膜トランジスタ(Thin-Film Transistor、TFT)を用いたもの(TFT-LCD)が広く普及している。

##### 【0003】

多くのAM-LCDでは、ツイステッドネマチック(Twisted Nematic、TN)型液晶の電気光学効果を利用しておあり、2枚の基板間に挟持された液晶に当該基板面に概ね垂直な電界を印加して、当該液晶の分子を変位させることにより画像を表示する。これを「縦電界方式」という。一方、当該基板面に概ね平行な電界により、当該基板面に概ね平行な面内で液晶分子を変位させることによって画像を表示する「横電界方式」の液晶表示装置も、以前から知られている。この横電界方式の液晶表示装置についても、縦電界方式と同様に種々の改良がなされて來ておあり、そのいくつかを例示すると、以下のとおりである。

##### 【0004】

特許文献1(米国特許第3807831号明細書、1974年発行)には、横電界方式の液晶表示装置において、相互に噛合する櫛歯状電極を用いる構成が開示されている(クレーム1、FIG.1～4、FIG.11を参照)。

##### 【0005】

特許文献2(特開昭56-091277号公報)には、TN型液晶の電気光学効果を利用したアクティブマトリックス型液晶表示装置において、特許文献1と同様の相互に噛合する櫛歯状電極を用いることにより、共通電極とドレインバスラインの間の寄生容量、あるいは共通電極とゲートバスラインとの間の寄生容量を低減する技術が開示されている(特許請求の範囲第2項、図7、図9～13を参照)。

##### 【0006】

10

20

30

40

50

特許文献3（特開平7-036058号公報）には、TFTを用いたアクティブマトリックス型液晶表示装置において、櫛歯状電極を使用しないで横電界方式を実現する技術が開示されている。この技術では、共通電極と映像信号電極または共通電極と液晶駆動電極を、絶縁膜を介して互いに異なる層に形成すると共に、共通電極または液晶駆動電極の平面形状をリング型、十字型、T字型、二字型、工字型あるいは梯子型といった形に形成している（特許請求の範囲第1項、第5項、図1～23を参照）。

【0007】

特許文献4（特開2001-222030号公報）には、液晶を駆動する櫛歯形状の電極（画素電極および共通電極）を、ドレインバスライン（データバスライン）よりも上層（液晶層に近く）に、透明導電体によって構成する技術が開示されている（要約、図3～5を参照）。

10

【0008】

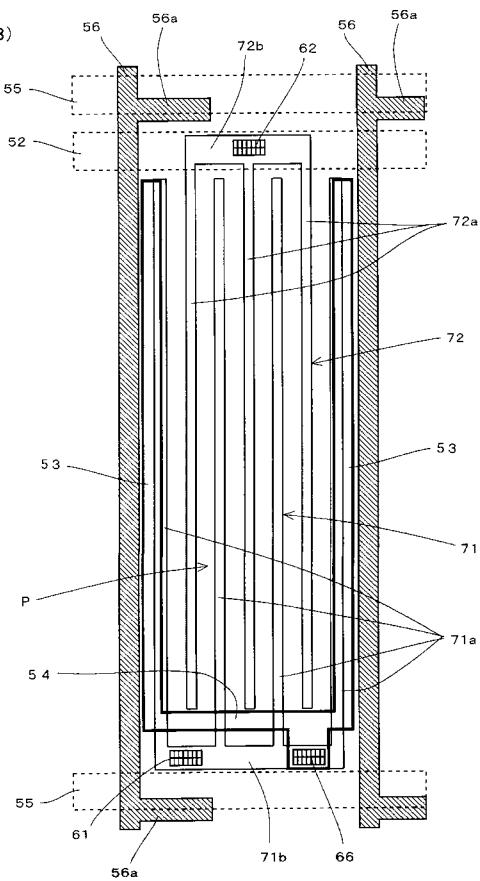

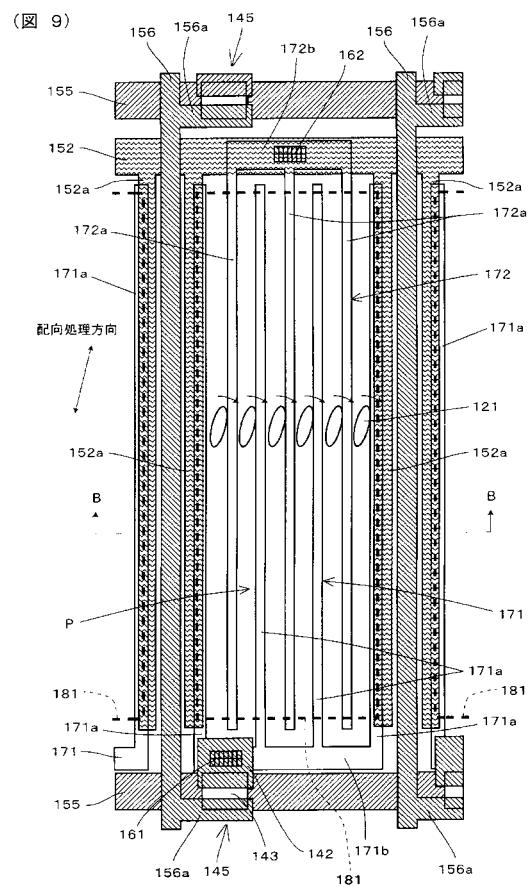

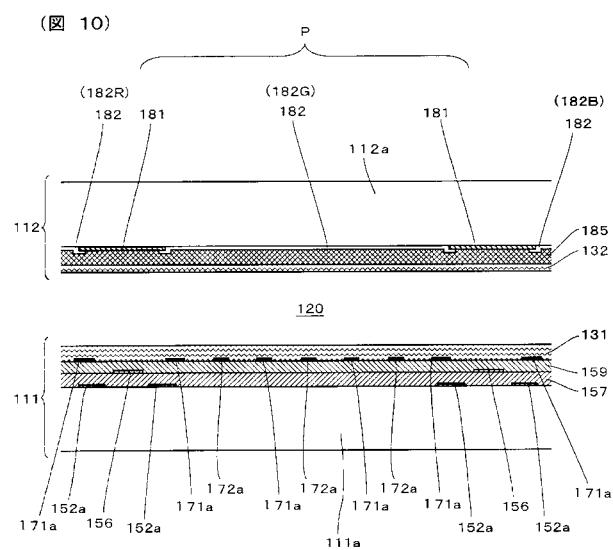

図9は、特許文献4に開示された従来の横電界方式の液晶表示装置に使用された第1基板（アクティブマトリックス基板）の構成例を示す平面図であり、図10は当該液晶表示装置の図9のB-B線に沿った断面図である。図9および図10は共に、一つの画素領域の構成を示している。

【0009】

図9および図10に示した従来の液晶表示装置は、図9の横方向（水平方向）に延在し且つ同図の縦方向（垂直方向）に等間隔で配置された複数本のゲートバスライン155と、図9の縦方向に延在し且つ同図の横方向に等間隔で配置された複数本のドレインバスライン156とを有している。これらのゲートバスライン155とドレインバスライン156によって画定される略矩形領域の各々には、画素領域Pが形成されている。これらの画素領域P（すなわち画素）は、全体として縦横のマトリックス状に配列されている。この従来の液晶表示装置は、さらに、複数のゲートバスライン155の各々と平行に延在する複数の共通バスライン152を有している。これらの共通バスライン152は、画素領域P毎に形成された共通電極172を電気的に相互接続するために設けられたものであり、ゲートバスライン155の各々の近傍にそれから所定距離をあけて配置されている。ゲートバスライン155とドレインバスライン156と共にバスライン152は、いずれも不透明の金属膜により形成されている。

20

【0010】

各画素領域Pの内部において、対応する共通バスライン152は、当該画素領域Pを画定する2本のドレインバスライン156に沿ってそれぞれ延在する2本の帯状の遮光部152aを有している。これら遮光部152aは、当該共通バスライン152と一体的に形成されている。図9の左側の遮光部152aは、同図の左側にあるドレインバスライン156の右側（当該画素領域Pの内側）に近接して配置されている。図9の右側の遮光部152aは、同図の右側にあるドレインバスライン156の左側（当該画素領域Pの内側）に近接して配置されている。これら2本の遮光部152aは、互いに同じ平面形状（パターン）を持っている。

30

【0011】

各画素領域Pに対しては、対応するゲートバスライン155と対応するドレインバスライン156との交点の近傍においてTFT145が形成されている。各TFT145は、対応するゲートバスライン155と一体的に形成されたゲート電極（図示せず）と、ゲート絶縁膜157を介して当該ゲート電極に重ねて形成されたアイランド状の半導体膜143と、対応するドレインバスライン156と一体的に形成され且つ当該半導体膜143に部分的に重ねて形成されたドレイン電極156aと、当該ドレイン電極156aに対して所定間隔をあけて対向・配置され且つ当該半導体膜143に部分的に重ねて形成されたソース電極142とから構成されている。ゲート電極、ドレイン電極156aおよびソース電極142は、不透明の金属膜により形成されている。

40

【0012】

各画素領域Pの内部には、液晶駆動電界を発生させる画素電極171および共通電極1

50

7 2 が形成されている。画素電極 1 7 1 および共通電極 1 7 2 は、いずれも、透明導電体によって形成されており、その平面形状は櫛形である。

【 0 0 1 3 】

画素電極 1 7 1 は、当該画素領域 P の内部で TFT 1 4 5 の側に配置された帯状の基部 1 7 1 b と、基部 1 7 1 b から TFT 1 4 5 の反対側に向かって（図 9 では上方に向かって）突出する 4 本の櫛歯状部 1 7 1 a とから形成されている。4 本の櫛歯状部 1 7 1 a は、ドレインバスライン 1 5 6 と平行に延在しており、基部 1 7 1 b に沿って（図 9 では横方向に）等間隔に配置されている。各櫛歯状部 1 7 1 a の先端は、対応する共通バスライン 1 5 2 の近傍まで達している。画素電極 1 7 1 の外側にある 2 本の櫛歯状部 1 7 1 a は、それぞれ、当該画素領域 P を画定する 2 本のドレインバスライン 1 5 6 の近傍にある遮光部 1 5 2 a と部分的に重なっている。画素電極 1 7 1 は、その基部 1 7 1 b において、コンタクトホール 1 6 1 を介して TFT 1 4 5 のソース電極 1 4 2 に電気的に接続されている。

10

【 0 0 1 4 】

共通電極 1 7 2 は、当該画素領域 P の内部で TFT 1 4 5 とは反対側に配置された帯状の基部 1 7 2 b と、基部 1 7 2 b から TFT 1 4 5 の側に向かって（図 9 では下方に向かって）突出する 3 本の櫛歯状部 1 7 2 a とから形成されている。3 本の櫛歯状部 1 7 2 a は、ドレインバスライン 1 5 6 と平行に延在しており、基部 1 7 2 b に沿って（図 9 では横方向に）等間隔に配置されている。各櫛歯状部 1 7 2 a の先端は、画素電極 1 7 1 の基部 1 7 1 b の近傍まで達している。3 本の櫛歯状部 1 7 2 a は、画素電極 1 7 1 の 4 本の櫛歯状部 1 7 1 a に対して交互に配置されている。従って、これらの櫛歯状部 1 7 2 a と櫛歯状部 1 7 1 a とは、相互に噛み合った状態にある。共通電極 1 7 2 は、その基部 1 7 2 b において、コンタクトホール 1 6 2 を介して共通バスライン 1 5 2 に電気的に接続されている。

20

【 0 0 1 5 】

図 10 に示すように、この液晶表示装置は、第 1 基板（アクティブマトリックス基板）1 1 1 と、これに所定間隔をおいて対向せしめられた第 2 基板（対向基板）1 1 2 と、両基板 1 1 1 および 1 1 2 の間に配置された液晶層 1 2 0 とを備えている。

【 0 0 1 6 】

第 1 基板 1 1 1 のガラス基板 1 1 1 a の表面には、ゲートバスライン 1 5 5 と、共通バスライン 1 5 2 と、遮光部 1 5 2 a と、TFT 1 4 5 のゲート電極とが形成されており、それらを覆うようにゲート絶縁膜 1 5 7 が形成されている（図 10 では遮光部 1 5 2 a のみが示されている）。ゲート電極は、対応するゲートバスライン 1 5 5 と一体的に形成されている。ゲート絶縁膜 1 5 7 の上には、ドレインバスライン 1 5 6 と、TFT 1 4 5 の半導体膜 1 4 3 、ドレイン電極 1 5 6 a およびソース電極 1 4 2 とが形成されており、これらは保護絶縁膜 1 5 9 で覆われている（図 10 ではドレインバスライン 1 5 6 のみが示されている）。保護絶縁膜 1 5 9 の上には、画素電極 1 7 1 と共通電極 1 7 2 が形成されている（図 10 では画素電極 1 7 1 の櫛歯状部 1 7 1 a と共通電極 1 7 2 の櫛歯状部 1 7 1 a のみが示されている）。

30

【 0 0 1 7 】

このように、共通バスライン 1 5 2 はガラス基板 1 1 1 a の表面に形成され、ドレインバスライン 1 5 6 はゲート絶縁膜 1 5 7 の上に形成されているので、共通バスライン 1 5 2 はドレインバスライン 1 5 6 よりも下層に（液晶層 1 2 0 から遠い層に）配置されていることになる。また、ゲートバスライン 1 5 5 も、ガラス基板 1 1 1 a の表面に形成されているので、ゲートバスライン 1 5 5 もドレインバスライン 1 5 6 よりも下層に（液晶層 1 2 0 から遠い層に）配置されている。画素電極 1 7 1 および共通電極 1 7 2 は、保護絶縁膜 1 5 9 の上に形成されているので、ドレインバスライン 1 5 6 よりも上層に（液晶層 1 2 0 に近い層に）配置されている。

40

【 0 0 1 8 】

以上の構成を持つ第 1 基板 1 1 1 の表面（内面）、すなわち保護絶縁膜 1 5 9 の上には

50

、有機高分子膜からなる配向膜 131 が形成されている。従って、画素電極 171 と共に電極 172 は、配向膜 131 によって覆われている。この配向膜 131 の表面には、所定の配向処理が施されている。

【0019】

他方、第2基板 112 のガラス基板 112a の表面には、各画素領域 P に対応して RGB の 3 原色からなる色層 182 が形成されており、各画素領域 P に対応する領域以外の領域には遮光用のブラックマトリックス層 181 が形成されている。色層 182 は、所定形状にパターン化された赤色層 182R と緑色層 182G と青色層 182B とから構成されている。ブラックマトリックス層 181 の平面形状（パターン）は、第1基板 111 上に不透明金属で形成されている構成要素、すなわちゲートバスライン 155、ドレインバスライン 156、共通バスライン 152、遮光部 152a および TFT145 を覆うと共に、各画素領域 P の内部に矩形の開口領域（透光領域）を形成するように設定されている。色層 182 は、これら開口部（透光部）内に配置されている。

10

【0020】

色層 182 とブラックマトリックス層 181 は、オーバーコート層 185 によって覆われている。このオーバーコート層 185 は、ガラス基板 112a の表面全体に形成されており、色層 182 とブラックマトリックス層 181 を保護するため、またそれらにより生じる段差を平坦化するために設けられている。ブラックマトリックス層 181 の上には、基板間隔を制御するための柱状スペーサ（図示せず）が形成されている。

20

【0021】

以上の構成を持つ第2基板 112 の表面（内面）、すなわちオーバーコート層 185 の上には、有機高分子膜からなる配向膜 132 が形成されている。この配向膜 132 の表面には、所定の配向処理が施されている。

【0022】

第1基板（アクティブマトリックス基板）111 と第2基板（対向基板）112 は、配向膜 131 および 132 が形成された面を内側にして所定間隔をおいて重ね合わされている。両基板 111 と 112 の間には液晶が封入され、液晶層 120 を形成している。換言すれば、液晶層 120 は両基板 111 と 112 によって挟持されている。第1基板 111 と第2基板 112 の外側（ガラス基板 111a と 112a の裏面）には、一対の偏光板（図示せず）がそれぞれ配置されている。

30

【0023】

配向膜 131 および 132 の表面の配向処理により、無電界時には、図 9 に矢印で示すように、液晶層 120 の液晶分子 121 は、同図の縦方向（垂直方向）から一定角度（一例として時計回り方向に 15 度程度）ずれた方向に沿って平行に配向せしめられる。つまり、液晶分子 121 の初期配向方位は、図 9 に矢印で示す方向とされている。また、前記一対の偏光板の透過軸の方向は、互いに直交せしめられており、これら偏光板の一方の透過軸は、液晶分子 121 の無電界時の配向方向（初期配向方位）に一致している。

【0024】

次に、図 9 および図 10 に示した従来の液晶表示装置の製造方法について説明する。

40

【0025】

第1基板 111 は次のようにして製造される。まず、ガラス基板 111a の表面全体にクロム（Cr）膜を形成し、その後この Cr 膜を所定形状にパターン化して、複数のゲートバスライン 155 と、複数の共通バスライン 152 と、複数の遮光部 152a とをガラス基板 111a の表面に形成する。ゲート電極は、対応するゲートバスライン 155 と一緒に形成される。次に、ガラス基板 111a の表面全体に窒化シリコン（SiN<sub>x</sub>）からなるゲート絶縁膜 157 を形成し、ゲート電極とゲートバスライン 155 と共にバスライン 152 と遮光部 152a とを覆う。

【0026】

続いて、ゲート絶縁膜 157 上にアモルファスシリコン（a-Si）膜を形成してからこれをアイランド状にパターン化し、TFT145 用の複数の半導体膜 143 を形成する

50

。これら半導体膜 143 の各々は、ゲート絶縁膜 157 を挟んで対応するゲートバスライン 155 と重なる位置に配置される。さらに、ゲート絶縁膜 157 上に Cr 膜を形成してからこれをパターン化し、ゲート絶縁膜 157 上に複数のドレインバスライン 156 と複数のドレイン電極 156a と複数のソース電極 142 を形成する。その後、ガラス基板 111a の表面全体にわたって SiN<sub>x</sub> からなる保護絶縁膜 159 を形成し、ドレインバスライン 156、ドレイン電極 156a およびソース電極 142 を覆う。

#### 【0027】

続いて、各ソース電極 142 と重なる所定の位置で保護絶縁膜 159 を選択的に除去し、各ソース電極 142 に達する複数のコンタクトホール 161 を形成する、また、各共通バスライン 152 と重なる所定の位置で保護絶縁膜 159 とゲート絶縁膜 157 を選択的に除去し、各共通バスライン 152 に達する複数のコンタクトホール 162 を形成する。

10

#### 【0028】

その後、保護絶縁膜 159 上にITO (Indium Tin Oxide) 等からなる透明導電体膜を形成してからこれを所定形状にパターン化し、複数の櫛歯状の画素電極 171 と複数の櫛歯状の共通電極 172 を形成する。この時、各画素電極 171 は、対応するコンタクトホール 161 を介して対応するソース電極 142 に接続され、各共通電極 172 は、対応するコンタクトホール 162 を介して対応する共通バスライン 152 に接続される。こうして第1基板 111 が完成する。

#### 【0029】

第2基板 112 は、次のようにして製造される。まず、ガラス基板 112a の表面に、所定形状 (パターン) を持つブラックマトリックス層 181 と色層 182 を形成する。色層 182 を形成する際には、それぞれ所定形状を持つ赤色層 182R と緑色層 182G と青色層 182B を適当な順序で順次形成すればよい。次に、ガラス基板 112a の表面全体にオーバーコート層 185 を形成し、ブラックマトリックス層 181 と色層 182 を覆う。その後、オーバーコート層 185 上に柱状スペーサー (図示せず) を形成する。こうして第2基板 112 が完成する。

20

#### 【0030】

続いて、このようにして製造された第1基板 (アクティブマトリックス基板) 111 と第2基板 (対向基板) 112 の表面に、それぞれ、ポリイミドからなる配向膜 131 と 132 が形成される。配向膜 131 と 132 の表面には、一様に、所定の配向処理が施される。

30

#### 【0031】

その後、両基板 111 および 112 は、例えば 4.0 μm の間隔をあけて重ね合わせられる。そして、真空チャンバー (図示せず) 内で、両基板 111 および 112 の間の隙間に例えば屈曲率異方性が 0.075 のネオマチック液晶を注入してから、この空間を封止する。その後、両基板 111 および 112 の外側にそれぞれ偏光板 (図示せず) を貼り合わせると、液晶表示パネルが完成する。

#### 【0032】

この液晶表示パネルに所定の駆動用LSI (Large-Scale Integrated Circuit) とバッカライト装置を装着すると、図9および図10に示した従来の液晶表示装置が完成する。

40

#### 【0033】

図9および図10に示した従来の液晶表示装置では、電圧印加時の液晶駆動電界は、およそ同図の横方向 (水平方向) に一様に発生する。このため、無電界時に初期配向方向 (図9の矢印の方向) に一様に配向していた液晶分子 121 は、前記液晶駆動電界によって時計回り方向に回転せしめられ、配向状態が変化する。この配向状態の変化により各画素領域 P (画素) の透過率が変調せしめられるため、所望の画像を表示することが可能となる。

#### 【0034】

また、図9および図10に示した従来の液晶表示装置では、液晶駆動電界を発生させる画素電極 171 と共通電極 172 がいずれも透明導電体によって形成されているため、画

50

素電極 171 と共に電極 172 が存在する領域においても光が透過する。このため、画素電極 171 と共に電極 172 を不透明金属によって形成した場合と比較して、開口率および透過率が向上する。

#### 【0035】

また、このようにしてブラックマトリックス層 181 の開口領域に存在する不透明金属部分が減少しているため、不透明金属部分のエッジによる光散乱や、当該エッジの近傍での段差による液晶配向の乱れが抑制される。この光散乱や液晶配向の乱れは、黒表示時の光漏れの原因となるが、この液晶表示装置ではこれらが抑制されるため、表示コントラストが向上する。

#### 【0036】

また、不透明金属部分がブラックマトリックス層 181 の開口領域内に存在すると、比較的明るい環境で使用した時に入射光を不透明金属が反射するために「明所コントラスト」の低下が顕著となる。しかし、この液晶表示装置では不透明金属部分が存在しないため、明所コントラストの低下が抑制される。

#### 【0037】

さらに、各ドレインバスライン 156 の近傍にそれに沿って、対応する共通バスライン 152 と一緒に形成された遮光部 152a が設けられていると共に、これら遮光部 152a とそれらに隣接するドレインバスライン 156 の間の領域は、ブラックマトリックス層 181 で覆われているため、各ドレインバスライン 156 から漏洩する電界によって生じる光漏れや縦クロストークの発生が抑制される。

10

20

30

40

【特許文献 1】米国特許第 3807831 号公報

【特許文献 2】特開昭 56-091277 号公報

【特許文献 3】特開平 7-036058 号公報

【特許文献 4】特開 2001-222030 号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0038】

図 9 および図 10 に示した従来の液晶表示装置では、上述したような利点があるが、その反面、共通バスライン 152 と一緒に形成された遮光部 152a の各々が、長い距離にわたって対応するドレインバスライン 156 に隣接して延在するため、各ドレインバスライン 156 と対応する共通バスライン 152 (共通電極 172) との結合容量 (寄生容量) が大きい。このため、ドレインバスライン 156 の電位変動 (信号電圧の変化) の影響が共通バスライン 152 を介して共通電極 172 に伝達される、換言すれば、ドレインバスライン 156 の電位変動に起因して、共通バスライン 152 に電気的に接続された共通電極 172 の電位 (これは本来、一定電位に保持されるべきである) に変動が生じる。その結果、横クロストークが発生するという問題がある。

#### 【0039】

本発明は、上記従来の液晶表示装置の持つこの問題を解決すべくなされたものであって、その目的とするところは、各ドレインバスラインとそれに対応する共通バスラインとの結合容量 (寄生容量) に起因する横クロストークを、簡単な構成で抑制することができる横電界方式のアクティブマトリクス型液晶表示装置を提供することにある。

#### 【0040】

本発明の他の目的は、図 9 および図 10 に示した従来の液晶表示装置よりも画質が改善された横電界方式のアクティブマトリクス型液晶表示装置を提供することにある。

#### 【0041】

ここに明記しない本発明の他の目的は、以下の説明及び添付図面から明らかであろう。

#### 【課題を解決するための手段】

#### 【0042】

(1) 本発明の第 1 の液晶表示装置は、

複数のゲートバスライン、当該ゲートバスラインに平行な複数の共通バスライン、およ

50

び前記ゲートバスラインと前記共通バスラインに交差する複数のドレインバスラインを有する第1基板と、

所定間隔をあけて前記第1基板に対向して保持された第2基板と、

前記第1基板および前記第2基板の間に配置された液晶層と、

前記ゲートバスラインと前記ドレインバスラインによって画定されると共に、マトリックス状に配置された複数の画素領域とを備え、

前記画素領域の各々は、薄膜トランジスタと、当該薄膜トランジスタに電気的に接続された画素電極と、対応する前記共通バスラインに電気的に接続された共通電極とを備えており、

前記画素電極と前記共通電極との間に印加される前記第1基板の表面に略平行な電界により、前記画素領域の各々において前記液晶層の液晶分子を前記第1基板に平行な面内で回転させることによって表示を行う横電界方式のアクティブマトリックス型液晶表示装置において、

前記画素領域の各々には、当該画素領域を画定する前記ドレインバスラインに隣接し且つそれに沿って延在する遮光電極が設けられており、

前記遮光電極は、電気的に孤立していると共に、当該画素領域に対応する前記画素電極の前記ドレインバスラインに隣接して延在する部分と絶縁膜を挟んで重なっていることを特徴とするものである。

#### 【0043】

本発明の第1の液晶表示装置では、前記画素領域の各々に、当該画素領域を画定する前記ドレインバスラインに隣接し且つそれに沿って延在する前記遮光電極が設けられている。そして、前記遮光電極は、電気的に孤立していると共に、当該画素領域に対応する前記画素電極の前記ドレインバスラインに隣接して延在する部分と前記絶縁膜を挟んで重なっている。この時、前記遮光電極の電位は、対応する前記画素電極の電位（信号電圧に相当する電位）に近い値になる。これは、孤立している前記遮光電極が、前記絶縁膜を挟んで、当該画素領域に対応する前記画素電極の前記ドレインバスラインに隣接して延在する前記部分と重なっているからである。このため、前記ドレインバスラインと対応する前記遮光電極との電位差は非常に小さい、すなわち、前記ドレインバスラインと対応する前記遮光電極との結合容量（寄生容量）が非常に小さいものとなる。

#### 【0044】

他方、図9および図10に示した従来の液晶表示装置では、前記遮光部は対応する前記共通バスラインと一体的に形成されているので、前記共通電極の電位に等しい。したがって、前記ドレインバスラインと対応する前記共通バスラインとの電位差は、前記ドレインバスラインに供給される信号電圧に相当する電位と前記共通電極の電位との差に等しくなる。これは、前記ドレインバスラインと対応する前記遮光部との結合容量（寄生容量）がかなり大きいことを意味している。

#### 【0045】

このように、本発明の第1の液晶表示装置における前記ドレインバスラインと対応する前記遮光電極との結合容量（寄生容量）は、図9および図10に示した従来の液晶表示装置における前記ドレインバスラインと対応する前記共通バスライン（遮光部）との結合容量（寄生容量）に比べて小さくなるため、横クロストークの発生を抑制することができる。また、横クロストークの抑制により、画質が改善される。

#### 【0046】

（2） 本発明の第2の液晶表示装置は、

複数のゲートバスライン、当該ゲートバスラインに平行な複数の共通バスライン、および前記ゲートバスラインと前記共通バスラインに交差する複数のドレインバスラインを有する第1基板と、

所定間隔をあけて前記第1基板に対向して保持された第2基板と、

前記第1基板および前記第2基板の間に配置された液晶層と、

前記ゲートバスラインと前記ドレインバスラインによって画定されると共に、マトリッ

10

20

30

40

50

クス状に配置された複数の画素領域とを備え、

前記画素領域の各々は、薄膜トランジスタと、当該薄膜トランジスタに電気的に接続された画素電極と、対応する前記共通バスラインに電気的に接続された共通電極とを備えており、

前記画素電極と前記共通電極との間に印加される前記第1基板の表面に略平行な電界により、前記画素領域の各々において前記液晶層の液晶分子を前記第1基板に平行な面内で回転させることによって表示を行う横電界方式のアクティブマトリクス型液晶表示装置において、

前記画素領域の各々には、当該画素領域を画定する前記ドレインバスラインに隣接し且つそれに沿って延在する遮光電極が設けられており、

前記遮光電極は、当該画素領域に対応する前記画素電極の前記ドレインバスラインに隣接して延在する部分と部分的に重なっていると共に、当該画素領域内のいずれかの箇所において前記画素電極に電気的に接続されていることを特徴とするものである。

#### 【0047】

本発明の第2の液晶表示装置は、前記遮光電極が、孤立しておらず、当該画素領域内のいずれかの箇所において前記画素電極に電気的に接続されている点で、上述した本発明の第1の液晶表示装置と異なっており、それ以外は同一である。

#### 【0048】

本発明の第2の液晶表示装置では、このように、前記遮光電極が当該画素領域内のいずれかの箇所において前記画素電極に電気的に接続されているので、前記遮光電極の電位が常に前記画素電極の電位と等しくなる。他方、本発明の第1の液晶表示装置で述べたように、電気的にフローティングである前記遮光電極の電位は、前記画素電極の電位に近い値となるため、本発明の第2の液晶表示装置の前記遮光電極は本発明の第1の液晶表示装置の前記遮光電極と同様に作用する。

#### 【0049】

よって、本発明の第2の液晶表示装置においても、前記ドレインバスラインと対応する前記遮光電極との結合容量（寄生容量）が、図9および図10に示した従来の液晶表示装置における前記ドレインバスラインと対応する前記共通バスライン（遮光部）との結合容量（寄生容量）に比べて小さくなり、その結果、横クロストークの発生を抑制することができる。また、横クロストークの抑制により、画質が改善される。

#### 【0050】

（3） 本発明の第1および第2の液晶表示装置の好ましい例では、前記遮光電極が、絶縁膜を挟んで前記ドレインバスラインとは異なる層に形成される。この場合、前記遮光電極が、前記ドレインバスラインよりも前記液晶層から遠い層に形成され、あるいは、前記ゲートバスラインと同じ層に形成されるのがより好ましい。

#### 【0051】

（4） 本発明の第1および第2の液晶表示装置の他の好ましい例では、前記画素電極の前記ドレインバスラインに隣接して延在する前記部分が、櫛歯状とされ、前記遮光電極が、前記ドレインバスラインに沿って延在する帯状とされる。

#### 【0052】

（5） 本発明の第1および第2の液晶表示装置のさらに他の好ましい例では、前記画素電極が、前記ドレインバスラインに沿って延在する複数の櫛歯状部を有していると共に、前記画素電極の外側にある2本の前記櫛歯状部が、それぞれ、当該画素領域を画定する2本の前記ドレインバスラインに隣接して延在する前記部分とされており、

前記遮光電極が帯状であって、2本の前記遮光電極が、当該画素領域を画定する2本の前記ドレインバスラインにそれぞれ沿って延在するように形成される。

#### 【0053】

（6） 本発明の第1および第2の液晶表示装置のさらに他の好ましい例では、前記画素領域の各々に対応して、前記ドレインバスラインが略V字状に屈曲せしめられ、それに対応して前記画素電極と前記共通電極が略V字状に屈曲せしめられる。

10

20

30

40

50

**【 0 0 5 4 】**

( 7 ) 本発明の第 1 および第 2 の液晶表示装置のさらに他の好ましい例では、前記画素電極が、絶縁膜を挟んで前記ドレインバスラインとは異なる層に形成される。この場合、前記画素電極が、前記ドレインバスラインよりも前記液晶層に近い層に形成されるのがより好ましい。

**【 0 0 5 5 】**

( 8 ) 本発明の第 1 および第 2 の液晶表示装置のさらに他の好ましい例では、前記共通電極が前記画素電極と同じ層に形成される。

**【 0 0 5 6 】**

( 9 ) 本発明の第 1 および第 2 の液晶表示装置のさらに他の好ましい例では、前記画素電極および前記共通電極の少なくとも一方が、透明導電体により形成される。

10

**【発明の効果】****【 0 0 5 7 】**

本発明の第 1 および第 2 の液晶表示装置では、( a ) 各ドレインバスラインとそれに対応する共通バスラインとの結合容量(寄生容量)に起因する横クロストークを、簡単な構成で抑制することができる、そして( b ) 図 9 および図 10 に示した従来の液晶表示装置よりも画質が改善される、という効果が得られる。

**【発明を実施するための最良の形態】****【 0 0 5 8 】**

以下、本発明の好適な実施の形態について添付図面を参照しながら説明する。

20

**【 0 0 5 9 】****( 第 1 実施形態の構成 )**

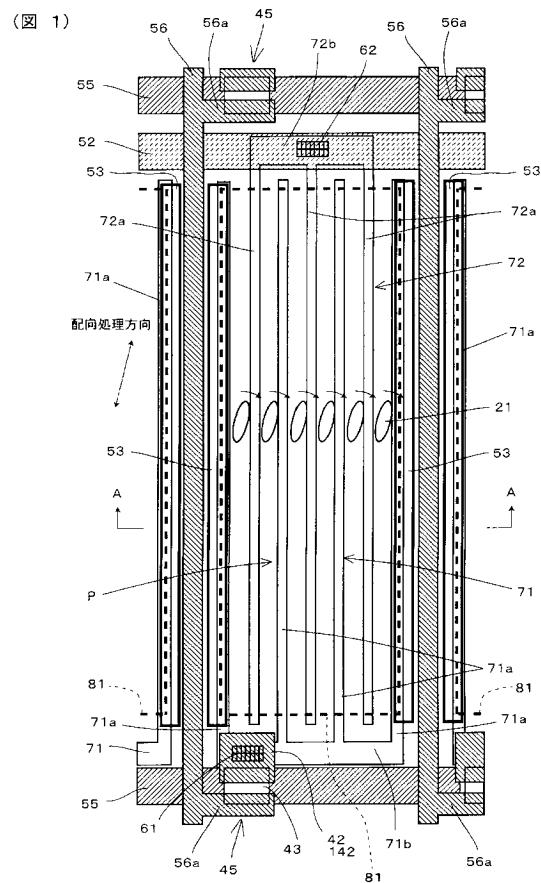

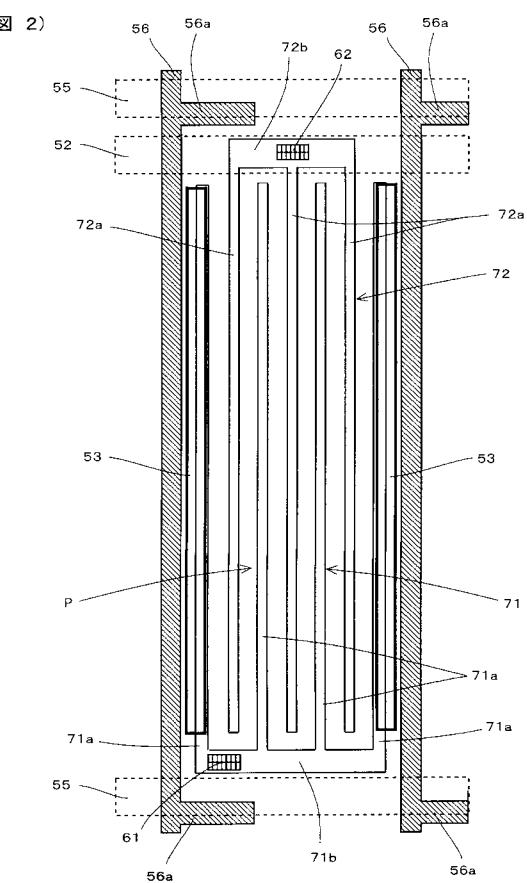

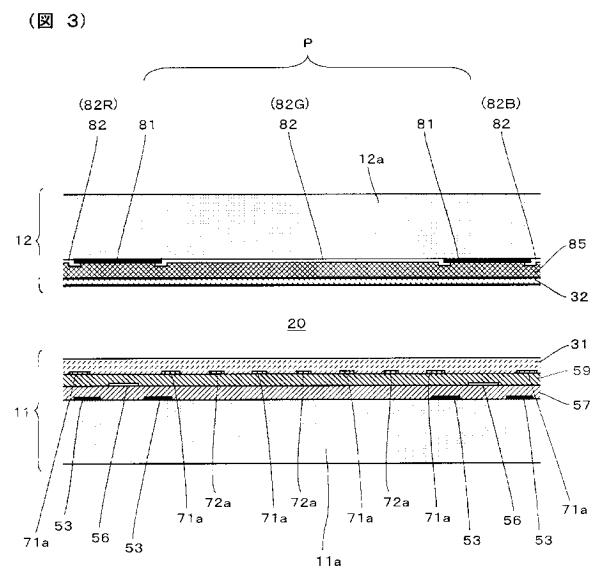

図 1 ~ 図 3 は、本発明の第 1 実施形態に係る横電界(IPS)方式のアクティブマトリックス型液晶表示装置を示す。図 1 は当該液晶表示装置に使用された第 1 基板(アクティブマトリックス基板)の平面図であり、図 2 はその画素電極と共通電極の平面形状(パターン)を示す説明図であり、図 3 は当該液晶表示装置の図 1 の A - A 線に沿った断面図である。これらの図はいずれも、一つの画素領域の構成を示している。

**【 0 0 6 0 】**

図 1 ~ 図 3 に示したように、本発明の第 1 実施形態の液晶表示装置の構成は、図 9 および図 10 に示した従来の液晶表示装置と多くの点で共通しているが、ドレインバスラインに沿って配置された遮光電極 53 が、その周囲の電極やバスラインとは電気的に接続されておらず、孤立している(換言すれば、遮光電極 53 がフローティング電極となっている)点が異なっている。以下、この液晶表示装置の構成について詳述する。

30

**【 0 0 6 1 】**

本第 1 実施形態の液晶表示装置は、図 1 の横方向(水平方向)に延在し且つ同図の縦方向(垂直方向)に等間隔で配置された複数本のゲートバスライン 55 と、図 1 の縦方向に延在し且つ同図の横方向に等間隔で配置された複数本のドレインバスライン 56 とを有している。これらのゲートバスライン 55 とドレインバスライン 56 によって画定される略矩形領域の各々には、画素領域 P が形成されている。これらの画素領域 P(すなわち画素)は、全体として縦横のマトリックス状に配列されている。

40

**【 0 0 6 2 】**

この液晶表示装置は、さらに、複数のゲートバスライン 55 の各々と平行に延在する複数の共通バスライン 52 を有している。これらの共通バスライン 52 は、各画素領域 P に形成された共通電極 72 を電気的に相互接続するために設けられたものであり、ゲートバスライン 55 の各々の近傍にそれから所定距離をあけて配置されている。

**【 0 0 6 3 】**

ゲートバスライン 55 とドレインバスライン 56 と共通バスライン 52 は、いずれも、不透明の金属膜により形成されている。

**【 0 0 6 4 】**

各画素領域 P の内部には、当該画素領域 P を画定する 2 本のドレインバスライン 56 に

50

沿ってそれぞれ配置された2本の帯状(ストライプ状)の遮光電極53が形成されている。これらの遮光電極53は、いずれも、周囲にある電極やバスラインとは電気的に接続されておらず、孤立している。

【0065】

図1の画素領域Pについて言えば、左側の遮光電極53は、同図の左側にあるドレインバスライン56の右側(当該画素領域Pの内側)に近接して配置されており、当該ドレインバスライン56から所定間隔を置いてそれに対して平行に延在している。この遮光電極53は、当該画素領域Pに対応する共通バスライン52およびゲートバスライン55とは重なっていない。

【0066】

図1の画素領域Pの右側の遮光電極53は、同図の右側にあるドレインバスライン56の左側(当該画素領域Pの内側)に近接して配置されており、当該ドレインバスライン56から所定間隔を置いてそれに対して平行に延在している。この遮光電極53も、当該画素領域Pに対応する共通バスライン52およびゲートバスライン55とは重なっていない。

【0067】

各画素領域Pに対しては、ゲートバスライン55とドレインバスライン56との交点の各々の近傍にTFT45が形成されている。各TFT45は、対応するゲートバスライン55と一体的に形成されたゲート電極(図示せず)と、ゲート絶縁膜57を介して当該ゲート電極に重ねて形成されたアイランド状の半導体膜43と、対応するドレインバスライン56と一体的に形成され且つ当該半導体膜43に部分的に重ねて形成されたドレイン電極56aと、当該ドレイン電極56aに対して所定間隔をあけて対向・配置され且つ当該半導体膜43に部分的に重ねて形成されたソース電極42とから構成されている。

【0068】

さらに、各画素領域Pの内部には、図1および図2に示すように、液晶駆動電界を発生させる画素電極71および共通電極72が形成されている。画素電極71および共通電極72は、いずれも、透明導電体によって形成されており、その平面形状は櫛形である。

【0069】

図1の画素領域Pについて言えば、画素電極71は、当該画素領域Pの内部でTFT45の側に配置された帯状の基部71bと、基部71bからTFT45の反対側に向かって(図1では上方に向かって)突出する4本の櫛歯状部71aとから形成されている。基部71bは、対応するゲートバスライン55とは重なっていないが、TFT45のソース電極42と重なっている。これらの櫛歯状部71aは、いずれも、当該画素領域Pを画定する2本のドレインバスライン56と平行に延在しており、基部71bに沿って(図1では横方向に)等間隔に配置されている。各櫛歯状部71aの先端は、対応する共通バスライン52の近傍まで達している。画素電極71の左右外側にある2本の櫛歯状部71aは、それぞれ、当該画素領域Pを画定する2本のドレインバスライン56の近傍にある2本の帯状の遮光電極53と部分的に重なっている。櫛歯状部71aの幅は、遮光電極53の幅よりも少し小さい。画素電極71は、その基部71bにおいて、コンタクトホール61を介してTFT45のソース電極42に電気的に接続されている。

【0070】

共通電極72は、当該画素領域Pの内部でTFT45とは反対側に配置された帯状の基部72bと、基部72bからTFT45の側に向かって(図1では下方に向かって)突出する3本の櫛歯状部72aとから形成されている。基部72bは、その全体が対応する共通バスライン52と重なっている。これらの櫛歯状部72aは、当該画素領域Pを画定する2本のドレインバスライン56と平行に延在しており、基部72bに沿って(図1では横方向に)等間隔に配置されている。従って、これらの櫛歯状部72aは、画素電極71の櫛歯状部71aおよびドレインバスライン56と平行である。また、各櫛歯状部72aの先端は、画素電極71の基部71bの近傍まで達している。3本の櫛歯状部72aは、画素電極71の4本の櫛歯状部71aに対して交互に配置されている。従って、3本の櫛

10

20

30

40

50

歯状部 7 2 a と 4 本の櫛歯状部 7 1 a とは、相互に噛み合った状態にある。共通電極 7 2 は、その基部 7 2 b において、コンタクトホール 6 2 を介して共通バスライン 5 2 に電気的に接続されている。

【0071】

図 3 に示すように、本第 1 実施形態の液晶表示装置は、第 1 基板（アクティブマトリックス基板）1 1 と、これに所定間隔をあいて対向せしめられた第 2 基板（対向基板）1 2 と、両基板 1 1 および 1 2 の間に配置された液晶層 2 0 とを備えている。

【0072】

第 1 基板 1 1 のガラス基板 1 1 a の表面には、ゲートバスライン 5 5 と、共通バスライン 5 2 と、遮光電極 5 3 と、TFT 4 5 のゲート電極とが形成されており、それらを覆うようにゲート絶縁膜 5 7 が形成されている（図 3 では遮光電極 5 3 のみが示されている）。各ゲート電極は、対応するゲートバスライン 5 5 と一体的に形成されている。ゲート絶縁膜 5 7 の上には、ドレインバスライン 5 6 と、TFT 4 5 の半導体膜 4 3、ドレイン電極 5 6 a およびソース電極 4 2 とが形成されており（図 3 ではドレインバスライン 5 6 のみが示されている）、これらは保護絶縁膜 5 9 で覆われている。保護絶縁膜 5 9 の上には、画素電極 7 1 と共通電極 7 2 が形成されている（図 3 では画素電極 7 1 の櫛歯状部 7 1 a と共通電極 7 2 の櫛歯状部 7 2 a のみが示されている）。

10

【0073】

このように、共通バスライン 5 2 はガラス基板 1 1 a の表面に形成され、ドレインバスライン 5 6 はゲート絶縁膜 5 7 の上に形成されているので、共通バスライン 5 2 はドレインバスライン 5 6 よりも下層に（液晶層 2 0 から遠い層に）配置されていることになる。同様に、ゲートバスライン 5 5 は、ガラス基板 1 1 a の表面に形成されているので、ゲートバスライン 5 5 もドレインバスライン 5 6 よりも下層に（液晶層 2 0 から遠い層に）配置されている。画素電極 7 1 および共通電極 7 2 は、保護絶縁膜 5 9 上に形成されているので、ドレインバスライン 5 6 よりも上層に（液晶層 2 0 に近い層に）配置されている。

20

【0074】

以上の構成を持つ第 1 基板 1 1 の表面（内面）、すなわち保護絶縁膜 5 9 の上には、有機高分子膜からなる配向膜 3 1 が形成されている。従って、画素電極 7 1 と共通電極 7 2 は、配向膜 3 1 によって覆われている。この配向膜 3 1 の表面には、所定の配向処理が施されている。

30

【0075】

他方、第 2 基板 1 2 のガラス基板 1 2 a の表面には、各画素領域 P に対応して、例えば RGB の 3 原色からなる色層 8 2 が形成されており、各画素領域 P に対応する領域以外の領域には遮光用のブラックマトリックス層 8 1 が形成されている。色層 8 2 は、所定形状にパターン化された赤色層 8 2 R と緑色層 8 2 G と青色層 8 2 B とから構成されている。ブラックマトリックス層 8 1 の平面形状（パターン）は、第 1 基板 1 1 上に不透明金属で形成されている構成要素、すなわちゲートバスライン 5 5、ドレインバスライン 5 6、共通バスライン 5 2 a および 5 2 b、遮光電極 5 3 および TFT 4 5 を覆うと共に、各画素領域 P の内部に矩形の開口領域（透光領域）を形成するように設定されている。色層 8 2 は、これら開口部（透光部）内に配置されている。

40

【0076】

色層 8 2 とブラックマトリックス層 8 1 は、オーバーコート層 8 5 によって覆われている。このオーバーコート層 8 5 は、ガラス基板 1 2 a の表面全体に形成されており、色層 8 2 とブラックマトリックス層 8 1 を保護するため、またそれらにより生じる段差を平坦化するために設けられている。ブラックマトリックス層 8 1 の上には、基板間隔を制御するための柱状スペーサ（図示せず）が形成されている。

【0077】

以上の構成を持つ第 2 基板 1 2 の表面（内面）、すなわちオーバーコート層 8 5 の上には、有機高分子膜からなる配向膜 3 2 が形成されている。従って、柱状スペーサは、配向膜 3 2 によって覆われている。この配向膜 3 2 の表面には、所定の配向処理が施されてい

50

る。

【0078】

第1基板(アクティブマトリックス基板)11と第2基板(対向基板)12は、配向膜31および32が形成された面を内側にして所定間隔をおいて重ね合わされている。両基板11と12の間には液晶が封入され、液晶層20を形成している。換言すれば、液晶層20は両基板11と12によって挟持されている。第1基板11と第2基板12の外側(ガラス基板11aと12aの裏面)には、一対の偏光板(図示せず)がそれぞれ配置されている。

【0079】

配向膜31および32の表面の配向処理により、無電界時には、図1に矢印で示すように、液晶層20の液晶分子21は、同図の縦方向(垂直方向)から一定角度(一例として時計回り方向に15度程度)ずれた方向に沿って平行に配向せしめられる。つまり、液晶分子21の初期配向方位は、図1に矢印で示す方向とされている。また、前記一対の偏光板の透過軸の方向は、互いに直交せしめられており、これら偏光板の一方の透過軸は、液晶分子21の無電界時の配向方向(すなわち初期配向方位)に一致している。

【0080】

(第1実施形態の製法)

次に、図1～図3に示した本第1実施形態の液晶表示装置の製造方法について説明する。

【0081】

まず、第1基板11のガラス基板11aの表面全体にCr膜を形成し、その後このCr膜を所定形状にパターン化して、複数のゲート電極と、複数のゲートバスライン55と、複数の共通バスライン52と、複数の遮光電極53とをガラス基板11aの表面に形成する。次に、ガラス基板11aの表面全体にSiNxからなるゲート絶縁膜57を形成し、ゲート電極とゲートバスライン55と共にバスライン52と遮光電極53とを覆う。

【0082】

続いて、ゲート絶縁膜57上にa-Si膜を形成してからこれを島状にパターン化し、TFT45用の複数の半導体膜43を形成する。これら半導体膜43の各々は、ゲート絶縁膜57を介して対応するゲート電極と重なる位置に配置される。さらに、Cr膜を形成してからこれをパターン化して、ゲート絶縁膜57上に複数のドレインバスライン56と複数のドレイン電極56aと複数のソース電極42とを形成する。その後、ガラス基板11aの表面全体にわたってSiNxからなる保護絶縁膜59を形成し、ドレインバスライン56、ドレイン電極56aおよびソース電極42を覆う。

【0083】

続いて、各ソース電極42と重なる所定の位置で保護絶縁膜59を選択的に除去し、各ソース電極42に達する複数のコンタクトホール61を形成する。また、各共通バスライン52と重なる所定の位置で保護絶縁膜59とゲート絶縁膜57とを選択的に除去し、各共通バスライン52に達する複数のコンタクトホール62を形成する。

【0084】

その後、保護絶縁膜59上にITO等からなる透明導電体膜を形成してからこれを所定形状にパターン化し、複数の櫛歯状の画素電極71と複数の櫛歯状の共通電極72を形成する。この時、各画素電極71は、対応するコンタクトホール61を介して対応するソース電極42に接続される。各共通電極72は、対応するコンタクトホール62を介して対応する共通バスライン52に接続される。こうして第1基板11が製造される。

【0085】

第2基板12は、次のようにして製造される。最初に、ガラス基板12aの表面にブラックマトリックス層81と色層82を形成する。色層82を形成する際には、それぞれ所定形状(パターン)を持つ赤色層82Rと緑色層82Gと青色層82Bを適当な順序で順次形成すればよい。次に、ガラス基板12aの表面全体にオーバーコート層85を形成し、ブラックマトリックス層81と色層82を覆う。その後、オーバーコート層85上に柱

10

20

30

40

50

状スペーサー（図示せず）を形成する。こうして第2基板12が製造される。

【0086】

続いて、このようにして製造された第1基板（アクティブマトリックス基板）11および第2基板（対向基板）12の表面に、それぞれ、ポリイミドからなる配向膜31と32が形成される。配向膜31と32の表面には、一様に所定の配向処理が施される。

【0087】

その後、両基板11および12が例えば4.0μmの間隔をあけて重ね合わせられる。そして、真空チャンバー（図示せず）内で、両基板11および12の間の隙間に例えば屈曲率異方性が0.075のネオマチック液晶を注入してから、この空間を封止する。その後、両基板11および12の外側にそれぞれ偏光板（図示せず）を貼り合わせると、液晶表示パネルが完成する。

10

【0088】

この液晶表示パネルに所定の駆動用LSIとバックライト装置を装着すると、図1～図3に示した本第1実施形態の液晶表示装置が完成する。

【0089】

図1～図3に示した本第1実施形態の液晶表示装置では、電圧印加時の液晶駆動電界は、おおよそ同図の横方向（水平方向）に一様に発生する。このため、無電界時に初期配向方向（図1の矢印の方向）に一様に配向していた液晶分子21は、前記液晶駆動電界によって時計回り方向に回転するように配向状態を変化させる。この配向状態の変化により、各画素領域P（画素）の透過率が変調せしめられるため、所望の画像を表示することが可能となる。

20

【0090】

また、本第1実施形態の液晶表示装置では、液晶駆動電界を発生させる画素電極71と共通電極72がいずれも透明導電体によって形成されているため、画素電極71と共通電極72が存在する領域においても光が透過する。このため、画素電極71と共通電極72を不透明金属によって形成した場合と比較して、開口率および透過率が向上する。

30

【0091】

また、ブラックマトリックス層81の開口領域内に存在する不透明金属部分が少なくなるため、不透明金属部分のエッジによる光散乱や、当該エッジの近傍での段差による液晶配向の乱れが抑制される。この光散乱や液晶配向の乱れは、黒表示時の光漏れの原因となるが、この液晶表示装置ではこれらが抑制されるため、表示コントラストが向上する。

【0092】

また、不透明金属部分がブラックマトリックス層81の開口領域内に存在すると、比較的明るい環境で使用した時に入射光を不透明金属が反射するために「明所コントラスト」の低下が顕著となる。しかし、当該開口領域内に不透明金属部分が存在しないこの液晶表示装置では、明所コントラストの低下が抑制される。

30

【0093】

さらに、各ドレインバスライン56の近傍にそれに沿って遮光電極53が設けられていると共に、これら遮光電極53と対応するドレインバスライン56の間の領域は、第2基板12上に形成されたブラックマトリックス層81で覆われているため、各ドレインバスライン56から漏洩する電界によって生じる光漏れや縦クロストークが抑制される。

40

【0094】

これらの点については上述した従来の液晶表示装置と同様である。しかし、本第1実施形態の液晶表示装置は、画素領域Pの各々に設けられた遮光電極53が、周囲の電極やバスラインとは電気的に接続されておらず孤立している点で、当該従来の液晶表示装置とは異なっている。

【0095】

すなわち、遮光電極53は、上述した従来の液晶表示装置と同様に、当該画素領域Pを画定するドレインバスライン56に隣接し且つそれに沿って延在しているが、周囲の電極やバスラインから孤立していると共に、当該画素領域Pに対応する画素電極71のドレイ

50

ンバスライン 5 6 に隣接して延在する櫛歯状部分 7 1 a と重なっていて、動作時には電気的にフローティング状態となる。この時、遮光電極 5 3 の電位は、対応する画素電極 7 1 の電位（信号電圧に相当する電位）に近い値になる。これは、孤立している遮光電極 5 3 が、ゲート絶縁膜 5 7 を挟んで、当該画素領域 P に対応する画素電極 7 1 のドレインバスライン 5 6 に隣接して延在する櫛歯状部分 7 1 a と重なっているからである。このため、ドレインバスライン 5 6 と対応する遮光電極 5 3 との電位差は非常に小さい、すなわち、ドレインバスライン 5 6 と対応する遮光電極 5 3 との結合容量（寄生容量）が非常に小さいものとなる。

#### 【0096】

他方、図 9 および図 10 に示した従来の液晶表示装置では、遮光部 1 5 2 a は対応する共通バスライン 1 5 2 と一体的に形成されているので、共通電極 1 7 2 の電位に等しい。したがって、ドレインバスライン 1 5 6 と対応する共通バスライン 1 5 2 との電位差は、ドレインバスライン 1 5 6 に供給される信号電圧に相当する電位と共通電極 1 7 2 の電位との差に等しくなる。これは、ドレインバスライン 1 5 6 と対応する遮光部 1 5 2 a との結合容量（寄生容量）がかなり大きいことを意味している。

10

#### 【0097】

このように、本第 1 実施形態の液晶表示装置におけるドレインバスライン 5 6 と対応する遮光電極 5 3 との結合容量（寄生容量）は、図 9 および図 10 に示した従来の液晶表示装置におけるドレインバスライン 1 5 6 と対応する共通バスライン 1 5 2（遮光部 1 5 2 a）との結合容量（寄生容量）に比べて小さくなるため、横クロストークの発生を抑制することができる。また、横クロストークの抑制により、画質が改善される。

20

#### 【0098】

なお、ドレインバスライン 5 6 に沿って配置された遮光電極 5 3 は、動作時には電気的にフローティングとなるが、画素電極 7 1 の左右外側にある櫛型状部分 7 1 a とゲート絶縁膜 5 7 を挟んで重なっているため、動作時の遮光電極 5 3 の電位は画素電極 7 1 の電位に近い値となる。したがって、当該櫛型状部分 7 1 a と遮光電極 5 3 との間には液晶の配向を初期配向方向から強く変化させるような電界は発生せず、安定な表示を行うことができる。

#### 【0099】

30

##### （第 2 実施形態の構成）

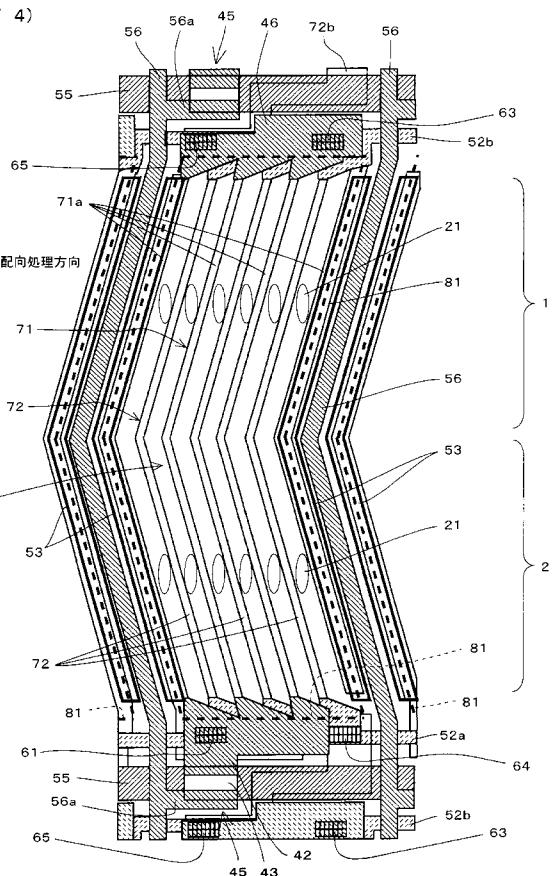

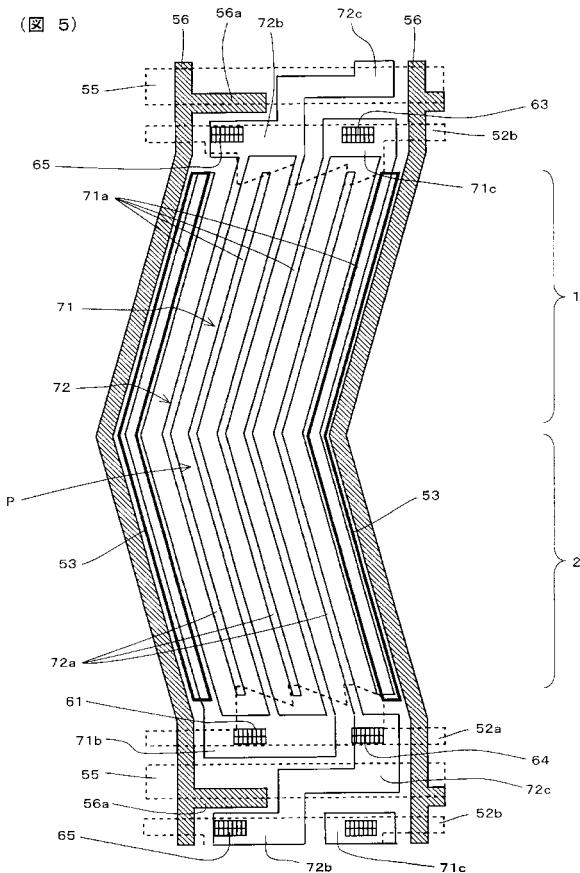

図 4 ~ 図 6 は、本発明の第 2 実施形態に係る横電界（IPS）方式のアクティブマトリックス型液晶表示装置を示す。図 4 は当該液晶表示装置に使用されたアクティブマトリックス基板の平面図であり、図 5 はその画素電極と共通電極の平面形状（パターン）を示す説明図であり、図 6 はその共通バスラインとソース電極と補助電極の平面形状（パターン）を示す説明図である。これらの図はいずれも、一つの画素領域の構成を示している。

#### 【0100】

40

本第 2 実施形態の液晶表示装置の構成は、図 1 ~ 図 3 に示した上記第 1 実施形態の液晶表示装置と多くの点で共通しているが、本第 2 実施形態の液晶表示装置では、横電界を発生させる画素電極 7 1 および共通電極 7 2 と、ドレインバスライン 5 6 とを、それらの中央部で略 V 字状に屈曲させており、電界作用時の液晶駆動（回転）方向をその屈曲部の両側で意図的に異ならせるようにしている点で、上記第 1 実施形態の液晶表示装置とは異なっている。また、画素電極 7 1 および共通電極 7 2 とソース電極 4 2 の形状も少し異なっている。

#### 【0101】

したがって、以下では主としてこれらの相違点について説明し、両液晶表示装置に共通する構成については、上記第 1 実施形態の液晶表示装置において使用したのと同じ符号を付してその説明を省略する。

#### 【0102】

本第 2 実施形態の液晶表示装置は、図 4 の横方向（水平方向）に延在し且つ同図の縦方向（垂直方向）に等間隔で配置された複数本のゲートバスライン 5 5 と、図 4 の縦方向に

50

延在し且つ同図の横方向に等間隔で配置された複数本のドレインバスライン 5 6 を有している。これらのゲートバスライン 5 5 とドレインバスライン 5 6 によって画定される略矩形領域の各々は、画素領域 P とされており、全体として縦横のマトリックス状に配列されている。ゲートバスライン 5 5 の平面形状は、上記第 1 実施形態の液晶表示装置と同じである。ドレインバスライン 5 6 の平面形状は、上記第 1 実施形態の液晶表示装置とは異なっており、画素領域 P の各々において、中央部で略 V 字状に屈曲していて、その屈曲部において画素領域 P を図 4 の上位にある第 1 サブ領域 1 と同図の下位にある第 2 サブ領域 2 とに分割している。ドレインバスライン 5 6 の傾き方向は、第 1 サブ領域 1 においては図 5 の縦（上下）方向に対して時計回りとされ、第 2 サブ領域 2 においては反時計回りとされている。第 1 サブ領域 1 での傾斜角度と第 2 サブ領域 2 でのドレインバスライン 5 6 の傾斜角度の大きさは同じである。

10

## 【0103】

この液晶表示装置は、さらに、複数のゲートバスライン 5 5 の各々と平行に延在する複数の共通バスライン 5 2 a および 5 2 b を有している。共通バスライン 5 2 a および 5 2 b は、各画素領域 P を画定する 2 本のゲートバスライン 5 5 の各々の近傍にあって、各画素領域 P の内側に対応するゲートバスライン 5 5 から所定距離をあけて配置されている。

20

## 【0104】

図 4 の画素領域 P について言えば、下位にある共通バスライン 5 2 a は、下位にあるゲートバスライン 5 5 の上方に近接してそれに平行に延在している。上位にある共通バスライン 5 2 b は、上位にあるゲートバスライン 5 5 の下方に近接してそれに平行に延在している。これらの共通バスライン 5 2 a および 5 2 b は、各画素領域 P に形成された共通電極 7 2 を電気的に相互接続するために設けられている。

30

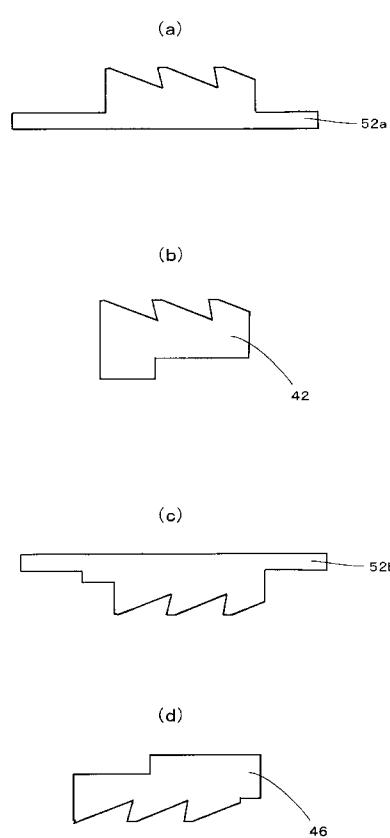

## 【0105】

共通バスライン 5 2 a の平面形状は、図 6 ( a ) に示すとおりであり、各画素領域 P の内部において幅広部を有していると共に、その幅広部の内側の端縁が鋸歯状になっている。共通バスライン 5 2 b の平面形状は、図 6 ( c ) に示すとおりであり、共通バスライン 5 2 a と同様に、各画素領域 P の内部において幅広部を有していると共に、その幅広部の内側の端縁が鋸歯状になっている。共通バスライン 5 2 a と 5 2 b の平面形状は、それらの設置個所の構造に応じて少し異なっている。

30

## 【0106】

ゲートバスライン 5 5 とドレインバスライン 5 6 と共通バスライン 5 2 a および 5 2 b は、いずれも、不透明の金属膜により形成されている。

## 【0107】

各画素領域 P の内部には、当該画素領域 P を画定する 2 本のドレインバスライン 5 6 に沿ってそれぞれ配置された 2 本の帯状（ストライプ状）の遮光電極 5 3 を有している。これら遮光電極 5 3 は、いずれも、ドレインバスライン 5 6 と同じように中央部で略 V 字状に屈曲されており、また、周囲にある電極やバスラインとは電気的に接続されておらず、孤立している。遮光電極 5 3 は、いずれも同じ平面形状（パターン）を持っている。各遮光電極 5 3 の屈曲部から上半分は、第 1 サブ領域 1 に属し、その下半分は第 2 サブ領域 2 に属している。

40

## 【0108】

図 4 の画素領域 P について言えば、左側の遮光電極 5 3 は、同図の左側にあるドレインバスライン 5 6 ( V 字状に屈曲している ) の右側（当該画素領域 P の内側）に近接して配置されており、当該ドレインバスライン 5 6 から所定間隔をおいてそれに対して平行に延在している。この遮光電極 5 3 は、当該画素領域 P に対応する共通バスライン 5 2 a および 5 2 b とゲートバスライン 5 5 とは交差していない。

## 【0109】

図 4 の右側の遮光電極 5 3 は、同図の右側にあるドレインバスライン 5 6 ( V 字状に屈曲している ) の左側（当該画素領域 P の内側）に近接して配置されており、当該ドレインバスライン 5 6 から所定間隔をおいてそれに対して平行に延在している。この遮光電極 5

50

3も、当該画素領域Pに対応する共通バスライン52aおよび52bとゲートバスライン55とは交差していない。

【0110】

また、各画素領域Pに対しては、対応するゲートバスライン55と対応するドレインバスライン56との交点の近傍においてTFT45が形成されている。各TFT45は、対応するゲートバスライン55と一体的に形成されたゲート電極(図示せず)と、ゲート絶縁膜57を介して当該ゲート電極に重ねて形成されたアイランド状の半導体膜43と、対応するドレインバスライン56と一体的に形成され且つ当該半導体膜43に部分的に重ねて形成されたドレイン電極56aと、当該ドレイン電極56aに対して所定間隔をあけて対向・配置され且つ当該半導体膜43に部分的に重ねて形成されたソース電極42とから構成されている。

10

【0111】

ソース電極42の平面形状は、図6(b)に示すとおりであり、第1実施形態の液晶表示装置よりも大きく、共通バスライン52aと重なる程度まで拡大されており、また、その内側の端縁が鋸歯状になっている。

【0112】

各画素領域Pの内部の共通バスライン52bと重なる箇所には、ソース電極42に似た形状の補助電極46が形成されている。補助電極46は、ソース電極42と同じ層に配置されており、ソース電極42と同じ材料で形成されている。補助電極46の平面形状は、図6(d)に示すとおりであり、ソース電極42と同様に、その内側の端縁が鋸歯状になっている。ソース電極42と補助電極46の平面形状は、それらの設置個所の構造に応じて少し異なっている。補助電極46は、コンタクトホール63を介して、後述する画素電極71の基部71cに電気的に接続されている。

20

【0113】

各画素領域Pの内部には、図4および図5に示すように、液晶駆動電界を発生させる画素電極71および共通電極72が形成されている。画素電極71および共通電極72は、いずれも、透明導電体によって形成されており、その平面形状はドレインバスライン56と同様の略V字状に屈曲された櫛形である。

【0114】

図5の画素領域Pについて言えば、画素電極71は、当該画素領域Pの内部でTFT45の側に配置された帯状の基部71bと、当該画素領域Pの内部でTFT45と反対側に配置された帯状の基部71cと、基部71bからTFT45の反対側に向かって(図5では上方に向かって)突出する3本の略V字状の櫛歯状部71aと、基部71cからTFT45の側に向かって(図5では下方に向かって)突出する1本の略V字状の櫛歯状部71aとから形成されている。基部71cは、基部71bから突出する3本の櫛歯状部71aのうち右側にあるものの先端部に接合されている。基部71bは、対応するゲートバスライン55とは重なっていないが、TFT45のソース電極42と重なっている。画素電極71の合計4本の櫛歯状部71aは、当該画素領域Pを画定する略V字状のドレインバスライン56と平行に延在しており、基部71bおよび71cに沿って(図5では横方向に)等間隔に配置されている。基部71bから突出している各櫛歯状部71aの先端は、対応する共通バスライン52bの近傍まで達している。基部71cから突出している櫛歯状部71aの先端は、対応する共通バスライン52aの近傍まで達している。画素電極71の左右の外側にある櫛歯状部71aは、それぞれ、当該画素領域Pを画定する2本のドレインバスライン56の近傍にある2本の遮光電極53と部分的に重なっている。櫛歯状部71aの幅は、遮光電極53の幅よりも少し小さい。画素電極71は、その基部71bにおいて、コンタクトホール61を介してTFT45のソース電極42に電気的に接続されている。

30

【0115】

共通電極72は、当該画素領域Pの内部でTFT45とは反対側に配置された略L字状の基部72bと、当該画素領域Pの内部でTFT45の側に配置された略L字状の基部7

40

50

2 c と、基部 7 2 b から TFT 4 5 の側に向かって（図 5 では下方に向かって）突出する 2 本の櫛歯状部 7 2 a と、基部 7 2 c から TFT 4 5 とは反対側に向かって（図 5 では上方に向かって）突出する 1 本の櫛歯状部 7 2 a とから形成されている。基部 7 2 b は、その全体が対応する共通バスライン 5 2 b と重なっている。基部 7 2 c は、対応する共通バスライン 5 2 a およびゲートバスライン 5 5 と重なっている。合計 3 本の櫛歯状部 7 2 a は、当該画素領域 P を画定する 2 本のドレインバスライン 5 6 と平行に延在しており、基部 7 2 b および 7 2 c に沿って（図 5 では横方向に）等間隔に配置されている。従って、これらの櫛歯状部 7 2 a は、画素電極 7 1 の櫛歯状部 7 1 a およびドレインバスライン 5 6 と平行である。また、各櫛歯状部 7 2 a の先端は、画素電極 7 1 の基部 7 1 b の近傍まで達している。3 本の櫛歯状部 7 2 a は、画素電極 7 1 の 4 本の櫛歯状部 7 1 a に対して交互に配置されている。従って、3 本の櫛歯状部 7 2 a と 4 本の櫛歯状部 7 1 a とは、相互に噛み合った状態にある。共通電極 7 2 は、その基部 7 2 b においてコンタクトホール 6 5 を介して共通バスライン 5 2 b に電気的に接続されていると共に、その基部 7 2 c においてコンタクトホール 6 4 を介して共通バスライン 5 2 a に電気的に接続されている。なお、図 5 から分かるように、基部 7 2 b と基部 7 2 c とは、図 5 の上下方向に隣接する画素領域 P の境界部において相互に接続されている。10

#### 【 0 1 1 6 】

画素電極 7 1 に電気的に接続されていてそれと同じ電位になるソース電極 4 2 および補助電極 4 6 は、それぞれ鋸歯状部分を有している。また、共通電極 7 2 に電気的に接続されていてそれと同じ電位となる共通バスライン 5 2 a および 5 2 b も、それぞれ鋸歯状部分を有している。そして、ソース電極 4 2 および補助電極 4 6 の鋸歯状部分と、共通バスライン 5 2 a および 5 2 b の鋸歯状部分は、ゲートバスライン 5 5 に沿って（図 5 の横方向に）交互に配置されている。これは、液晶分子 2 1 を第 1 サブ領域 1 および第 2 サブ領域 2 のそれぞれの内部において一様かつ互いに反対方向に回転させるようするためである。つまり、このような構成とすることにより、第 1 サブ領域 1 と第 2 サブ領域 2 の各々において、画素電極 7 1 の櫛歯状部 7 1 a と共通電極 7 2 の櫛歯状部 7 1 a の先端部の近傍での液晶分子 2 1 の回転方向を、それ以外の領域における液晶分子 2 1 の回転方向と略一致させることができる。20

#### 【 0 1 1 7 】

本第 2 実施形態の液晶表示装置も、第 1 実施形態の液晶表示装置と同様に、第 1 基板（アクティブマトリックス基板）1 1 と第 2 基板（対向基板）1 2 と液晶層 2 0 とを備えているが、第 2 基板 1 2 と液晶層 2 0 の構成は第 1 実施形態の液晶表示装置と同じであるから、それらについての説明は省略し、本第 2 実施形態の液晶表示装置の第 1 基板 1 1 について説明する。30

#### 【 0 1 1 8 】

なお、本第 2 実施形態の液晶表示装置の A - A 線に沿った断面構造は、上記第 1 実施形態の液晶表示装置のそれと同じであるので、以下の説明は適宜、図 3 を参照して行うことにする。

#### 【 0 1 1 9 】

第 1 基板 1 1 のガラス基板 1 1 a の表面には、ゲートバスライン 5 5 と、共通バスライン 5 2 a および 5 2 b と、遮光電極 5 3 と、TFT 4 5 のゲート電極とが形成されており、それらを覆うようにゲート絶縁膜 5 7 が形成されている（図 3 では遮光電極 5 3 のみが示されている）。各ゲート電極は、対応するゲートバスライン 5 5 と一体的に形成されている。ゲート絶縁膜 5 7 の上には、ドレインバスライン 5 6 と、TFT 4 5 の半導体膜 4 3、ドレイン電極 5 6 a およびソース電極 4 2 と、補助電極 4 6 とが形成されており（図 3 ではドレインバスライン 5 6 のみが示されている）、これらは保護絶縁膜 5 9 で覆われている。保護絶縁膜 5 9 の上には、画素電極 7 1 と共通電極 7 2 が形成されている（図 3 では画素電極 7 1 の櫛歯状部 7 1 a と共通電極 7 2 の櫛歯状部 7 2 a のみが示されている）。

#### 【 0 1 2 0 】

50

このように、共通バスライン 52a および 52b はガラス基板 11a の表面に形成され、ドレインバスライン 56 はゲート絶縁膜 57 の上に形成されているので、共通バスライン 52a および 52b はドレインバスライン 56 よりも下層に（液晶層 20 から遠い層に）配置されていることになる。また、ゲートバスライン 55 は、ガラス基板 11a の表面に形成されているので、ゲートバスライン 55 もドレインバスライン 56 よりも下層に（液晶層 20 から遠い層に）配置されている。画素電極 71 および共通電極 72 は、保護絶縁膜 59 上に形成されているので、ドレインバスライン 56 よりも上層に（液晶層 20 に近い層に）配置されている。

#### 【0121】

以上の構成を持つ第 1 基板 11 の表面（内面）、すなわち保護絶縁膜 59 の上には、有機高分子膜からなる配向膜 31 が形成されている。従って、画素電極 71 と共通電極 72 は、配向処理を施された配向膜 31 によって覆われている。

10

#### 【0122】

配向膜 31 および 32 の表面の配向処理により、無電界時には、図 4 に矢印で示すように、液晶層 20 の液晶分子 21 は、同図の縦方向（垂直方向）に沿って平行に配向せしめられる。つまり、液晶分子 21 の初期配向方位は、図 4 に矢印で示す方向とされている。

#### 【0123】

（第 2 実施形態の製法）

次に、図 4～図 6 に示した本第 2 実施形態の液晶表示装置の製造方法について説明する。

20

#### 【0124】

まず、第 1 基板 11 のガラス基板 11a の表面全体に Cr 膜を形成し、その後この Cr 膜を所定形状にパターン化して、ガラス基板 11a の表面に複数のゲート電極と、複数のゲートバスライン 55 と、複数の共通バスライン 52a および 52b と、複数の遮光電極 53 とを形成する。次に、ガラス基板 11a の表面全体に SiNx からなるゲート絶縁膜 57 を形成し、ゲート電極とゲートバスライン 55 と共通バスライン 52 と遮光電極 53 とを覆う。

#### 【0125】

続いて、ゲート絶縁膜 57 上に a-Si 膜を形成してからこれを島状にパターン化し、TFT45 用の複数の半導体膜 43 を形成する。これら半導体膜 43 の各々は、ゲート絶縁膜 57 を介して対応するゲート電極と重なる位置に配置される。さらに、ゲート絶縁膜 57 上に Cr 膜を形成してからこれをパターン化して、ゲート絶縁膜 57 上に複数のドレインバスライン 56 と複数のドレン電極 56a と複数のソース電極 42 と複数の補助電極 46 を形成する。その後、ガラス基板 11a の表面全体にわたって SiNx からなる保護絶縁膜 59 を形成し、ドレインバスライン 56、ドレン電極 56a、ソース電極 42 および補助電極 46 を覆う。

30

#### 【0126】

続いて、各ソース電極 42 と重なる所定の位置で保護絶縁膜 59 を選択的に除去し、各ソース電極 42 に達する複数のコンタクトホール 61 と、各補助電極 46 に達する複数のコンタクトホール 65 とを形成する。また、各共通バスライン 52a および 52b と重なる所定の位置で保護絶縁膜 59 とゲート絶縁膜 57 とを選択的に除去し、各共通バスライン 52a および 52b に達する複数のコンタクトホール 63 および 64 を形成する。

40

#### 【0127】

その後、保護絶縁膜 59 上にITO等からなる透明導電体膜を形成してからこれを所定形状にパターン化し、複数の櫛歯状の画素電極 71 と複数の櫛歯状の共通電極 72 を形成する。この時、各画素電極 71 は、対応するコンタクトホール 61 と 65 を介して、対応するソース電極 42 と補助電極 46 にそれぞれ接続される。各共通電極 72 は、対応するコンタクトホール 63 と 64 を介して対応する共通バスライン 52b と 52a にそれぞれ接続される。こうして第 1 基板 11 が製造される。

#### 【0128】

50

第2基板12は、上述した第1実施形態の液晶表示装置と同様にして製造される。

【0129】

そこで、こうして製造された第1基板11と第2基板12を用いて、上述した第1実施形態の液晶表示装置と同様にして液晶表示パネルを形成した後、この液晶表示パネルに所定の駆動用LSIとバックライト装置を装着すると、図4～図6に示した本第2実施形態の液晶表示装置が完成する。

【0130】

以上説明したように、本第2実施形態の液晶表示装置は、各ドレインバスライン56の近傍において、画素電極71の櫛歯状部71aに沿って延在する遮光電極53を周囲の電極やバスラインから孤立させて設けた点は、上述した第1実施形態の液晶表示装置と同じであるから、上述した第1実施形態の液晶表示装置と同じ効果が得られることは明らかである。

10

【0131】

しかし、本第2実施形態の液晶表示装置では、電圧印加時の液晶駆動電界は、第1サブ領域1では、図4の横方向に対して時計回りに若干傾いた方向に発生し、第2サブ領域2では、同図の横方向に対して反時計回りに若干傾いた方向に発生するため、無電界時の図4の縦方向（垂直方向）に沿って一様に初期配向していた液晶分子21は、前述の液晶駆動電界により、第1サブ領域1では時計回りに、第2サブ領域2では反時計回りに、それぞれ回転する。このように、2つのサブ領域1, 2における液晶分子の回転方向が逆になるため、視角変化による表示の色づきを抑制することができる、という利点がある。

20

【0132】

また、本第2実施形態の液晶表示装置では、各画素領域Pに設けられた共通電極72が、共通バスライン52aおよび52bによって図4の横（左右）方向に相互接続されると共に、基部72bおよび72cによってゲートバスライン55を跨ぐように同図の縦（上下）方向にも相互接続されており、全体として網目状の構造を持っているため、各画素領域Pの共通電極72は、ドレインバスライン56の電位変動の影響を受けにくい。よって、横クロストークの発生を上述した第1実施形態の液晶表示装置よりも確実に抑制することが可能となり、結果として、画質がいっそう改善される、という利点がある。

30

【0133】

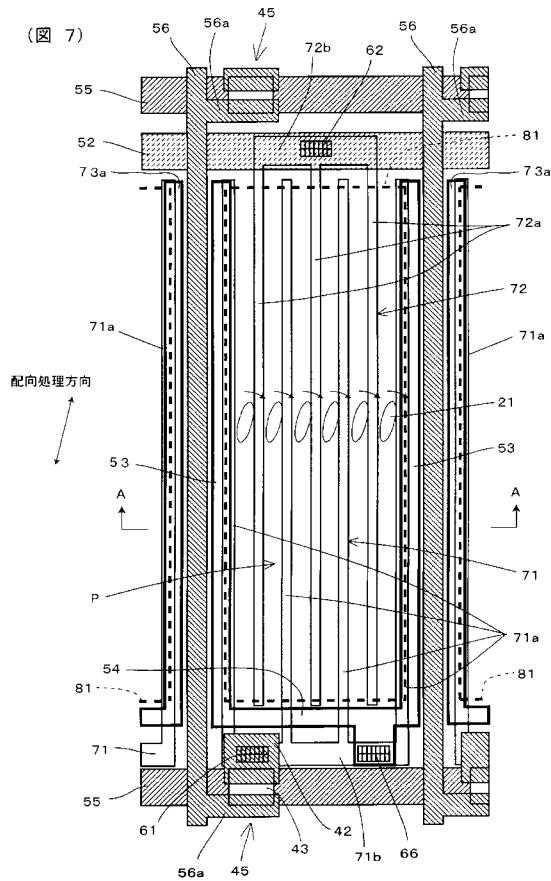

（第3実施形態）

30

図7～図8は、本発明の第3実施形態に係る横電界（IPS）方式のアクティブマトリックス型液晶表示装置を示す。図7は当該液晶表示装置に使用されたアクティブマトリックス基板の平面図であり、図8はその画素電極と共通電極の平面形状（パターン）を示す説明図である。これらの図はいずれも、一つの画素領域の構成を示している。

【0134】

本第3実施形態の液晶表示装置の構成は、各画素領域P内の2本の遮光電極53が相互接続され、さらに対応する画素電極71に電気的に接続されている（フローティング電極ではない）点が異なるのみであり、それ以外の点は図1～図3に示した上記第1実施形態の液晶表示装置と同じである。よって、同一の構成については、上記第1実施形態の液晶表示装置において使用したのと同じ符号を付してその説明を省略する。

40

【0135】

本第3実施形態では、各画素領域Pに設けられた2本の帯状（ストライプ状）の遮光電極53は、上記第1実施形態の液晶表示装置と同様に、当該画素領域Pを画定する2本のドレインバスライン56の近傍にそれらに沿ってそれぞれ配置されているが、周囲の電極やバスラインから孤立していない。すなわち、これら2本の遮光電極53は、TFT45の近傍に形成された略帯状の連結部54によって相互に接続されている。連結部54は、ゲートバスライン55の近傍に位置していてそれに平行に延在している。連結部54は、その一部が下方（TFT45の側に）に突出して画素電極71の基部71bと重なっており、その箇所でゲート絶縁膜57を貫通するコンタクトホール66を介して画素電極71に接続されている。共通電極72の櫛歯状部72aは、連結部54と重ならないように、

50

上記第1実施形態の液晶表示装置よりも少し短くされている。

【0136】

本第3実施形態の液晶表示装置では、このように、各画素領域Pに設けられた2本の遮光電極53が、当該画素領域の内部において対応する画素電極71の基部71bと電気的に接続されているので、遮光電極53は常に画素電極71と同じ電位になる。上記第1実施形態の液晶表示装置において述べたように、電気的にフロー・ティングである遮光電極53の電位は、対応する画素電極71の電位に近い値となるのであるから、本第3実施形態の液晶表示装置の構成においても、上記第1実施形態の場合とほぼ同様の作用が得られる。よって、上記第1実施形態の液晶表示装置と同じ効果が得られることが明らかである。

【0137】

なお、ここでは、各画素領域Pに設けられた2本の遮光電極53が、帯状の連結部54によって相互接続されると共に、コンタクトホール66を介して画素電極71に接続されているが、本発明はこれに限定されない。連結部54を使用せずに、2本の遮光電極53が直接、個別にコンタクトホール66を介して画素電極71に接続されていてもよい。遮光電極53は、各画素領域P内のいずれかの箇所において、画素電極71と電気的に接続されていれば足りる。

【0138】

(変形例)

上記第1～3の実施形態は本発明の好適な例を示すものである。したがって、本発明はこれら実施形態に限定されず、種々の変形が可能なことは言うまでもない。

例えば、上記第1～3の実施形態では遮光電極53は帯状とされているが、本発明はこれには限定されない。遮光電極53は、ドレインバスライン56の近傍にそれに沿って延在していれば足りるのであり、帯状以外の任意の形状であってもよい。

【図面の簡単な説明】

【0139】

【図1】本発明の第1実施形態に係る横電界方式のアクティブマトリックス型液晶表示装置に使用されたアクティブマトリックス基板の平面図である。

【図2】図1のアクティブマトリックス基板の画素電極と共通電極の平面形状を示す説明図である。

【図3】図1のA-A線に沿った要部断面図である。

【図4】本発明の第2実施形態に係る横電界方式のアクティブマトリックス型液晶表示装置に使用されたアクティブマトリックス基板の平面図である。

【図5】図4のアクティブマトリックス基板の画素電極と共通電極の平面形状を示す説明図である。

【図6】(a)は図4のアクティブマトリックス基板の一方の共通バスラインの幅広部の平面形状を示す説明図、(b)はそのソース電極の平面形状を示す説明図、(c)は図4のアクティブマトリックス基板の他方の共通バスラインの幅広部の平面形状を示す説明図、(d)はその補助電極の平面形状を示す説明図である。

【図7】本発明の第3実施形態に係る横電界方式のアクティブマトリックス型液晶表示装置に使用されたアクティブマトリックス基板の平面図である。

【図8】図7のアクティブマトリックス基板の画素電極と共通電極の平面形状を示す説明図である。

【図9】従来の横電界方式のアクティブマトリックス型液晶表示装置に使用されたアクティブマトリックス基板の平面図である。

【図10】図9のB-B線に沿った要部断面図である。

【符号の説明】

【0140】

1 画素領域の第1サブ領域

2 画素領域の第2サブ領域

11 第1基板(アクティブマトリックス基板)

10

20

30

40

50

- 1 1 a ガラス基板

1 2 第2基板(対向基板)

1 2 a ガラス基板

2 0 液晶層

2 1 液晶分子

3 1、3 2 配向膜

4 2 ソース電極

4 3 半導体膜

4 5 薄膜トランジスタ(TFT)

4 6 補助電極 10

5 2、5 2 a、5 2 b 共通バスライン

5 3 遮光電極

5 4 遮光電極の連結部

5 5 ゲートバスライン

5 6 ドレインバスライン

5 6 a ドレイン電極

5 7 ゲート絶縁膜

5 9 保護絶縁膜

6 1、6 2、6 3、6 4、6 5、6 6 コンタクトホール

7 1 画素電極 20

7 1 a 画素電極の櫛歯状部

7 1 b、7 1 c 画素電極の基部

7 2 共通電極

7 2 a 共通電極の櫛歯状部

7 2 b、7 2 c 共通電極の基部

8 1 ブラックマトリックス層

8 2 色層

8 5 オーバーコート層

P 画素領域

【図1】

【図2】

【図3】

【図4】

【 図 5 】

【 図 6 】

【図7】

〔 図 8 〕

【図9】

【図10】

---

フロントページの続き

F ターム(参考) 2H092 GA14 GA17 JA24 JB05 JB32 JB33 JB52 JB53 JB54 NA01

NA23

2H191 FA13Y FA14Y FB14 FD04 GA05 GA19 LA08 LA21

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 水平电场型有源矩阵型液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP2009103925A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2009-05-14 |

| 申请号            | JP2007275702                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2007-10-23 |

| [标]申请(专利权)人(译) | NEC液晶技术株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | NEC LCD科技有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人         | 鈴木 照晃<br>西田 真一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 鈴木 照晃<br>西田 真一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368 G02F1/1335                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| CPC分类号         | G02F1/13439 G02F1/134363 G02F1/136286                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| FI分类号          | G02F1/1343 G02F1/1368 G02F1/1335.500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| F-TERM分类号      | 2H091/FA34Y 2H091/FA35Y 2H091/FB08 2H091/FD04 2H091/GA03 2H091/GA13 2H091/LA08 2H091/LA16 2H092/GA14 2H092/GA17 2H092/JA24 2H092/JB05 2H092/JB32 2H092/JB33 2H092/JB52 2H092/JB53 2H092/JB54 2H092/NA01 2H092/NA23 2H191/FA13Y 2H191/FA14Y 2H191/FB14 2H191/FD04 2H191/GA05 2H191/GA19 2H191/LA08 2H191/LA21 2H192/AA24 2H192/BB03 2H192/BB53 2H192/BB73 2H192/BB82 2H192/BC31 2H192/CB05 2H192/CC04 2H192/CC42 2H192/CC55 2H192/DA74 2H192/EA04 2H192/EA15 2H192/EA22 2H192/EA43 2H192/GA03 2H192/JA33 2H291/FA13Y 2H291/FA14Y 2H291/FB14 2H291/FD04 2H291/GA05 2H291/GA19 2H291/LA08 2H291/LA21 |         |            |

| 代理人(译)         | 泉 克文                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | <a href="#">JP5224237B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

### 摘要(译)

解决的问题：提供一种抑制水平串扰的高质量的水平电场型液晶显示装置。在由栅极总线55和漏极总线56限定的每个像素区域P中设置有遮光电极53，遮光电极53与限定像素区域P的漏极总线56相邻并沿其延伸。遮光电极53被隔离，并且与邻近像素电极71的漏极总线56延伸的梳齿部分71a重叠，并且在它们之间插入有绝缘膜，并且在操作期间电浮置。由于处于浮置状态的遮光电极53的电势变为接近像素电极71的电势的值，因此漏极总线56和公共电极72（公共总线52）之间的耦合电容减小，并且不会产生水平串扰。被压制。[选型图]图1