(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-106657

(P2006-106657A)

(43) 公開日 平成18年4月20日(2006.4.20)

| (51) Int.CI.                | F 1                                                | テーマコード (参考)                                                                   |

|-----------------------------|----------------------------------------------------|-------------------------------------------------------------------------------|

| <b>G09G 3/36 (2006.01)</b>  | GO9G 3/36                                          | 2 H 093                                                                       |

| <b>G02F 1/133 (2006.01)</b> | GO2F 1/133 520                                     | 5 C 006                                                                       |

| <b>G09G 3/20 (2006.01)</b>  | GO2F 1/133 550<br>GO9G 3/20 611A<br>GO9G 3/20 621B | 5 C 080                                                                       |

|                             | 審査請求 未請求 請求項の数 33 O L (全 42 頁) 最終頁に続く              |                                                                               |

| (21) 出願番号                   | 特願2005-16518 (P2005-16518)                         | (71) 出願人 302062931<br>N E C エレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部1753番地               |

| (22) 出願日                    | 平成17年1月25日 (2005.1.25)                             |                                                                               |

| (31) 優先権主張番号                | 特願2004-73741 (P2004-73741)                         | (74) 代理人 100103894<br>弁理士 家入 健                                                |

| (32) 優先日                    | 平成16年3月16日 (2004.3.16)                             |                                                                               |

| (33) 優先権主張国                 | 日本国 (JP)                                           | (72) 発明者 橋本 義春<br>神奈川県川崎市中原区下沼部1753番地<br>N E C エレクトロニクス株式会社内                  |

| (31) 優先権主張番号                | 特願2004-262191 (P2004-262191)                       | F ターム (参考) 2H093 NA16 NA32 NA34 NA43 NC03<br>NC05 NC22 NC26 NC34 ND39<br>ND49 |

| (32) 優先日                    | 平成16年9月9日 (2004.9.9)                               |                                                                               |

| (33) 優先権主張国                 | 日本国 (JP)                                           |                                                                               |

最終頁に続く

## (54) 【発明の名称】表示装置の駆動回路及び表示装置

## (57) 【要約】 (修正有)

【課題】ドット反転駆動の液晶表示装置のデータ線駆動回路の回路規模を縮小する。

【解決手段】シリアルに入力されたデジタル映像信号に基づき生成されたアナログ映像信号をパラレルに出力する表示装置の駆動回路であって、シリアルに入力されたデジタル映像信号の電圧レベルを変換するレベルシフト回路32と、レベルシフト回路32によってレベル変換されたデジタル映像信号に基づきアナログ映像信号を生成するD/A変換回路14、24と、D/A変換回路14、24の出力側もしくはレベルシフト回路32とD/A変換回路14、24との間に接続され、入力されたシリアルの映像信号をパラレルに展開して保持し、映像信号をパラレルに出力する展開回路12、22とを有する。このようにレベルシフト回路32を前記画像信号レジスタ回路12、22の前段に形成する。

【選択図】図 8

**【特許請求の範囲】****【請求項 1】**

シリアルに入力されたデジタル映像信号に基づき生成されたアナログ映像信号をパラレルに出力する、表示装置の駆動回路であって、

シリアルに入力されたデジタル映像信号の電圧レベルを変換するレベルシフト回路と、

前記レベルシフト回路によってレベル変換されたデジタル映像信号に基づきアナログ映像信号を生成する D A 変換回路と、

前記 D A 変換回路の出力側もしくは前記レベルシフト回路と前記 D A 変換回路との間に接続され、入力されたシリアルの映像信号をパラレルに展開して保持し、映像信号をパラレルに出力する展開回路と、

を有する駆動回路。

**【請求項 2】**

前記レベルシフト回路は、シリアルに入力されたデジタル映像信号の電圧レベルを変換し基準電圧に対して正極のデジタル映像信号を出力する正極レベルシフト回路と、シリアルに入力されたデジタル映像信号の電圧レベルを変換し基準電圧に対して負極のデジタル映像信号を出力する負極レベルシフト回路とを備え、

前記 D A 変換回路は、前記正極デジタル映像信号に基づき正極アナログ映像信号を生成する正極 D A 変換回路と、前記負極デジタル映像信号に基づき負極アナログ映像信号を生成する負極 D A 変換回路とを備え、

前記展開回路は、前記正極 D A 変換回路の出力側もしくは前記正極レベルシフト回路と前記正極 D A 変換回路との間に接続され、シリアルに入力された正極映像信号をパラレルに展開して保持し、正極映像信号をパラレルに出力する正極展開回路と、前記負極 D A 変換回路の出力側もしくは前記負極レベルシフト回路と前記負極 D A 変換回路との間に接続され、シリアルに入力された負極映像信号をパラレルに展開して保持し、負極映像信号をパラレルに出力する負極展開回路とを備える、

請求項 1 に記載の駆動回路。

**【請求項 3】**

前記正極展開回路は、前記正極レベルシフト回路によってレベル変換され、シリアルに入力されたデジタルの映像信号をラッチし、ラッチされた前記映像信号をパラレルに出力する正極レジスタ回路を備え、

前記負極展開回路は、前記負極レベルシフト回路によってレベル変換され、シリアルに入力されたデジタルの映像信号をラッチし、ラッチされた前記映像信号をパラレルに出力する負極レジスタ回路を備え、

前記正極 D A 変換回路は、前記正極展開回路からパラレルに入力されたデジタル映像信号からアナログ映像信号を生成してパラレルに出力し、

前記負極 D A 変換回路は、前記負極展開回路からパラレルに入力されたデジタル映像信号からアナログ映像信号を生成してパラレルに出力する、

請求項 2 に記載の駆動回路。

**【請求項 4】**

前記正極 D A 変換回路は、前記正極レベルシフト回路によってレベル変換されたシリアルの正極デジタル映像信号からシリアルの正極アナログ映像信号を生成し、

前記負極 D A 変換回路は、前記負極レベルシフト回路によってレベル変換されたシリアルの負極デジタル映像信号からシリアルの負極アナログ映像信号を生成し、

前記正極展開回路は、前記シリアルの正極アナログ映像信号を順次保持し、前記正極アナログ映像信号をパラレルに出力する正極サンプルホールド回路を備え、

前記負極展開回路は、前記シリアルの負極アナログ映像信号を順次保持し、前記負極アナログ映像信号をパラレルに出力する負極サンプルホールド回路を備える、

請求項 2 に記載の駆動回路。

**【請求項 5】**

前記基準電圧はシステムグランドである、請求項 2 に記載の駆動回路。

前記共通電極に印加される共通電圧は、前記表示装置の電源回路の低位電圧である、

請求項 1 4 に記載の表示装置。

【請求項 1 6】

基準電圧に対して極性の異なる正極アナログ映像信号と負極アナログ映像信号を表示装置のデータ線に出力する、表示装置の駆動回路であつて、

基板上の第 1 の連続領域に形成され、前記正極のアナログ映像信号を出力する正極駆動回路と、

前記基板上の前記第 1 の連続領域と異なる第 2 の連続領域に形成され、前記負極のアナログ映像信号を出力する負極駆動回路と、

前記基板上の前記第 1 及び前記第 2 の連続領域と異なる第 3 の連続領域に形成され、前記正極駆動回路から出力される前記正極のアナログ映像信号と前記負極駆動回路から出力される前記負極のアナログ映像信号とを切り換える切換回路と、

を備える、表示装置の駆動回路。

【請求項 1 7】

前記基準電圧はシステムグランド電圧である、請求項 1 6 に記載の表示装置の駆動回路。

【請求項 1 8】

前記正極駆動回路は、シリアルに入力されたデジタル映像信号の電圧レベルを変換し前記基準電圧に対して正極のデジタル映像信号を出力する正極レベルシフト回路と、前記正極のデジタル映像信号をパラレルに展開して出力する正極ラッチ回路と、前記正極ラッチ回路から出力されたデジタル映像信号を D A 変換して正極のアナログ映像信号を生成する正極 D A 変換回路とを備え、

前記負極駆動回路は、シリアルに入力されたデジタル映像信号の電圧レベルを変換し前記基準電圧に対して負極のデジタル映像信号を出力する負極レベルシフト回路と、前記負極のデジタル映像信号をパラレルに展開して出力する負極ラッチ回路と、前記負極ラッチ回路から出力されたデジタル映像信号を D A 変換して負極のアナログ映像信号を生成する負極 D A 変換回路とを備える、

請求項 1 6 に記載の表示装置の駆動回路。

【請求項 1 9】

前記正極駆動回路は、シリアルに入力されたデジタル映像信号の電圧レベルを変換し前記基準電圧に対して正極のデジタル映像信号を出力する正極レベルシフト回路と、前記正極のデジタル映像信号を D A 変換して正極のアナログ映像信号を生成する正極 D A 変換回路と、前記アナログ映像信号をパラレルに展開して出力する正極サンプルホールド回路とを備え、

前記負極駆動回路は、シリアルに入力されたデジタル映像信号の電圧レベルを変換し前記基準電圧に対して負極のデジタル映像信号を出力する負極レベルシフト回路と、前記負極のデジタル映像信号を D A 変換して負極のアナログ映像信号を生成する負極 D A 変換回路と、前記アナログ映像信号をパラレルに展開して出力する負極サンプルホールド回路とを備える、

請求項 1 6 に記載の表示装置の駆動回路。

【請求項 2 0】

前記正極レベルシフト回路及び前記負極レベルシフト回路の一方は、入力された映像信号を第 1 の電圧レベルに変換する第 1 段目の電圧変換回路と、前記第 1 段目の電圧変換回路の出力を第 2 の電圧レベルに変換する第 2 段目の電圧変換回路と、を備え、

前記正極レベルシフト回路及び前記負極レベルシフト回路の他方は、前記一方のレベルシフト回路よりも少ない段数の電圧変換回路と、遅延回路とを備える、

請求項 2 、 1 8 又は 1 9 のいずれかに記載の表示装置の駆動回路。

【請求項 2 1】

前記正極駆動回路は、第 1 の電圧 > 第 2 の電圧であるような、前記第 1 の電圧と前記第 2 の電圧の範囲で動作する前記第 1 の連続領域に形成され、前記負極駆動回路は、第 3 の

10

20

30

40

50

電圧 > 第 4 の電圧であるような、前記第 3 の電圧と前記第 4 の電圧の範囲で動作する前記第 2 の連続領域に形成され、前記第 1 の電圧 > 前記第 3 の電圧、前記第 2 の電圧 > 前記第 4 の電圧であり、前記切換回路は第 1 の電圧と第 4 の電圧の範囲で動作する第 3 の連続領域に形成されている、請求項 1 6 に記載の駆動回路。

**【請求項 2 2】**

前記第 2 の電圧と前記第 3 の電圧は、前記基準電圧と等しい電圧である請求項 2 1 に記載の表示装置の駆動回路

**【請求項 2 3】**

前記第 1 の連続領域、前記第 2 の連続領域及び前記第 3 の連続領域は、それぞれ M O S トランジスタを形成し、

10

前記第 1 の連続領域及び前記第 2 の前記 M O S トランジスタのゲート酸化膜の厚さは、前記第 3 の連続領域の M O S トランジスタのゲート酸化膜の厚さはそれよりも厚い、

請求項 2 1 に記載の表示装置の駆動回路。

**【請求項 2 4】**

前記第 1 の連続領域、前記第 2 の連続領域及び前記第 3 の連続領域は、それぞれ M O S トランジスタを形成し、

前記第 1 の連続領域及び前記第 2 の前記 M O S トランジスタのゲート長の長さは前記第 3 の連続領域の M O S トランジスタのゲート長よりも長い、

請求項 2 1 に記載の表示装置の駆動回路。

**【請求項 2 5】**

複数の画素を備える表示パネルと、基準電圧に対して極性の異なる正極アナログ映像信号と負極アナログ映像信号を前記表示パネルに出力する駆動回路と、を備える表示装置であって、前記駆動回路は、

20

基板上の第 1 の連続領域に形成され、前記基準電圧に対して正極のデジタル映像信号を処理し、前記正極のデジタル映像信号を D A 変換することによって正極のアナログ映像信号を出力する正極駆動回路と、

前記基板上の前記第 1 の連続領域と異なる第 2 の連続領域に形成され、前記基準電圧に対して負極のデジタル映像信号を処理し、前記負極のデジタル映像信号を D A 変換することによって負極のアナログ映像信号を出力する負極駆動回路と、

前記正極駆動回路と前記負極駆動回路のからの出力を切り換える切換回路と、

30

を備える、表示装置。

**【請求項 2 6】**

前記表示パネルは 2 枚の基板の間に封入された液晶材料と、前記液晶材料に電界を印加する表示電極及び共通電極と、を備え、

前記基準電圧は、前記共通電極に供給される共通電圧と同一であり、

前記共通電圧は、前記表示装置の電源電圧の低位電圧である、

請求項 2 5 に記載の表示装置。

**【請求項 2 7】**

前記共通電圧はシステムグランド電圧である、請求項 2 6 に記載の表示装置。

**【請求項 2 8】**

基準電圧に対して極性の異なる正極のアナログ映像信号と負極のアナログ映像信号とを表示装置のデータ線に出力する表示装置の駆動回路であって、

40

前記正極のアナログ映像信号を出力する正極駆動回路と、

前記負極のアナログ映像信号を出力する負極駆動回路と、

極性信号に応じて前記正極又は負極のアナログ映像信号を切り換えて前記データ線に供給する切換回路と、

前記正極駆動回路と前記切換回路との間に形成され、前記データ線に供給するアナログ映像信号の極性が正極から負極に変化する前に、前記データ線を正極プリチャージ電圧にプリチャージ可能な正極プリチャージスイッチと、

前記負極駆動回路と前記切換回路との間に形成され、前記データ線に供給するアナログ

50

映像信号の極性が負極から正極に変化する前に、前記データ線を負極プリチャージ電圧にプリチャージ可能な負極プリチャージスイッチと、

を備える、表示装置の駆動回路。

**【請求項 29】**

前記基準電圧はシステムグランド電圧である、請求項28に記載の表示装置の駆動回路。

。

**【請求項 30】**

前記正極プリチャージ電圧及び前記負極プリチャージ電圧は共にシステムグランド電圧である、請求項28に記載の表示装置の駆動回路。

**【請求項 31】**

デジタル映像信号をD/A変換してアナログ映像信号を表示装置のデータ線に供給する表示装置の駆動回路であって、

システムグランドを基準に正極のアナログ映像信号を出力する正極駆動回路と、

システムグランドを基準に負極のアナログ映像信号を出力する負極駆動回路と、

前記正極駆動回路の高位電圧と前記負極駆動回路の低位電圧との範囲内であって、システムグランド電圧と異なる値に調整された直流電圧を生成し、前記表示装置の共通電極に供給する電源回路と、

を備える表示装置の駆動回路。

**【請求項 32】**

前記表示装置はn型のTFT素子を有し、

前記電源回路は、前記負極駆動回路の低位電圧とシステムグランド電圧との範囲内であって、システムグランド電圧と異なる直流電圧を生成して、前記表示装置の共通電極に供給する、請求項31に記載の表示装置の駆動回路。

**【請求項 33】**

前記表示装置はp型のTFT素子を有し、

前記電源回路は、前記正極駆動回路の高位電圧とシステムグランド電圧との範囲内であって、システムグランド電圧と異なる直流電圧を生成して、前記表示装置の共通電極に供給する、請求項31に記載の表示装置の駆動回路。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、表示装置の駆動回路及び表示装置に関し、特に、ドット反転駆動の液晶表示装置に好適な駆動回路及び表示装置に関する。

**【背景技術】**

**【0002】**

液晶表示装置は、低消費電力、軽量、薄型で携帯電話機など様々な電子機器の表示装置に採用されている。液晶表示装置には、単純マトリクス型と画素回路にTFT(Thin Film Transistor)などのアクティブ素子を用いたアクティブマトリクス型(AMLCD; Active Matrix Liquid Crystal Display)などがある。

**【0003】**

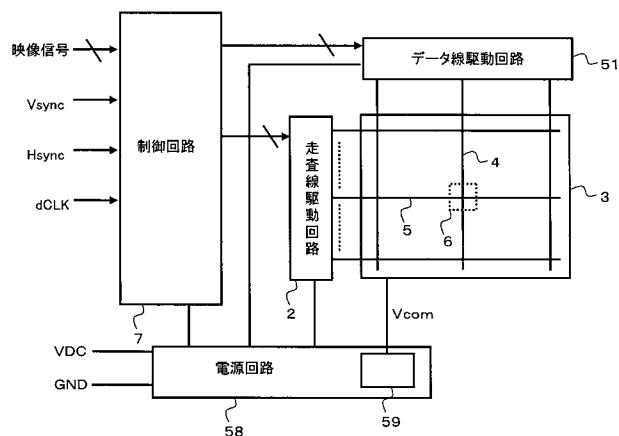

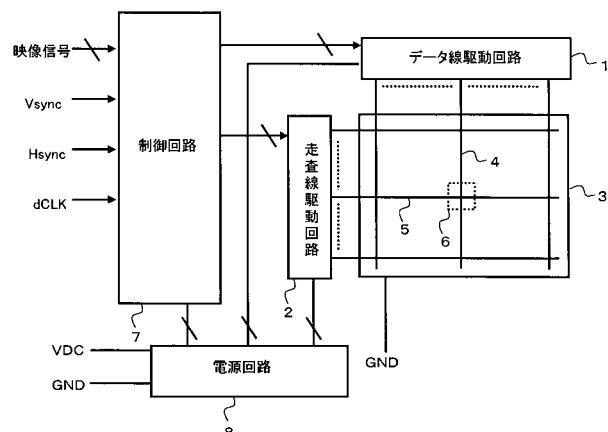

図1に公知の液晶表示装置のブロック図を示す。液晶表示装置は、走査線駆動回路2、液晶パネル3、制御回路7、データ線駆動回路51、電源回路58、コモン電圧生成回路59を有している。制御回路7には、映像信号、垂直同期信号Vsync、水平同期信号Hsync、ドットクロック信号dCLKの各信号が入力される。電源回路58は、VCD、システムGNDの電源電圧が供給される。各TFTのゲート電極は、行方向に沿った走査線5に接続され、ドレイン電極は、列方向に沿ったデータ線4に接続され、各データ線4には、制御回路7によって制御されるデータ線駆動回路51からの表示信号が入力される。この液晶表示装置は、制御回路7からの制御信号に応じて、走査線駆動回路2が走査線5を順番に走査することによって、1つの映像をディスプレイに表示する(線順次方式)。この1映像を表示する操作は、フレーム(フィールド)と呼ばれている。

10

20

30

40

50

## 【0004】

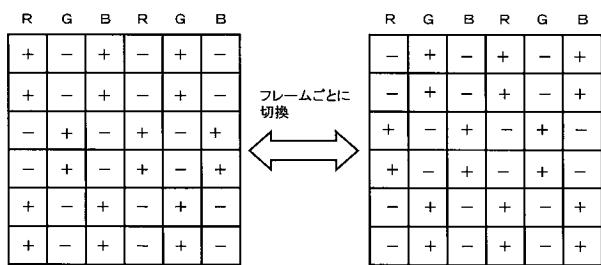

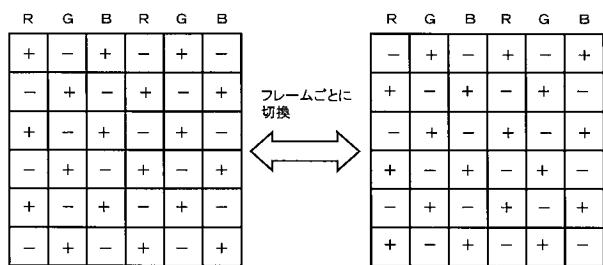

公知の液晶表示装置において、データ線4からTFTを介して画素に印加される電圧(以下、画素電圧と参照される)の極性は、所定の期間毎に反転する。つまり、画素は交流的に駆動される。ここで、極性とは、液晶の共通電極の電圧(c<sub>o</sub>m電圧)を基準とした場合の画素電圧の正負を示す。このような駆動方法は、液晶材料が劣化するのを抑制するために適用されている。例えば、図2に示すように、隣り合う画素ごとに極性が異なるよう隣り合うデータ線及び走査線ごとに画素電圧の極性を反転するドット反転駆動方式や、図3に示すように、隣り合うデータ線ごとに反転し、2本走査線ごとに極性を反転する2ラインドット反転駆動方式などが知られ、これらの駆動方式により、フリッカなどが低減され画質が向上する。

10

## 【0005】

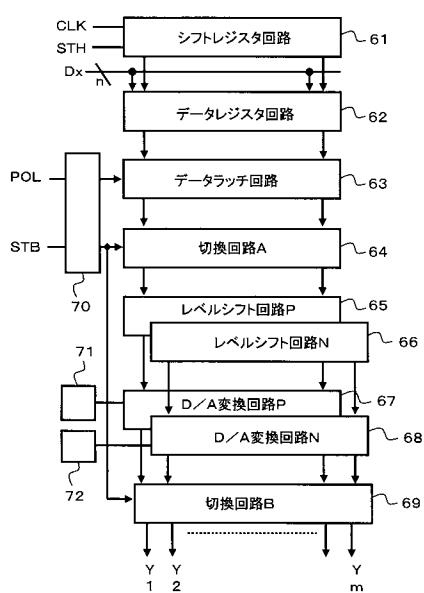

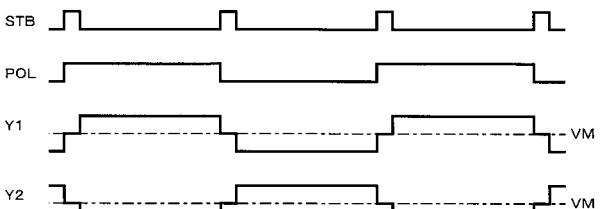

ドット反転駆動方式を実現するデータ線駆動回路51として、特許文献1によれば、図4に示す構成が開示されている。データ線駆動回路51は、シフトレジスタ回路61、データレジスタ回路62、データラッチ回路63、切換回路A64、レベルシフト回路P65、レベルシフト回路N66、DA変換回路P67、DA変換回路N68、切換回路B69、信号処理回路70、71正の階調電圧生成回路、72負の階調電圧生成回路、を有している。信号処理回路70には、ラッチ信号S<sub>T</sub>B、極性信号P<sub>O</sub>Lが入力されている。また、シフトレジスタ回路61には、水平スタート信号S<sub>T</sub>H、クロック信号C<sub>L</sub>Kが入力されている。切換回路A64は、映像信号を正極駆動回路又は負極駆動回路のいずれかに入力するように選択する。また、切換回路B69は、正極駆動回路と負極駆動回路からの出力を映像信号に対応するようにして切り換える。

20

## 【0006】

正極駆動回路は、映像信号をc<sub>o</sub>m電圧よりも正側にレベルシフトするレベルシフト回路P65と正極DA変換回路67を含み、負極駆動回路は、映像信号をc<sub>o</sub>m電圧よりも負側にレベルシフトするレベルシフト回路N66と負極DA変換回路68を含み、各電圧設定例としてc<sub>o</sub>m電圧は5V、正極側電圧は5Vから10V、負極側電圧は0Vから5Vであることが開示されている。この場合において、電源回路58でc<sub>o</sub>m電圧、データ線駆動回路の電圧、走査線駆動の電圧などを生成している。

30

## 【0007】

図5は、S<sub>T</sub>B信号、P<sub>O</sub>L信号、隣接するデータ線4の出力の関係を示すタイミングチャートである。図5に示すように、隣接するデータ線の極性は反転しており、また、フレーム毎にデータ線の出力は反転する。図6は切換回路A64及び切換回路B69の詳細図で、図5に示された各タイミングにおいてのスイッチ状態を示している。図5及び6から理解されるように、切換回路A及び切換回路B69は、ライン及びフレームごとに出力が反転するようにスイッチング動作し、ドット反転駆動を実現している。

40

## 【特許文献1】特開平10-62744号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0008】

しかしながら、この従来の駆動回路にはいくつかの問題点がある。第1の問題点は、回路規模が増大することである。各データ線に対応する駆動回路にはレベルシフト回路を設けており、レベルシフト回路は入力される電圧とレベルシフトする電圧の差が大きいと回路規模が増大する。また、レベルシフト回路は、電源電圧が高いと回路を構成する素子の耐圧を高くする必要があり、ゲート酸化膜T<sub>ox</sub>を厚く、ゲート長L及びゲート幅Wを長く、また素子間の距離を長くするなどしているため、回路面積が大きくなる。

50

## 【0009】

そして、従来の駆動回路(図4)においては、1走査線分の映像信号をデータラッチ回路63において並列にラッチした後、隣り合う2信号ごとに正もしくは負にレベルシフトするため、各駆動回路のレベルシフト回路の数は、映像信号がnビットでデータ線数がm個であれば、n×m個のレベルシフト回路が必要となる。

## 【0010】

さらに従来の駆動回路においては、1走査線分のデジタル映像信号をデータラッチ回路63において並列にラッチした後、隣り合う2信号ごとの極性を正負のレベルシフト回路65、66へ切り換えるため、デジタル映像信号を切り換える切換回路64もn×m個必要となる。

## 【0011】

第2の問題点は、消費電力が大きいことである。com電圧を5Vとすると、電源回路では、正極側電圧の高位電圧10V程度の電圧を生成するため、電源回路の効率が低下し消費電力が大きくなってしまう。電源回路は、複数の容量とスイッチで構成したチャージポンプ方式などが採用され、2.5Vから10Vの電圧を生成すると、電源の効率は60%から70%程度である。これは、スイッチなどには寄生容量があり、その寄生容量で電力を消費するために効率が低下する。例として、2.5Vから5Vの昇圧では80%の効率、5Vから10Vの昇圧でも同様に80%であっても、2.5Vから10Vだと $80\% \times 80\% = 64\%$ の効率になってしまふ。このように駆動する電源電圧が高いと昇圧する回数が増え電源回路の効率が低下し消費電力が大きくなってしまう。

## 【0012】

本発明は、上記事情を背景としてなされたものであって、表示装置もしくは表示装置の駆動回路の回路規模を低減し、更に表示装置の消費電力を低減することを目的とする。

## 【課題を解決するための手段】

## 【0013】

本発明の第1の態様に係る駆動回路は、シリアルに入力されたデジタル映像信号に基づき生成されたアナログ映像信号をパラレルに出力する、表示装置の駆動回路であって、シリアルに入力されたデジタル映像信号の電圧レベルを変換するレベルシフト回路と、前記レベルシフト回路によってレベル変換されたデジタル映像信号に基づきアナログ映像信号を生成するDA変換回路と、前記DA変換回路の出力側もしくは前記レベルシフト回路と前記DA変換回路との間に接続され、入力されたシリアルの映像信号をパラレルに展開して保持し、映像信号をパラレルに出力する展開回路と、を有する。レベルシフト回路をDA変換回路と展開回路の前段に配置することによって、回路規模を低減することができる。

## 【0014】

前記レベルシフト回路は、シリアルに入力されたデジタル映像信号の電圧レベルを変換し基準電圧に対して正極のデジタル映像信号を出力する正極レベルシフト回路と、シリアルに入力されたデジタル映像信号の電圧レベルを変換し基準電圧に対して負極のデジタル映像信号を出力する負極レベルシフト回路とを備え、前記DA変換回路は、前記正極デジタル映像信号に基づき正極アナログ映像信号を生成する正極DA変換回路と、前記負極デジタル映像信号に基づき負極アナログ映像信号を生成する負極DA変換回路とを備え、前記展開回路は、前記正極DA変換回路の出力側もしくは前記正極レベルシフト回路と前記正極DA変換回路との間に接続され、シリアルに入力された正極映像信号をパラレルに展開して保持し、正極映像信号をパラレルに出力する正極展開回路と、前記負極DA変換回路の出力側もしくは前記負極レベルシフト回路と前記負極DA変換回路との間に接続され、シリアルに入力された負極映像信号をパラレルに展開して保持し、負極映像信号をパラレルに出力する負極展開回路とを備えることが好ましい。これによって正極と負極の信号を出力する駆動回路の回路規模を低減することができる。

## 【0015】

前記正極展開回路は、前記正極レベルシフト回路によってレベル変換され、シリアルに入力されたデジタルの映像信号をラッチし、ラッチされた前記映像信号をパラレルに出力する正極レジスタ回路を備え、前記負極展開回路は、前記負極レベルシフト回路によってレベル変換され、シリアルに入力されたデジタルの映像信号をラッチし、ラッチされた前記映像信号をパラレルに出力する負極レジスタ回路を備え、前記正極DA変換回路は、前記正極展開回路からパラレルに入力されたデジタル映像信号からアナログ映像信号を生成

10

20

30

40

50

してパラレルに出力し、前記負極 D A 変換回路は、前記負極展開回路からパラレルに入力されたデジタル映像信号からアナログ映像信号を生成してパラレルに出力することが好ましい。パラレルの D A 変換回路を備えることによって、D A 変換回路の動作に伴うオフセットばらつきによる表示品質に低下を抑制することができる。

#### 【 0 0 1 6 】

前記正極 D A 変換回路は、前記正極レベルシフト回路によってレベル変換されたシリアルの正極デジタル映像信号からシリアルの正極アナログ映像信号を生成し、前記負極 D A 変換回路は、前記負極レベルシフト回路によってレベル変換されたシリアルの負極デジタル映像信号からシリアルの負極アナログ映像信号を生成し、前記正極展開回路は、前記シリアルの正極アナログ映像信号を順次保持し、前記正極アナログ映像信号をパラレルに出力する正極サンプルホールド回路を備え、前記負極展開回路は、前記シリアルの負極アナログ映像信号を順次保持し、前記負極アナログ映像信号をパラレルに出力する負極サンプルホールド回路を備えることが好ましい。シリアルの D A 変換回路を備えることによって、階調数が大きい場合における回路規模の増大を低減することができる。

#### 【 0 0 1 7 】

前記基準電圧はシステムグランドであることが好ましい。これによって、液晶表示装置における共通電圧を生成する回路をシンプルにすることができます。

#### 【 0 0 1 8 】

アナログ映像信号を出力する複数の外部出力端子と、前記外部出力端子のそれぞれに入力される正極アナログ映像信号と負極アナログ映像信号を切り換える切換回路をさらに備えることが好ましい。さらに、前記切換回路は、前記正極レベルシフト回路によって変換される最高電圧以上の電圧、もしくは、前記負極レベルシフト回路によって変換される最低電圧以下の電圧で制御されることが好ましい。これによって、駆動回路と異なる電圧で動作する回路を同一基板内に容易に実装することができる。

#### 【 0 0 1 9 】

前記切換回路の切り換え処理の前に前記複数の外部出力端子をプリチャージ配線に接続する複数のプリチャージスイッチをさらに備えることが好ましい。これによって、外部端子へ信号を出力する回路に過大な電圧が印加されることを防止することができる。さらに、前記複数のプリチャージスイッチは、前記切換回路の前段側に接続され、複数の前記外部出力端子を正極プリチャージ配線に接続する正極プリチャージスイッチと、前記切換回路の前段側に接続され、複数の前記外部出力端子を負極プリチャージ配線に接続する負極プリチャージスイッチと、をさらに備えることが好ましい。これによって、プリチャージスイッチのサイズを小さくすることができる。

#### 【 0 0 2 0 】

前記正極 D A 変換回路は、同一色の一出力に対応する複数の正極 D A 変換回路要素を備え、前記正極 D A 変換回路要素によって変換されたアナログ映像信号を選択的に出力し、前記負極 D A 変換回路は、同一色の一出力に対応する複数の負極 D A 変換回路要素を備え、前記負極 D A 変換回路要素によって変換されたアナログ映像信号を選択的に出力することが好ましい。これによって、D A 変換回路の動作におけるオフセットのばらつきを低減することができる。

#### 【 0 0 2 1 】

前記正極 D A 変換回路及び負極 D A 変換回路は、それぞれボルテージフォロワ回路を備え、第 1 の駆動期間にデジタル映像信号に基づいて選択した信号を前記ボルテージフォロワ回路を介して出力し、第 2 の駆動期間においてデジタル映像信号に基づいて選択した信号を前記ボルテージフォロワ回路を介さずに出力することができる。これによって、D A 変換回路の動作におけるオフセットのばらつきを低減することができる。

#### 【 0 0 2 2 】

前記正極 D A 変換回路及び負極 D A 変換回路は、それぞれ、差動入力を切り換えるボルテージフォロワ回路を備えることが好ましい。これによって、D A 変換回路の動作におけるオフセットのばらつきを低減することができる。あるいは、前記正極 D A 変換回路及び

10

20

30

40

50

負極 D A 変換回路は、それぞれ、 R G B ごとに独立した階調電圧生成回路を備えることが好ましい。これによって、画像品質を向上することができる。

#### 【 0 0 2 3 】

本発明の第 2 の態様は、複数の画素を備える表示パネルと、前記画素の輝度を制御するアナログ映像信号を出力する駆動回路と、を備える表示装置であって、前記駆動回路は、シリアルに入力されたデジタル映像信号の電圧レベルを変換するレベルシフト回路と、前記レベルシフト回路によってレベル変換されたデジタル映像信号に基づきアナログ映像信号を生成する D A 変換回路と、前記 D A 変換回路の出力側もしくは前記レベルシフト回路と前記 D A 変換回路との間に接続され、入力されたシリアルの映像信号をパラレルに展開して保持し、映像信号をパラレルに出力する展開回路を有する。

10

#### 【 0 0 2 4 】

前記表示パネルは、2枚の基板の間に封入された液晶材料と、前記液晶材料に電界を印加する表示電極と共に通電極とを備え、前記共通電極に印加される共通電圧は、前記表示装置の電源回路の低位電圧であることが好ましい。これによって、共通電圧生成回路をシンプルにすることができる。

#### 【 0 0 2 5 】

本発明の第 3 の態様は、基準電圧に対して極性の異なる正極アナログ映像信号と負極アナログ映像信号を表示装置のデータ線に出力する、表示装置の駆動回路であって、基板上の第 1 の連続領域に形成され、前記正極のアナログ映像信号を出力する正極駆動回路と、前記基板上の前記第 1 の連続領域と異なる第 2 の連続領域に形成され、前記負極のアナログ映像信号を出力する負極駆動回路と、前記基板上の前記第 1 及び前記第 2 の連続領域と異なる第 3 の連続領域に形成され、前記正極駆動回路から出力される前記正極のアナログ映像信号と前記負極駆動回路から出力される前記負極のアナログ映像信号とを切り換える切換回路と、を備える、表示装置の駆動回路。ことが好ましい。これによって、回路規模を低減することができる。さらに、前記基準電圧はシステムグランド電圧であることが好ましい。

20

#### 【 0 0 2 6 】

前記正極駆動回路は、シリアルに入力されたデジタル映像信号の電圧レベルを変換し前記基準電圧に対して正極のデジタル映像信号を出力する正極レベルシフト回路と、前記正極のデジタル映像信号をパラレルに展開して出力する正極ラッチ回路と、前記正極ラッチ回路から出力されたデジタル映像信号を D A 変換して正極のアナログ映像信号を生成する正極 D A 変換回路とを備え、前記負極駆動回路は、シリアルに入力されたデジタル映像信号の電圧レベルを変換し前記基準電圧に対して負極のデジタル映像信号を出力する負極レベルシフト回路と、前記負極のデジタル映像信号をパラレルに展開して出力する負極ラッチ回路と、前記負極ラッチ回路から出力されたデジタル映像信号を D A 変換して負極のアナログ映像信号を生成する負極 D A 変換回路とを備えることが好ましい。

30

#### 【 0 0 2 7 】

前記正極駆動回路は、シリアルに入力されたデジタル映像信号の電圧レベルを変換し前記基準電圧に対して正極のデジタル映像信号を出力する正極レベルシフト回路と、前記正極のデジタル映像信号を D A 変換して正極のアナログ映像信号を生成する正極 D A 変換回路と、前記アナログ映像信号をパラレルに展開して出力する正極サンプルホールド回路とを備え、前記負極駆動回路は、シリアルに入力されたデジタル映像信号の電圧レベルを変換し前記基準電圧に対して負極のデジタル映像信号を出力する負極レベルシフト回路と、前記負極のデジタル映像信号を D A 変換して負極のアナログ映像信号を生成する負極 D A 変換回路と、前記アナログ映像信号をパラレルに展開して出力する負極サンプルホールド回路とを備えてよい。これにより、n ビットのデジタル映像信号の場合には n 本必要であるデータ線を 1 本にすることができる。

40

#### 【 0 0 2 8 】

前記正極レベルシフト回路及び前記負極レベルシフト回路の一方は、入力された画像信号を第 1 の電圧レベルに変換する第 1 段目の電圧変換回路と、前記第 1 段目の電圧変換回

50

路の出力を第2の電圧レベルに変換する第2段目の電圧変換回路と、を備え、前記正極レベルシフト回路及び前記負極レベルシフト回路の他方は、前記一方のレベルシフト回路よりも少ない段数の電圧変換回路と、遅延回路とを備えることが好ましい。これによって、入力されるデジタル映像信号の電圧に応じてレベルシフト回路を構成すると共に、回路構成の相違による出力信号のタイミング差を防止することができる。

【0029】

前記正極駆動回路は、第1の電圧 > 第2の電圧であるような、前記第1の電圧と前記第2の電圧の範囲で動作する前記第1の連続領域に形成され、前記負極駆動回路は、第3の電圧 > 第4の電圧であるような、前記第3の電圧と前記第4の電圧の範囲で動作する前記第2の連続領域に形成され、前記第1の電圧 > 前記第3の電圧、前記第2の電圧 > 前記第4の電圧であり、前記切換回路は第1の電圧と第4の電圧の範囲で動作する第3の連続領域に形成されていてもよい。また、前記第2の電圧と前記第3の電圧は前記基準電圧と等しい電圧であってもよい。

【0030】

前記第1の連続領域、前記第2の連続領域及び前記第3の連続領域は、それぞれMOSトランジスタを形成し、前記第1の連続領域及び前記第2の前記MOSトランジスタのゲート酸化膜の厚さは、前記第3の連続領域のMOSトランジスタのゲート酸化膜の厚さはそれよりも厚いことが好ましい。

【0031】

前記第1の連続領域、前記第2の連続領域及び前記第3の連続領域は、それぞれMOSトランジスタを形成し、前記第1の連続領域及び前記第2の前記MOSトランジスタのゲート長の長さは前記第3の連続領域のMOSトランジスタのゲート長よりも長いことが好ましい。

【0032】

本発明の第4の態様は、複数の画素を備える表示パネルと、基準電圧に対して極性の異なる正極アナログ映像信号と負極アナログ映像信号を前記表示パネルに出力する駆動回路と、を備える表示装置であって、前記駆動回路は、基板上の第1の連続領域に形成され、前記基準電圧に対して正極のデジタル映像信号を処理し、前記正極のデジタル映像信号をDA変換することによって正極のアナログ映像信号を出力する正極駆動回路と、前記基板上の前記第1の連続領域と異なる第2の連続領域に形成され、前記基準電圧に対して負極のデジタル映像信号を処理し、前記負極のデジタル映像信号をDA変換することによって負極のアナログ映像信号を出力する負極駆動回路と、前記正極駆動回路と前記負極駆動回路のからの出力を切り換える切換回路を備える。

【0033】

前記表示パネルは2枚の基板の間に封入された液晶材料と、前記液晶材料に電界を印加する表示電極及び共通電極と、を備え、前記基準電圧は、前記共通電極に供給される共通電圧と同一であり、前記共通電圧は、前記表示装置の電源電圧の低位電圧であることが好ましい。さらに、前記共通電圧はシステムグランド電圧であることが好ましい。

【0034】

本発明の第5の態様は、基準電圧に対して極性の異なる正極のアナログ映像信号と負極のアナログ映像信号とを表示装置のデータ線に出力する表示装置の駆動回路であって、前記正極のアナログ映像信号を出力する正極駆動回路と、前記負極のアナログ映像信号を出力する負極駆動回路と、極性信号に応じて前記正極又は負極のアナログ映像信号を切り換えて前記データ線に供給する切換回路と、前記正極駆動回路と前記切換回路との間に形成され、前記データ線に供給するアナログ映像信号の極性が正極から負極に変化する前に、前記データ線を正極プリチャージ電圧にプリチャージ可能な正極プリチャージスイッチと、前記負極駆動回路と前記切換回路との間に形成され、前記データ線に供給するアナログ映像信号の極性が負極から正極に変化する前に、前記データ線を負極プリチャージ電圧にプリチャージ可能な負極プリチャージスイッチとを備える。この場合においては、前記基準電圧はシステムグランド電圧であることが好ましい。

10

20

30

40

50

## 【0035】

更に、前記正極プリチャージ電圧及び前記負極プリチャージ電圧は共にシステムグランド電圧であることが好ましい。プリチャージ電源を別個に設ける必要がなくなる。

## 【0036】

本発明の第6の態様は、デジタル映像信号をDA変換してアナログ映像信号を表示装置のデータ線に供給する表示装置の駆動回路であって、システムグランドを基準に正極のアナログ映像信号を出力する正極駆動回路と、システムグランドを基準に負極のアナログ映像信号を出力する負極駆動回路と、前記正極駆動回路の高位電圧と前記負極駆動回路の低位電圧との範囲内であって、システムグランド電圧でない直流電圧を生成して、前記表示装置の共通電極に供給する電源回路とを備える。これにより、表示装置が有するTFT素子のフィードスルー誤差による影響を低減することができる。10

## 【0037】

前記表示装置がn型のTFT素子を有する場合は、前記電源回路は、前記負極駆動回路の低位電圧とシステムグランド電圧との範囲内であって、システムグランド電圧でない直流電圧を生成して、前記表示装置の共通電極に供給し、前記表示装置がp型のTFT素子を有する場合は、前記電源回路は、前記正極駆動回路の高位電圧とシステムグランド電圧との範囲内であって、システムグランド電圧でない直流電圧を生成して、前記表示装置の共通電極に供給することが好ましい。

## 【発明の効果】

## 【0038】

本発明により、表示装置の駆動回路の回路規模の低減及び消費電力の低減を図ることができる。20

## 【発明を実施するための最良の形態】

## 【0039】

以下に、本発明を適用可能な実施の形態が説明される。以下の説明は、本発明の実施形態を説明するものであり、本発明が以下の実施形態に限定されるものではない。説明の明確化のため、以下の記載は、適宜、省略及び簡略化がなされている。又、当業者であれば、以下の実施形態の各要素を、本発明の範囲において容易に変更、追加、変換することが可能である。

## 【0040】

実施の形態1.

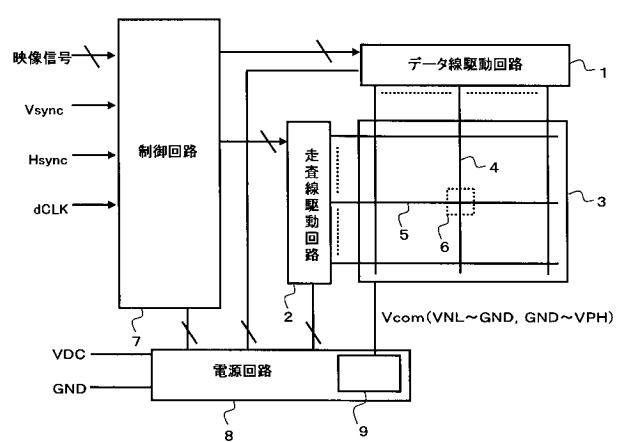

図7に本形態の液晶表示装置のブロック図を示す。液晶パネル3上には、複数のデータ線4と、データ線と直交するように配置する複数の走査線5とが形成され、その各交点にスイッチング素子としてのTFT(Thin Film Transistor)と液晶などを含む画素6が形成されている。画素には、液晶に電界を印加する表示電極と共に通電極が形成されている。表示電極にはデータ線から画素の輝度(光の透過量)を制御するアナログ映像信号が供給され、共通電極には直流電圧(DC)のCOM電圧が供給される。さらに、液晶表示装置は、データ線4を駆動するデータ線駆動回路1と、走査線5を駆動する走査線駆動回路2と、データ線駆動回路1及び走査線駆動回路2を制御する制御回路7と、制御回路7とデータ線駆動回路1と走査線駆動回路2に電源を供給する電源回路8とを備える。電源回路8に供給する電源電圧の高位電圧はVDCで、低位電圧はシステムGNDである。40

## 【0041】

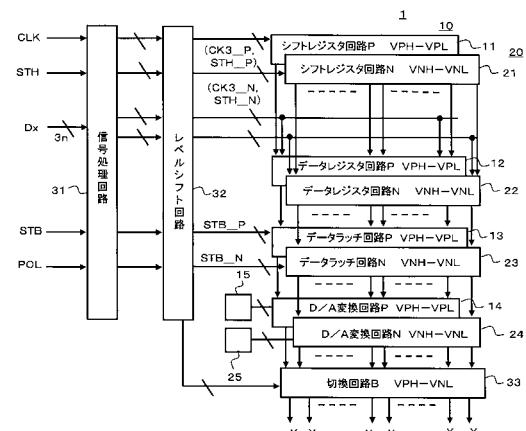

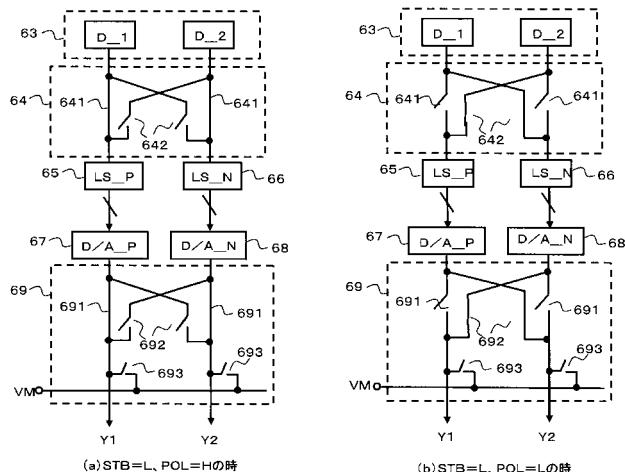

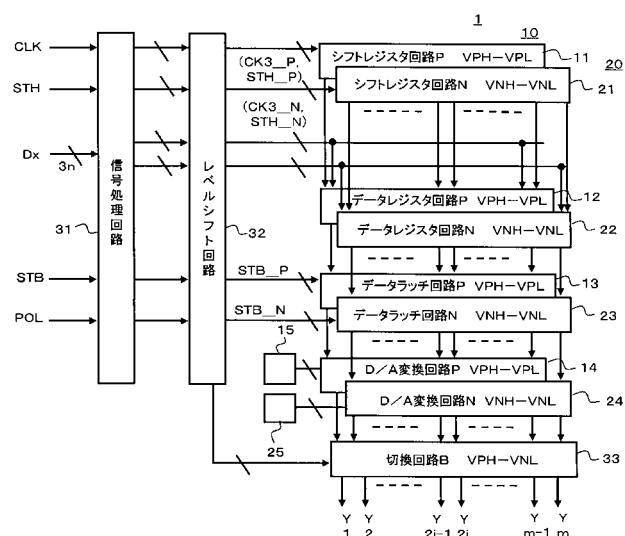

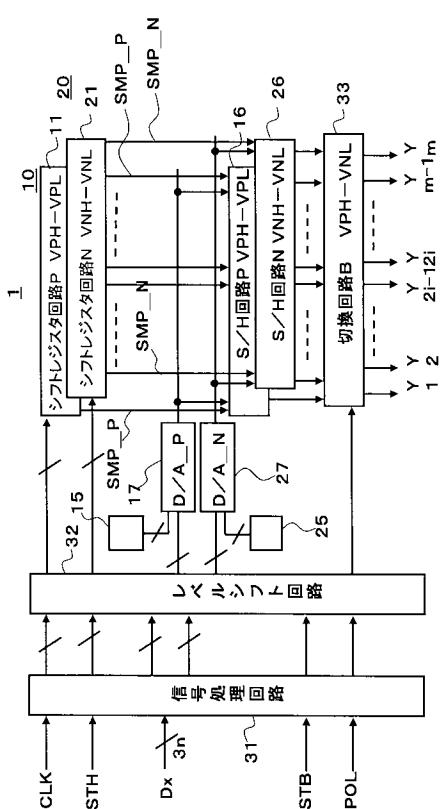

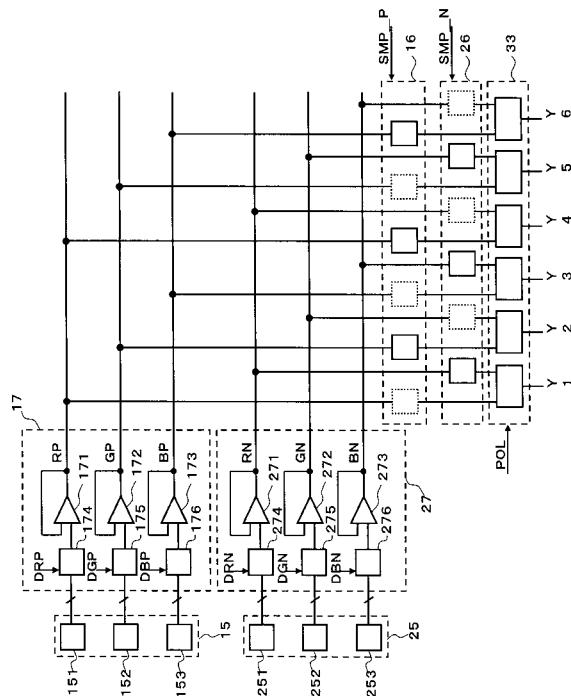

図8は本発明のデータ線駆動回路1のブロック図を示している。以下に、各部の構成及び動作について説明する。データ線駆動回路1は、シフトレジスタ回路11、21、データレジスタ回路12、22、データラッチ回路13、23、DA変換回路14、24、階調電圧生成回路15、25、信号処理回路31、レベルシフト回路32、切換回路33を含む回路を備える。

## 【0042】

データ線駆動回路1に入力する信号は、少なくともデジタル映像信号DX(以下映像信号DXと略す)、クロック信号CLK、水平スタート信号STH、ラッチ信号STB、50

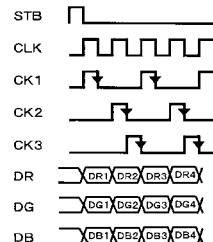

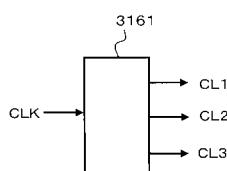

極性信号 P O L を含み、これらの信号から信号処理回路 3 1 にて所望のタイミング信号を生成し、後述のデータラッチ回路 1 3、2 3 や切換回路 3 3などを制御している。また、信号処理回路 3 1 は、図 9 に示すようなクロック生成回路 3 1 6 1 を備え、クロック生成回路 3 1 6 1 においてクロック信号 C L K から、図 1 0 に示すようなクロック信号 C L K に同期した C K 1 信号、C K 2 信号、C K 3 信号なども生成している。

#### 【 0 0 4 3 】

64 階調（6 ビット）のカラー液晶表示装置では、映像信号 D x は、D R ( D R 0 0 , D R 0 1 , D R 0 2 , D R 0 3 , D R 0 4 , D R 0 5 ) , D G ( D G 0 0 , D G 0 1 , D G 0 2 , D G 0 3 , D G 0 4 , D G 0 5 ) , D B ( D B 0 0 , D B 0 1 , D B 0 2 , D B 0 3 , D B 0 4 , D B 0 5 ) の計 18 ビットの 1 画素分の信号をクロック信号 C L K に同期して入力する。以下映像信号 D x が R G B 各 6 ビットの場合において説明するが、それに限定されるものではなく映像信号 D x は各 7 ビット以上でもよいし、各 5 ビット以下でもよい。

#### 【 0 0 4 4 】

データ線駆動回路 1 に入力するデジタル映像信号を 1 画素ごと（18 ビット）に入力すると、画素数が Q V G A ( 2 4 0 R G B × 3 2 0 ) では、クロック周波数は、フレーム周波数 × 画素数 = 6 0 H z × 3 2 0 × 2 4 0 = 約 4 . 6 M H z 程度である。画素数が 4 倍の V G A ( 4 8 0 R G B × 6 4 0 ) でもデータ線駆動回路に入力する映像信号を 2 画素ごと（36 ビット）にすればクロック周波数は 9 . 2 M H z 程度で済む。

#### 【 0 0 4 5 】

水平スタート信号 S T H がシフトレジスタ回路 1 1、2 1 に入力されると、シフトレジスタ回路 1 1、2 1 では、順にクロック信号 C L K に同期したサンプリング信号が生成される。シフトレジスタ回路は、複数のフリップ・フロップ回路から構成されている。クロック信号 C L K に同期して順次入力した映像信号 D x は、サンプリング信号に応じてデータレジスタ回路 1 2、2 2 でラッチされる。データレジスタ回路 1 2、2 2 でラッチされた映像信号 D x は、ラッチ信号 S T B の入力に応答して、並列にデータラッチ回路 1 3、2 3 に出力され、データラッチ回路 1 3、2 3 でラッチされる。データラッチ回路 1 3、2 3 は D A 変換回路 1 4、2 4 に接続されており、極性信号 P O L に応じて正極信号と負極信号を交互に選択する切換回路 3 3 を介し、正極及び負極の信号を各データ線に供給する。

#### 【 0 0 4 6 】

本発明のデータ線駆動回路 1 は、隣り合う各データ線に同時に異なる極性のアナログ映像信号を出力する。データ線駆動回路 1 は、正極のアナログ映像信号を供給する正極駆動回路 1 0 及び負極のアナログ映像信号を供給する負極駆動回路 2 0 を備え、切換回路 3 3 で正極又は負極を選択してデータ線へ出力する。ここで正極、負極とは液晶の液晶共通電極の電圧（c o m 電圧）を基準とした場合の画素電圧の正負を示す。

#### 【 0 0 4 7 】

本発明においては、データ線にアナログ映像信号を供給する駆動回路が主体である。正極駆動回路 1 0 の動作電圧は V P L ~ V P H 、負極駆動回路 2 0 の動作電圧は V N L ~ V N H である。また、データ線を駆動する駆動回路の基準電圧はシステム G N D ( 0 V ) であり、c o m 電圧も G N D である。V P L と V N H が G N D と同電圧の場合は、V P L と V N H を G N D にショートしてもよいが、V P H > V P L 、V P H > V N H 、V N H > V N L 、V P L > V N L の関係であれば、V N H と V P L は別電圧でもよい。以降実施の形態 1 での説明においては、説明を簡便化するために V P L = V N H = G N D 、V P H = 5 V 、V N L = - 5 V として説明する。ここで、液晶のしきい電圧が 3 V 程度で動作するのであれば、V P H = 3 V 、V N L = - 3 V としてもよい。また、T F T 素子の寄生容量によるフィードスルー誤差を考慮する場合、V P H = 6 V 、V N L = - 4 V 、又は V P H = 4 V 、V N L = - 6 V 、としてもよい。

#### 【 0 0 4 8 】

正極駆動回路 1 0 は、少なくとも正極 D A 変換回路 1 4 、正極階調電圧生成回路 1 5 を

10

20

30

40

50

含んでいる。本形態においては、正極駆動回路10はさらに、正極シフトレジスタ回路11、ラッチ回路である正極データレジスタ回路12と正極データラッチ回路13などを含む。各回路の動作電圧はGND～VPHである。負極駆動回路20は、少なくとも負極DA変換回路24、負極階調電圧生成回路25を含む。また、負極シフトレジスタ回路21、ラッチ回路である負極データレジスタ回路22と負極データラッチ回路23などを含む。各回路の動作電圧はVNL～GNDである。

#### 【0049】

信号処理回路31はVSS～VDD(2.5V)で動作している。そのため、信号処理回路31と正極駆動回路10及び負極駆動回路20との間にはレベルシフト回路32を設ける。信号処理回路31の低位電圧VSSはGNDにショートしてもよいし、VSSはGND以外の電圧でもよい。以降実施の形態1での説明においては、説明を簡便化するためにVSS=GNDとして説明する。10

#### 【0050】

レベルシフト回路32は、信号処理回路31で生成する各信号に対応して後述の正極レベルシフト回路321と負極レベルシフト回路322と、高圧レベルシフト回路323を備えている。正極駆動回路10及び負極駆動回路20に入力する信号は、それぞれ、正極レベルシフト回路321及び負極レベルシフト回路によって各々の動作電圧へレベルシフトされた後に入力される。例えば、クロック信号CLKから生成されたCK3信号は、正極側にレベルシフトしたCK3\_P信号が正極駆動回路10に入力され、負極側にレベルシフトされたCK3\_Nが負極駆動回路20に入力される。スタート信号STHなど他の信号についても同様に、信号\_P及び信号\_Nのそれぞれが、正極駆動回路10及び負極駆動回路20に入力される。切換回路33を制御する信号は、(VNL-VPH)の電圧で動作するので、高圧レベルシフト回路323を介して信号が入力される。ここで、切換回路33を制御する信号の電圧がVPH以上の電圧、VNL以下の電圧であればよい。20

#### 【0051】

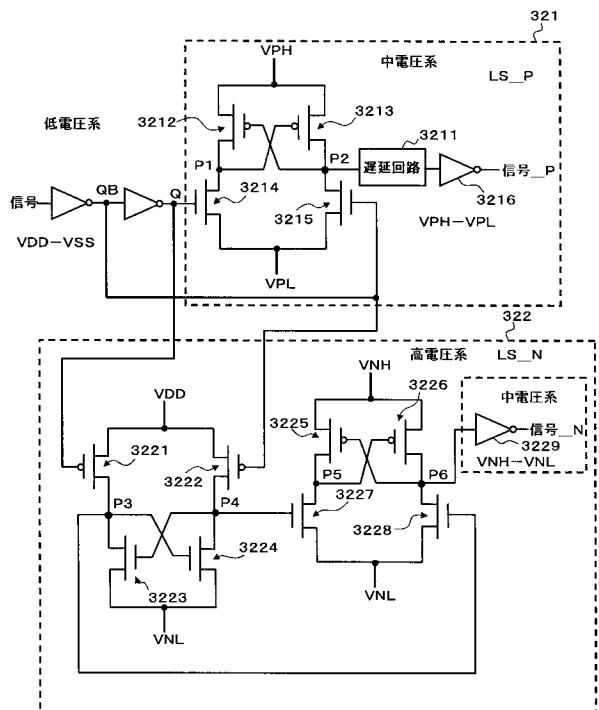

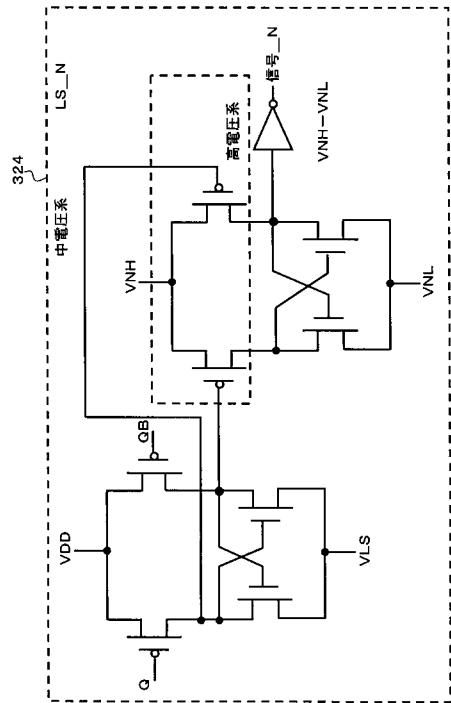

以下に、レベルシフト回路32の詳細を説明する。図11及び図12に示すのが、本形態において使用されるレベルシフト回路32である。図11、12において、トランジスタの記号は通常使用されるものであって、ゲートに円が付されているものがPchトランジスタ、円のないものがNchトランジスタである。尚、この点は、以下の図面において同様である。図11に示される正極レベルシフト回路321は、(GND-VDD)レベルの信号を正極信号(GND-VPH)に変換する。負極レベルシフト回路322は、(GND-VDD)レベルの信号を負極信号(VNL-GND)に変換する。正極レベルシフト回路321は、遅延回路3211を有する点以外は、一般的に使用されているレベルシフト回路と同様である。入力電圧を変換する正極レベルシフト回路321は、VPH-GND間に接続されたPchトランジスタ3212及びNchトランジスタ3214の直列回路並びにPchトランジスタ3213及びNchトランジスタ3215の直列回路を備えている。外部からの入力は低電圧側のNchトランジスタ3214又はNchトランジスタ3215のゲートに入力され、一方の直列回路におけるPchトランジスタ3213とNchトランジスタ3215の中間ノード(PchトランジスタとNchトランジスタの間)P2から信号が出力される。Pchトランジスタ3212又はPchトランジスタ3213のゲートは、他方の直列回路の中間ノードP1又はP2に接続されている。30

#### 【0052】

正極レベルシフト回路321の動作を簡単に説明する。簡略化のため、ノードQ又はノードQBの入力に対するノードP2の出力を説明する。ノードQに「H」レベル即ちVDD電圧が入力された場合、Nchトランジスタ3214がアクティブとなりノードP1がGND電圧、即ち「L」レベルとなる。従ってPchトランジスタ3213がアクティブとなりノードP2がVPH電圧となる。逆にノードQに「L」レベル即ちGND電圧が入力される場合、そのときノードQBは「H」レベルとなっているので、Nchトランジスタ3215がアクティブとなる。従ってノードP2がGND電圧となる。このように入力信号に応じて出力された信号は、遅延回路を介し、インバータ3216によって外部に出40

力される。

#### 【0053】

負極レベルシフト回路322は、2段構成のレベルシフト回路で、1段目のレベルシフトでVNL-VDDにシフトし、2段目で(VNL-GND)にシフトしている。1段目において、VDD-VNL間に接続されたPchトランジスタ3221及びNchトランジスタ3223の直列回路並びにPchトランジスタ3222及びNchトランジスタ3224の直列回路を備えている。外部からの入力は高電圧側のPchトランジスタ3221又はPchトランジスタ3222の各ゲートに入力され、一方の直列回路におけるPchトランジスタ3222とNchトランジスタ3224の中間ノードP4から信号が出力される。Nchトランジスタ3223又はNchトランジスタ3224のゲートは、他方の直列回路の中間ノードP3又はP4に接続されている。外部からの極性の異なる信号がノードQB、Qから高電圧側に接続された各Pchトランジスタのゲートに入力されている。10

#### 【0054】

2段目において、1段目からの出力のそれぞれが、低電圧側に接続されたNchトランジスタ3227又はNchトランジスタ3228のゲートに入力されている。2段目の出力はインバータ3229を介して外部に出力される。2段目の回路構成は、電源電圧は異なるが、正極レベルシフト回路のレベルシフタ3211と同様である。即ち、GND-VNL間に並列に接続されたPchトランジスタ3225及びNchトランジスタ3227の直列回路並びにPchトランジスタ3226及びNchトランジスタ3228の直列回路を備えている。20

#### 【0055】

負極レベルシフト回路322の動作を説明する。まずノードQ又はノードQBに対するノードP3及びノードP4の出力について説明する。ノードQに「H」レベル即ちVDD電圧が入力された場合、ノードQBは「L」レベル即ちGND電圧となっているので、Pchトランジスタ3222がアクティブとなる。従ってノードP4はVDD電圧、即ち「H」レベルとなる。するとNchトランジスタ3223がアクティブとなるのでノードP3はVNL電圧、即ち「L」レベルとなる。逆にノードQに「L」レベル即ちGND電圧が入力された場合、Pchトランジスタ3221がアクティブとなりノードP3がVDD電圧、即ち「H」レベルとなる。従ってNchトランジスタ3224がアクティブとなりノードP4がVNL電圧、即ち「L」レベルとなる。30

#### 【0056】

次にノードP4に対するノードP6の出力について説明する。ノードP4が「H」レベル即ちVDD電圧の場合、Nchトランジスタ3227がアクティブとなりノードP5がVNL電圧、即ち「L」レベルとなる。するとPchトランジスタ3226がアクティブとなりノードP6がGND電圧となる。逆にノードP4が「L」レベル即ちVNL電圧の場合はノードP3が「H」レベルとなっているので、Nchトランジスタ3228がアクティブとなる。従ってノードP6がVNL電圧となる。

#### 【0057】

2段構成である負極レベルシフト回路322は遅延時間が大きいため、上記のように、正極レベルシフト回路321で負極レベルシフト回路と同じ遅延時間になるように遅延回路3211を設けるとよい。尚、コンパレータを使用してレベルシフトすることも可能であるが、コンパレータは定常電流が流れ消費電力が大きくなることから携帯型電子機器などの液晶表示装置には必ずしも好適ではない。40

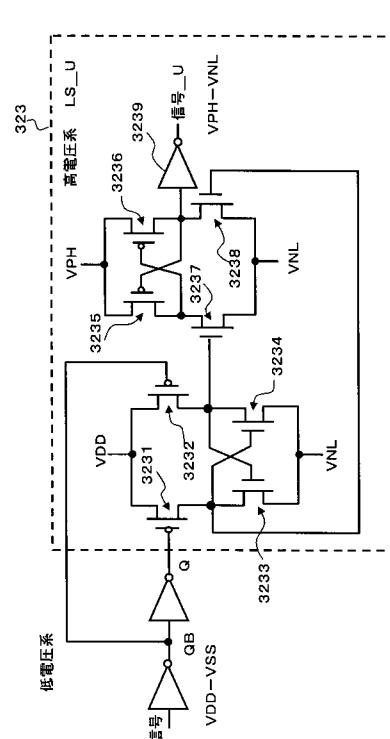

#### 【0058】

図12に高圧レベルシフト回路323の詳細図を示す。回路構成は、負極レベルシフト回路322と実質的に同様であり、2段構成となっている。即ち、1段目においてVDD-VNL間に接続されたPchトランジスタ3231及びNchトランジスタ3233の直列回路並びにPchトランジスタ3232及びNchトランジスタ3234の直列回路を備え、2段目においてVPH-VNL間に接続されたPchトランジスタ3235及び50

Nchトランジスタ3237の直列回路並びにPchトランジスタ3236及びNchトランジスタ3238の直列回路を備えている。高圧レベルシフト回路323は、(GND-VDD)レベルの信号を(VNL-VPH)レベルにシフトする。1段目において(GND-VDD)レベルの信号を(VNL-VDD)レベルにシフトし、2段目において(VNL-VPH)レベルにシフトする。動作原理については上記の通り負極レベルシフト回路322と同様であるため省略する。2段目の出力はインバータ3239を介して外部に出力される。前述したように、切換回路33はVPH以上の電圧、VNL以下の電圧であればよいので、この場合、高圧レベルシフト回路323の動作電圧もVPH以上の電圧、VNL以下の電圧にすればよい。

## 【0059】

10

カラー表示では、1画素はRGBの3つのドットで構成されるので、表示色はRGBの3ドットが単位となる。ドット反転駆動方式では、図13に示すようにX1ラインの1画素目(R1, G1, B1)では(+, -, +)、2画素目(R2, G2, B2)では(-, +, -)を印加する。つまり隣り合う画素の極性が異なるために、隣り合う2端子Y(2i-1), Y(2i)(iは自然数)において、それぞれ正、負又は負、正を同時に供給することになる。ここで、RGBの3ドット単位に、もしくは、正、負の2ドット単位に制御するよりも、2と3の公倍数である6ドット単位、つまり2画素ごとに制御すると信号処理回路31の回路構成が簡単になる。6ドット単位以外でも12ドット単位や18ドット単位など6の倍数のドット数で制御するのが好ましい。

## 【0060】

20

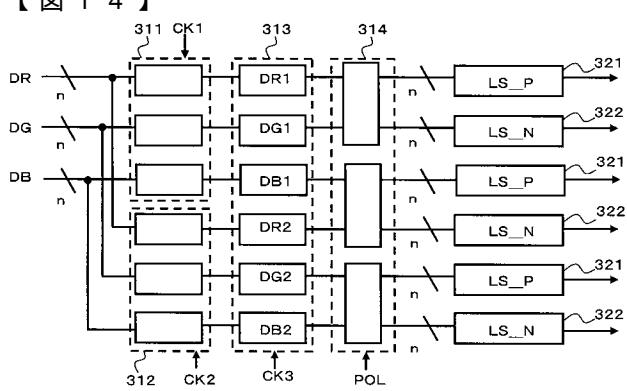

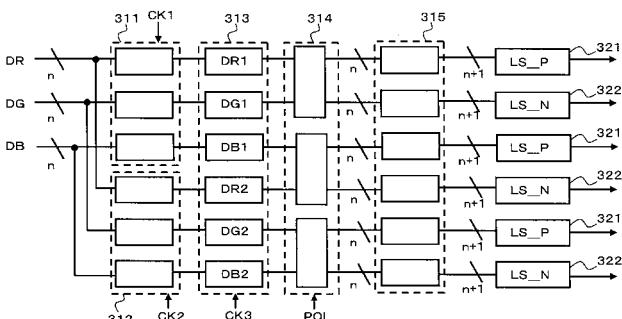

図14に示すのが、信号処理回路31において、映像信号DX(DR, DG, DB)を正極駆動回路10又は負極駆動回路20に振り分ける回路である。1画素目の映像信号(DR1, DG1, DB1)及び2画素目の映像信号(DR2, DG2, DB2)をそれぞれCK1信号及びCK2信号に応じてラッチ回路311及びラッチ回路312でラッチし、1画素目の映像信号(DR1, DG1, DB1)及び2画素目の映像信号(DR2, DG2, DB2)を同時にCK3信号に応じてラッチ回路313でラッチする。ラッチ回路313でラッチした映像信号は、映像信号切換回路314で正極駆動回路10及び負極駆動回路20のいずれかに選択的に入力される。映像信号切換回路314の出力の選択は、極性信号POLのH、Lに応じてなされる。

## 【0061】

30

図14においてはデータ線駆動回路1に入力される映像信号DXが1画素ごとに入力される場合を考え、6ドット単位の処理を行なうために、ラッチ回路311及び312と、クロック信号CLKから生成されたCK1信号及びCK2信号を用いてラッチ回路313で映像信号を6ドット分ラッチしたが、データ線駆動回路1に入力する映像信号が元から2画素ごと(36ビット)であれば、ラッチ回路311及び312は不要で、クロック信号CLKに同期してラッチ回路313で映像信号DXをラッチすればよいので、クロックCK1、CK2、CK3は生成しなくてもよい。これによって、回路規模を低減することができる。クロック信号CLKからCLK\_P信号とCLK\_N信号を生成して正極駆動回路10と負極駆動回路20に入力すればよい。

## 【0062】

40

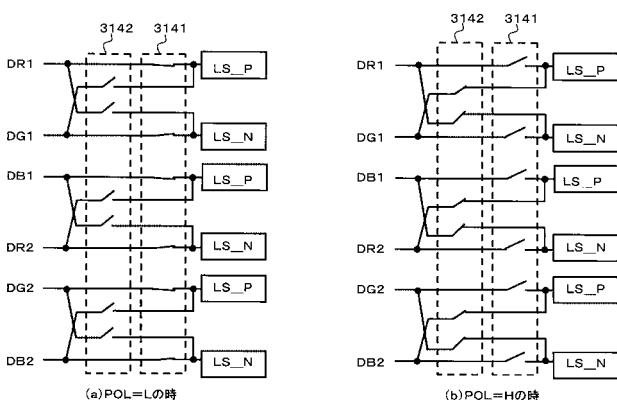

図15に示す回路は、映像信号切換回路314の詳細図で極性信号POLに対応したスイッチ状態を示す。図15(a)が極性信号POL=Lの時の状態を示し、図15(b)が極性信号POL=Hの時の状態を示している。映像信号切換回路314は、スイッチ3141とスイッチ3142を備えている。映像信号切換回路314は、映像信号DR1とDG1、DB1とDR2、DG2とDB2とをそれぞれ対として、極性信号POLのH、Lに応じてスイッチ3141、3142のオン、オフを切り換えることにより、正極レベルシフト回路321又は負極レベルシフト回路322への入力を切り換えている。図15において、極性信号POL=Lの時(図15(a))、スイッチ3141がONであり、スイッチ3142がOFFである(図13のX1ラインに相当)。極性信号POL=Hの時図15(b)、スイッチ3141がOFFであり、スイッチ3142がONである(図

50

13のX2ラインに相当)。

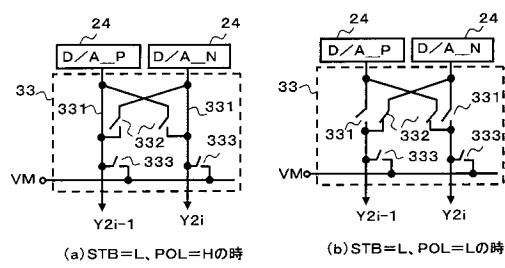

#### 【0063】

図16に示す回路は、DA変換回路14、24からの出力を切り換えてデータ線に出力する切換回路33の詳細図である。切換回路33は、スイッチ331、スイッチ332及びプリチャージスイッチ333を備えている。切換回路33は後述の高電圧素子で製造される。なお、正極駆動回路10及び負極駆動回路20などは、後述の中電圧素子で製造される。中電圧は液晶のしきい電圧と同等の電圧、高電圧は液晶のしきい電圧の2倍以上となるようとする。

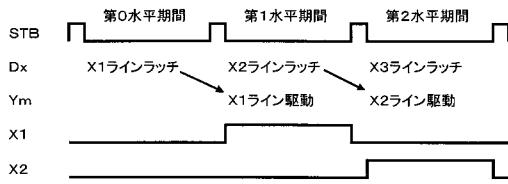

#### 【0064】

図17は、映像信号をデータレジスタ回路12、22にラッチするタイミングと、データ線を駆動するタイミングの関係を示すタイミングチャートである。図17に示すように、映像信号をデータレジスタ回路12、22にラッチするタイミングとデータ線を駆動するタイミングとは、1水平期間ずれるのが一般的である。つまり、第(k-1)水平期間で走査線Xkに相当する映像信号をデータレジスタ回路12、22にラッチして、第k水平期間で第(k-1)水平期間にラッチした映像信号をデータラッチ回路13、23でラッチし、その映像信号に応じた信号でデータ線を駆動する。

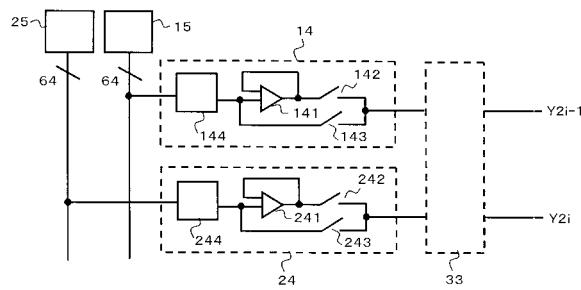

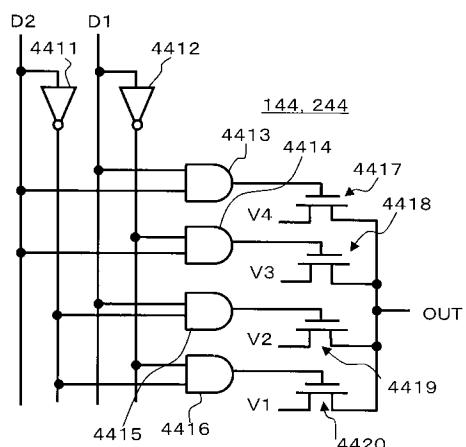

#### 【0065】

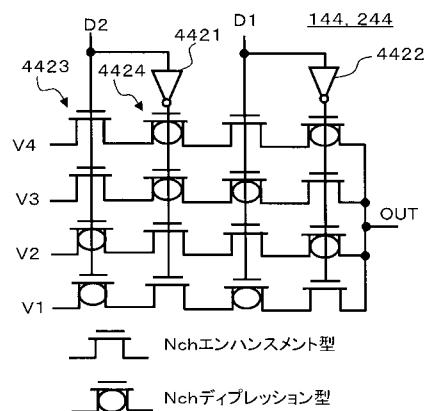

図18に、DA変換回路14、24の詳細図を示す。DA変換回路14、24は、デコーダ回路144、244と増幅器141、241とスイッチ142、143、242、243を含む回路で構成することができる。デコーダ回路144、244は、例えば図19に示すように構成することができる。図19では、論理回路と複数のスイッチで構成されており、映像信号DXを入力する入力端子とインバータ4411及びインバータ4412と論理回路4413、4414、4415、4416とNchトランジスタ4417、4418、4419、4420と出力端子とを有する。また、図20に示すように構成することもでき、図20によると映像信号DXを入力する入力端子とインバータ4421及びインバータ4422とNchエンハンスマント型4423とNchディプレッション型4424と出力端子とを有する。階調電圧を選択する複数のスイッチは、PchトランジスタとNchトランジスタを並列にしたトランスファスイッチで構成するが、説明を簡単にするためにNchトランジスタのみを図示している。尚、正極階調電圧生成回路15と、負極階調電圧生成回路25は、複数の抵抗を直列に接続した抵抗ストリング回路で構成し、ガンマ特性に合うように各抵抗値を設定して各接続点から所望の階調電圧(Vn)を得る。各階調電圧は、DA変換回路14、24に接続される。

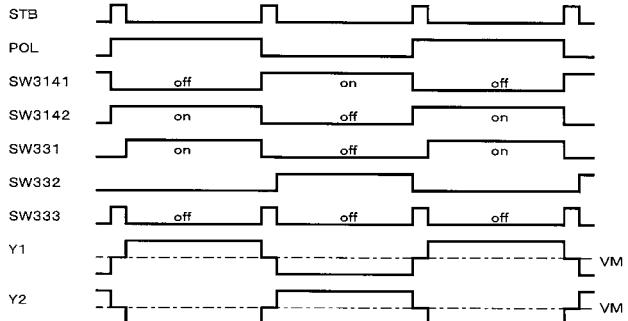

#### 【0066】

次に、図21のタイミングチャートと図15及び図16を用いて、各スイッチの動作について説明する。尚、説明の明確化のため、図13に示すようにデータ線が6本で走査線が2本の場合について説明する。また、Y1端子とデータ線R1、Y2端子とデータ線G1、Y3端子とデータ線B1、Y4端子とデータ線R2、Y5端子とデータ線G2、Y6端子とデータ線B2を接続して、各データ線(R1, G1, B1, R2, G2, B2)に対応する映像信号を(DR1, DG1, DB1, DR2, DG2, DB2)とする。そして、図13に示すように第1走査線X1での各画素の極性は(+, -, +, -, +, -)、第2走査線X2での各画素の極性は(-, +, -, +, -, +)となるようにドット反転駆動する場合を例に説明する。

#### 【0067】

まず、説明を簡単にするためにデータ線R1とG1を例に説明する。第(k-1)水平期間で極性信号POLが「L」の時、映像信号切換回路314は、図15(a)に示すスイッチ状態で、スイッチ3141がオン、スイッチ3142がオフしており、映像信号DR1は正極レベルシフト回路321を介して正極駆動回路10に入力され、正極データレジスタ回路12でラッチする。映像信号DG1は負極レベルシフト回路322を介して負極駆動回路20に入力され、負極データレジスタ回路22でラッチする。第k水平期間でラッチ信号STBが入力されるとデータレジスタ回路12、22でラッチした映像信号(

10

20

30

40

50

D R 1 , D G 1 ) はデータラッチ回路 1 3 、 2 3 でラッチする。この時、極性信号 P O L は「 L 」から「 H 」に切り換わる。正極 D A 変換回路 1 4 に映像信号 D R 1 に応じた正極信号が入力される。また同時に負極 D A 変換回路 2 4 に映像信号 D G 1 に応じた負極信号が入力される。極性信号 P O L が「 H 」の時は、切換回路 3 3 は、図 1 6 ( a ) に示すようにスイッチ 3 3 1 がオン、スイッチ 3 3 2 及び 3 3 3 がオフしており、映像信号 D R 1 に応じた正極信号をデータ線 R 1 に、映像信号 D G 1 に応じた負極信号をデータ線 G 1 にそれぞれ供給する。

#### 【 0 0 6 8 】

第 ( k - 1 ) 水平期間で極性信号 P O L が「 H 」の時は、映像信号切換回路 3 1 4 は、図 1 5 ( b ) に示すスイッチ状態で、スイッチ 3 1 4 2 がオン、スイッチ 3 1 4 1 がオフしており、映像信号 D R 1 は負極レベルシフト回路 3 2 2 を介して負極駆動回路 2 0 に入力され、負極データレジスタ回路 2 2 でラッチする。映像信号 D G 1 は正極レベルシフト回路 3 2 1 を介して正極駆動回路 1 0 に入力され、データレジスタ回路 1 2 でラッチする。第 k 水平期間でラッチ信号 S T B が入力されるとデータレジスタ回路 2 2 、 1 2 でラッチした映像信号 ( D R 1 , D G 1 ) はデータラッチ回路 2 3 、 1 3 でラッチする。この時、極性信号 P O L は「 H 」から「 L 」に切り換わる。負極 D A 変換回路 2 4 で映像信号 D R 1 に応じた負極信号を選択し、また同時に正極 D A 変換回路 1 4 で映像信号 D G 1 に応じた正極信号を選択する。P O L が「 L 」の時は、切換回路 3 3 は、図 1 6 ( b ) に示すようにスイッチ 3 3 2 がオン、スイッチ 3 3 1 及び 3 3 3 がオフしており、映像信号 D R 1 に応じた負極信号をデータ線 R 1 に、映像信号 D G 1 に応じた正極信号をデータ線 G 1 にそれぞれ供給する。

10 20

#### 【 0 0 6 9 】

前述の通りデータ線 R 1 と G 1 で説明したが、映像信号 D B 1 と D R 2 に応じた正極又は負極の信号がデータ線 B 1 とデータ線 R 2 、映像信号 D G 2 と D B 2 に応じた正極又は負極の信号がデータ線 G 2 とデータ線 B 2 に出力される。各信号処理動作は、上記 R 1 と G 1 について説明された動作と同様である。

#### 【 0 0 7 0 】

尚、ラッチ信号 S T B が「 H 」期間は、プリチャージスイッチ 3 3 3 をオン、スイッチ 3 3 1 及び 3 3 2 はオフして各出力端子を V M にショートする。V M は、V P H と V N L の中間電圧であるが、V P H と V N L の中間電圧が G N D であれば G N D にショートするのがよい。このように、各端子をショートして、D A 変換回路に耐圧以上の電圧が印加されないようにする。

30

#### 【 0 0 7 1 】

具体的には、第 ( k - 1 ) 水平期間でデータ線に正極信号が供給されていたとする、第 k 水平期間には負極 D A 変換回路 2 4 で負極信号を供給するが、データ線は正極の電圧を保持しているので、一瞬、耐圧以上の電圧が負極 D A 変換回路 2 4 に供給されることになる。このため、最も好ましくないケースにおいては、中電圧素子で構成した負極 D A 変換回路 2 4 を破壊することになる。そこで、負極 D A 変換回路 2 4 に耐圧以上の電圧が印加されないように、データ線を V M にプリチャージしてから負極 D A 変換回路 2 4 でデータ線を駆動する。正極 D A 変換回路も同様である。

40

#### 【 0 0 7 2 】

本形態においては、正極及び負極にレベルシフトした映像信号を正極駆動回路 1 0 及び負極駆動回路 2 0 に入力するので、従来のようにデータ線ごとに設けていたレベルシフト回路は不要である。信号処理回路 3 1 で生成した信号を正極駆動回路 1 0 及び負極駆動回路 2 0 に入力する前段でレベルシフトするレベルシフト回路の数は、各制御信号 × 2 個あり、少なくともクロック信号 C L K 1 個、スタート信号 S T H 1 個、映像信号 D × 3 6 個、ラッチ信号 S T B 1 個、極性信号 P O L 1 個などで、 $4 0 \times 2 = 8 0$  個であり、従来のデータ線駆動回路では、画素数を Q V G A ( 2 4 0 R G B × 3 2 0 ) とすると、レベルシフト回路はデータ線数と映像信号のビット数 n を掛け合せた数なので、 $2 4 0 \times 3 \times 6 = 4 3 2 0$  個必要であったが、本発明によれば、 $8 0 / 4 3 2 0 =$  約 1 / 5 4 まで低減す

50

ることができる。

【0073】

また、従来の切換回路64において、切換回路数がデータ線数×映像信号のビット数であったが、本発明において、映像信号切換回路314における切換回路数は映像信号のビット数になる。このため、切換回路数は1/データ線数に低減している。また、本発明では、画素数が変わってもレベルシフト回路数は変わらないので、画素数が大きくなればなるほどその効果は倍増する。

【0074】

本発明では、従来技術に比べてシフトレジスタ回路、データレジスタ回路及びデータラッチ回路部のトランジスタなどの素子が大きくなるため、この回路部の素子面積が大きくなるが、素子面積の大きいレベルシフト回路と切換回路Aを削減する効果の方がはるかに大きいためチップ面積を縮小することができる。

10

【0075】

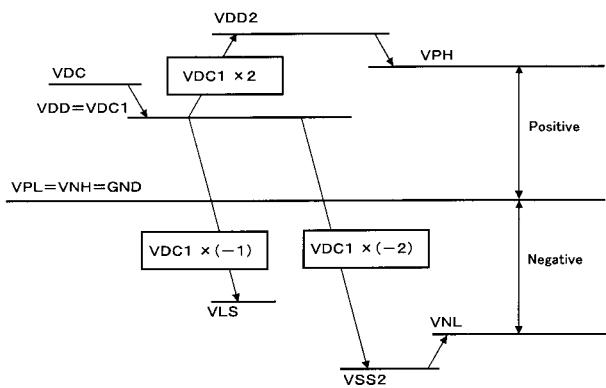

本形態において、com電圧を電源回路の低位電圧のGNDとしている。これによって、com電圧を生成する回路が不要となるため、電源回路8の回路規模を低減することができる。図31に電源電圧の相関図を示す。電源回路8では、供給されるVDCを基に、VDC1の電圧(2.5V)を生成し、昇圧回路で2×VDC1(VDD2)の電圧を生成して、VDD2からVPHを生成する。また、2×VDC1の電圧からダイオード、スイッチ及びコンデンサで反転させ、-2×VDC1(VSS2)を生成し、VSS2からVNLの電圧を生成する。従来は、2.5Vから5Vを生成し、5Vから10Vの電圧を生成する2段昇圧であったが、本発明ではcom電圧をGNDとした事により、2.5Vから5Vの電圧を生成する1段昇圧なので、電源効率は80%と従来の64%に比べ効率が良いため、消費電力が低減される。

20

【0076】

次に、本発明のデータ線駆動回路1を半導体製造装置で製造する例を説明する。本発明では、低電圧素子(2.5V)、中電圧素子(5V)、高電圧素子(10V)の拡散プロセスで製造する例を説明する。尚、上記()内の電圧は例であって、低電圧<中電圧<高電圧の関係であれば、これら以外の電圧でもよい。

【0077】

一般に、半導体回路におけるトランジスタなどのデバイス素子は、電圧が高いと素子面積が大きくなることが知られており、最小となるゲート長Lmin、ゲート幅Wmin、ゲート酸化膜厚Toxの関係は、Lmin(2.5V) < Lmin(5V) < Lmin(10V)、Wmin(2.5V) < Wmin(5V) < Wmin(10V)、Tox(2.5V) < Tox(5V) < Tox(10V)である。よって、高電圧素子をできるだけ使用しない回路構成にすることで、チップサイズを小さくすることができる。本形態においては、高電圧素子は切換回路33とレベルシフト回路32の一部においてのみ形成されており、チップサイズを小さくすることができる。

30

【0078】

本形態では、信号処理回路31は低電圧素子で製造し、正極駆動回路10及び負極駆動回路20は中電圧素子で製造し、切換回路33とレベルシフト回路32の一部を高電圧素子で製造する。液晶のしきい電圧が3Vと低い時は、信号処理回路31と正極駆動回路及び負極駆動回路を中電圧(3V)素子で製造し、切換回路33及びレベルシフト回路32の一部を高電圧(6V)素子で製造してもよい。

40

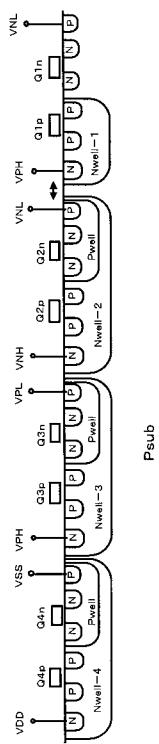

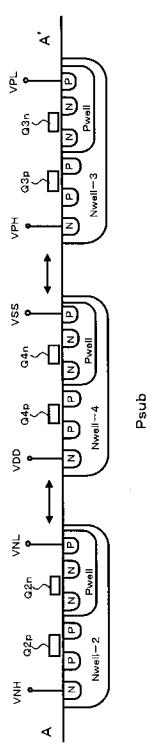

【0079】

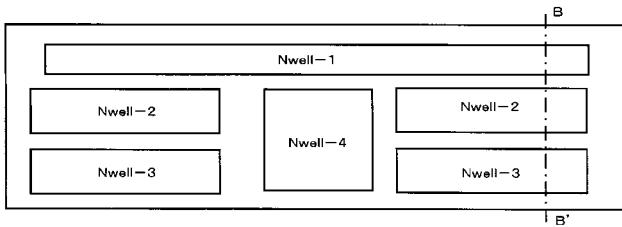

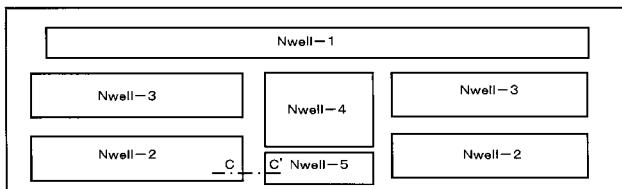

図22は半導体回路装置における基板及び基板上の素子の構成を示す断面図、図23は本形態のデータ線駆動回路をレイアウトした時の略図、図24は図23のA-A'での断面図である。高電圧基準で製造したN型トランジスタをQ1n、P型トランジスタをQ1p、中電圧基準で製造したNwell1-2上のN型トランジスタをQ2n、P型トランジスタをQ2pとし、Nwell1-3上のN型トランジスタをQ3n、P型トランジスタをQ3pとし、低電圧基準で製造したNwell1-4上のN型トランジスタをQ4n、P型

50

トランジスタをQ4pとする。

#### 【0080】

基板( Psub )の電圧は最低電圧  $V_{NL} = -5V$  として、信号処理回路31はNwell11-4上に、正極駆動回路10はNwell11-3上に、負極駆動回路20はNwell11-2上に製造し、切換回路33とレベルシフト回路32の一部はPsubとNwell11-1上に製造する。半導体回路装置においては、トランジスタ以外に抵抗や、コンデンサやダイオードなどのデバイス素子があるが、それらの素子も耐圧を確保する。

#### 【0081】

図25に示すように、( $V_{DD} = 2.5V$ ,  $V_{SS} = GND$ ,  $V_{PH} = 5V$ ,  $V_{PL} = GND$ ,  $V_{NH} = GND$ ,  $V_{NL} = -5V$ )といった電圧で動作する場合には、基板( Psub )は $-5V$ 、Nwell11-1が $V_{PH}$ 、Nwell11-2が $GND$ 、Nwell11-3が $V_{PH}$ 、Nwell11-4が $V_{DD}$ となる。

10

#### 【0082】

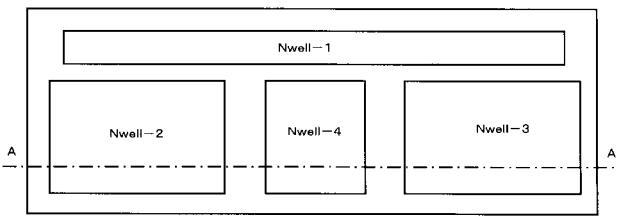

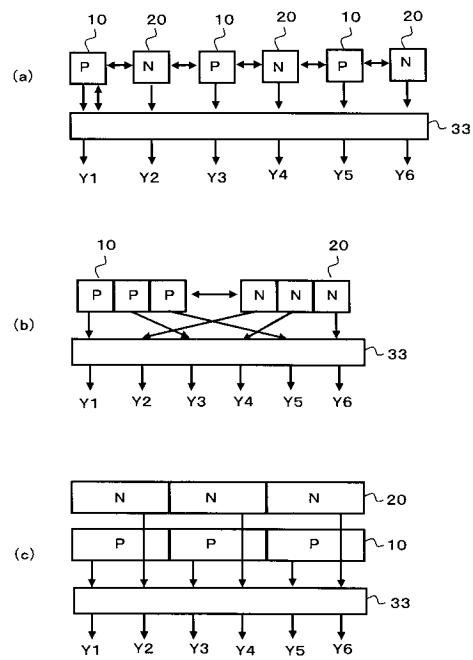

異電圧のNwell11間隔は数十 $\mu m$ 離す必要があり、図26(a)に示すように正極駆動回路10と負極駆動回路20を交互に配置するより、異なる連続領域に正極駆動回路10と負極駆動回路20を配置することによって、チップサイズを小さくすることができる。つまり、図26(b)又は図26(c)のように、第1の連続領域に正極駆動回路10を形成し、これと異なる第2の連続領域に負極駆動回路20をそれぞれ形成し、同電圧のNwell11をまとめて配置する。これによって、チップサイズを小さくすることができる。

20

#### 【0083】

図23では、図26(b)に相当する配置で、Y軸に平行な線に対して、正極駆動回路10(Nwell11-3)と負極駆動回路20(Nwell11-2)を左右に配置している。図27では、X軸に平行な線に対して正極駆動回路10(Nwell11-3)と負極駆動回路20(Nwell11-2)を上下に配置している。図28に図27のB-B'での断面図を示す。いうまでもないが、正極駆動回路10と負極駆動回路20は、図23に示すような左右を反対にして左右に配置してもよいし、図27に示すような上下を反対にして上下に配置してもよい。尚、基板をNsub(N型基板)としてもよい。その場合、Nsubは、 $V_{PH}$ など最高電圧にされる。

#### 【0084】

実施の形態2.

実施の形態1では、信号処理回路31で生成した信号を、レベルシフト回路32を介して正極駆動回路10及び負極駆動回路20に入力するが、入力する信号はレベルシフトした電圧なので、映像信号バスでの消費電力が増加する。しかし、図29に示すように映像信号切換回路314とレベルシフト回路32との間にデータ反転回路315を設けることで映像信号バスの消費電力を抑制することができる。

#### 【0085】

データ反転回路315は、映像信号ごとに前データと次データをラッチして比較する回路と、比較した結果に応じて映像信号を反転する回路と、映像反転信号INVを生成する回路を含む。データ反転回路315は、前データとその次のデータを比較し、多数決論理により過半数より多くのビットが反転(不一致)している時に映像反転信号INVを0にして、反転ビットが過半数以下の時は、映像反転信号INVを1にする。また、本形態において、データレジスタ回路12、22の初段の回路を排他的論理和回路にする。

40

#### 【0086】

例えば映像信号が6ビットである場合において、前データが000011、次データが111111であれば、6ビット中4ビットの映像信号が反転しているので、4ビットの信号を反転させて111111にするよりも、2ビットを反転させて000000にする方が電力消費を抑えられる。よって、映像反転信号INVを0にして、正極レベルシフト回路321又は負極レベルシフト回路322に入力する映像信号を000000に反転して正極データレジスタ回路12又は負極データレジスタ回路22に入力する。更に正極デ

50

ー タレジスタ回路 12 又は負極データレジスタ回路 22 で、映像反転信号 INV に応じて画映像信号を 111111 に反転してラッチする。

#### 【 0087 】

前データが 000011、次データが 110011 であれば、6 ビット中 2 ビットの映像信号しか反転していないので、上記とは逆となる。映像反転信号 INV を 1 にして、正極レベルシフト回路 321 又は負極レベルシフト回路 322 に入力する映像信号を 110011 のまま入力する。正極データレジスタ回路 12 又は負極データレジスタ回路 22 で映像信号を、映像反転信号 INV に応じて 110011 としてラッチする。

#### 【 0088 】

消費電力は  $c \cdot v^2 \cdot f$  ( $c$  : 容量、 $v$  : 電圧幅、 $f$  : 周波数) である。データレジスタ回路が低電圧素子から中電圧素子になることで容量  $c$  は約 2 倍になり、また、電圧幅  $v$  も 2.5 V から 5 V の 2 倍になるので、消費電力は最大で 8 倍になるが、データ反転回路 315 により 6 ビット中の 3 ビットが反転した時に最大で 4 倍に低減される。全白、全黒など全画面同色では映像信号が変化しないので消費電力は 0 で、1 画素市松模様では映像反転信号 INV だけが反転するので消費電力は  $8 / 6 = 1.3$  倍程度である。文字情報では、白地に黒文字が多いので、最大でも 1.3 倍程度の増加で済む。しかも、液晶表示装置全体からみればデータ線 4 及び走査線 5 を駆動する消費電力とデータ線駆動回路の DA 変換回路での消費電力がほとんどで、映像信号バスでの消費電力は、全体の消費電力からみて最大でも 10 % 未満である。このため、映像信号バスの消費電力が 1.3 倍になったとしても装置全体からみれば 3 % 未満の増加にすぎない。 $com$  電圧を GND とすることでも、駆動系の電源回路の効率が 64 % から 80 % まで改善するので、相殺しても低消費電力になる。

#### 【 0089 】

##### 実施の形態 3 .

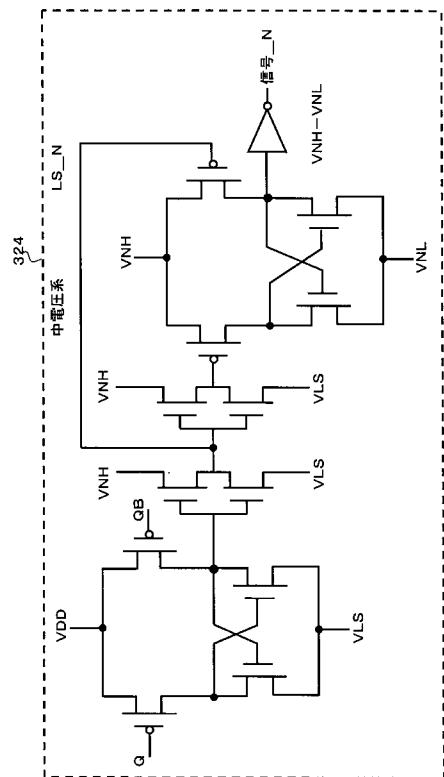

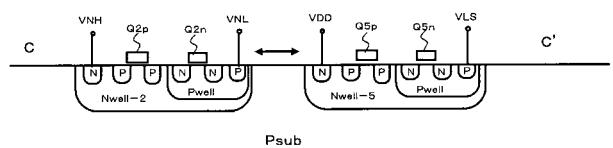

図 30 に、実施の形態 1 で説明した負極レベルシフト回路 322 とは別の負極レベルシフト回路を示す。負極レベルシフト回路 322 は、高電圧素子で製造するが、負極レベルシフト回路 324 は、2 段目の Pch トランジスタ以外は中電圧素子で製造する。負極レベルシフト回路 322 と 324 の違いは、1 段目のレベルシフト回路の低位電圧が、VLS (-1 × VDC1) (図 31 参照) で、1 段目の出力は、2 段目のレベルシフト回路の Pch トランジスタに入力する点が異なる。また、1 段目のレベルシフト回路と 2 段目のレベルシフト回路との間に図 32 に示すように VLS - GND の電圧で動作するインバータを挿入すれば、レベルシフト回路を構成する素子はすべて中電圧素子で製造できる。

#### 【 0090 】

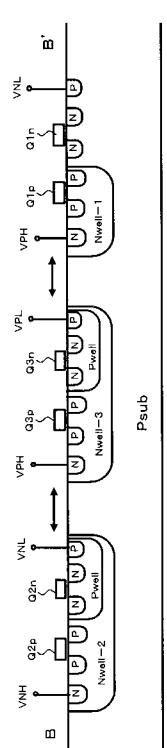

この回路によれば、1 段目のレベルシフト回路と 2 段目のレベルシフト回路は別の Nwe11 上に製造する。図 33 に本実施の形態の Nwe11 配置図、図 34 に図 33 の C-C' での断面図を示す。図 34 に示すように、1 段目のレベルシフト回路は Nwe11-5 上に、2 段目のレベルシフト回路は負極駆動回路 20 と同じ Nwe11-2 上に製造する。本形態によれば、負極レベルシフト回路を中電圧素子で製造するので、高電圧素子で形成する場合に比較して、素子面積を低減することができる。

#### 【 0091 】

##### 実施の形態 4 .

実施の形態 1 乃至 3 においては、切換回路であるスイッチ 331 とスイッチ 332 の後にプリチャージスイッチ 333 を設けていた。従って一つのプリチャージスイッチ 333 で正極、負極の両方の電圧に対応する必要があり、そのためにはプリチャージスイッチ 333 も高電圧素子である必要があった。本実施形態においては、正極駆動回路と切換回路、負極駆動回路と切換回路との間に、それぞれに正極プリチャージスイッチと負極プリチャージスイッチを用意することによって、プリチャージスイッチを中電圧素子で製造することを可能とし、更に回路規模を低減する例を説明する。本実施の形態においては、実施の形態 1 において図 15、図 16 及び図 21 を用いて説明した箇所について変更点があるものであり、同様の符号を付すものについては説明を省略する。

10

20

30

40

50

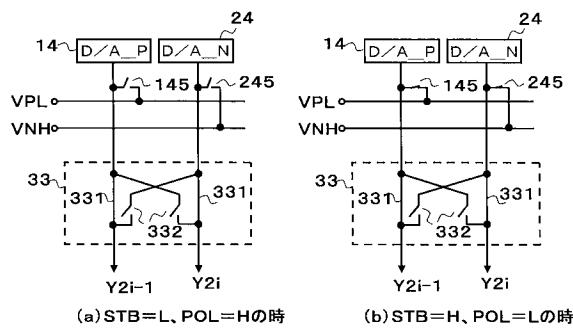

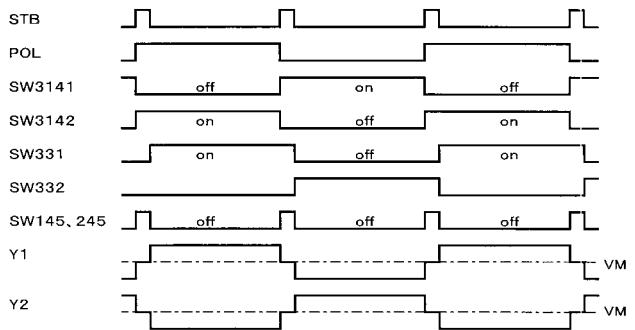

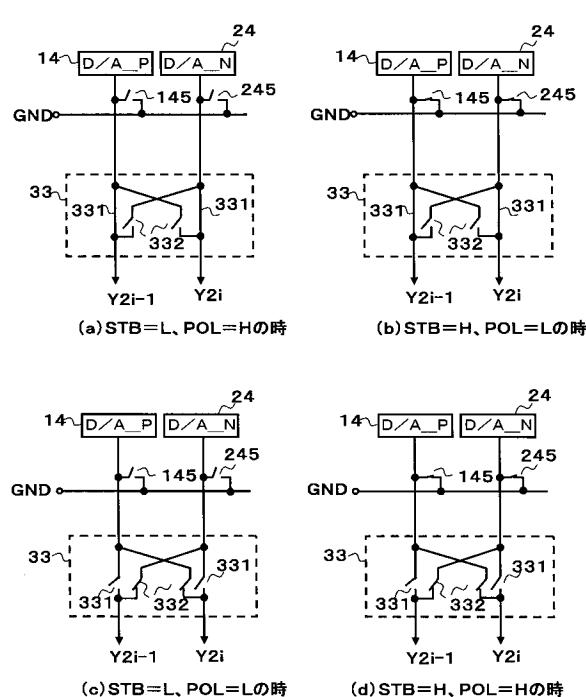

## 【0092】

図35は本実施形態にかかるプリチャージスイッチ(145、245)及び切換回路33のスイッチ切換動作を説明する図である。図35(a)から図35(d)は、時間経過に伴うスイッチの接続状態の順次変化を表している。切換回路33内のスイッチ331及びスイッチ332の機能については図16を参照して説明した例と同様である。プリチャージスイッチ145及びプリチャージスイッチ245は、実施の形態1におけるプリチャージスイッチ333に替わって用いられるものである。すなわち、プリチャージスイッチ145及びプリチャージスイッチ245はそれぞれ所定電圧と接続されており、データ線を所定電圧に接続することによって所定電圧にプリチャージし、正極DA変換回路14、負極DA変換回路24に耐圧以上の電圧が印加されることを防ぐものである。図によると、正極DA変換回路14にはプリチャージスイッチ145が、負極DA変換回路24にはプリチャージスイッチ245がそれぞれ接続されている。更にプリチャージスイッチ145はVPL電圧に接続されており、プリチャージスイッチ245はVNH電圧に接続されている。

10

## 【0093】

次に図35(a)から図35(d)のそれぞれの状態を、図36を用いながら説明する。図36のタイミングチャートは実施の形態1での図21に対応するものであり、プリチャージスイッチ333に代わりプリチャージスイッチ145及びプリチャージスイッチ245のタイミングが示されている。図35(a)はラッチ信号STBがL、極性信号POLがHのタイミングにおけるスイッチ状態を示しており、奇数番目の出力端子Y<sub>2i-1</sub>からは正極の映像信号が、偶数番目の出力端子Y<sub>2i</sub>からは負極の映像信号がそれぞれ出力されている。図35(b)ではラッチ信号STBがHに、極性信号POLがLに変化したときの接続状態を示している。プリチャージスイッチ145及びプリチャージスイッチ245がオンになり、出力端子Y<sub>2i-1</sub>、Y<sub>2i</sub>をそれぞれVPL電圧、VNH電圧にプリチャージする。

20

## 【0094】

図35(c)はラッチ信号STBがLになった状態を示している。プリチャージスイッチ145及びプリチャージスイッチ245がオフとなり、更にスイッチ331とスイッチ332のオン、オフがそれぞれ切り換わることによって、奇数番目の出力端子Y<sub>2i-1</sub>から負極映像信号を、偶数番目の出力端子Y<sub>2i</sub>からは正極映像信号をそれぞれ出力する。図35(d)は更に次のタイミングでラッチ信号STB、極性信号POLが共にHのタイミングの状態を示している。プリチャージスイッチ145及びプリチャージスイッチ245がオンになり、出力端子(Y<sub>2i-1</sub>、Y<sub>2i</sub>)は、それぞれVNH電圧、VPL電圧にプリチャージされる。次のタイミングではラッチ信号STBがLとなり、図35(a)の状態に戻る。

30

## 【0095】

前述のように、スイッチ331及びスイッチ332をオフとする前に、プリチャージスイッチ145及びプリチャージスイッチ245をオンとすることによって、DA変換回路14及びDA変換回路24の出力端子(データ線)に印加されている電圧をVPL又はVNHにそれぞれショートする(プリチャージする)際に、DA変換回路14及びDA変換回路24に耐圧以上の電圧が印加されないように制御する。プリチャージスイッチ145及びプリチャージスイッチ245はそれぞれ正極又は負極の電圧にそれぞれ対応すればよいので、高電圧素子ではなく中電圧素子で製造することができ、回路規模を低減することができる。尚、VPL、VNHをシステムグランドGNDとすることも可能である。その場合における回路及びスイッチ切換動作を説明する詳細図を図37に示す。動作については図35と同様であるため説明を省略する。

40

## 【0096】

実施の形態5.

実施の形態1乃至4においては、シリアルに入力されたデジタル映像信号をデータレジスタ回路及びデータラッピング回路でパラレルにデジタル映像信号として展開し保持していた

50

。本実施形態においては、シリアルに入力されたデジタル映像信号をアナログ映像信号に変換し、そのアナログ映像信号をサンプルホールド回路に展開し保持することによってデータ線を駆動する例を説明する。このような構成とすることによって、nビットのデジタル映像信号の場合n本必要だったデータ線数をアナログのデータ線1本にすることができるため、データ線数を低減し、以って回路規模を低減することができる。

#### 【0097】

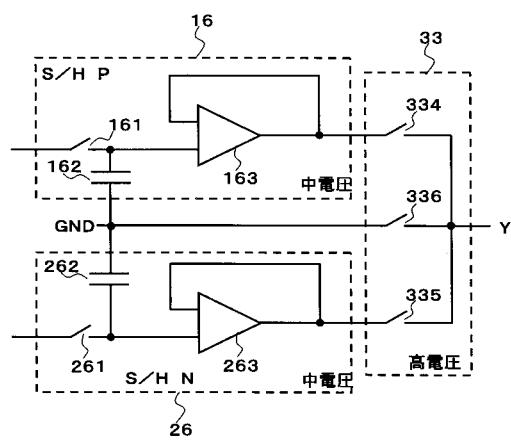

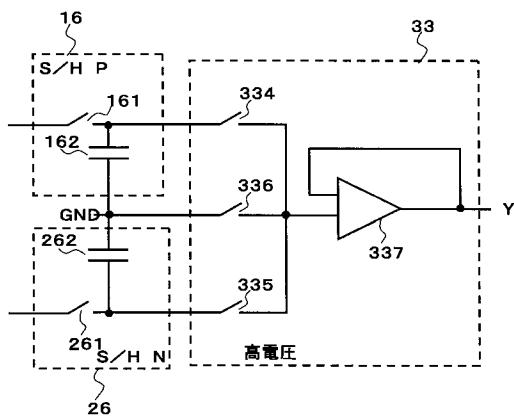

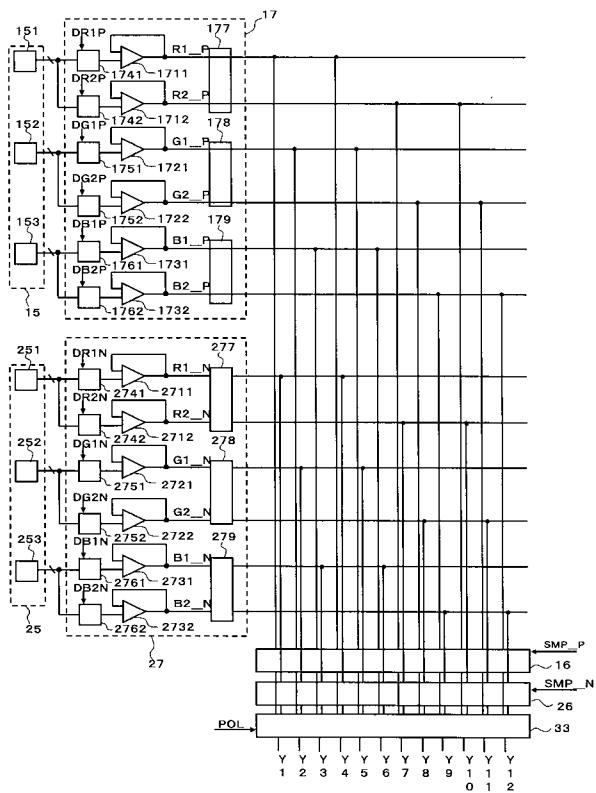

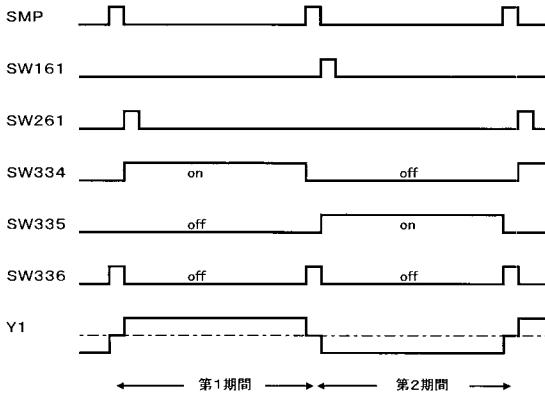

図38は本実施形態にかかる液晶表示装置のデータ線駆動回路装置を表すブロック図である。実施の形態1乃至4におけるデータレジスタ回路12、22、データラッチ回路13、23に代わり、サンプルホールド回路16、26が設けられている。またDA変換回路14、24に代わり、DA変換回路17、27がレベルシフト回路32とサンプルホールド回路16、26との間に設けられている。また、DA変換回路17、27には階調電圧生成回路15、25が接続されている。レベルシフト回路32で正極又は負極にシフトされたシリアルのデジタル映像信号はDA変換回路17、27においてアナログ映像信号に変換され、サンプルホールド回路16、26でクロックに従って順次サンプリングされる。このように、シリアルに入力されたデジタル映像信号がアナログ映像信号に変換され、そのアナログ映像信号がサンプルホールド回路に展開されて保持される。この時、シフトレジスタ回路11、21から出力されるSMP信号によって正極サンプルホールド回路16でサンプリングされるか、負極サンプルホールド回路26でサンプリングされるかが決定される。その後、切換回路33によって正負の切り換えが行なわれ出力される。

#### 【0098】

図39は一つのデータ線(画素)に対応するサンプルホールド回路16、26及び切換回路33の詳細を示した図である。一つのデータ線に対して、正極と負極用の2個のサンプルホールド回路16、26が接続されている。各サンプルホールド回路16、26において、スイッチ161とスイッチ334の間に正極増幅器(ボルテージフォロア)163が、スイッチ261とスイッチ335の間には負極増幅器(ボルテージフォロア)263が設けられている。スイッチ161とGNDの間には正極のアナログ映像信号を蓄積(サンプリング)する容量162が、スイッチ261とGNDの間には負極のアナログ映像信号を蓄積(サンプリング)する容量262が接続されている。

#### 【0099】

スイッチ161、261、容量162、26及び増幅器163、263は中電圧素子で製造されている。スイッチ161、261はシフトレジスタ回路11、21から入力されるサンプリング信号SMPによって切り換えられる。また、切換回路33を構成しているスイッチ334、335、336は高電圧素子で製造する。スイッチ334は正極のアナログ映像信号を、スイッチ335は負極のアナログ映像信号を出力し、スイッチ336は正極増幅器163及び負極増幅器263に動作電圧以上の電圧が印加されないようにGNDにブリッヂする。切換回路33は、実施の形態1乃至4においては、2個の出力端子で共用して正極及び負極のアナログ映像信号を選択していたが、本実施形態においては出力端子ごとにスイッチ334、335、336を設ける。

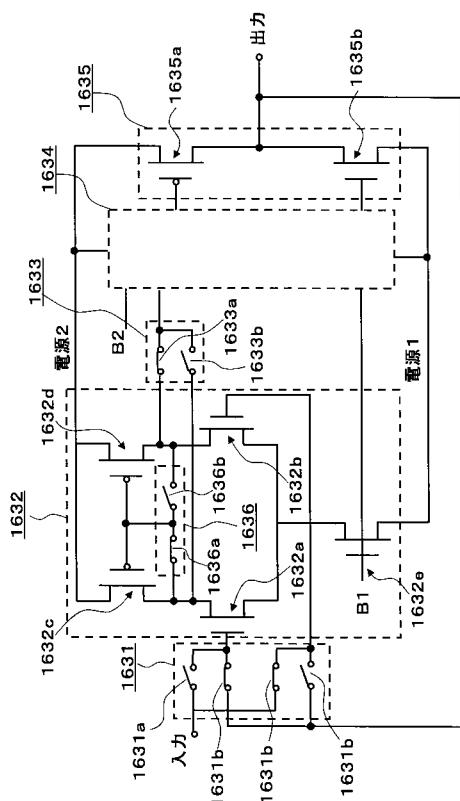

#### 【0100】

このように、1個の出力端子に2個の増幅器(ボルテージフォロア)163、263を接続する構成の場合、増幅器のオフセット電圧ばらつきあり、薄い縦線が表示される等の問題がある。このため、増幅器のオフセット電圧をフレーム間でキャンセルする必要がある。従って、図40に示すような差動入力(反転入力、非反転入力)を入れ換える切換回路を、増幅器163、263に設けるのがよい。図40は、差動入力を入れ換える切換回路を備える増幅器の構成例を示している。増幅器は、入力切換回路1631、差動増幅段1632、差動増幅段の出力切換回路1633、ソース接地回路などを含む中段の回路1634及びPMOSトランジスタ1635a、bから構成される出力段1635を備えている。B1及びB2はバイアス電圧を示している。差動増幅段1632は、NMOSトランジスタ1632a、bから構成される差動対、PMOSトランジスタ1632c、dから構成されるカレントミラー回路、差動対のテール側に接続されたNMOSトランジスタ

10

20

30

40

50

1632を備える。さらに、カレントミラー回路のゲート接続を切り換える切換回路1636を備えている。

#### 【0101】

入力切換回路1631は4つのスイッチ1631a～dを備え、差動増幅段1632への入力信号と出力からのフィードバックを、それぞれ、差動対の一方のトランジスタに接続する。図において、スイッチ1631b、dがON、スイッチ1631a、cがOFFであり、入力信号がNMOSトランジスタ1632bに入力し、出力がNMOSトランジスタ1632aにフィードバックされている。切換回路1636のスイッチ1636aがON、スイッチ1636bがOFF、出力切換回路1633のスイッチ1633aがON、スイッチ1633bがOFFであり、NMOSトランジスタの。入力切換回路1631を切り換えて差動入力を入れ換える場合、出力切換回路1633及び切換回路1636の全てのスイッチを切り換える。このように、差動入力を入れ換ることによって、増幅器のオフセット電圧のばらつきを防止することができる。

#### 【0102】

図41は図39とは別のサンプルホールド回路16、26及び切換回路33の詳細を示す図である。サンプルホールド回路16、26は、それぞれ、増幅器163、263を備えておらず、切換回路33が一つの増幅器337を備えている。スイッチ161とスイッチ334並びにスイッチ261とスイッチ335とを増幅器を介さずに直接接続し、スイッチ334、335、336の他端（出力側）に高電圧素子で製造する増幅器337を接続している。このように、1個の出力端子に1個の増幅器（ボルテージフォロア）を接続する構成の場合、正極電圧出力時のオフセット電圧甲と負極電圧出力時のオフセット電圧乙は、通常甲=乙なので正極、負極で交流駆動することでオフセット電圧はキャンセルされるため、切換回路の必要は無い。ただし、増幅器337の入力部の寄生容量と容量162、262とで電荷の分配があるので、ゲインは1より小さくなり、ゲインばらつきを生じるので増幅器337の入力部の寄生容量はできるだけ小さくするのが好ましい。

#### 【0103】

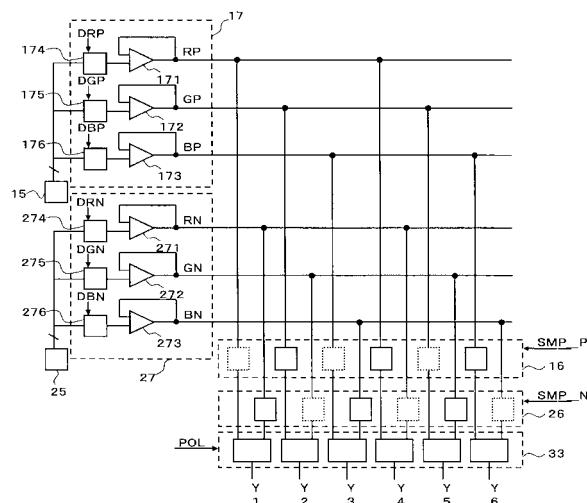

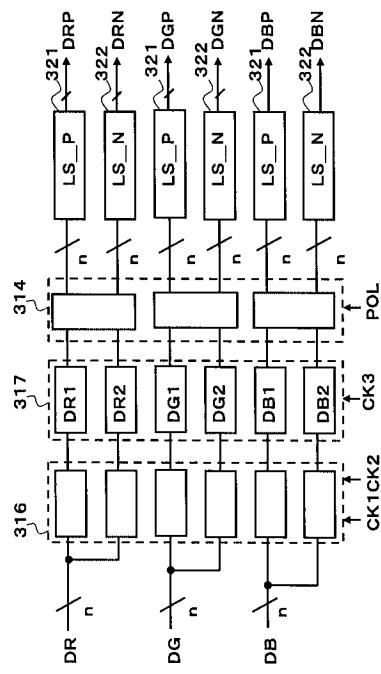

正極DA変換回路17と負極DA変換回路27は、図42に示すように、階調電圧生成回路15、25との接続によって、シリアルのデジタル映像信号に応じた階調電圧を選択して、ボルテージフォロアで高速にサンプルホールド回路16、26につながるデータ線を駆動する。ここで、信号処理回路31及びレベルシフト回路32は実施の形態1乃至4と同様であるので詳細な説明を省略するが、図43にその構成、及び出力される信号を示している。図43において、316及び317はラッチ回路である。ラッチ回路316はRGBの各映像信号に対応して2つのラッチ要素を備えており、CK1及びCK2信号に従って一方のラッチ要素が入力映像信号を選択的にラッチする。つまり、1画素目の映像信号を一方のラッチ要素がラッチし、2画素目の映像信号をもう一方のラッチ要素がラッチする。

#### 【0104】

ラッチ回路317はラッチ回路316の各ラッチ要素に対応したラッチ要素を備えており、ラッチ回路316からの出力は、CK3に従ってラッチ回路317がラッチする。ラッチ回路317は、1画素目の映像信号（DR1、DG1、DB1）と2画素目の映像信号（DR2、DG2、DB2）を同時にラッチする。他の構成要素は既に説明したものと同様である。本発明にかかるデータ線駆動回路装置はドット反転方式であるため、隣り合う出力端子の極性は反転している。レベルシフト回路32及びシフトレジスタ回路11、21からサンプルホールド回路16、26に入力されるサンプリング信号SMPによってそれが可能となっている。図38及び図42に示すように、正極シフトレジスタ回路11からは正極サンプリング信号SMP\_Pが正極サンプルホールド回路16へ入力されており、負極シフトレジスタ回路21からは負極サンプリング信号SMP\_Nが負極サンプルホールド回路26へ入力されている。

#### 【0105】

図42において、サンプルホールド回路16、26内部は夫々のデータ線に対応するサ

10

20

30

40

50

ンプルホールド回路が点線又は実線の四角によって描かれている。この点線と実線の違いは、サンプリング信号 SMP に対する反応の違いである。例えば、サンプリング信号 SMP が「H」の時は点線で描かれたサンプルホールド回路のみがサンプリングを行い、サンプリング信号 SMP が「L」の時は実線で描かれたサンプルホールド回路のみがサンプリングを行なう。この SMP 信号に対する動作は逆でも良い。サンプリング信号 SMP をクロックに同期して切り換えることによってドット反転が実現される。すなわち図 4 2 の例であれば、SMP 信号が「H」の場合は点線で描かれたサンプルホールド回路がサンプリングを行なうため、Y1、Y3、Y5 の出力端子には正極サンプルホールド回路 16 でサンプリングされた信号が出力され、Y2、Y4、Y6 の出力端子には負極サンプルホールド回路 26 でサンプリングされた信号が出力される。

10

### 【0106】

図 4 2 の例においては、正極 DA 変換回路 17 と負極 DA 変換回路 27 は、それぞれ、3 個の正極増幅器 171、172、173 (RGB ごと) と 3 個の負極増幅器 271、272、273 (RGB ごと) を備えている。また、正極 DA 変換回路 17 は、各増幅器 171、172、173 のそれぞれに対応して、デコーダ 174、175、176 を備えている。同様に、負極 DA 変換回路 27 は、各増幅器 271、272、273 のそれぞれに対応して、デコーダ 274、275、276 を備えている QVGA 画素 (240RGB × 320) では、フレーム周波数 60 Hz でプランギング期間を除くと 1 水平期間は約 50 μsec であるので、 $50 \mu\text{sec} / 120 = 416 \text{nsec}$  で駆動する。尚、階調電圧生成回路 15、25 のそれぞれが、図 4 4 に示すように、RGB ごとに独立した階調電圧生成回路要素を備えている場合、回路規模は増大するが高画質化することが可能となる。図 4 4 においては、正極の階調電圧生成回路 15 は、RGB にそれぞれ対応して、階調電圧生成回路要素 151、152、153 を備えている。同様に、負極の階調電圧生成回路 25 は、RGB にそれぞれ対応して、階調電圧生成回路要素 251、252、253 を備えている。

20

### 【0107】

画素数が多い場合、図 4 5 に示すように DA 変換回路要素の数を増やすことが好ましい。図 4 5 において、正極 DA 変換回路 17 及び負極 DA 変換回路 27 のそれぞれは、RGB にそれぞれ対応して、各 2 つの DA 変換回路要素を備えている。具体的構成について説明する。正極 DA 変換回路 17 は、R に対応して増幅器 1711 及びそれに対応するデコーダ 1741 と、増幅器 1712 及びそれに対応するデコーダ 1742 を備えている。増幅器 1711 と増幅器 1712 の出力は、切換回路 177 によって選択的に外部に出力される。図において、増幅器 1711、1712 の各出力は異なる配線に出力され、増幅器 1711 の出力 R1\_P は上側の配線 (Y1、Y4 との接続配線) に、増幅器 1712 の出力 R2\_P は下側の配線 (Y7、Y10 との接続配線) に出力される。また、G に対応して増幅器 1721 及びそれに対応するデコーダ 1751 と、増幅器 1722 及びそれに対応するデコーダ 1752 を備えている。増幅器 1721 と増幅器 1722 の出力は、切換回路 178 によって選択的に外部に出力される。増幅器 1721 の出力 G1\_P は上側の配線 (Y2、Y5 との接続配線) に、増幅器 1722 の出力 G2\_P は下側の配線 (Y8、Y11 との接続配線) に出力される。さらに、B に対応して増幅器 1731 及びデコーダ 1761 と、増幅器 1732 及びデコーダ 1762 を備えている。増幅器 1731 と増幅器 1732 の出力は、切換回路 179 によって選択的に外部に出力される。増幅器 1731 の出力 B1\_P は上側の配線 (Y3、Y6 との接続配線) に、増幅器 1732 の出力 B2\_P は下側の配線 (Y9、Y12 との接続配線) に出力される。

30

40

### 【0108】

負極 DA 変換回路 27 も同様に、RGB にそれぞれ対応して、各 2 つの DA 変換回路要素を備えている。具体的には、R に対応して増幅器 2711 及びデコーダ 2741 と、増幅器 2722 及びデコーダ 2742 を備えている。増幅器 2711 と増幅器 2712 の出力は、切換回路 277 によって選択的に外部に出力される。また、G に対応して増幅器 2721 及びデコーダ 2751 と、増幅器 2722 及びデコーダ 2752 を備えている。増幅器 2731 及びデコーダ 2761 と、増幅器 2732 及びデコーダ 2762 を備えている。増幅器 2731 と増幅器 2732 の出力は、切換回路 279 によって選択的に外部に出力される。増幅器 2731 の出力 B1\_P は上側の配線 (Y3、Y6 との接続配線) に、増幅器 2732 の出力 B2\_P は下側の配線 (Y9、Y12 との接続配線) に出力される。

50

幅器 2721 と增幅器 2722 の出力は、切換回路 278 によって選択的に外部に出力される。さらに、B に対応して增幅器 2731 及びデコーダ 2761 と、增幅器 2732 及びデコーダ 2762 を備えている。增幅器 2731 と增幅器 2732 の出力は、切換回路 279 によって選択的に外部に出力される。各增幅器と出力配線との接続関係は、DA 変換回路 17 と同様の規則に従っている。

#### 【0109】

例えば、X1 ラインに信号を出力する場合において、(Y1、Y2、Y3、Y4、Y5、Y6、Y7、Y8、Y9、Y10、Y11、Y12) には、それぞれ、(R1\_P、G1\_N、B1\_P、R1\_N、G1\_P、B1\_N、R2\_P、G2\_N、B2\_P、R2\_N、G2\_P、B2\_N) の信号が出力される。ライン毎あるいはフレーム毎に極性を反転させる場合は、各端子の出力極性の P、N が切り換わる。つまり、(Y1、Y2、Y3、Y4、Y5、Y6、Y7、Y8、Y9、Y10、Y11、Y12) には、それぞれ、(R1\_N、G1\_P、B1\_N、R1\_P、G1\_N、B1\_P、R2\_N、G2\_P、B2\_N、R2\_P、G2\_N、B2\_P) の信号が出力される。各配線への出力の切り換えは、各切換回路によって決定される。このように、一つのラインにおいて、同一極同一色の 2 つの DA 変換回路要素が、交互に信号を出力する。同一色かつ同一極性の複数の DA 変換回路要素を用意し、各 DA 変換回路要素が同一ラインで交互に信号を出力するように切換回路を設けることによって、増幅器のオフセット電圧を時間的に分散して表示むらの発生を抑制することができる。尚、同一極同一色のそれぞれについて、3 以上の DA 変換回路要素を備えることも可能である。この場合も、各 DA 変換回路要素が順番に(巡回的に)信号を出力する。尚、この時、各増幅器において、図 40 に示すように差動入力(反転入力、非反転入力)を入れ換えてよい。

#### 【0110】

図 46 にタイミングチャートを示し、出力 Y1 を例に詳細に動作を説明する。図 46 は、出力 Y1 及び出力 Y2 を制御する各スイッチの動作タイミングを示している。前述の通り、ドット反転駆動では隣り合うデータ線ごとに極性が異なるため、2n 番目と(2n-1) 番目のサンプリングスイッチ 161、261 は、それぞれ異なるタイミングでオンしてアナログ映像信号をサンプリングする。このスイッチ 161、261 の切り換えは前述の通りサンプリング信号 SMP によって行なわれる。以下では、例として出力 Y1 について図 46 を参照して説明する。また、あわせて出力 Y2 についても言及する。尚、図 46 において示された符号は、SMP はサンプリング信号、SW161-336 はそれぞれスイッチ 161-336、Y1 は出力 Y1 を示している。

#### 【0111】

図 46 の第 1 期間において、X1 ラインとして Y1 から正極のアナログ映像信号、Y2 から負極のアナログ映像信号がそれぞれ出力されている場合、図 39 又は図 41 を見てもわかるとおり、図 46 に示すように切換回路 33 のスイッチは Y1 では 334 がオンとなる。一方、Y2 では 335 がオンとなっている。この時、サンプルホールド回路 16、26 では X2 ラインとして出力されるアナログ映像信号のサンプリングが行なわれている。すなわち、Y1 側では、図 46 に示すように、スイッチ 261 がオンとなって負極のアナログ映像信号をサンプルホールドする。一方、Y2 側ではスイッチ 161 がオンとなって正極のアナログ映像信号をサンプルホールドしている。第 1 期間から第 2 期間に切り換わる際に、Y1、Y2 共にスイッチ 334、335 をオフしてスイッチ 336 をオンにし、データ線を GND レベルにプリチャージする。

#### 【0112】

サンプリング信号 SMP に応じて第 1 期間から第 2 期間へ切り換わる。スイッチ 336 によるプリチャージに関しても、サンプリング信号 SMP に同期させても良い。第 2 期間に切り換わると、図 46 に示すように、Y1 ではスイッチ 335 がオンになり、第 1 期間においてサンプリングした負極のアナログ映像信号を出力する。また、スイッチ 161 がオンになり、正極のアナログ映像信号をサンプリングする。Y2 では正負逆の動作が行なわれる。上記の動作を SMP に同期して繰り返すことによって、ドット反転駆動が実現さ

れる。

### 【0113】

また、プリチャージする電圧はシステムグランド GND としたが、システムグランド GND ではなく正極駆動回路の低位電圧 VPL や負極駆動回路の高位電圧 VNH でもよい。本実施形態においては  $VPL = VNH = GND$  としている。このような構成により、n ビットのデジタル映像信号ではなくアナログ映像信号を用いることが可能となる。n ビットのデジタル映像信号のデータ線（データバス）の本数は n 本になるが、DA 変換してしまえば 1 本のアナログ映像信号になるため、このデータ線を駆動する DA 変換回路の消費電力はデジタル映像信号を処理するのに比べ  $1/n$  になる。また、データ線数が減るため、回路規模の低減を図ることもできる。

10

### 【0114】

以上説明したように本実施の形態によれば回路規模及び消費電力を更に低減した液晶表示装置のデータ線駆動回路装置を提供することができる。

### 【0115】

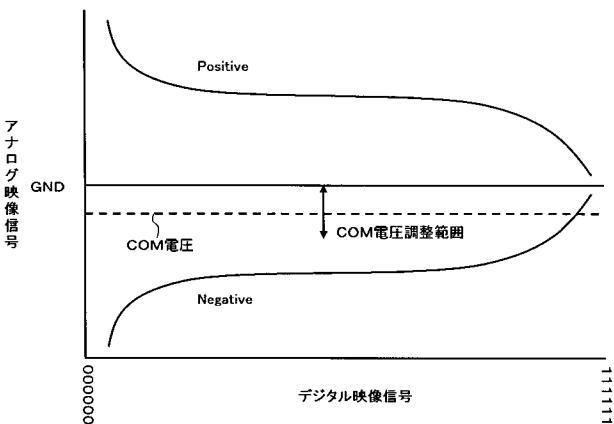

実施の形態 6.

本実施の形態においては、TFT 素子で発生するフィードスルーメーカー誤差を考慮し、意図的に com 電圧を GND とは異なる値に設定する例を説明する。フィードスルーメーカー誤差とは、ゲート電極の寄生容量によって生じ、TFT 素子のゲート電極に入力される信号の変化が出力信号に影響する誤差である。即ち、TFT 素子がホールド状態になる際、走査線 5 から TFT 素子のゲート電極へ入力される走査信号が、出力側である画素電極の電圧へ影響してしまう誤差である。

20

### 【0116】

N 型の TFT 素子を例とすると、TFT 素子のゲート電極とドレイン電極（画素電極）との間の寄生容量によって、走査線電圧の変化に従って、画素電極の電位が変化する。この電圧変化がフィードスルーメーカー誤差である。実施の形態 1 から 5 までは、駆動回路の基準電圧と液晶の共通電極の電圧（com 電圧）を GND としたが、フィードスルーメーカー誤差を考慮する場合は意図的に GND とは異なる電圧を com 電圧として設定し、当該フィードスルーメーカー誤差を補償する。

20

### 【0117】

ここで、フィードスルーメーカー誤差の値はパネルごとに異なり、パネルごとに com 電圧を調整することが必要である。n 型 TFT 素子の場合は、フィードスルーメーカー誤差は負側に現れることが多いので、駆動回路の基準電圧は GND で、com 電圧は GND より低く、負極駆動回路の低位電圧より高い直流電圧に設定する。他方、p 型 TFT 素子の場合は、フィードスルーメーカー誤差は正側に現れることが多いので、駆動回路の基準電圧は GND で、com 電圧は GND より高く、正極駆動回路の高位電圧より低い直流電圧である。こうすることにより、TFT 素子で発生するフィードスルーメーカー誤差を com 電圧で相殺することができる。また、com 電圧の値に併せて、データ線駆動回路 1 の動作電圧も調整する。

30

### 【0118】

詳細な各数値の例としては、n 型の TFT 素子の場合、フィードスルーメーカー誤差を -1V 程度とすると、com 電圧 = -1V、VPH = 5V、VNL = -5V である。また、p 型の TFT 素子であればフィードスルーメーカー誤差が 1V 程度とすると、com 電圧 = 1V、VPH = 5V、VNL = -5V である。これにより、フィードスルーメーカー誤差による電圧を com 電圧で相殺することができる。フィードスルーメーカー誤差に対する com 電圧の調整は例えば ±2V 程度の範囲で調整する。一般に n 型の TFT 素子が多いため、以下の説明においては n 型の TFT 素子を例として説明する。

40

### 【0119】

図 47 は本実施の形態にかかる液晶表示装置のブロック図である。データ線駆動回路 1 は実施の形態 1 から 5 のいずれかの回路、若しくはそれらを組み合わせた回路を使用する。電源回路 8 には com 電圧生成回路 9 を設け、com 電圧を生成する。電源回路 8 は、データ線駆動回路 1 と同一の基板上に製造してもよいし、別の基板上に製造してもよい。

50

c o m 電圧は、正極の高位電圧 V P H と負極の低位電圧 V N L で動作するバッファで生成し、可変抵抗や抵抗分圧回路等で調整すれば 2 V から - 2 V の電圧を出力することができる。この場合、バッファは高電圧素子で製造する必要がある。但し、c o m 電圧に求められる出力は - 1 V から - 2 V 程度であるので、バッファを G N D と負極の低位電圧 V N L とで動作させてもよい。この場合、バッファを中電圧素子で製造することが可能である。バッファを G N D と負極の低位電圧 V N L とで動作させると、G N D の電圧が出力されにくくなるが、c o m 電圧に G N D が求められないのであれば問題ない。V P L G N D c o m 電圧 V N L とすることで、電源回路での D C D C コンバータの昇圧回数を削減し、電源回路の高効率化及び消費電力の低減を図ることができる。

## 【 0 1 2 0 】

c o m 電圧は図に示す c o m 電圧生成回路 9 で生成するが、G N D と V N L との間に抵抗分圧回路を設け、抵抗と抵抗との接続点にバイパスコンデンサを設ける簡単な回路構成であってもよい。この場合、c o m 電圧の調整は抵抗分圧回路の接続抵抗を調整することにより行なうことができる。図 4 8 に、正極のガンマカーブと負極のガンマカーブ及び c o m 電圧の関係を示す。正極のガンマカーブは G N D 以上の電圧、負極のガンマカーブは G N D 以下の電圧となるようにして、c o m 電圧を - 1 ± 1 V の範囲で調整する。ここで、調整範囲は便宜的に - 1 ± 1 V としたが、上記のように G N D と負極の低位電圧 V N L で c o m 電圧を生成すれば、その範囲で調整可能である。実施の形態 1 では c o m 電圧が G N D であったのでガンマカーブの調整は、正極及び負極ごとに行なうが、本形態では正極及び負極のガンマカーブは固定して、c o m 電圧だけを調整するので、利便性が向上する。

## 【 0 1 2 1 】

以上説明したように、本実施の形態によれば T F T 素子のフィードスルー誤差による影響を相殺し、回路規模の増大を抑制した液晶表示装置のデータ線駆動回路装置を提供することができる。

## 【 0 1 2 2 】

以上、本発明についてデータ線駆動回路を例として説明をしてきたが、各回路は、シリコン基板上、ガラス基板上、あるいはプラスチック基板上に製造することができる。

## 【 図面の簡単な説明 】

## 【 0 1 2 3 】

【 図 1 】従来技術における液晶表示装置のブロック図である。

【 図 2 】従来技術におけるドット反転駆動での各画素の極性を示す模式図である。

【 図 3 】従来技術における 2 ラインドット反転駆動での各画素の極性を示す模式図である。

## 【 図 4 】従来技術におけるデータ線駆動回路のブロック図である。

【 図 5 】従来技術におけるデータ線駆動回路のタイミングチャートである。

【 図 6 】従来技術におけるデータ線駆動回路のスイッチ状態を示す図である。

【 図 7 】本発明の第 1 の実施形態における液晶表示装置のブロック図である。

【 図 8 】本発明の第 1 の実施形態におけるデータ線駆動回路 1 のブロック図である。

## 【 図 9 】本発明の第 1 の実施形態におけるクロック生成回路である。

【 図 1 0 】本発明の第 1 の実施形態におけるクロック生成のタイミングチャートである。

【 図 1 1 】本発明の第 1 の実施形態における正極レベルシフト回路 3 2 1 及び負極レベルシフト回路 3 2 2 の詳細図である。

【 図 1 2 】本発明の第 1 の実施形態における高圧レベルシフト回路 3 2 3 の詳細図である。

【 図 1 3 】本発明の第 1 の実施形態におけるドット反転駆動の画素の極性を模式した図である。

【 図 1 4 】本発明の第 1 の実施形態における信号処理回路 3 1 の信号を振り分ける回路の図である。

10

20

30

40

50

【図15】本発明の第1の実施形態における映像信号切換回路314の詳細図である。

【図16】本発明の第1の実施形態における切換回路33の詳細図である。

【図17】本発明の第1の実施形態における映像信号と駆動信号のタイミング図である。

【図18】本発明の第1の実施形態におけるDA変換回路の詳細図である。

【図19】本発明の第1の実施形態におけるデコーダ回路である。

【図20】本発明の第1の実施形態におけるデコーダ回路である。

【図21】本発明の第1の実施形態において使用するタイミングチャートである。

【図22】本発明の第1の実施形態における半導体回路装置の断面図である。

【図23】本発明の第1の実施形態における領域配置図である。

【図24】本発明の第1の実施形態における半導体回路装置の断面図である。 10

【図25】本発明の第1の実施形態における電源電圧表である。

【図26】本発明の第1の実施形態における正極駆動回路と負極駆動回路の配置図である

。

【図27】本発明の第1の実施形態における領域配置図である。

【図28】本発明の第1の実施形態における半導体回路装置の断面図である。

【図29】本発明の第2の実施形態における映像信号回路のブロック図である。

【図30】本発明の第3の実施形態における負極レベルシフト回路324の詳細図である

。

【図31】本発明の実施形態における電源電圧の相関図である。

【図32】本発明の第3の実施形態における負極レベルシフト回路324の詳細図である 20

。

【図33】本発明の第3の実施形態における領域配置図である。

【図34】本発明の第3の実施形態における半導体回路装置の断面図である。

【図35】本発明の第4の実施形態におけるプリチャージスイッチの詳細図である。

【図36】本発明の第4の実施形態におけるタイミングチャートである。

【図37】本発明の第4の実施形態におけるプリチャージスイッチの詳細図である。

【図38】本発明の第5の実施形態におけるデータ線駆動回路のブロック図である。

【図39】本発明の第5の実施形態におけるサンプルホールド回路である。

【図40】本発明の第5の実施形態における増幅器詳細図である。

【図41】本発明の第5の実施形態におけるサンプルホールド回路である。 30

【図42】本発明の第5の実施形態におけるDA変換回路の詳細図である。

【図43】本発明の第5の実施形態における映像信号回路のブロック図である。

【図44】本発明の第5の実施形態におけるDA変換回路の詳細図である。

【図45】本発明の第5の実施形態におけるDA変換回路である。

【図46】本発明の第5の実施形態におけるタイミングチャートである。

【図47】本発明の第6の実施形態における液晶表示装置のブロック図である。

【図48】本発明の第6の実施形態におけるデジタル映像信号とアナログ映像信号との相関図である。

#### 【符号の説明】

##### 【0124】

1 データ線駆動回路、2 走査線駆動回路、3 液晶パネル、4 データ線、

5 走査線、6 画素、7 制御回路、8 電源回路、9 com電圧生成回路、

10 正極駆動回路、11 正極シフトレジスタ回路、12 正極データレジスタ回路、

13 正極データラッチ回路、14 変換回路、15 正極階調電圧生成回路、

16 正極サンプルホールド回路、17 変換回路、20 負極駆動回路、

21 負極シフトレジスタ回路、22 負極データレジスタ回路、

23 負極データラッチ回路、24 変換回路、25 負極階調電圧生成回路

26 負極サンプルホールド回路、27 変換回路、31 信号処理回路、

32 レベルシフト回路、33 切換回路、51 データ線駆動回路、

58 電源回路、59 コモン電圧生成回路、61 シフトレジスタ回路、 40

6 2 データレジスタ回路、6 3 データラッチ回路、6 4 切換回路、

6 5 レベルシフト回路、6 7 変換回路、6 8 変換回路、7 0 信号処理回路、

1 4 1 増幅器、1 4 2 スイッチ、1 4 4 デコーダ回路、

1 4 5 プリチャージスイッチ、1 5 1 階調電圧生成回路要素、

1 6 1 サンプリングスイッチ、1 6 2 容量、1 6 3 正極増幅器、

1 7 1 正極増幅器、1 7 4 デコーダ、1 7 7 切換回路、1 7 8 切換回路、

1 7 9 切換回路、2 4 5 プリチャージスイッチ、2 5 1 階調電圧生成回路要素、

2 6 1 スイッチ、2 6 2 容量、2 6 3 負極増幅器、2 7 1 負極増幅器、

2 7 4 デコーダ、2 7 7、2 7 8、2 7 9 切換回路、

3 1 1、3 1 2、3 1 3 ラッチ回路、3 1 4 映像信号切換回路、

3 1 5 データ反転回路、3 1 6、3 1 7 ラッチ回路、3 2 1 正極レベルシフト回路

、

3 2 2 負極レベルシフト回路、3 2 3 高圧レベルシフト回路、

3 2 4 負極レベルシフト回路、3 3 1、3 3 2 スイッチ、

3 3 3 プリチャージスイッチ、3 3 4、3 3 5、3 3 6 スイッチ、

3 3 7 増幅器、1 6 3 1 b、1 6 3 1 a スイッチ、1 6 3 1 入力切換回路、

1 6 3 2 a、1 6 3 2 c、1 6 3 2、1 6 3 2 b、1 6 3 2 a パソコン、

1 6 3 2 差動増幅段、1 6 3 3 a、1 6 3 3 b スイッチ、1 6 3 3 出力切換回路、

1 6 3 4 回路、1 6 3 5 a パソコン、1 6 3 5 出力段、

1 6 3 6 a、1 6 3 6 b スイッチ、1 6 3 6 切換回路、

1 7 1 1、1 7 1 2、1 7 2 1、1 7 2 2、1 7 3 1、1 7 3 2 増幅器、

1 7 4 1、1 7 4 2、1 7 5 1、1 7 5 2、1 7 6 1、1 7 6 2 デコーダ、

2 7 1 1、2 7 1 2、2 7 2 1、2 7 2 2、2 7 3 1、2 7 3 2 増幅器、

2 7 4 1、2 7 4 2、2 7 5 1、2 7 5 2、2 7 6 1、2 7 6 2 デコーダ、

3 1 4 1、3 1 4 2 スイッチ、3 1 6 1 クロック生成回路、3 2 1 1 レベルシフタ

、

3 2 1 1 遅延回路、3 2 1 2、3 2 1 3、3 2 1 4、3 2 1 5 パソコン、

3 2 1 6 インバータ、3 2 2 1、3 2 2 2、3 2 2 3、3 2 2 4、

3 2 2 5、3 2 2 6、3 2 2 7、3 2 2 8 パソコン、3 2 2 9 インバータ、

3 2 3 1、3 2 3 2、3 2 3 3、3 2 3 4、3 2 3 5、3 2 3 6、3 2 3 7、

3 2 3 8 パソコン、3 2 3 9、4 4 1 1、4 4 1 2 インバータ、

4 4 1 3 論理回路、4 4 1 7 パソコン、4 4 2 1、4 4 2 2 インバータ、

4 4 2 3 Nch エンハンスマント型トランジスタ、

4 4 2 4 Nch ディプレッション型トランジスタ

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図10】

【図9】

【図11】

【図12】

【図13】

|       | R1 | G1 | B1 | R2 | G2 | B2 |

|-------|----|----|----|----|----|----|

| X1ライン | +  | -  | +  | -  | +  | -  |

| X2ライン | -  | +  | -  | +  | -  | +  |

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図24】

【図23】

【図25】

| 電源名 | 電圧   |

|-----|------|

| VDD | 2.5V |

| VSS | 0V   |

| VPH | 5V   |

| VPL | 0V   |

| VNH | 0V   |

| VNL | -5V  |

| 層名      | 電圧   |

|---------|------|

| Psub    | -5V  |

| Nwell-1 | 5V   |

| Nwell-2 | 0V   |

| Nwell-3 | 5V   |

| Nwell-4 | 2.5V |

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図4-3】

【図4-4】

【図4-5】

【図4-6】

【図47】

【図48】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 2 1 L

G 0 9 G 3/20 6 2 3 A

G 0 9 G 3/20 6 2 3 F

G 0 9 G 3/20 6 2 3 J

G 0 9 G 3/20 6 2 3 L

F ターム(参考) 5C006 AA22 AC11 AC21 AC26 AF25 AF42 AF43 AF44 AF71 AF83

BB16 BC03 BC12 BC16 BF03 BF11 BF24 BF25 BF34 BF46

FA41 FA47

5C080 AA10 BB05 CC03 DD22 DD26 EE28 EE29 EE30 FF11 JJ02

JJ03 JJ04 JJ05 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置的驱动电路和显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP2006106657A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2006-04-20 |

| 申请号            | JP2005016518                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2005-01-25 |

| [标]申请(专利权)人(译) | NEC电子股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | NEC电子公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 橋本義春                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 橋本 義春                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| CPC分类号         | G09G3/3607 G09G3/3614 G09G3/3648 G09G3/3655 G09G3/3688 G09G2310/0248 G09G2310/027<br>G09G2310/0289 G09G2310/0297 G09G2310/06 G09G2320/0219 G09G2330/021 A61H23/006 A61H23<br>/0254 A61H2201/0165 A61H2201/1418 A61H2201/149 A61H2201/50 A61H2205/12                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| FI分类号          | G09G3/36 G02F1/133.520 G02F1/133.550 G09G3/20.611.A G09G3/20.621.B G09G3/20.621.L G09G3<br>/20.623.A G09G3/20.623.F G09G3/20.623.J G09G3/20.623.L G09G3/20.621.M                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-Term分类号      | 2H093/NA16 2H093/NA32 2H093/NA34 2H093/NA43 2H093/NC03 2H093/NC05 2H093/NC22 2H093<br>/NC26 2H093/NC34 2H093/ND39 2H093/ND49 5C006/AA22 5C006/AC11 5C006/AC21 5C006/AC26<br>5C006/AF25 5C006/AF42 5C006/AF43 5C006/AF44 5C006/AF71 5C006/AF83 5C006/BB16 5C006<br>/BC03 5C006/BC12 5C006/BC16 5C006/BF03 5C006/BF11 5C006/BF24 5C006/BF25 5C006/BF34<br>5C006/BF46 5C006/FA41 5C006/FA47 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD22 5C080<br>/DD26 5C080/EE28 5C080/EE29 5C080/EE30 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04<br>5C080/JJ05 5C080/JJ06 2H193/ZA04 2H193/ZC02 2H193/ZC13 2H193/ZC14 2H193/ZC20 2H193<br>/ZF03 |         |            |

| 优先权            | 2004073741 2004-03-16 JP<br>2004262191 2004-09-09 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 其他公开文献         | JP4847702B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

## 摘要(译)

解决的问题：减小点反转驱动的液晶显示装置的数据线驱动电路的电路规模。显示装置的驱动电路，其并行输出基于串行输入的数字视频信号生成的模拟视频信号，该电平移位转换串行输入的数字视频信号的电压电平。电路32，DA转换电路14和24，其基于由电平移位电路32，DA转换电路14和24的输出侧或电平移位电路32和DA转换电路进行了电平转换的数字视频信号来生成模拟视频信号。它具有连接在14和24之间的扩展电路12和22，用于并行扩展和保持输入的串行视频信号并并行输出视频信号。以这种方式，在图像信号寄存器电路12和22之前形成电平移位电路32。[\[选择图\]](#)[\[图8\]](#)