(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-310113

(P2004-310113A)

(43) 公開日 平成16年11月4日(2004.11.4)

(51) Int.Cl.<sup>7</sup>

**G09G** 3/36

**G02F** 1/133

**G02F** 1/1337

**G09G** 3/20

F 1

G09G 3/36

G02F 1/133 550

G02F 1/133 570

G02F 1/133 575

G02F 1/1337 505

テーマコード(参考)

2H090

2H093

5C006

5C080

審査請求 未請求 請求項の数 60 O L (全 58 頁) 最終頁に続く

|              |                              |           |                                              |

|--------------|------------------------------|-----------|----------------------------------------------|

| (21) 出願番号    | 特願2004-113685 (P2004-113685) | (71) 出願人  | 390019839<br>三星電子株式会社<br>大韓民国京畿道水原市靈通区梅灘洞416 |

| (22) 出願日     | 平成16年4月7日 (2004.4.7)         | (74) 代理人  | 100094145<br>弁理士 小野 由己男                      |

| (31) 優先権主張番号 | 2003-021638                  | (74) 代理人  | 100106367<br>弁理士 稲積 朋子                       |

| (32) 優先日     | 平成15年4月7日 (2003.4.7)         | (72) 発明者  | 宋 長 根<br>大韓民国ソウル特別市江南区大峙2洞ミド                 |

| (33) 優先権主張国  | 韓国(KR)                       | (72) 発明者  | アパート110等304号                                 |

| (31) 優先権主張番号 | 2003-061880                  | (72) 発明者  | 朴 東 園<br>大韓民国ソウル特別市西大门区▲ヒョン▼                 |

| (32) 優先日     | 平成15年9月4日 (2003.9.4)         |           | 底洞極東アパート103棟304号                             |

| (33) 優先権主張国  | 韓国(KR)                       | F ターム(参考) | 2H090 HC10 HD11 KA04 LA04 MA01<br>MA15       |

最終頁に続く

(54) 【発明の名称】表示装置、駆動装置及び駆動方法

## (57) 【要約】

【課題】 表示装置とこれの駆動装置及び方法を提供する。

## 【解決手段】

階調信号補正部は階調信号ソースから階調信号を受信し、以前フレームの階調信号と現在フレームの階調信号と次フレームの階調信号とを考慮して現在フレームの補正階調信号を出力する。データドライバーは補正階調信号に対応するデータ電圧に変換して画像信号を出力する。走査ドライバーは走査信号を順次に供給する。表示パネルは走査信号を伝達する複数の走査ラインと、画像信号を伝達する複数のデータラインと、走査ライン及びデータラインにより囲まれた領域に形成され走査ライン及びデータラインにそれぞれ連結されたスイッチング素子を備えてマトリックス状の配列された複数の画素を含む。これによって、現在フレームの階調信号が印加されるによって以前フレームの階調信号と次フレームの階調信号とを考慮して補正された階調信号を現在フレームに印加することで液晶の応答速度を高速化させることができる。

**【特許請求の範囲】****【請求項 1】**

階調信号ソースから階調信号を受信して、前記階調信号に基づいて補正階調信号を生成して出力する階調信号補正部と、

前記補正階調信号に基づいて、画像信号を生成して供給するデータドライバーと、

走査信号を順次的に供給する走査ドライバーと、

前記データドライバーから前記画像信号が供給されるとともに、前記走査ドライバーから前記走査信号が供給される表示パネルと、

を備え、

前記表示パネルは、

前記走査信号を伝達する複数の走査ラインと、

前記画像信号を伝達する複数のデータラインと、

前記走査ライン及び前記データラインにより囲まれた領域に形成され、前記走査ライン及び前記データラインにそれぞれ連結された複数のスイッチング素子と、

前記スイッチング素子により制御され、マトリックス状に配列された複数の画素と、を有し、

前記階調信号補正部は、第1フレームの前記階調信号と、前記第1フレームの次のフレームである第2フレームの前記階調信号と、前記第2フレームの次のフレームである第3フレームの前記階調信号とを考慮して、前記第2フレームの前記補正階調信号を生成して出力する、

表示装置。

**【請求項 2】**

前記補正階調信号は、前記階調信号に対して1フレームの期間だけ遅れて出力される、請求項1に記載の表示装置。

**【請求項 3】**

前記階調信号補正部は、

前記第1フレームの前記階調信号の電圧である第1電圧と前記第2フレームの前記階調信号の電圧である第2電圧とが相異する場合、前記第3フレームの前記階調信号が受信される期間において、前記第1電圧に対する前記第2フレームの前記補正階調信号の電圧の変化量が前記第1電圧に対する前記第2電圧の変化量よりも大きくなるように、前記第2フレームの前記補正階調信号を生成して出力する、

請求項1に記載の表示装置。

**【請求項 4】**

前記階調信号補正部は、

前記第1フレームの前記階調信号の電圧が第1低階調信号電圧であり、前記第2フレームの前記階調信号の電圧が前記第1低階調信号電圧より高い電圧である第1高階調信号電圧である場合、前記第2フレームの前記階調信号が受信される期間において、前記第1低階調信号電圧より高く前記第1高階調信号電圧より低い電圧である第2高階調信号電圧になるように前記第1フレームの前記補正階調信号を生成して出力する、

請求項3に記載の表示装置。

**【請求項 5】**

前記第1低階調信号電圧はブラック階調信号の電圧である、

請求項4に記載の表示装置。

**【請求項 6】**

前記画素は、液晶を含み、

前記第2高階調信号電圧になるように生成された前記補正階調信号は、前記液晶をプリチルト(p r e - t i l t)させるためのプリチルト形成信号である、

請求項5に記載の表示装置。

**【請求項 7】**

10

30

40

50

前記表示パネルは、

前記スイッチング素子を経由して前記データラインから前記画素信号の供給を受ける画素電極と、

前記画素電極との間で前記液晶に電圧を印加するための共通電極と、

をさらに有し、

前記階調信号の電圧又は前記補正階調信号の電圧は、前記共通電極に対する前記画素電極の電圧であり、

前記ブラック階調信号の電圧は、0.5～1.5ボルトのうちいずれかの電圧であり、

前記プリチルト形成信号の電圧は、2～3.5ボルトのうちいずれかの電圧である、

請求項6に記載の表示装置。

10

#### 【請求項8】

前記階調信号及び前記補正階調信号は、デジタル階調の信号である、

請求項1に記載の表示装置。

#### 【請求項9】

前記階調信号補正部は、

前記階調信号に対応するデジタル階調の信号を並列変換するための並列変換部と、

前記並列変換部が並列変換した前記階調信号を直列変換して、前記補正階調信号に対応するデジタル階調の信号を前記データドライバーに出力するための直列変換部と、

をさらに有する、

請求項8に記載の表示装置。

20

#### 【請求項10】

前記階調信号及び前記補正階調信号は、アナログ階調の信号である、

請求項1に記載の表示装置。

#### 【請求項11】

前記階調信号補正部は、

前記階調信号に対応するアナログ階調の信号の周波数を、処理可能な周波数に変換するための合成器と、

前記補正階調信号に対応するアナログ階調の信号を分離して前記データドライバーに出力するための分離器と、

を有する、

請求項10記載の表示装置。

30

#### 【請求項12】

前記階調信号補正部は、

受信された前記階調信号を所定フレームの期間だけ保存して出力する第1メモリと、

前記階調信号を前記第1メモリから受け取り、さらに前記所定フレームの期間だけ前記階調信号を保存して出力する第2メモリと、

前記第1メモリから前記階調信号を読み出すことである第1読出動作と、前記第2メモリから前記階調信号を読み出すことである第2読出動作と、前記第1メモリへ前記階調信号を書き込むことである第1書き込み動作と、前記第2メモリへ前記階調信号を書き込むことである第2書き込み動作とを制御するコントローラと、

前記第2メモリが出力した前記第1フレームの前記階調信号と、前記第1メモリが出力した前記第2フレームの前記階調信号と、受信された前記第3フレームの前記階調信号とを考慮して、前記第2フレームの前記補正階調信号を生成して出力する階調信号変換部と、

を有する、

請求項1に記載の表示装置。

40

#### 【請求項13】

前記所定フレームの期間は、1フレームの期間である、

請求項12に記載の表示装置。

#### 【請求項14】

50

前記第1読出動作、前記第2読出動作、前記第1書込動作及び前記第2書込動作に同期されるクロック周波数は、前記階調信号補正部に供給されるクロック周波数と同一である、

請求項12に記載の表示装置。

【請求項15】

前記第1読出動作、前記第2読出動作、前記第1書込動作及び前記第2書込動作の少なくとも1つに同期されるクロック周波数は、前記階調信号補正部に供給されるクロック周波数を正の整数で割った値である、

請求項12に記載の表示装置。

【請求項16】

前記階調信号補正部は、

前記階調信号に対応するアナログ階調の信号の周波数を、処理可能な周波数に変換するための合成器と、

前記補正階調信号に対応するアナログ階調の信号を分離して前記データドライバーに出力するための分離器と、

をさらに有する、

請求項15に記載の表示装置。

【請求項17】

前記階調信号補正部は、

受信された前記階調信号を所定フレームの期間だけ保存して出力するメモリと、

前記メモリから前記階調信号を読み出すことである読出動作と、前記メモリへ前記階調信号を書き込むことである書込動作とを制御するコントローラと、

前記第1フレームの前記階調信号と前記第2フレームの前記階調信号と前記第3フレームの前記階調信号とを考慮して、前記第2フレームの前記補正階調信号を生成して出力する階調信号変換部と、

を有する、

請求項1に記載の表示装置。

【請求項18】

前記所定フレームの期間は、1フレームの期間である、

請求項17に記載の表示装置。

30

【請求項19】

前記読出動作及び前記書込動作に同期されるクロック周波数は、前記階調信号補正部に供給されるクロック周波数と同一である、

請求項17に記載の表示装置。

【請求項20】

前記読出動作及び前記書込動作の少なくとも1つに同期されるクロック周波数は、前記階調信号補正部に供給されるクロック周波数を正の整数で割った値である、

請求項17に記載の表示装置。

【請求項21】

前記階調信号補正部は、

前記階調信号に対応するアナログ階調の信号の周波数を、処理可能な周波数に変換するための合成器と、

前記補正階調信号に対応するアナログ階調の信号を分離して前記データドライバーに出力するための分離器と、

をさらに有する、

請求項17に記載の表示装置。

40

【請求項22】

前記画素は、液晶を含み、

前記表示パネルは、垂直配向モード、パターン化された垂直配向モード、多重ドメイン垂直配向モードのうちいずれかを採用する、

50

請求項 1 に記載の表示装置。

【請求項 2 3】

前記階調信号補正部は、

前記第 2 フレームの前記階調信号の電圧と前記第 3 フレームの前記階調信号の電圧とが同じ場合、前記第 3 フレームの次のフレームである第 4 フレームの前記階調信号が受信される期間において、前記第 3 フレームの前記補正階調信号の電圧が前記第 3 フレームの前記階調信号の電圧と同じになるように、前記第 3 フレームの前記補正階調信号を生成して出力する、

請求項 3 に記載の表示装置。

【請求項 2 4】

前記階調信号補正部は、

前記第 1 フレームの前記階調信号と前記第 2 フレームの前記階調信号とを考慮して、前記第 2 フレームの第 1 補正階調信号を生成して出力する階調信号変換部と、

前記第 2 フレームの前記第 1 補正階調信号を前記階調信号変換部から受け取り、所定フレームの期間だけ前記第 2 フレームの前記第 1 補正階調信号を保存して出力するメモリと、

前記メモリから前記第 2 フレームの前記第 1 補正階調信号を読み出すことである補正読出動作と、前記メモリへ前記第 2 フレームの前記第 1 補正階調信号を書き込むことである補正書込動作とを制御するコントローラと、

を有し、

前記階調信号変換部は、前記第 3 フレームの前記階調信号が入力され、前記メモリから前記第 2 フレームの前記第 1 補正階調信号を受け取り、前記第 2 フレームの前記第 1 補正階調信号と前記第 3 フレームの前記階調信号とを考慮して、前記第 2 フレームの第 2 補正階調信号を前記第 2 フレームの前記補正階調信号として生成して出力する、

請求項 1 に記載の表示装置。

【請求項 2 5】

前記第 2 フレームの前記第 1 補正階調信号は、

前記階調信号に関する情報である階調信号情報と、

前記第 1 電圧に対する前記第 2 フレームの電圧の変化量が前記第 1 電圧に対する前記第 2 電圧の変化量よりも大きくなるように生成されることである補正処理の存否を示す履歴情報と、

を含む、

請求項 2 4 に記載の表示装置。

【請求項 2 6】

前記階調信号変換部は、前記第 2 フレームの前記第 1 補正階調信号を生成するとき、前記階調信号情報において前記補正処理が存在している場合に前記履歴情報に対応する信号を活性化させ、前記階調信号情報において前記補正処理が存在していない場合に前記履歴情報に対応する信号を非活性化させる、

請求項 2 5 に記載の表示装置。

【請求項 2 7】

前記階調信号変換部は、前記第 3 フレームの前記第 1 補正階調信号を生成するとき、前記第 2 フレームの前記第 1 補正階調信号の前記履歴情報に対応する信号が活性化されている場合に、前記第 3 フレームの前記第 1 補正階調信号の前記履歴情報に対応する信号を非活性化させる、

請求項 2 6 に記載の表示装置。

【請求項 2 8】

階調信号ソースから階調信号を受信して、前記階調信号に基づいて補正階調信号を生成して出力するタイミング制御部と、

前記補正階調信号に基づいて、画像信号を生成して供給するデータドライバーと、

走査信号を順次的に供給する走査ドライバーと、

10

20

30

40

50

前記データドライバーから前記画像信号が供給されるとともに、前記走査ドライバーから前記走査信号が供給される表示パネルと、

を備え、

前記表示パネルは、

前記走査信号を伝達する複数の走査ラインと、

前記画像信号を伝達する複数のデータラインと、

前記走査ライン及び前記データラインにより囲まれた領域に形成され、前記走査ライン及び前記データラインにそれぞれ連結された複数のスイッチング素子と、

前記スイッチング素子により制御され、マトリックス状に配列された複数の画素と、

を有し、

前記タイミング制御部は、前記階調信号に対応するフル階調の輝度をダウンさせる処理である輝度低減処理を行い、第1フレームの前記輝度低減処理された前記階調信号と、前記第1フレームの次のフレームである第2フレームの前記輝度低減処理された前記階調信号とを考慮して、前記補正階調信号を生成して出力する、

表示装置。

#### 【請求項 29】

前記タイミング制御部は、

前記輝度低減処理された前記階調信号のレベルが前記フル階調のレベルより小さい場合に前記第1フレームの前記階調信号と前記第2フレームの前記階調信号とを考慮して前記補正階調信号を出力し、

前記輝度低減処理された前記階調信号のレベルがフル階調のレベルである場合にオーバーシュート電圧を発生するように前記補正階調信号を出力する、

請求項 28 に記載の表示装置。

#### 【請求項 30】

前記タイミング制御部は、

前記階調信号を前記輝度低減処理して出力するデータ変換部と、

前記輝度低減処理された前記階調信号のレベルが前記フル階調のレベルより小さい場合に前記第1フレームの前記階調信号と前記第2フレームの前記階調信号とを考慮して前記補正階調信号を出力し、前記輝度低減処理された前記階調信号のレベルがフル階調のレベルである場合にオーバーシュート電圧を発生するように前記補正階調信号を出力する階調信号補正部と、

を有する、

請求項 29 に記載の表示装置。

#### 【請求項 31】

前記階調信号は、

赤色の階調に関する信号である赤色階調信号と、

緑色の階調に関する信号である緑色階調信号と、

青色の階調に関する信号である青色階調信号と、

を含み、

前記データ変換部は、

前記輝度低減処理される前の前記赤色階調信号のレベルと前記輝度低減処理された後の前記赤色階調信号のレベルとを記憶しているRルックアップテーブルと、

前記輝度低減処理される前の前記緑色階調信号のレベルと前記輝度低減処理された後の前記緑色階調信号のレベルとを記憶しているGルックアップテーブルと、

前記輝度低減処理される前の前記青色階調信号のレベルと前記輝度低減処理された後の前記青色階調信号のレベルとを記憶しているBルックアップテーブルと、

を含む、

請求項 30 に記載の表示装置。

#### 【請求項 32】

前記Rルックアップテーブルの前記赤色階調信号のレベル、前記Gルックアップテーブル

10

20

30

40

50

ルの前記緑色階調信号のレベル及び前記Bルックアップテーブルの前記青色階調信号のレベルは、それぞれ複数存在する、

請求項31記載の表示装置。

**【請求項33】**

前記データ変換部は、フル階調のレベルが $2^k$ であるkビットの前記階調信号(kは正の整数)をビット数の拡張によりフル階調のレベルが $2^{k+p}-r$ である( $k+p$ )ビットの前記階調信号(pは正の整数、rはkより小さい正の整数)に変換し、フル階調のレベルが $2^{k+p}-r$ である( $k+p$ )ビットの前記階調信号をフル階調のレベルが $2^k-r$ であるkビットの前記階調信号に変換する、

請求項30に記載の表示装置。 10

**【請求項34】**

前記階調信号補正部は、フル階調のレベルが $2^k-r$ であるkビットの前記階調信号に対して前記Rルックアップテーブル、前記Gルックアップテーブル及び前記Bルックアップテーブルを用いて前記補正階調信号を生成し、残りのr階調データに対してオーバーシュート電圧を発生するように前記補正階調信号を生成する、

請求項33に記載の表示装置。

**【請求項35】**

前記データ変換部は、フル階調のレベルが225である8ビットの前記階調信号をビット数の拡張によりフル階調のレベルが1008である10ビットの前記階調信号に変換し、フル階調のレベルが1008である10ビットの前記階調信号をフル階調のレベルが252である8ビットの前記階調信号に変換する、 20

請求項30に記載の表示装置。

**【請求項36】**

前記階調信号補正部は、フル階調のレベルが252である8ビットの前記階調信号に対して前記Rルックアップテーブル、前記Gルックアップテーブル及び前記Bルックアップテーブルを用いて前記補正階調信号を生成し、残りの3階調データに対してオーバーシュート電圧を発生するように前記補正階調信号を生成する、

請求項35に記載の表示装置。

**【請求項37】**

前記データドライバーは、デジタルの信号とアナログの信号とを相互に変換するDA変換器を有し、 30

前記DA変換器は、直列に連結された複数の抵抗素子を含み、

前記複数の抵抗素子の一端にはオーバーシュート基準電圧が印加される、

請求項28に記載の表示装置。

**【請求項38】**

複数の走査ラインと、前記走査ラインと絶縁されて交差する複数のデータラインと、前記走査ライン及び前記データラインにより囲まれる領域に形成されそれぞれ前記走査ライン及び前記データラインに連結された複数のスイッチング素子と、前記スイッチング素子により制御されマトリックス型で配列された複数の画素とを有する表示パネルを駆動する駆動装置であって、 40

階調信号ソースから階調信号を受信し、前記階調信号に基づいて補正階調信号を生成して出力する階調信号補正部と、

前記補正階調信号に基づいて、画像信号を生成して前記データラインに供給するデータドライバーと、

走査信号を前記走査ラインに順次的に供給する走査ドライバーと、

を備え、

前記階調信号補正部は、第1フレームの前記階調信号と、前記第1フレームの次のフレームである第2フレームの前記階調信号と、前記第2フレームの次のフレームである第3フレームの前記階調信号とを考慮して、前記第2フレームの前記補正階調信号を生成して出力する、 50

駆動装置。

**【請求項 3 9】**

前記階調信号補正部は、前記階調信号に対応するフル階調の輝度をダウンさせる処理である輝度低減処理が行われた前記階調信号のレベルがフル階調のレベルより小さい場合に前記第1フレームの前記階調信号と前記第2フレームの前記階調信号とを考慮して前記補正階調信号を出力し、前記輝度低減処理された前記階調信号のレベルがフル階調のレベルである場合にオーバーシュート電圧を発生するように前記補正階調信号を出力する、請求項38に記載の駆動装置。

**【請求項 4 0】**

前記階調信号補正部は、

前記第2フレームの前記階調信号の電圧と前記第3フレームの前記階調信号の電圧とが同じ場合、前記第3フレームの次のフレームである第4フレームの前記階調信号が受信される期間において、前記第3フレームの前記補正階調信号の電圧が前記第3フレームの前記階調信号の電圧と同じになるように、前記第3フレームの前記補正階調信号を生成して出力する、

請求項38に記載の駆動装置。

**【請求項 4 1】**

前記階調信号補正部は、

前記第1フレームの前記階調信号と前記第2フレームの前記階調信号とを考慮して、前記第2フレームの第1補正階調信号を生成して出力する階調信号変換部と、

前記第2フレームの前記第1補正階調信号を前記階調信号変換部から受け取り、所定フレームの期間だけ前記第2フレームの前記第1補正階調信号を保存して出力するメモリと、

前記メモリから前記第2フレームの前記第1補正階調信号を読み出すことである補正読出動作と、前記メモリへ前記第2フレームの前記第1補正階調信号を書き込むことである補正書込動作とを制御するコントローラと、

を有し、

前記階調信号変換部は、前記第3フレームの前記階調信号が入力され、前記メモリから前記第2フレームの前記第1補正階調信号を受け取り、前記第2フレームの前記第1補正階調信号と前記第3フレームの前記階調信号とを考慮して、前記第2フレームの第2補正階調信号を前記第2フレームの前記補正階調信号として生成して出力する、

請求項40に記載の駆動装置。

**【請求項 4 2】**

複数の走査ラインと、前記走査ラインと絶縁されて交差する複数のデータラインと、前記走査ライン及び前記データラインにより囲まれる領域に形成されそれぞれ前記走査ライン及び前記データラインに連結された複数のスイッチング素子と、前記スイッチング素子により制御されマトリックス型で配列された複数の画素とを有する表示パネルを駆動する駆動装置であって、

階調信号ソースから階調信号を受信し、前記階調信号に基づいて補正階調信号を生成して出力するタイミング制御部と、

前記補正階調信号に基づいて、画像信号を生成して前記データラインに供給するデータドライバーと、

走査信号を前記走査ラインに順次的に供給する走査ドライバーと、

を備え、

前記タイミング制御部は、前記階調信号に対応するフル階調の輝度をダウンさせる処理である輝度低減処理を行い、第1フレームの前記輝度低減処理された前記階調信号と前記第1フレームの次のフレームである第2フレームの前記輝度低減処理された前記階調信号とを考慮して、前記補正階調信号を生成して出力する、

駆動装置。

**【請求項 4 3】**

10

20

30

40

50

前記タイミング制御部は、前記輝度低減処理された前記階調信号のレベルが前記フル階調のレベルより小さい場合に前記第1フレームの前記階調信号と前記第2フレームの前記階調信号とを考慮して前記補正階調信号を出力し、前記輝度低減処理された前記階調信号のレベルがフル階調のレベルである場合にオーバーシュート電圧を発生するように前記補正階調信号を出力する、

請求項42に記載の駆動装置。

【請求項44】

前記タイミング制御部は、

前記階調信号を前記輝度低減処理して出力するデータ変換部と、

前記輝度低減処理された前記階調信号のレベルがフル階調のレベルより小さい場合に前記第1フレームの前記階調信号と前記第2フレームの前記階調信号とを考慮して前記補正階調信号を出力し、前記輝度低減処理された前記階調信号のレベルがフル階調のレベルである場合にオーバーシュート電圧を発生するように前記補正階調信号を出力する階調信号補正部と、

を有する、

請求項43に記載の駆動装置。

【請求項45】

複数の走査ラインと、前記走査ラインと絶縁されて交差する複数のデータラインと、前記走査ライン及び前記データラインにより囲まれる領域に形成されそれぞれ前記走査ライン及び前記データラインに連結された複数のスイッチング素子と、前記スイッチング素子により制御されマトリックス型で配列された複数の画素とを有する表示パネルが駆動される駆動方法であって、

(a) 前記走査ラインに走査信号が順次的に供給される段階と、

(b) 階調信号ソースから階調信号が受信され、第1フレームの前記階調信号と、前記第1フレームの次のフレームである第2フレームの前記階調信号と、前記第2フレームの次のフレームである第3フレームの前記階調信号とを考慮して、前記第2フレームの前記補正階調信号が生成される段階と、

(c) 前記補正階調信号に基づいて、画像信号が生成されて前記データラインに供給される段階と、

を備えた、

駆動方法。

【請求項46】

前記第2フレームの前記補正階調信号は、前記第1フレームの前記階調信号の電圧である第1電圧と前記第2フレームの前記階調信号の電圧である第2電圧とが相異する場合、前記第3フレームの前記階調信号が受信される期間において、前記第1電圧に対する前記第2フレームの前記補正階調信号の電圧の変化量が前記第1電圧に対する前記第2電圧の変化量よりも大きくなるように生成されて出力されたものである、

請求項45に記載の駆動方法。

【請求項47】

前記画素は、液晶を含み、

前記第2フレームの前記補正階調信号は、

前記第1フレームの前記階調信号の電圧がブラック階調の電圧であり前記第2フレームの前記階調信号の電圧がホワイト階調の電圧である場合に、前記第2フレームの前記階調信号が受信される期間において、前記ブラック階調の電圧より高く前記ホワイト階調の電圧より低い電圧を印加して前記液晶をプリチルトさせるためのプリチルト信号である、

請求項45に記載の駆動方法。

【請求項48】

前記段階(b)は、

(b-11) 受信された前記階調信号が所定フレームの期間だけ保存されて出力される段階と、

10

20

30

40

50

(b - 12) 前記段階 (b - 11) で出力された前記階調信号が受け取られ、さらに前記所定フレームの期間だけ前記階調信号が保存されて出力される段階と、

(b - 13) 前記段階 (b - 12) で出力された前記第1フレームの前記階調信号と、前記段階 (b - 11) で出力された前記第2フレームの前記階調信号と、受信された前記第3フレームの前記階調信号とを考慮して、前記第2フレームの前記補正階調信号が生成されて出力される段階と、

を有する、

請求項45に記載の駆動方法。

**【請求項49】**

前記所定フレームの期間は、1フレームの期間である、

10

請求項48に記載の駆動方法。

**【請求項50】**

前記段階 (b) は、

(b - 21) 前記第1フレームの前記階調信号と前記第2フレームの前記階調信号とを考慮して、前記第2フレームの第1補正階調信号が生成されて出力される段階と、

(b - 22) 前記段階 (b - 21) で出力された前記第2フレームの前記第1補正階調信号が受け取られ、所定フレームの期間だけ前記第2フレームの前記第1補正階調信号が保存されて出力される段階と、

(b - 23) 前記第3フレームの前記階調信号が入力され、前記段階 (b - 21) で出力された前記第2フレームの前記第1補正階調信号が受け取られ、前記第2フレームの前記第1補正階調信号と前記第3フレームの前記階調信号とを考慮して、前記第2フレームの第2補正階調信号が前記第2フレームの前記補正階調信号として生成されて出力される段階と、

20

を有する、

請求項45に記載の駆動方法。

**【請求項51】**

前記所定フレームの期間は、1フレームの期間である、

請求項50に記載の駆動方法。

**【請求項52】**

前記段階 (b) では、

30

前記第2フレームの前記階調信号の電圧と前記第3フレームの前記階調信号の電圧と同じ場合、前記第3フレームの次のフレームである第4フレームの前記階調信号が受信される期間において、前記第3フレームの前記補正階調信号の電圧が前記第3フレームの前記階調信号の電圧と同じになるように、前記第3フレームの前記補正階調信号が生成されて出力される、

請求項45に記載の駆動方法。

**【請求項53】**

前記段階 (b) は、

(b - 21) 前記第1フレームの前記階調信号と前記第2フレームの前記階調信号とを考慮して、前記第2フレームの第1補正階調信号が生成されて出力される段階と、

40

(b - 31) 前記第3フレームの前記階調信号が入力され、前記第2フレームの前記第1補正階調信号が抽出される段階と、

(b - 32) 前記第2フレームの前記第1補正階調信号のレベルが第1階調であるとともに前記第3フレームの前記階調信号のレベルが第2階調であることである第1条件が満たされるか否かが判断される段階と、

(b - 33) 前記段階 (b - 32) で前記第1条件が満たされないと判断された場合に、前記第3フレームの前記階調信号が変換されて、前記第2フレームの前記第1補正階調信号と前記第3フレームの前記階調信号とを考慮して、前記第2フレームの第2補正階調信号が前記第2フレームの前記補正階調信号として生成されて出力される段階と、

(b - 34) 前記段階 (b - 32) で前記第1条件が満たされると判断された場合に、

50

前記第2フレームの前記第1補正階調信号と前記第3フレームの前記階調信号とを考慮して、前記第2フレームの前記第2補正階調信号が前記第2フレームの前記補正階調信号として出力される段階と、

を有する、

請求項52に記載の駆動方法。

**【請求項54】**

前記第1階調はブラック階調であり、

前記第2階調はホワイト階調である、

請求項53に記載の駆動方法。

**【請求項55】**

前記段階(b)は、

(b-21) 前記第1フレームの前記階調信号と前記第2フレームの前記階調信号とを考慮して、前記第2フレームの第1補正階調信号が生成されて出力される段階と、

(b-41) 前記第3フレームの前記階調信号が入力され、前記第2フレームの前記第1補正階調信号が抽出される段階と、

(b-42) 前記第1電圧に対する前記第2フレームの電圧の変化量が前記第1電圧に対する前記第2電圧の変化量よりも大きくなるように生成されることである補正処理の存否を示す履歴情報に対応する信号が前記第2フレームの前記第1補正階調信号から抽出されて、前記履歴情報に対応する信号に基づいて前記補正処理の存否が判断される段階と、

(b-43) 前記段階(b-42)で前記補正処理が存在しないと判断される場合に、前記第3フレームの前記第1補正階調信号の前記履歴情報に対応する信号が活性化される段階と、

(b-44) 前記段階(b-42)で前記補正処理が存在すると判断される場合に、前記第3フレームの前記第1補正階調信号の前記履歴情報に対応する信号が非活性化される段階と、

を有する、

請求項46に記載の駆動方法。

**【請求項56】**

前記履歴情報に対応する信号は、前記補正処理の可否に関する情報を含む、

請求項55に記載の駆動方法。

**【請求項57】**

前記段階(b-43)で前記補正処理が存在しないと判断される場合に、前記第2フレームの前記第1補正階調信号に前記補正処理が行われずに、前記第2フレームの前記第2フレームの第2補正階調信号が前記第2フレームの前記補正階調信号として生成されて出力される、

請求項55記載の駆動方法。

**【請求項58】**

前記段階(b-44)で前記補正処理が存在すると判断される場合に、前記第2フレームの前記第1補正階調信号に前記補正処理が行われて、前記第2フレームの前記第1補正階調信号と前記第3フレームの前記階調信号とを考慮して、前記第2フレームの第2補正階調信号が前記第2フレームの前記補正階調信号として生成されて出力される、

請求項55記載の駆動方法。

**【請求項59】**

複数の走査ラインと、前記走査ラインと絶縁されて交差する複数のデータラインと、前記走査ライン及び前記データラインにより囲まれる領域に形成されそれぞれ前記走査ライン及び前記データラインに連結された複数のスイッチング素子と、前記スイッチング素子により制御されマトリックス型で配列された複数の画素とを有する表示パネルが駆動される駆動方法であって、

(a) 前記走査ラインに走査信号が順次的に供給される段階と、

(d) 前記階調信号に対応するフル階調の輝度をダウンさせる処理である輝度低減処理

10

20

30

40

50

が行われ、第1フレームの前記輝度低減処理された前記階調信号と、前記第1フレームの次のフレームである第2フレームの前記輝度低減処理された前記階調信号とを考慮して、前記補正階調信号が生成されて出力される段階と、

(c) 前記補正階調信号に基づいて、画像信号が生成されて前記データラインに供給される段階と、

を備えた、

駆動方法。

#### 【請求項 6 0】

前記段階(d)では、

前記輝度低減処理された前記階調信号のレベルが前記フル階調のレベルより小さい場合に前記第1フレームの前記階調信号と前記第2フレームの前記階調信号とを考慮して前記補正階調信号が出力され、前記輝度低減処理された前記階調信号のレベルがフル階調のレベルである場合にオーバーシュート電圧を発生するように前記補正階調信号が出力される、

請求項59記載の駆動方法。

10

20

30

40

50

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は表示装置、駆動装置及び駆動方法に関する。

##### 【背景技術】

##### 【0002】

一般に、液晶表示装置は2つの基板の間に注入されている異方性誘電率を有する液晶物質に電界を印加し、電界の強さを調節して基板に透過される光の量を調節することで所望する画像信号を得る表示装置である。このような液晶表示装置は携帯が便利なプレートパネル型ディスプレーの中で代表的なもので、その中でも薄膜トランジスターをスイッチング素子として用いた液晶表示装置が主に利用されている。

##### 【0003】

最近では、液晶表示装置が、コンピュータ用モニターだけではなくテレビまでその領域を拡大して使用されるようになり、動画像を表示することが増えてきている。

##### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0004】

しかし、従来の液晶表示装置は、動画像を表示する際に応答速度が十分でないことがある。このような応答速度の問題を改善するために、従来の技術では、OCB(Optic al l y Compensated Band)モードが使用されるか、強誘電性液晶物質FLCを使用する液晶表示装置が使用されることがある。ところが、このようにOCBモードやFLCが使用される場合には、液晶表示装置のパネル構造を大幅に変えなければならないことがある。

##### 【0005】

そこで、本発明の課題は、パネル構造を大幅に変えることなく応答速度を高速化することができる表示装置、駆動装置及び駆動方法を提供することにある。

##### 【課題を解決するための手段】

##### 【0006】

第1発明に係る表示装置は、階調信号補正部とデータドライバーと走査ドライバーと表示パネルとを備える。階調信号補正部は、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。データドライバーは、補正階調信号に基づいて、画像信号を生成して供給する。走査ドライバーは、走査信号を順次的に供給する。表示パネルには、データドライバーから画像信号が供給されるとともに、走査ドライバーから走査信号が供給される。表示パネルは、複数の走査ラインと複数のデータライン

と複数のスイッチング素子と複数の画素とを有する。走査ラインは、走査信号を伝達する。データラインは、画像信号を伝達する。スイッチング素子は、走査ライン及びデータラインにより囲まれた領域に形成される。スイッチング素子は、走査ライン及びデータラインにそれぞれ連結されている。画素は、スイッチング素子により制御され、マトリックス状に配列されている。階調信号補正部は、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。第2フレームは、第1フレームの次のフレームである。第3フレームは、第2フレームの次のフレームである。

#### 【0007】

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。走査ドライバーが、走査信号を順次的に供給する。データドライバーが、補正階調信号に基づいて、画像信号を生成して供給する。表示パネルに、データドライバーから画像信号が供給されるとともに、走査ドライバーから走査信号が供給される。表示パネルの走査ラインが、走査信号を伝達する。表示パネルのデータラインが、画像信号を伝達する。表示パネルのスイッチング素子が、走査ラインに連結されており、走査ライン経由で走査信号を受けてON/OFFされ得る。表示パネルのスイッチング素子が、データラインに連結されており、ONされた際にデータライン経由で画像信号が供給されることにより画素を制御することができる。

10

20

#### 【0008】

したがって、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して第2フレームの補正階調信号を生成して出力するので、階調信号の変化を考慮して画素を制御することができる。このため、パネル構造を大幅に変えることなく応答速度を高速化することができる。

第2発明に係る表示装置は、第1発明の表示装置であって、補正階調信号は、階調信号に対して1フレームの期間だけ遅れて出力される。

#### 【0009】

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。補正階調信号が、階調信号に対して1フレームの期間だけ遅れて出力される。

30

#### 【0010】

したがって、第3フレームの階調信号が階調信号補正部に受信される期間に第2フレームの補正階調信号を生成して出力することができるので、第1フレームの階調信号と第2フレームの階調信号とだけでなく第3フレームの階調信号も考慮して第2フレームの補正階調信号を生成することができる。

第3発明に係る表示装置は、第1発明の表示装置であって、階調信号補正部は、第1電圧と第2電圧とが相異する場合、第3フレームの階調信号が受信される期間において、第1電圧に対する第2フレームの補正階調信号の電圧の変化量が第1電圧に対する第2電圧の変化量よりも大きくなるように、第2フレームの補正階調信号を生成して出力する。第1電圧は、第1フレームの階調信号の電圧である。第2電圧は、第2フレームの階調信号の電圧である。

40

#### 【0011】

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。階調信号補正部が、第1電圧と第2電圧とが相異する場合、第3フレームの階調信号が受信される期間において、第1電圧に対する第2フレ

50

ームの補正階調信号の電圧の変化量が第1電圧に対する第2電圧の変化量よりも大きくなるように、第2フレームの補正階調信号を生成して出力する。

【0012】

したがって、第1フレームから第2フレームにかけて階調信号に対する電圧が変化する場合でも、第2フレームの補正階調信号により画素に十分な電圧が印可されるようになることができる。

第4発明に係る表示装置は、第3発明の表示装置であって、階調信号補正部は、第1フレームの階調信号の電圧が第1低階調信号電圧であり第2フレームの階調信号の電圧が第1低階調信号電圧より高い電圧である第1高階調信号電圧である場合、第2フレームの階調信号が受信される期間において、第2高階調信号電圧になるように第1フレームの補正階調信号を生成して出力する。第2高階調信号電圧は、第1低階調信号電圧より高く、第1高階調信号電圧より低い電圧である。

10

【0013】

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。階調信号補正部が、第1電圧と第2電圧とが相異する場合、第3フレームの階調信号が受信される期間において、第1電圧に対する第2フレームの補正階調信号の電圧の変化量が第1電圧に対する第2電圧の変化量よりも大きくなるように、第2フレームの補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号の電圧が第1低階調信号電圧であり第2フレームの階調信号の電圧が第1低階調信号電圧より高い電圧である第1高階調信号電圧である場合、第2フレームの階調信号が受信される期間において、第2高階調信号電圧になるように第1フレームの補正階調信号を生成して出力する。

20

【0014】

したがって、第1フレームから第2フレームにかけて階調信号に対する電圧が変化する場合でも、第1高階調信号電圧が画素に印可される前に、第1フレームの補正階調信号により、第2高階調信号電圧を画素に印可することができる。このため、画素の応答速度を高速化することができる。

第5発明に係る表示装置は、第4発明の表示装置であって、第1低階調信号電圧はブラック階調信号の電圧である。

30

【0015】

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。階調信号補正部が、第1電圧と第2電圧とが相異する場合、第3フレームの階調信号が受信される期間において、第1電圧に対する第2フレームの補正階調信号の電圧の変化量が第1電圧に対する第2電圧の変化量よりも大きくなるように、第2フレームの補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号の電圧が第1低階調信号電圧であり第2フレームの階調信号の電圧が第1低階調信号電圧より高い電圧である第1高階調信号電圧である場合、第2フレームの階調信号が受信される期間において、第2高階調信号電圧になるように第1フレームの補正階調信号を生成して出力する。第1低階調信号電圧がブラック階調信号の電圧である。

40

【0016】

したがって、ブラック階調信号の電圧から第2フレームの階調信号に対する電圧へ変化する場合でも、第1高階調信号電圧が画素に印可される前に、第1フレームの補正階調信号により、第2高階調信号電圧を画素に印可することができる。このため、画素の応答速度を高速化することができる。

第6発明に係る表示装置は、第5発明の表示装置であって、画素は、液晶を含む。第2高階調信号電圧になるように生成された補正階調信号は、液晶をプリチルト(p r e - t

50

i l t ) させるためのプリチルト形成信号である。

【 0 0 1 7 】

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。階調信号補正部が、第1電圧と第2電圧とが相異する場合、第3フレームの階調信号が受信される期間において、第1電圧に対する第2フレームの補正階調信号の電圧の変化量が第1電圧に対する第2電圧の変化量よりも大きくなるように、第2フレームの補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号の電圧が第1低階調信号電圧であり第2フレームの階調信号の電圧が第1低階調信号電圧より高い電圧である第1高階調信号電圧である場合、第2フレームの階調信号が受信される期間において、第2高階調信号電圧になるように第1フレームの補正階調信号を生成して出力する。第1低階調信号電圧がブラック階調信号の電圧である。第2高階調信号電圧になるように生成された補正階調信号が、液晶をプリチルト ( p r e - t i l t ) させるためのプリチルト形成信号である。

【 0 0 1 8 】

したがって、ブラック階調信号の電圧から第2フレームの階調信号に対する電圧へ変化する場合でも、第1高階調信号電圧が画素に印可される前に、第1フレームの補正階調信号により、第2高階調信号電圧を画素に印可して液晶をプリチルト ( p r e - t i l t ) させることができる。このため、画素の応答速度を高速化することができる。

第7発明に係る表示装置は、第6発明の表示装置であって、表示パネルは、画素電極と共通電極とをさらに有する。画素電極は、スイッチング素子を経由してデータラインから画素信号の供給を受ける。共通電極は、画素電極との間で液晶に電圧を印加する。階調信号の電圧又は補正階調信号の電圧は、共通電極に対する画素電極の電圧である。ブラック階調信号の電圧は、0 . 5 ~ 1 . 5 ボルトのうちいずれかの電圧である。プリチルト形成信号の電圧は、2 ~ 3 . 5 ボルトのうちいずれかの電圧である。

【 0 0 1 9 】

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。階調信号補正部が、第1電圧と第2電圧とが相異する場合、第3フレームの階調信号が受信される期間において、第1電圧に対する第2フレームの補正階調信号の電圧の変化量が第1電圧に対する第2電圧の変化量よりも大きくなるように、第2フレームの補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号の電圧が第1低階調信号電圧であり第2フレームの階調信号の電圧が第1低階調信号電圧より高い電圧である第1高階調信号電圧である場合、第2フレームの階調信号が受信される期間において、第2高階調信号電圧になるように第1フレームの補正階調信号を生成して出力する。第1低階調信号電圧がブラック階調信号の電圧である。第2高階調信号電圧になるように生成された補正階調信号が、液晶をプリチルト ( p r e - t i l t ) させるためのプリチルト形成信号である。走査ドライバーが、走査信号を順次的に供給する。データドライバーが、補正階調信号に基づいて、画像信号を生成して供給する。表示パネルに、データドライバーから画像信号が供給されるとともに、走査ドライバーから走査信号が供給される。表示パネルの走査ラインが、走査信号を伝達する。表示パネルのデータラインが、画像信号を伝達する。表示パネルのスイッチング素子が、走査ラインに連結されており、走査ライン経由で走査信号を受けてON / OFF され得る。表示パネルの画素電極が、スイッチング素子を経由してデータラインから画素信号の供給を受ける。共通電極が、画素電極との間で液晶に電圧を印加する。階調信号の電圧又は補正階調信号の電圧が、共通電極に対する画素電極の電圧である。ブラック階調信号の電圧が、0 . 5 ~ 1 . 5 ボルトのうちいずれかの電圧である。プリチルト形成信号の電圧が、2 ~ 3 . 5 ボルトのうちいずれかの電圧である。

10

20

30

40

50

**【 0 0 2 0 】**

したがって、ブラック階調信号の電圧から第2フレームの階調信号に対する電圧へ変化する場合でも、第1高階調信号電圧が画素電極と共通電極により画素に印可される前に、第1フレームの補正階調信号により、第2高階調信号電圧を画素電極と共通電極により画素に印可して液晶をプリチルト（pre-tilet）させることができる。このため、画素の応答速度を高速化することができる。

**【 0 0 2 1 】**

第8発明に係る表示装置は、第1発明の表示装置であって、階調信号及び補正階調信号は、デジタル階調の信号である。

この表示装置では、階調信号及び補正階調信号が、デジタル階調の信号である。階調信号補正部が、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。走査ドライバーが、走査信号を順次的に供給する。データドライバーが、補正階調信号に基づいて、画像信号を生成して供給する。表示パネルに、データドライバーから画像信号が供給されるとともに、走査ドライバーから走査信号が供給される。表示パネルの走査ラインが、走査信号を伝達する。表示パネルのデータラインが、画像信号を伝達する。表示パネルのスイッチング素子が、走査ラインに連結されており、走査ライン経由で走査信号を受けてON/OFFされ得る。表示パネルのスイッチング素子が、データラインに連結されており、ONされた際にデータライン経由で画像信号が供給されることにより画素を制御することができる。

**【 0 0 2 2 】**

したがって、階調信号及び補正階調信号がデジタル階調の信号であるので、階調信号に基づいて補正階調信号を生成することが容易である。また、補正階調信号により画素に印可される電圧を制御することが容易である。

第9発明に係る表示装置は、第8発明の表示装置であって、階調信号補正部は、並列変換部と直列変換部とをさらに有する。並列変換部は、階調信号に対応するデジタル階調の信号を並列変換する。直列変換部は、並列変換部が並列変換した階調信号を直列変換する。直列変換部は、補正階調信号に対応するデジタル階調の信号をデータドライバーに出力する。

**【 0 0 2 3 】**

この表示装置では、階調信号及び補正階調信号が、デジタル階調の信号である。階調信号補正部が、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。階調信号補正部の並列変換部が、階調信号に対応するデジタル階調の信号を並列変換する。これにより、並列変換部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを、並列に出力することができる。階調信号補正部の直列変換部が、並列変換部が並列変換した階調信号を直列変換する。階調信号補正部の直列変換部が、補正階調信号に対応するデジタル階調の信号をデータドライバーに出力する。これにより、階調信号補正部の直列変換部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力することができる。

**【 0 0 2 4 】**

したがって、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とが直列に入力されても、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力することができる。

第10発明に係る表示装置は、第1発明の表示装置であって、階調信号及び補正階調信号は、アナログ階調の信号である。

**【 0 0 2 5 】**

この表示装置では、階調信号及び補正階調信号が、アナログ階調の信号である。階調信号補正部が、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。

10

20

30

40

50

号補正部が、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。走査ドライバーが、走査信号を順次的に供給する。データドライバーが、補正階調信号に基づいて、画像信号を生成して供給する。表示パネルに、データドライバーから画像信号が供給されるとともに、走査ドライバーから走査信号が供給される。表示パネルの走査ラインが、走査信号を伝達する。表示パネルのデータラインが、画像信号を伝達する。表示パネルのスイッチング素子が、走査ラインに連結されており、走査ライン経由で走査信号を受けてON/OFFされ得る。表示パネルのスイッチング素子が、データラインに連結されており、ONされた際にデータライン経由で画像信号が供給されることにより画素を制御することができる。

10

#### 【0026】

したがって、階調信号及び補正階調信号がアナログ階調の信号であるので、データドライバーで補正階調信号が増幅されることにより広い範囲の階調を実現することができる。

第11発明に係る表示装置は、第10発明の表示装置であって、階調信号補正部は、合成器と、分離器とを有する。合成器は、階調信号に対応するアナログ階調の信号の周波数を、処理可能な周波数に変換する。分離器は、補正階調信号に対応するアナログ階調の信号を分離して、データドライバーに出力する。

#### 【0027】

この表示装置では、階調信号及び補正階調信号が、アナログ階調の信号である。階調信号補正部が、階調信号ソースから階調信号を受信する。階調信号補正部の合成器が、階調信号に対応するアナログ階調の信号の周波数を、処理可能な周波数に変換する。階調信号補正部が、階調信号に基づいて補正階調信号を生成する。階調信号補正部の分離器が、補正階調信号に対応するアナログ階調の信号を分離して、データドライバーに出力する。階調信号補正部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。走査ドライバーが、走査信号を順次的に供給する。データドライバーが、補正階調信号に基づいて、画像信号を生成して供給する。表示パネルに、データドライバーから画像信号が供給されるとともに、走査ドライバーから走査信号が供給される。表示パネルの走査ラインが、走査信号を伝達する。表示パネルのデータラインが、画像信号を伝達する。表示パネルのスイッチング素子が、走査ラインに連結されており、走査ライン経由で走査信号を受けてON/OFFされ得る。表示パネルのスイッチング素子が、データラインに連結されており、ONされた際にデータライン経由で画像信号が供給されることにより画素を制御することができる。

20

30

#### 【0028】

したがって、階調信号の処理可能な周波数に変換して階調信号を補正後に周波数を元に戻すことができるので、階調信号補正部の処理可能な周波数と階調信号に同期している周波数とが異なる場合でも、階調信号に基づいて補正階調信号を生成して出力することができる。

第12発明に係る表示装置は、第1発明の表示装置であって、階調信号補正部は、第1メモリと第2メモリとコントローラと階調信号変換部とを有する。第1メモリは、受信された階調信号を所定フレームの期間だけ保存して出力する。第2メモリは、階調信号を第1メモリから受け取る。第2メモリは、さらに所定フレームの期間だけ階調信号を保存して出力する。コントローラは、第1読出動作と第2読出動作と第1書込動作と第2書込動作とを制御する。第1読出動作は、第1メモリから階調信号を読み出すことである。第2読出動作は、第2メモリから階調信号を読み出すことである。第1書込動作は、第1メモリへ階調信号を書き込むことである。第2書込動作は、第2メモリへ階調信号を書き込むことである。階調信号変換部は、第2メモリが出力した第1フレームの階調信号と、第1メモリが出力した第2フレームの階調信号と、受信された第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。

40

50

**【 0 0 2 9 】**

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信する。階調信号補正部の第1メモリが、受信された階調信号を所定フレームの期間だけ保存して出力する。第2メモリが、階調信号を第1メモリから受け取る。第2メモリが、さらに所定フレームの期間だけ階調信号を保存して出力する。コントローラが、第1読出動作と第2読出動作と第1書き動作と第2書き動作とを制御する。階調信号変換部が、第1フレームの階調信号を第2メモリから受け取ることができる。階調信号変換部が、第2フレームの階調信号を第1メモリから受け取ることができる。階調信号変換部が、受信された第3フレームの階調信号を受け取ることができる。階調信号変換部が、第2メモリが出力した第1フレームの階調信号と、第1メモリが出力した第2フレームの階調信号と、受信された第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。

10

**【 0 0 3 0 】**

したがって、第1メモリで所定フレームの期間だけ保存され、第2メモリさらに所定フレームの期間だけ保存されるので、階調信号変換部が第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを受け取ることができる。このため、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して第2フレームの補正階調信号を生成して出力することができる。

**【 0 0 3 1 】**

第13発明に係る表示装置は、第12発明の表示装置であって、所定フレームの期間は、1フレームの期間である。

20

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信する。階調信号補正部の第1メモリが、受信された階調信号を所定フレームの期間だけ保存して出力する。ここで、所定フレームの期間が、1フレームの期間である。第2メモリが、階調信号を第1メモリから受け取る。第2メモリが、さらに所定フレームの期間だけ階調信号を保存して出力する。コントローラが、第1読出動作と第2読出動作と第1書き動作と第2書き動作とを制御する。階調信号変換部が、第1フレームの階調信号を第2メモリから受け取ることができる。階調信号変換部が、第2フレームの階調信号を第1メモリから受け取ることができる。階調信号変換部が、受信された第3フレームの階調信号を受け取ることができます。階調信号変換部が、第2メモリが出力した第1フレームの階調信号と、第1メモリが出力した第2フレームの階調信号と、受信された第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。

30

**【 0 0 3 2 】**

したがって、所定フレームの期間が1フレームの期間であるので、第1メモリで1フレームの期間だけ保存され、第2メモリさらに1フレームの期間だけ保存されるため、階調信号変換部が第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを受け取ることができます。このため、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して第2フレームの補正階調信号を生成して出力することができる。

**【 0 0 3 3 】**

第14発明に係る表示装置は、第12発明の表示装置であって、第1読出動作、第2読出動作、第1書き動作及び第2書き動作に同期されるクロック周波数は、階調信号補正部に供給されるクロック周波数と同一である。

40

この表示装置では、コントローラが、第1読出動作と第2読出動作と第1書き動作と第2書き動作とを制御する。第1読出動作、第2読出動作、第1書き動作及び第2書き動作に同期されるクロック周波数が、階調信号補正部に供給されるクロック周波数と同一である。

**【 0 0 3 4 】**

したがって、第1読出動作、第2読出動作、第1書き動作及び第2書き動作に同期されるクロック周波数が階調信号補正部に供給されるクロック周波数と同一であるので、コントローラに供給されるクロック周波数を階調信号補正部に供給されるクロック周波数と同

50

ーすることができる。このため、階調信号補正部に供給されるクロック信号をそのままコントローラに供給することができる。

#### 【0035】

第15発明に係る表示装置は、請求項12に記載の表示装置であって、第1読出動作、第2読出動作、第1書込動作及び第2書込動作の少なくとも1つに同期されるクロック周波数は、階調信号補正部に供給されるクロック周波数を正の整数で割った値である。

この表示装置では、コントローラが、第1読出動作と第2読出動作と第1書込動作と第2書込動作とを制御する。第1読出動作、第2読出動作、第1書込動作及び第2書込動作に同期されるクロック周波数が、階調信号補正部に供給されるクロック周波数を正の整数で割った値である。これにより、階調信号補正部に供給されるクロック信号を簡易に周波数変換してコントローラに供給することができる。あるいは、階調信号補正部に供給されるクロック信号をそのままコントローラに供給してコントローラにおいて簡易に周波数変換することができる。

#### 【0036】

したがって、第1読出動作、第2読出動作、第1書込動作及び第2書込動作に同期されるクロック周波数が階調信号補正部に供給されるクロック周波数を正の整数で割った値であるので、簡易な周波数変換をするだけで、第1読出動作、第2読出動作、第1書込動作及び第2書込動作を制御することができる。

第16発明に係る表示装置は、第15発明の表示装置であって、階調信号補正部は、合成器と、分離器とをさらに有する。合成器は、階調信号に対応するアナログ階調の信号の周波数を、処理可能な周波数に変換する。分離器は、補正階調信号に対応するアナログ階調の信号を分離してデータドライバーに出力する。

#### 【0037】

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信する。階調信号補正部の合成器が、受信した階調信号を受け取ることができる。階調信号補正部の合成器が、階調信号に対応するアナログ階調の信号の周波数を、処理可能な周波数に変換する。階調信号補正部の第1メモリが、受信され変換された階調信号を所定フレームの期間だけ保存して出力する。ここで、所定フレームの期間が、1フレームの期間である。第2メモリが、階調信号を第1メモリから受け取る。第2メモリが、さらに所定フレームの期間だけ階調信号を保存して出力する。コントローラが、第1読出動作と第2読出動作と第1書込動作と第2書込動作とを制御する。第1読出動作、第2読出動作、第1書込動作及び第2書込動作に同期されるクロック周波数が、階調信号補正部に供給されるクロック周波数を正の整数で割った値である。階調信号変換部が、第1フレームの階調信号を第2メモリから受け取ることができる。階調信号変換部が、第2フレームの階調信号を第1メモリから受け取ることができる。階調信号変換部が、受信された第3フレームの階調信号を受け取ることができる。階調信号変換部が、第2メモリが出力した第1フレームの階調信号と、第1メモリが出力した第2フレームの階調信号と、受信された第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。階調信号補正部の分離器が、階調信号変換部が出力した第2フレームの補正階調信号を受け取ることができる。階調信号補正部の分離器が、補正階調信号に対応するアナログ階調の信号を分離してデータドライバーに出力する。

#### 【0038】

したがって、第1読出動作、第2読出動作、第1書込動作及び第2書込動作に同期されるクロック周波数を階調信号補正部において階調信号及び補正階調信号に同期される周波数に一致させることができる。このため、第1読出動作、第2読出動作、第1書込動作及び第2書込動作に同期されるクロック周波数が階調信号補正部以外において階調信号及び補正階調信号に同期される周波数と異なる場合であっても、第1読出動作、第2読出動作、第1書込動作及び第2書込動作を行わせることができる。

#### 【0039】

第17発明に係る表示装置は、第1発明の表示装置であって、階調信号補正部は、メモ

10

20

30

40

50

リとコントローラと階調信号変換部とを有する。メモリは、受信された階調信号を所定フレームの期間だけ保存して出力する。コントローラは、読み動作と書き動作とを制御する。読み動作は、メモリから階調信号を読み出すことである。書き動作は、メモリへ階調信号を書き込むことである。階調信号変換部は、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。

#### 【0040】

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信する。階調信号補正部のメモリが、受信された階調信号を所定フレームの期間だけ保存して出力する。コントローラが、読み動作と書き動作とを制御する。階調信号補正部の階調信号変換部が、第1フレームの階調信号を考慮した信号である第1フレームの第1補正階調信号をメモリから受け取ることができる。階調信号補正部の階調信号変換部が、受信された第2フレームの階調信号を受け取ることができる。階調信号補正部の階調信号変換部が、第1フレームの階調信号と第2フレームの階調信号とを考慮して第2フレームの第1補正階調信号を生成してメモリに出力することができる。階調信号補正部のメモリが、第2フレームの第1補正階調信号を所定フレームの期間だけ保存して階調信号変換部へ出力することができる。階調信号補正部の階調信号変換部が、メモリから第2フレームの第1補正階調信号を受け取ることができる。階調信号補正部の階調信号変換部が、受信された第3フレームの階調信号を受け取ることができる。階調信号補正部の階調信号変換部が、第2フレームの第1補正階調信号と第3フレームの階調信号とを考慮して、第2フレームの第2補正階調信号を第2フレームの補正階調信号として生成して出力することができる。これにより、階調信号補正部の階調信号変換部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。

#### 【0041】

したがって、メモリで所定フレームの期間だけ保存され、第1フレームの階調信号と第2フレームの階調信号とを考慮して第2フレームの第1補正階調信号が生成され得るので、階調信号変換部が第2フレームの第1補正階調信号と第3フレームの階調信号とを受け取ることができる。このため、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して第2フレームの補正階調信号を生成して出力することができる。

#### 【0042】

第18発明に係る表示装置は、第17発明の表示装置であって、所定フレームの期間は、1フレームの期間である。

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信する。階調信号補正部のメモリが、受信された階調信号を所定フレームの期間だけ保存して出力する。ここで、所定フレームの期間が、1フレームの期間である。コントローラが、読み動作と書き動作とを制御する。階調信号補正部の階調信号変換部が、第1フレームの階調信号を第2メモリから受け取ることができる。階調信号補正部の階調信号変換部が、受信された第2フレームの階調信号を受け取ることができる。階調信号補正部の階調信号変換部が、第1フレームの階調信号と第2フレームの階調信号とを考慮して第2フレームの第1補正階調信号を生成してメモリに出力することができる。階調信号補正部のメモリが、第2フレームの第1補正階調信号を所定フレームの期間だけ保存して階調信号変換部へ出力することができる。階調信号補正部の階調信号変換部が、受信された第3フレームの階調信号を受け取ることができる。階調信号補正部の階調信号変換部が、第2フレームの第1補正階調信号と第3フレームの階調信号とを考慮して、第2フレームの第2補正階調信号を第2フレームの補正階調信号として生成して出力することができる。これにより、階調信号補正部の階調信号変換部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。

#### 【0043】

10

20

30

40

50

したがって、メモリで1フレームの期間だけ保存され、第1フレームの階調信号と第2フレームの階調信号とを考慮して第2フレームの第1補正階調信号が生成され得るので、階調信号変換部が第2フレームの第1補正階調信号と第3フレームの階調信号とを受け取ることができる。このため、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して第2フレームの補正階調信号を生成して出力することができる。

#### 【0044】

第19発明に係る表示装置は、第17発明の表示装置であって、読み動作及び書き動作に同期されるクロック周波数は、階調信号補正部に供給されるクロック周波数と同一である。

10

この表示装置では、コントローラが、第1読み動作と第2読み動作と第1書き動作と第2書き動作とを制御する。第1読み動作、第2読み動作、第1書き動作及び第2書き動作に同期されるクロック周波数が、階調信号補正部に供給されるクロック周波数と同一である。

#### 【0045】

したがって、読み動作及び書き動作に同期されるクロック周波数が階調信号補正部に供給されるクロック周波数と同一であるので、コントローラに供給されるクロック周波数を階調信号補正部に供給されるクロック周波数と同一することができる。このため、階調信号補正部に供給されるクロック信号をそのままコントローラに供給することができる。

第20発明に係る表示装置は、第17発明の表示装置であって、読み動作及び書き動作の少なくとも1つに同期されるクロック周波数は、階調信号補正部に供給されるクロック周波数を正の整数で割った値である。

20

#### 【0046】

この表示装置では、コントローラが、読み動作と書き動作とを制御する。読み動作及び書き動作に同期されるクロック周波数が、階調信号補正部に供給されるクロック周波数を正の整数で割った値である。これにより、階調信号補正部に供給されるクロック信号を簡単に周波数変換してコントローラに供給することができる。あるいは、階調信号補正部に供給されるクロック信号をそのままコントローラに供給してコントローラにおいて簡単に周波数変換することができる。

#### 【0047】

したがって、読み動作及び書き動作に同期されるクロック周波数が階調信号補正部に供給されるクロック周波数を正の整数で割った値であるので、簡単な周波数変換をするだけで、読み動作及び書き動作を制御することができる。

30

第21発明に係る表示装置は、第17発明の表示装置であって、階調信号補正部は、合成器と分離器とをさらに有する。合成器は、階調信号に対応するアナログ階調の信号の周波数を、処理可能な周波数に変換する。分離器は、補正階調信号に対応するアナログ階調の信号を分離してデータドライバーに出力する。

#### 【0048】

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信する。階調信号補正部の合成器が、受信した階調信号を受け取ることができる。階調信号補正部の合成器が、階調信号に対応するアナログ階調の信号の周波数を、処理可能な周波数に変換する。階調信号補正部のメモリが、受信され変換された階調信号を所定フレームの期間だけ保存して出力する。コントローラが、読み動作と書き動作とを制御する。階調信号補正部の階調信号変換部が、第1フレームの階調信号を第2メモリから受け取ることができる。階調信号補正部の階調信号変換部が、受信された第2フレームの階調信号を受け取ることができる。階調信号補正部の階調信号変換部が、第1フレームの階調信号と第2フレームの階調信号とを考慮して第2フレームの第1補正階調信号を生成してメモリに出力することができる。階調信号補正部のメモリが、第2フレームの第1補正階調信号を所定フレームの期間だけ保存して階調信号変換部へ出力することができる。階調信号補正部の階調信号変換部が、受信された第3フレームの階調信号を受け取ることができる。階調信号補正

40

部の階調信号変換部が、第2フレームの第1補正階調信号と第3フレームの階調信号とを考慮して、第2フレームの第2補正階調信号を第2フレームの補正階調信号として生成して出力することができる。これにより、階調信号補正部の階調信号変換部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。階調信号補正部の分離器が、階調信号変換部が出力した第2フレームの補正階調信号を受け取ることができる。階調信号補正部の分離器が、補正階調信号に対応するアナログ階調の信号を分離してデータドライバーに出力する。

#### 【0049】

したがって、読み動作及び書き動作に同期されるクロック周波数を階調信号補正部において階調信号及び補正階調信号に同期される周波数に一致させることができ。このため、読み動作及び書き動作に同期されるクロック周波数が階調信号補正部以外において階調信号及び補正階調信号に同期される周波数と異なる場合であっても、読み動作及び書き動作を行わせることができる。10

#### 【0050】

第22発明に係る表示装置は、第1発明の表示装置であって、画素は、液晶を含む。表示パネルは、垂直配向モード、パターン化された垂直配向モード、多重ドメイン垂直配向モードのうちいずれかを採用する。

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。走査ドライバーが、走査信号を順次的に供給する。データドライバーが、補正階調信号に基づいて、画像信号を生成して供給する。表示パネルに、データドライバーから画像信号が供給されるとともに、走査ドライバーから走査信号が供給される。表示パネルの走査ラインが、走査信号を伝達する。表示パネルのデータラインが、画像信号を伝達する。表示パネルのスイッチング素子が、走査ラインに連結されており、走査ライン経由で走査信号を受けてON/OFFされ得る。表示パネルのスイッチング素子が、データラインに連結されており、ONされた際にデータライン経由で画像信号が供給されることにより画素を制御することができる。画素が、液晶を含む。表示パネルが、垂直配向モード、パターン化された垂直配向モード、多重ドメイン垂直配向モードのうちいずれかを採用する。20

#### 【0051】

したがって、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して第2フレームの補正階調信号を生成して出力するので、表示パネルが垂直配向モード、パターン化された垂直配向モード、多重ドメイン垂直配向モードのうちいずれかを採用する場合でも、画素の応答速度を高速化することができる。30

第23発明に係る表示装置は、第3発明の表示装置であって、階調信号補正部は、第2フレームの階調信号の電圧と第3フレームの階調信号の電圧とが同じ場合、第4フレームの階調信号が受信される期間において、第3フレームの補正階調信号の電圧が第3フレームの階調信号の電圧と同じになるように、第3フレームの補正階調信号を生成して出力する。第4フレームは、第3フレームの次のフレームである。40

#### 【0052】

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。階調信号補正部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。階調信号補正部が、第1電圧と第2電圧とが相異する場合、第3フレームの階調信号が受信される期間において、第1電圧に対する第2フレームの補正階調信号の電圧の変化量が第1電圧に対する第2電圧の変化量よりも大きくなるように、第2フレームの補正階調信号を生成して出力する。階調信号補正部が、第2フレームの階調信号の電圧と第3フレームの階調信号の電圧とが同じ場合、第4フレームの50

階調信号が受信される期間において、第3フレームの補正階調信号の電圧が第3フレームの階調信号の電圧と同じになるように、第3フレームの補正階調信号を生成して出力する。

#### 【0053】

したがって、第1電圧に対する第2フレームの補正階調信号の電圧の変化量が第1電圧に対する第2電圧の変化量よりも大きくなるように第2フレームの補正階調信号を生成して出力する後に、第3フレーム以降の補正階調信号の電圧が第3フレーム以降の階調信号の電圧に対して変動して表示パネルの表示の品質が低下することを低減することができる。

#### 【0054】

第24発明に係る表示装置は、第1発明の表示装置であって、階調信号補正部は、階調信号変換部とメモリとコントローラとを有する。階調信号変換部は、第1フレームの階調信号と第2フレームの階調信号とを考慮して、第2フレームの第1補正階調信号を生成して出力する。メモリは、第2フレームの第1補正階調信号を階調信号変換部から受け取る。メモリは、所定フレームの期間だけ第2フレームの第1補正階調信号を保存して出力する。階調信号変換部には、第3フレームの階調信号が入力される。階調信号変換部は、メモリから第2フレームの第1補正階調信号を受け取る。階調信号変換部は、第2フレームの第1補正階調信号と第3フレームの階調信号とを考慮して、第2フレームの第2補正階調信号を第2フレームの補正階調信号として生成して出力する。コントローラは、補正読出動作と補正書込動作とを制御する。補正読出動作は、メモリから第2フレームの第1補正階調信号を読み出すことである。補正書込動作は、メモリへ第2フレームの第1補正階調信号を書き込むことである。

10

#### 【0055】

この表示装置では、階調信号補正部が、階調信号ソースから階調信号を受信する。階調信号補正部のメモリが、受信された階調信号を所定フレームの期間だけ保存して出力する。コントローラが、補正読出動作と補正書込動作とを制御する。階調信号補正部の階調信号変換部が、第1フレームの階調信号を考慮した信号である第1フレームの第1補正階調信号をメモリから受け取ることができる。階調信号補正部の階調信号変換部が、受信された第2フレームの階調信号を受け取ることができる。階調信号補正部の階調信号変換部が、第1フレームの階調信号と第2フレームの階調信号とを考慮して、第2フレームの第1補正階調信号を生成して出力する。階調信号補正部のメモリが、第2フレームの第1補正階調信号を階調信号変換部から受け取る。階調信号補正部のメモリが、所定フレームの期間だけ第2フレームの第1補正階調信号を保存して出力する。階調信号補正部の階調信号変換部が、メモリから第2フレームの第1補正階調信号を受け取る。階調信号補正部の階調信号変換部に、第3フレームの階調信号が入力される。階調信号補正部の階調信号変換部が、第2フレームの第1補正階調信号と第3フレームの階調信号とを考慮して、第2フレームの第2補正階調信号を第2フレームの補正階調信号として生成して出力する。これにより、階調信号補正部の階調信号変換部が、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。

20

30

40

#### 【0056】

したがって、メモリで所定フレームの期間だけ保存され、第1フレームの階調信号と第2フレームの階調信号とを考慮して第2フレームの第1補正階調信号が生成され得るので、階調信号変換部が第2フレームの第1補正階調信号と第3フレームの階調信号とを受け取ることができる。このため、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して第2フレームの補正階調信号を生成して出力することができる。

#### 【0057】

第25発明に係る表示装置は、第24発明の表示装置であって、第2フレームの第1補正階調信号は、階調信号情報と履歴情報とを含む。階調信号情報は、階調信号に関する情

50

報である。履歴情報は、補正処理の存否を示す。補正処理は、第1電圧に対する第2フレームの電圧の変化量が第1電圧に対する第2電圧の変化量よりも大きくなるように生成されることである。

#### 【0058】

この表示装置では、階調信号補正部の階調信号変換部が、第1フレームの階調信号と第2フレームの階調信号とを考慮して、第2フレームの第1補正階調信号を生成して出力する。第2フレームの第1補正階調信号が、階調信号情報と履歴情報とを含む。

したがって、第2フレームの第1補正階調信号が階調信号情報と履歴情報とを含むので、第2フレームの第1補正階調信号を第1フレームの階調信号と第2フレームの階調信号とを考慮したものとすることができる。

10

#### 【0059】

第26発明に係る表示装置は、第25発明の表示装置であって、階調信号変換部は、第2フレームの第1補正階調信号を生成するとき、階調信号情報において補正処理が存在している場合に履歴情報に対応する信号を活性化させ、階調信号情報において前記補正処理が存在していない場合に前記履歴情報に対応する信号を非活性化させる。

この表示装置では、階調信号補正部の階調信号変換部が、第1フレームの階調信号と第2フレームの階調信号とを考慮して、第2フレームの第1補正階調信号を生成して出力する。第2フレームの第1補正階調信号が、階調信号情報と履歴情報とを含む。階調信号補正部の階調信号変換部が、第2フレームの第1補正階調信号を生成するとき、階調信号情報において補正処理が存在している場合に履歴情報に対応する信号を活性化させ、階調信号情報において前記補正処理が存在していない場合に前記履歴情報に対応する信号を非活性化させる。

20

#### 【0060】

したがって、第3フレーム以降の補正階調信号の電圧が第3フレーム以降の階調信号の電圧に対して変動して表示パネルの表示の品質が低下することを低減することができる。

第27発明に係る表示装置は、第26発明の表示装置であって、階調信号変換部は、第3フレームの第1補正階調信号を生成するとき、第2フレームの第1補正階調信号の履歴情報に対応する信号が活性化されている場合に、第3フレームの第1補正階調信号の前記履歴情報に対応する信号を非活性化させる。

#### 【0061】

第28発明に係る表示装置は、タイミング制御部とデータドライバーと走査ドライバーと表示パネルとを備える。タイミング制御部は、階調信号ソースから階調信号を受信して、階調信号に基づいて補正階調信号を生成して出力する。データドライバーは、補正階調信号に基づいて、画像信号を生成して供給する。走査ドライバーは、走査信号を順次的に供給する。表示パネルは、データドライバーから画像信号が供給されるとともに、走査ドライバーから走査信号が供給される。表示パネルは、複数の走査ラインと複数のデータラインと複数のスイッチング素子と複数の画素とを有する。走査ラインは、走査信号を伝達する。データラインは、画像信号を伝達する。スイッチング素子は、走査ライン及びデータラインにより囲まれた領域に形成され、走査ライン及びデータラインにそれぞれ連結される。画素は、スイッチング素子により制御され、マトリックス状に配列されている。タイミング制御部は、輝度低減処理を行い、第1フレームの輝度低減処理された階調信号と第2フレームの輝度低減処理された階調信号とを考慮して、補正階調信号を生成して出力する。輝度低減処理は、階調信号に対応するフル階調の輝度をダウンさせる処理である。

30

40

第2フレームは、第1フレームの次のフレームである。

#### 【0062】

第29発明に係る表示装置は、第28発明の表示装置であって、タイミング制御部は、輝度低減処理された階調信号のレベルがフル階調のレベルより小さい場合に、第1フレームの前記階調信号と前記第2フレームの前記階調信号とを考慮して、補正階調信号を出力する。タイミング制御部は、輝度低減処理された階調信号のレベルがフル階調のレベルである場合に、オーバーシュート電圧を発生するように補正階調信号を出力する。

50

## 【0063】

第30発明に係る表示装置は、第29発明の表示装置であって、タイミング制御部は、データ変換部と、階調信号補正部とを有する。データ変換部は、階調信号を輝度低減処理して出力する。階調信号補正部は、輝度低減処理された階調信号のレベルがフル階調のレベルより小さい場合に、第1フレームの階調信号と第2フレームの階調信号とを考慮して、補正階調信号を出力する。階調信号補正部は、輝度低減処理された階調信号のレベルがフル階調のレベルである場合に、オーバーシュート電圧を発生するように補正階調信号を出力する。

## 【0064】

第31発明に係る表示装置は、第30発明の表示装置であって、階調信号は、赤色階調信号と緑色階調信号と青色階調信号とを含む。赤色階調信号は、赤色の階調に関する信号である。緑色階調信号は、緑色の階調に関する信号である。青色階調信号は、青色の階調に関する信号である。データ変換部は、RルックアップテーブルとGルックアップテーブルとBルックアップテーブルとを含む。Rルックアップテーブルは、輝度低減処理される前の赤色階調信号のレベルと輝度低減処理された後の赤色階調信号のレベルとを記憶している。Gルックアップテーブルは、輝度低減処理される前の緑色階調信号のレベルと輝度低減処理された後の緑色階調信号のレベルとを記憶している。Bルックアップテーブルは、輝度低減処理される前の青色階調信号のレベルと輝度低減処理された後の青色階調信号のレベルとを記憶している。

## 【0065】

第32発明に係る表示装置は、第31発明の表示装置であって、Rルックアップテーブルの赤色階調信号のレベル、Gルックアップテーブルの緑色階調信号のレベル及びBルックアップテーブルの青色階調信号のレベルは、それぞれ複数存在する。

第33発明に係る表示装置は、第30発明の表示装置であって、データ変換部は、フル階調のレベルが $2^k$ であるkビットの階調信号(kは正の整数)をビット数の拡張によりフル階調のレベルが $2^{k+p}-r$ である( $k+p$ )ビットの階調信号(pは正の整数、rはkより小さい正の整数)に変換する。データ変換部は、フル階調のレベルが $2^{k+p}-r$ である( $k+p$ )ビットの階調信号をフル階調のレベルが $2^k-r$ であるkビットの階調信号に変換する。

## 【0066】

第34発明に係る表示装置は、第33発明の表示装置であって、階調信号補正部は、フル階調のレベルが $2^k-r$ であるkビットの階調信号に対してRルックアップテーブル、Gルックアップテーブル及びBルックアップテーブルを用いて補正階調信号を生成する。階調信号補正部は、残りのr階調データに対してオーバーシュート電圧を発生するように補正階調信号を生成する。

## 【0067】

第35発明に係る表示装置は、第30発明の表示装置であって、データ変換部は、フル階調のレベルが225である8ビットの階調信号をビット数の拡張によりフル階調のレベルが1008である10ビットの前記階調信号に変換する。データ変換部は、フル階調のレベルが1008である10ビットの前記階調信号をフル階調のレベルが252である8ビットの前記階調信号に変換する。

## 【0068】

第36発明に係る表示装置は、第35発明の表示装置であって、階調信号補正部は、フル階調のレベルが252である8ビットの階調信号に対してRルックアップテーブル、Gルックアップテーブル及びBルックアップテーブルを用いて補正階調信号を生成する。階調信号補正部は、残りの3階調データに対してオーバーシュート電圧を発生するように補正階調信号を生成する。

## 【0069】

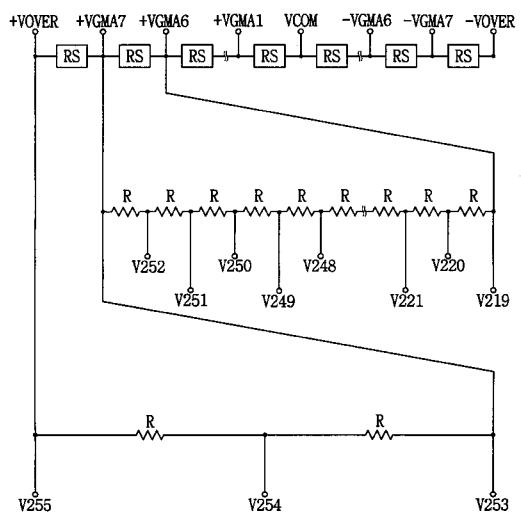

第37発明に係る表示装置は、第28発明の表示装置であって、データドライバーは、DA変換器を有する。DA変換器は、デジタルの信号とアナログの信号とを相互に変換す

10

20

30

40

50

る。D A 変換器は、直列に連結された複数の抵抗素子を含む。複数の抵抗素子の一端にはオーバーシュート基準電圧が印加される。

第38発明に係る駆動装置は、表示パネルを駆動する駆動装置であって、階調信号補正部とデータドライバーと走査ドライバーとを備える。表示パネルは、複数の走査ラインと複数のデータラインと複数のスイッチング素子と複数の画素とを有する。データラインは、走査ラインと絶縁されて交差する。スイッチング素子は、走査ライン及びデータラインにより囲まれる領域に形成され、それぞれ走査ライン及びデータラインに連結されている。画素は、スイッチング素子により制御され、マトリックス型で配列されている。階調信号補正部は、階調信号ソースから階調信号を受信し、階調信号に基づいて補正階調信号を生成して出力する。データドライバーは、補正階調信号に基づいて、画像信号を生成してデータラインに供給する。走査ドライバーは、走査信号を走査ラインに順次的に供給する。階調信号補正部は、第1フレームの階調信号と第2フレームの階調信号と第3フレームの前記階調信号とを考慮して、第2フレームの補正階調信号を生成して出力する。第2フレームは、第1フレームの次のフレームである。第3フレームは、第2フレームの次のフレームである。

10

#### 【0070】

第39発明に係る駆動装置は、第38発明の駆動装置であって、階調信号補正部は、輝度低減処理が行われた階調信号のレベルがフル階調のレベルより小さい場合に、第1フレームの階調信号と第2フレームの階調信号とを考慮して、補正階調信号を出力する。輝度低減処理は、階調信号に対応するフル階調の輝度をダウンさせる処理である。階調信号補正部は、輝度低減処理された階調信号のレベルがフル階調のレベルである場合に、オーバーシュート電圧を発生するように補正階調信号を出力する。

20

#### 【0071】

第40発明に係る駆動装置は、第38発明の駆動装置であって、階調信号補正部は、第2フレームの階調信号の電圧と第3フレームの階調信号の電圧とが同じ場合、第4フレームの前記階調信号が受信される期間において、第3フレームの補正階調信号の電圧が第3フレームの階調信号の電圧と同じになるように、第3フレームの補正階調信号を生成して出力する。第4フレームは、第3フレームの次のフレームである。

#### 【0072】

第41発明に係る駆動装置は、第40発明の駆動装置であって、階調信号補正部は、階調信号変換部と、メモリと、コントローラとを有する。階調信号変換部は、第1フレームの階調信号と第2フレームの階調信号とを考慮して、第2フレームの第1補正階調信号を生成して出力する。メモリは、第2フレームの第1補正階調信号を階調信号変換部から受け取り、所定フレームの期間だけ第2フレームの第1補正階調信号を保存して出力する。コントローラは、補正読出動作と補正書込動作とを制御する。補正読出動作は、メモリから第2フレームの第1補正階調信号を読み出すことである。補正書込動作は、メモリへ第2フレームの第1補正階調信号を書き込むことである。階調信号変換部には、第3フレームの階調信号が入力される。階調信号変換部は、メモリから第2フレームの第1補正階調信号を受け取る。階調信号変換部は、第2フレームの第1補正階調信号と第3フレームの階調信号とを考慮して、第2フレームの第2補正階調信号を第2フレームの補正階調信号として生成して出力する。

30

40

#### 【0073】

第42発明に係る駆動装置は、表示パネルを駆動する駆動装置であって、タイミング制御部とデータドライバーと走査ドライバーとを備える。表示パネルは、複数の走査ラインと複数のデータラインと複数のスイッチング素子と複数の画素とを有する。データラインは、走査ラインと絶縁されて交差する。スイッチング素子は、走査ライン及びデータラインにより囲まれる領域に形成され、それぞれ走査ライン及びデータラインに連結されている。画素は、スイッチング素子により制御され、マトリックス型で配列されている。タイミング制御部は、階調信号ソースから階調信号を受信し、階調信号に基づいて補正階調信号を生成して出力する。データドライバーは、補正階調信号に基づいて、画像信号を生成

50

してデータラインに供給する。走査ドライバーは、走査信号を走査ラインに順次的に供給する。タイミング制御部は、輝度低減処理を行い、第1フレームの輝度低減処理された階調信号と第2フレームの輝度低減処理された階調信号とを考慮して、補正階調信号を生成して出力する。輝度低減処理は、階調信号に対応するフル階調の輝度をダウンさせる処理である。第2フレームは、第1フレームの次のフレームである。

#### 【0074】

第43発明に係る駆動装置は、第42発明の駆動装置であって、タイミング制御部は、輝度低減処理された階調信号のレベルがフル階調のレベルより小さい場合に、第1フレームの階調信号と第2フレームの階調信号とを考慮して、補正階調信号を出力する。タイミング制御部は、輝度低減処理された階調信号のレベルがフル階調のレベルである場合に、オーバーシュート電圧を発生するように補正階調信号を出力する。

10

#### 【0075】

第44発明に係る駆動装置は、第43発明の駆動装置であって、タイミング制御部は、データ変換部と、階調信号補正部とを有する。データ変換部は、階調信号を輝度低減処理して出力する。階調信号補正部は、輝度低減処理された階調信号のレベルがフル階調のレベルより小さい場合に、第1フレームの階調信号と第2フレームの階調信号とを考慮して、補正階調信号を出力する。階調信号補正部は、輝度低減処理された階調信号のレベルがフル階調のレベルである場合に、オーバーシュート電圧を発生するように補正階調信号を出力する。

#### 【0076】

第45発明に係る駆動方法は、表示パネルが駆動される駆動方法であって、(a)段階と、(b)段階と、(c)段階とを備える。表示パネルは、複数の走査ラインと複数のデータラインと複数のスイッチング素子と複数の画素とを有する。データラインは、走査ラインと絶縁されて交差する。スイッチング素子は、走査ライン及びデータラインにより囲まれる領域に形成されている。スイッチング素子は、それぞれ走査ライン及びデータラインに連結されている。画素は、スイッチング素子により制御され、マトリックス型で配列されている。(a)段階では、走査ラインに走査信号が順次的に供給される。(b)段階では、階調信号ソースから階調信号が受信される。(b)段階では、第1フレームの階調信号と第2フレームの階調信号と第3フレームの階調信号とを考慮して、第2フレームの補正階調信号が生成される。第2フレームは、第1フレームの次のフレームである。第3フレームは、第2フレームの次のフレームである。(c)段階では、補正階調信号に基づいて、画像信号が生成されてデータラインに供給される。

20

#### 【0077】

第46発明に係る駆動方法は、第45発明の駆動方法であって、第2フレームの補正階調信号は、第1電圧と第2電圧とが相異する場合、第3フレームの階調信号が受信される期間において、第1電圧に対する第2フレームの補正階調信号の電圧の変化量が第1電圧に対する第2電圧の変化量よりも大きくなるように生成されて出力されたものである。第1電圧は、第1フレームの階調信号の電圧である。第2電圧は、第2フレームの階調信号の電圧である。

30

#### 【0078】

第47発明に係る駆動方法は、第45発明の駆動方法であって、画素は、液晶を含む。第2フレームの補正階調信号は、第1フレームの階調信号の電圧がブラック階調の電圧であり第2フレームの階調信号の電圧がホワイト階調の電圧である場合に、第2フレームの階調信号が受信される期間において、ブラック階調の電圧より高くホワイト階調の電圧より低い電圧を印加して液晶をプリチルトさせるためのプリチルト信号である。

40

#### 【0079】

第48発明に係る駆動方法は、第45発明の駆動方法であって、段階(b)は、(b-11)段階と、(b-12)段階と、(b-13)段階とを有する。(b-11)段階では、受信された階調信号が所定フレームの期間だけ保存されて出力される。(b-12)段階では、段階(b-11)で出力された階調信号が受け取られ、さらに所定フレームの

50

期間だけ階調信号が保存されて出力される。(b-13)段階では、段階(b-12)で出力された第1フレームの階調信号と、段階(b-11)で出力された第2フレームの階調信号と、受信された第3フレームの階調信号とを考慮して、第2フレームの補正階調信号が生成されて出力される。

【0080】

第49発明に係る駆動方法は、請求項48に記載の駆動方法であって、所定フレームの期間は、1フレームの期間である。

第50発明に係る駆動方法は、第45発明の駆動方法であって、段階(b)は、(b-21)段階と、(b-22)段階と、(b-23)段階とを有する。(b-21)段階では、第1フレームの階調信号と第2フレームの階調信号とを考慮して、第2フレームの第1補正階調信号が生成されて出力される。(b-22)段階では、段階(b-21)で出力された第2フレームの第1補正階調信号が受け取られ、所定フレームの期間だけ第2フレームの第1補正階調信号が保存されて出力される。(b-23)段階では、第3フレームの前記階調信号が入力され、段階(b-21)で出力された前記第2フレームの前記第1補正階調信号が受け取られる。(b-23)段階では、第2フレームの第1補正階調信号と第3フレームの階調信号とを考慮して、第2フレームの第2補正階調信号が第2フレームの補正階調信号として生成されて出力される。

【0081】

第51発明に係る駆動方法は、第50発明の駆動方法であって、所定フレームの期間は、1フレームの期間である。

第52発明に係る駆動方法は、請求項45に記載の駆動方法であって、段階(b)では、第2フレームの階調信号の電圧と第3フレームの階調信号の電圧とが同じ場合、第4フレームの階調信号が受信される期間において、第3フレームの補正階調信号の電圧が第3フレームの階調信号の電圧と同じになるよう、第3フレームの補正階調信号が生成されて出力される。第4フレームは、第3フレームの次のフレームである。

【0082】

第53発明に係る駆動方法は、第52発明の駆動方法であって、段階(b)は、(b-21)段階と(b-31)段階と(b-32)段階と(b-33)段階と(b-34)段階とを有する。(b-21)段階では、第1フレームの階調信号と第2フレームの階調信号とを考慮して、第2フレームの第1補正階調信号が生成されて出力される。(b-31)段階では、第3フレームの階調信号が入力され、第2フレームの第1補正階調信号が抽出される。(b-32)段階では、第1条件が満たされるか否かが判断される。第1条件は、第2フレームの第1補正階調信号のレベルが第1階調であるとともに第3フレームの階調信号のレベルが第2階調であることである。(b-33)段階では、段階(b-32)で第1条件が満たされないと判断された場合に、第3フレームの階調信号が変換されて、第2フレームの第1補正階調信号と第3フレームの階調信号とを考慮して、第2フレームの第2補正階調信号が第2フレームの補正階調信号として生成されて出力される。(b-34)段階では、段階(b-32)で第1条件が満たされると判断された場合に、第2フレームの第1補正階調信号と第3フレームの階調信号とを考慮して、第2フレームの第2補正階調信号が第2フレームの補正階調信号として出力される。

【0083】

第54発明に係る駆動方法は、第53発明の駆動方法であって、第1階調はブラック階調であり、第2階調はホワイト階調である。

第55発明に係る駆動方法は、第46発明の駆動方法であって、段階(b)は、(b-21)段階と(b-41)段階と(b-42)段階と(b-43)段階と(b-44)段階とを有する。(b-21)段階では、第1フレームの階調信号と第2フレームの階調信号とを考慮して、第2フレームの第1補正階調信号が生成されて出力される。(b-41)段階では、第3フレームの階調信号が入力され、第2フレームの第1補正階調信号が抽出される。(b-42)段階では、履歴情報に対応する信号が第2フレームの第1補正階調信号から抽出されて、履歴情報に対応する信号に基づいて補正処理の存否が判断される

10

20

30

40

50

。履歴情報は、補正処理の存否を示す。補正処理は、第1電圧に対する第2フレームの電圧の変化量が第1電圧に対する第2電圧の変化量よりも大きくなるように生成されることである。(b-43)段階では、段階(b-42)で補正処理が存在しないと判断される場合に、第3フレームの第1補正階調信号の履歴情報に対応する信号が活性化される。(b-44)段階では、段階(b-42)で補正処理が存在すると判断される場合に、第3フレームの第1補正階調信号の履歴情報に対応する信号が非活性化される。

#### 【0084】

第56発明に係る駆動方法は、第55発明の駆動方法であって、履歴情報に対応する信号は、補正処理の可否に関する情報を含む。

第57発明に係る駆動方法は、第55発明の駆動方法であって、段階(b-43)で補正処理が存在しないと判断される場合に、第2フレームの第1補正階調信号に補正処理が行われずに、第2フレームの第2フレームの第2補正階調信号が第2フレームの補正階調信号として生成されて出力される。

#### 【0085】

第58発明に係る駆動方法は、第55発明の駆動方法であって、段階(b-44)で補正処理が存在すると判断される場合に、第2フレームの第1補正階調信号に補正処理が行われて、第2フレームの第1補正階調信号と第3フレームの階調信号とを考慮して、第2フレームの第2補正階調信号が第2フレームの補正階調信号として生成されて出力される。

#### 【0086】

第59発明に係る駆動方法は、表示パネルが駆動される駆動方法であって、(a)前記走査ラインに走査信号が順次的に供給される段階と、(d)前記階調信号に対応するフル階調の輝度をダウンさせる処理である輝度低減処理が行われ、第1フレームの前記輝度低減処理された前記階調信号と、前記第1フレームの次のフレームである第2フレームの前記輝度低減処理された前記階調信号とを考慮して、前記補正階調信号が生成されて出力される段階と、(c)前記補正階調信号に基づいて、画像信号が生成されて前記データラインに供給される段階とを備える。表示パネルは、複数の走査ラインと、複数のデータラインと、複数のスイッチング素子と、前記スイッチング素子により制御されマトリックス型で配列された複数の画素とを有する。データラインは、走査ラインと絶縁されて交差する。スイッチング素子は、走査ライン及びデータラインにより囲まれる領域に形成され、それぞれ走査ライン及びデータラインに連結されている。

#### 【0087】

第60発明に係る駆動方法は、第59発明の駆動方法であって、段階(d)では、輝度低減処理された階調信号のレベルがフル階調のレベルより小さい場合に、第1フレームの階調信号と第2フレームの階調信号とを考慮して、補正階調信号が出力される。段階(d)では、輝度低減処理された階調信号のレベルがフル階調のレベルである場合に、オーバーシュート電圧を発生するように補正階調信号が出力される。

#### 【発明を実施するための最良の形態】

#### 【0088】

以下、図面を参照して本発明の望ましい一実施形態をより詳細に説明する。

液晶表示装置は走査信号を伝達する複数のゲートラインとこのゲートラインに交差して形成されデータ電圧を伝達するデータラインを含む。また、液晶表示装置はこれらのゲートラインとデータラインにより囲まれた領域に形成されそれぞれゲートライン及びデータラインとスイッチング素子を通じて連結される行列形態の複数の画素を含む。

#### 【0089】

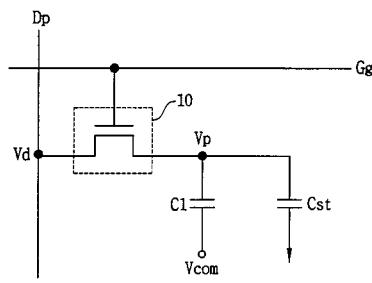

前記液晶表示装置で各画素は液晶を誘電体として有するキャパシター即ち、液晶キャパシターとしてモデリングすることができるが、このような液晶表示装置の各画素の等価回路は図1のようである。

図1にしめすように、液晶表示装置の各画素はデータラインとゲートラインにそれぞれソース電極とゲート電極とが連結されるTFT10と、TFTのドレーン電極と共に通電圧

10

20

30

40

50

との間に連結される液晶キャパシターと、TFTのドレーン電極に連結されるストレージキャパシターとを含む。

#### 【0090】

動作時、ゲートラインにゲートラインオン信号が印加され TFT10 がターンオンされると、データラインに供給されたデータ電圧が TFT10 を通じて各画素電極（図示せず）に印加される。そうすると、画素電極に印加される画素電圧と共に電圧との差異に当る電界が液晶（図1では等価的に液晶キャパシターとして示す）に印加されてこの電界の強さに対応する透過率で光が透過されるようになる。このとき、画素電圧は1フレームの期間保持されなければならないが、図1においてストレージキャパシターは画素電極に印加された画素電圧を保持するため補助的に使用される。

10

#### 【0091】

一方、液晶は異方性誘電率を有するので、液晶の方向により誘電率が異なる特性がある。即ち、電圧が印加されることにより液晶の方向子が変わると誘電率もともに変わるこれによって液晶キャパシターのキャパシタンス（以下ではこれを液晶キャパシタンスと称する）も変わらるようになる、TFTがオンされる区間の間液晶キャパシターに電荷を供給した後、TFTがオフ状態になるが、 $Q = CV$  であるので前記液晶キャパシタンスが変わると液晶にかかる画素電圧も変わらるようになる。

#### 【0092】

ノーマリホワイトモードTN（twisted Nematics）液晶表示装置を例に上げると、画素に供給される画素電圧が0Vである場合には液晶分子が基板に平行な方向に配列されているので液晶キャパシタンスは $C(0V) = \gamma * A/d$ となる。ここで、 $\gamma$ は液晶分子が基板に平行な方向に配列された場合即ち、液晶分子が光の方向と垂直な方向に配列された場合の誘電率を示し、Aとdはそれぞれ液晶表示装置基板の面積と基板との間の距離を示す。フル・ブラックを表示するための電圧が5Vであるとすると液晶に5Vが印加される場合液晶分子が基板に垂直する方向に配列されるので液晶キャパシタンスは $C(5V) = \gamma' * A/d$ となる。TNモードに使用される液晶の場合には $\gamma' > \gamma$ であるので液晶に印加される画素電圧が高くなるほど液晶キャパシタンスがさらに大きくなる。

20

#### 【0093】

n番目フレームでフル・ブラックを作るためにTFTが充電させるべき電荷量は $C(5V) * 5V$ である。しかし、すぐ前のフレームである(n-1)番目フレームでフル・ホワイト( $V_{n-1} = 0V$ )であったとするとTFTのターンオン時間の間には液晶がまだ応答する前であるので液晶キャパシタンス $C(0V)$ となる。従って、フル・ブラックを作るためにn番目フレームで5Vのデータ電圧 $V_d$ を印加しても実際画素に充電される電荷量は $C(0V) * 5V$ となり、 $C(0V) < C(5V)$ であるので液晶に実際供給される画素電圧 $V_p$ は5Vに至らない画素電圧（例えば3.5V）が印加されてフル・ブラックが表示されない。

30

#### 【0094】

また、次フレームであるn+1番目フレームでフル・ブラックを表示するためにデータ電圧 $V_d$ を5Vに印加した場合には液晶に充電される電荷量は $C(3.5V) * 5V$ となり、結局液晶に供給される電圧 $V_p$ は3.5Vと5Vとの間になる。このような過程を繰り返すと結局幾つかのフレームの後画素電圧 $V_p$ が所望する電圧に到達するようになる。

40

これを階調の観点から説明すると、任意の画素に印加される信号（画素電圧）が低い階調から高い階調に（または高い階調から低い階調へ）変わる場合、現在フレームの階調は以前フレームの階調の影響の受けるのですぐ所望する階調に到達できなく、幾つかのフレームが経過された後にこそ所望する階調に到達するようになる。同じように、現在フレームの画素の透過率は以前フレームの画素の透過率の影響を受け幾つかのフレームが経過された後所望する透過率を得られる。

#### 【0095】

一方、n-1フレームがフル・ブラックであり即ち、画素電圧 $V_p$ が5Vで、nフレー

50

ムでフル・ブラックを表示するために5Vのデータ電圧が印加されたとすると、液晶キャパシタンスはC(5V)であるので画素にはC(5V)\*5Vに該当する電荷量が充電されこれによって液晶の画素電圧V<sub>p</sub>は5Vとなる。

このように、液晶に実際供給される画素電圧V<sub>p</sub>は現在フレームに供給されるデータ電圧だけではなく以前フレームの画素電圧V<sub>p</sub>によっても決定される。

#### 【0096】

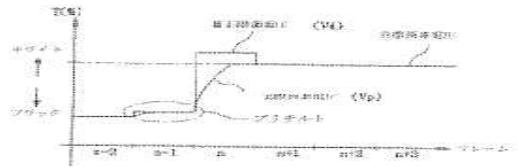

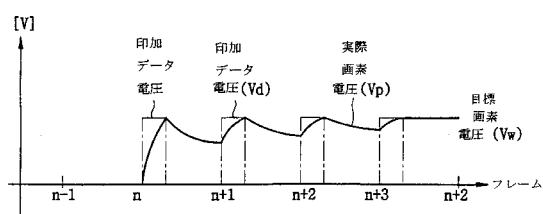

図2は従来の駆動方式で印加される場合のデータ電圧及び画素電圧を示す図面である。

図2に示すように、従来には以前フレームの画素電圧V<sub>p</sub>を考慮しないで、目標画素電圧V<sub>w</sub>に該当するデータ電圧V<sub>d</sub>をフレーム毎に印加した。従って、実際液晶に印加される画素電圧V<sub>p</sub>は前述したように

10

、以前フレームの画素電圧に対応する液晶キャパシタンスにより目標画素電圧より低くまたは高くなる。従って、幾つかのフレームが経過された後にこそ目標画素電圧に到達するようになる。

#### 【0097】

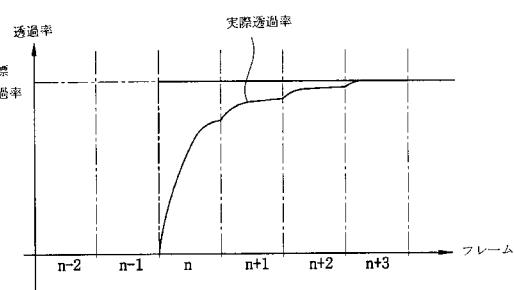

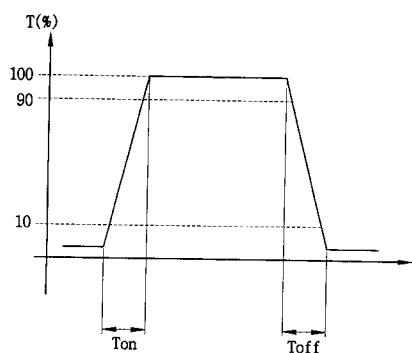

図3はこのような従来の駆動方法による液晶表示装置の透過率を示す図面である。

図3に示すように、従来には前述したように実際画素電圧が目標画素電圧より低くなるので液晶の応答時間が一つのフレーム以内である場合にも幾つかのフレームが経過した後にこそ目標透過率に到達するようになる。

20

しかし、本発明においては現在フレームの画像信号P<sub>n</sub>が入力されるにつれ以前フレームの画像信号P<sub>n-1</sub>と次フレームの画像信号P<sub>n+1</sub>との比較を通じて次のような補正信号P<sub>n'</sub>を生成した後、補正された画像信号P<sub>n'</sub>を各画素に印加する。ここで、画像信号P<sub>n</sub>は液晶表示装置がアナログ駆動方式を採用する場合にはデータ電圧を意味するが、デジタル駆動方式を採用する場合には前記データ電圧を制御するために二進化された階調信号（または階調データ）を使用するので実際画素に印加される電圧の補正是前記階調信号の補正を通じて行われる。

20

#### 【0098】

まず、現在フレームの画像信号（データ電圧または階調信号）が以前フレームの画像信号と同様であるか類似していると補正を行わない。

次に、現在フレームの階調信号が以前フレームの階調信号より高い場合には現在フレームの階調信号よりさらに高い補正された階調信号を出力し、現在フレームの階調信号が以前フレームの階調信号より低い場合には現在フレームの階調信号よりさらに低い補正された階調信号を出力する。このとき、補正が行われる程度は現在フレームの階調信号と以前フレームの階調信号と次フレームの階調信号との差に比例する。

30

#### 【0099】

以下、一般的データ電圧補正方法を概略的に説明する。

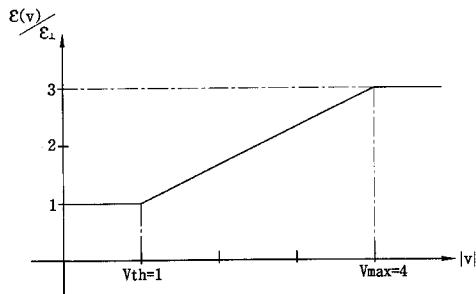

図4は液晶表示装置の電圧-誘電率間の関係を簡単にモデリングした図面である。

図4で、横軸は画素電圧であり、縦軸は、特定画素電圧においての誘電率（（V））と、液晶とが基板に平行な方向に配列された場合即ち液晶が光の透過方向と垂直する場合の誘電率（^）との比を示す。

40

#### 【0100】

図4では、（V）/^の最大値即ち、（V）/^を3だと仮定し、V<sub>th</sub>とV<sub>max</sub>をそれぞれ1V、4Vに仮定した。ここで、V<sub>th</sub>とV<sub>max</sub>はそれぞれフル・ホワイト及びフル・ブラック（またはその反対）に該当する画素電圧を示す。

ストレージキャパシターのキャパシタンス（以下では、これをストレージキャパシタンスと称する）が液晶キャパシタンスの平均値C<sub>st</sub>と同じであるとし、液晶表示装置基板の広さ及び基板の間の距離をそれぞれAとdだとすると、ストレージキャパシタンスC<sub>st</sub>は次の数式1に示すことができる。

#### 【0101】

【数1】

$$\begin{aligned} C_s t &= \langle C_1 \rangle = 1/3 * (\epsilon_{\parallel} + 2 \epsilon_{\perp}) * A/d \\ &= (5/3) \epsilon_{\parallel} * A/d = (5/3) * C_o \end{aligned}$$

ここで、 $C_o = \epsilon_{\perp} * A / d$  である。

図4から、 $\epsilon(V) / \epsilon_{\perp}$  は次の式2に示すところができる。

【0 1 0 2】

【数2】

10

$$\epsilon(V) / \epsilon_{\perp} = 1/3 * (2V + 1)$$

液晶表示装置の総キャパシタンス  $C(V)$  は液晶キャパシタンスとストレージキャパシタンスとを足したものであるので、液晶表示装置のキャパシタンスは  $C(V)$  は式1及び式2から次の式3に示すことができる。

【0 1 0 3】

【数3】

20

$$\begin{aligned} C(V) &= C_1 + C_s t = \epsilon(V) * A/d + 5/3 * C_o \\ &= 1/3 (2V + 1) C_o + 5/3 (V + 3) C_o \end{aligned}$$

【0 1 0 4】

【数4】

$$Q = C(V_n - 1) * V_n = C(V_f) * V_f$$

30

ここで、 $V_n$  は現在フレームに印加されるデータ電圧（反転駆動式の場合にはデータ電圧の絶対値）を示し、 $C(V_n - 1)$  は以前フレーム（n-1フレーム）の画素電圧に対応するキャパシタンスを示し、 $C(V_f)$  は現在フレーム（nフレーム）の実際画素電圧  $V_f$  に対応するキャパシタンスを示す。

【0 1 0 5】

式3及び式4から次の式5が誘導され得る。

【0 1 0 6】

【数5】

$$\begin{aligned} C(V_n - 1) * V_n &= C(V_f) * V_f \\ &= 2/3 (V_n - 1 + 3) * V_n = 2/3 (V_f + 3) * V_f \end{aligned}$$

40

従って、実際画素電圧  $V_f$  は次の式6に示され得る。

【0 1 0 7】

【数6】

$$V_f = \{-3 + \sqrt{9 + 4V_n(V_n - 1 + 3)}\}/2$$

前記した式6から明らかであるように、実際画素電圧  $V_f$  は現在フレームに印加されたデータ電圧  $V_n$  と以前フレームに印加された画素電圧 ( $V_n - 1$ ) により決定される。

一方、nフレームで画素電圧が目標画素電圧  $V_n$  に到達するようにするために印加され

50

るデータ電圧を  $V_{n'}$  だとすると、 $V_{n'}$  は数式 5 から下記する数式 7 に示され得る。

【0108】

【数7】

$$(V_n - 1 + 3) V_n' = (V_n + 3) V_n$$

従って、 $V_{n'}$  は下記する数式 8 に示され得る。

【0109】

【数8】

10

$$\begin{aligned} V_n' &= \{V_n + 3\} / \{V_n - 1 + 3\} V_n \\ &= V_n + \{V_n - V_n - 1\} / \{V_n - 1 + 3\} V_n \end{aligned}$$

このように、現在フレームの目標画素電圧  $V_n$  と以前フレームの画素電圧 ( $V_{n-1}$ ) とを考慮して前記数式 8 により求められるデータ電圧  $V_{n'}$  を印加すると、目標とする画素電圧  $V_n$  にすぐ到達することができる。

【0110】

前記の数式 8 は図 4 に示された図面及び幾つかの基本仮定から誘導された式であり、一般的な液晶表示装置で適用されるデータ電圧  $V_{n'}$  は次の数式 9 に示すことができる。

20

【0111】

【数9】

$$|V_n'| = |V_n| + f(|V_n| - |V_{n-1}|)$$

ここで、関数  $f$  は液晶表示装置の特性により決定され、基本的に次の性質を有する。即ち、 $V_n$  の絶対値と  $n-1$  の絶対値とが同じである場合に前記  $f$  は 0 となり、 $V_n$  の絶対値が  $V_{n-1}$  の絶対値より大きい場合前記  $f$  は 0 より大きく、 $V_n$  の絶対値が  $V_{n-1}$  の絶対値より小さい場合前記  $f$  は 0 より小さい。

30

【0112】

前記した技術を根拠として、液晶の応答速度を高速化するため現在フレームの目標画素電圧と以前フレームの画素電圧とを考慮して補正データ電圧を印加することで、画素電圧がすぐ目標電圧に到達するようになる。具体的に、現在フレームの目標電圧と以前フレームの画素電圧とが異なる場合には現在フレームの目標電圧よりさらに高い電圧を補正されたデータ電圧として印加して一番目のフレームですぐ目標電圧レベルに到達するようにした後以後のフレームでは目標電圧をデータ電圧に印加する方式を通じて液晶の応答速度を改善することができる。このとき、補正データ電圧（即ち、電荷量）は以前フレームの画素電圧により決定される液晶キャパシタンスを考慮して決定する。即ち、以前フレームの画素電圧レベルを考慮して電荷量を供給することにより一番目のフレームですぐ目標画素電圧レベルに到達するようになる。

40

【0113】

しかし、一般的な垂直配向モードの液晶を採用する液晶表示装置では階調が変化するとき目標値電圧より高い電圧を 1 フレームの期間印加して液晶を強制に早く駆動してもブラック階調からホワイト階調に変換するときの液晶の応答速度を高速化するには限界がある。

特に、画素電極（または透明電極）に開口パターンを形成し、フリンジフィールド（fringe field）を形成して液晶の傾く方向を 4 方向に均等に分散させ光視野角を確保し得るパターン化された垂直配向（以下、PVA）モードを採用する液晶表示装置の場合には応答速度を高速化するには限界がある。

【0114】

50

下記する表1は32インチの解像度と前記垂直配向モードの一例であるPVAモードを採用する液晶表示装置で測定したデータとして、各階調間応答速度を示す。

【0115】

【表1】

|           |        | 変化後階調     |            |            |           |            |

|-----------|--------|-----------|------------|------------|-----------|------------|

|           |        | 0[%]      | 25[%]      | 50[%]      | 75[%]     | 100[%]     |

| 変化前階<br>調 | 0[%]   | -         | 11.8[msec] | 10.8[msec] | 9.2[msec] | 15.6[msec] |

|           | 25[%]  | 5.8[msec] | -          | 10.4[msec] | 8.2[msec] | 9.0[msec]  |

|           | 50[%]  | 5.8[msec] | 9.6[msec]  | -          | 7.2[msec] | 7.6[msec]  |

|           | 75[%]  | 6.2[msec] | 9.4[msec]  | 8.6[msec]  | -         | 4.6[msec]  |

|           | 100[%] | 7.0[msec] | 9.6[msec]  | 9.0[msec]  | 7.0[msec] | -          |

前記した表1に示すように、大部分の階調変換時10[msec]以下の良好な応答速度を示す反面、0%から100%の階調へ変換時、即ち、ブラック階調からホワイト階調に変わるとの応答速度は15.6[msec]であることを確認することができる。

【0116】

このように、PVAモードの液晶を採用する液晶表示装置においてブラック階調からホワイト階調に画素をターンオンさせるとき応答速度が大きい理由は次のようにある。

一般に、前記PVAモードではブラック階調で液晶、具体的に液晶の長軸が全部垂直に立っている。万一、ブラック状態からホワイトに急変するように制御する強い電圧が印加されると、液晶表示装置に具備されるカラーフィルター基板やアレイ基板に形成されたITOパターン、突起などにより特定方向に液晶が横になる。このとき、ドメイン境界から遠い部分に位置する液晶は正確に方向を見つけることができず所望しない違う方向に向かって横になる。このような理由から再び液晶が本来の位置を見つけるに時間が所要されるので応答速度が遅い。

【0117】

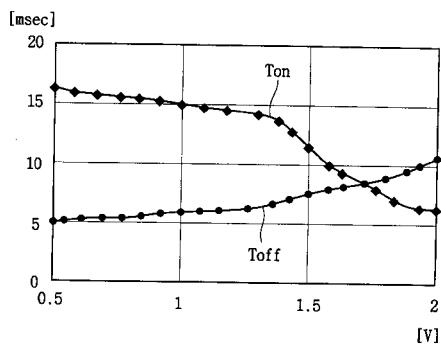

図5は液晶動作時間に応じる輝度特性を示す画面であり、図6はPVAモードでブラック電圧による液晶オン時間(Ton)と液晶オフ時間(Toff)を示すための画面である。

図5及び図6に示すように、前記したPVAモードでブラック階調に対応する電圧(以下、ブラック電圧)が高くなるほどフォーリング(Toff、falling time)時間は遅いが、ライジング(Ton、rising time)時間は速くなる。その理由は前記ブラック電圧が高くなると液晶が垂直状態ではない少しづつITOパターンが誘導する方向にプリチルト(pre tilt)角を有する傾斜配列状態となるのである。このとき、ホワイト階調に対応する電圧(以下、ホワイト電圧)が印加されると液晶は速くもとの方向に横になり応答速度が速くなる。

【0118】

これをを利用して応答速度を早くすることが本発明による液晶の高速応答のための駆動方法である。しかし、前記ブラック電圧をどこまでも高めることができない。それはブラック電圧を高めると液晶オフ時間が遅くなるだけではなく、視野角が狭くなり、コントラスト比率も減少するからである。

本発明による液晶の高速応答のための駆動方法は下記する図7のようにブラック階調からホワイト階調に変わると、変換する前一つのフレーム前に予め一定レベル電圧、例えば、2~3.5ボルト内外の電圧を印加して液晶をプリチルト(pre tilt)させた後次フレームでホワイト階調に変わるとブラック階調からホワイト階調に変わった応答速度は速くなる。

10

20

30

40

50

## 【0119】

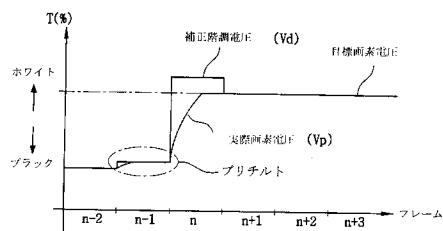

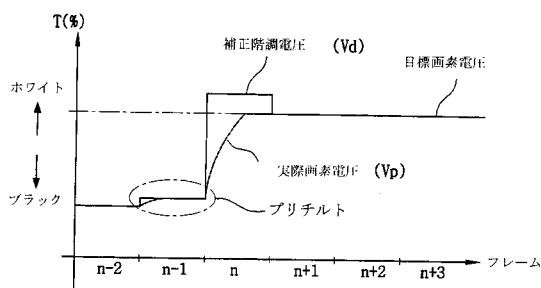

図7は本発明によるデータ電圧印加方法を示す図面である。

図7に示すように、本発明においては現在フレームの目標画素電圧と以前フレームの画素電圧（またはデータ電圧）及び次フレームの画素電圧とを考慮して補正データ電圧 $V_n'$ を印加して、現在フレームの画素電圧 $V_p$ がすぐ目標電圧に到達するようとする。

即ち、ブラック階調からホワイト階調に変わると、ホワイト階調に変換する1フレーム前の期間に前記ブラック階調より高い電圧を印加して予め液晶をプリチルトさせる。一般にブラック電圧は0.5~1.5Vである点を勘案すると、前記プリチルトさせるための高い電圧は大略2~3.5Vであることが望ましい。また、フル-階調が256階調であるなら0~50グレイに当ると前記ブラック階調として定義されることができ、200~225グレイに当ると前記ホワイト階調として定義することができる。勿論、設計者により前記したブラック階調やホワイト階調の範囲は任意で設定可能である。また、前記プリチルトさせる電圧も、グレイとは関係なしに設定されたブラック階調に一括的に対応されるように設定することができ、それぞれのグレイに対応するように互いに異なる値を有するように設定される。

## 【0120】

その次のフレームでホワイト階調に変わるとブラック階調信号からホワイト階調に変換する速度を高速化させることができる。

具体的に、現在フレームがブラック階調であるとき、次フレームがどんな階調の信号がくるかについて前もって知っているべきである。このとき、次フレームがホワイト階調または明るい階調であると現在フレームにはブラック階調ではないブラック階調より高い階調の信号を印加する。

## 【0121】

このように、原始階調信号がブラック階調からホワイト階調に変換するときプリチルト発生のための補正階調信号とオーバーシュート発生のための補正階調信号を出力することにより液晶の応答速度を高速化させることができる。

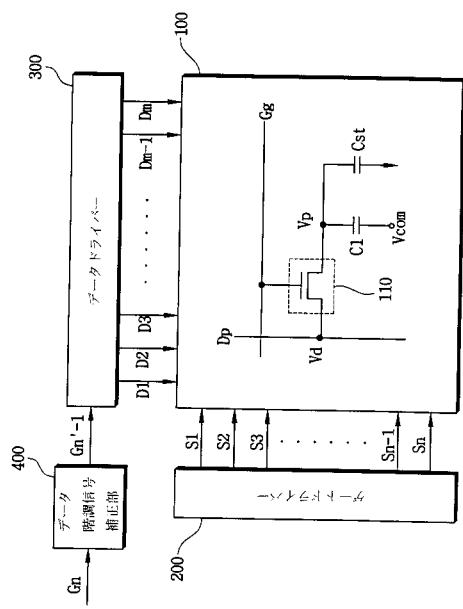

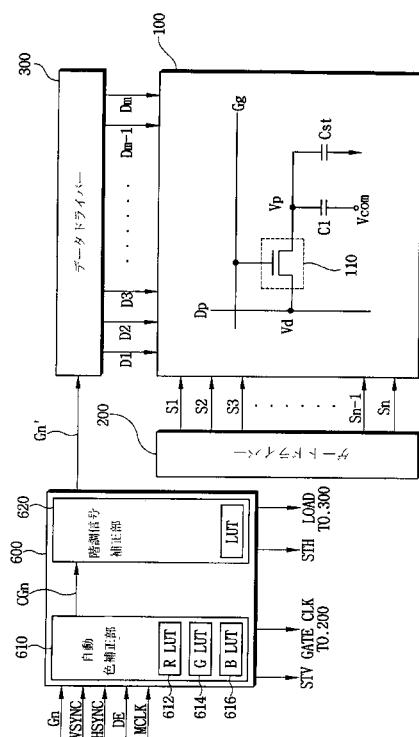

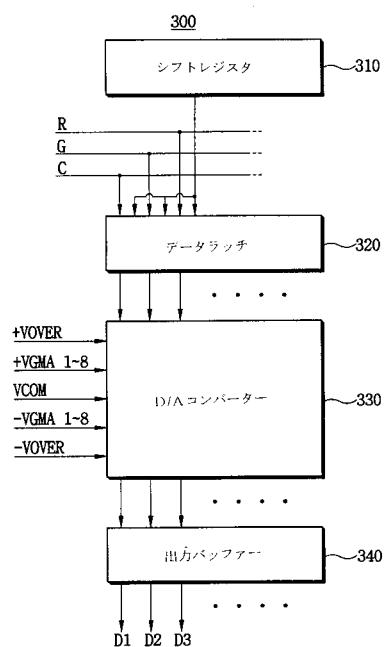

図8は本発明による液晶表示装置を示すための図面で、特にデジタル駆動方法を有する液晶表示装置を説明する。

## 【0122】

図8に示すように、本発明による液晶表示装置は液晶パネル100、ゲートドライバー200、データドライバー300及び階調信号補正部400を含む。ここで、ゲートドライバー200、データドライバー300及び階調信号補正部400はグラフィックコントローラのような外部のホストから提供される画像信号を液晶パネル100に適応するよう変換して出力する液晶表示装置の駆動装置として動作を遂行する。

## 【0123】

液晶パネル100にはゲートオン信号を伝達するための複数のゲートライン（走査ライン）が形成され、補正されたデータ電圧を伝達するためのデータライン（またはソースライン）が形成されている。前記ゲートラインと前記データラインにより囲まれた領域はそれぞれ画素を成し、各画素は前記ゲートラインと前記データラインにそれぞれゲート電極及びソース電極が連結される薄膜トランジスタ110と、前記薄膜トランジスタ110のドレーン電極に連結される液晶キャパシターC1と、ストレージキャパシターCstとを含む。

## 【0124】

特に、液晶パネルは垂直配向モードを採用することもでき、パターン化された垂直配向モードを採用することもでき、混載（mixide）された垂直配向モードを採用することもできる。ここで、垂直配向モードはアレイ基板のラビングラインとカラーフィルター基板のラビングラインとが交差する角度が0でありながらその方向が正反対である液晶モードであり、前記混載された垂直配向モードはアレイ基板のラビングラインとカラーフィルター基板のラビングラインとが交差する角度が0より大きく90より小さいその方向が正反対である液晶モードである。

## 【0125】

ゲートドライバー200は前記ゲートラインに順次にゲートオン電圧(S1、S2、S3、....、Sn)を印加して、前記ゲートオン電圧が印加されたゲートラインにゲート電極が連結される薄膜トランジスタ110をターンオンさせる。

データドライバー300は階調信号補正部400から受信された補正階調信号(Gn'-1)を該当階調電圧(データ電圧)に変更したデータ信号(D1、D2、....、Dn)をそれぞれデータラインに印加する。

## 【0126】

階調信号補正部400は階調信号ソース、例えばグラフィックコントローラ(図示せず)から原始階調信号Gnを受信した後、前述したように現在フレーム、以前フレーム及び次フレームの階調信号を考慮して補正階調信号(Gn'-1)を出力する。10

即ち、現在フレームの原始階調信号と次フレームの原始階調信号(Gn+1)とが同一である場合には補正されないが、現在フレームの原始階調信号Gnがブラック階調に対応し、次フレームの原始階調信号(Gn+1)が明るい階調またはホワイト階調に対応する階調だとすると現在フレームには前記ブラック階調よりは高い階調が形成されるように補正階調信号を出力する。具体的に、現在フレームの原始階調信号と以前フレームの原始階調信号との比較を通じてオーバーシュート波形形成のための補正階調信号を出力し、現在フレームの原始階調信号と次フレームの原始階調信号との比較を通じて液晶をプリチルトさせるための補正階調信号を出力する。

## 【0127】

一方、図面上では階調信号補正部400がスタンドアローン(stand-alone)ユニットで存在することを図示したが、グラフィックカードや液晶表示モジュール、タイミングコントローラ、データドライバーなどに連合されるように表示することもできる。20

以上、本発明によるとデータ電圧を補正し、補正されたデータ電圧を画素に印加することによって画素電圧がすぐ目標電圧レベルに到達するようになる。従って、液晶パネルの構造を変更するか、液晶の物性を変更しなくても液晶の応答速度を改善させることができ動画像を有用にディスプレーすることができる。

## 【0128】

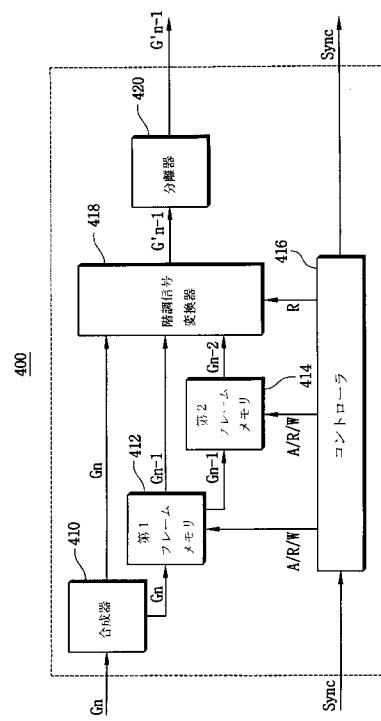

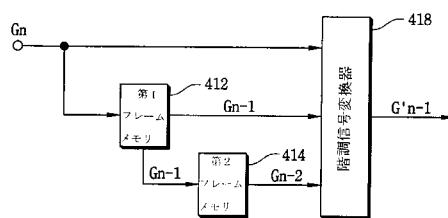

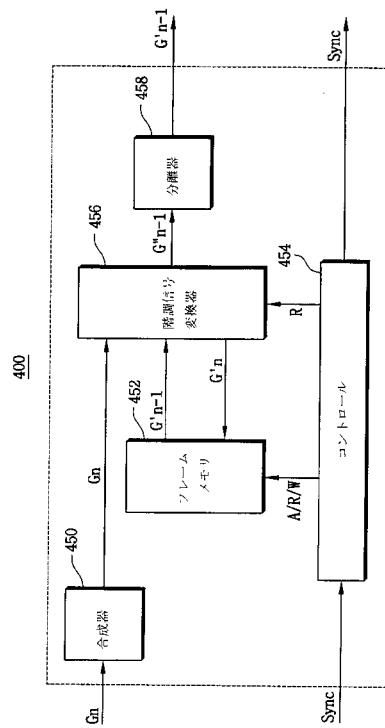

図9は本発明の第1実施形態による階調信号補正部を示すための図面である。

図9に示すように、本発明の第1実施形態による階調信号補正部400は合成器410は、第1フレームメモリ412、第2フレームメモリ414、コントローラ416、階調信号変換器418及び分離器420を含み、現在フレームの原始階調信号Gnの提供を受け以前フレームに対応する補正階調信号(G'n-1)を出力する。30

## 【0129】

合成器410は階調信号ソース(図示せず)から伝送される現在フレームの原始階調信号Gnを受信し、階調信号補正部400が処理可能な速度にデータストリームの周波数を変換する。例えば、前記階調信号ソースから24ビットのデータが65(MHz)周波数に同期して受信され、階調信号補正部400の構成要素の処理速度が50(MHz)が限界だとすると、合成器410は24ビットの原始階調信号を2つずつ束にして48ビットの階調信号Gnとして合成して第1フレームメモリ412及び階調信号変換器418に伝送する。このとき、コントローラ416が、入力されたクロック信号Syncの周波数を1/2にして、後述のアドレスクロック、リードクロックR及びライトクロックWを生成する。なお、クロック信号Syncの周波数をあからじめ分周してコントローラ416に入力させるようにしてもよい。40

## 【0130】

第1フレームメモリ412はコントローラ416から提供されるアドレスクロック及びリードクロックRに応答して予め保存された以前フレームの階調信号Gn-1を階調信号変換器418及び第2フレームメモリ414に出力する。コントローラ416から提供されるアドレスクロックA及びライトクロックWに応答して合成器410から提供される現50

在フレームの階調信号  $G_n$  を保存する。

【0131】

第2フレームメモリ414はコントローラ416から提供されるアドレスクロックA及びリードクロックRに応答して所定アドレスに保存されている以前フレームの階調信号  $G_{n-2}$  を階調信号変換器418に出力する。コントローラ416から提供されるアドレスクロックA及びライトクロックWに応答して第1フレームメモリ412から提供される以前フレームの階調信号  $G_{n-1}$  を保存する。

【0132】

階調信号変換器418はコントローラ416から提供されるリードクロックRに応答して合成器410から出力される現在フレームの階調信号  $G_n$  と、第1フレームメモリ412から出力される以前フレームの階調信号  $G_{n-1}$  と、第2フレームメモリ414から出力されるその以前フレームの階調信号  $G_{n-2}$  をそれぞれ受信し、現在フレームの階調信号  $G_n$  と以前フレームの階調信号  $G_{n-1}$  とその以前フレームの階調信号  $G_{n-2}$  とを考慮して補正階調信号  $G_{n-1}$  を生成する。

【0133】

つまり、階調信号変換器418は  $n-1$  番目フレームの原始階調信号と  $n$  番目フレームの原始階調信号が相異する場合に、 $n$  番目フレーム駆動時  $n$  番目フレームの目標電圧より高いオーバーシュート波形が印加されるように補正階調信号を出力し、 $n-1$  番目フレームの階調信号がブラック階調である場合、 $n$  番目フレームが明るい階調またはホワイト階調であると  $n-1$  番目フレームには前記ブラック階調よりは高い階調信号を印加して液晶をプリチルトさせるための補正階調信号を出力する。

【0134】

分離器420は階調信号変換器418から出力される補正階調信号  $G_{n-1}$  を分離し、分離された階調信号  $G'_{n-1}$  をデータドライバー300に出力する。例えば、補正された階調信号  $G'_{n-1}$  が48ビットを有すると分離された階調信号  $G_{n-1}$  は24ビットを有する。

以上、前記階調信号に同期するクロック周波数が第1フレームメモリ412及び第2フレームメモリ414をアクセスするクロック周波数と相異するので、前記階調信号を合成及び分離する合成器410及び分離器420が必要であった。しかし、前記階調信号に同期するクロック周波数と第1フレームメモリ412及び第2フレームメモリ414をアクセスするクロック周波数が同一な場合には前記した合成器と分離器は不要である。

【0135】

一方、前記した階調信号変換器418は前述した数式9を満たすデジタル回路を直接製造して使用でき、ルックアップテーブルを作成してROM(Read Only Memory)に保存した後アクセスして階調信号を補正することもできる。実際、補正データ電圧  $V_{n'}$  は単純に以前フレームのデータ電圧  $V_{n-1}$  と現在フレームのデータ電圧  $V_n$  の差のみに比例するものではなく前述したようにそれぞれの絶対値にも依存する複雑な関数であるので前記したルックアップテーブルを構成すると演算処理に依存するより回路がずっと簡単になるという長所がある。

【0136】

一方、本発明の実施形態によるデータ電圧を補正するためには実際に使われるグレイスケール範囲よりさらに広いダイナミックレンジを有するべきである。しかし、アナログ回路では高電圧ICを使用することにより解決できるのに対して、デジタル方式においては分けられる階調数が限定されている。例えば、6ビット階調である場合64個の階調レベルのうち一部分は実際の階調表示ではなく変造された電圧のために割当てなければならない。即ち、一部の階調レベルは電圧補正用として割当てるべきである。従って、表現しなければならない階調の数が減ることになる。

【0137】

前記した階調の数の減少を防ぐためには次のような打切り(truncation)の概念が導入され得る。例えば、液晶が1Vから4Vの間で駆動し補正電圧を考慮したとき

10

20

30

40

50

電圧が 0 V から 8 V まで必要とされる場合を仮定しよう。このとき、補正を充実するために 0 V から 8 V までを 64 個の段階に分けると実際表現できる階調は 30 個程度に過ぎない。従って、電圧幅を 1 ~ 4 V に低くし計算上矯正された電圧  $V_{n'}$  が 4 V を越える場合には全部補正電圧を 4 V に打切りすると階調数の減少を減らすことができる。

#### 【 0138 】

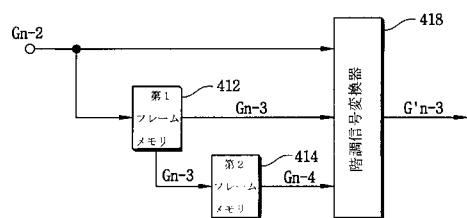

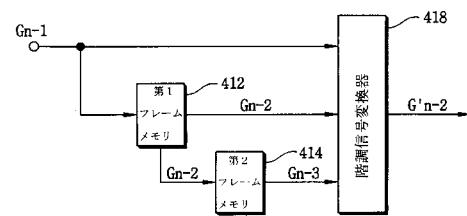

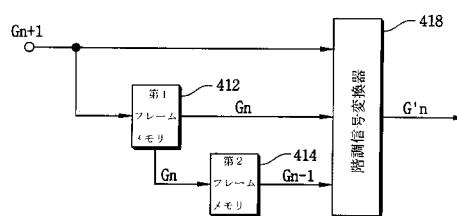

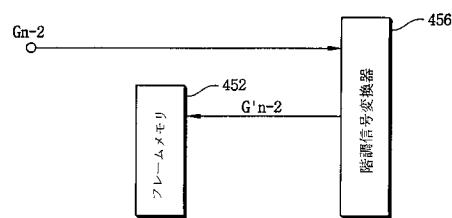

図 10 ~ 図 13 は前記した図 9 の階調信号補正部の動作を概念的に示すための図である。

図 10 に示すように、 $n - 2$  番目フレームの階調信号  $G_{n-2}$  が第 1 フレームメモリ 412 及び階調信号変換器 418 に提供されることにより、第 1 フレームメモリ 412 に保存された  $n - 3$  番目フレームの階調信号  $G_{n-3}$  は第 2 フレームメモリ 414 及び階調信号変換器 418 に提供され、第 2 フレームメモリ 414 に保存された  $n - 4$  番目フレームの階調信号  $G_{n-4}$  は階調信号変換器 418 に提供される。このとき、階調信号変換器 418 に提供された  $n - 2$  番目フレームの階調信号  $G_{n-2}$  と、 $n - 3$  番目フレームの階調信号  $G_{n-3}$  と、 $n - 4$  番目フレームの階調信号  $G_{n-4}$  は液晶の高速応答のために補正された  $n - 3$  番目フレームの補正階調信号を  $G_{n-3}$  を出力する。10

#### 【 0139 】

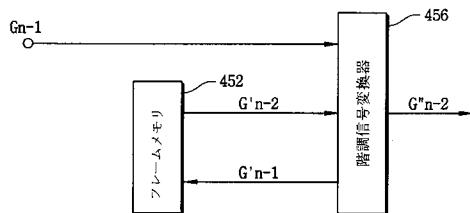

一方、図 11 に示すように、 $n - 1$  番目フレームの階調信号  $G_{n-1}$  が第 1 フレームメモリ 412 及び階調信号変換器 418 に提供されることにより、第 1 フレームメモリ 412 に保存された  $n - 2$  番目フレームの階調信号  $G_{n-2}$  は第 2 フレームメモリ 414 及び階調信号変換器 418 に提供され、第 2 フレームメモリ 414 に保存された  $n - 3$  番目フレームの階調信号  $G_{n-3}$  は階調信号変換器 418 に提供される。このとき、階調信号変換器 418 に提供された  $n - 1$  番目フレームの階調信号  $G_{n-1}$  と、 $n - 2$  番目フレームの階調信号  $G_{n-2}$  と、 $n - 3$  番目フレームの階調信号  $G_{n-3}$  は液晶の高速応答のために補正されて  $n - 2$  番目フレームの補正階調信号  $G_{n-2}$  を出力する。20

#### 【 0140 】

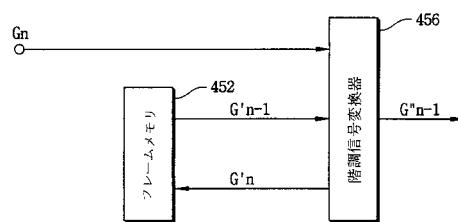

一方、図 12 に示すように、 $n$  番目フレームの階調信号  $G_n$  が第 1 フレームメモリ 412 及び階調信号変換器 418 に提供されることにより、第 1 フレームメモリ 412 に保存された  $n - 1$  番目フレームの階調信号  $G_{n-1}$  は第 2 フレームメモリ 414 及び階調信号変換器 418 に提供され、第 2 フレームメモリ 414 に保存された  $n - 2$  番目フレームの階調信号  $G_{n-2}$  は階調信号変換器 418 に提供される。このとき、階調信号変換器 418 に提供された  $n$  番目フレームの階調信号  $G_n$  と、 $n - 1$  番目フレームの階調信号  $G_{n-1}$  と、 $n - 2$  番目フレームの階調信号  $G_{n-2}$  は液晶の高速応答のために補正され  $n - 1$  番目フレームの補正階調信号  $G_{n-1}$  を出力する。30

#### 【 0141 】

一方、図 13 に示すように、 $n + 1$  番目フレームの階調信号  $G_{n+1}$  が第 1 フレームメモリ 412 及び階調信号変換器 418 に提供されることにより、第 1 フレームメモリ 412 に保存された  $n$  番目フレームの階調信号  $G_n$  は第 2 フレームメモリ 414 及び階調信号変換器 418 に提供され、第 2 フレームメモリ 414 に保存された  $n - 1$  番目フレームの階調信号  $G_{n-1}$  は階調信号変換器 418 に提供される。このとき、階調信号変換器 418 に提供された  $n + 1$  番目フレームの階調信号  $G_{n+1}$  と、 $n$  番目フレームの階調信号  $G_n$  と、 $n - 1$  番目フレームの階調信号  $G_{n-1}$  は液晶の高速応答のために補正されて  $n$  番目フレームの補正階調信号  $G_n$  を出力する。40

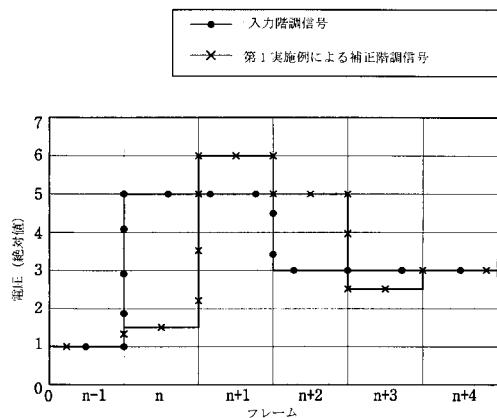

#### 【 0142 】

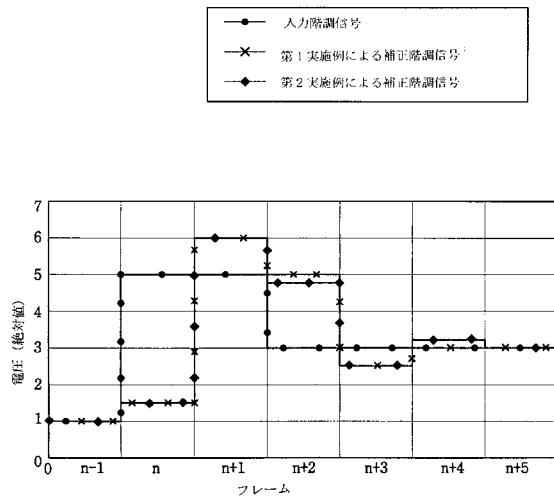

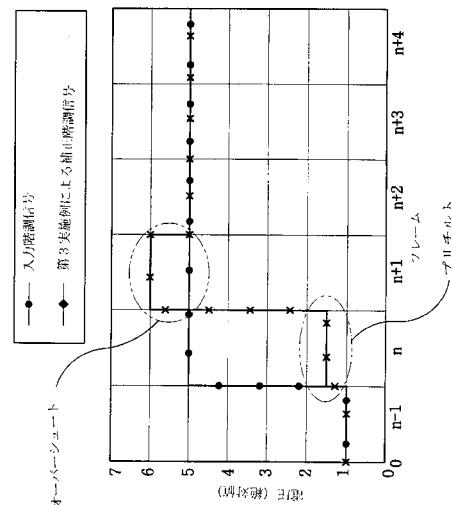

図 14 は本発明の第 1 実施形態による入力階調信号と出力補正階調信号とを対比して示す波形図である。

図 14 に示すように、 $n - 1$  番目フレームの期間に 1 ボルトに対応し、 $n$  番目と  $n + 1$  番目フレームの期間に 5 ボルトに対応し、 $n + 2$  番目フレーム以後には 3 ボルトに対応する原始階調信号が入力されると、本発明の第 1 実施形態による補正階調信号は次のように出力される。50

## 【0143】

即ち、 $n$ 番目フレームの期間には液晶をプリチルトさせるための形成信号として前記1ボルトよりは高い1.5ボルトに対応する補正階調信号が出力され、 $n+1$ 番目フレームの期間に前記5ボルトより高い6ボルトに対応する補正階調信号が出力された後、 $n+2$ 番目フレームの期間に5ボルトに対応する補正階調信号が出力される。

このように、本発明の第1実施形態による補正階調信号は原始階調信号を対比して1フレーム期間ずつ遅延され出力されるので液晶の応答速度を高速化することができる。特に、低電圧が要求されるブラック階調から高電圧が要求されるホワイト階調に急変するとき、まず液晶をプリチルト(*pre tilt*)させるためのプリチルト形成信号を出力した後、次のフレーム期間に目標画素電圧より高い高階調の信号が入力されるので液晶の応答速度を向上させることができる。

10

## 【0144】

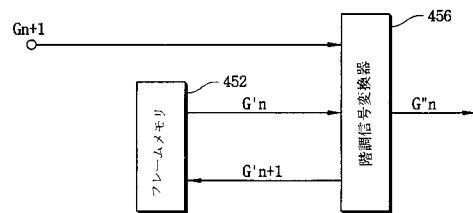

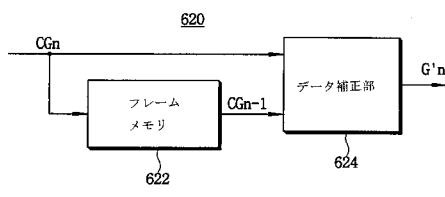

図15は本発明の第2実施形態による階調信号補正部を示すための図である。

図15に示すように、本発明の第2実施形態による階調信号補正部400は合成器450、フレームメモリ452、コントローラ454、階調信号変換器456及び分離器458を含み、現在フレームの原始階調信号 $G_n$ の提供を受け以前フレームに対応する補正階調信号 $G'_{n-1}$ を出力する。

## 【0145】

合成器450は階調信号ソース(図示せず)から伝送される現在フレームの原始階調信号 $G_n$ を受信し、階調信号補正部400が処理し得る速度でデータストリームの周波数を変換した後、変換された現在フレームの階調信号を階調信号変換器456に提供する。

20

フレームメモリ452はコントローラ454から提供されるアドレスクロックA及びリードクロックRに応答して予め保存された以前フレームの第1補正階調信号 $G'_{n-1}$ を階調信号変換器418に出力すると同時に、コントローラ416から提供されるアドレスクロックA及びライトクロックWに応答して階調信号変換器418から提供される現在フレームの第1補正階調信号 $G'_{n}$ を保存する。

## 【0146】

階調信号変換器456はコントローラ454から提供されるリードクロックRに応答して合成器450から出力される現在フレームの階調信号 $G_n$ と、フレームメモリ452から出力される以前フレームの第1補正階調信号 $G'_{n-1}$ とを考慮して以前フレームの第2補正階調信号 $G'_{n-1}$ を生成した後分離器458に提供する。また、現在フレームの第1補正階調信号 $G'_{n-1}$ をフレームメモリ412に保存するように提供する。つまり、階調信号変換器418は $n-1$ 番目フレームの原始階調信号と $n$ 番目フレームの原始階調信号が相異する場合、 $n$ 番目フレーム駆動時 $n$ 番目フレームの目標電圧より高いオーバーシュート波形が印加されるように第2補正階調信号 $G'_{n-1}$ を出力し、 $n-1$ 番目フレームの階調信号がブラック階調信号であるとき、 $n$ 番目フレームが明るい階調またはホワイト階調であると $n-1$ 番目フレームには前記ブラック階調よりは高い階調信号を印加して液晶をプリチルトさせるための第2補正階調信号 $G'_{n-1}$ を出力する。

30

## 【0147】

分離器458は第2補正階調信号 $G_{n-1}$ を分離し、分離された階調信号を補正階調信号 $G'_{n-1}$ として定義してデータドライバー300に出力する。例えば、前記第2補正階調信号 $G_{n-1}$ が48ビットを有すると前記補正階調信号 $G_{n-1}$ は24ビットを有するようになる。

このように、本発明の第2実施形態による階調信号補正部は一つのフレームメモリのみを備えても以前フレームの階調信号と現在フレームの階調信号と次フレームの階調信号とを考慮して前記現在フレームに対応する補正階調信号を出力することができる。

40

## 【0148】

図16～図19は前記した図15の階調信号補正部の動作を概念的に説明するための図面である。

図16に示すように、 $n-2$ 番目フレームの階調信号 $G_{n-2}$ が階調信号変換器456

に提供されることにより、階調信号変換器 456 は n - 2 番目フレームの第 1 補正階調信号 G' n - 2 をフレームメモリ 452 に提供する。

#### 【0149】

一方、図 17 に示すように、n - 1 番目フレームの階調信号 G n - 1 が階調信号変換器 456 に提供されることにより、階調信号変換器 456 はコントローラ 454 から提供されるリードクロック R に応答してフレームメモリ 452 から n - 2 番目フレームの第 1 補正階調信号 G' n - 2 を抽出し、n - 1 番目フレームの第 1 補正階調信号 G' n - 1 をフレームメモリ 452 に提供し、前記 n - 2 番目フレームの第 1 補正階調信号 G' n - 2 と前記 n - 1 番目フレームの階調信号 G n - 1 とを考慮して n - 2 番目フレームの第 2 補正階調信号 G' n - 2 を出力する。 10

#### 【0150】

一方、図 18 に示すように、n 番目フレームの階調信号 G n が階調信号変換器 456 に提供されることにより、階調信号変換器 456 はコントローラ 454 から提供されるリードクロック R に応答してフレームメモリ 452 から n - 1 番目フレームの第 1 補正階調信号 G' n - 1 を抽出し、n 番目フレームの第 1 補正階調信号 G' n をフレームメモリ 452 に提供し、前記 n - 1 番目フレームの第 1 補正階調信号 G' n - 1 と前記 n 番目フレームの階調信号 G n とを考慮して n - 1 番目フレームの第 2 補正階調信号 G' n - 1 を出力する。

#### 【0151】

一方、図 19 に示すように、n + 1 番目フレームの階調信号 G n + 1 が階調信号変換器 456 に提供されることにより、階調信号変換器 456 はコントローラ 454 から提供されるリードクロック R に応答してフレームメモリ 452 から n 番目フレームの第 1 補正階調信号 G' n を抽出し、n + 1 番目フレームの第 1 補正階調信号 G' n + 1 をフレームメモリ 452 に提供し、前記 n 番目フレームの第 1 補正階調信号 G' n と前記 n + 1 番目フレームの階調信号 G n + 1 とを考慮して n 番目フレームの第 2 補正信号 G' n を出力する。 20

#### 【0152】

このように、本発明の第 2 実施形態による補正階調信号は原始階調信号を対比して 1 フレームずつ遅延されて出力され、特に低電圧が要求されるブラック階調から高電圧が要求されるホワイト階調に急変するとき、まず液晶をプリチルトさせるためのプリチルト形成信号を出力した後、次に高い高階調の信号が入力されるので液晶の応答速度を向上させることができる。 30

#### 【0153】

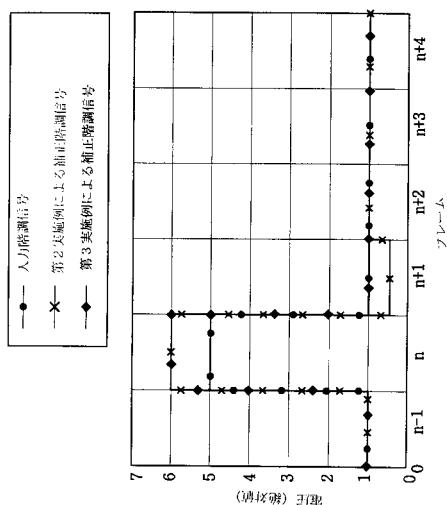

図 20 は本発明の第 2 実施形態による入力階調信号と出力補正階調信号とを対比して示す波形図で、特に、前記した本発明の第 1 実施形態による入力階調信号と出力補正信号とを対比した波形図を共に図示する。

図 20 に示すように、n - 1 番目フレームの期間 1 ボルトに対応し、n 番目と n + 1 番目フレームの期間 5 ボルトに対応し、n + 2 番目フレームの以後には 3 ボルトに対応する原始階調信号に入力されると、本発明の第 2 実施形態による補正階調信号は次のように出力される。 40

#### 【0154】

即ち、n - 1 番目フレームの期間 1 ボルトに対応する階調信号を保持し、n 番目フレームの期間には液晶をプリチルトさせるための形成信号として前記 1 ボルトよりは高い大略 1.5 ボルトに対応し、n + 1 番目フレームの期間前記 5 ボルトより高い 6 ボルトに対応し、n + 2 番目フレームの期間 5 ボルトより低い大略 4.8 ボルトに対応し、n + 3 番目フレームの期間 3 ボルトよりは低い 2.5 ボルトに対応し、n + 4 番目フレームの期間には 3 ボルトよりは若干高い 3.2 ボルトに対応し、n + 5 番目フレームから 3 ボルトに対応する補正階調信号が出力される。

#### 【0155】

このように、本発明の第 2 実施形態においては一つのメモリを使用する。このとき、前 50

記フレームメモリには現在フレームの階調信号が保存されるのではなく、階調信号変換器で以前フレームの階調信号とその以前フレームの階調信号とを根拠にして変換された第1補正階調信号が保存される。そして、出力されるのは予め保存された第1補正階調信号と現在フレームの階調信号とを比較して液晶をプリチルトさせる必要がある場合またその変換を経て第2補正階調信号を出力する。

#### 【0156】

前記した本発明の第1実施形態においては以前フレームの階調信号とその以前フレームの階調信号を保存して、現在フレームの階調信号と共に3つのフレームを比べるが、本発明の第2実施形態においては以前フレームの階調信号とその以前フレームの階調信号とが比較されたデータである第1補正階調信号が保存され、第1補正階調信号と現在フレームの階調信号とが比較される。このため、前記した方法においてメモリを減らすことで発生する情報損失分がある。10

#### 【0157】

前記した本発明の第2実施形態を適用すると前記した図20のように $n+1$ 番目と $n+4$ 番目フレームで2回のオーバーシュート波形が反復される。即ち、階調信号変換器で現在フレームの階調信号と以前フレームの階調信号とを比較するのではなく、現在フレームの階調信号と第1補正階調信号とを比較するからである。しかし、二番目に発生されるオーバーシュート波形即ち、 $n+4$ 番目フレームで発生されるオーバーシュート波形の大きさは一番目のオーバーシュート波形に比べてその大きさが顕著に小さくなるので液晶の応答速度差異は殆ど発生しない。20

#### 【0158】

しかし、前記した本発明の第2実施形態による補正階調信号にはオーバーシュート波形が発生された後リップル波形が発生する。それは、前記フレームメモリには現在フレームの階調信号が保存されるのではなく、階調信号変換器で変換された第1補正階調信号が保存され、出力されるのは以前第1補正階調信号と現在階調信号とを考慮してプリチルトまたはオーバーシューティングする必要がある場合にはまたの変換を経て以前第2補正階調信号が出力されるからである。

#### 【0159】

前記したリップル波形は目標値階調信号に未達するか超過して所望する階調レベルに至らなくディスプレー品質を悪化させる恐れがある。30

そうすると、前記リップル波形の発生を抑制するための階調信号補正部を下記する図面を参照して説明する。

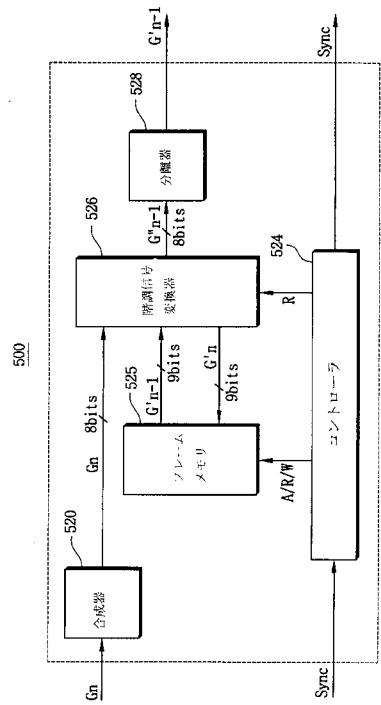

図21は本発明の第3実施形態による階調信号補正部を示すための図である。

#### 【0160】

図21に示すように、本発明の第3実施形態による階調信号補正部500は合成器520、フレームメモリ525、コントローラ524、階調信号変換器526及び分離器528を含み、現在原始階調信号 $G_n$ の提供を受け以前フレームに対応する階調信号 $G_{n-1}$ を出力する。52

合成器520はグラフィックコントローラのような階調信号ソース(図示せず)から伝送される現在原始階調信号 $G_n$ を受信し、階調信号補正部500が処理可能な速度でデータストリームの周波数を変換した後変換された現在階調信号を階調信号変換器526に提供する。図面上では説明の便宜上現在原始階調信号 $G_n$ が8ビットであるのを図示する。勿論、前記原始階調信号がR、G、B階調信号であるとそれぞれのR、G、B階調信号は8ビットからなり、総24ビットの原始階調信号 $G_n$ が階調信号変換器526に提供される。40

#### 【0161】

フレームメモリ525はコントローラ524から提供されるアドレスクロックA及びリードクロックRに応答して予め保存された以前第1補正階調信号 $G_{n-1}$ を階調信号変換器526に出力すると同時に、コントローラ526から提供されるアドレスクロックA及びライトクロックWに応答して階調信号変換器526から提供される現在第1補正階調信50

号  $G_n$  を保存する。

【0162】

前記フレームメモリ525に保存される以前第1補正階調信号  $G_{n-1}$  や現在第1補正階調信号  $G_n$  はオーバーシューティングのためのオプション信号を含む。前記オプション信号は第1ビットからなり、前記第1補正階調信号 ( $G_{n-1}$  または  $G_n$ ) が前記オーバーシューティングのために変換された場合であると前記オプション信号には1が記入され、前記オーバーシューティングのために未変換された場合であると前記オプション信号には0が記入される。即ち、前記オプション信号には該当フレームのオーバーシュート適用可否に対するヒストリー情報が含まれる。

【0163】

階調信号変換器526はコントローラ524から提供されるリードクロックRに応答して合成器520から出力される8ビットの現在階調信号  $G_n$  と、フレームメモリ525から出力される9ビットの以前第1補正階調信号  $G_{n-1}$  を考慮して8ビットの以前第2補正階調信号  $G'_{n-1}$  を生成した後分離器528に提供すると同時に、9ビットの現在第1補正階調信号  $G_n$  をフレームメモリ525に保存されるように提供する。

【0164】

つまり、階調信号変換器526はフレームメモリ525に保存された  $n-1$  番目第1補正階調信号  $G'_{n-1}$  と合成器520を経由して提供される  $n$  番目原始階調信号  $G_n$  が相異する場合、 $n$  番目フレーム駆動時  $n$  番目目標電圧より高いオーバーシュート波形が印加されるように第2補正階調信号  $G'_{n-1}$  を出力する。このとき、前記  $n$  番目原始階調信号  $G_n$  と比べられる前記  $n-1$  番目第1補正階調信号  $G'_{n-1}$  は1ビットのオプション信号を除いた8ビットが利用される。前記1ビットのオプション信号は連続してオーバーシュート波形が印加されないように利用される。

【0165】

一方、階調信号変換器526は  $n-1$  番目階調信号がブラック階調である場合、 $n$  番目フレームが明るい階調またはホワイト階調であると  $n-1$  番目フレームには前記ブラック階調よりは高い階調信号を印加して液晶をプリチルトさせるための第2補正階調信号  $G'_{n-1}$  を出力する。このとき、前記  $n$  番目原始階調信号  $G_n$  と比べられる前記  $n-1$  番目第1補正階調信号  $G'_{n-1}$  は1ビットのオプション信号を除いた8ビットが利用される。

【0166】

分離器528は第2補正階調信号  $G'_{n-1}$  を分離し、分離された階調信号を補正階調信号  $G'_{n-1}$  として定義してデータドライバー300に出力する。例えば、前記第2補正階調信号  $G'_{n-1}$  が48ビットを有すると前記補正階調信号  $G_{n-1}$  は24ビットを有する。

図面上では合成器510と分離器518を図示したが、これを省略しても良いのである。

【0167】

このように、本発明の第3実施形態によると階調信号補正部に一つのフレームメモリのみを備えても以前階調信号と現在階調信号と次階調信号とを考慮して前記現在フレームに対応する補正階調信号を出力できるだけではなく、連続してオーバーシュート波形が印加されないようにすることができる。

具体的に、補正階調信号は原始階調信号を対比して1フレーム期間ずつ遅延されて出力され、特に低電圧が要求されるブラック階調から高電圧が要求されるホワイト階調に急変するときまず液晶をプリチルトさせるためのプリチルト形成信号を出力した後、その次に高いオーバーシューティングされた高階調の信号が入力されるので液晶の応答速度を向上させることができる。

【0168】

また、前記したプリチルト形成信号を発生した後、オーバーシュートが発生するとフレームメモリに保存される第1補正階調信号に含まれるオプション信号を活性化させ次フレ

10

20

30

40

50

ームでオーバーシュートが発生されることを遮断することによりオーバーシュートされない原始階調信号が出力される。これによって、前記補正階調信号にリップルが発生されることを遮断することができる。

#### 【0169】

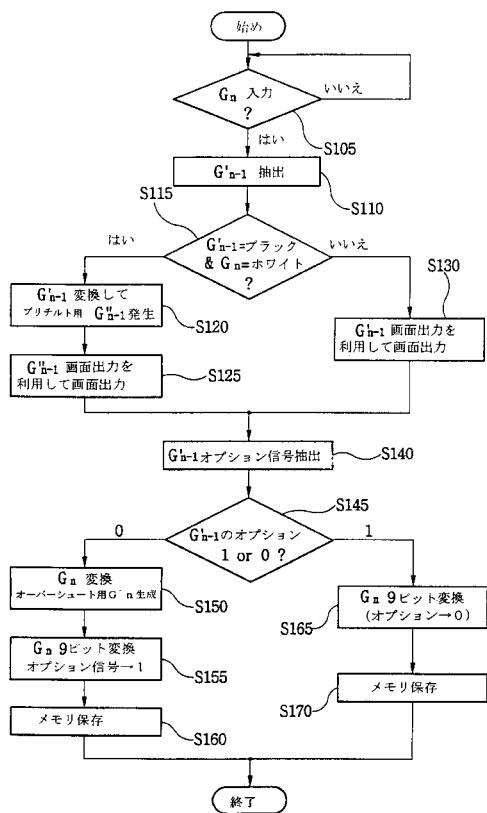

図22は前記した図21の動作を説明するための流れ図である。特に、本発明の第3実施形態による階調信号変換器の動作を説明する。

図21及び図22に示すように、外部のグラフィックコントローラのようなホストから現在原始階調信号G<sub>n</sub>の入力可否を判断して(段階S105)、前記現在原始階調信号が入力されることで判断される場合にはフレームメモリ452に保存された以前第1補正階調信号G'\_{n-1}を抽出する(段階S110)。前記現在原始階調信号G<sub>n</sub>の大きさが8ビットであるとフレームメモリ452に保存された以前第1補正階調信号G'\_{n-1}の大きさは1ビットのオプション信号が付加された9ビットである。

10

#### 【0170】

続いて、前記以前第1補正階調信号G'\_{n-1}がブラック階調で、現在原始階調信号G<sub>n</sub>がホワイト階調である第1条件を満足するかの可否を判断する(段階S115)。前記ブラック階調はフル-ブラック階調でもあり、前記フル-ブラック階調に近接する階調でもあり、前記ホワイト階調はフル-ホワイト階調でもあり、前記フル-ホワイト階調に近接する階調でもある。

20

前記段階S115で前記第1条件を満足すると判断される場合には液晶の応答速度を高速化するために以前第1補正階調信号G'\_{n-1}を変換して以前第2補正階調信号G'\_{n-1}を生成した後(段階S120)、生成された以前第2補正階調信号G'\_{n-1}を利用して画面を出力する(段階S125)。

#### 【0171】

一方、前記段階S115で前記第1条件を満足しないと判断される場合には以前第1補正階調信号G'\_{n-1}を利用して画面を出力する(段階S130)。

前記段階S125及び段階S130に続き、前記以前第1補正階調信号G'\_{n-1}に含まれたオプション信号を抽出する(段階S140)。前記オプション信号には以前フレームに対応してオーバーシューティングされた波形の出力ヒストリー情報が含まれる。

30

#### 【0172】

続いて、前記段階S140で抽出されたオプション信号が1か0かが判断される(段階S145)。例えば、前記オプション信号が1である場合には以前フレームに対応してオーバーシューティングされた波形が出力されたヒストリー情報が含まれる。

40

前記段階S145で以前第1補正階調信号G'\_{n-1}のオプション信号が0と判断される場合には以前フレームに対応してオーバーシューティングされた波形が未出力されたこととして見なして現在階調信号G<sub>n</sub>の変換を通じてオーバーシュート発生のための現在第1補正階調信号G'\_{n}を生成する(段階S150)。続いて、前記段階S150で生成された現在第1補正階調信号G'\_{n}に1ビットのオプション信号、例えば1のオプション信号を付加した後(段階S155)、フレームメモリ452に保存する(段階S160)。前記フレームメモリ452に保存された活性化されたオプション信号と現在第1補正階調信号G'\_{n}は次フレームに対応する階調信号出力時利用される。

#### 【0173】

前記段階S145で以前第1補正階調信号G'\_{n-1}のオプション信号が1として判断される場合には以前フレームに対応してオーバーシューティングされた波形が出力されたこととして見なして現在階調信号G<sub>n</sub>に1ビットのオプション信号、例えば0のオプション信号を付加した後(段階S165)、フレームメモリ452に保存する(段階S170)。前記フレームメモリ452に保存された非活性化されたオプション信号と現在第1補正階調信号は次フレームに対応する階調信号出力時利用される。

#### 【0174】

図23は本発明の第3実施形態による入力階調信号と出力補正階調信号とを対比して示す波形図である。

50

図23に示すように、n-1番目フレームの期間1ボルトに対応し、n番目フレーム以後に5ボルトに対応する原始階調信号が入力されると、本発明の第3実施形態による補正階調信号は次のように出力される。

#### 【0175】

n-1番目フレームの期間1ボルトに対応する階調信号を保持し、n番目フレームの期間には液晶をプリチルトさせるための形成信号として前記1ボルトよりは高い大略1.5ボルトに対応する補正階調信号が出力される。

続いて、n+1番目フレームの期間前記5ボルトより高い6ボルトに対応する補正階調信号が出力され、n+2番目フレームからはオーバーシュート発生が抑制されてこそ5ボルトに対応する補正階調信号が出力される。

#### 【0176】

前記したオーバーシュート発生の抑制によりリップルが発生されることを遮断でき、これによって一回のオーバーシュート波形が発生された以後に正常的に該当階調信号を用いて画像をディスプレーすることができる。

以上、本発明の第3実施形態においては一つのピクセルに2フレーム連続して変わる原始階調信号が入力されるとき2番目フレームに対応してはオーバーシュートが適用されない原始階調信号が出力されるので前記2番目のフレームでは画面に残像が存在し得る可能性がある。しかし、T V信号やD V D信号など大部分の場合には30Hz未満の信号を出力するので60Hz駆動時二つのフレームが連続変わる信号が入力される場合は殆どない。

#### 【0177】

モニターの場合2回連続変わる場合があるが、このとき、オーバーシュートが2回連続適用され過度に補償されて画面が歪曲される。

即ち、図24に示されたように、本発明の第2実施形態によるとn番目フレームをディスプレーするとき、ブラック階調からホワイト階調に急激に変換されると一番目オーバーシュート（即ち、ホワイトオーバーシュート）が発生され、n+1番目フレームをディスプレーするとき、ホワイト階調からブラック階調に急激に変換されると2番目オーバーシュート（即ち、ブラックオーバーシュートまたはアンダーシュート）が発生される。前記二番目オーバーシュートはn+1番目フレームをディスプレーするが実質にディスプレー歪曲を誘発する。それは目標値階調電圧は1ボルトであるが、供給される階調電圧は大略0.5ボルトであるので液晶キャパシターに正常に充電されないからである。

#### 【0178】

しかし、本発明の第3実施形態によると、n番目フレームをディスプレーするとき、ブラック階調からホワイト階調に急激に変換されると一番目のオーバーシュートが発生され、n+1番目フレームをディスプレーするとき、ホワイト階調からブラック階調に階調が急激に変換されても二番目オーバーシュートが発生されることを遮断し、該当入力階調信号がそのまま出力される。これによって、オーバーシュート変換後発生されるリップルを遮断してディスプレー不良を解決することができる。

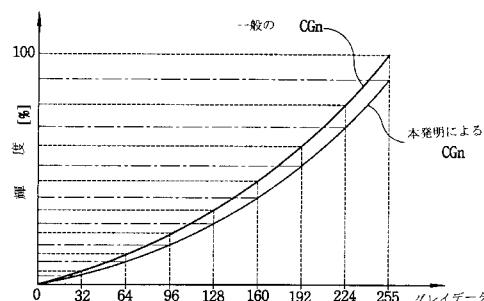

#### 【0179】

一方、液晶表示装置はR、G、Bそれぞれの階調毎に色感が異なって示される視認性の問題と、色温度が変わる問題を解決するために自動色補償方式（以下、ACC）を採用している。

すなわち、外部から印加される原始画像データをR、G、Bそれぞれに対して別途に調節して互いに異なるR、G、Bそれぞれのガンマ曲線を一つの曲線に示すことで、階調毎に色感が異なって示される視認性の問題点及び色温度が変化する問題点を解決することができる。

#### 【0180】

下記する表2は一般の自動色補償方式ACCにより入力されるデータに対応して変換されたデータを説明する。

#### 【0181】

10

20

30

40

50

【表2】

| 入力<br>8<br>ビット | 10<br>ビット<br>変換 | ACC変換データ<br>(10ビット) |      |      | ACC変換データ<br>(8ビット) |     |         |

|----------------|-----------------|---------------------|------|------|--------------------|-----|---------|

|                |                 | R                   | G    | B    | R                  | G   | B       |

| 0              | 0               | 0                   | 0    | 0    | 0                  | 0   | 0       |

| 1              | 4               | 4                   | 4    | 4    | 1                  | 1   | 1       |

| 2              | 8               | 8                   | 8    | 7    | 2                  | 2   | 1. 75   |

| 3              | 12              | 13                  | 12   | 11   | 3. 25              | 3   | 2. 75   |

| 4              | 16              | 17                  | 16   | 15   | 4. 25              | 4   | 3. 75   |

| 5              | 20              | 21                  | 20   | 18   | 5. 25              | 5   | 4. 5    |

| ...            | ...             | ...                 | ...  | ...  | ...                | ... | ...     |

| 250            | 1000            | 1004                | 1000 | 992  | 251                | 250 | 248     |

| 251            | 1004            | 1007                | 1004 | 998  | 251. 75            | 251 | 249. 5  |

| 252            | 1008            | 1010                | 1008 | 1003 | 252. 5             | 252 | 250. 75 |

| 253            | 1012            | 1014                | 1012 | 1009 | 253. 5             | 253 | 252. 25 |

| 254            | 1016            | 1017                | 1016 | 1014 | 254. 25            | 254 | 253. 5  |

| 255            | 1020            | 1020                | 1020 | 1020 | 255                | 255 | 255     |

10

20