特開2002 - 229532

(P2002 - 229532A)

(43)公開日 平成14年8月16日(2002.8.16)

| (51) Int.CI <sup>7</sup> | 識別記号   | F I           | テ-マコード <sup>8</sup> (参考) |

|--------------------------|--------|---------------|--------------------------|

| G 0 9 G 3/36             |        | G 0 9 G 3/36  | 2 H 0 9 2                |

| G 0 2 F 1/133            | 510    | G 0 2 F 1/133 | 2 H 0 9 3                |

|                          | 550    |               | 5 C 0 0 6                |

|                          | 1/1343 |               | 5 C 0 8 0                |

| G 0 9 G 3/20             | 611    | G 0 9 G 3/20  | 611 F                    |

審査請求 未請求 請求項の数 18〇 L (全 13数) 最終頁に続く

(21)出願番号 特願2001 - 351795(P2001 - 351795)

(22)出願日 平成13年11月16日(2001.11.16)

(31)優先権主張番号 特願2000 - 365426(P2000 - 365426)

(32)優先日 平成12年11月30日(2000.11.30)

(33)優先権主張国 日本(JP)

(71)出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(72)発明者 木村 裕之

埼玉県深谷市幡羅町一丁目9番地2 株式会

社東芝深谷工場内

(72)発明者 紺島 貴徳

埼玉県深谷市幡羅町一丁目9番地2 株式会

社東芝深谷工場内

(74)代理人 100083806

弁理士 三好 秀和 (外7名)

最終頁に続く

(54)【発明の名称】 液晶表示装置及び液晶表示装置の駆動方法

(57)【要約】

【課題】 携帯電話等のディスプレイとして用いられる液晶表示装置において、画面の高精細化を実現し、且つ高精細画素に対しても、待ち受け時には低消費電力で静止画表示を行い、また通話時にはフルカラーによる中間調表示や動画表示を行うことができるようとする。

【解決手段】 DM (デジタルメモリ) 18を、1つのインバータ回路23 (又はインバータ回路23と第2の容量素子25) で構成することにより、DM18を構成する素子数を削減し、DM18の配置領域を小さくして画面の高精細化を可能とする。また、通話時には、フルカラー用映像信号により中間調/動画表示を行い、待ち受け時には、走査線/信号線駆動回路の動作を止めつつ、DM18に保持されたマルチカラー用映像信号を画像表示に用いることにより、高精細画素に対しても低消費電力でマルチカラー表示を行うことができる。

## 【特許請求の範囲】

【請求項1】 互いに交差して配置された複数の走査線及び複数の信号線、これら両線の各交差部に配置された画素電極、前記画素電極と電気的に並列に接続された第1の容量素子、前記走査線に供給される行選択信号によりオン／オフ制御され、オン時に前記信号線と前記画素電極間を導通させて前記信号線に供給された映像信号を前記画素電極に書き込む第1のスイッチ素子を含む第1の電極基板と、前記画素電極に対し所定間隔をもって対向配置された対向電極を含む第2の電極基板と、前記第1の電極基板と第2の電極基板との間に狭持された液晶層と、一水平走査期間に対応して前記複数の信号線に映像信号を供給する信号線駆動回路と、前記一水平走査期間毎に前記走査線に行選択信号を順次供給する走査線駆動回路とを備えた液晶表示装置において、

前記第1の電極基板は、

前記信号線に供給された映像信号を保持可能な1つのインバータ回路により構成されたデジタルメモリと、前記画素電極と前記デジタルメモリ間の導通を制御するデジタルメモリスイッチ回路と、

を含むことを特徴とする液晶表示装置。

【請求項2】 前記デジタルメモリは、1つのインバータ回路と第2の容量素子により構成されることを特徴とする請求項1に記載の液晶表示装置。

【請求項3】 前記インバータ回路は、CMOS回路で構成されることを特徴とする請求項1又は2に記載の液晶表示装置。

【請求項4】 前記画素電極は、金属薄膜で構成された光反射型の画素電極であることを特徴とする請求項1に記載の液晶表示装置。

【請求項5】 前記デジタルメモリスイッチ回路は、前記デジタルメモリの入力端子に接続する第2のスイッチ素子と、前記デジタルメモリの出力端子に接続する第3のスイッチ素子とで構成されることを特徴とする請求項1又は2に記載の液晶表示装置。

【請求項6】 前記デジタルメモリスイッチ回路は、前記デジタルメモリの入力端子に接続する第2のスイッチ素子と、前記デジタルメモリの出力端子に接続する第3のスイッチ素子とで構成され、

前記第2の容量素子は、前記第2のスイッチ素子と前記インバータ回路との間に接続されることを特徴とする請求項2に記載の液晶表示装置。

【請求項7】 前記第2のスイッチ素子及び前記第3のスイッチ素子は同一導電型の電界制御トランジスタで構成され、それぞれ異なる制御信号線に接続されることを特徴とする請求項5に記載の液晶表示装置。

【請求項8】 前記第2のスイッチ素子及び前記第3のスイッチ素子は互いに異なる導電型の電界制御トランジスタで構成され、それぞれ共通の制御信号線に接続されることを特徴とする請求項5に記載の液晶表示装置。

【請求項9】 前記インバータ回路を構成するCMOS回路に、第3及び第4の容量素子が接続されることを特徴とする請求項3に記載の液晶表示装置。

【請求項10】 前記デジタルメモリの電源配線の一方と、前記第1の容量素子に所定の電圧を供給する電源配線とを共通化したことを特徴とする請求項1に記載の液晶表示装置。

【請求項11】 第1の表示期間では、前記デジタルメモリスイッチ回路により前記画素電極と前記デジタルメモリ間を非導通とし、且つ、前記第1のスイッチ素子を所定周期でオンして、前記信号線に供給された第1の映像信号を前記画素電極に書き込むことで表示を行い、

第2の表示期間では、前記デジタルメモリスイッチ回路により前記画素電極と前記デジタルメモリ間を導通させて、前記信号線に供給された第2の映像信号を前記デジタルメモリに保持させた後、前記第1のスイッチ素子により前記信号線と前記画素電極間を非導通とし、前記デジタルメモリに保持された第2の映像信号を前記画素電極に書き込むことで表示を行うことを特徴とする請求項1に記載の液晶表示装置の駆動方法。

【請求項12】 前記第1の表示期間では、前記デジタルメモリスイッチ回路において、前記第2のスイッチ素子と画素電極間のみ導通させることを特徴とする請求項1に記載の液晶表示装置の駆動方法。

【請求項13】 前記第2の表示期間では、1フレーム毎に前記第2のスイッチ素子と第3のスイッチ素子を交互に導通させて、前記画素電極に前記デジタルメモリから1フレーム毎に極性の異なる第2の映像信号を供給し、且つ、この周期に合わせて前記対向電極の電位を反転させることを特徴とする請求項11又は12に記載の液晶表示装置の駆動方法。

【請求項14】 前記第2の表示期間において、前記第3のスイッチ素子の導通時間が、前記第2のスイッチ素子の導通時間よりも長いことを特徴とする請求項13に記載の液晶表示装置の駆動方法。

【請求項15】 前記第2の表示期間では、所定フレーム数毎に前記デジタルメモリスイッチ回路により前記画素電極と前記デジタルメモリ間を導通させて、前記信号線に供給された第2の映像信号を前記デジタルメモリに保持させた後、前記第1のスイッチ素子により前記信号線と前記画素電極間を非導通とし、前記デジタルメモリに保持された第2の映像信号を所定フレーム数の間、前記画素電極に書き込むことで表示を行うことを特徴とする請求項11又は12に記載の液晶表示装置の駆動方法。

【請求項16】 前記第2の表示期間では、所定フレーム数毎に前記デジタルメモリに極性の異なる第2の映像信号を保持させ、且つ、この周期に合わせて前記対向電極の電位を反転させることを特徴とする請求項15に

記載の液晶表示装置の駆動方法。

【請求項17】前記デジタルメモリに直流の電源電圧を供給することを特徴とする請求項11乃至16のいずれか一つに記載の液晶表示装置の駆動方法。

【請求項18】前記デジタルメモリに交流の電源電圧を供給し、且つ、前記交流の周期に合わせて前記対向電極の電位を反転させることを特徴とする請求項15又は16に記載の液晶表示装置の駆動方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】この発明は、携帯電話や電子ブック等に使用される高画質、低消費電力な液晶表示装置及び液晶表示装置の駆動方法に関する。

【0002】

【従来の技術】従来、液晶表示装置は軽量、薄型、低消費電力という利点を活かして携帯電話や電子ブック等の小型情報端末のディスプレイとして使われている。このような小型情報端末は、一般にバッテリー駆動方式が採用されていることから、低消費電力化が重要な課題となっている。

【0003】とくに携帯電話においては、待ち受け時間中に低消費電力で表示できることが求められており、これを実現するための技術として、例えば特開2001-264814号公報には、画素内にデジタルメモリを備えた画像表示装置が開示されている。ここに開示された画像表示装置は、待ち受け時（静止画表示時）において、前記デジタルメモリに保持した二値データにより液晶を交流駆動するための交流駆動回路のみを動作させ、その他の周辺駆動回路を止めることにより、大幅な消費電力の低減を図っている。

【0004】

【発明が解決しようとする課題】ところで、従来のデジタルメモリを備えた液晶表示装置では、デジタルメモリとしてSRAMが使用されており、通常は5個のトランジスタで構成されている。このため、基板上にある程度のデジタルメモリの配置領域が必要となり、高精細化が困難な状況となっている。

【0005】この発明の目的は、画素の高精細化を実現するとともに、高精細画素に対して、待ち受け時には低消費電力で静止画表示を行い、また通話時にはフルカラーによる中間調表示や動画表示を行うことができる液晶表示装置及びその駆動方法を提供することにある。

【0006】

【課題を解決するための手段】上記目的を達成するため、請求項1の発明は、互いに交差して配置された複数の走査線及び複数の信号線、これら両線の各交差部に配置された画素電極、前記画素電極と電気的に並列に接続された第1の容量素子、前記走査線に供給される行選択信号によりオン／オフ制御され、オン時に前記信号線と前記画素電極間を導通させて前記信号線に供給された映

像信号を前記画素電極に書き込む第1のスイッチ素子を含む第1の電極基板と、前記画素電極に対し所定間隔をもって対向配置された対向電極を含む第2の電極基板と、前記第1の電極基板と第2の電極基板との間に狭持された液晶層と、一水平走査期間に対応して前記複数の信号線に映像信号を供給する信号線駆動回路と、前記一水平走査期間毎に前記走査線に行選択信号を順次供給する走査線駆動回路とを備えた液晶表示装置において、前記第1の電極基板は、前記信号線に供給された映像信号を保持可能な1つのインバータ回路により構成されたデジタルメモリと、前記画素電極と前記デジタルメモリ間の導通を制御するデジタルメモリスイッチ回路とを含むことを特徴とする。

【0007】好ましい形態として、前記第1のスイッチ素子と前記デジタルメモリスイッチ回路を、ともにMOSトランジスタで構成する。

【0008】請求項2の発明は、請求項1において、前記デジタルメモリを、1つのインバータ回路と第2の容量素子により構成することを特徴とする。

【0009】好ましい形態として、前記第1の容量素子と前記第2の容量素子の容量を合わせて、通常駆動に必要な容量を形成する。

【0010】請求項3の発明は、請求項1又は2において、前記インバータ回路がCMOS回路で構成されることを特徴とする。

【0011】請求項4の発明は、請求項1において、前記画素電極が金属薄膜で構成された光反射型の画素電極であることを特徴とする。

【0012】請求項5の発明は、請求項1又は2において、前記デジタルメモリスイッチ回路が、前記デジタルメモリの入力端子に接続する第2のスイッチ素子と、前記デジタルメモリの出力端子に接続する第3のスイッチ素子とで構成されることを特徴とする。

【0013】請求項6の発明は、請求項2において、前記デジタルメモリスイッチ回路が、前記デジタルメモリの入力端子に接続する第2のスイッチ素子と、前記デジタルメモリの出力端子に接続する第3のスイッチ素子とで構成され、前記第2の容量素子が、前記第2のスイッチ素子と前記インバータ回路との間に接続されることを特徴とする。

【0014】請求項7の発明は、請求項5において、前記第2のスイッチ素子及び前記第3のスイッチ素子が同一導電型の電界制御トランジスタで構成され、それぞれ異なる制御信号線に接続されることを特徴とする。

【0015】好ましい形態として、前記第2及び第3のスイッチ素子をN-ch TFT又はP-ch TFTのいずれか一方で構成するとともに、それぞれ個別のメモリ制御信号線に接続し、各メモリ制御信号線から供給されるメモリ制御信号により、前記第2及び第3のスイッチ素子の導通を独立して制御する。

【0016】請求項8の発明は、請求項5において、前記第2のスイッチ素子及び前記第3のスイッチ素子が互いに異なる導電型の電界制御トランジスタで構成され、それぞれ共通の制御信号線に接続されることを特徴とする。

【0017】好ましい形態として、前記第2及び第3のスイッチ素子をN-ch TFT及びP-ch TFTで構成する。ここで、前記第2のスイッチ素子をN-ch TFTで構成した場合、前記第3のスイッチ素子はP-ch TFTで構成され、前記第2のスイッチ素子をP-ch TFTで構成した場合、前記第3のスイッチ素子はN-ch TFTで構成される。さらに、前記第2及び第3のスイッチ素子を同一のメモリ制御信号線に接続し、1つのメモリ制御信号線から供給されるメモリ制御信号により、前記第2及び第3のスイッチ素子の導通を共通に制御する。

【0018】請求項9の発明は、請求項3において、前記インバータ回路を構成するCMOS回路に、第3及び第4の容量素子が接続されることを特徴とする。

【0019】好ましい形態として、前記第1の容量素子、前記第2の容量素子、前記第3及び第4の容量素子の容量を合わせて、通常駆動に必要な容量を形成する。

【0020】請求項10の発明は、請求項1において、前記ディジタルメモリの電源配線の一方と、前記第1の容量素子に所定の電圧を供給する電源配線とを共通化したことを特徴とする。

【0021】請求項11の発明は、請求項1に記載の液晶表示装置の駆動方法において、第1の表示期間では、前記ディジタルメモリスイッチ回路により前記画素電極と前記ディジタルメモリ間を非導通とし、且つ、前記第1のスイッチ素子を所定周期でオンして、前記信号線に供給された第1の映像信号を前記画素電極に書き込むことで表示を行い、第2の表示期間では、前記ディジタルメモリスイッチ回路により前記画素電極と前記ディジタルメモリ間を導通させて、前記信号線に供給された第2の映像信号を前記ディジタルメモリに保持させた後、前記第1のスイッチ素子により前記信号線と前記画素電極間を非導通とし、前記ディジタルメモリに保持された第2の映像信号を前記画素電極に書き込むことで表示を行うことを特徴とする。

【0022】請求項12の発明は、請求項11において、前記第1の表示期間では、前記ディジタルメモリスイッチ回路において、前記第2のスイッチ素子と画素電極間のみ導通させることを特徴とする。

【0023】請求項13の発明は、請求項11又は12において、前記第2の表示期間では、1フレーム毎に前記第2のスイッチ素子と第3のスイッチ素子を交互に導通させて、前記画素電極に前記ディジタルメモリから1フレーム毎に極性の異なる第2の映像信号を供給し、且つ、この周期に合わせて前記対向電極の電位を反転させ

ることを特徴とする。

【0024】請求項14の発明は、請求項13において、前記第2の表示期間において、前記第3のスイッチ素子の導通時間が、前記第2のスイッチ素子の導通時間よりも長いことを特徴とする。

【0025】請求項15の発明は、請求項11又は12において、前記第2の表示期間では、所定フレーム数毎に前記ディジタルメモリスイッチ回路により前記画素電極と前記ディジタルメモリ間を導通させて、前記信号線に供給された第2の映像信号を前記ディジタルメモリに保持させた後、前記第1のスイッチ素子により前記信号線と前記画素電極間を非導通とし、前記ディジタルメモリに保持された第2の映像信号を所定フレーム数の間、前記画素電極に書き込むことで表示を行うことを特徴とする。

【0026】好ましい形態として、第1の表示期間では、前記第2のスイッチ素子をオフして前記画素電極と前記ディジタルメモリ間を非導通とし、且つ、前記第1のスイッチ素子を所定周期でオンし、第2の表示期間では、第2の映像信号を前記ディジタルメモリに保持させた後、前記第1のスイッチ素子と前記第2のスイッチ素子をオフ、前記第3のスイッチ素子をオンすることを特徴とする。

【0027】請求項16の発明は、請求項15において、前記第2の表示期間では、所定フレーム数毎に前記ディジタルメモリに極性の異なる第2の映像信号を保持させ、且つ、この周期に合わせて前記対向電極の電位を反転させることを特徴とする。

【0028】請求項17の発明は、請求項11乃至16のいずれか一つにおいて、前記ディジタルメモリに直流の電源電圧を供給することを特徴とする。

【0029】請求項18の発明は、請求項15又は16において、前記ディジタルメモリに交流の電源電圧を供給し、且つ、前記交流の周期に合わせて前記対向電極の電位を反転させることを特徴とする。

【0030】上記構成による液晶表示装置によれば、ディジタルメモリを1つのインバータ回路で構成することにより、従来は5個必要としていたディジタルメモリのトランジスタ数を、インバータ回路のための2個に削減することができる。したがって、基板上でのディジタルメモリの配置領域を小さくすることが可能となり、画面の高精細化を実現することができる。

【0031】また、上記液晶表示装置においては、通話時(第1の表示期間)には、通常のフルカラーによる中間調/動画表示を行うことができ、また待ち受け時(第2の表示期間)には、走査線/信号線駆動回路の動作を止めつつ、前記ディジタルメモリに保持された映像信号で画像表示を行うため、高精細画素に対しても低消費電力で静止画表示を行うことができる。

【0032】

【発明の実施の形態】以下、この発明に係わる液晶表示装置及び液晶表示装置の駆動方法を、アクティブマトリクス型液晶表示装置及びその駆動方法に適用した場合の実施形態について説明する。

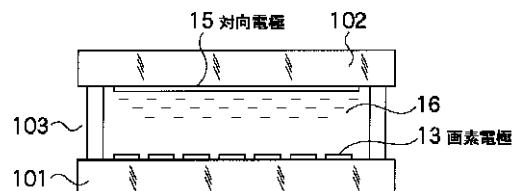

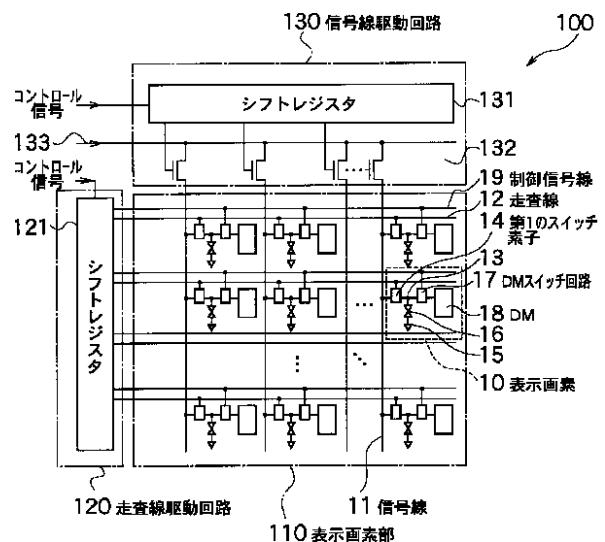

【0033】図3は、この実施形態に係わるアクティブマトリクス型液晶表示装置の回路構成図であり、図4は図3の概略断面図である。

【0034】この液晶表示装置100は、大別すると、複数の表示画素10が形成された表示画素部110、走査線駆動回路120及び信号線駆動回路130により構成されている。

【0035】この実施形態において、走査線駆動回路120及び信号線駆動回路130は、アレイ基板101上において、後述する信号線11、走査線12及び画素電極13などと一体に形成されている。

【0036】表示画素部110は、アレイ基板101上に複数本の信号線11及びこれと交差する複数本の走査線12が図示しない絶縁膜を介してマトリクス状に配置されており、両線の各交差部には表示画素10が形成されている。

【0037】また、アレイ基板101上には、走査線12と並行してメモリ制御信号線19が配置されており、図示しない外部駆動回路からメモリ制御信号が供給されている。なお、後述する実施形態ではメモリ制御信号線19a, 19bとして2本配置した例も示しているが、図3では説明を簡単にするためにメモリ制御信号線19として示している。

【0038】表示画素10は、画素電極13、第1のスイッチ素子14、対向電極15、液晶層16、デジタルメモリスイッチ回路（以下、DMスイッチ回路）17及びデジタルメモリ（以下、DM）18により構成されている。なお、表示画素10には補助容量としての第1の容量素子24が含まれているが、図3では説明を簡単にするために図示を省略している。

【0039】第1のスイッチ素子14のソースは信号線11に、ゲートは走査線12に、ドレインは画素電極13にそれぞれ接続されている。また画素電極13はDMスイッチ回路17を介してDM18に接続されており、そのDMスイッチ回路17のゲートはメモリ制御信号線19に、ソースは画素電極13に、ドレインはDM18にそれぞれ接続されている。

【0040】画素電極13はアレイ基板101上に形成され、この画素電極13と相対する対向電極15は対向基板102上に形成されている。対向電極15には、図示しない外部駆動回路から所定の対向電極電位が与えられている。さらに、画素電極13と対向電極15の間に液晶層16が挟持され、表示画素10ごとに液晶容量C1cを形成している。アレイ基板101と対向基板102の周囲はシール材103により封止されている。図4では、配向膜や偏光板などの図示は省略している。な

お、アレイ基板101、対向基板102は、それぞれ本実施形態における第1の電極基板、第2の電極基板である。

【0041】走査線駆動回路120は、シフトレジスタ121及び図示しないパッファ回路などで構成されており、図示しない外部駆動回路から供給されるコントロール信号（垂直のクロック／スタート信号）に基づいて、一水平走査期間毎に上から順に走査線12に行選択信号を出力する。

【0042】走査線駆動回路120では、中間調表示や動画表示時（以下、通常表示時）には、通常のアクティブマトリクス型液晶表示装置と同様に一水平走査期間毎に行選択信号を走査線12に出力する。また静止画表示時には、全ての走査線12について行選択信号の出力を停止する。

【0043】信号線駆動回路130は、シフトレジスタ131、ASW（アナログスイッチ）132などで構成されており、図示しない外部駆動回路からコントロール信号（水平のクロック／スタート信号）及びビデオバス133を通じて映像信号が供給されている。信号線駆動回路130では、水平のクロック／スタート信号に基づいて、シフトレジスタ131からASW132の開閉信号を供給することにより、ビデオバス133から供給される映像信号を所定のタイミングで信号線11にサンプリングする。

【0044】なお、本実施形態では、通常表示期間において、フルカラーによる中間調表示／動画表示を行うための映像信号をフルカラー用映像信号といい、静止画表示期間において、マルチカラーによる静止画表示を行うための映像信号をマルチカラー用映像信号という。マルチカラー用映像信号とは、二値の情報をもつ映像信号である。RGBの3つのサブ画素（表示画素10）の組み合わせで表示単位としての1画素が構成されるとすると、3つのサブ画素合計で8（2の3乗）色のマルチカラー表示を行うことができる。

【0045】上記通常表示期間、静止画表示期間は、それぞれ本実施形態における第1の表示期間、第2の表示期間である。また、フルカラー用映像信号、マルチカラー用映像信号は、それぞれ本実施形態における第1の映像信号、第2の映像信号である。

【0046】ここで、通常のアクティブマトリクス型液晶表示装置として駆動する場合の動作について簡単に説明する。

【0047】走査線駆動回路120から一水平走査期間ごとに行選択信号を出力して、各走査線12を上から順に選択すると、選択された走査線12に接続するすべての第1のスイッチ素子14が一水平走査期間だけオンする。これと同期するように信号線11に映像信号をサンプリングすると、信号線11にサンプリングされた映像信号は第1のスイッチ素子14を通じて画素電極13に

書き込まれる。このとき、画素電極13に書き込まれた映像信号の電荷の大きさに応じて液晶層16が応答することで表示画素からの透過光量が制御される。このような動作を1フレーム期間内にすべての走査線12について実施することにより、一画面の映像が出来上がる。画素電極13に書き込まれた映像信号は、次フレームで極性反転された新たな映像信号が書き込まれるまで保持される。

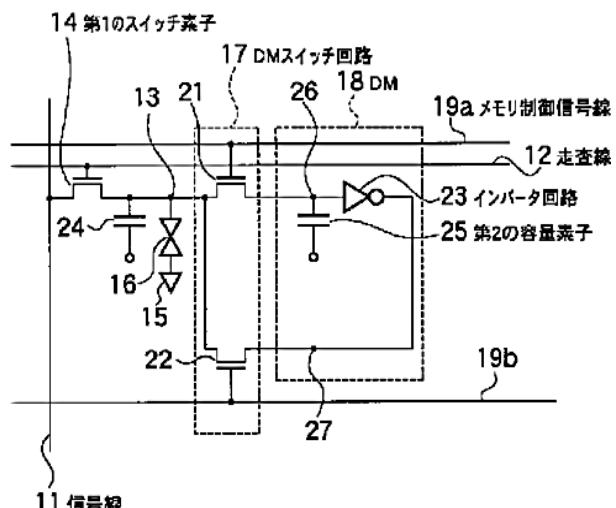

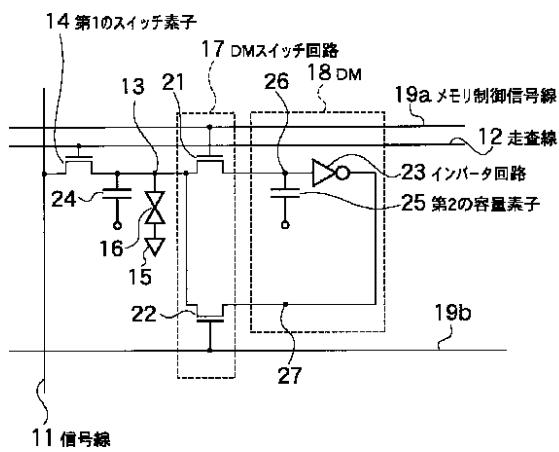

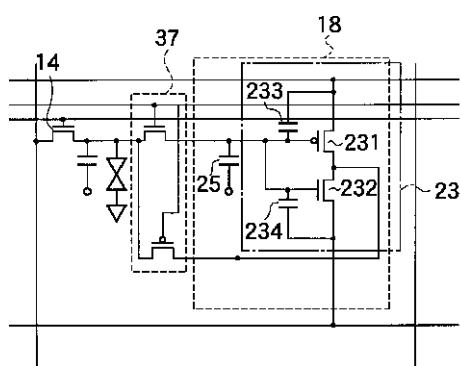

【0048】次に、表示画素10の回路構成を、図1を参照しながら、さらに詳細に説明する。

【0049】図1は、図3に示す表示画素10の回路構成図である。

【0050】第1のスイッチ素子14のドレイン側には、画素電極13及びこれと電気的に並列に第1の容量素子24が接続されている。第1の容量素子24は、画素電極13と図示しない補助容量線との間に補助容量Csを形成している。前記補助容量線には、図示しない外部駆動回路から所定の補助容量電圧が供給されている。この第1の容量素子24は、画素電極13に書き込まれた映像信号を安定して保持するためのものであり、画素電極13に書き込まれた前記映像信号は、液晶容量C1cと補助容量Csとにそれぞれ充電電荷として保持される。

【0051】DMスイッチ回路17は、N-ch TFTからなる第2のスイッチ素子21と、同じくN-ch TFTからなる第3のスイッチ素子22とで構成されており、DM18の入力端子26及び出力端子27と、画素電極13との間に挿入されている。DMスイッチ回路17のうち、第2のスイッチ素子21のゲートはメモリ制御信号線19aに接続され、第3のスイッチ素子22のゲートはメモリ制御信号線19bに接続されている。メモリ制御信号線19a、19bには、図示しない外部駆動回路からオン又はオフレベルのメモリ制御信号が供給され、これにより第2のスイッチ素子21と第3のスイッチ素子22のオン/オフは独立して制御される。この実施形態において、第1のスイッチ素子14とDMスイッチ回路17は、ともにMOSトランジスタで構成されている。

【0052】DM18は、1つのインバータ回路23と第2の容量素子25とから構成されている。静止画表示の際にDM18に書き込まれるマルチカラー用映像信号は、インバータ回路23のみでも保持することができるが、第2の容量素子25を接続することにより、インバータ回路23での充電電荷をより安定して保持することができる。ちなみに、DM18をインバータ回路23のみで構成した場合、マルチカラー用映像信号は、配線容量とインバータ自体の容量成分により保持されることになる。

【0053】なお、インバータ回路23の正極性側と負極性側には、それぞれ図示しない正電源配線と負電源配

線が接続されており、図示しない電源電圧発生回路からは、直流のHigh電源電圧とLow電源電圧がそれぞれ供給されている。インバータ回路23の電源配線については後に説明する。

【0054】図1に示したように、DM18を1つのインバータ回路23と第2の容量素子25で構成することにより、従来は5個必要としていたDMのトランジスタ数を、インバータ回路のための2個と容量素子1つに削減することができる。また、DM18を1つのインバータ回路23のみで構成した場合は、DMのトランジスタ数を、インバータ回路のための2個に削減することができる。したがって、上記のような回路構成を採用することにより、基板上でのDM18の配置領域を小さくすることが可能となり、画面の高精細化を実現することができる。さらに、プロセスの微細化が進めば、数画素を表示単位としての1画素とすることにより、静止画表示時にも階調表示が可能となる。

【0055】また通常表示時において、第2のスイッチ素子21のみをオンさせ、第1の容量素子24と第2の容量素子25との間を導通させるように駆動した場合は、画素電極13に書き込まれたフルカラー用映像信号の電荷の一部を第2の容量素子25に保持させることができる。したがって、第1の容量素子24と第2の容量素子25の2つの容量を合わせて、通常駆動に必要とされる容量を形成すれば、第2の容量素子25を付加した分だけ第1の容量素子24の容量を小さくすることができる。これによれば、基板上での回路面積を小さくして、高精細化と歩留まりの向上を実現することができる。

【0056】次に、上記のように構成された液晶表示装置100において、通常表示及び静止画表示を行う場合の駆動方法について説明する。

【0057】まず、通常表示時には、メモリ制御信号線19aをオンレベル、メモリ制御信号線19bをオフレベルとして、第2のスイッチ素子21のみをオンとする。そして、走査線駆動回路120及び信号線駆動回路130に対し、それぞれクロック信号、スタート信号及びフルカラー用映像信号を供給して、通常のアクティブマトリクス型液晶表示装置と同様に駆動を行うことにより、フルカラーによる高画質な中間調/動画表示を行うことができる。

【0058】先に説明したように、通常表示時において、第2のスイッチ素子21のみをオンさせるように駆動した場合は、画素電極13に書き込まれたフルカラー用映像信号の電荷の一部が第2の容量素子25にも保持されるため、第1の容量素子24での充電電荷をさらに安定して保持することができる。なお、通常表示時において、メモリ制御信号線19a、19bをともにオフレベルとし、第2のスイッチ素子21と第3のスイッチ素子22をともにオフするように駆動することもできる。

この場合、画素電極13に書き込まれたフルカラー用映像信号の電荷は、液晶層16と第1の容量素子24で保持されることになる。

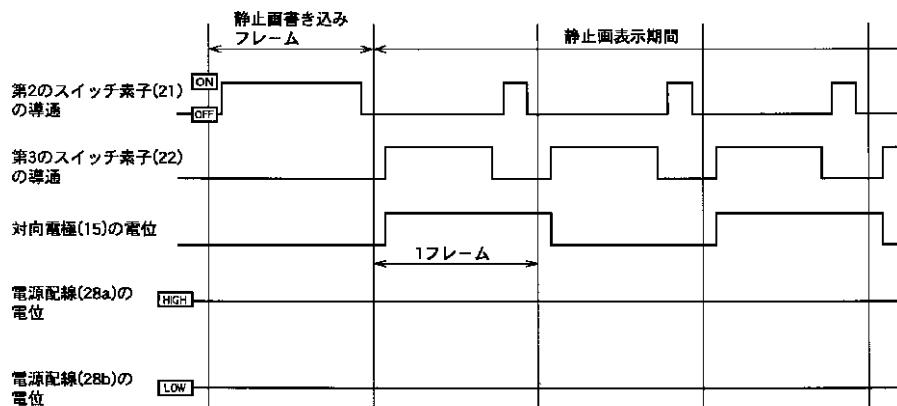

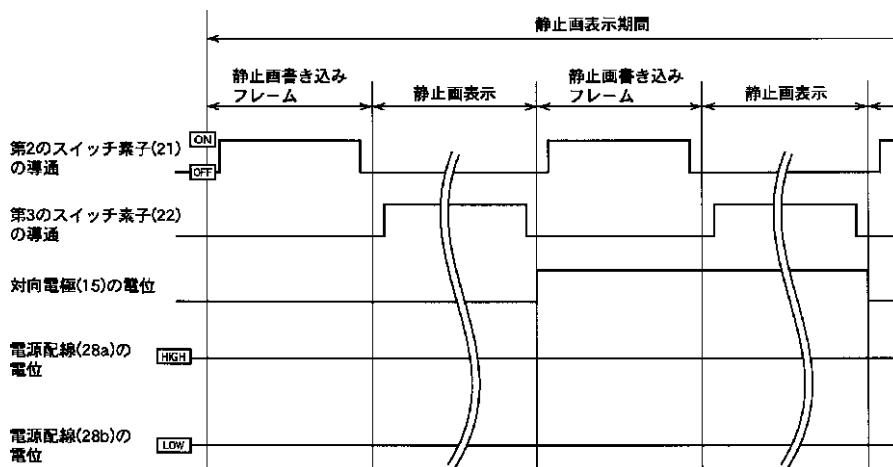

【0059】続いて、静止画表示を行う場合の駆動方法を、図5に示す信号波形のタイミングチャートを参照しながら説明する。この例では、電源配線28a、28bに直流のHig h電源電圧、Low電源電圧をそれぞれ供給している。

【0060】通常表示から静止画表示に切り替える際は、通常表示から静止画表示に移行する最後のフレーム(静止画書き込みフレーム)において、メモリ制御信号線19aをオンレベル、メモリ制御信号線19bをオフレベルとし、第2のスイッチ素子21のみをオンさせる。そして、第1のスイッチ素子14が行選択信号によりオンしている間に、信号線11にマルチカラー用映像信号をサンプリングし、これを第1のスイッチ素子14からDMスイッチ回路17の第2のスイッチ素子21を通じてDM18に書き込む。

【0061】DM18にマルチカラー用映像信号が書き込まれた後に、第1のスイッチ素子14がオフすると、マルチカラー用映像信号はDM18の第2の容量素子25(及びインバータ回路23、以下同じ意味として略称する)に保持される。

【0062】静止画表示の期間において、DM18に書き込まれたマルチカラー用映像信号は、短時間であればこの状態で保持することもできるが、長時間保持すると直流成分により液晶層16が劣化するため、交流駆動する必要がある。この実施形態では、一定の周期でメモリ制御信号線19a、同19bを交互にオンレベルとすることによって、第2のスイッチ素子21と第3のスイッチ素子22を交互にオンし、同時に対向電極15の電位を反転させることで交流駆動を実現している。

【0063】すなわち、静止画表示期間の各フレームでは、最初にメモリ制御信号線19bをオンレベルとし、第3のスイッチ素子22をオンにすることで第2の容量素子25に保持されているマルチカラー用映像信号を画素電極13に書き込む。この間、メモリ制御信号線19aはオフレベルとする。そして、1フレームの終了間際にメモリ制御信号線19aをオンレベルとし、第2のスイッチ素子21をオンにすることで画素電極13に書き込まれていたマルチカラー用映像信号を再び第2の容量素子25に保持させる。この間、メモリ制御信号線19bはオフレベルとする。このような動作を1フレームごとに交互に繰り返すと、第2の容量素子25からマルチカラー用映像信号が取り出される度に、インバータ回路23により極性反転されて画素電極13に書き込まれるため、この周期に合わせて対向電極15の電位を反転させることで極性反転駆動を行うことができる。

【0064】また、こうした動作を可能とするために、静止画表示期間においては、図5に示すように、第3の

スイッチ素子22のオン時間が、第2のスイッチ素子21のオン時間よりも長くなるように設定する。この実施形態では、第2のスイッチ素子21のオン時間を、第3のスイッチ素子22のオン時間の1/10程度としているが、液晶パネルの設計条件に応じて適宜に設定することができる。

【0065】このように、第2のスイッチ素子21と第3のスイッチ素子22を1フレーム毎に交互にオンすることで、画素電極13にはHig h電源電圧/Low電源電圧の電位が交互に出力され、これと同期させて対向電極15の電位をHig h電源電圧/Low電源電圧に相当する電位間でシフトすることにより、対向電極15と極性が同じ表示画素10では液晶層16に電圧がかからず、また逆極性の表示画素10では液晶層16に電圧がかかることになり、2値の画像表示を行うことができる。このとき、表示画素部110で動作しているのは、低周波数のメモリ制御信号線19と対向電極15だけであるため、低消費電力で静止画表示を行うことができる。また、この間、画素電極13への電位の供給はDM18からとなるため、第1の容量素子24と図示しない補助容量線との間に形成される補助容量Csの電位は表示と無関係になる。このため、前記補助容量線には、通常表示において第1の容量素子24に与えている補助容量電位よりも低い電位を供給することができるため、低消費電力化を達成することができる。

【0066】また、図5には示していないが、静止画表示から通常表示に切り替える際は、最後のフレーム(静止画最終フレーム)を経て、再びメモリ制御信号線19a、19bをオフレベル(又は19bのみオフレベル)とし、走査線駆動回路120及び信号線駆動回路130に対し、それぞれクロック信号、スタート信号及びフルカラー用映像信号を供給する。

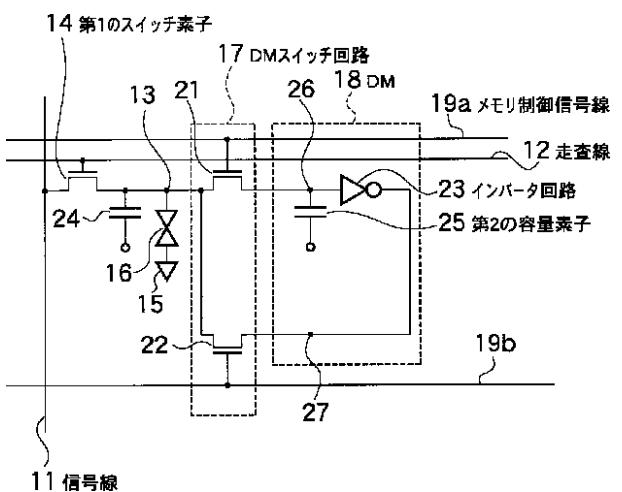

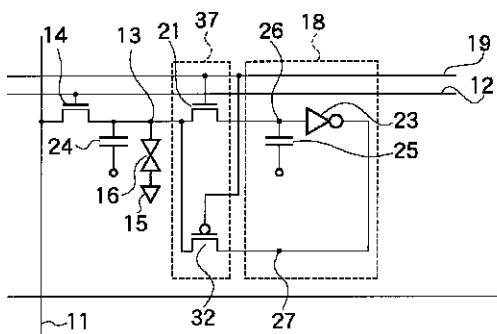

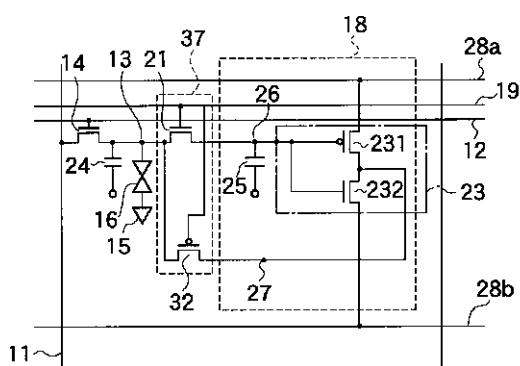

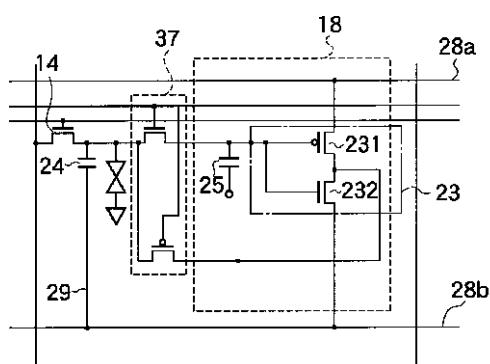

【0067】次に、DMスイッチ回路17の他の実施形態について説明する。図2は、図3に示す表示画素10の他の実施形態を示す回路構成図であり、図1と同等部分を同一符号で示している。

【0068】この実施形態のDMスイッチ回路37は、N-ch TFTからなる第2のスイッチ素子21と、P-ch TFTからなる第3のスイッチ素子32とで構成されている。各スイッチ素子のゲートは共通のメモリ制御信号線19に接続されており、メモリ制御信号線19から供給されるメモリ制御信号によって、第2のスイッチ素子31と第3のスイッチ素子32のオン/オフが同時に制御される。すなわち、図2に示すDMスイッチ回路37では、第2のスイッチ素子31がオンのときは第3のスイッチ素子32がオフし、また第2のスイッチ素子31がオフのときは第3のスイッチ素子32がオンすることになる。

【0069】通常表示時において、第2のスイッチ素子21をオンし、第2の容量素子25にもフルカラー用映

像信号の電荷を充電させる場合には、2つのスイッチ素子を同時にオフにする必要がないので、図2のような回路構成とすることにより、メモリ制御信号線19の数を図1の回路構成に比べて半分に減らすことができる。なお、この実施形態において、第2のスイッチ素子21と第3のスイッチ素子32は、CMOSトランジスタで構成されている。

【0070】次に、DM18の具体的な回路構成について説明する。ここでは、図2の回路構成を例として説明する。また、静止画表示を行う場合の他の駆動方法についても説明する。

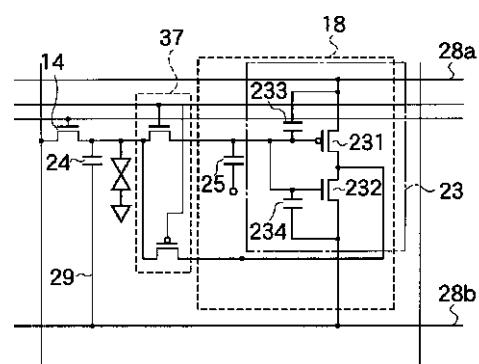

【0071】図6は、図2に示す表示画素10の詳細な回路構成図であり、図2と同等部分を同一符号で表している。

【0072】DM18に含まれるインバータ回路23は、直列に接続されたP-ch TFT231及びN-ch TFT232により構成されており、その正極性側には正電源配線として電源配線28aが接続され、負極性側には負電源配線として電源配線28bが接続されている。

【0073】なお、第2の容量素子25を接続しても、インバータ回路23に書き込まれたマルチカラー用映像信号の充電電荷を安定して保持できない場合は、図7に示すように、P-ch TFT231及びN-ch TFT232に、それぞれ第3の容量素子233及び第4の容量素子234を付加する。これにより、充電電荷のさらに安定して保持させることができる。

【0074】この場合も、通常表示時において、第2のスイッチ素子21のみをオンさせ、第1の容量素子24と、第2の容量素子25、第3の容量素子233及び第4の容量素子234との間を導通させるように駆動した場合は、画素電極13に書き込まれたフルカラー用映像信号の電荷の一部をDM18側の3つの容量素子(25, 233, 234)に保持させることができる。したがって、第1の容量素子24とDM18側の3つの容量素子の容量とを合わせて、通常駆動に必要とされる容量を形成すれば、DM18側の3つの容量素子を付加した分だけ第1の容量素子24の容量を小さくすることができる。これによれば、基板上での回路面積を小さくして、高精細化と歩留まりの向上を実現することができる。

【0075】次に、図6に示す回路構成において、通常表示及び静止画表示を行う場合の駆動方法について説明する。ただし、通常表示を行う場合の駆動方法は上記実施形態と同じであるため、ここでは静止画表示を行う場合の駆動方法についてのみ説明する。

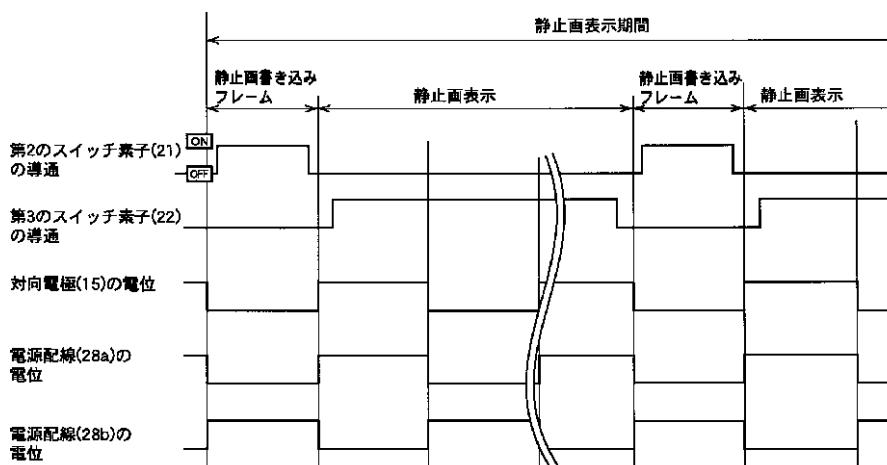

【0076】図8は、静止画表示を行う場合の他の駆動方法を示す信号波形のタイミングチャートである。この例では、電源配線28a、28bに直流のHigh電源電圧、Low電源電圧をそれぞれ供給している。

10

20

30

40

50

【0077】この実施形態の駆動方法では、静止画表示期間中、数フレーム毎にマルチカラー用映像信号の書き込みを行っている。すなわち、静止画表示期間の静止画書き込みフレームでは、メモリ制御信号線19をオンレベルとし、第2のスイッチ素子21のみをオンさせる。そして、第1のスイッチ素子14が行選択信号によりオンしている間に、マルチカラー用映像信号を信号線11にサンプリングし、これを第1のスイッチ素子14からDMスイッチ回路17の第2のスイッチ素子21を通じてDM18に書き込む。この後、第1のスイッチ素子14がオフすると、マルチカラー用映像信号はDM18の第2の容量素子25に保持される。

【0078】その後は、DM18に書き込んだマルチカラー用映像信号により静止画表示を行うが、所定フレーム数毎に一度の割合で静止画書き込みフレームを設け、マルチカラー用映像信号の書き込みを行っている。このとき書き込まれるマルチカラー用映像信号は、前回の静止画書き込みフレームで書き込まれたマルチカラー用映像信号とは反対極性の信号となり、これに合わせて対向電極15の電位を反転させることで極性反転駆動を行うことができる。

【0079】この実施形態における静止画表示期間では、新たなマルチカラー用映像信号が書き込まれるまでの所定フレーム数の間、液晶層16には同一極性のマルチカラー用映像信号が印加されるため、この間はメモリ制御信号線19を駆動する必要はない。一方、所定フレーム数毎に走査線駆動回路120と信号線駆動回路130を駆動することになるが、本発明者らによるシミュレーションによれば、図5に示す駆動方法に比べ、静止画表示期間をさらに低消費電力で駆動できることが確認されている。

【0080】なお、マルチカラー用映像信号による静止画表示のフレーム数は、DM18に書き込まれたマルチカラー用映像信号の電位が液晶駆動に必要な電位を保持できるフレーム数であればよく、数フレームから数十フレームの間に設定される。

【0081】図9は、静止画表示を行う場合のさらに他の駆動方法を示す信号波形のタイミングチャートである。この例では、電源配線28a、28bに交流の電源電圧を供給している。

【0082】この実施形態の駆動方法では、図8に示した実施形態と同様に、静止画表示期間中、数フレーム毎にマルチカラー用映像信号の書き込みを行っている。相違点は、1フレーム毎に極性反転駆動を行うことにある。すなわち、DM18に書き込んだマルチカラー用映像信号による静止画表示の間は、1フレーム毎に電源配線28a、28bの電位を反転させるとともに、この周期に合わせて対向電極15の電位を反転させている。以下、詳細に説明する。

【0083】静止画表示の間、第2のスイッチ素子21

はオフ、第3のスイッチ素子22はオンとなるため、第2の容量素子25に保持されているマルチカラー用映像信号の電位（その画素に書き込まれたマルチカラー用映像信号の電位であり、Highレベル又はLowレベルの二値情報）に応じて、インバータ回路23のP-ch TFT231又はN-ch TFT232の一方がオンする。すると、DM18に書き込まれたマルチカラー用映像信号の電位が、P-ch TFT231又はN-ch TFT232から第3のスイッチ素子23を通じて画素電極13に供給される。したがって、あるフレームにおいて、マルチカラー用映像信号の電位がHighであれば、N-ch TFT232から第3のスイッチ素子23を通じてLowレベルの電位が画素電極13に供給される。このとき、対向電極15は逆極性となるため、液晶層16に電圧が印加される（Highレベル表示）。また、同一フレームにおいて、マルチカラー用映像信号の電位がLowであれば、P-ch TFT231から第3のスイッチ素子23を通じてHighレベルの電位が画素電極13に印加される。このとき、対向電極15は同一極性となるため、液晶層16に電圧が印加されないことになる（Lowレベル表示）。次フレームで電源配線28a、28bに供給される電源電圧の極性が反転した場合も、画素電極13に供給されるマルチカラー用映像信号の電位と対向電極15の電位との関係が反転するため、上記と同様の結果となる。このように、1フレーム毎に電源配線28a、28bの電位を反転させるとともに、この周期に合わせて対向電極15の電位を反転させることにより、所定フレーム数に及ぶ静止画表示においても極性反転駆動を行うことができる。

【0084】なお、第1の容量素子24に補助容量電位を供給する配線（補助容量線）とインバータ回路23の電源配線とを共通化することもできる。この場合の回路構成を図10及び図11に示す。図10は図7に対応し、図11は図8に対応する。図10及び図11では、補助容量線29と電源配線28bとを共通化した回路構成を示している。ただし、補助容量線29と電源配線28aとを共通化した回路構成としてもよい。図10又は図11に示すように、補助容量線とインバータ回路23の電源配線とを共通化した場合は、基板上に電源配線を個別に引き回す必要がないため、基板上での配線数を少なくすることができます。したがって、従来よりも画素ピッチを狭めることができるようになり、画面の高精細化を達成することができる。また、配線数が少なくなることで、配線間でのショート不良の発生も少なくなり、歩留まりの向上を果たすことができる。

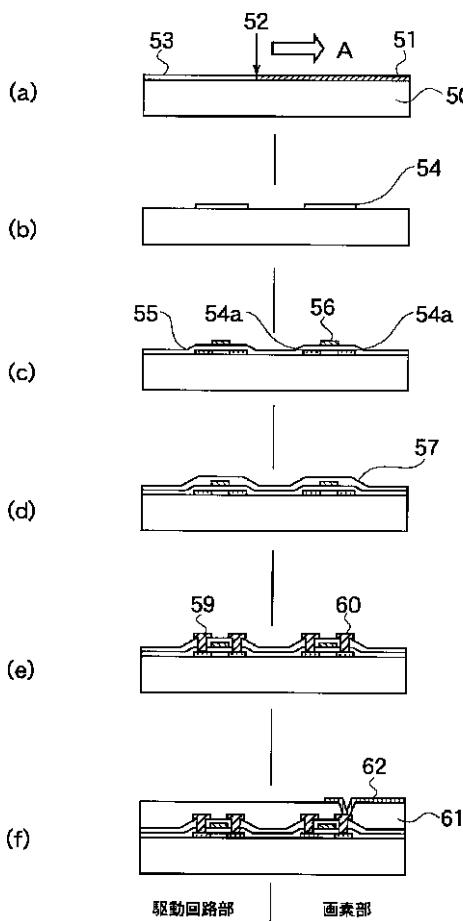

【0085】次に、この実施形態による液晶表示装置100の製造方法を図12を用いて説明する。図12は液晶表示装置の製造プロセスを示す概略断面図であり、右側の領域は画素部（表示画素部110）、左側の領域が駆動回路部（走査線駆動回路120など）を示してい

る。以下、図12の（a）～（f）の順に説明する。

【0086】（a）ガラスなどの透明絶縁基板50上に、プラズマCVD法により厚さ50nmのアモルファスシリコン（a-Si）薄膜51を堆積し、このアモルファスシリコン薄膜51を図示しないXeC1エキシマレーザ装置でアニールすることで多結晶化する。ここで、前記XeC1エキシマレーザ装置からのレーザ光52は、図中Aの方向に走査され、このレーザ光52が照射された領域は結晶化され多結晶シリコン膜53となる。その際、レーザ照射エネルギーを段階的に上げて複数回照射を行うことにより、アモルファスシリコン膜中の水素を効果的に抜くことができ、結晶化時のアブレーションを防ぐことができる。なお、照射エネルギーは200～500mJ/cm<sup>2</sup>とする。

【0087】（b）多結晶シリコン膜53をフォトリソグラフィ法を用いてパターニングし、薄膜トランジスタの活性層54を形成する。

【0088】（c）シリコン酸化膜によるゲート絶縁膜55をプラズマCVD法で形成した後、モリブデン-タンゲステン合金膜をスパッタ法で成膜、パターニングすることでゲート電極56を形成する。また、前記パターニング時に走査線も同時に形成する。ゲート絶縁膜55としては、このほかに窒化シリコン膜や常圧CVD法によるシリコン酸化膜を使うことができる。

【0089】ゲート電極56を形成後に、ゲート電極56をマスクとしてイオンドーピング法で不純物を打ち込み、薄膜トランジスタのソース／ドレイン領域54aを形成する。不純物としては、N-chトランジスタについてはリンを、P-chトランジスタについてはボロンを用いることができる。画素部のトランジスタについてはオフ時のリーク電流を抑えるためにLDD（Lightly Doped Drain）構造を用いるのが効果的である。この場合、ソース／ドレイン電極54aへの不純物注入後にゲート電極56を再パターニングし、一定量だけ細かくした後、再度低濃度の不純物打ち込みを行う。

【0090】（d）ゲート電極56上にプラズマCVD法又は常圧CVD法でシリコン酸化膜による第1の層間絶縁膜57を形成する。

【0091】（e）第1の層間絶縁膜57及びゲート絶縁膜55にコンタクトホールを形成後、スパッタ法でA1膜を形成、パターニングすることでソース／ドレイン電極59、60を形成する。このとき、信号線も同時に形成する。

【0092】（f）前記A1膜上に低誘電率絶縁膜（第2の層間絶縁膜）61を形成する。低誘電率絶縁膜61としては、プラズマCVD法で作成した窒化シリコン膜や、酸化シリコン膜、有機絶縁膜等の低誘電率絶縁膜を用いることができる。そして、低誘電率絶縁膜61にコンタクトホールを形成し、A1薄膜62を形成し、パタ

ーニングすることで画素電極を形成する。

【0093】以上のプロセスにより、透明絶縁基板50上に画素部と駆動回路部とを一体で形成することができる。この後、透明絶縁基板50と、図示しない対向電極が形成された対向基板とを対向し、周囲をエポキシ樹脂からなるシール材で密閉し、内部に液晶組成物を注入、封止することで液晶表示装置を完成することができる(図4参照)。

【0094】なお、p-Si(ポリシリコン)TFTは、a-Si TFTに比べて電子の移動度が二桁程度高いため、TFTサイズを小さくすることが可能であり、周辺駆動回路をも同時に基板上に一体に形成することができる。この周辺回路としては、高速化、低消費電力化を図るためにCMOS構造とすることが望ましい。そのため、前記不純物ドーピング工程は、レジストマスクを用いてP型及びN型不純物ドーピング工程の2回に分けて行っている。

【0095】また、この実施形態のように、画素電極13を金属薄膜で構成された光反射型の画素電極とした場合は、バックライトが不要となるため、バックライトを用いた透過型の構成に比べて、さらに低消費電力での駆動が可能となる。ちなみに、対角5cm、25万画素の液晶パネルについてフレーム周波数60Hzで静止画表示を行ったところ、消費電力を5mWとすることができた。

#### 【0096】

【発明の効果】以上説明したように、この発明によれば、ディジタルメモリが1つのインバータ回路で構成されているため、従来に比べてディジタルメモリのトランジスタ数を削減することができる。したがって、基板上でのディジタルメモリの配置領域を小さくすることができるとなり、画面の高精細化を実現することができる。

【0097】また、通話時には、第1の映像信号により通常のフルカラーによる中間調/動画表示を行うことができ、また待ち受け時には、走査線/信号線駆動回路の動作を止めつつ、前記ディジタルメモリに保持された第2の映像信号で画像表示を行うため、高精細画素に対し\*

\*ても低消費電力でマルチカラー表示を行うことができる。

#### 【図面の簡単な説明】

【図1】実施形態における表示画素の回路構成図。

【図2】他の実施形態における表示画素の回路構成図。

【図3】実施形態におけるアクティブマトリクス型液晶表示装置の回路構成図。

【図4】図3の概略断面図。

【図5】静止画表示を行う場合の動作を示す信号波形のタイミングチャート。

【図6】図2に示す表示画素の詳細な回路構成図。

【図7】図6のインバータ回路に容量素子を付加した場合の回路構成図。

【図8】静止画表示を行う場合の他の駆動方法を示す信号波形のタイミングチャート。

【図9】静止画表示を行う場合のさらに他の駆動方法を示す信号波形のタイミングチャート。

【図10】図7に示す表示画素において補助容量線とインバータ回路の電源配線とを共通化した場合の回路構成図。

【図11】図8に示す表示画素において補助容量線とインバータ回路の電源配線とを共通化した場合の回路構成図。

【図12】液晶表示装置の製造プロセスを示す概略断面図。

#### 【符号の説明】

10...表示画素、11...信号線、12...信号線、13...画素電極、14...第1のスイッチ素子、15...対向電極、16...液晶層、17, 37...DMスイッチ回路、18...DM(ディジタルメモリ)、19(19a, 19b)...メモリ制御信号線、21, 31...第2のスイッチ素子、22, 32...第3のスイッチ素子、23...インバータ回路、24...第1の容量素子(補助容量)、25...第2の容量素子、28a, 28b...電源配線、29...補助容量線、231...P-ch TFT、232...N-ch TFT、233, 234...容量素子、110...表示画素部、120...走査線駆動回路、130...信号線駆動回路

【図2】

【図4】

【図1】

【図3】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

フロントページの続き

(51) Int.Cl.<sup>7</sup>

G 09 G 3/20

識別記号

6 2 1

6 2 4

6 3 1

F I

G 09 G 3/20

テ-マコ-ド (参考)

6 2 1 B

6 2 4 B

6 3 1 H

(72)発明者 前田 孝志

埼玉県深谷市幡羅町一丁目9番地2 株式

会社東芝深谷工場内

F ターム(参考) 2H092 JB07 NA01 NA26

2H093 NA33 NA53 NC11 NC34 ND06

ND20 ND39 ND49 ND53

5C006 AA01 AA02 AA16 AA22 AC28

AF44 BB16 BC06 BC11 BC20

BF09 BF27 EB04 EB05 FA43

FA47

5C080 AA10 BB05 CC03 DD22 DD26

EE19 EE29 FF11 JJ02 JJ03

JJ04 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置和液晶显示装置的驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2002229532A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2002-08-16 |

| 申请号            | JP2001351795                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2001-11-16 |

| [标]申请(专利权)人(译) | 株式会社东芝                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 东芝公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 木村裕之<br>綱島貴徳<br>前田孝志                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 木村 裕之<br>綱島 貴徳<br>前田 孝志                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G02F1/1343 G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| CPC分类号         | G09G3/3659 G09G3/2011 G09G3/3614 G09G2300/0814 G09G2300/0823 G09G2300/0833 G09G2300/0842 G09G2320/10 G09G2330/021 G09G2340/0428                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G09G3/36 G02F1/133.510 G02F1/133.550 G02F1/1343 G09G3/20.611.F G09G3/20.621.B G09G3/20.624.B G09G3/20.631.H G11C11/34.371.H G11C11/401 G11C7/10.100 G11C7/10.480                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号      | 2H092/JB07 2H092/NA01 2H092/NA26 2H093/NA33 2H093/NA53 2H093/NC11 2H093/NC34 2H093/ND06 2H093/ND20 2H093/ND39 2H093/ND49 2H093/ND53 5C006/AA01 5C006/AA02 5C006/AA16 5C006/AA22 5C006/AC28 5C006/AF44 5C006/BB16 5C006/BC06 5C006/BC11 5C006/BC20 5C006/BF09 5C006/BF27 5C006/EB04 5C006/EB05 5C006/FA43 5C006/FA47 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD22 5C080/DD26 5C080/EE19 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 2H092/JB44 2H093/NC40 2H193/ZA04 2H193/ZA20 2H193/ZB09 2H193/ZC15 2H193/ZD23 2H193/ZF44 5M024/AA04 5M024/AA53 5M024/AA54 5M024/BB30 5M024/CC20 5M024/KK24 5M024/KK27 5M024/KK30 5M024/PP01 5M024/PP02 5M024/PP03 5M024/PP05 5M024/PP07 |         |            |

| 优先权            | 2000365426 2000-11-30 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

## 摘要(译)

解决的问题：在用作移动电话等的显示器的液晶显示装置中实现高清屏幕，并且在待机模式下以低功耗显示全像素并且在通话中以全彩显示。启用半色调显示和动态图像显示。DM ( 数字存储器 ) 18由一个反相器电路23 ( 或反相器电路23和第二电容元件25 ) 构成，以减少构成DM 18的元件的数量，并将DM 18布置在布置区域中。使屏幕更精细。另外，在通话期间，利用全色视频信号进行半色调/运动图像显示，并且在待机期间，停止扫描线/信号线驱动电路的操作，并且将保持在DM18中的多色视频信号用于图像显示。因此，即使对于高清像素，也可以以低功耗执行多色显示。