(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4731206号

(P4731206)

(45) 発行日 平成23年7月20日(2011.7.20)

(24) 登録日 平成23年4月28日(2011.4.28)

(51) Int.CI.

G02F 1/1368 (2006.01)

F 1

G02F 1/1368

請求項の数 4 (全 13 頁)

(21) 出願番号 特願2005-158069 (P2005-158069)

(22) 出願日 平成17年5月30日 (2005.5.30)

(65) 公開番号 特開2006-330634 (P2006-330634A)

(43) 公開日 平成18年12月7日 (2006.12.7)

審査請求日 平成19年9月7日 (2007.9.7)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100101214

弁理士 森岡 正樹

(72) 発明者 木原 正博

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通ディスプレイテクノロジーズ

株式会社内

(72) 発明者 田口 善久

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通ディスプレイテクノロジーズ

株式会社内

審査官 金高 敏康

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に互いに並列して形成された複数のゲートバスラインと、

前記複数のゲートバスラインに絶縁膜を介して交差して形成された複数のドレインバス

ラインと、

前記ゲートバスラインに並列して形成された複数の蓄積容量バスラインと、

n番目の前記ゲートバスラインと前記ドレインバスラインの交点近傍に設置された第1

及び第2の薄膜トランジスタと、

前記第1の薄膜トランジスタに電気的に接続された第1の画素電極と、

前記第2の薄膜トランジスタに電気的に接続され、前記第1の画素電極と分離された第

2の画素電極と、

(n+1)番目の前記ゲートバスラインと前記ドレインバスラインの交点近傍に設置さ

れ、ソース／ドレイン電極が前記第2の画素電極に電気的に接続された第3の薄膜トラン

ジスタと、

前記第3の薄膜トランジスタのドレイン／ソース電極に電気的に接続された、辺の数が

4以上である正多角形状の第1のバッファ容量電極と、絶縁膜を介して前記第1のバッフ

ア容量電極に対向して配置され、前記蓄積容量バスラインに電気的に接続された、辺の数

が4以上である正多角形状の第2のバッファ容量電極とを備え、前記第1の画素電極及び

前記第2の画素電極と重ならないバッファ容量部と

を有することを特徴とする液晶表示装置。

10

20

**【請求項 2】**

請求項 1 記載の液晶表示装置において、

前記辺の数が 4 以上である正多角形状の第 1 のバッファ容量電極に代えて円形状の第 1 のバッファ容量電極を有し、

前記辺の数が 4 以上である正多角形状の第 2 のバッファ容量電極に代えて円形状の第 2 のバッファ容量電極を有すること

を特徴とする液晶表示装置。

**【請求項 3】**

基板上に互いに並列して形成された複数のゲートバスラインと、

前記複数のゲートバスラインに絶縁膜を介して交差して形成された複数のドレインバス 10

ラインと、

前記ゲートバスラインに並列して形成された複数の蓄積容量バスラインと、

n 番目の前記ゲートバスラインと前記ドレインバスラインの交点近傍に設置された第 1

及び第 2 の薄膜トランジスタと、

前記第 1 の薄膜トランジスタに電気的に接続された第 1 の画素電極と、

前記第 2 の薄膜トランジスタに電気的に接続され、前記第 1 の画素電極と分離された第

2 の画素電極と、

( n + 1 ) 番目の前記ゲートバスラインと前記ドレインバスラインの交点近傍に設置さ

れ、ソース / ドレイン電極が前記第 2 の画素電極に電気的に接続された第 3 の薄膜トラン

ジスタと、

前記第 3 の薄膜トランジスタのドレイン / ソース電極に電気的に接続された、辺の数が

4 以上である多角形状の第 1 のバッファ容量電極と、絶縁膜を介して前記第 1 のバッファ

容量電極に対向して配置され、前記蓄積容量バスラインに電気的に接続された、辺の数が

4 以上である多角形状の第 2 のバッファ容量電極とを備え、前記第 1 の画素電極及び前記

第 2 の画素電極と重ならないバッファ容量部と

を有することを特徴とする液晶表示装置。

**【請求項 4】**

請求項 1 乃至 3 のいずれか 1 項に記載の液晶表示装置において、

前記第 1 のバッファ容量電極の縁が前記第 2 のバッファ容量電極の縁の内側にあること

を特徴とする液晶表示装置。

30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、液晶表示装置に関し、特に画素が複数の副画素に分割されている液晶表示装置に関する。

**【背景技術】****【0002】**

液晶表示装置は、C R T ( C a t h o d e R a y T u b e ) に比べて薄くて軽量であり、低電圧で駆動でき消費電力が小さいという利点があるため、テレビ、ノート型 P C ( パーソナルコンピュータ ) 、ディスクトップ型 P C 、 P D A ( 携帯端末 ) および携帯電話などの電子機器に多く使用されている。特に、各画素 ( サブピクセル ) 每にスイッチング素子として T F T ( T h i n F i l m T r a n s i s t o r : 薄膜トランジスタ ) を設けたアクティブマトリクス型液晶表示装置は、その駆動能力の高さから C R T にも匹敵する優れた表示特性を示し、ディスクトップ型 P C やテレビなど従来 C R T が使用されていた分野にも広く使用されるようになった。

40

**【0003】**

これらの用途では、表示画面をあらゆる方向から見ることのできる高い視角特性が求められている。広視野角の得られる液晶表示装置として、M V A ( M u l t i - d o m a i n V e r t i c a l A l i g n m e n t ) 方式の液晶表示装置が知られている。M V A 方式の液晶表示装置は、各画素領域内に液晶分子の配向方向が相互に異なる複数の領域

50

(ドメイン)を有することで高い視角特性を実現できる。

#### 【0004】

MVA方式のように液晶分子を基板に垂直に配向させる垂直配向型の液晶表示装置では、液晶の複屈折性を主に利用して光のスイッチングが行われる。一般に垂直配向型の液晶表示装置では、表示画面の法線方向に進む光とそれより斜めの方向に進む光との間で複屈折により生じる位相差が異なるため、程度の差はあるが画面の斜め方向では全階調において階調輝度特性(特性)が設定値からずれてしまう。したがって、液晶への印加電圧に対する透過率特性(T-V特性)は表示画面の法線方向と斜め方向とで異なるため、画面法線方向のT-V特性を最適に調整しても、斜め方向から見るとT-V特性が歪んで画面の色が白っぽく変化してしまうという現象がある。この現象は白っ茶け(Wash Out)と呼ばれている。10

#### 【0005】

白っ茶けを改善する手段として、各画素を副画素Aと副画素Bとに分割させ、副画素Aと副画素Bとでそれぞれの液晶への印加電圧を異ならせたいわゆるハーフトーン構造の液晶表示装置が提案されている。ハーフトーン構造の液晶表示装置では、画素内に異なる特性を有することで斜め方向での複屈折による位相差の正面とのズレを抑えることが可能となり、白っ茶けを抑制できる。

#### 【0006】

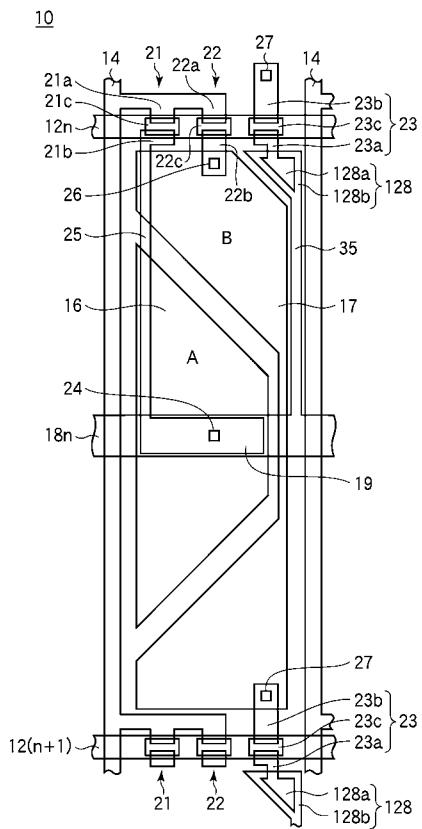

図5はハーフトーン構造の液晶表示装置の画素構成を示している。図5に示すように、TFT基板は、ガラス基板10上に形成された複数のゲートバスライン12と、SiN膜等からなる絶縁膜を介してゲートバスライン12に交差して形成された複数のドレインバスライン14とを有している。ここで、複数のゲートバスライン12は順次走査され、図2では、n番目に走査されるn番目のゲートバスライン12nと、(n+1)番目に走査される(n+1)番目のゲートバスライン12(n+1)とを示している。20

#### 【0007】

ゲートバスライン12nおよびドレインバスライン14の交差位置近傍には、画素毎に形成された第1のTFT(薄膜トランジスタ)21および第2のTFT22が互いに隣り合って配置されている。ゲートバスライン12nの一部は第1のTFT21および第2のTFT22のゲート電極として機能する。ゲートバスライン12n上には、絶縁膜を介して第1のTFT21の動作半導体層21cおよび第2のTFT22の動作半導体層22cが形成されている。動作半導体層21c、22c上にはそれぞれ不図示のチャネル保護膜が形成されている。TFT21のチャネル保護膜上には、ドレン電極21aおよびその下層の不図示のn型不純物半導体層と、ソース電極21bおよびその下層の不図示のn型不純物半導体層とが所定の間隙を介して対向して形成されている。また、TFT22のチャネル保護膜上には、ドレン電極22aおよびその下層の不図示のn型不純物半導体層と、ソース電極22bおよびその下層の不図示のn型不純物半導体層とが所定の間隙を介して互いに対向して形成されている。TFT21のドレン電極21aおよびTFT22のドレン電極22aは、ドレインバスライン14にそれぞれ電気的に接続されている。TFT21、22は並列に配置されている。TFT21、22上の基板全面には、SiN膜等の誘電体からなる不図示の保護膜が形成されている。3040

#### 【0008】

また、ゲートバスライン12nおよびドレインバスライン14により画定された画素領域を横切って、ゲートバスライン12nに並列して延びる蓄積容量バスライン18nが形成されている。蓄積容量バスライン18n上には、絶縁膜を介して蓄積容量電極19が画素毎に形成されている。蓄積容量電極19は、接続電極25を介してTFT21のソース電極21bに電気的に接続されている。絶縁膜を介して対向する蓄積容量バスライン18nと蓄積容量電極19との間には、第1の蓄積容量が形成される。

#### 【0009】

ゲートバスライン12nおよびドレインバスライン14により画定された画素領域は、副画素Aと副画素Bとに分割されている。例えば台形状の副画素Aは画素領域の中央部左50

寄りに配置され、副画素Bは画素領域のうち副画素Aの領域を除いた上部、下部および中央部右側端部に配置されている。画素領域内の副画素A、Bの配置は、例えば蓄積容量バスライン18nに対しほぼ線対称になっている。副画素Aには画素電極16が形成され、副画素Bには画素電極16から電気的に分離された画素電極17が形成されている。画素電極16、17は、共にITO等の透明導電膜により形成されている。画素電極16は、保護膜が開口されたコンタクトホール24を介して、蓄積容量電極19およびTFT21のソース電極21bに電気的に接続されている。画素電極17は、保護膜が開口されたコンタクトホール26を介してTFT22のソース電極22bに電気的に接続されている。また画素電極17は、保護膜および絶縁膜を介して蓄積容量バスライン18nに重なる領域を有している。当該領域では、保護膜および絶縁膜を介して対向する画素電極17と蓄積容量バスライン18nとの間に第2の蓄積容量が形成される。10

#### 【0010】

また、各画素領域の下方には、第3のTFT23が配置されている。TFT23のゲート電極は、当該画素の次段のゲートバスライン12(n+1)に電気的に接続されている。ゲート電極上には、絶縁膜を介して動作半導体層23cが形成されている。動作半導体層23c上には、不図示のチャネル保護膜が形成されている。チャネル保護膜上には、ドレイン電極23aおよびその下層の不図示のn型不純物半導体層と、ソース電極23bおよびその下層の不図示のn型不純物半導体層とが所定の間隙を介して対向して形成されている。

#### 【0011】

TFT23のソース電極23bは、コンタクトホール27を介して画素電極17に電気的に接続されている。TFT23の近傍には、直角三角形状のバッファ容量電極128bが配置されている。バッファ容量電極128bは、接続電極35を介してゲートバスライン12(n+1)とゲートバスライン12(n+2)との間に配置された蓄積容量バスライン18(n+1)(図5では図示せず)に電気的に接続されている。蓄積容量バスライン18は全て同電位であるため、バッファ容量電極128bを次段の蓄積容量バスライン18(n+1)に接続しても、蓄積容量バスライン18nに接続した場合とバッファ容量電極128bの電位は変わらない。バッファ容量電極128b上には、絶縁膜を介して直角三角形状のバッファ容量電極128aが配置されている。バッファ容量電極128aは、ドレイン電極23aに電気的に接続されている。互いに対向して配置されたバッファ容量電極128a、128b、およびそれらの間に挟まれた絶縁膜はバッファ容量部128を構成し、バッファ容量部128にはバッファ容量が形成される。TFT23のドレイン電極23aと蓄積容量バスライン18との間は、バッファ容量C<sub>b</sub>を介した容量結合により間接的に接続されている。20

#### 【0012】

このように、図5に示す液晶表示装置は、画素毎に3つのTFT21、22、23が設けられている。以下、このような液晶表示装置の構造を「3 TFTハーフトーン構造」という。

#### 【0013】

バッファ容量電極128aが製造プロセスによりばらつくことで、各画素間でバッファ容量電極128aの面積が変動した結果、バッファ容量C<sub>b</sub>の値が変動し、表示むらが発生するという問題がある。30

#### 【0014】

【特許文献1】特開平2-12号公報

【特許文献2】米国特許第4840460号明細書

【特許文献3】特許第3076938号公報

【特許文献4】特開2004-78157号公報

【特許文献5】特開2003-255303号公報

【特許文献6】特開2005-3916号公報

【発明の開示】

10

20

30

40

50

**【発明が解決しようとする課題】**

**【0015】**

本発明の目的は、良好な表示品質の得られる液晶表示装置を提供することにある。

**【課題を解決するための手段】**

**【0016】**

上記目的は、基板上に互いに並列して形成された複数のゲートバスラインと、前記複数のゲートバスラインに絶縁膜を介して交差して形成された複数のドレインバスラインと、前記ゲートバスラインに並列して形成された複数の蓄積容量バスラインと、n番目の前記ゲートバスラインと前記ドレインバスラインの交点近傍に設置された第1及び第2の薄膜トランジスタと、前記第1の薄膜トランジスタに電気的に接続された第1の画素電極と、前記第2の薄膜トランジスタに電気的に接続され、前記第1の画素電極と分離された第2の画素電極と、(n+1)番目の前記ゲートバスラインと前記ドレインバスラインの交点近傍に設置され、ソース／ドレイン電極が前記第2の画素電極に電気的に接続された第3の薄膜トランジスタと、前記第3の薄膜トランジスタのドレイン／ソース電極に電気的に接続された、辺の数が4以上である正多角形状の第1のバッファ容量電極と、絶縁膜を介して前記第1のバッファ容量電極に対向して配置され、前記蓄積容量バスラインに電気的に接続された、辺の数が4以上である正多角形状の第2のバッファ容量電極とを備えたバッファ容量部とを有することを特徴とする液晶表示装置によって達成される。10

**【0017】**

上記本発明の液晶表示装置において、前記辺の数が4以上である正多角形状の第1のバッファ容量電極に代えて円形状の第1のバッファ容量電極を有し、前記辺の数が4以上である正多角形状の第2のバッファ容量電極に代えて円形状の第2のバッファ容量電極を有することを特徴とする。20

**【発明の効果】**

**【0018】**

本発明によれば、良好な表示品質の得られる液晶表示装置を実現できる。

**【発明を実施するための最良の形態】**

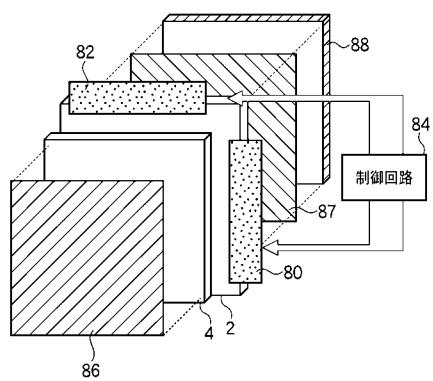

**【0019】**

**[第1の実施の形態]**

本発明の第1の実施の形態による液晶表示装置について図1乃至図3を用いて説明する。図1は、本実施の形態による液晶表示装置の概略構成を示している。図1に示すように、液晶表示装置は、TFT基板2と、対向基板4と、両基板2、4間に封止された不図示の液晶層とを有している。30

**【0020】**

TFT基板2には、複数のゲートバスラインを駆動するドライバICが実装されたゲートバスライン駆動回路80と、複数のドレインバスラインを駆動するドライバICが実装されたドレインバスライン駆動回路82とが接続されている。これらの駆動回路80、82は、制御回路84から出力された所定の信号に基づいて、走査信号やデータ信号を所定のゲートバスラインあるいはドレインバスラインに出力するようになっている。TFT基板2のTFT素子形成面と反対側の面には偏光板87が配置され、対向基板4の共通電極形成面と反対側の面には、偏光板87とクロスニコルに配置された偏光板86が配置されている。偏光板87のTFT基板2と反対側の面にはバックライトユニット88が配置されている。40

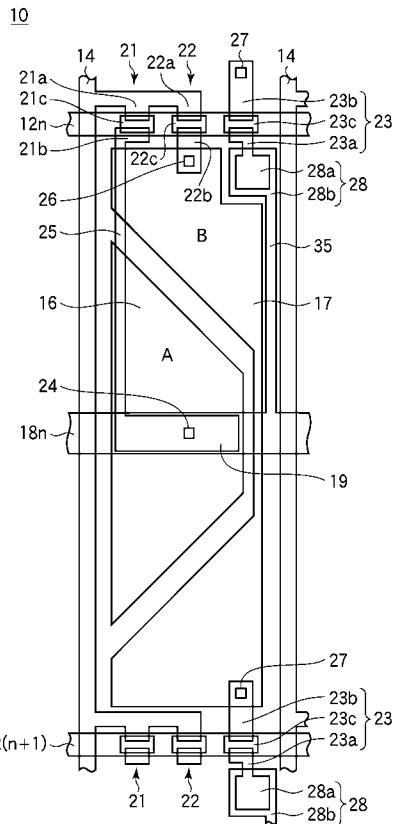

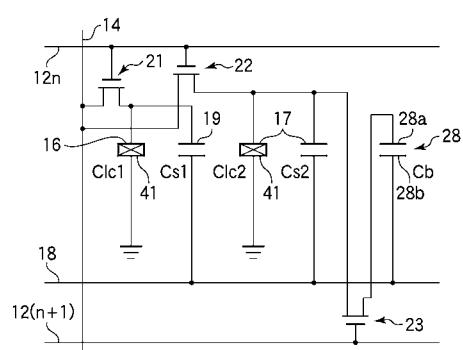

**【0021】**

図2は本実施の形態による液晶表示装置の1画素の構成を示している。また、図3は、この液晶表示装置の1画素の等価回路を示している。図2および図3に示すように、TFT基板2は、ガラス基板10上に形成された複数のゲートバスライン12と、SiN膜等からなる絶縁膜を介してゲートバスライン12に交差して形成された複数のドレインバスライン14とを有している。ここで、複数のゲートバスライン12は順次走査され、図2では、n番目に走査されるn番目のゲートバスライン12nと、(n+1)番目に走査さ50

れる(  $n + 1$  )番目のゲートバスライン 12(  $n + 1$  )とを示している。

#### 【0022】

ゲートバスライン 12n およびドレインバスライン 14 の交差位置近傍には、画素毎に形成された第1のTFT(薄膜トランジスタ)21 および第2のTFT22 が互いに隣り合って配置されている。ゲートバスライン 12n の一部は第1のTFT21 および第2のTFT22 のゲート電極として機能する。ゲートバスライン 12n 上には、絶縁膜を介して第1のTFT21 の動作半導体層 21c および第2のTFT22 の動作半導体層 22c が形成されている。動作半導体層 21c、22c 上にはそれぞれ不図示のチャネル保護膜が形成されている。TFT21 のチャネル保護膜上には、ドレイン電極 21a およびその下層の不図示のn型不純物半導体層と、ソース電極 21b およびその下層の不図示のn型不純物半導体層とが所定の間隙を介して対向して形成されている。また、TFT22 のチャネル保護膜上には、ドレイン電極 22a およびその下層の不図示のn型不純物半導体層と、ソース電極 22b およびその下層の不図示のn型不純物半導体層とが所定の間隙を介して互いに対向して形成されている。TFT21 のドレイン電極 21a およびTFT22 のドレイン電極 22a は、ドレインバスライン 14 にそれぞれ電気的に接続されている。TFT21、22 は並列に配置されている。TFT21、22 上の基板全面には、SiN膜等の誘電体からなる不図示の保護膜が形成されている。

10

#### 【0023】

また、ゲートバスライン 12n およびドレインバスライン 14 により画定された画素領域を横切って、ゲートバスライン 12n に並列して延びる蓄積容量バスライン 18n が形成されている。蓄積容量バスライン 18n 上には、絶縁膜を介して蓄積容量電極 19 が画素毎に形成されている。蓄積容量電極 19 は、接続電極 25 を介して TFT21 のソース電極 21b に電気的に接続されている。絶縁膜を介して対向する蓄積容量バスライン 18n と蓄積容量電極 19 との間には、第1の蓄積容量 C<sub>s1</sub> が形成される。

20

#### 【0024】

ゲートバスライン 12n およびドレインバスライン 14 により画定された画素領域は、副画素 A と副画素 B とに分割されている。例えば台形状の副画素 A は画素領域の中央部左寄りに配置され、副画素 B は画素領域のうち副画素 A の領域を除いた上部、下部および中央部右側端部に配置されている。画素領域内の副画素 A、B の配置は、例えば蓄積容量バスライン 18n に対しほぼ線対称になっている。副画素 A には第1の画素電極 16 が形成され、副画素 B には画素電極 16 から電気的に分離された第2の画素電極 17 が形成されている。画素電極 16、17 は、共にITO等の透明導電膜により形成されている。画素電極 16 は、保護膜が開口されたコンタクトホール 24 を介して、蓄積容量電極 19 およびTFT21 のソース電極 21b に電気的に接続されている。画素電極 17 は、保護膜が開口されたコンタクトホール 26 を介して TFT22 のソース電極 22b に電気的に接続されている。また画素電極 17 は、保護膜および絶縁膜を介して蓄積容量バスライン 18n に重なる領域を有している。当該領域では、保護膜および絶縁膜を介して対向する画素電極 17 と蓄積容量バスライン 18n との間に第2の蓄積容量 C<sub>s2</sub> が形成される。

30

#### 【0025】

また、各画素領域の下方には、第3のTFT23 が配置されている。TFT23 のゲート電極は、当該画素の次段のゲートバスライン 12(  $n + 1$  )に電気的に接続されている。ゲート電極上には、絶縁膜を介して動作半導体層 23c が形成されている。動作半導体層 23c 上には、不図示のチャネル保護膜が形成されている。チャネル保護膜上には、ドレイン電極 23a およびその下層の不図示のn型不純物半導体層と、ソース電極 23b およびその下層の不図示のn型不純物半導体層とが所定の間隙を介して対向して形成されている。

40

#### 【0026】

TFT23 のソース電極 23b は、コンタクトホール 27 を介して画素電極 17 に電気的に接続されている。TFT23 の近傍には、バッファ容量電極 28b が配置されている。バッファ容量電極 28b は、接続電極 35 を介してゲートバスライン 12(  $n + 1$  )と

50

ゲートバスライン 12 (n + 2)との間に配置された蓄積容量バスライン 18 (n + 1)（図2では図示せず）に電気的に接続されている。蓄積容量バスライン 18 は全て同電位であるため、バッファ容量電極 28 bを次段の蓄積容量バスライン 18 (n + 1)に接続しても、蓄積容量バスライン 18 n に接続した場合とバッファ容量電極 28 b の電位は変わらない。バッファ容量電極 28 b 上には、絶縁膜を介してバッファ容量電極 28 a が配置されている。バッファ容量電極 28 a は、ドレイン電極 23 a に電気的に接続されている。互いに対向して配置されたバッファ容量電極 28 a、28 b、およびそれらの間に挟まれた絶縁膜はバッファ容量部 28 を構成し、バッファ容量部 28 にはバッファ容量 C b が形成される。TFT 23 のドレイン電極 23 a と蓄積容量バスライン 18との間は、バッファ容量 C b を介した容量結合により間接的に接続されている。

10

#### 【0027】

対向基板 4 は、ガラス基板上に形成された CF 樹脂層と、CF 樹脂層上に形成され、蓄積容量バスライン 18 と同電位に維持される共通電極 41 とを有している。TFT 基板 2 と対向基板 4 との間には、例えば負の誘電率異方性を有する液晶が封止されて液晶層が形成されている。副画素 A の画素電極 16、共通電極 41、およびそれらの間に挟まれた液晶層 1 により液晶容量 C1c1 が形成され、副画素 B の画素電極 17、共通電極 41、およびそれらの間に挟まれた液晶層により液晶容量 C1c2 が形成される。TFT 基板 2 の液晶層との界面には配向膜（垂直配向膜）が形成され、対向基板 4 の液晶層 6 との界面には配向膜（垂直配向膜）が形成されている。これにより、液晶層の液晶分子は、電圧無印加時に基板面にほぼ垂直に配向する。

20

#### 【0028】

3 TFT ハーフトーン構造の液晶表示装置では、ゲートバスライン 12 n が選択状態になって TFT 21、22 がオン状態になると、副画素 A、B の各液晶容量 C1c1、C1c2 に一旦同じ電圧が印加される。その後、次段のゲートバスライン 12 (n + 1) が選択状態になって第 3 の TFT 23 がオン状態になると、副画素 B の液晶容量 C1c2 に蓄えられた電荷がバッファ容量 C b に移動することにより副画素 B の液晶容量 C1c2 の電圧が低下し、副画素 A の液晶容量 C1c1 の電圧と副画素 B の液晶容量 C1c2 の電圧とに差が生じる。

#### 【0029】

このように、液晶層に印加される電圧が互いに異なる副画素 A、B が 1 画素内に存在すると、液晶層への印加電圧に対する透過率特性 (T-V 特性) の歪みが副画素 A、B で分散される。このため、白っ茶け（斜め方向から見たときに画像の色が白っぽくなる現象）を抑制でき、視角特性が改善される。

30

#### 【0030】

また、3 TFT ハーフトーン構造の液晶表示装置では、副画素 B の画素電極 17 が TFT 22 を介してドレインバスライン 14 に接続されている。TFT 22 の動作半導体層 22 c の電気抵抗は、オフ状態であっても絶縁膜や保護膜等の電気抵抗よりも極めて低い。このため、画素電極 17 に蓄えられた電荷は容易に放電されるようになっている。したがって本実施の形態によれば、広視野角の得られるハーフトーン法を用いているのにもかかわらず、濃い焼付きが生じることがない。

40

#### 【0031】

本実施の形態によれば、バッファ容量電極 28 a の形状が正方形なので、図 5 に示す従来の直角三角形状のバッファ容量電極 128 a と比較して、製造プロセスによるばらつきの影響を受けにくくなるため、表示むらのない良好な表示品質が得られる。

#### 【0032】

【表1】

| バッファ容量電極の形状               | 正方形    |        | 直角三角形  |        |

|---------------------------|--------|--------|--------|--------|

|                           | 1 μm細り | 1 μm太り | 1 μm細り | 1 μm太り |

| 設計値S[μm <sup>2</sup> ]    | 100.00 | 100.00 | 100.00 | 100.00 |

| 出来あがり面積[μm <sup>2</sup> ] | 64.00  | 144.00 | 62.05  | 146.89 |

| 差分[μm <sup>2</sup> ]      | -36.00 | 44.00  | -37.95 | 46.89  |

| 変化量[%]                    | -36.00 | 44.00  | -37.95 | 46.89  |

10

## 【0033】

表1は、バッファ容量電極の面積が設計値Sからずれた場合の正方形と直角三角形とのバッファ容量電極の面積の差を示している。バッファ容量電極の面積の設計値Sが100 μm<sup>2</sup>であり、製造プロセスでオーバーエッチングにより、パターンが1 μm細ると仮定した場合の出来あがり面積は、表1に示すとおり正方形のバッファ容量電極28aで出来上がり面積[μm<sup>2</sup>] = (10 - 2)[μm] × (10 - 2)[μm] = 64 μm<sup>2</sup>直角三角形状のバッファ容量電極128aで約62.05 μm<sup>2</sup>となり、正方形のバッファ容量電極28aの方が設計値に対して約1.95%有利となる。

20

## 【0034】

逆に、パターンが1 μm太ると出来あがり面積は、正方形のバッファ容量電極28aで出来上がり面積[μm<sup>2</sup>] = (10 + 2)[μm] × (10 + 2)[μm] = 144 μm<sup>2</sup>直角三角形状のバッファ容量電極128aで約146.89 μm<sup>2</sup>となり、正方形のバッファ容量電極28aの方が設計値に対して約2.89%有利となる。

30

## 【0035】

以上の結果から、正方形のバッファ容量電極28aを用いた3 TFTハーフトーン構造の液晶表示装置において、図5に示す従来の直角三角形状のバッファ容量電極128aを用いた場合と比較して、製造プロセスによるバッファ容量電極の面積変動を少なくし、各画素間でのバッファ容量Cbの変動による表示むらを軽減できることが分かる。

## 【0036】

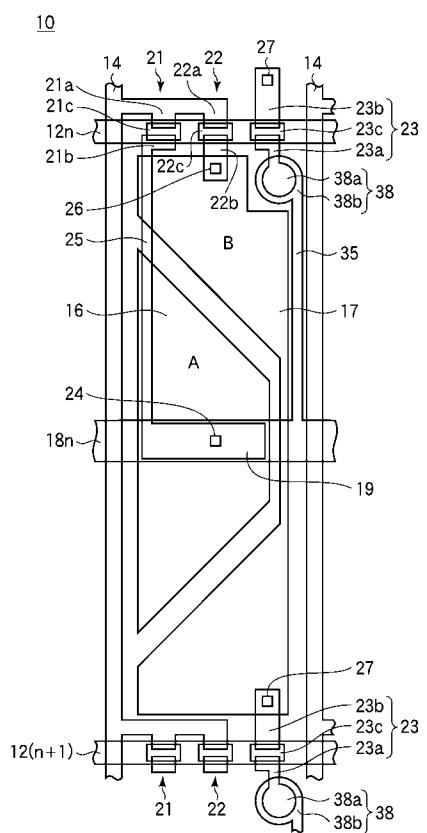

## [第2の実施の形態]

本発明の第2の実施の形態による液晶表示装置について図4を用いて説明する。図4は、本実施の形態による液晶表示装置の1画素の構成を示している。なお本実施の形態による液晶表示装置等の説明において、第1の実施の形態と同一の機能、作用を奏する構成要素には同一の符号を付して詳細な説明は省略する。

40

## 【0037】

本実施の形態による液晶表示装置では、第1の実施の形態の正方形のバッファ容量電極28aに代えて円形状のバッファ容量電極38aが配置され、正方形のバッファ容量電極28bに代えて円形状のバッファ容量電極38bが配置されている。

## 【0038】

バッファ容量電極38bは、接続電極35を介してゲートバスライン12(n+1)とゲートバスライン12(n+2)との間に配置された蓄積容量バスライン18(n+1)(図4では図示せず)に電気的に接続されている。バッファ容量電極38aは、ドレイン電極23aに電気的に接続されている。互いに対向して配置されたバッファ容量電極38a、38b、およびそれらの間に挟まれた絶縁膜はバッファ容量部38を構成し、バッフ

50

ア容量部38にはバッファ容量C<sub>b</sub>が形成される。TFT23のドレン電極23aと蓄積容量バスライン18との間は、バッファ容量C<sub>b</sub>を介した容量結合により間接的に接続されている。

#### 【0039】

本実施の形態によれば、バッファ容量電極38aの形状が円形なので、図5に示す従来の直角三角形状のバッファ容量電極128aと比較して、製造プロセスによるばらつきの影響を受けにくくなるため、表示むらのない良好な表示品質が得られる。

#### 【0040】

##### 【表2】

| バッファ容量電極の形状               | 円形     |        | 正方形    |        | 直角三角形  |        |

|---------------------------|--------|--------|--------|--------|--------|--------|

|                           | 1 μm細り | 1 μm太り | 1 μm細り | 1 μm太り | 1 μm細り | 1 μm太り |

| 設計値S[μm <sup>2</sup> ]    | 100.00 | 100.00 | 100.00 | 100.00 | 100.00 | 100.00 |

| 出来あがり面積[μm <sup>2</sup> ] | 67.60  | 138.44 | 64.00  | 144.00 | 62.05  | 146.89 |

| 差分[μm <sup>2</sup> ]      | -32.40 | 38.44  | -36.00 | 44.00  | -37.95 | 46.89  |

| 変化量[%]                    | -32.40 | 38.44  | -36.00 | 44.00  | -37.95 | 46.89  |

10

#### 【0041】

表2は、バッファ容量電極の形状が円形、正方形および直角三角形の場合のバッファ容量電極の面積の差を示している。表2に示すとおり、バッファ容量電極の面積の設計値Sが100 μm<sup>2</sup>であり、製造プロセスによりオーバーエッチングにより、パターンが1 μm細ると仮定した場合の出来あがり面積は、円形状のバッファ容量電極38aで約67.6 μm<sup>2</sup>、直角三角形状のバッファ容量電極128aで約62.05 μm<sup>2</sup>となり、円形の方が設計値に対して約5.55%有利となる。

#### 【0042】

逆に、パターンが1 μm太ると出来あがり面積は、円形状のバッファ容量電極38aで約138.44 μm<sup>2</sup>、直角三角形状のバッファ容量電極128aで約146.89 μm<sup>2</sup>となり、円形状のバッファ容量電極38aの方が設計値に対して約8.45%有利となる。

#### 【0043】

以上の結果から、バッファ容量電極38aの形状を円形とすることで、図5に示す従来の直角三角形のバッファ容量電極128aと比較して、製造プロセスによるバッファ容量電極38aの面積変動を少なくし、各画素間でのバッファ容量C<sub>b</sub>の変動による表示むらを軽減できることが分かる。

#### 【0044】

以上説明したように、本発明によれば、3 TFTハーフトーン構造の液晶表示装置において、表示むらの原因となるバッファ容量C<sub>b</sub>の変動を抑止できる。これにより、焼付きが生じ難く、表示むらのない表示特性を安定して得られる広視野角の液晶表示装置を実現できる。なお、本実施の形態では基本的にMVA方式等のVAモードの液晶表示装置への適用を念頭に置いた画素構成となっているが、原理や効果はVAモードに限定されるものではなく、TN、IPS、OCB等のあらゆる液晶モードの液晶表示装置に適用可能である。

#### 【0045】

本発明は、上記実施の形態に限らず種々の変形が可能である。

例えば、上記実施の形態では正方形のバッファ容量電極28a、28bを例に挙げた

30

40

50

が、本発明はこれに限らず、辺の数が 5 以上の正多角形状のバッファ容量電極にも適用できる。

#### 【 0 0 4 6 】

また上記実施の形態ではバッファ容量電極 28b が接続電極 35 を介してゲートバスライン 12(n+1) とゲートバスライン 12(n+2) との間に配置された蓄積容量バスライン 18(n+1) に電気的に接続されている液晶表示装置を例に挙げたが、本発明はこれに限らず、バッファ容量電極 28b がゲートバスライン 12n とゲートバスライン 12(n+1) との間に配置された蓄積容量バスライン 18n に電気的に接続されている液晶表示装置にも適応できる。

#### 【 0 0 4 7 】

また上記実施の形態では透過型の液晶表示装置を例に挙げたが、本発明はこれに限らず、反射型や半透過型等の他の液晶表示装置にも適用できる。

#### 【 0 0 4 8 】

また上記実施の形態では、対向基板 4 上に CF 樹脂層が形成された液晶表示装置を例に挙げたが、本発明はこれに限らず、TFT 基板 2 上に CF 樹脂層が形成された、いわゆる CF-on-TFT 構造の液晶表示装置にも適用できる。

#### 【 図面の簡単な説明 】

#### 【 0 0 4 9 】

【図 1】本発明の第 1 の実施の形態による液晶表示装置の概略構成を示す図である。

【図 2】本発明の第 1 の実施の形態による液晶表示装置の 1 画素の構成を示す図である。

【図 3】本発明の第 1 の実施の形態による液晶表示装置の 1 画素の等価回路を示す図である。

【図 4】本発明の第 2 の実施の形態による液晶表示装置の 1 画素の構成を示す図である。

【図 5】従来の液晶表示装置の 1 画素の構成を示す図である。

#### 【 符号の説明 】

#### 【 0 0 5 0 】

2 TFT 基板

4 対向基板

10 ガラス基板

12 ゲートバスライン

14 ドレインバスライン

16、17 画素電極

18 蓄積容量バスライン

19 蓄積容量電極

21、22、23 TFT

21a、22a、23a ドレイン電極

21b、22b、23b ソース電極

21c、22c、23c 動作半導体層

24、26、27 コンタクトホール

28、38 バッファ容量部

28a、28b、38a、38b バッファ容量電極

35 接続電極

41 共通電極

80 ゲートバスライン駆動回路

82 ドレインバスライン駆動回路

84 制御回路

86、87 偏光板

88 パックライトユニット

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開2005-062882(JP,A)

特開2005-010784(JP,A)

特開2006-133577(JP,A)

特開2004-279904(JP,A)

特開2005-004212(JP,A)

特開平08-201777(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1368

|                |                                                                                                                                                                                                                                                                                                                       |         |            |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|--|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                |         |            |  |  |  |

| 公开(公告)号        | <a href="#">JP4731206B2</a>                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2011-07-20 |  |  |  |

| 申请号            | JP2005158069                                                                                                                                                                                                                                                                                                          | 申请日     | 2005-05-30 |  |  |  |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                |         |            |  |  |  |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                  |         |            |  |  |  |

| 当前申请(专利权)人(译)  | 夏普公司                                                                                                                                                                                                                                                                                                                  |         |            |  |  |  |

| [标]发明人         | 木原正博<br>田口善久                                                                                                                                                                                                                                                                                                          |         |            |  |  |  |

| 发明人            | 木原 正博<br>田口 善久                                                                                                                                                                                                                                                                                                        |         |            |  |  |  |

| IPC分类号         | G02F1/1368                                                                                                                                                                                                                                                                                                            |         |            |  |  |  |

| CPC分类号         | G02F1/13624 G02F1/134309 G02F1/136213 G02F1/1393 G02F2001/134345                                                                                                                                                                                                                                                      |         |            |  |  |  |

| FI分类号          | G02F1/1368                                                                                                                                                                                                                                                                                                            |         |            |  |  |  |

| F-TERM分类号      | 2H092/GA11 2H092/JA24 2H092/JA37 2H092/JA41 2H092/JA46 2H092/JB22 2H092/JB31 2H092 /JB42 2H092/NA01 2H092/PA01 2H092/PA02 2H092/PA06 2H092/PA08 2H092/PA11 2H092/PA13 2H192/AA24 2H192/BC24 2H192/BC26 2H192/BC31 2H192/CB05 2H192/CB12 2H192/CC04 2H192 /DA12 2H192/DA15 2H192/DA43 2H192/DA52 2H192/EA43 2H192/JA13 |         |            |  |  |  |

| 代理人(译)         | 盛冈正树                                                                                                                                                                                                                                                                                                                  |         |            |  |  |  |

| 其他公开文献         | JP2006330634A                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                             |         |            |  |  |  |

## 摘要(译)

要解决的问题：提供一种能够获得良好显示特性的液晶显示装置。

ΣSOLUTION：显示装置被配置为包括：第一和第二TFT 21,22，设置在第n栅极总线12n和漏极总线14的交叉点附近;第一像素电极16，与TFT21电连接;第二像素电极17，与TFT22电连接，与第一像素电极16分离;第三TFT23，其源极电极与第二像素电极17电连接;缓冲电容器28，具有与第三TFT23的漏电极23a电连接的方形的第一缓冲电容器电极28a，并且具有与第一缓冲电容器电极28a相对设置的方形的第二缓冲电容器电极28b。通过绝缘膜并电连接到存储电容器总线18

| パッファ容量電極の形状          | 正方形    |        | 直角三角形  |        |

|----------------------|--------|--------|--------|--------|

|                      | 1μm細り  | 1μm太り  | 1μm細り  | 1μm太り  |

| 設計値S[ $\mu m^2$ ]    | 100.00 | 100.00 | 100.00 | 100.00 |

| 出来あがり面積[ $\mu m^2$ ] | 64.00  | 144.00 | 62.05  | 146.89 |

| 差分[ $\mu m^2$ ]      | -36.00 | 44.00  | -37.95 | 46.89  |

| 変化量[%]               | -36.00 | 44.00  | -37.95 | 46.89  |