(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4841438号

(P4841438)

(45) 発行日 平成23年12月21日(2011.12.21)

(24) 登録日 平成23年10月14日(2011.10.14)

|                       |                 |

|-----------------------|-----------------|

| (51) Int.Cl.          | F 1             |

| G02F 1/1368 (2006.01) | G02F 1/1368     |

| G09F 9/00 (2006.01)   | G09F 9/00 352   |

| G09F 9/30 (2006.01)   | G09F 9/30 338   |

| H01L 29/786 (2006.01) | H01L 29/78 612A |

請求項の数 5 (全 13 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2006-548849 (P2006-548849) |

| (86) (22) 出願日 | 平成17年12月13日 (2005.12.13)     |

| (86) 国際出願番号   | PCT/JP2005/022840            |

| (87) 国際公開番号   | W02006/064789                |

| (87) 国際公開日    | 平成18年6月22日 (2006.6.22)       |

| 審査請求日         | 平成19年6月12日 (2007.6.12)       |

| (31) 優先権主張番号  | 特願2004-360654 (P2004-360654) |

| (32) 優先日      | 平成16年12月14日 (2004.12.14)     |

| (33) 優先権主張国   | 日本国 (JP)                     |

前置審査

|           |                                              |

|-----------|----------------------------------------------|

| (73) 特許権者 | 000005049<br>シャープ株式会社<br>大阪府大阪市阿倍野区長池町22番22号 |

| (74) 代理人  | 100095669<br>弁理士 上野 登                        |

| (72) 発明者  | 野田 知希<br>大阪府大阪市阿倍野区長池町22番22号<br>シャープ株式会社内    |

| (72) 発明者  | 津幡 俊英<br>大阪府大阪市阿倍野区長池町22番22号<br>シャープ株式会社内    |

| (72) 発明者  | 縁田 憲史<br>大阪府大阪市阿倍野区長池町22番22号<br>シャープ株式会社内    |

最終頁に続く

(54) 【発明の名称】 液晶表示装置および液晶表示装置の欠陥修正方法

## (57) 【特許請求の範囲】

## 【請求項 1】

透明基板上に互いに下層側と上層側とに交差して形成された複数本のゲート配線およびソース配線と、マトリクス状に配列された複数の画素電極とを有し、

前記画素電極は、それぞれ下層に配置される下層側配線を間に挟む複数の副画素電極に分割され、

前記副画素電極のそれぞれには、ゲート配線とソース配線との交差部周辺において、共通のゲート配線および共通のソース配線により駆動される独立したアクティブ素子が接続され、

前記ゲート配線とソース配線との交差部において、前記下層に配置される各下層側配線自体に、少なくとも1つ以上の開口部が形成されているアクティブマトリクスアレイ基板を備え、

前記開口部は、前記下層側配線を間に挟む複数の副画素電極のそれぞれに接続された各アクティブ素子間に位置するよう、かつ、前記各アクティブ素子に接続される上層側配線が上側を通過するように形成されていることを特徴とする液晶表示装置。

## 【請求項 2】

前記下層側配線が前記ゲート配線であり、前記下層側配線の上層に配置される上層側配線が前記ソース配線であることを特徴とする請求項1に記載の液晶表示装置。

## 【請求項 3】

前記ソース配線に部分的に接続されるとともに前記ソース配線に沿う他のソース配線が

さらに形成されていることを特徴とする請求項 1 または 2 に記載の液晶表示装置。

【請求項 4】

前記交差部において、ソース配線にバイパス配線が接続されていることを特徴とする請求項 1 または 2 に記載の液晶表示装置。

【請求項 5】

前記開口部には、前記上層側配線以外の電極層および / または半導体層が存在しないことを特徴とする請求項 1 ~ 4 の何れかに記載の液晶表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、液晶表示装置に関し、さらに詳しくは、画素分割方式の液晶表示装置に関するものである。

【背景技術】

【0002】

液晶表示装置は、高精細、薄型、軽量および低消費電力などの優れた特徴を有している。そのため、近年、生産能力の向上および他の表示装置に対する価格競争力の向上などに伴って市場規模が急速に拡大している。

【0003】

この種の液晶表示装置としては、例えば、特開 2004-78157 号公報に、それぞれの画素電極が複数の副画素電極の集合体からなる画素分割方式を採用したアクティブマトリクスアレイ基板を備えた液晶表示装置が開示されている。

20

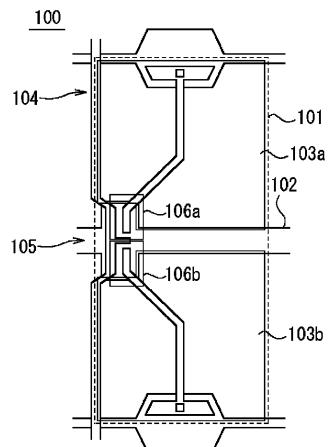

【0004】

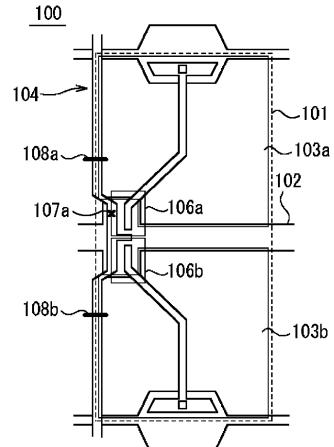

図 13 は、従来の液晶表示装置が備えるアクティブマトリクスアレイ基板上に形成されている一つの画素電極を模式的に示したものである。すなわち、図 13 に示すように、アクティブマトリクスアレイ基板 100 上の画素電極 101 は、ゲート配線 102 を間に挟んで副画素電極 103a、103b に分割されている。ゲート配線 102 とソース配線 104 の交差部 105 周辺には、共通のゲート配線 102 および共通のソース配線 104 により駆動される独立した TFT 106a、106b が設けられており、これら TFT 106a、106b は、それぞれ対応する副画素電極 103a、103b に電気的に接続されている。

30

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、上記アクティブマトリクスアレイ基板 100 を備えた液晶表示装置では、共通のゲート配線 102 およびソース配線 104 にて複数の副画素電極 103a、103b を独立した複数の TFT 106a、106b で駆動させている。

【0006】

そのため、例えば、図 14 に示すように、一方の TFT 106a において、ゲート配線 102 とソース配線 104 とのリーカー 107a (以下、「SG リーカー」ということがある。) が生じ、これをレーザなどの修正手段を用いて修正する場合、ソース配線 104 を切断部 108a、108b にて切断し、SG リーカー 107a をソース配線 104 より完全に分離しなければならない。したがって、リーカー箇所が片方の TFT 106a であっても、もう片方の TFT 106b により駆動される副画素電極 103b が欠陥となってしまう。

40

【0007】

つまり、せっかく画素電極が複数の副画素電極の集合体からなる画素分割方式を採用していても、欠陥画素は 1 画素単位になってしまいといった問題があった (例えば、ノーマリブラックモードの液晶表示装置においては、1 画素単位の全黒点の欠陥となる。)。

【0008】

本発明は、上記問題点に鑑みてなされたもので、本発明の解決しようとする課題は、欠陥サイズを従来よりも縮小可能な画素分割方式の液晶表示装置を提供することにある。

50

**【課題を解決するための手段】****【0009】**

上記課題を解決するため、本発明に係る液晶表示装置は、透明基板上に互いに下層側と上層側とに交差して形成された複数本のゲート配線およびソース配線と、マトリクス状に配列された複数の画素電極とを有し、前記画素電極は、それぞれ下層に配置される下層側配線を間に挟む複数の副画素電極に分割され、前記副画素電極のそれぞれには、ゲート配線とソース配線との交差部周辺において、共通のゲート配線および共通のソース配線により駆動される独立したアクティブ素子が接続され、前記ゲート配線とソース配線との交差部において、前記下層に配置される各下層側配線自体に、少なくとも1つ以上の開口部が形成されているアクティブマトリクスアレイ基板を備え、前記開口部は、前記下層側配線を間に挟む複数の副画素電極のそれぞれに接続された各アクティブ素子間に位置するように、かつ、前記各アクティブ素子に接続される上層側配線が上側を通過するように形成されていることを要旨とする。

10

**【0010】**

上記液晶表示装置では、下層側配線がゲート配線とされ、下層側配線の上層に配置される上層側配線がソース配線とされていることが好ましい。

**【0011】**

また、上記液晶表示装置では、ソース配線に部分的に接続されるとともにソース配線に沿う他のソース配線がさらに形成されているか、あるいは、交差部において、ソース配線にバイパス配線が接続されていることが好ましい。

20

**【0012】**

また、前記開口部には、前記上層側配線以外の電極層および／または半導体層が存在しないことが好ましい。

**【発明の効果】****【0014】**

上記液晶表示装置は、ゲート配線とソース配線との交差部周辺において、共通のゲート配線および共通のソース配線により駆動される独立したアクティブ素子が、対応する副画素電極にそれぞれ接続されており、さらに、ゲート配線とソース配線との交差部において、下層側配線に開口部が形成されているアクティブマトリクスアレイ基板を備えている。

30

**【0015】**

そのため、何れかのアクティブ素子などにて欠陥が生じた場合、レーザなどの修正手段により、開口部上を通過する上層側配線を容易に切断できる。そして、切断された配線のうち、欠陥部位を含む配線を切断すれば、欠陥部位を配線より完全に分離することができる。

**【0016】**

その後、必要に応じて補助配線修正などを行えば、欠陥画素を1画素単位ではなく、副画素単位にすることができる。そのため、従来よりも欠陥サイズが縮小され、無欠陥化することができる。したがって、特に、比較的大型の液晶表示装置などでは、欠陥数削減による品位向上、製造効率（歩留まり）向上などに寄与するところが大きいといった利点がある。

40

**【0017】**

この際、ソース配線に部分的に接続されるとともにソース配線に沿う他のソース配線がさらに形成されている場合には、補助配線修正を行うことなく上記効果が得られる。したがって、欠陥修正にかかる作業時間を短縮することができ、液晶表示装置の製造効率が一層向上するといった利点がある。

**【0018】**

また、交差部において、ソース配線にバイパス配線が接続されている場合には、上記と同様に一定の冗長性を保ちながら、1画素当たりの開口面積を広く確保することができる。そのため、表示輝度の向上に伴う表示品位の向上や、輝度効率向上に伴うバックライトのコストダウンもしくは消費電力削減などに大きく寄与するといった利点がある。

50

## 【0019】

また、開口部に電極層および／または半導体層が存在しない場合には、レーザなどの修正手段による配線切断に伴う切断片によって電極層とのリークなどが生じ難く、また、修正も行い易いといった利点がある。

## 【図面の簡単な説明】

## 【0022】

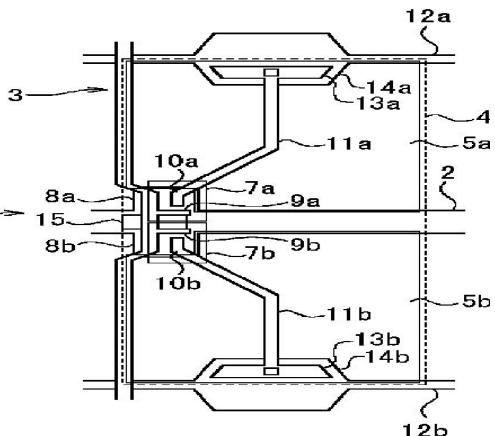

【図1】第1実施形態に係る液晶表示装置が備えるアクティブマトリクスアレイ基板上に形成されている一つの画素電極を模式的に示した図である。

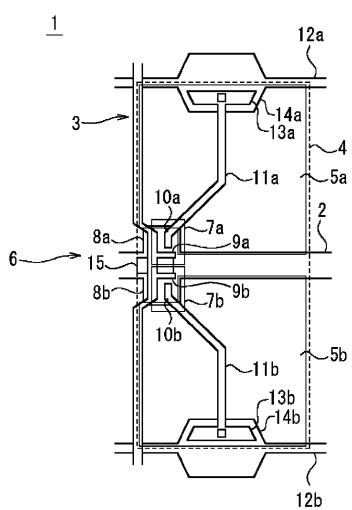

【図2】実施形態に係る液晶表示装置の画素電極（副画素電極）に形成されるスリットと、対向電極に形成されるリブの配置関係（MVAモード）を模式的に示した図である。 10

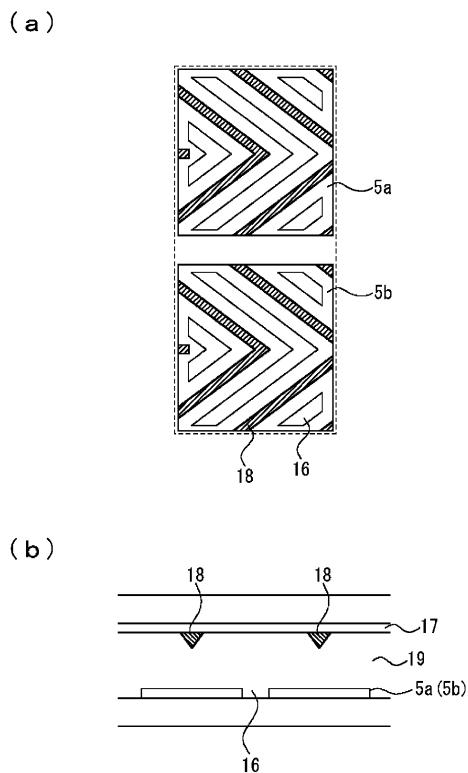

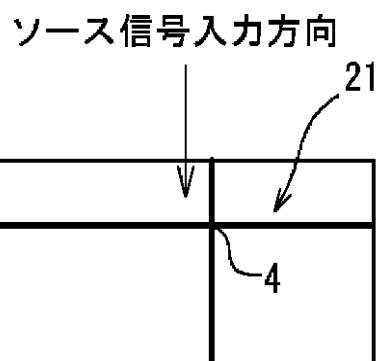

【図3】第1実施形態に係る液晶表示装置が備えるアクティブマトリクスアレイ基板上のTFTに生じたSGリークの位置を示した図である。

【図4】図3のSGリークが生じている場合に、アクティブマトリクスアレイ基板の透明基板側から確認される画像を模式的に示した図である。

【図5】第1実施形態に係る液晶表示装置において、開口部上のソース配線を切断した後、入力側のソース配線または非入力側のソース配線を切断してSGリークを分離し、補助配線修正を行う手順を説明するための図である。

【図6】開口部上のソース配線を切断した場合に、アクティブマトリクスアレイ基板の透明基板側から確認される画像を模式的に示した図である。

【図7】入力側のソース配線または非入力側のソース配線を切断してSGリークを分離した場合に、アクティブマトリクスアレイ基板の透明基板側から確認される画像を模式的に示した図である。 20

【図8】補助配線修正を行った場合に、アクティブマトリクスアレイ基板の透明基板側から確認される画像を模式的に示した図である。

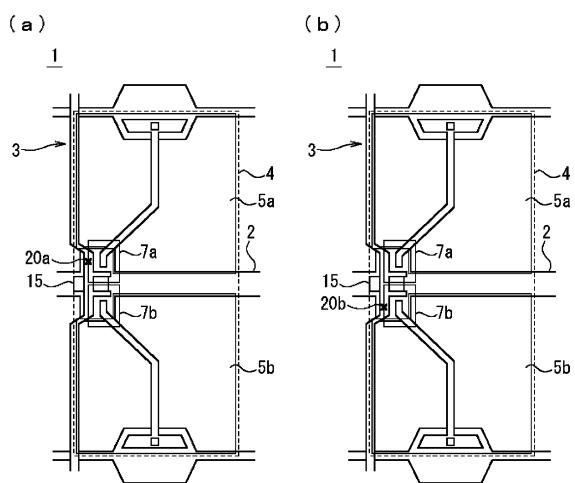

【図9】第2実施形態に係る液晶表示装置が備えるアクティブマトリクスアレイ基板上に形成されている一つの画素電極を模式的に示した図である。

【図10】第2実施形態に係る液晶表示装置において、開口部上のソース配線を切断した後、入力側のソース配線または非入力側のソース配線を切断してSGリークを分離する手順を説明するための図である。

【図11】第3実施形態に係る液晶表示装置が備えるアクティブマトリクスアレイ基板上に形成されている一つの画素電極を模式的に示した図である。 30

【図12】第3実施形態に係る液晶表示装置において、開口部上のソース配線を切断した後、入力側のソース配線または非入力側のソース配線を切断してSGリークを分離する手順を説明するための図である。

【図13】従来の液晶表示装置が備えるアクティブマトリクスアレイ基板上に形成されている一つの画素電極を模式的に示したものである。

【図14】従来の液晶表示装置において、何れかのTFTにてSGリークが発生した場合の欠陥修正方法を説明するための図である。

## 【発明を実施するための最良の形態】

## 【0023】

以下に、本実施形態に係る液晶表示装置およびこの液晶表示装置の欠陥修正方法について詳細に説明する。

## 【0024】

ここで、本発明に係る液晶表示装置は、基本的には、透明基板上に複数の画素電極、アクティブライト子を少なくとも有するアクティブマトリクスアレイ基板と、透明基板と対向する対向透明基板上に複数の画素電極に対して共通な単一の対向電極を少なくとも有する基板との間に液晶物質が封入された液晶パネルに、液晶物質の配向を外部信号により制御する駆動回路が少なくとも取り付けられ、光を変調することによって情報を表示しうる装置である。

## 【0025】

上記液晶表示装置は、アクティブマトリクスアレイ基板が新規な構造を有する点に特徴を有している。そのため、以下では、本実施形態に係る液晶表示装置が備えるアクティブマトリクスアレイ基板の構造を主に説明する。

#### 【0026】

一方、本発明に係る液晶表示装置の欠陥修正方法は、本発明に係る液晶表示装置が備えるアクティブマトリクスアレイ基板の新規な構造を利用して欠陥の修正を行うものである。そのため、以下では、本実施形態に係る液晶表示装置毎にその欠陥修正方法を説明する。

#### 【0027】

<第1実施形態>

10

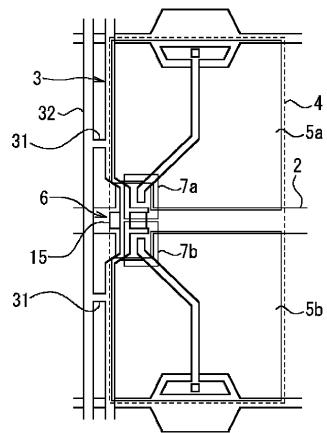

図1は、第1実施形態に係る液晶表示装置が備えるアクティブマトリクスアレイ基板上に形成されている一つの画素電極を模式的に示したものである。

#### 【0028】

図1に示すように、アクティブマトリクスアレイ基板1を構成する透明基板(図示されない)上には、行方向に延びる複数のゲート配線2と、絶縁層(図示されない)を挟んでゲート配線2と直交して列方向に延びる複数のソース配線3が形成されている。なお、図1中に示したゲート配線2、ソース配線3は、それぞれn番目、m番目のものである。また、ゲート配線2が下層側配線、ソース配線3が上層側配線とされている。

#### 【0029】

画素電極4は、ゲート配線2を間に挟んで2つの副画素電極5a、5bに分割されている。ゲート配線2とソース配線3の交差部6周辺には、それぞれの副画素電極5a、5bに接続される独立したTFT7a、7bが設けられている。

20

#### 【0030】

TFT7a、7bは、共通のゲート配線2に接続されたゲート電極8a、8bより供給される走査信号電圧によってオン／オフ制御される。また、共通のソース配線3に接続されたソース電極9a、9bより供給される表示信号電圧を、ドレイン電極10a、10bから延長されたドレイン配線11a、11bを介して副画素電極5a、5bに供給する。

#### 【0031】

ドレイン配線11a、11bのうち、ゲート配線2と平行に設けられた補助容量配線12a、12bと絶縁層(図示されない)を介して対向する部分が補助容量電極13a、13bとして機能する。また、補助容量配線12a、12bのうち、補助容量電極13a、13bと絶縁層を介して対向する部分が補助容量対向電極14a、14bとして機能する。

30

#### 【0032】

ゲート配線2とソース配線3の交差部6では、下層側配線であるゲート配線2に少なくとも1つの開口部15が形成されている。ここで、この開口部15には、電極層および／または半導体層などが存在しないことが好ましい。つまち、開口部15には、上層側配線以外のパターンが存在しないことが好ましい。

#### 【0033】

開口部15に電極層および／または半導体層が存在しない場合には、レーザなどの修正手段による配線切断時に、切断片と電極層とのリークなどが生じ難く、また、修正も行い易いからである。電極層、半導体層としては、具体的には、上層のITOやn<sup>+</sup>／i層などが挙げられる。

40

#### 【0034】

なお、第1実施形態に係る液晶表示装置(後述する他の実施形態についても同様)では、図2(a)(b)に模式的に示すように、副画素電極5a、5bにスリット16(電極層がない部分)が形成されるとともに、対向電極17にリブ18が形成され、液晶物質19として負の誘電異方性を有するネマチック液晶材料を用いると良い。スリット16とリブ18との作用により電界印加時に液晶分子が多方向に配向するため良好な視野角特性を得ることができるからである。

50

**【0035】**

次に、上記第1実施形態に係る液晶表示装置の欠陥修正方法を図3～図8を用いて説明する。

**【0036】**

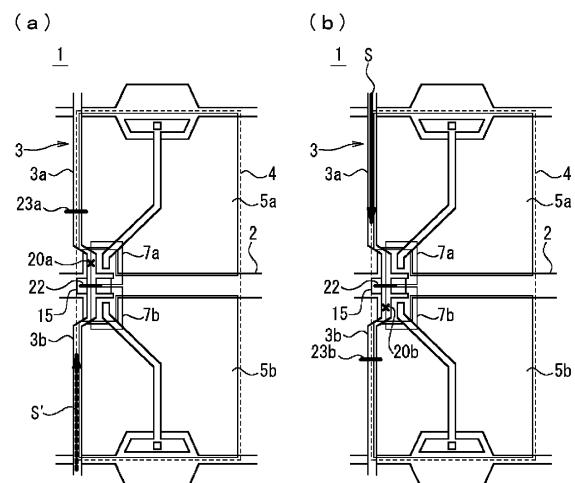

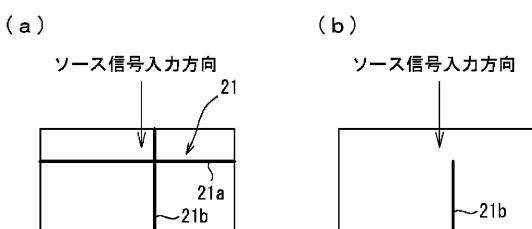

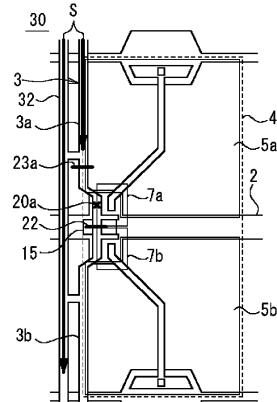

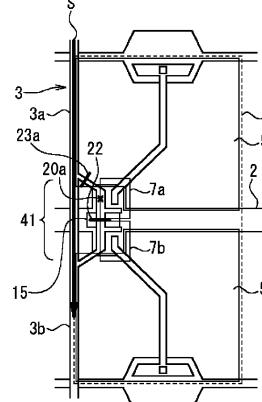

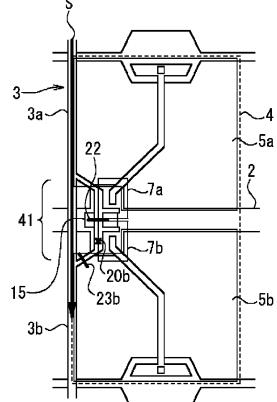

図3(a)(b)に示すように、TFT7a、7bのうち、何れか一方において、ゲート配線2とソース配線3との間にSGリーク20a、20bが生じている場合、液晶パネルの点灯確認を行うと、アクティブマトリクスアレイ基板1の透明基板側から見た画像には、図4に示すように、画素電極4を交点とした十字線欠陥21が生じている。なお、この時点では、何れのTFT7a、7bにおいてSGリーク20a、20bが生じているかは不明である。つまり、図3(a)の状態なのか、図3(b)の状態なのか不明である。10

**【0037】**

ここで、図5(a)(b)に示すように、開口部15上を通過する上層側配線としてのソース配線3を透明基板側からレーザなどの修正手段を用いて切断部22で切断し、再度、液晶パネルの点灯確認を行う。

**【0038】**

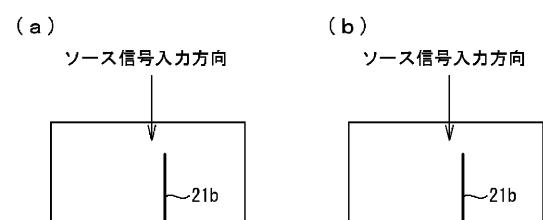

そうすると、図5(a)に示すように、ソース配線3の切断部22よりソース入力側(以下、「入力側」という。)のTFT7aにおいてSGリーク20aが生じている場合には、図6(a)に示すように、依然として十字線欠陥21が確認される。一方、図5(b)に示すように、ソース配線3の切断部22よりソース開放端側(以下、「非入力側」という。)のTFT7bにおいてSGリーク20bが生じている場合には、図6(b)に示すように、ゲート配線2方向の線欠陥21aが消滅し、ソース配線3方向の線欠陥21bが確認される。20

**【0039】**

すなわち、開口部15上を通過するソース配線3を切断部22で切断することにより、何れのTFT7a、7bにおいてSGリーク20a、20bが生じていたのかを容易に判別することができる。これにより、切断された配線(入力側のソース配線3aと非入力側のソース配線3b)のうち、何れの配線を次工程において切断すれば良いのか判断することができる。

**【0040】**

次いで、図5(a)に示すように、TFT7aにおいてSGリーク20aが生じていた場合には、入力側のソース配線3aを切断部23aで切断し、SGリーク20aをソース配線3より完全に分離する。この場合、点灯確認による画像では、図7(a)に示すように、ゲート配線2方向の線欠陥21aが消滅し、ソース配線3方向の線欠陥21bが確認される。30

**【0041】**

一方、図5(b)に示すように、TFT7bにおいてSGリーク20bが生じていた場合には、非入力側のソース配線3bを切断部23bで切断し、SGリーク20bをソース配線3より完全に分離する。この場合、点灯確認による画像では、図7(b)に示すように、依然としてソース配線3方向の線欠陥21bが確認される。

**【0042】**

次いで、図5(a)に示すように、TFT7aにおいてSGリーク20aが生じていた場合には、補助配線(冗長配線、図示されない)による修正を行い、非入力側のソース配線3bからTFT7bに補助配線を経由したソース信号S'を入力すれば、副画素(画素電極5b)を駆動させることができる。一方、図5(b)に示すように、TFT7bにおいてSGリーク20bが生じていた場合には、補助配線による修正を行い、非入力側のソース配線3bからソース信号S'(図示されない)を入力すれば、副画素(副画素電極5b)より非入力側に配置されている副画素(画素)(図示されない)を駆動させることができる。40

**【0043】**

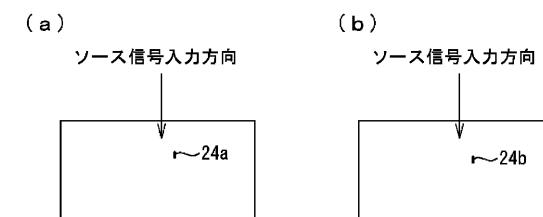

そのため、例えば、第1実施形態に係る液晶表示装置がノーマリブラックモードであれ50

ば、1画素単位の全黒点ではなく、図8(a)(b)に示すように、副画素単位の半黒点24a、24bとなる。また例えば、第1実施形態に係る液晶表示装置がノーマリホワイトモードであれば、副画素単位の半輝点となるので、さらに黒点化などの処理を行えば、副画素単位の半黒点24a、24bとなる。いずれにしても、従来よりも欠陥サイズが縮小され、無欠陥化することができる(表示品位上、正常なレベルとなる)ので、液晶表示装置の品位が向上する。

#### 【0044】

なお、補助配線による修正は、公知の方法(例えば、特開平5-203986号公報、特開平9-146121号公報など)を用いることができる。

#### 【0045】

具体的には、例えば、アクティブマトリクスアレイ基板1上の表示領域の外周部に補助配線(図示されない)を一周もしくは半周するように配置し、ソース配線3の入力端、開放端とを補助配線で短絡するなどすれば良い。

#### 【0046】

##### <第2実施形態>

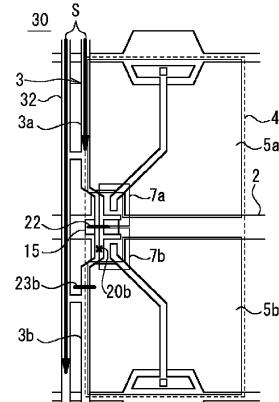

図9は、第2実施形態に係る液晶表示装置が備えるアクティブマトリクスアレイ基板上に形成されている一つの画素電極を模式的に示したものである。

#### 【0047】

第2実施形態に係る液晶表示装置が備えるアクティブマトリクスアレイ基板30の構造は、基本的には、ソース配線3を除いて第1実施形態に係る液晶表示装置が備えるアクティブマトリクスアレイ基板1の構造と同じである。そのため、以下では、第1実施形態に係る液晶表示装置およびその欠陥修正方法との差異点を主に説明する。

#### 【0048】

図9に示すように、第2実施形態に係る液晶表示装置が備えるアクティブマトリクスアレイ基板30では、接続部31によりソース配線3に部分的に接続されるとともにソース配線3に沿う他のソース配線32がさらに形成されている。

#### 【0049】

上記第2実施形態に係る液晶表示装置では、図10(a)(b)に示すように、TFT7a、7bのうち、何れか一方においてSGリーケ20a、20bが生じている場合、これを修正するには、第1実施形態と同様に、先ず、開口部15上を通過する上層側配線としてのソース配線3を透明基板側からレーザなどの修正手段を用いて切断部22で切断する。

#### 【0050】

そうすると、何れのTFT7a、7bにおいてSGリーケ20a、20bが生じていたかを、透明基板側から見た画像により判別することができる。その後、図10(a)に示すように、TFT7aにおいてSGリーケ20aが生じていた場合には、入力側のソース配線3aを切断部23aで切断し、SGリーケ20aをソース配線3より完全に分離する。

#### 【0051】

ここで、第2実施形態に係る液晶表示装置のアクティブマトリクスアレイ基板30は、他のソース配線32を有しているので、これを通じて入力側からのソース信号SがTFT7bに入力される。そのため、補助配線修正を行わなくても、副画素(副画素電極5b)を駆動させることができる。

#### 【0052】

一方、図10(b)に示すように、TFT7bにおいてSGリーケ20bが生じていた場合には、非入力側のソース配線3bを切断し、SGリーケ20bをソース配線3より完全に分離する。

#### 【0053】

これにより、他のソース配線32を通じて入力側からのソース信号Sが非入力側にも供給される。そのため、補助配線修正を行わなくても、副画素より非入力側に配置されてい

る副画素（画素）を駆動させることができる。

**【0054】**

したがって、上記第2実施形態に係る液晶表示装置によても、1画素単位の欠陥ではなく、副画素単位の欠陥となり、従来よりも欠陥サイズが縮小され、無欠陥化することができる。

**【0055】**

加えて、上記第2実施形態に係る液晶表示装置では、補助配線修正を行わずに済むことから、欠陥修正にかかる作業時間を短縮でき、液晶表示装置の製造効率が向上する。また、液晶表示装置が大型化した場合、補助配線修正に起因するソース信号の遅延なども回避できる。

10

**【0056】**

<第3実施形態>

図11は、第3実施形態に係る液晶表示装置が備えるアクティブマトリクスアレイ基板上に形成されている一つの画素電極を模式的に示したものである。

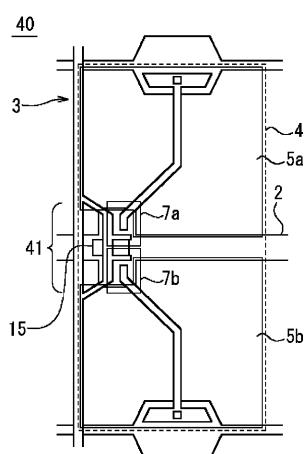

**【0057】**

第3実施形態に係る液晶表示装置が備えるアクティブマトリクスアレイ基板40の構造も、基本的には、ソース配線3を除いて第1実施形態に係る液晶表示装置が備えるアクティブマトリクスアレイ基板1の構造と同じである。そのため、以下では、第1実施形態に係る液晶表示装置およびその欠陥修正方法との差異点を主に説明する。

**【0058】**

図11に示すように、第3実施形態に係る液晶表示装置が備えるアクティブマトリクスアレイ基板40では、ソース配線3の開口部15近傍にバイパス配線41が形成されている。なお、ここでは、バイパス配線41が開口部15上を通過していない場合を例示しているが、開口部15上を通過していても良い。

20

**【0059】**

上記第3実施形態に係る液晶表示装置では、図12(a)(b)に示すように、TFT7a、7bのうち、何れか一方においてSGリード20a、20bが生じている場合、これを修正するには、第1、第2実施形態と同様に、先ず、開口部15上を通過する上層側配線としてのソース配線3を透明基板側からレーザなどの修正手段を用いて切断部22で切断する。

30

**【0060】**

そうすると、何れのTFT7a、7bにおいてSGリード20a、20bが生じていたかを、透明基板側から見た画像により判別することができる。その後、図12(a)に示すように、TFT7aにおいてSGリード20aが生じていた場合には、入力側のソース配線3aを切断部23aで切断し、SGリード20aをソース配線3より完全に分離する。

**【0061】**

ここで、第3実施形態に係る液晶表示装置のアクティブマトリクスアレイ基板40は、バイパス配線41を有しているので、これを通じて入力側からのソース信号SがTFT7bに入力される。そのため、補助配線修正を行わなくても、副画素（副画素電極5b）を駆動させることができる。

40

**【0062】**

一方、図12(b)に示すように、TFT7bにおいてSGリード20bが生じていた場合には、非入力側のソース配線3bを切断し、SGリード20bをソース配線3より完全に分離する。

**【0063】**

これにより、バイパス配線41を通じて入力側からのソース信号Sが非入力側にも供給される。そのため、補助配線修正を行わなくても、副画素より非入力側に配置されている副画素（画素）を駆動させることができる。

**【0064】**

50

したがって、上記第3実施形態に係る液晶表示装置によつても、1画素単位の欠陥ではなく、副画素単位の欠陥となり、従来よりも欠陥サイズが縮小され、無欠陥化することができる。また、上記第2実施形態に係る液晶表示装置と同等の冗長性を有する。

#### 【0065】

さらに、上記第3実施形態に係る液晶表示装置では、1画素の開口面積を広く確保することができる。そのため、表示輝度の向上に伴う表示品位の向上や、輝度効率向上に伴うバックライトのコストダウンもしくは消費電力削減などに大きく寄与する。

#### 【0066】

以上、本実施形態について説明したが、上記実施形態は本発明を何ら限定するものではなく、その趣旨を逸脱しない範囲で種々変形・改良が可能である。

10

#### 【0067】

例えば、本実施形態では、画素電極のそれぞれが2つの副画素電極の集合体からなる場合について説明したが、3つ以上の副画素電極の集合体からなっていても良い。

#### 【0068】

また例えば、本実施形態では、ゲート配線が下層側配線、ソース配線が上層側配線の場合について説明したが、ゲート配線が上層側配線、ソース配線が下層側配線とされていても良い。

#### 【0069】

なお、本実施形態では、アクティブ素子としてTFTを用いた場合について例示したが、MIMなどのスイッチとして機能する素子であれば何れのものでも適用可能である。

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図8】

【図6】

【図9】

30

【図10】

(a)

(b)

【図11】

【図12】

(a)

(b)

【図13】

【図14】

---

フロントページの続き

(72)発明者 武内 正典

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

審査官 山口 裕之

(56)参考文献 特開平04-096021(JP,A)

特開平03-024524(JP,A)

特開平02-223929(JP,A)

特開平04-134430(JP,A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1368

|                |                                                      |         |            |

|----------------|------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置和液晶显示装置的缺陷校正方法                                 |         |            |

| 公开(公告)号        | <a href="#">JP4841438B2</a>                          | 公开(公告)日 | 2011-12-21 |

| 申请号            | JP2006548849                                         | 申请日     | 2005-12-13 |

| [标]申请(专利权)人(译) | 夏普株式会社                                               |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                 |         |            |

| 当前申请(专利权)人(译)  | 夏普公司                                                 |         |            |

| [标]发明人         | 野田知希<br>津幡俊英<br>縁田憲史<br>武内正典                         |         |            |

| 发明人            | 野田 知希<br>津幡 俊英<br>縁田 憲史<br>武内 正典                     |         |            |

| IPC分类号         | G02F1/1368 G09F9/00 G09F9/30 H01L29/786              |         |            |

| CPC分类号         | G02F1/1368 G02F1/134309 G02F2001/136263 G02F2201/508 |         |            |

| FI分类号          | G02F1/1368 G09F9/00.352 G09F9/30.338 H01L29/78.612.A |         |            |

| 代理人(译)         | 上野登                                                  |         |            |

| 审查员(译)         | 山口博之                                                 |         |            |

| 优先权            | 2004360654 2004-12-14 JP                             |         |            |

| 其他公开文献         | JPWO2006064789A1                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                            |         |            |

## 摘要(译)

与现有技术相比能够减小缺陷尺寸的像素分割型液晶显示装置，以及用于液晶显示装置的缺陷校正方法。栅线2和源极线3被形成为彼此交叉的透明衬底上，并且被配置成矩阵状的像素电极4，每一个像素电极4，子像素电极5A，5B的集合从现在开始，各子像素电极5a，5b，在交叉路口6与栅极线2的附近和源极线3，公共栅极线2和公共源极线3连接待驱动的独立TFT 7a和7b，并且在交叉点6处，具有有源矩阵阵列基板1的液晶，该有源矩阵阵列基板1具有形成在下层侧布线中的至少一个或多个开口15从而形成显示装置。

图 1