(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4800381号

(P4800381)

(45) 発行日 平成23年10月26日(2011.10.26)

(24) 登録日 平成23年8月12日(2011.8.12)

|                      |                |

|----------------------|----------------|

| (51) Int.CI.         | F 1            |

| G02F 1/133 (2006.01) | G02F 1/133 550 |

| G09G 3/36 (2006.01)  | G09G 3/36      |

| G09G 3/20 (2006.01)  | G02F 1/133 575 |

| G09G 3/34 (2006.01)  | G02F 1/133 570 |

|                      | G02F 1/133 525 |

請求項の数 60 (全 64 頁) 最終頁に続く

|               |                              |           |                                               |

|---------------|------------------------------|-----------|-----------------------------------------------|

| (21) 出願番号     | 特願2008-511946 (P2008-511946) | (73) 特許権者 | 000005049<br>シャープ株式会社<br>大阪府大阪市阿倍野区長池町22番22号  |

| (86) (22) 出願日 | 平成18年12月19日(2006.12.19)      | (74) 代理人  | 110000338<br>特許業務法人原謙三國際特許事務所                 |

| (86) 国際出願番号   | PCT/JP2006/325279            | (72) 発明者  | 塙見 誠<br>日本国大阪府大阪市阿倍野区長池町22番<br>22号 シャープ株式会社内  |

| (87) 国際公開番号   | W02007/122777                | (72) 発明者  | 内田 歳久<br>日本国大阪府大阪市阿倍野区長池町22番<br>22号 シャープ株式会社内 |

| (87) 国際公開日    | 平成19年11月1日(2007.11.1)        | (72) 発明者  | 津幡 俊英<br>日本国大阪府大阪市阿倍野区長池町22番<br>22号 シャープ株式会社内 |

| 審査請求日         | 平成20年6月11日(2008.6.11)        |           |                                               |

| (31) 優先権主張番号  | 特願2006-116197 (P2006-116197) |           |                                               |

| (32) 優先日      | 平成18年4月19日(2006.4.19)        |           |                                               |

| (33) 優先権主張国   | 日本国(JP)                      |           |                                               |

| (31) 優先権主張番号  | 特願2006-247305 (P2006-247305) |           |                                               |

| (32) 優先日      | 平成18年9月12日(2006.9.12)        |           |                                               |

| (33) 優先権主張国   | 日本国(JP)                      |           |                                               |

最終頁に続く

(54) 【発明の名称】 液晶表示装置およびその駆動方法、テレビ受像機、液晶表示プログラム、液晶表示プログラムを記録したコンピュータ読み取り可能な記録媒体、並びに駆動回路

## (57) 【特許請求の範囲】

## 【請求項1】

複数のデータ信号線と、これら複数のデータ信号線と交差する複数の走査信号線と、上記複数のデータ信号線と上記複数の走査信号線との交点に対応してマトリクス状に配置され対応する交点を通過する走査信号線が選択されているときに対応する交点を通過するデータ信号線の電圧を画素値として取り込む複数の画素部と、を備えたアクティブマトリクス型の液晶表示装置の駆動方法において、

互いに隣接する水平走査期間の境界に非画像信号をデータ信号線に印加する一方、上記走査信号線を有効走査期間で選択し、その後該走査信号線を非選択にした時点から次の有効走査期間よりも前に上記データ信号線への非画像信号の印加のタイミングに合わせて該走査信号線を選択し、

電界により液晶分子の配向方向を制御する、垂直配向モードの液晶表示装置の駆動方法であって、

上記非画像信号を、上記液晶分子をプレチルトさせるためのプレチルト信号にするとともに、

上記データ信号線への非画像信号の印加は、隣接するデータ信号線を互いに短絡させて行ない、

上記データ信号線への非画像信号の印加は、各データ信号線に固定電圧を与えることにより行なうことを特徴とする液晶表示装置の駆動方法。

## 【請求項2】

10

20

上記非画像信号の電圧極性は、該非画像信号が印加された直後の水平走査期間における画像信号の電圧極性と同じであることを特徴とする請求項1に記載の液晶表示装置の駆動方法。

【請求項3】

1垂直走査期間の最後に選択され、上記画素部に印加される非画像信号の極性は、該1垂直走査期間の次の1垂直走査期間で選択される画像信号の極性と同じであることを特徴とする請求項1または2に記載の液晶表示装置の駆動方法。

【請求項4】

白輝度レベルを1とし、黒輝度レベルを0とした場合の表示輝度Tが、表示階調L、白表示階調Lw、および特性に関して、 $T = (L / Lw)^{1/3}$ と略近似できるときに、10

上記プレチルト信号を、 $Lw \times 10^{1/3}$ 以上を示す信号とすることを特徴とする請求項1～3のいずれか1項に記載の液晶表示装置の駆動方法。

【請求項5】

白輝度レベルを1とし、黒輝度レベルを0とした場合の表示輝度Tを示す表示階調Lを特性に関して、10

$$L = 255 \times T^{(1/2.2)}$$

上記プレチルト信号を、 $L = 12$ のときの階調電圧より大きい階調電圧を発生する信号とすることを特徴とする請求項1～3のいずれか1項に記載の液晶表示装置の駆動方法。

【請求項6】

上記プレチルト信号を、特性2.2、表示階調256階調のうちの、12階調以上を示す信号とすることを特徴とする請求項4または5に記載の液晶表示装置の駆動方法。20

【請求項7】

上記プレチルト信号を、特性2.2、表示階調1024階調のうちの、45階調以上を示す信号とすることを特徴とする請求項4または5に記載の液晶表示装置の駆動方法。

【請求項8】

表示が白となる輝度レベルを100%とする一方、表示が黒となる輝度レベルを0%とした場合、上記プレチルト信号の輝度レベルを0.1%以上とすることを特徴とする請求項1～7のいずれか1項に記載の液晶表示装置の駆動方法。

【請求項9】

上記の非画像信号は、互いに異なる極性間の電圧であり、30

該非画像信号の上記データ信号線への印加は、データ信号の極性反転時に行なうことと特徴とする請求項1～8のいずれか1項に記載の液晶表示装置の駆動方法。

【請求項10】

上記データ信号線における信号の極性が、1水平走査期間ごとに反転するときに、上記データ信号線への非画像信号の印加のタイミングにあわせて該走査信号線を選択する回数が偶数であることを特徴とする請求項9に記載の液晶表示装置の駆動方法。

【請求項11】

上記非画像信号のデータ信号線への印加は、1垂直走査期間ごとに極性が反転する電圧を各データ信号線に共通に与えることにより行なうことを特徴とする請求項1～10のいずれか1項に記載の液晶表示装置の駆動方法。40

【請求項12】

上記非画像信号のデータ信号線への印加は、1水平走査期間ごとに極性が反転する電圧を与えることにより行なうことを特徴とする請求項1～10のいずれか1項に記載の液晶表示装置の駆動方法。

【請求項13】

上記非画像信号のデータ信号線への印加は、1水平走査期間ごとに極性が反転するとともに隣接するデータ信号線同士は互いに異なる極性となる電圧を与えることにより行なうことを特徴とする請求項1～10のいずれか1項に記載の液晶表示装置の駆動方法。

【請求項14】

上記データ信号線における信号の極性は、複数の水平走査期間ごとに反転することを特50

徴とする請求項 1 ~ 8 のいずれか 1 項に記載の液晶表示装置の駆動方法。

【請求項 1 5】

隣接する水平期間の間でデータ信号の極性が反転しない時に非画像信号をデータ信号線に印加することを特徴とする請求項 1 4 に記載の液晶表示装置の駆動方法。

【請求項 1 6】

上記データ信号線における信号の極性が、n 個（ここで、n は 2 以上の整数）の水平走査期間ごとに反転するときに、上記データ信号線への非画像信号の印加のタイミングにあわせて該走査信号線を選択する回数が n の倍数であることを特徴とする請求項 1 4 または 1 5 に記載の液晶表示装置の駆動方法。

【請求項 1 7】

10

上記データ信号線への非画像信号の印加のタイミングにあわせて該走査信号線を選択する回数が  $2^n$  の倍数であることを特徴とする請求項 1 6 に記載の液晶表示装置の駆動方法。

【請求項 1 8】

上記データ信号線への非画像信号の印加は、各データ信号線に固定電圧を与えることにより行ない、

該固定電圧の極性は、上記複数の水平走査期間ごとに反転することを特徴とする請求項 1 4 ~ 1 7 の何れか 1 項に記載の液晶表示装置の駆動方法。

【請求項 1 9】

20

上記固定電圧は、複数の水平走査期間ごとに極性が反転するとともに、隣接するデータ信号線同士に与えられる固定電圧は互いに異なる極性を有することを特徴とする請求項 1 8 に記載の液晶表示装置の駆動方法。

【請求項 2 0】

オーバーシュート駆動を行なう液晶表示装置の駆動方法であって、

画素の極性および外部から得た映像信号に基づいて、オーバーシュート駆動に用いる階調補正量を求める特徴とする請求項 1 ~ 1 9 のいずれか 1 項に記載の液晶表示装置の駆動方法。

【請求項 2 1】

30

上記画素の極性および上記外部から得た映像信号を対応付けたルックアップテーブルを用いて上記オーバーシュート駆動に用いる階調補正量を求める特徴とする請求項 2 0 に記載の液晶表示装置の駆動方法。

【請求項 2 2】

オーバーシュート駆動を行なう液晶表示装置の駆動方法であって、

外部から得た映像信号に対し上記オーバーシュート駆動によるオーバーシュート補正量を求めた後に、上記画素の極性および上記オーバーシュート補正量を対応付けたルックアップテーブルを用いて階調補正量を求める特徴とする請求項 1 ~ 1 9 のいずれか 1 項に記載の液晶表示装置の駆動方法。

【請求項 2 3】

バックライトを有する液晶表示装置の駆動方法であって、

上記非画像信号のデータ信号線への印加のタイミングに合わせて、バックライトを消灯することを特徴とする請求項 1 ~ 2 2 のいずれか 1 項に記載の液晶表示装置の駆動方法。

【請求項 2 4】

40

上記データ信号線への上記非画像信号の印加時間は、上記データ信号へ印加される画像を表示するための画像信号の印加時間に比べて短いことを特徴とする請求項 1 に記載の液晶表示装置の駆動方法。

【請求項 2 5】

当該液晶表示装置が、電圧を印加しない状態で黒表示となるノーマリーブラックモードの液晶表示装置であることを特徴とする請求項 1 に記載の液晶表示装置の駆動方法。

【請求項 2 6】

複数のデータ信号線と、これら複数のデータ信号線と交差する複数の走査信号線と、上

50

記複数のデータ信号線と上記複数の走査信号線との交点に対応してマトリクス状に配置され対応する交点を通過する走査信号線が選択されているときに対応する交点を通過するデータ信号線の電圧を画素値として取り込む複数の画素部と、を備えたアクティブマトリクス型の液晶表示装置において、

互いに隣接する水平走査期間の境界に非画像信号がデータ信号線に印加される一方、

上記走査信号線が有効走査期間で選択され、その後該走査信号線が非選択された時点から次の有効走査期間よりも前に上記データ信号線への非画像信号の印加のタイミングに合わせて該走査信号線が選択され、

電界により液晶分子の配向方向を制御する、垂直配向モードの液晶表示装置であって、

上記非画像信号は、上記液晶分子をプレチルトさせるためのプレチルト信号であるとともに、

隣接するデータ信号線は互いに短絡可能に接続されており、上記データ信号線への非画像信号の印加は、データ信号線が短絡されることにより行なわれ、

各データ信号線に共通の固定電圧を与えることにより上記データ信号線への非画像信号を印加する固定電圧電源を有していることを特徴とする液晶表示装置。

#### 【請求項 27】

上記非画像信号の電圧極性は、該非画像信号が印加された直後の水平走査期間における画像信号の電圧極性と同じであることを特徴とする請求項26に記載の液晶表示装置。

#### 【請求項 28】

1 垂直走査期間の最後に選択され、上記画素部に印加される非画像信号の極性は、該1垂直走査期間の次の1垂直走査期間で選択される画像信号の極性と同じになっていることを特徴とする請求項26または27に記載の液晶表示装置。

#### 【請求項 29】

白輝度レベルを1とし、黒輝度レベルを0とした場合の表示輝度Tが、表示階調L、白表示階調Lw、および特性に関して、 $T = (L / Lw)$ と略近似できるときに、

上記プレチルト信号を、 $Lw \times 10^{(-3/4)}$ 以上を示す信号とする特徴とする請求項26～28の何れか1項に記載の液晶表示装置。

#### 【請求項 30】

白輝度レベルを1とし、黒輝度レベルを0とした場合の表示輝度Tを示す表示階調Lを特性に関して、

$$L = 255 \times T^{(1/2 - 2)} \text{ と定義し、}$$

上記プレチルト信号を、 $L = 12$ のときの階調電圧より大きい階調電圧を発生する信号とすることを特徴とする請求項26～28の何れか1項に記載の液晶表示装置。

#### 【請求項 31】

上記プレチルト信号を、特性2.2、表示階調256階調のうちの、12階調以上を示す信号とすることを特徴とする請求項29または30に記載の液晶表示装置。

#### 【請求項 32】

上記プレチルト信号を、特性2.2、表示階調1024階調のうちの、45階調以上を示す信号とすることを特徴とする請求項29または30に記載の液晶表示装置。

#### 【請求項 33】

表示が白となる輝度レベルを100%とする一方、表示が黒となる輝度レベルを0%とした場合、上記プレチルト信号の輝度レベルが0.1%以上であることを特徴とする請求項26～32のいずれか1項に記載の液晶表示装置。

#### 【請求項 34】

上記の非画像信号は、互いに異なる極性間の電圧であり、

該非画像信号の上記データ信号線への印加は、データ信号の極性反転時に行なわれることを特徴とする請求項26～33のいずれか1項に記載の液晶表示装置。

#### 【請求項 35】

上記データ信号線における信号の極性が、1水平走査期間ごとに反転しているときに、上記データ信号線への非画像信号の印加のタイミングにあわせて該走査信号線を選択する

10

20

30

40

50

回数が偶数となっていることを特徴とする請求項 3 4 に記載の液晶表示装置。

【請求項 3 6】

1 垂直走査期間ごとに極性が反転する電圧を各データ信号線に共通に与えることにより上記データ信号線へ非画像信号を印加する、第 1 の極性反転電源を有していることを特徴とする請求項 2 6 ~ 3 5 のいずれか 1 項に記載の液晶表示装置。

【請求項 3 7】

1 水平走査期間ごとに極性が反転する電圧を各データ信号線に共通に与えることにより上記データ信号線へ非画像信号を印加する、第 2 の極性反転電源を有していることを特徴とする請求項 2 6 ~ 3 5 のいずれか 1 項に記載の液晶表示装置。

【請求項 3 8】

上記第 2 の極性反転電源は、1 水平走査期間ごとに極性が反転するとともに、隣接するデータ信号線同士は互いに異なる極性となる電圧を各データ信号線に共通に与えることにより上記データ信号線へ非画像信号を印加することを特徴とする請求項 3 7 に記載の液晶表示装置。

【請求項 3 9】

上記データ信号線における信号の極性は、複数の水平走査期間ごとに反転していることを特徴とする請求項 2 6 ~ 3 3 のいずれか 1 項に記載の液晶表示装置。

【請求項 4 0】

隣接する水平期間の間でデータ信号の極性が反転しない時に非画像信号をデータ信号線に印加していることを特徴とする請求項 3 9 に記載の液晶表示装置。

10

【請求項 4 1】

上記データ信号線における信号の極性が、n 個（ここで、n は 2 以上の整数）の水平走査期間ごとに反転しているときに、上記データ信号線への非画像信号の印加のタイミングにあわせて該走査信号線を選択する回数が n の倍数となっていることを特徴とする請求項 3 9 または 4 0 に記載の液晶表示装置。

【請求項 4 2】

上記データ信号線への非画像信号の印加のタイミングにあわせて該走査信号線を選択する回数が  $2n$  の倍数となっていることを特徴とする請求項 4 1 に記載の液晶表示装置。

【請求項 4 3】

上記複数の水平走査期間ごとに極性が反転している電圧を各データ信号線に与えることにより上記データ信号線へ非画像信号を印加する、第 3 の極性反転電源を有していることを特徴とする請求項 3 9 ~ 4 2 の何れか 1 項に記載の液晶表示装置。

20

【請求項 4 4】

上記第 3 の極性反転電源は、上記複数の水平走査期間ごとに極性が反転するとともに隣接するデータ信号線同士は互いに異なる極性となる電圧を各データ信号線に与えることにより上記データ信号線へ非画像信号を印加するものであることを特徴とする請求項 4 3 に記載の液晶表示装置。

30

【請求項 4 5】

上記データ信号線への上記非画像信号の印加時間は、上記データ信号へ印加される画像を表示するための画像信号の印加時間に比べて短くなっていることを特徴とする請求項 2 6 に記載の液晶表示装置。

40

【請求項 4 6】

電圧を印加しない状態で黒表示となるノーマリーブラックモードの液晶表示装置であることを特徴とする請求項 2 6 に記載の液晶表示装置。

【請求項 4 7】

各画素の極性情報を検知する極性情報検知手段と、

該極性情報および外部から得た映像信号に基づいてオーバーシュート駆動の階調補正量を求める補正量演算手段と、をさらに有していることを特徴とする請求項 2 6 ~ 4 4 のいずれか 1 項に記載の液晶表示装置。

【請求項 4 8】

50

上記画素の極性および上記外部から得た映像信号を対応付けたルックアップテーブルを有していることを特徴とする請求項47に記載の液晶表示装置。

【請求項49】

請求項47または48に記載の液晶表示装置を動作させるための液晶表示プログラムであって、

コンピュータを上記極性情報検知手段および上記補正量演算手段として機能させるための液晶表示プログラム。

【請求項50】

請求項49に記載の液晶表示プログラムを記録したコンピュータ読み取り可能な記録媒体。

10

【請求項51】

請求項26～48のいずれか1項に記載の液晶表示装置と、

テレビジョン放送を受信するチューナー部とを備えて成ることを特徴とするテレビ受像機。

【請求項52】

複数のデータ信号線と、これら複数のデータ信号線と交差する複数の走査信号線と、上記複数のデータ信号線と上記複数の走査信号線との交点に対応してマトリクス状に配置され対応する交点を通過する走査信号線が選択されているときに対応する交点を通過するデータ信号線の電圧を画素値として取り込む複数の画素部と、を備えたアクティブマトリクス型の液晶表示装置に用いる駆動回路において、

20

互いに隣接する水平走査期間の境界に非画像信号がデータ信号線に印加される一方、上記走査信号線が有効走査期間で選択され、その後該走査信号線が非選択された時点から次の有効走査期間よりも前に上記データ信号線への非画像信号の印加のタイミングに合わせて該走査信号線が選択され、

電界により液晶分子の配向方向を制御する、垂直配向モードの液晶表示装置の駆動回路であって、

上記非画像信号は、上記液晶分子をプレチルトさせるためのプレチルト信号であるとともに、

隣接するデータ信号線は互いに短絡可能に接続されており、上記データ信号線への非画像信号の印加は、データ信号線が短絡されることにより行なわれ、

30

各データ信号線に共通の固定電圧を与えることにより上記データ信号線への非画像信号を印加する固定電圧電源を有していることを特徴とする駆動回路。

【請求項53】

複数のデータ信号線と、これら複数のデータ信号線と交差する複数の走査信号線と、上記複数のデータ信号線と上記複数の走査信号線との交点に対応してマトリクス状に配置され対応する交点を通過する走査信号線が選択されているときに対応する交点を通過するデータ信号線の電圧を画素値として取り込む複数の画素部と、を備えたアクティブマトリクス型の液晶表示装置に用いられ、複数のデータ信号線にデータ信号を供給する駆動回路であって、

上記複数のデータ信号線に接続され、極性反転する電圧を生成可能な第1の極性反転電源を備えており、

40

該第1の極性反転電源は、ゲートスタートパルス信号の当該電源への入力のタイミングに同期して1垂直走査期間ごとに極性が反転する電圧を生成し、該生成された電圧を上記データ信号の極性の反転時に非画像信号として上記複数のデータ信号線に印加し、

電界により液晶分子の配向方向を制御する、垂直配向モードの液晶表示装置の駆動回路であって、

上記非画像信号は、上記液晶分子をプレチルトさせるためのプレチルト信号であるとともに、

隣接するデータ信号線は互いに短絡可能に接続されており、上記データ信号線への非画像信号の印加は、データ信号線が短絡されることにより行なわれ、

50

各データ信号線に共通の固定電圧を与えることにより上記データ信号線への非画像信号を印加する固定電圧電源を有していることを特徴とする駆動回路。

【請求項 5 4】

複数のデータ信号線と、これら複数のデータ信号線と交差する複数の走査信号線と、上記複数のデータ信号線と上記複数の走査信号線との交点に対応してマトリクス状に配置され対応する交点を通過する走査信号線が選択されているときに対応する交点を通過するデータ信号線の電圧を画素値として取り込む複数の画素部と、を備えたアクティブマトリクス型の液晶表示装置に用いられ、複数のデータ信号線に映像信号を供給する駆動回路であって、

上記複数のデータ信号線に接続され、極性反転する電圧を生成可能な第 2 の極性反転電源を備えており、

該第 2 の極性反転電源は、ゲートクロック信号の当該電源への入力のタイミングに同期して 1 水平走査期間ごとに極性が反転する電圧を生成し、該生成された電圧をデータ信号の極性の反転時に非画像信号として上記複数のデータ信号線に印加し、

電界により液晶分子の配向方向を制御する、垂直配向モードの液晶表示装置の駆動回路であって、

上記非画像信号は、上記液晶分子をプレチルトさせるためのプレチルト信号であるとともに、

隣接するデータ信号線は互いに短絡可能に接続されており、上記データ信号線への非画像信号の印加は、データ信号線が短絡されることにより行なわれ、

各データ信号線に共通の固定電圧を与えることにより上記データ信号線への非画像信号を印加する固定電圧電源を有していることを特徴とする駆動回路。

【請求項 5 5】

複数のデータ信号線と、これら複数のデータ信号線と交差する複数の走査信号線と、上記複数のデータ信号線と上記複数の走査信号線との交点に対応してマトリクス状に配置され対応する交点を通過する走査信号線が選択されているときに対応する交点を通過するデータ信号線の電圧を画素値として取り込む複数の画素部と、を備えたアクティブマトリクス型の液晶表示装置に用いられ、複数のデータ信号線に映像信号を供給する駆動回路であって、

上記複数のデータ信号線に接続され、極性反転する電圧を生成可能な第 2 の極性反転電源を備えており、

該第 2 の極性反転電源は、ゲートクロック信号の当該電源への入力のタイミングに同期して 1 水平走査期間ごとに極性が反転する電圧を生成し、上記複数のデータ信号線のうち奇数行のデータ信号線には上記生成された電圧をデータ信号の極性の反転時に非画像信号として印加する一方、上記複数のデータ信号線のうち偶数行のデータ信号線には上記生成された電圧とは極性の異なる電圧をデータ信号の極性の反転時に非画像信号として印加し、

電界により液晶分子の配向方向を制御する、垂直配向モードの液晶表示装置の駆動回路であって、

上記非画像信号は、上記液晶分子をプレチルトさせるためのプレチルト信号であるとともに、

隣接するデータ信号線は互いに短絡可能に接続されており、上記データ信号線への非画像信号の印加は、データ信号線が短絡されることにより行なわれ、

各データ信号線に共通の固定電圧を与えることにより上記データ信号線への非画像信号を印加する固定電圧電源を有していることを特徴とする駆動回路。

【請求項 5 6】

複数のデータ信号線に映像信号を供給する駆動回路であって、

上記複数のデータ信号線にそれぞれ接続された定電圧ダイオードと、

これら定電圧ダイオードを介して上記複数のデータ信号線に接続され、上記複数のデータ信号線のそれぞれに共通の固定電圧をデータ信号の極性の反転時に非画像信号として印

10

20

30

40

50

加する固定電圧電源とを備えており、

電界により液晶分子の配向方向を制御する、垂直配向モードの液晶表示装置の駆動回路であって、

上記非画像信号は、上記液晶分子をプレチルトさせるためのプレチルト信号であるとともに、

隣接するデータ信号線は互いに短絡可能に接続されており、上記データ信号線への非画像信号の印加は、データ信号線が短絡されることにより行なわれることを特徴とする駆動回路。

【請求項 5 7】

複数のデータ信号線に映像信号を供給する駆動回路であって、

上記複数のデータ信号線に接続され、極性反転する電圧を生成可能な第3の極性反転電源を備えており、

該第3の極性反転電源は、複数の水平走査期間ごとに極性が反転する電圧を生成し、該生成された電圧を非画像信号として上記複数のデータ信号線に印加し、

電界により液晶分子の配向方向を制御する、垂直配向モードの液晶表示装置の駆動回路であって、

上記非画像信号は、上記液晶分子をプレチルトさせるためのプレチルト信号であるとともに、

隣接するデータ信号線は互いに短絡可能に接続されており、上記データ信号線への非画像信号の印加は、データ信号線が短絡されることにより行なわれ、

各データ信号線に共通の固定電圧を与えることにより上記データ信号線への非画像信号を印加する固定電圧電源を有していることを特徴とする駆動回路。

【請求項 5 8】

上記第3の極性反転電源は、複数の水平走査期間ごとに極性が反転する電圧を生成するとともに、上記複数のデータ信号線のうち奇数行のデータ信号線には上記生成された電圧を非画像信号として印加する一方、上記複数のデータ信号線のうち偶数行のデータ信号線には上記生成された電圧とは極性の異なる電圧を非画像信号として印加することを特徴とする請求項5 7に記載の駆動回路。

【請求項 5 9】

複数のデータ信号線と、これら複数のデータ信号線と交差する複数の走査信号線と、上記複数のデータ信号線と上記複数の走査信号線との交点に対応してマトリクス状に配置され対応する交点を通過する走査信号線が選択されているときに対応する交点を通過するデータ信号線の電圧を画素値として取り込む複数の画素部と、を備えたアクティブマトリクス型の液晶表示装置の駆動方法において、

互いに隣接する水平走査期間の境界に、後半の水平走査期間において印加される画像信号の電圧極性と同じ電圧極性の非画像信号を、データ信号線に印加し、

電界により液晶分子の配向方向を制御する、垂直配向モードの液晶表示装置の駆動方法であって、

上記非画像信号を、上記液晶分子をプレチルトさせるためのプレチルト信号にするとともに、

上記データ信号線への非画像信号の印加は、隣接するデータ信号線を互いに短絡させて行ない、

上記データ信号線への非画像信号の印加は、各データ信号線に固定電圧を与えることにより行なうことを特徴とする液晶表示装置の駆動方法。

【請求項 6 0】

請求項5 9に記載の駆動方法を用いた液晶表示装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、薄膜トランジスタ等のスイッチング素子を用いたアクティブマトリクス型の

10

20

30

40

50

液晶表示装置およびこの液晶表示装置の駆動方法に関し、更に詳しくは、このような液晶表示装置における動画表示性能の改善に関する。

【背景技術】

【0002】

薄型、軽量、低消費電力で高画質な表示を行なうことができる表示装置として、TFT (Thin Film Transistor: 薄膜トランジスタ) を使用した液晶表示装置がパソコンコンピュータ、携帯電話、およびテレビなどに幅広く使用されている。このような液晶表示装置は、通常、TFT 素子が配されたアレイ基板と、対向電極が配された対向基板間に液晶を封止して成っている。また、近年、画質を向上させつつ、消費電力を低減した液晶表示装置が種々提案されている。

10

【0003】

例えば、特許文献 1 に記載の液晶表示装置は、短絡回路を有しており、互いに隣接する信号線間を短絡回路により短絡しながら、順次各画素に書き込みを行っている。これにより、書き込み動作直前の各信号線の電位が正極性・負極性信号電位の均一化された中間電位となり、信号線駆動回路の消費電力を半減させている。

【0004】

また、特許文献 2 に記載の液晶装置は、隣接するデータ信号線に互いに異なる極性のデータ信号を供給し、隣接するデータ信号線同士をショートさせている。これにより、各データ信号線は中間電位 (プリチャージ電位) に向けて収束する。このプリチャージの際の負荷は、データ信号線間の短絡経路の負荷のみとなり、寄生抵抗、寄生容量が小さくなるため、高速でのプリチャージが可能となっている。

20

【0005】

また、特許文献 3 に記載の表示装置は、n (n は 2 以上の整数) 水平走査期間周期で、少なくとも 2 つの出力端子間を所定期間短絡させるよう制御された電荷回収手段を有している。そして、出力端子の極性が切り替わる際に電荷回収を行なうことで、電荷回収手段を介して電荷の再配分を行っている。これにより、表示品質の向上および消費電力の低減を実現している。

【0006】

また、特許文献 4 に記載の駆動回路は、所定の電位より高い複数の電圧 (第 1 の電圧) と、所定の電位より低い複数の電圧 (第 2 の電圧) を供給する階調電圧発生回路を有しており、ソースラインの奇数列およびソースラインの偶数列に対して、第 1 の電圧と第 2 の電圧とを所定の周期で切換えて短絡させている。これにより、消費電力を効果的に低減させている。

30

【0007】

また、特許文献 5 に記載の液晶表示装置は、プランキング期間において、切離しスイッチでデジタルアナログ変換手段と出力端子とを切り離し、短絡手段により出力端子間を短絡している。これにより、駆動信号反転時の消費電力を低減している。

【0008】

さらに、特許文献 6 に記載の駆動回路は、液晶容量への書き込みの初期時にソースライン駆動部出力をソースラインから切り離し、ソースラインを所定の電位にショートさせている。これにより、消費電流を低減し、ソースラインを所定のレベルまで充電 / 放電させる時間を短縮している。

40

【0009】

ところで、CRT (Cathode Ray Tube: 陰極線管) のようなインパルス型の表示装置においては、個々の画素に着目すると、画像が表示される点灯期間と画像が表示されない消灯期間とが交互に繰り返される。例えば動画の表示が行われた場合にも、1 画面分の画像の書き換えが行われる際に消灯期間が挿入されるため、人間の視覚に動いている物体の残像が生じることがない。このため、背景と物体とが明瞭に見分けられ、違和感なく動画が視認される。

【0010】

50

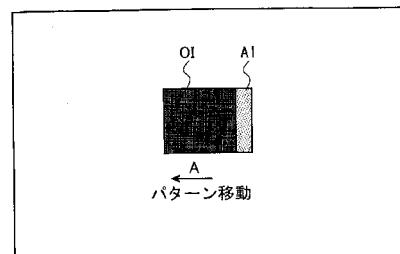

これに対し、上記した特許文献 1 ないし 6 では次のような問題が生じる。すなわち、TFT (Thin Film Transistor: 薄膜トランジスタ) を使用した液晶表示装置のようなホールド型の表示装置では、個々の画素の輝度は各画素容量に保持される電圧によって決まり、画素容量における保持電圧は、一旦書き換えられると、1 フレーム期間維持される。このようにホールド型の表示装置では、画素データとして画素容量に保持すべき電圧は、一旦書き込まれると次に書き換えられるまで保持されるので、各フレームの画像は、その 1 フレーム前の画像と時間的に近接することになる。これにより、動画が表示される場合に、人間の視覚には動いている物体の残像が生じる。例えば、図 5 9 に示すように、物体を表す画像 O I が、A 方向 (パターン移動方向) へ動いている場合、尾を引くように残像 (尾引残像) A I が生じる。

10

#### 【0011】

アクティブマトリクス型の液晶表示装置等のようなホールド型の表示装置では、動画表示の際にこのような尾引残像 A I が生じるので、主として動画表示が行われるテレビ等のディスプレイには従来、インパルス型の表示装置が採用されるのが一般的である。ところが、近年、テレビ等のディスプレイについて軽量化や薄型化が強く要求されており、そのようなディスプレイについて軽量化や薄型化が容易な液晶表示装置のようなホールド型の液晶表示装置の採用が急速に進んでいる。

#### 【0012】

従って、尾引残像 A I が生じない、液晶表示装置においてもホールド型からの脱却が望まれている。このような液晶表示装置として、特許文献 7 には、1 フレーム期間中に黒表示を行なう期間を挿入する (黒挿入) 等により液晶表示装置における表示をインパルス化する方法が記載されている。

20

【特許文献 1】日本国公開特許公報「特開平 9 - 243998 号公報 (公開日: 平成 9 年 9 月 19 日)」

【特許文献 2】日本国公開特許公報「特開平 11 - 85115 号公報 (公開日: 平成 11 年 3 月 30 日)」

【特許文献 3】日本国公開特許公報「特開 2004 - 279626 号公報 (公開日: 平成 16 年 10 月 7 日)」

【特許文献 4】日本国公開特許公報「特開 2005 - 121911 号公報 (公開日: 平成 17 年 5 月 12 日)」

30

【特許文献 5】日本国公開特許公報「特開平 9 - 212137 号公報 (公開日: 平成 9 年 8 月 15 日)」

【特許文献 6】日本国公開特許公報「特開平 11 - 030975 号公報 (公開日: 平成 11 年 2 月 2 日)」

【特許文献 7】日本国公開特許公報「特開 2003 - 66918 号公報 (公開日: 平成 15 年 3 月 5 日)」

【特許文献 8】日本国公開特許公報「特開 2004 - 310113 号公報 (公開日: 平成 16 年 11 月 4 日)」

【特許文献 9】日本国公開特許公報「特開 2002 - 175057 号公報 (公開日: 平成 14 年 6 月 21 日)」

40

#### 【発明の開示】

#### 【0013】

しかしながら、ホールド型表示装置としてのアクティブマトリクス型液晶表示装置において、特許文献 7 に記載の方法によってインパルス化を実現しようとすると、黒挿入のために駆動回路などが複雑化すると共に、駆動回路の動作周波数も増大し、画素容量の充電のために確保できる時間も短くなる、という問題が生じる。

#### 【0014】

本発明は、上記の問題点に鑑みてなされたものであり、その目的は、駆動回路などの複雑化や動作周波数の増大や充電効率の低下を抑えつつ表示をインパルス化できる液晶表示装置およびその駆動方法を提供することである。

50

## 【0015】

本発明の液晶表示装置の駆動方法は、上記課題を解決するために、複数のデータ信号線と、これら複数のデータ信号線と交差する複数の走査信号線と、上記複数のデータ信号線と上記複数の走査信号線との交点に対応してマトリクス状に配置され対応する交点を通過する走査信号線が選択されているときに対応する交点を通過するデータ信号線の電圧を画素値として取り込む複数の画素部と、を備えたアクティブマトリクス型の液晶表示装置の駆動方法において、互いに隣接する水平走査期間の境界に非画像信号をデータ信号線に印加する一方、上記走査信号線を有効走査期間で選択し、その後該走査信号線を非選択にした時点から次の有効走査期間よりも前に上記データ信号線への非画像信号の印加のタイミングに合わせて該走査信号線を選択することを特徴としている。

10

## 【0016】

また、本発明の液晶表示装置は、複数のデータ信号線と、これら複数のデータ信号線と交差する複数の走査信号線と、上記複数のデータ信号線と上記複数の走査信号線との交点に対応してマトリクス状に配置され対応する交点を通過する走査信号線が選択されているときに対応する交点を通過するデータ信号線の電圧を画素値として取り込む複数の画素部と、を備えたアクティブマトリクス型の液晶表示装置において、互いに隣接する水平走査期間の境界に非画像信号がデータ信号線に印加される一方、上記走査信号線が有効走査期間で選択され、その後該走査信号線が非選択された時点から次の有効走査期間よりも前に上記データ信号線への非画像信号の印加のタイミングに合わせて該走査信号線が選択されることを特徴としている。

20

## 【0017】

ここで、非画像信号は、黒表示信号を含む、低階調表示、および低輝度表示を行なう信号をいう。

## 【0018】

上記構成によれば、互いに隣接する水平走査期間の境界（すなわち、隣り合う1水平走査期間と1水平走査期間との間）に非画像信号をデータ信号線に印加する一方、走査信号線を有効走査期間で選択し、その後該走査信号線を非選択にした時点から次の有効走査期間よりも前にデータ信号線への非画像信号の印加のタイミングに合わせて該走査信号線を選択している。

30

## 【0019】

上記の「走査信号線を非選択にした時点から次の有効走査期間よりも前」とは、有効走査期間と有効走査期間との間の期間のことをいう。つまり、有効走査期間と有効走査期間との間の期間（非有効走査期間）に、非画像信号をデータ信号線に印加することにより、非画像表示を行なっている。ここで、有効走査期間とは、水平走査期間のうち表示期間に相当する期間のことをいう。具体的には、走査信号線において画素データ書き込みパルスが High レベルになり、データ信号線のその画素に対応する画像信号が選択される期間のことを意味する。それゆえ、非画像表示を行なうための駆動回路をわざわざ設ける必要がなく、かつ、画素値書き込みのための画素容量での充電時間を短縮することなく、インパルス化を図ることができる。その結果、液晶表示装置の動画表示性能を高めることができる。さらに、非画像表示を行なうために、データ線駆動回路などの動作速度を高める必要もない。

40

## 【0020】

従って、駆動回路などの複雑化や動作周波数の増大を抑えつつ表示をインパルス化できる液晶表示装置の駆動方法を提供することができる。

## 【0021】

また、本発明の液晶表示装置の駆動方法では、電界により液晶分子の配向方向を制御する、垂直配向モードの液晶表示装置の駆動方法であって、上記非画像信号を、上記液晶分子をプレチルトさせるためのプレチルト信号にすることが好ましい。

## 【0022】

また、本発明の液晶表示装置では、電界により液晶分子の配向方向を制御する、垂直配

50

向モードの液晶表示装置であって、上記非画像信号は、上記液晶分子をプレチルトさせるためのプレチルト信号であることが好ましい。

【0023】

上記構成によれば、特許文献8に開示されているようなプレチルト信号を発生させる階調信号駆動部を必要とせず、また、特別な演算処理を行うことなく容易にプレチルト信号を生成することができる。

【0024】

また、垂直配向モード(VAモード)の液晶分子を、上記の非画像信号によって、書き込む場合に、非画像信号の電位を液晶分子が垂直配向状態になるまで低くしてしまうと、数フレームにわたる応答異常を生ずることがある。

10

【0025】

すなわち、非画像信号を用いて、黒表示を含む低階調表示および低輝度表示を、画素部に書き込む際の電圧が低ければ低いほど、液晶分子は垂直配向に近くなり、この垂直配向状態から、正規の書き込みをするために電圧を印加すると、液晶分子の傾斜角度は、与える電圧の大きさでコントロールすることができるが、倒れる方向(水平方向)まではコントロールすることができない。

【0026】

この場合、液晶分子は、その時点において、エネルギー的に、安定な配向状態に一旦移行し、その後、液晶分子同士で互いに排斥しながら、正しい水平方向に移動する。従って、所望の配向状態(透過率)に到達するまで、すなわち、目標の階調に到達するまでに時間がかかり、数フレームにわたる応答異常を生じる。数フレームにわたる応答異常が生じた場合、尾引きが生じるという問題がある。

20

【0027】

これに対して、上記構成によれば、非画像信号は、液晶分子をプレチルトさせるためのプレチルト信号となっている。これにより、液晶分子は、垂直配向からプレチルト角、傾斜した状態になる。つまり、黒表示を含む低階調表示および低輝度表示を書き込むときの電圧が、プレチルト角の分だけ、完全に垂直に配向した場合よりも高くなっている。従って、このプレチルト角の分だけ傾斜した状態から電圧を印加させた場合、液晶分子が所望の水平方向へ倒れ、透過率が目標の値に近づくまでの時間を短縮することができる。そのため、応答異常を防止することができ、尾引きを改善することができる。

30

【0028】

また、本発明の液晶表示装置の駆動方法では、白輝度レベルを1とし、黒輝度レベルを0とした場合の表示輝度Tが、表示階調L、白表示階調Lw、および特性に関して、 $T = (L / Lw)$ と略近似できるときに、上記プレチルト信号を、 $Lw \times 10^{-3/4}$ 以上を示す信号とすることが好ましい。

【0029】

また、本発明の液晶表示装置では、白輝度レベルを1とし、黒輝度レベルを0とした場合の表示輝度Tが、表示階調L、白表示階調Lw、および特性に関して、 $T = (L / Lw)$ と略近似できるときに、上記プレチルト信号を、 $Lw \times 10^{-3/4}$ 以上を示す信号とすることが好ましい。

40

【0030】

本発明者らは、白輝度レベルを1とし、黒輝度レベルを0とした場合の表示輝度Tが、表示階調L、白表示階調Lw、および特性に関して、 $T = (L / Lw)$ と略近似できるときに、上記プレチルト信号を、 $Lw \times 10^{-3/4}$ 以上を示す信号とすることにより、尾引き残像を改善できる。

【0031】

また、本発明の液晶表示装置の駆動方法では、白輝度レベルを1とし、黒輝度レベルを0とした場合の表示輝度Tを示す表示階調Lを特性に関して、 $L = 255 \times T^{1/2 \cdot 2}$ と定義し、上記プレチルト信号を、L=12のときの階調電圧より大きい階調電圧を発生する信号とすることが好ましい。

50

## 【0032】

また、本発明の液晶表示装置では、白輝度レベルを1とし、黒輝度レベルを0とした場合の表示輝度Tを示す表示階調Lを特性に関して、 $L = 255 \times T^{(1/2 - 2)}$ と定義し、上記プレチルト信号を、L=12のときの階調電圧より大きい階調電圧を発生する信号とすることが好ましい。

## 【0033】

本発明者らは、白輝度レベルを1とし、黒輝度レベルを0とした場合の表示輝度Tを示す表示階調Lを特性に関して、 $L = 255 \times T^{(1/2 - 2)}$ と定義し、上記プレチルト信号を、L=12のときの階調電圧より大きい階調電圧を発生する信号とした場合にも、尾引き残像を改善できる。

10

## 【0034】

また、本発明の液晶表示装置の駆動方法では、上記プレチルト信号を、特性2.2、表示階調256階調のうちの、12階調以上を示す信号とすることが好ましい。また、本発明の液晶表示装置では、上記プレチルト信号を、特性2.2、表示階調256階調のうちの、12階調以上を示す信号とすることが好ましい。

## 【0035】

本発明者らは、上記プレチルト信号を、特性2.2、表示階調256階調のうちの、12階調以上を示す信号とすれば、尾引き残像を改善できる。

## 【0036】

また、本発明の液晶表示装置の駆動方法では、上記プレチルト信号を、特性2.2、表示階調1024階調のうちの、45階調以上を示す信号とすることが好ましい。また、本発明の液晶表示装置では、上記プレチルト信号を、特性2.2、表示階調1024階調のうちの、45階調以上を示す信号とすることが好ましい。

20

## 【0037】

本発明者らは、上記プレチルト信号を、特性2.2、表示階調1024階調のうちの、45階調以上を示す信号とすれば、尾引き残像を改善できる。

## 【0038】

また、本発明の液晶表示装置の駆動方法では、表示が白となる輝度レベルを100%とする一方、表示が黒となる輝度レベルを0%とした場合、上記プレチルト信号の輝度レベルを0.1%以上とすることが好ましい。

30

## 【0039】

また、本発明の液晶表示装置では、表示が白となる輝度レベルを100%とする一方、表示が黒となる輝度レベルを0%とした場合、上記プレチルト信号の輝度レベルが0.1%以上であることが好ましい。

## 【0040】

本発明者らは、鋭意検討の結果、表示が白となる輝度レベルを100%とする一方、表示が黒となる輝度レベルを0%とした場合、上記プレチルト信号の輝度レベルを0.1%以上とすることにより、尾引き残像を改善できる。

## 【0041】

また、本発明の液晶表示装置の駆動方法では、上記データ信号線への非画像信号の印加は、隣接するデータ信号線を互いに短絡させて行なうことが好ましい。

40

## 【0042】

また、本発明の液晶表示装置では、隣接するデータ信号線は互いに短絡可能に接続されており、上記データ信号線への非画像信号の印加は、データ信号線が短絡されることにより行なわれることが好ましい。

## 【0043】

上記構成によれば、非画像信号のデータ信号線への印加は、隣接するデータ信号線を互いに短絡させることにより行なっている。つまり、データ信号の極性反転時に隣接するデータ信号線を短絡させることによって、データに非画像信号を印加している。それゆえ、消費電力を低減させることができる。

50

**【 0 0 4 4 】**

また、本発明の液晶表示装置の駆動方法では、上記データ信号線への非画像信号の印加は、各データ信号線に固定電圧を与えることにより行なうことが好ましい。

**【 0 0 4 5 】**

また、本発明の液晶表示装置では、各データ信号線に共通の固定電圧を与えることにより上記データ信号線への非画像信号を印加する固定電圧電源を有していることが好ましい。

**【 0 0 4 6 】**

画素部内の寄生容量に基づく引き込み電圧が、輝度の高い画素を表示する場合の画素電圧と、輝度の低い画素を表示する場合の画素電圧とでは異なる。そのため、隣接するデータ信号線を互いに短絡させることにより発生する電圧（非画像信号を与える電圧；チャージシェア電圧ともいう）が、表示階調により異なってしまう。その結果、表示のパターンによっては、ユーザに表示のパターンの影が視認されるという問題が生じる。

**【 0 0 4 7 】**

これに対して、上記構成のように、固定電圧を与えて、非画像信号を印加することにより、データ信号線の電圧を常に同一にすることができ、表示のパターンの影が視認されることを改善できる。

**【 0 0 4 8 】**

また、本発明の液晶表示装置の駆動方法では、上記の非画像信号は、互いに異なる極性間の電圧であり、該非画像信号の上記データ信号線への印加は、データ信号の極性反転時に行なうことが好ましい。

**【 0 0 4 9 】**

また、本発明の液晶表示装置では、上記の非画像信号は、互いに異なる極性間の電圧であり、該非画像信号の上記データ信号線への印加は、データ信号の極性反転時に行なわれることが好ましい。

**【 0 0 5 0 】**

上記構成によれば、非画像信号は互いに異なる極性間の電圧であり、非画像信号のデータ信号線への印加を、データ信号の極性反転時に行なっている。従って、いわゆるドット反転駆動の極性反転のタイミングに合わせて、非画像信号を印加することができ、回路を簡略化することができる。

**【 0 0 5 1 】**

また、本発明の液晶表示装置の駆動方法では、上記データ信号線における信号の極性が、1水平走査期間ごとに反転するときに、上記データ信号線への非画像信号の印加のタイミングにあわせて該走査信号線を選択する回数が偶数であることが好ましい。

**【 0 0 5 2 】**

また、本発明の液晶表示装置では、上記データ信号線における信号の極性が、1水平走査期間ごとに反転しているときに、上記データ信号線への非画像信号の印加のタイミングにあわせて該走査信号線を選択する回数が偶数となっていることが好ましい。

**【 0 0 5 3 】**

上記の構成によれば、各走査信号線において、負から正へ反転する間の非画像信号が選択される回数、および、正から負への反転する間の非画像信号が選択される回数を等しくすることができる。これによって、隣接する画素間の充電率の差を小さくすることができ、走査線ごとに生じる表示ムラを改善しつつ、表示をインパルス化できる液晶表示装置の駆動方法を提供することができる。

**【 0 0 5 4 】**

なお、連続する水平期間毎に非画像信号を選択することがより好ましい。1水平期間毎に画像信号の極性が反転するので、これにより隣接する走査線において、印加される非画像信号の特性をそろえる、すなわち極性の偏りを無くすことができる。

**【 0 0 5 5 】**

また、本発明の液晶表示装置の駆動方法では、上記非画像信号のデータ信号線への印加

10

20

30

40

50

は、1垂直走査期間ごとに極性が反転する電圧を各データ信号線に共通に与えることにより行なうことが好ましい。

【0056】

また、本発明の液晶表示装置では、1垂直走査期間ごとに極性が反転する電圧を各データ信号線に共通に与えることにより上記データ信号線へ非画像信号を印加する、第1の極性反転電源を有していることが好ましい。

【0057】

上記構成によれば、固定電圧を各データ信号線に共通に与えたことにより生じる効果に加えて、1垂直走査期間ごとにデータ信号線に印加する非画像信号の極性を反転させてい10るので、焼き付きを防止することができる。

【0058】

また、本発明の液晶表示装置の駆動方法では、上記非画像信号のデータ信号線への印加は、1水平走査期間ごとに極性が反転する電圧を与えることにより行なうことが好ましい。

【0059】

また、本発明の液晶表示装置では、1水平走査期間ごとに極性が反転する電圧を各データ信号線に共通に与えることにより上記データ信号線へ非画像信号を印加する、第2の極性反転電源を有していることが好ましい。

【0060】

上記構成によれば、固定電圧を各データ信号線に共通に与えたことにより生じる効果に加えて、1水平走査期間ごとにデータ信号線に印加する非画像信号の極性を反転させてい20るので、焼きつきを防止することができる。

【0061】

また、本発明の液晶表示装置の駆動方法では、上記非画像信号のデータ信号線への印加を、隣接するデータ信号線同士を互いに短絡させて、1水平走査期間ごとに極性が反転するとともに隣接するデータ信号線同士は互いに異なる極性となる電圧を与えることにより行なうことが好ましい。

【0062】

また、本発明の液晶表示装置では、上記第2の極性反転電源は、1水平走査期間ごとに極性が反転するとともに、隣接するデータ信号線同士は互いに異なる極性となる電圧を各データ信号線に共通に与えることにより、上記データ信号線へ非画像信号を印加することが好ましい。

【0063】

上記構成によれば、いわゆるドット反転駆動にて駆動させることができるので、焼き付きを防止するとともに、フリッカを防止できる。

【0064】

また、本発明の液晶表示装置の駆動方法では、上記非画像信号の電圧極性は、該非画像信号が印加された直後の水平走査期間における画像信号の電圧極性と同じであることが好ましい。

【0065】

また、本発明の液晶表示装置では、上記非画像信号の電圧極性は、該非画像信号が印加された直後の水平走査期間における画像信号の電圧極性と同じであることが好ましい。

【0066】

上記構成によれば、非画像信号の極性を、後に続く水平走査期間のデータ信号の極性と等しくすることにより、充電率向上に有利となる。

【0067】

また、本発明の液晶表示装置の駆動方法では、1垂直走査期間の最後に選択され、上記画素部に印加される非画像信号の極性は、該1垂直走査期間の次の1垂直走査期間で選択される画像信号の極性と同じであることが好ましい。

【0068】

10

20

30

40

50

また、本発明の液晶表示装置では、1垂直走査期間の最後に選択され、上記画素部に印加される非画像信号の極性は、該1垂直走査期間の次の1垂直走査期間で選択される画像信号の極性と同じになっていることが好ましい。

【0069】

上記構成によれば、後の垂直走査期間（フレーム）において画素部に印加する画像信号の極性と、前の垂直走査期間（フレーム）で画素部に印加する最後の非画像信号（プレチルト信号）の極性とが、同じ極性であることにより、画素の充電率向上に有利となる。

【0070】

また、本発明の液晶表示装置の駆動方法では、上記データ信号線における信号の極性は、複数の水平走査期間ごとに反転することが好ましい。

10

【0071】

また、本発明の液晶表示装置では、上記データ信号線における信号の極性は、複数の水平走査期間ごとに反転することが好ましい。

【0072】

上記構成によれば、1水平走査期間ごとにデータ信号の極性を反転させる場合と比較して、たとえば、パソコンのマイクロソフト社製OS「Windows」（登録商標）終了画面の市松ドット画面や、1ドットでは表現できない輝度の階調を、数ピクセルの組み合わせ（タイルパターン）によって表現するディザリング画面などにおいて、フリッカーなどが発生してキラーパターンとなる可能性を少なくすることができます。

【0073】

なお、非画像信号の極性を後に続く水平走査期間のデータ信号の極性と等しくすることが好ましい。これにより、充電率向上に有利となる。

20

【0074】

また、本発明の液晶表示装置の駆動方法では、隣接する水平期間の間でデータ信号の極性が反転しない時に非画像信号をデータ信号線に印加することが好ましい。

【0075】

また、本発明の液晶表示装置では、隣接する水平期間の間でデータ信号の極性が反転しない時に非画像信号をデータ信号線に印加していることが好ましい。

【0076】

上記構成によれば、複数の水平走査期間ごとにデータ信号の極性を反転させる場合にも、1水平走査期間ごとに走査信号線を選択して、非画像信号を印加することができる。つまり、データ信号線における信号の極性が反転する時だけではなく、極性が反転しない時にも、非画像信号を印加する。これによって、非画像信号が画素に印加される始めと終りのタイミングやトータルの時間を各走査信号線において合わせ易くすることができる。また、極性反転しないときに非画像信号を印加することで、極性反転した直後の水平走査期間の充電率とその後の水平走査期間の充電率とをあわせやすくすることができるため、上記複数の水平走査期間毎に発生するムラ（たとえば2H反転であれば走査線2本毎のムラ）を防止することができる。

30

【0077】

なお、上記の構成において、データ信号線におけるデータ信号の極性が反転する時に入力された非画像信号が選択される回数が各走査信号線において等しくなることが好ましい。また、データ信号線におけるデータ信号の極性が反転しない時に入力された非画像信号が選択される回数が各走査信号線において等しくなることが好ましい。

40

【0078】

そのために、本発明の液晶表示装置の駆動方法においては、上記データ信号線における信号の極性が、n個（ここで、nは2以上の整数）の水平走査期間ごとに反転するときには、上記データ信号線への非画像信号の印加のタイミングにあわせて該走査信号線を選択する回数がnの倍数であることが好ましい。

【0079】

また、本発明の液晶表示装置においては、上記データ信号線における信号の極性が、n

50

個（ここで、 $n$  は 2 以上の整数）の水平走査期間ごとに反転しているときに、上記データ信号線への非画像信号の印加のタイミングにあわせて該走査信号線を選択する回数が  $n$  の倍数となっていることが好ましい。

【0080】

上記構成によれば、隣接する走査線間において、極性が反転するときに印加される非画像信号の数と、極性が反転しないときに印加される非画像信号の数とをそろえることができる。これによって、隣接する画素間の充電率の差を小さくすることができ、走査線ごとに生じる表示ムラを改善しつつ、表示をインパルス化できる液晶表示装置を提供することができる。

【0081】

なお、連続する水平期間毎に非画像信号を選択することがより好ましい。これによれば、 $n$  個の水平期間で画像信号極性が反転する数と極性反転しない数が各走査線において一定となるので、隣接する走査線間において、印加される非画像信号の特性をそろえることができる。

【0082】

また、本発明の液晶表示装置の駆動方法では、上記データ信号線への非画像信号の印加のタイミングにあわせて該走査信号線を選択する回数が  $2n$  の倍数であることが好ましい。

【0083】

また、本発明の液晶表示装置では、上記データ信号線への非画像信号の印加のタイミングにあわせて該走査信号線を選択する回数が  $2n$  の倍数となっていることが好ましい。

【0084】

上記構成によれば、各走査信号線においてデータ信号の極性が反転する場合の、負から正へ反転する間の非画像信号が選択される回数、および、正から負への反転する間の非画像信号が選択される回数を等しくすることができるとともに、信号の極性が反転しない場合の、正と正との間に印加される非画像信号が選択される回数、および、負と負との間に印加される非画像信号が選択される回数を等しくすることができる。これによって、隣接する画素間の充電率の差をより小さくすることができ、走査線ごとに生じるムラをより改善することができる。

【0085】

なお、連続する水平期間毎に非画像信号を選択することがより好ましい。これによれば、 $2n$  個の水平期間周期で画像信号の極性が反転するので、隣接する走査線間において、印加される非画像信号の特性をそろえる、すなわち極性の偏りを無くすことができる。

【0086】

また、本発明の液晶表示装置の駆動方法では、上記データ信号線への非画像信号の印加は、各データ信号線に固定電圧を与えることにより行ない、該固定電圧の極性は、上記複数の水平走査期間ごとに反転することが好ましい。

【0087】

本発明の液晶表示装置では、上記複数の水平走査期間ごとに極性が反転する電圧を各データ信号線に与えることにより上記データ信号線へ非画像信号を印加する、第 3 の極性反転電源を有していることが好ましい。

【0088】

上記構成によれば、固定電圧を各データ信号線に与えたことにより生じる効果に加えて、複数の水平走査期間ごとにデータ信号線に印加する非画像信号の極性を反転させているので、焼きつきを防止することができる。

【0089】

また、本発明の液晶表示装置の駆動方法では、上記固定電圧は、複数の水平走査期間ごとに極性が反転するとともに、隣接するデータ信号線同士に与えられる固定電圧は互いに異なる極性を有することが好ましい。

【0090】

10

20

30

40

50

本発明の液晶表示装置では、上記第3の極性反転電源は、上記複数の水平走査期間ごとに極性が反転するとともに隣接するデータ信号線同士は互いに異なる極性となる電圧を各データ信号線に与えることにより上記データ信号線へ非画像信号を印加するものであることが好ましい。

【0091】

上記構成によれば、いわゆるドット反転駆動にて駆動させることができるので、焼き付きを防止するとともに、フリッカを防止できる。

【0092】

また、本発明の液晶表示装置の駆動方法では、オーバーシュート駆動を行なう液晶表示装置の駆動方法であって、画素の極性および外部から得た映像信号に基づいて、オーバーシュート駆動に用いる階調補正量を求めることが好ましい。10

【0093】

また、本発明の液晶表示装置では、各画素の極性情報を検知する極性情報検知手段と、該極性情報および外部から得た映像信号に基づいてオーバーシュート駆動の階調補正量を求める補正量演算手段と、をさらに有していることが好ましい。

【0094】

通常、オーバーシュート駆動は、開始階調と目的階調とから適切な階調補正量（OS量）を演算して、行なっている。また、液晶分子のプレチルト角が非常に小さい場合には、液晶分子が倒れる方向が定まらないため、階調補正量を求めるためには、この点を考慮に入れた特別な補正アルゴリズムを構築する必要がある。そのため、回路規模が大きくなるか、または、リアルタイムでの演算が困難になるという問題がある。これに対して、上記構成によれば、画素の極性および外部から得た映像信号に基づいて、オーバーシュート駆動に用いる階調補正量を求めてている。そのため、特別な補正アルゴリズムを用いることなく、階調補正量を求めることができると共に、既存のオーバーシュート駆動をほぼそのまま用いることができる。20

【0095】

また、本発明の液晶表示装置の駆動方法では、上記画素の極性および上記外部から得た映像信号を対応付けたルックアップテーブルを用いて上記オーバーシュート駆動に用いる階調補正量を求めることが好ましい。

【0096】

また、本発明の液晶表示装置では、上記画素の極性および上記外部から得た映像信号を対応付けたルックアップテーブルを有していることが好ましい。30

【0097】

上記構成によれば、画素の極性と外部から得た映像信号とから、ルックアップテーブルを参照するだけで、階調補正量を求めることができる。

【0098】

また、本発明の液晶表示装置の駆動方法では、バックライトを有する液晶表示装置の駆動方法であって、上記非画像信号のデータ信号線への印加のタイミングに合わせて、バックライトを消灯することが好ましい。

【0099】

非画像信号をデータ信号線に印加した場合に、その電位が輝度アップにつながり、黒輝度が浮いてくるという問題が生じる。これに対して、上記のようにバックライトを消灯させれば、この黒輝度の浮きが視認されることを防止することができる。40

【0100】

また、本発明の液晶表示装置の駆動方法では、上記データ信号線への上記非画像信号の印加時間は、上記データ信号へ印加される画像を表示するための画像信号の印加時間に比べて短いことが好ましい。

【0101】

また、本発明の液晶表示装置では、上記データ信号線への上記非画像信号の印加時間は、上記データ信号へ印加される画像を表示するための画像信号の印加時間に比べて短くな50

っていることが好ましい。

【0102】

特許文献9には、1フレーム期間内に各ゲートライン（走査信号線）が少なくとも2回選択され、該ゲートラインに接続された画素に、各画素の状態をそろえるための消去電圧および表示すべき画像に対応した階調電圧がそれぞれ少なくとも1回ずつ書き込まれるようにした液晶表示装置が開示されている。この液晶表示装置によれば、表示画像の残像を抑制して良好な動画表示を得ることができる。しかし、この液晶表示装置では、ソースラインに供給される電圧は、画像信号に基づく階調電圧と黒化電圧との間で交互に切換えられ、階調電圧の印加のために各ゲートラインが選択される期間は、1フレーム期間をゲートラインの本数で割った時間のさらに半分の時間となっている。このように、階調電圧による画素容量の充電のための時間が短くなると、充電不足が発生することが懸念される。

10

【0103】

そこで、上記構成のように、データ信号線に印加される非画像信号の印加時間を、画像信号の印加時間に比べて短くすることで、各画素における画像信号の充電不足を抑えながら表示をインパルス化することが可能となる。特に画面サイズの大型化や高精細化に伴うデータ信号線等の負荷増大時や、フレーム周波数の高速化によるさらなる動画視認性改善を行う場合の画像信号の印加時間の縮小時に、上記構成は好適となる。

【0104】

また、本発明の液晶表示装置の駆動方法においては、当該液晶表示装置が、電圧を印加しない状態で黒表示となるノーマリーブラックモードの液晶表示装置であることが好ましい。

20

【0105】

また、本発明の液晶表示装置は、電圧を印加しない状態で黒表示となるノーマリーブラックモードの液晶表示装置であることが好ましい。

【0106】

上記構成によれば、ノーマリーブラックモードの液晶表示装置として、例えば、非画像信号をチャージシェア電位とする場合において、容易に黒挿入表示が可能となるとともに、消費電力的にも有利な表示装置を構成することができる。

【0107】

また、本発明の液晶表示プログラムは、上記液晶表示装置を動作させるための液晶表示プログラムであって、コンピュータを上記極性情報検知手段および上記補正量演算手段として機能させる液晶表示プログラムであることが好ましい。

30

【0108】

また、本発明のコンピュータ読み取り可能な記録媒体は、上記液晶表示プログラムを記録したコンピュータ読み取り可能な記録媒体であることが好ましい。

【0109】

また、本発明のテレビ受像機は、上記液晶表示装置とテレビジョン放送を受信するチューナー部とを備えて成ることが好ましい。

【0110】

また、本発明の駆動回路は、上記課題を解決するために、複数のデータ信号線と、これら複数のデータ信号線と交差する複数の走査信号線と、上記複数のデータ信号線と上記複数の走査信号線との交点に対応してマトリクス状に配置され対応する交点を通過する走査信号線が選択されているときに対応する交点を通過するデータ信号線の電圧を画素値として取り込む複数の画素部と、を備えたアクティブマトリクス型の液晶表示装置に用いる駆動回路において、互いに隣接する水平走査期間の境界に非画像信号がデータ信号線に印加される一方、上記走査信号線が有効走査期間で選択され、その後該走査信号線が非選択された時点から次の有効走査期間よりも前に上記データ信号線への非画像信号の印加のタイミングに合わせて該走査信号線が選択されることを特徴としている。

40

【0111】

上記構成によれば、互いに隣接する水平走査期間の境界に非画像信号をデータ信号線に

50

印加する一方、走査信号線を有効走査期間で選択し、その後該走査信号線を非選択にした時点から次の有効走査期間よりも前にデータ信号線への非画像信号の印加のタイミングに合わせて該走査信号線を選択している。

【0112】

つまり、有効走査期間と有効走査期間との間の期間（非有効走査期間）に、非画像信号をデータ信号線に印加することにより、非画像表示を行なっている。ここで、有効走査期間とは、水平走査期間のうち表示期間に相当する期間のことをいう。具体的には、走査信号線において画素データ書き込みパルスがHighレベルになる期間のことを意味する。それゆえ、非画像表示を行なうための駆動回路をわざわざ設ける必要がなく、かつ、画素値書き込みのための画素容量での充電時間を短縮することなく、インパルス化を図ることができる。その結果、液晶表示装置の動画表示性能を高めることができる。さらに、非画像表示を行なうために、データ線駆動回路などの動作速度を高める必要もない。

10

【0113】

従って、本発明の駆動回路を使用すれば、駆動回路などの複雑化や動作周波数の増大を抑えつつ表示をインパルス化できる液晶表示装置を実現することができる。

【0114】

また、本発明の駆動回路は、上記課題を解決するために、複数のデータ信号線と、これら複数のデータ信号線と交差する複数の走査信号線と、上記複数のデータ信号線と上記複数の走査信号線との交点に対応してマトリクス状に配置され対応する交点を通過する走査信号線が選択されているときに対応する交点を通過するデータ信号線の電圧を画素値として取り込む複数の画素部と、を備えたアクティブマトリクス型の液晶表示装置に用いられ、複数のデータ信号線にデータ信号を供給する駆動回路であって、上記複数のデータ信号線に接続され、極性反転する電圧を生成可能な第1の極性反転電源を備えており、該第1の極性反転電源は、ゲートスタートパルス信号の当該電源への入力のタイミングに同期して1垂直走査期間ごとに極性が反転する電圧を生成し、該生成された電圧を上記データ信号の極性の反転時に非画像信号として上記複数のデータ信号線に印加することを特徴としている。

20

【0115】

ここで、ゲートスタートパルス信号とは、ゲートドライバのシフトレジスタの動作を開始するために液晶表示装置の表示制御回路で生成された信号である。

30

【0116】

上記構成によれば、駆動回路は、非画像信号としてデータ信号線に印加する電圧を1垂直走査期間ごとに反転させる第1の極性反転電源を備えている。つまり、データ信号線に印加する電圧をフレーム反転させている。従って、電圧が片側極性となることにて生じる焼き付きを防止することができる。

【0117】

また、本発明の駆動回路は、上記課題を解決するために、複数のデータ信号線と、これら複数のデータ信号線と交差する複数の走査信号線と、上記複数のデータ信号線と上記複数の走査信号線との交点に対応してマトリクス状に配置され対応する交点を通過する走査信号線が選択されているときに対応する交点を通過するデータ信号線の電圧を画素値として取り込む複数の画素部と、を備えたアクティブマトリクス型の液晶表示装置に用いられ、複数のデータ信号線に映像信号を供給する駆動回路であって、上記複数のデータ信号線に接続され、極性反転する電圧を生成可能な第2の極性反転電源を備えており、該第2の極性反転電源は、ゲートクロック信号の当該電源への入力のタイミングに同期して1水平走査期間ごとに極性が反転する電圧を生成し、該生成された電圧をデータ信号の極性の反転時に非画像信号として上記複数のデータ信号線に印加することを特徴としている。

40

【0118】

ここで、ゲートクロック信号とは、ゲートドライバのシフトレジスタがシフト動作するタイミングを制御するために液晶表示装置の表示制御回路で生成された信号である。

【0119】

50

上記構成によれば、駆動回路は、非画像信号としてデータ信号線に印加する電圧を1水平走査期間ごとに極性が反転する電圧を生成可能な第2の極性反転電源を備えている。つまり、データ信号線に印加する電圧をライン反転させている。従って、電圧が片側極性となることにて生じる焼き付きを防止することができる。

【0120】

また、本発明の駆動回路は、上記課題を解決するために、複数のデータ信号線と、これら複数のデータ信号線と交差する複数の走査信号線と、上記複数のデータ信号線と上記複数の走査信号線との交点に対応してマトリクス状に配置され対応する交点を通過する走査信号線が選択されているときに対応する交点を通過するデータ信号線の電圧を画素値として取り込む複数の画素部と、を備えたアクティブマトリクス型の液晶表示装置に用いられ、複数のデータ信号線に映像信号を供給する駆動回路であって、上記複数のデータ信号線に接続され、極性反転する電圧を生成可能な第2の極性反転電源を備えており、該第2の極性反転電源は、ゲートクロック信号の入力のタイミングに同期して1水平走査期間ごとに極性が反転する電圧を生成し、上記複数のデータ信号線のうち奇数行のデータ信号線には上記生成された電圧をデータ信号の極性の反転時に非画像信号として印加する一方、上記複数のデータ信号線のうち偶数行のデータ信号線には上記生成された電圧とは極性の異なる電圧をデータ信号の極性の反転時に非画像信号として印加することを特徴としている。

10

【0121】

上記構成によれば、駆動回路は、奇数行のデータ信号線には上記生成された電圧をデータ信号の極性の反転時に非画像信号として印加する一方、偶数行のデータ信号線には上記生成された電圧とは極性の異なる電圧をデータ信号の極性の反転時に非画像信号として印加する第2の極性反転電源を備えている。つまり、データ信号線に印加する電圧をドット反転させている。従って、電圧が片側極性となることにて生じる焼き付きを防止することができると共に、フリッカを防止することができる。

20

【0122】

また、本発明の駆動回路は、上記課題を解決するために、複数のデータ信号線に映像信号を供給する駆動回路であって、上記複数のデータ信号線にそれぞれ接続された定電圧ダイオードと、これら定電圧ダイオードを介して上記複数のデータ信号線に接続され、上記複数のデータ信号線のそれぞれに共通の固定電圧をデータ信号の極性の反転時に非画像信号として印加する固定電圧電源とを備えていることを特徴としている。上記構成によれば、定電圧ダイオードを介して、固定電圧電源とデータ信号線とを接続させている。そして、この定電圧ダイオードに電圧を蓄積することができるので、より簡易な構造で電圧のドット反転を実現することができる。

30

【0123】

また、本発明の駆動回路は、上記課題を解決するために、複数のデータ信号線に映像信号を供給する駆動回路であって、上記複数のデータ信号線に接続され、極性反転する電圧を生成可能な第3の極性反転電源を備えており、該第3の極性反転電源は、複数の水平走査期間ごとに極性が反転する電圧を生成し、該生成された電圧を非画像信号として上記複数のデータ信号線に印加することを特徴としている。

40

【0124】

ここで、上記電圧の極性は、極性反転を決定するためのリバース信号の第3の極性反転電源への入力のタイミングに同期して極性を反転する。

【0125】

上記構成によれば、駆動回路は、非画像信号としてデータ信号線に印加する電圧を複数の水平走査期間ごとに極性が反転する電圧を生成可能な第3の極性反転電源を備えている。つまり、データ信号線に印加する電圧をライン反転させている。従って、電圧が片側極性となることにて生じる焼き付きを防止することができる。

【0126】

また、本発明の駆動回路では、上記第3の極性反転電源は、複数の水平走査期間ごとに

50

極性が反転する電圧を生成するとともに、上記複数のデータ信号線のうち奇数行のデータ信号線には上記生成された電圧を非画像信号として印加する一方、上記複数のデータ信号線のうち偶数行のデータ信号線には上記生成された電圧とは極性の異なる電圧を非画像信号として印加することが好ましい。

【0127】

上記構成によれば、駆動回路は、奇数行のデータ信号線には上記生成された電圧を非画像信号として印加する一方、偶数行のデータ信号線には上記生成された電圧とは極性の異なる電圧を非画像信号として印加する第3の極性反転電源を備えている。つまり、データ信号線に印加する電圧をドット反転させている。従って、電圧が片側極性となることにて生じる焼き付きを防止することができると共に、フリッカを防止することができる。

10

【0128】

また、本発明の液晶表示装置の駆動方法は、複数のデータ信号線と、これら複数のデータ信号線と交差する複数の走査信号線と、上記複数のデータ信号線と上記複数の走査信号線との交点に対応してマトリクス状に配置され対応する交点を通過する走査信号線が選択されているときに対応する交点を通過するデータ信号線の電圧を画素値として取り込む複数の画素部と、を備えたアクティブマトリクス型の液晶表示装置の駆動方法において、互いに隣接する水平走査期間の境界に、後半の水平走査期間において印加される画像信号の電圧極性と同じ電圧極性の非画像信号を、データ信号線に印加することを特徴とする。

【0129】

上記構成によれば、互いに隣接する水平走査期間の境界に印加される非画像信号の電圧極性が、隣接する水平走査期間の後半側の水平走査期間において印加される画像信号の電圧極性と同じであることにより、画素の充電率向上に有利となる。

20

【0130】

また、本発明の液晶表示装置は、上記の駆動方法を用いて駆動されるものであってもよい。これによれば、画素の充電率向上に有利となる。

【0131】

本発明のさらに他の目的、特徴、および優れた点は、以下に示す記載によって十分わかるであろう。また、本発明の利益は、添付図面を参照した次の説明で明白になるであろう。

【図面の簡単な説明】

30

【0132】

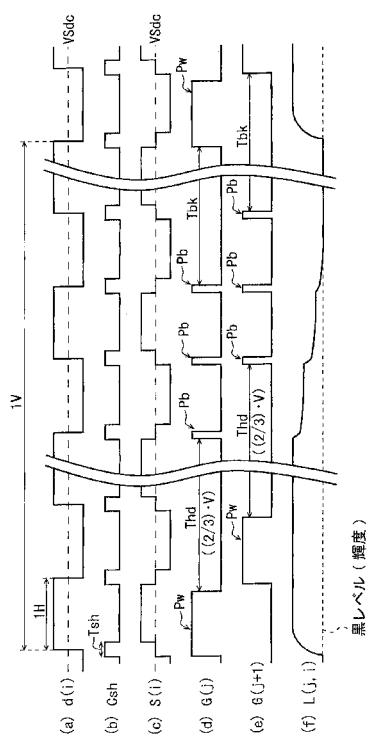

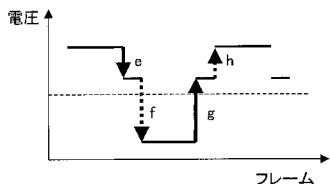

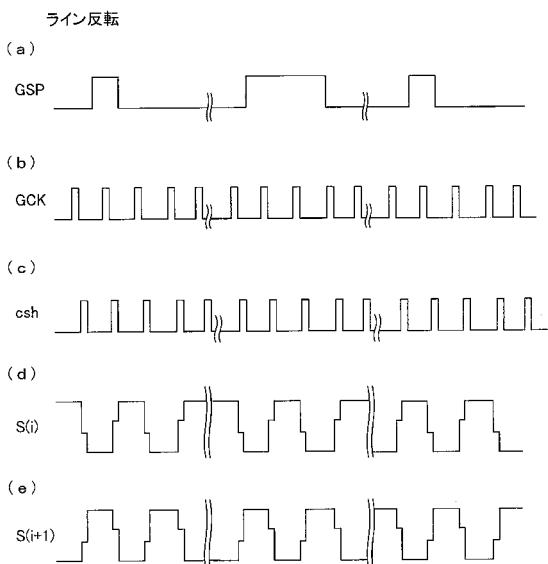

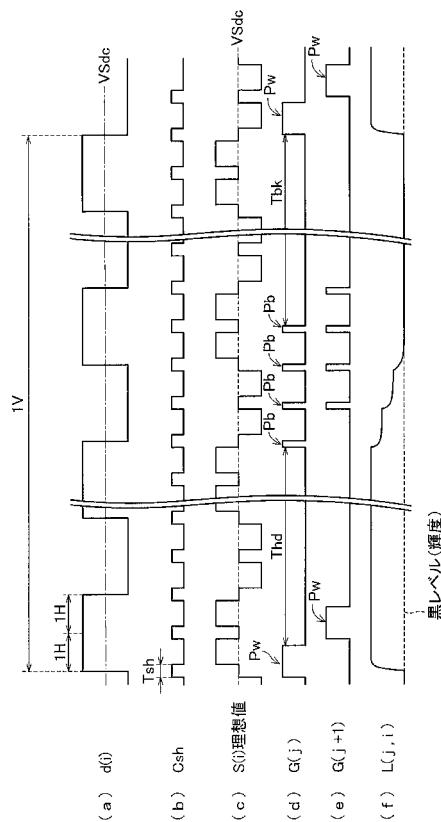

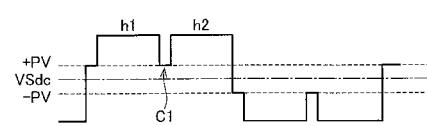

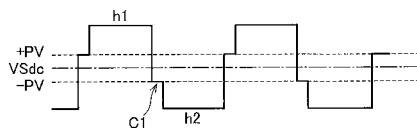

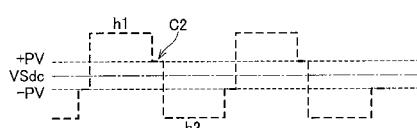

【図1】(a)はアナログ電圧信号を示す波形図であり、(b)はチャージシェア制御信号を示す波形図であり、(c)はデータ信号を示す波形図であり、(d)はゲートラインG<sub>Lj</sub>に印加される走査信号G<sub>(j)</sub>を示す波形図であり、(e)はゲートラインG<sub>j+1</sub>に印加される走査信号G<sub>(j+1)</sub>を示す波形図であり、(f)は画素の輝度を示す波形図である。なお、これらの波形図は、本発明の第1の実施の形態の液晶表示装置に関するものである。

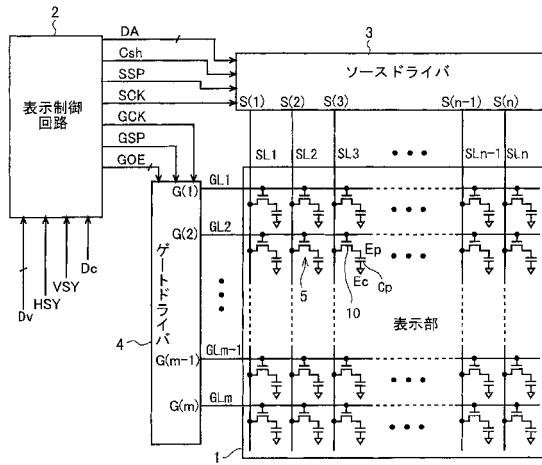

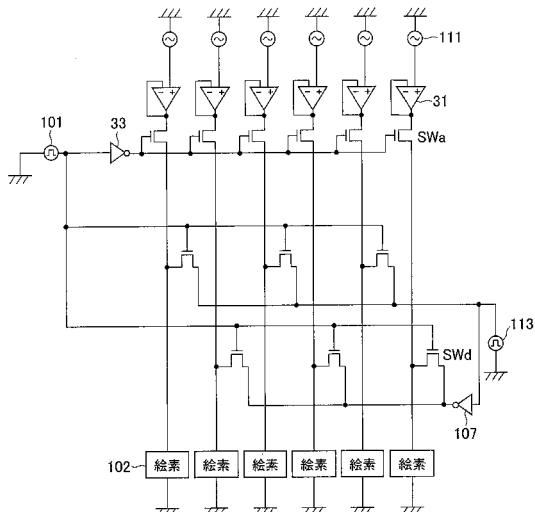

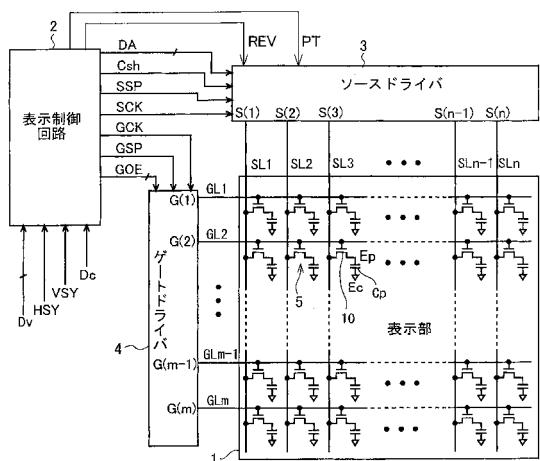

【図2】本実施の形態の液晶表示装置を、その表示部の等価回路と共に示すブロック図である。

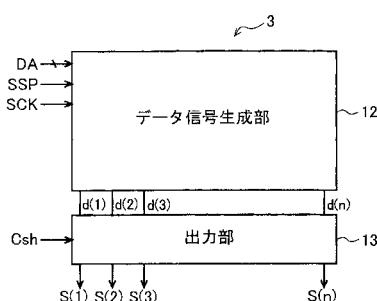

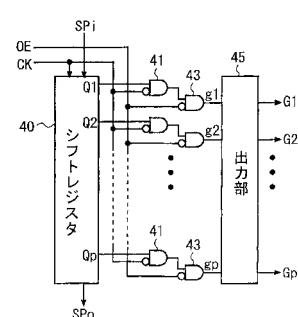

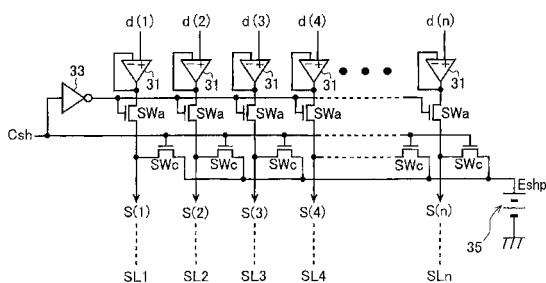

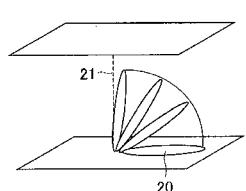

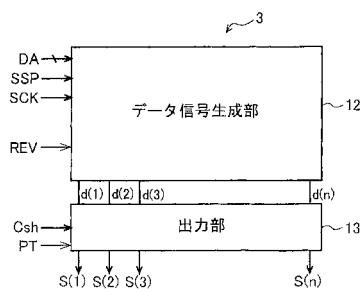

【図3】図2に示すソースドライバの構成を示すブロック図である。

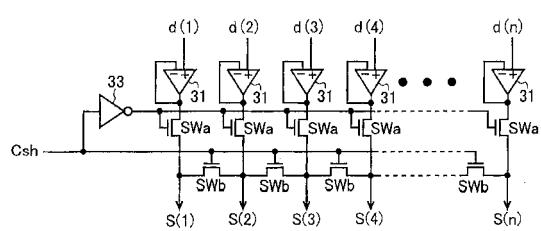

40

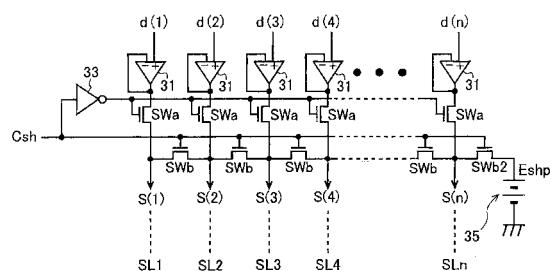

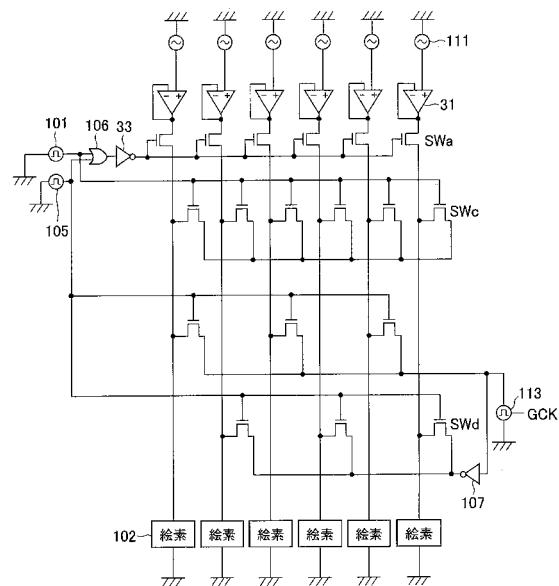

【図4】図3に示すソースドライバの出力部を示す回路図である。

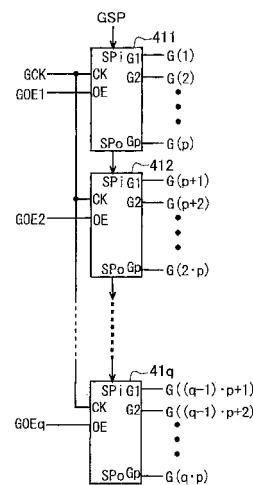

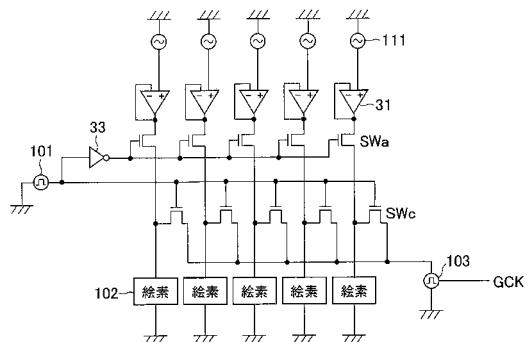

【図5(a)】図2に示すゲートドライバの構成を示すブロック図である。

【図5(b)】図5(a)のゲートドライバ用ICチップの構成を示すブロック図である。

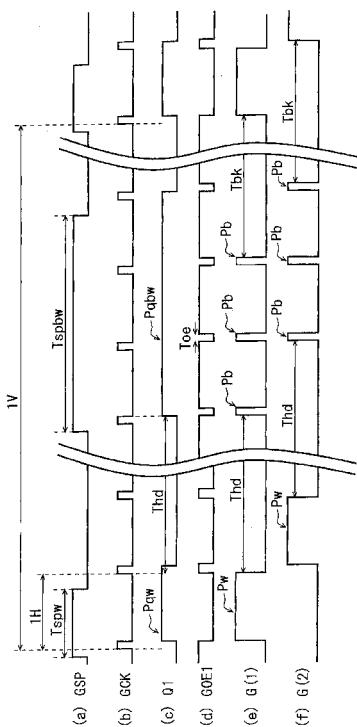

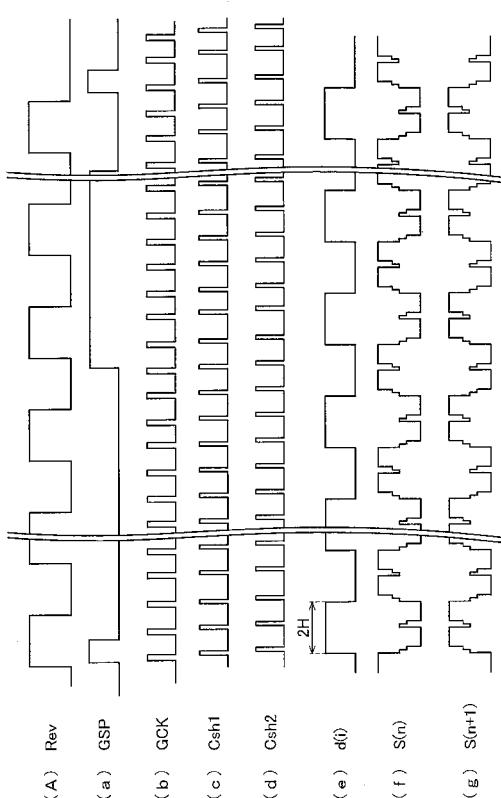

【図6】(a)はゲートスタートパルス信号G<sub>SP</sub>を示す波形図であり、(b)はゲートクロック信号G<sub>CK</sub>を示す波形図であり、(c)はシフトレジスタの初段の出力信号Q<sub>1</sub>を示す波形図であり、(d)は先頭のゲートドライバ用ICチップ411に与えられるゲートドライバ出力制御信号G<sub>OE</sub>1を示す波形図であり、(e)はゲートラインG<sub>L1</sub>に印加される走査信号G<sub>(1)</sub>を示す波形図であり、(f)はゲートラインG<sub>L2</sub>に印加される走査信号G<sub>(2)</sub>を示す波形図である。

50

【図7】各画素形成部におけるTFTのゲート・ドレイン間に存在する寄生容量を示す図である。

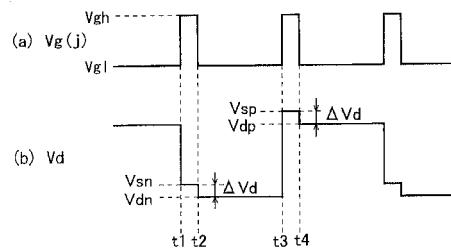

【図8】(a)はゲートラインG<sub>Lj</sub>に印加される走査信号G(j)の電圧であるゲート電圧V<sub>g(j)</sub>を示す波形図であり、(b)は画素形成部5における画素電極E<sub>p</sub>の電圧(画素電圧)V<sub>d</sub>を示す波形図である。

【図9】輝度の高い画素を表示する場合の画素電圧(高輝度画素電圧)V<sub>d(B)</sub>の電圧波形W<sub>d(B)</sub>と、輝度の低い画素を表示する場合の画素電圧(低輝度画素電圧)V<sub>d(D)</sub>の電圧波形W<sub>d(D)</sub>と、高輝度画素電圧V<sub>d(B)</sub>を与えるためのデータ信号の電圧(高輝度ソース電圧)V<sub>s(B)</sub>の電圧波形W<sub>s(B)</sub>と、低輝度画素電圧V<sub>d(D)</sub>を与えるためのデータ信号の電圧(低輝度ソース電圧)V<sub>s(D)</sub>の電圧波形W<sub>s(D)</sub>と、を示す波形図である。

10

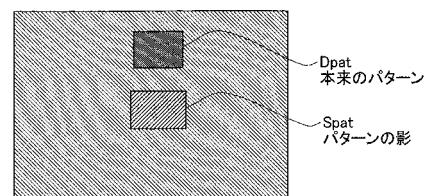

【図10】黒電圧としてのチャージシェア電圧V<sub>csh</sub>の書き込みに基づく表示パターンD<sub>pat</sub>に相当する影のパターンS<sub>pat</sub>を示す図である。

【図11】ソースドライバの出力部の図4とは異なる、他の構成を示す回路図である。

【図12】ソースドライバの出力部の図4とは異なる、さらに他の構成を示す回路図である。

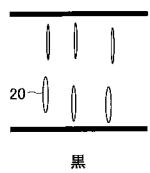

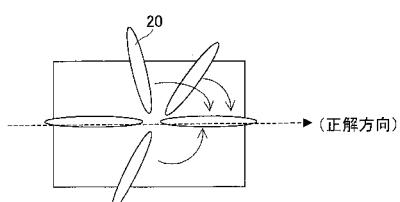

【図13(a)】垂直配向状態の液晶分子を示す模式図である。

【図13(b)】図13(a)の状態から高電圧を印加した場合の液晶分子の配向状態を示す模式図である。

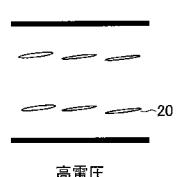

【図14】垂直配向状態の液晶分子に電圧を印加することによる液晶分子の傾斜角度の制御の様子を示す図である。

20

【図15】垂直配向状態の液晶分子に電圧を印加した場合の液晶分子の転倒方向を上から見た平面図である。

【図16】液晶を傾斜配向させるための構成を示す図である。

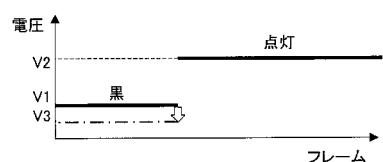

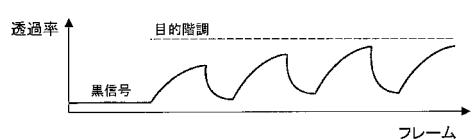

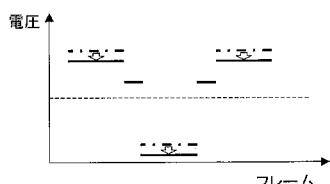

【図17(a)】黒信号電位、黒書き込み電位、および点灯状態の電位を示す電圧・フレームの関係図である。

【図17(b)】黒から点灯状態への階調の変化および黒書き込みから点灯状態への階調の変化を示すグラフである。

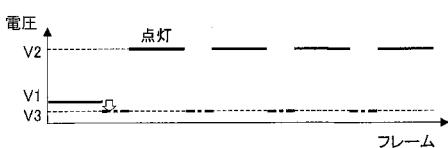

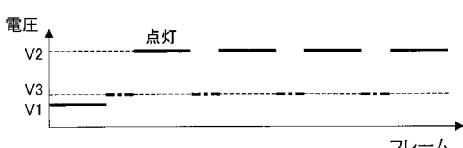

【図18(a)】電圧・フレームの関係図であり、図17(a)に対応した図である。

【図18(b)】チャージシェアインパルス駆動の黒から点灯状態への階調の変化および黒書き込みから点灯状態への階調の変化を示すグラフであり、図17(b)に対応した図である。

30

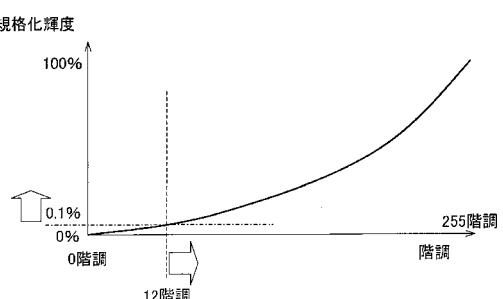

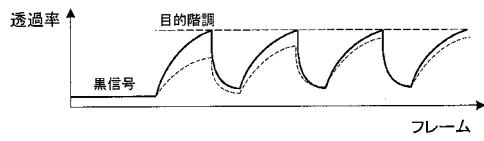

【図19】縦軸を規格化輝度とする一方、横軸を階調した場合の、所望の輝度および階調の範囲を示す図である。

【図20(a)】図19に示す所望の輝度および階調の範囲とした場合の電圧・フレームの関係図であり、図18(a)に対応した図である。

【図20(b)】図19に示す所望の輝度および階調の範囲とした場合の黒から点灯状態への階調の変化および黒書き込みから点灯状態への階調の変化を示すグラフであり、図18(b)に対応した図である。

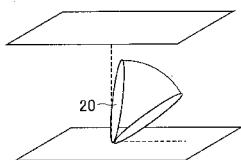

【図21】プレチルト信号を256階調(2.2)中、12階調以上に設定して黒書き込みを行なうことにより、液晶分子20が垂直配向状態からやや傾斜した状態から転倒する様子を示す図である。

40

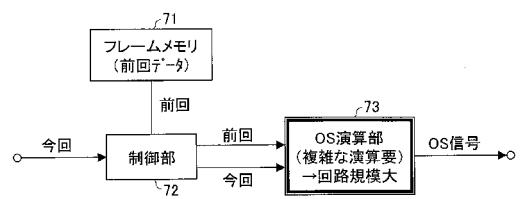

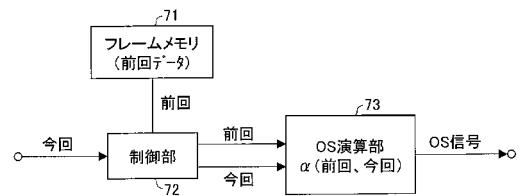

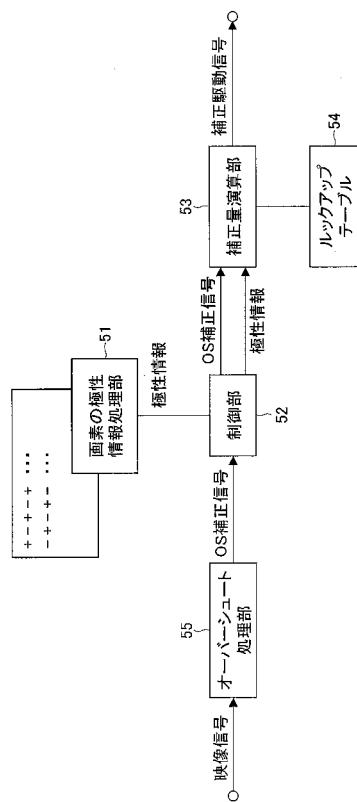

【図22】水平方位角方向を制御できない場合の、OS駆動回路を示すブロック図である。

【図23】水平方位角方向を制御できる場合の、OS駆動回路を示すブロック図である。

【図24】黒書き込みを行なう場合の、理想的な電圧とフレームとの関係を示すグラフである。

【図25】黒書き込みを固定電位にて行なう場合の、電圧とフレームとの関係を示すグラフである。

【図26】図25に示す電圧とフレームとの関係から、アナログ電圧を調整してプラス極

50

性とマイナス極性での実効値を補正した電圧とフレームとの関係を示すグラフである。

【図27】OS駆動回路の概略構成を示すブロック図である。

【図28】画素の極性情報と画素の位置情報である番地との関係を示す図である。

【図29】図27に示すLUTの構成を示す図である。

【図30】他のOS駆動回路の概略構成を示すブロック図である。

【図31】図30に示すLUTの構成を示す図である。

【図32】図25に示す電圧とフレームとの関係から、図27に示すOS駆動回路を用いて極性値をデジタル補正した電圧とフレームとの関係を示すグラフである。

【図33】バックライトの概略構成を示す図である。

【図34】(a)は、1Vにおける、あるゲートラインGLjに印加される走査信号の波形図であり、(b)は、1Vにおける、バックライトの点灯・消灯とを示す波形図である。

【図35】テレビジョン受信機用の液晶表示装置の回路ブロックを示す図である。

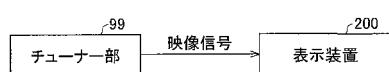

【図36】チューナー部と表示装置との信号のやりとりを示すブロック図である。

【図37】液晶表示装置を用いたテレビジョン受信機を示す分解斜視図である。

【図38】ソースドライバの出力部の他の構成を示す回路図である。

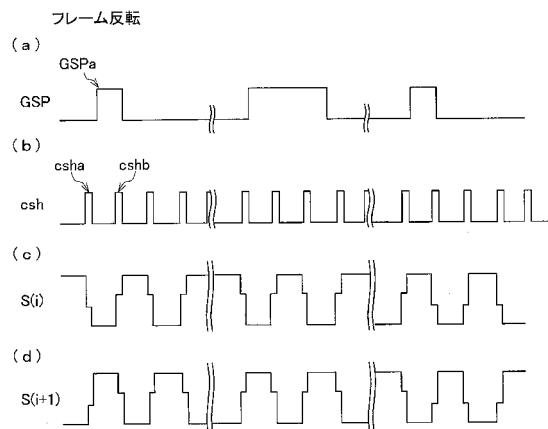

【図39】(a)はゲートスタートパルス信号GSPを示す波形図であり、(b)はチャージシェア制御信号を示す波形図であり、(c)はデータ信号を示す波形図であり、(d)は同じくデータ信号を示す波形図である。

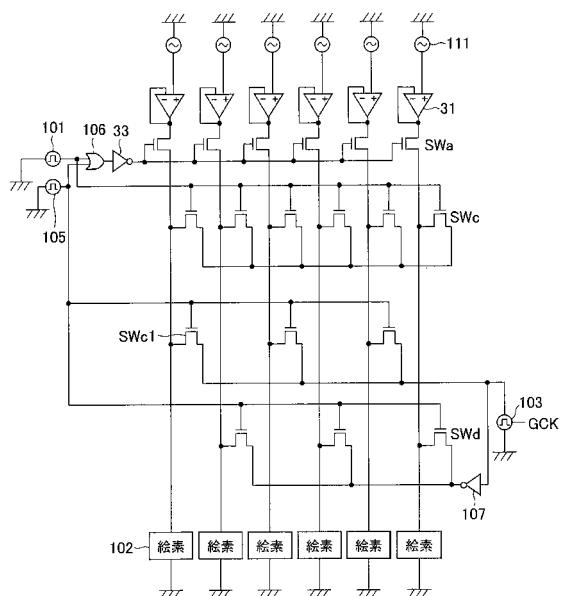

【図40】ソースドライバの出力部の他の構成を示す回路図である。

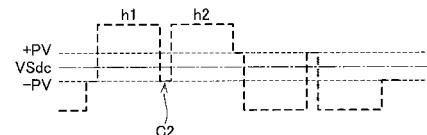

【図41】(a)はゲートスタートパルス信号GSPを示す波形図であり、(b)はゲートロック信号を示す波形図であり、(c)はチャージシェア制御信号を示す波形図であり、(d)はデータ信号を示す波形図であり、(e)は同じくデータ信号を示す波形図である。

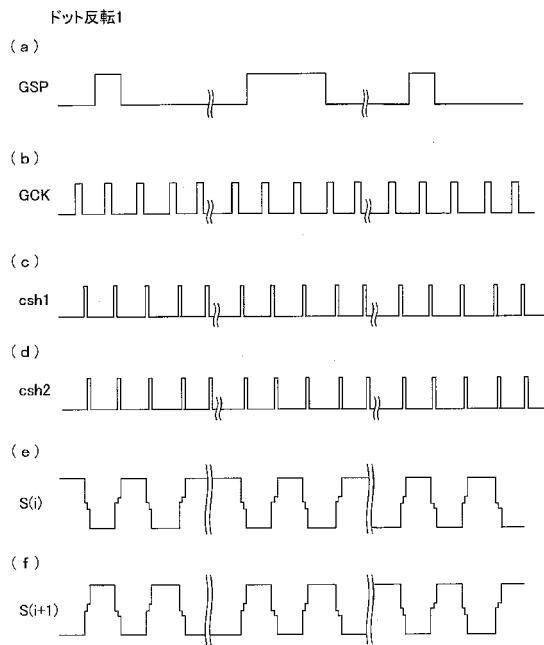

【図42】ソースドライバの出力部の他の構成を示す回路図である。

【図43】(a)はゲートスタートパルス信号GSPを示す波形図であり、(b)はゲートロック信号を示す波形図であり、(c)はチャージシェア制御信号を示す波形図であり、(d)は同じくチャージシェア制御信号を示す波形図であり、(e)はデータ信号を示す波形図であり、(f)は同じくデータ信号を示す波形図である。

【図44】ソースドライバの出力部の他の構成を示す回路図である。

【図45】(a)はゲートスタートパルス信号GSPを示す波形図であり、(b)はゲートロック信号を示す波形図であり、(c)はチャージシェア制御信号を示す波形図であり、(d)はデータ信号を示す波形図であり、(e)は同じくデータ信号を示す波形図である。

【図46】ソースドライバの出力部の他の構成を示す回路図である。

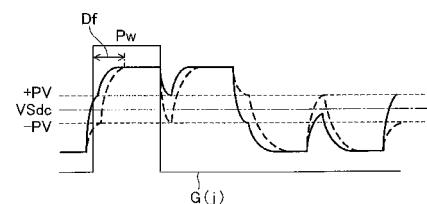

【図47】(a)はゲートスタートパルス信号GSPを示す波形図であり、(b)はゲートロック信号を示す波形図であり、(c)はチャージシェア制御信号を示す波形図であり、(d)はアナログ電圧信号を示す波形図であり、(e)は同じくアナログ電圧信号を示す波形図であり、(f)は非画像信号を示す波形図であり、(g)は同じく非画像信号を示す波形図であり、(h)はデータ信号を示す波形図であり、(i)は同じくデータ信号を示す波形図である。

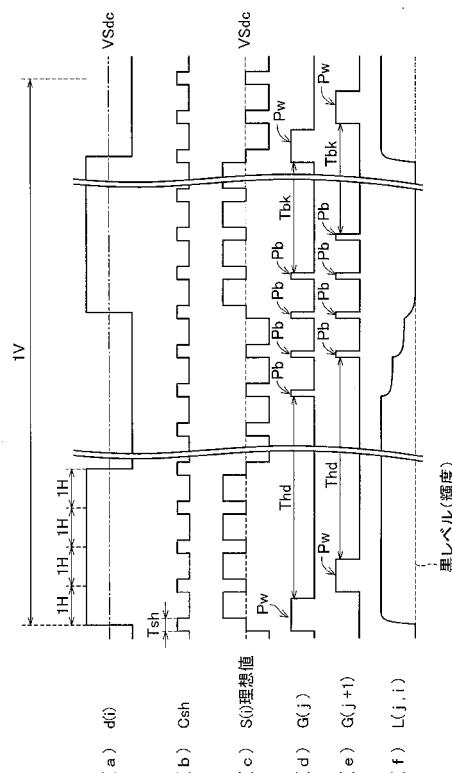

【図48】第2の実施の形態の液晶表示装置における各信号の波形図である。(a)はアナログ電圧信号を示す波形図であり、(b)はチャージシェア制御信号を示す波形図であり、(c)はデータ信号を示す波形図であり、(d)はゲートラインGLjに印加される走査信号G(j)を示す波形図であり、(e)はゲートラインGj+1に印加される走査信号G(j+1)を示す波形図であり、(f)は画素の輝度を示す波形図である。

【図49(a)】2Hドット反転を模式的に示す図である。

【図49(b)】2Hライン反転を模式的に示す図である。

【図49(c)】4Hドット反転を模式的に示す図である。

【図50】第2の実施の形態の液晶表示装置における各信号の波形図の他の例である。(50)

a ) はアナログ電圧信号を示す波形図であり、( b ) はチャージシェア制御信号を示す波形図であり、( c ) はデータ信号を示す波形図であり、( d ) はゲートライン  $G_{Lj}$  に印加される走査信号  $G(j)$  を示す波形図であり、( e ) はゲートライン  $G_{j+1}$  に印加される走査信号  $G(j+1)$  を示す波形図であり、( f ) は画素の輝度を示す波形図である。

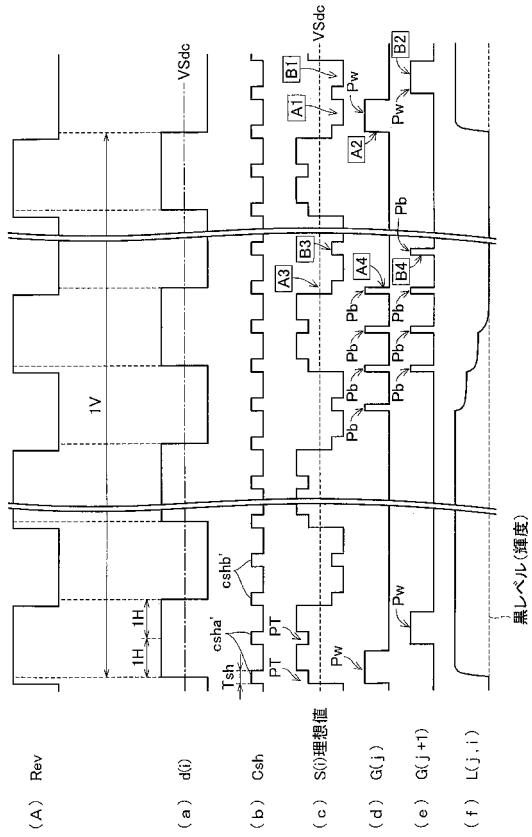

【図 5 1】第 2 の実施の形態の液晶表示装置における各信号の波形図のさらに他の例である。( A ) は、リバース信号  $REV$  を示す波形図であり、( a ) はアナログ電圧信号を示す波形図であり、( b ) はチャージシェア制御信号を示す波形図であり、( c ) はデータ信号を示す波形図であり、( d ) はゲートライン  $G_{Lj}$  に印加される走査信号  $G(j)$  を示す波形図であり、( e ) はゲートライン  $G_{j+1}$  に印加される走査信号  $G(j+1)$  を示す波形図であり、( f ) は画素の輝度を示す波形図である。

【図 5 2】図 5 1 に示す信号を出力するソースドライバの出力部の構成の一例を示す回路図である。

【図 5 3】第 2 の実施の形態の液晶表示装置の一例を、その表示部の等価回路と共に示すブロック図である。

【図 5 4】図 5 3 に示すソースドライバの構成を示すブロック図である。

【図 5 5】第 2 の実施の形態の液晶表示装置における各信号の波形図のさらに他の例である。( A ) は、リバース信号  $REV$  を示す波形図であり、( a ) はゲートスタートパルス信号  $GSP$  を示す波形図であり、( b ) はゲートクロック信号を示す波形図であり、( c ) はチャージシェア制御信号を示す波形図であり、( d ) は同じくチャージシェア制御信号を示す波形図であり、( e ) はアナログ電圧信号を示す波形図であり、( f ) はデータ信号を示す波形図であり、( g ) は同じくデータ信号を示す波形図である。

【図 5 6】図 5 5 に示す信号を出力するソースドライバの出力部の構成の一例を示す回路図である。

【図 5 7 ( a )】実施の形態 2 において、非画像信号の極性を後のデータ信号の極性と同じにした場合と異ならせた場合のデータ信号の波形をそれぞれ示す波形図である。

【図 5 7 ( b )】実施の形態 2 において、非画像信号の極性を後のデータ信号の極性と同じにした場合と異ならせた場合のデータ信号の波形をそれぞれ示す波形図である。

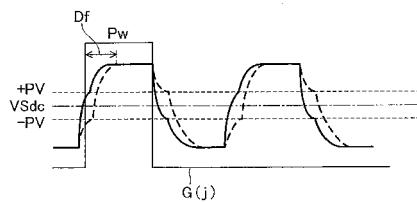

【図 5 7 ( c )】図 5 7 ( a ) および図 5 7 ( b ) の場合の実際の波形を示す波形図であり、実線が図 5 7 ( a ) の場合の実際の波形、破線が図 5 7 ( b ) の場合の実際の波形である。

【図 5 8 ( a )】実施の形態 1 において、非画像信号の極性を後のデータ信号の極性と同じにした場合と異ならせた場合のデータ信号の波形をそれぞれ示す波形図である。

【図 5 8 ( b )】実施の形態 1 において、非画像信号の極性を後のデータ信号の極性と同じにした場合と異ならせた場合のデータ信号の波形をそれぞれ示す波形図である。

【図 5 8 ( c )】図 5 8 ( a ) および図 5 8 ( b ) の場合の実際の波形を示す波形図であり、実線が図 5 8 ( a ) の場合の実際の波形、破線が図 5 8 ( b ) の場合の実際の波形である。

【図 5 9】従来技術を説明するための図であり、尾引残像を示す図である。

【符号の説明】

【0133】

|           |                        |

|-----------|------------------------|

| 3         | ソースドライバ(駆動回路)          |

| 5         | 画素形成部                  |

| 20        | 液晶分子                   |

| 35        | チャージシェア電圧固定用電源(固定電圧電源) |

| 51        | 極性情報処理部(極性情報検知手段)      |

| 53        | 補正量演算部(補正量演算手段)        |

| 54        | LUT(ルックアップテーブル)        |

| 82a ~ 82h | 蛍光ランプ(バックライト)          |

| 99        | チューナー部                 |

10

20

30

40

50

|                   |                   |    |

|-------------------|-------------------|----|

| 1 0 0             | 第 1 の極性反転電源       |    |

| 1 0 3             | 第 2 の極性反転電源       |    |

| 1 1 3             | 第 3 の極性反転電源       |    |

| 1 0 8             | 定電圧ダイオード          |    |

| 2 0 0             | 表示装置 ( 液晶表示装置 )   |    |

| D v               | 映像信号              |    |

| E s h p           | 固定電圧              |    |

| S L 1 ~ S L n     | ソースライン ( データ信号線 ) |    |

| G L 1 ~ G L m     | ゲートライン ( 走査信号線 )  |    |

| S ( 1 ) ~ S ( n ) | データ信号             | 10 |

| G S P             | ゲートスタートパルス信号      |    |

| G C K             | ゲートクロック信号         |    |

【発明を実施するための最良の形態】

【 0 1 3 4 】

〔実施の形態 1 〕

本発明の一実施の形態について、図面を用いて説明する。

【 0 1 3 5 】

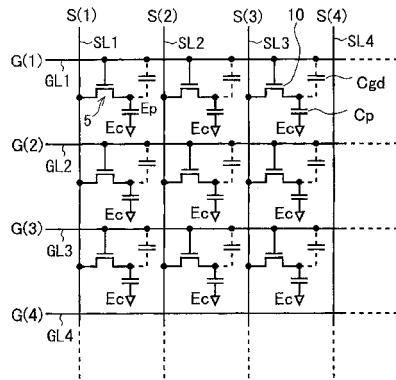

図 2 は、本実施の形態の液晶表示装置を、その表示部の等価回路と共に示すブロック図である。液晶表示装置は、同図に示すように、データ信号線駆動回路としてのソースドライバ ( 駆動回路 ) 3 と、走査信号線駆動回路としてのゲートドライバ 4 と、アクティブマトリクス型の表示部 1 と、ソースドライバ 3 およびゲートドライバ 4 を制御するための表示制御回路 2 と、を備えている。 20

【 0 1 3 6 】

表示部 1 は、複数本 ( m 本 ) の走査信号線としてのゲートライン G L 1 ~ G L m と、これらのゲートライン G L 1 ~ G L m のそれぞれと直交する複数本 ( n 本 ) のデータ信号線としてのソースライン S L 1 ~ S L n と、これらのゲートライン G L 1 ~ G L m とソースライン S L 1 ~ S L n との交差点にそれぞれ対応して設けられた複数個 ( m × n 個 ) の画素形成部 5 と、を含んでいる。

【 0 1 3 7 】

画素形成部 5 は、マトリクス状に配置されて、画素アレイを構成し、各画素形成部 5 は、対応する交差点を通過するゲートライン G L j にゲート端子が接続されると共に、当該交差点を通過するソースライン S L i にソース端子が接続されたスイッチング素子である TFT 1 0 と、当該 TFT 1 0 のドレイン端子に接続された画素電極 E p と、上記複数の画素形成部 5 に共通的に設けられた対向電極である共通電極 E c と、これら画素電極 E p と共に通電極 E c との間に挟持された液晶層と、からなる。 30

【 0 1 3 8 】

画素電極 E p と共に通電極 E c とにより形成される液晶容量により画素容量 C p が構成される。なお、画素容量 C p に確実に電圧を保持すべく、液晶容量 ( 画素容量 C p ) に並列に補助容量を設けてよい。但し、当該補助容量は、本発明には直接に関係しないので、その説明および図示を省略する。 40

【 0 1 3 9 】

画素電極 E p には、後述するように、動作するソースドライバ 3 およびゲートドライバ 4 により、表示すべき画像に応じた電位が与えられる一方、共通電極 E c には、図示しない電源回路から所定電位 V c o m が与えられる。これにより、画素電極 E p と共に通電極 E c との間の電位差に応じた電圧が液晶層に印加され、この電圧印加によって液晶層に対する光の透過量が制御されることで画像表示が行われる。ただし、液晶層への電圧印加によって光の透過量を制御するためには図示しない偏光板が使用され、本実施の形態の液晶表示装置では、一例として、ノーマリーブラックとなるように偏光板が配置されているものとする。ノーマリーブラックモードの液晶表示装置は、電圧を印加しない状態で黒表示となるため、容易に黒挿入を行うことができ、消費電力も抑えることができる。 50

## 【0140】

表示制御回路2は、図示しない外部の信号源から、表示すべき画像を表すデジタルビデオ信号Dvと、当該デジタルビデオ信号Dvに対応する水平同期信号HSYおよび垂直同期信号VSYと、表示動作を制御するための制御信号Dcと、を受け取る。

## 【0141】

表示制御回路2は、これらの各種信号Dv・HSY・VSY・Dcに基づき、デジタルビデオ信号Dvの表す画像を表示部1に表示させるための信号として、データスタートパルス信号SSPと、データクロック信号SCKと、チャージシェア制御信号Cshと、表示すべき画像を表すデジタル画像信号DA(上記ビデオ信号Dvに相当する信号)と、ゲートスタートパルス信号GSPと、ゲートクロック信号GCKと、ゲートドライバ出力制御信号GOE(GOE1～GOEq)と、を生成し、出力する。

10

## 【0142】

より詳細には、外部の信号源から受け取ったビデオ信号Dvを図示しない内部メモリで必要に応じてタイミング調整等を行った後に、デジタル画像信号DAとして表示制御回路2から出力し、そのデジタル画像信号DAの表す画像の各画素に対応するパルスからなる信号としてデータクロック信号SCKを生成し、水平同期信号HSYに基づき1水平走査期間毎に所定期間だけハイレベル(Hレベル)となる信号としてデータスタートパルス信号SSPを生成し、垂直同期信号VSYに基づき1フレーム期間(1垂直走査期間)毎に所定期間だけHレベルとなる信号としてゲートスタートパルス信号GSPを生成し、水平同期信号HSYに基づきゲートクロック信号GCKを生成し、水平同期信号HSYおよび制御信号Dcに基づき、チャージシェア制御信号Cshおよびゲートドライバ出力制御信号GOEを生成する。

20

## 【0143】

上記のようにして表示制御回路2において生成された信号のうち、デジタル画像信号DAとチャージシェア制御信号Cshとデータスタートパルス信号SSPおよびデータクロック信号SCKとは、ソースドライバ3に入力される一方、ゲートスタートパルス信号GSPおよびゲートクロック信号GCKとゲートドライバ出力制御信号GOEとは、ゲートドライバ4に入力される。

## 【0144】

図3は、上記ソースドライバ3の構成を示すブロック図である。

30

## 【0145】

上記ソースドライバ3は、図3に示すように、データ信号生成部12と該データ信号生成部12の後段に配された出力部13とを備えている。データ信号生成部12は、データスタートパルス信号SSPおよびデータクロック信号SCKに基づき、デジタル画像信号DAから、ソースラインSL1～SLnにそれぞれ対応するアナログ電圧信号d(1)～d(n)を生成する。このデータ信号生成部12の構成は、従来のソースドライバのデータ信号生成部12と同様の構成であるので、これ以上の説明を省略する。

## 【0146】

出力部13は、データ信号生成部12で生成されるアナログ電圧信号d(i)毎に設けられた電圧ホロワからなる複数の出力バッファ31(図4)を含み、これらの出力バッファ31により各アナログ電圧信号d(i)をインピーダンス変換し、データ信号S(i)として出力する(i=1, 2, ..., n)。

40

## 【0147】

ただし、後述のように、チャージシェア制御信号Cshに基づき、チャージシェア期間Tsh(図1(b))において、データ信号S(1)～S(n)のソースラインSL1～SLnへの印加が遮断されると共に、ソースラインSL1～SLnが互いに短絡される。詳細については図4を用いて後述するが、出力部13には、このような動作を実現するためのスイッチ回路と電源が含まれている。

## 【0148】

ソースドライバ3は、デジタル画像信号DAとデータスタートパルス信号SSPおよび

50

データクロック信号 SCK とに基づき、デジタル画像信号 DA の表す画像の各水平走査線における画素値に相当するアナログ電圧としてデータ信号 S(1) ~ S(n) を 1 水平走査期間毎に順次生成し、これらのデータ信号 S(1) ~ S(n) をソースライン SL1 ~ SLn にそれぞれ印加する。

#### 【 0 1 4 9 】

本実施の形態におけるソースドライバ 3 は、液晶層への印加電圧の極性が 1 フレーム期間毎に反転されると共に各フレーム内において 1 ゲートライン毎かつ 1 ソースライン毎にも反転されるようにデータ信号 S(1) ~ S(n) が outputされる駆動方式、すなわち、ドット反転駆動方式が採用されている。ドット反転駆動方式は、換言すれば、1 水平走査期間ごとに極性が反転するとともに、隣接するデータ信号線同士は互いに異なる極性となっている。

10

#### 【 0 1 5 0 】

従って、ソースドライバ 3 は、ソースライン SL1 ~ SLn への印加電圧の極性をソースライン SL1 ~ SLn 毎に反転させ、かつ、各ソースライン SLi に印加されるデータ信号 S(i) の電圧極性を 1 水平走査期間毎に反転させている。ここで、ソースライン SL1 ~ SLn への印加電圧の極性反転の基準となる電位は、データ信号 S(1) ~ S(n) の直流レベル（直流成分に相当する電位）であり、この直流レベルは、一般的には共通電極 Ec の直流レベルとは一致せず、各画素形成部 5 における TFT10 のゲート・ドレイン間の寄生容量 Cgd による引き込み電圧 Vd だけ共通電極 Ec の直流レベルと異なる。

#### 【 0 1 5 1 】

20

ただし、寄生容量 Cgd による引き込み電圧 Vd が液晶の光学的しきい値電圧 Vth に対して十分に小さい場合には、データ信号 S(1) ~ S(n) の直流レベルは共通電極 Ec の直流レベルに等しいとみなせるので、データ信号 S(1) ~ S(n) の極性、すなわち、ソースライン SL1 ~ SLn への印加電圧の極性は、共通電極 Ec の電位（対向電圧）を基準として 1 水平走査期間毎に反転すると考えてもよい。

#### 【 0 1 5 2 】

また、上記のソースドライバ 3 では、消費電力を低減するためにデータ信号 S(1) ~ S(n) の極性反転時に、隣接ソースライン SL1 ~ SLn 間が短絡されるいわゆるチャージシェアリング方式が採用されている。

#### 【 0 1 5 3 】

30

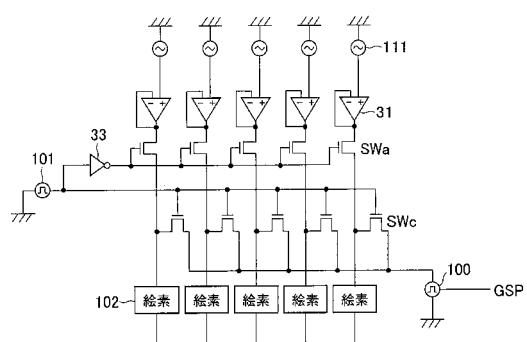

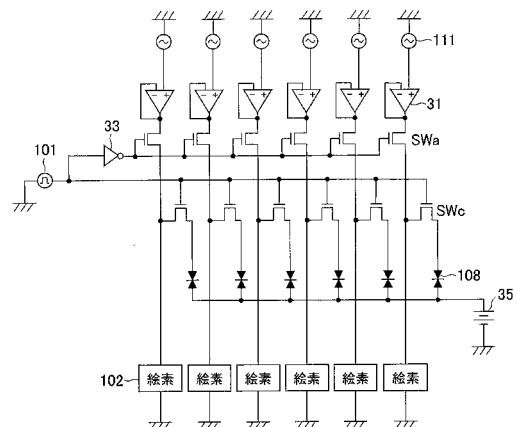

このため、ソースドライバ 3 においてデータ信号 S(1) ~ S(n) を出力する部分である出力部 13 は、図 4 に示すように構成される。すなわち、この出力部 13 は、デジタル画像信号 DA に基づき生成されたアナログ電圧信号 d(1) ~ d(n) を受け取り、これらのアナログ電圧信号 d(1) ~ d(n) をインピーダンス変換することによって、ソースライン SL1 ~ SLn で伝達すべき映像信号としてデータ信号 S(1) ~ S(n) を生成する。この出力部 13 は、図 4 に示すように、このインピーダンス変換のための電圧ホロワとして n 個の出力バッファ 31 を有している。さらに、同図に示すように、各出力バッファ 31 の出力端子には、スイッチング素子としての第 1 の MOS トランジスタ SWa が接続され、各出力バッファ 31 からのデータ信号 S(i) は、第 1 の MOS トランジスタ SWa を介してソースドライバ 3 の出力端子から出力される (i = 1, 2, ..., n)。

40

#### 【 0 1 5 4 】

また、ソースドライバ 3 の隣接する出力端子間は、スイッチング素子としての第 2 の MOS トランジスタ SWb によって接続されている。つまり、これにより、隣接ソースライン SL1 ~ SLn 間が第 2 の MOS トランジスタ SWb によって接続されることになる。そして、これらの出力端子間の第 2 の MOS トランジスタ SWb のゲート端子には、チャージシェア制御信号 Csh が与えられ、各出力バッファ 31 の出力端子に接続された第 1 の MOS トランジスタ SWa のゲート端子には、インバータ 33 の出力信号すなわちチャージシェア制御信号 Csh の論理反転信号が与えられる。

#### 【 0 1 5 5 】

50

したがって、チャージシェア制御信号 Csh が非アクティブ（ローレベル）のときには、第1のMOSトランジスタ SWa がオンし（導通状態となり）、第2のMOSトランジスタ SWb がオフする（遮断状態となる）ので、各出力バッファ31からのデータ信号は、第1のMOSトランジスタ SWa を介してソースドライバ3から出力される。

【0156】

一方、チャージシェア制御信号 Csh がアクティブ（ハイレベル）のときには、第1のMOSトランジスタ SWa がオフし（遮断状態となり）、第2のMOSトランジスタ SWb がオンする（導通状態となる）ので、各出力バッファ31からのデータ信号は、出力されず（すなわちデータ信号 S(1) ~ S(n) のソースライン SL1 ~ SLn への印加は遮断され）、表示部1における隣接ソースライン SL1 ~ SLn が、第2のMOSトランジスタ SWb を介して短絡される。

10

【0157】

ソースドライバ3のデータ信号生成部12では、図1(a)に示すように、1水平走査期間(1H)毎に極性の反転する映像信号としてアナログ電圧信号 d(i) が生成される。一方、表示制御回路2では、図1(b)に示すように、各アナログ電圧信号 d(i) の極性の反転時に所定期間(1水平プランキング期間程度の短い期間；チャージシェア期間) Tsh だけハイレベル(Hレベル)となるチャージシェア制御信号 Csh が生成される。

【0158】

上記のように、チャージシェア制御信号 Csh がローレベル(Lレベル)のときには、各アナログ電圧信号 d(i) がデータ信号 S(i) として出力され、チャージシェア制御信号 Csh がハイレベル(Hレベル)のときには、データ信号 S(1) ~ S(n) のソースライン SL1 ~ SLn への印加が遮断されると共に、隣接ソースライン SL1 ~ SLn が互いに短絡される。

20

【0159】

そして、ドット反転駆動方式が採用されていることから、隣接ソースライン SL1 ~ SLn の電圧は、互いに逆極性であって、しかも、その絶対値はほぼ等しい。従って、各データ信号 S(i) の値、すなわち、各ソースライン SLi の電圧は、チャージシェア期間 Tsh において、黒表示に相当する電圧(黒電圧)となる。

【0160】

30

本実施の形態の液晶表示装置では、各データ信号 S(i) は、データ信号 S(i) の直流レベル VSdc を基準として極性が反転するので、図1(c)に示すように、チャージシェア期間 Tsh においてデータ信号 S(i) の直流レベル VSdc にほぼ等しくなる。

【0161】

なお、このようにデータ信号 S(1) ~ S(n) の極性反転時に隣接ソースライン SL1 ~ SLn を短絡することで各ソースライン SLi の電圧を黒電圧(データ信号 S(i) の直流レベル VSdc )に等しくするという構成は、消費電力を低減するための手段として従来提案されており、図4に示した構成に限定されるものではない。

【0162】

ゲートドライバ4は、ゲートスタートパルス信号 GSP およびゲートクロック信号 GCK と、ゲートドライバ出力制御信号 GOEr (r = 1, 2, ..., q) とに基づき、各データ信号 S(1) ~ S(n) を各画素形成部5(の画素容量)に書き込むために、デジタル画像信号 DA の各フレーム期間(各垂直走査期間)においてゲートライン GL1 ~ GLm をほぼ1水平走査期間ずつ順次選択すると共に、後述の黒挿入のために、上記したデータ信号 S(i) の極性反転時に所定期間だけゲートライン GLj を選択する(j = 1 ~ m)。

40

【0163】

すなわち、ゲートドライバ4は、図1(d)(e)に示すような画素データ書込パルス Pw と黒電圧印加パルス(非画像信号を印加するパルス) Pb とを含む走査信号 G(1) ~ G(m) をゲートライン GL1 ~ GLm にそれぞれ印加し、これらの画素データ書込パ

50

ルス P w・黒電圧印加パルス P b が印加されているゲートライン G L j は選択状態となり、選択状態のゲートライン G L j に接続された TFT 10 がオン状態となる一方、非選択状態のゲートライン G L j に接続された TFT 10 はオフ状態となる。

#### 【0164】

ここで、画素データ書き込みパルス P w は、水平走査期間 (1 H) のうち表示期間に相当する有効走査期間で H レベルとなるのに対し、黒電圧印加パルス P b は、水平走査期間 (1 H) のうちブランкиング期間 (表示期間以外の期間) に相当するチャージシェア期間 T sh 内で H レベルとなる。

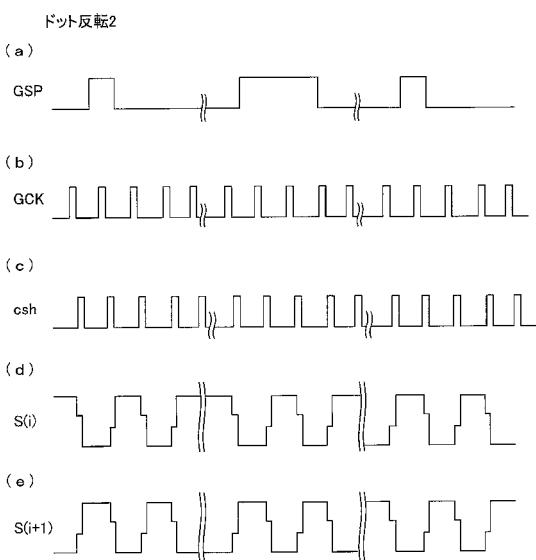

#### 【0165】

図 1 (d) (e) に示すように、各走査信号 G (j) において、画素データ書き込みパルス P w と、当該画素データ書き込みパルス P w の後に最初に現れる黒電圧印加パルス P b と、の間は、2/3 フレーム期間 (2/3 V; Thd) であり、黒電圧印加パルス P b は、1 フレーム期間 (1 V) において、1 水平走査期間 (1 H) の間隔で続いている。

#### 【0166】

黒電圧印加パルス P b の幅は、1.0 μ秒から 2.0 μ秒が好ましく、1.2 μ秒から 1.8 μ秒がより好ましい。非画像信号をデータ信号線に印加する期間の幅 (図 1 では T sh) は、黒電圧印加パルス P b の幅の 2~3 倍程度であることが望ましい。すなわち、T sh の幅は、2~6 μ秒であることが好ましく、3~5 μ秒であることがより好ましい。

#### 【0167】

また、データ信号線への非画像信号の印加時間 (すなわち、P b の幅) は、データ信号線への画像信号の印加時間 (すなわち、P w の幅) よりも短いことが好ましい。これは、画像信号の画素への充電率を確保するためである。非画像信号の画素への充電率に関しては、黒電圧印加パルス P b の本数を増やすことで確保することができる。表 1 には、Full HD (1080 × 1920 × RGB ドット) 機種で確認した最適な画像信号および非画像信号の印加時間を示す。表 1 には、データ信号線または走査信号線への各印加時間を示す。

#### 【0168】

##### 【表 1】

| 機種        | Pbの幅  | 画像信号   | 非画像信号 | Pbの本数 |

|-----------|-------|--------|-------|-------|

| 37型FullHD | 1.2μ秒 | 11.2μ秒 | 3.6μ秒 | 4本    |

| 46型FullHD | 1.6μ秒 | 10.8μ秒 | 4.0μ秒 | 4本    |

| 52型FullHD | 1.8μ秒 | 10.6μ秒 | 4.2μ秒 | 4本    |

#### 【0169】

なお、本発明は必ずしもこれに限定はされず、液晶表示素子の精細度や画面サイズなどで適した値が異なるので、適宜条件出しするのが望ましい。

#### 【0170】

黒電圧印加パルス P b の個数は、実施したい黒挿入レベルに応じて適宜選択可能であるが、2 個から 8 個程度が適当である。より好ましくは 3 個から 6 個がよい。また黒電圧印加パルス P b を印加するタイミングは、データ信号の極性が + (正) から - (負) に変わったタイミングと - から + に変わったタイミングがあり、これらがどちらかに偏るとフリッカーや走査線毎のムラが生じる場合がある。1 フレーム毎にデータ信号の極性を反転し駆動することや、Thd、Tbk を微調整することで、上記不具合を抑制することができる。そこで、黒電圧印加パルス P b を偶数個 (たとえば 4 本) にすることで、隣接する走査線

10

20

30

40

50

ごとに + - - + のタイミングの黒電圧印加パルス P b の本数が等しくなるようにしてもよい。

#### 【0171】

次に、図1を参照しつつ、上記ソースドライバ3およびゲートドライバ4による表示部1(図1参照)の駆動について説明する。表示部1における各画素形成部5では、それに含まれるTFT10のゲート端子に接続されるゲートラインGLjに画素データ書き込パルスPwが印加されることにより、当該TFT10がオンされ、当該TFT10のソース端子に接続されるソースラインSLiの電圧がデータ信号S(i)の値として当該画素形成部5に書き込まれる。すなわち、ソースラインSLiの電圧が、画素容量Cpに保持される。その後、当該ゲートラインGLjは、黒電圧印加パルスPbが現れるまでの期間(非選択状態の期間；画素データ保持期間)Thdは非選択状態となるので、当該画素形成部5に書き込まれた電圧がそのまま保持される。

#### 【0172】

黒電圧印加パルスPbは、画素データ保持期間Thdの後のチャージシェア期間Tshに、ゲートラインGLjに印加される。既述のようにチャージシェア期間Tshでは、各データ信号S(i)の値すなわち各ソースラインSLiの電圧は、データ信号S(i)の直流レベルにほぼ等しくなる。すなわち、各ソースラインSLiの電圧は、黒電圧となる。

#### 【0173】

従って、当該ゲートラインGLjへの黒電圧印加パルスPbの印加により、該画素形成部5の画素容量Cpに保持される電圧は、黒電圧に向かって変化する。しかし、黒電圧印加パルスPbを印加するタイミングは、データ信号S(i)の極性反転時であるため、黒電圧印加パルスPbのパルス幅は短い。そのため、画素容量Cpにおける保持電圧を確実に黒電圧にするために、図1(d)(e)に示すように、各フレーム期間において1水平走査期間(1H)間隔で3個の黒電圧印加パルスPbが続けて当該ゲートラインGLjに印加される。これにより、当該ゲートラインGLjに接続される画素形成部5によって形成される画素の輝度(画素容量での保持電圧によって決まる透過光量)L(j,i)は、図1(f)に示すように変化する。

#### 【0174】

そのため、各ゲートラインGLjに接続される画素形成部5に対応する1表示ラインにおいて、画素データ保持期間Thdではデジタル画像信号DAに基づく表示が行われ、その後に上記3個の黒電圧印加パルスPbが印加されてから次に当該ゲートラインGLjに画素データ書き込パルスPwが印加される時点までの期間Tbkでは黒表示が行われる。このようにして、黒表示の行われる期間(黒表示期間)Tbkが各フレーム期間に挿入されることにより、液晶表示装置による表示のインパルス化が行われる。

#### 【0175】

図1(d)(e)からもわかるように、画素データ書き込パルスPwの現れる時点は、走査信号G(j)毎に1水平走査期間(1H)ずつ、ずれているので、黒電圧印加パルスPbの現れる時点も走査信号G(j)毎に1水平走査期間(1H)ずつずれている。従って、黒表示期間Tbkも1表示ライン毎に1水平走査期間(1H)ずつずれて全ての表示ラインにつき同じ長さの黒挿入が行われる。

#### 【0176】

このようにして、画素データ書き込のための画素容量Cpでの充電期間を短縮することなく、十分な黒挿入期間(非画像挿入期間)が確保される。また、黒挿入(非画像挿入)のためにソースドライバ3などの動作速度を上げる必要もない。

#### 【0177】

次に、本実施形態におけるゲートドライバ4の構成などについて、さらに詳細に説明する。図5(a)は、上記した図1(d)(e)の波形を示すように動作するゲートドライバ4の構成を示すブロック図である。このゲートドライバ4は、図5(a)に示すように、シフトレジスタ40(図5(b))を含む複数個(q個)の部分回路としてのゲートド

10

20

30

40

50

ライバ用 I C ( Integrated Circuit ) チップ 4 1 1 , 4 1 2 , … , 4 1 q からなる。各ゲートドライバ用 I C チップ 4 1 1 , 4 1 2 , … , 4 1 q は、図 5 ( b ) に示すように、シフトレジスタ 4 0 と、当該シフトレジスタ 4 0 の各段に対応して設けられた第 1 および第 2 の AND ゲート 4 2 ～ 4 3 と、第 2 の AND ゲート 4 3 の出力信号  $g_1 \sim g_p$  に基づき走査信号  $G_1 \sim G_p$  を出力する出力部 4 5 とを備え、外部からの信号をスタートパルス信号 S P i 、クロック信号 C K 、および出力制御信号 O E として受け取る。

#### 【 0 1 7 8 】

スタートパルス信号 S P i はシフトレジスタ 4 0 の入力端に与えられ、シフトレジスタ 4 0 の出力端からは、後続のゲートドライバ用 I C チップに入力されるべきスタートパルス信号 S P o が出力される。また、それぞれの第 1 の AND ゲート 4 1 にはクロック信号 C K の論理反転信号が入力される一方、それぞれの第 2 の AND ゲート 4 3 には出力制御信号 O E の論理反転信号が入力される。そして、シフトレジスタ 4 0 の各段の出力信号  $Q_k$  ( $k = 1 \sim p$ ) は、当該段に対応する第 1 の AND ゲート 4 1 に入力され、当該第 1 の AND ゲート 4 1 の出力信号は当該段に対応する第 2 の AND ゲート 4 3 に入力される。

10

#### 【 0 1 7 9 】

また、ゲートドライバ 4 は、図 5 ( a ) に示すように、上記構成の複数 ( q 個 ) のゲートドライバ用 I C チップ 4 1 1 ～ 4 1 q が継続接続されて構成されている。すなわち、ゲートドライバ用 I C チップ 4 1 1 ～ 4 1 q 内のシフトレジスタ 4 0 が 1 つのシフトレジスタを形成するように ( 以下、このように継続接続によって形成されるシフトレジスタを「結合シフトレジスタ」という ) 、各ゲートドライバ用 I C チップ 4 1 1 ～ 4 1 q 内のシフトレジスタの出力端 ( スタートパルス信号 S P o の出力端子 ) が次のゲートドライバ用 I C チップ 4 1 1 ～ 4 1 q 内のシフトレジスタの入力端 ( スタートパルス信号 S P i の入力端子 ) に接続される。

20

#### 【 0 1 8 0 】

ただし、先頭のゲートドライバ用 I C チップ 4 1 1 内のシフトレジスタの入力端には、表示制御回路 2 からゲートスタートパルス信号 G S P が入力され、最後尾のゲートドライバ用 I C チップ 4 1 q 内のシフトレジスタの出力端は外部と未接続となっている。

#### 【 0 1 8 1 】

また、表示制御回路 2 からのゲートクロック信号 G C K は、各ゲートドライバ用 I C チップ 4 1 1 ～ 4 1 q にクロック信号 C K として共通に入力される。

30

一方、表示制御回路 2 において生成されるゲートドライバ出力制御信号 G O E は第 1 ～ 第 q のゲートドライバ出力制御信号 G O E 1 ～ G O E q からなり、これらのゲートドライバ出力制御信号 G O E 1 ～ G O E q は、ゲートドライバ用 I C チップ 4 1 1 ～ 4 1 q に出力制御信号 O E としてそれぞれ個別に入力される。

#### 【 0 1 8 2 】

次に、図 6 ( a ) ～ ( f ) を用いて、上記ゲートドライバ 4 の動作について説明する。表示制御回路 2 は、図 6 ( a ) に示すように、画素データ書き込みパルス P w に対応する期間  $T_{s p w}$  および 3 個の黒電圧印加パルス P b に対応する期間  $T_{s p b w}$  だけ H レベル ( アクティブ ) となる信号をゲートスタートパルス信号 G S P として生成すると共に、図 6 ( b ) に示すように、1 水平走査期間 ( 1 H ) 每に所定期間だけ H レベルとなるゲートクロック信号 G C K を生成する。このようなゲートスタートパルス信号 G S P およびゲートクロック信号 G C K がゲートドライバ 4 に入力されると、先頭のゲートドライバ用 I C チップ 4 1 1 のシフトレジスタ 4 0 の初段の出力信号  $Q_1$  として、図 6 ( c ) に示すような信号が出力される。この出力信号  $Q_1$  は、各フレーム期間において、画素データ書き込みパルス P w に対応する 1 個のパルス P q w と、3 個の黒電圧印加パルス P b に対応する 1 個のパルス P q b w とを含み、これらの 2 個のパルス P q w と P q b w との間はほぼ画素データ保持期間  $T_{h d}$  だけ離れている。

40

#### 【 0 1 8 3 】

このような 2 個のパルス P q w および P q b w がゲートクロック信号 G C K に従ってゲートドライバ 4 0 0 内の結合シフトレジスタを順次転送されていく。それに応じて結合シ

50

フレジスタの各段から、図6(c)に示すような波形の信号が1水平走査期間(1H)ずつ順次ずれて出力される。

#### 【0184】

また、表示制御回路2は、既述のように、ゲートドライバ4を構成するゲートドライバ用ICチップ411～41qに与えるべきゲートドライバ出力制御信号GOE1～GOEqを生成する。ここで、r番目のゲートドライバ用ICチップ41rに与えるべきゲートドライバ出力制御信号GOErは、当該ゲートドライバ用ICチップ41r内のシフトレジスタ40のいずれかの段から画素データ書込パルスPwに対応するパルスPqwが出力されている期間では、画素データ書込パルスPwの調整のためにゲートクロック信号GCKのパルス近傍の所定期間でHレベルとなることを除きLレベルとなり、それ以外の期間では、ゲートクロック信号GCKがHレベルからLレベルに変化した直後の所定期間Toe(この所定期間Toeはチャージシェア期間Tshに含まれるように設定される)だけLレベルとなることを除きHレベルとなる。

#### 【0185】

例えは、先頭のゲートドライバ用ICチップ411には、図6(d)に示すようなゲートドライバ出力制御信号GOE1が与えられる。なお、画素データ書込パルスPwの調整のためにゲートドライバ出力制御信号GOE1～GOEqに含まれるパルス(これは上記所定期間でHレベルとなることに相当し、以下「書込期間調整パルス」という)は、必要な画素データ書込パルスPwに応じて、ゲートクロック信号GCKの立ち上がりよりも早く立ち上がったり、ゲートクロック信号GCKの立ち下がりよりも遅く立ち下がったりする。

#### 【0186】

また、このような書込期間調整パルスを使用せずに、ゲートクロック信号GCKのパルスだけで画素データ書込パルスPwを調整するようにしてもよい。各ゲートドライバ用ICチップ411r(r=1～q)では、上記のようなシフトレジスタ40各段の出力信号Qk(k=1～p)、ゲートクロック信号GCKおよびゲートドライバ出力制御信号GOErに基づき、第1および第2のANDゲート41・43により、内部走査信号g1～gpが生成され、それらの内部走査信号g1～gpが出力部45でレベル変換されて、ゲートラインに印加すべき走査信号G1～Gpが出力される。

#### 【0187】

これにより、図6(e)(f)に示す走査信号G(1)G(2)から分かるように、ゲートラインGL1・GL2・・・には、順次画素データ書込パルスPwが印加されると共に、各ゲートラインGL1・GL2・・・では、画素データ書込パルスの印加時点から画素データ保持期間Thdだけ経過した時点で、黒電圧印加パルスPbが印加され、その後、1水平走査期間(1H)間隔で2個の黒電圧印加パルスPbが印加される。このようにして3個の黒電圧印加パルスPbが印加された後は、次のフレーム期間の画素データ書込パルスPwが印加されるまでLレベルが維持される。すなわち、上記3個の黒電圧印加パルスPbが印加されてから次の画素データ書込パルスPwが印加されるまでは黒表示期間Tbkとなる。

#### 【0188】

上記のようにして、図5(a)および図5(b)に示した構成のゲートドライバ4により、液晶表示装置において図1(c)～(f)に示したようなインパルス化駆動を実現することができ、同時に液晶プレチルト電圧を与えることができる。

#### 【0189】

ところで、一般に、TFT10を使用したアクティブマトリクス型の液晶表示装置では、図7に示すように、各画素形成部5におけるTFT10のゲート・ドレイン間に寄生容量Cgdが存在する。この寄生容量Cgdの存在により、各画素形成部5における画素電極Epの電圧(画素電圧)Vdは、その画素電極Epに接続されるTFT10がオン状態(導通状態)からオフ状態(遮断状態)へと切り替わる時に、画素容量Cpと寄生容量Cgdとの比に応じて低下する。以下、寄生容量Cgdに起因するこのような画素電圧Vd

の変化をレベルシフトと呼び、この変化量を引き込み電圧と呼び記号  $V_d$  で示すものとする。

#### 【0190】

具体的には、図8(a)(b)に示すように、いずれかのゲートライン  $GL_j$  に印加される走査信号  $G(j)$  の電圧であるゲート電圧  $V_g(j)$  がオン電圧  $V_{gh}$  となって(時刻  $t_1$  または  $t_3$ )、当該ゲートライン  $GL_j$  に接続された TFT10 を介してソースライン  $SL_i$  の電圧  $V_{sn}$  または  $V_{sp}$  が画素電極に与えられた後に、そのゲート電圧  $V_g(j)$  がオフ電圧  $V_{g1}$  へと変化すると(時刻  $t_2$  または  $t_4$ )、画素電圧  $V_d$  は、次の(1)式で表される引き込み電圧  $V_d$  だけ低下する( $j = 1, 2, \dots, m$ ;  $i = 1, 2, \dots, n$ )。

10

#### 【0191】

$$V_d = (V_{gh} - V_{g1}) \cdot C_{gd} / (C_p + C_{gd}) \dots (1)$$

液晶はそれに印加される電圧によって誘電率が変化するので、画素容量  $C_p$  は、画素の階調によって異なる値を持つ。従って、(1)式から、上記引き込み電圧  $V_d$  も画素の階調によって異なる。

#### 【0192】

一般に、液晶表示装置では、液晶への印加電圧の極性が共通電極  $E_c$  の電位すなわち対向電圧を基準として所定周期で反転し、液晶における光の透過率はそれへの印加電圧の実効値に応じて変化する。従って、フリッカの無い表示を得るには、液晶への印加電圧の平均値が0になるように対向電圧に対してソースラインの電圧(ソース電圧)、すなわち、データ信号の値を上記引き込み電圧  $V_d$  だけ補正する必要がある。この引き込み電圧  $V_d$  は、上記のように、画素の階調によって異なる。そこで、全ての階調についてフリッカの無い表示を得るために、ソース電圧は、表示すべき画素の階調に応じて補正される。すなわち、ソース電圧の補正量は表示階調によって異なる。

20

#### 【0193】

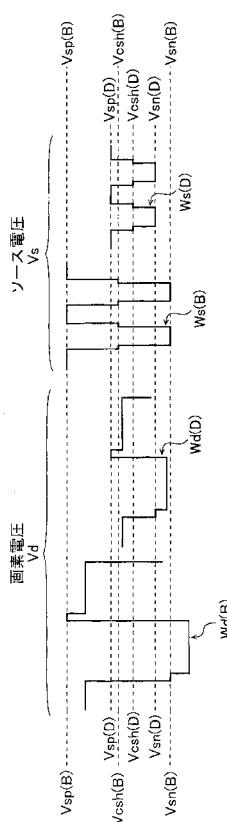

ところで、チャージシェア期間  $T_{sh}$  でのソース電圧(チャージシェア電圧)は、そのチャージシェア期間直前ににおける各ソースドライバの全ソースラインについての電圧の平均値にほぼ等しい。上記のようにソース電圧の補正量が画素の階調によって異なるので、図9を用いて次に示すように、チャージシェア電圧は表示階調によって異なる。

#### 【0194】

30

図9は、輝度の高い画素を表示する場合の画素電圧(高輝度画素電圧)  $V_d(B)$  の電圧波形  $W_d(B)$  と、輝度の低い画素を表示する場合の画素電圧(低輝度画素電圧)  $V_d(D)$  の電圧波形  $W_d(D)$  と、高輝度画素電圧  $V_d(B)$  を与えるためのデータ信号の電圧(高輝度ソース電圧)  $V_s(B)$  の電圧波形  $W_s(B)$  と、低輝度画素電圧  $V_d(D)$  を与えるためのデータ信号の電圧(低輝度ソース電圧)  $V_s(D)$  の電圧波形  $W_s(D)$  と、を示している。

#### 【0195】

ただし、高輝度画素電圧の電圧波形  $W_d(B)$  および低輝度画素電圧の電圧波形  $W_d(D)$  と、高輝度ソース電圧の電圧波形  $W_s(B)$  および低輝度ソース電圧の電圧波形  $W_s(D)$  とでは、時間軸(横軸)のスケールは、一致しているわけではない。なお、図9において、 $V_{sp}(B)$  は高輝度ソース電圧  $V_s(B)$  の最大値を、 $V_{sn}(B)$  は高輝度ソース電圧  $V_s(B)$  の最小値をそれぞれ示し、 $V_{sp}(D)$  は低輝度ソース電圧  $V_s(D)$  の最大値を、 $V_{sn}(D)$  は低輝度ソース電圧  $V_s(D)$  の最小値をそれぞれ示している。

40

#### 【0196】

また、 $V_{chs}(B)$  は、高輝度ソース電圧  $V_s(B)$  がソースラインに与えられた場合のチャージシェア電圧を、 $V_{chs}(D)$  は、低輝度ソース電圧  $V_s(D)$  がソースラインに与えられた場合のチャージシェア電圧をそれぞれ示している。図9からわかるように、高輝度画素電圧  $V_d(B)$  と低輝度画素電圧  $V_d(D)$  とで引き込み電圧  $V_d$  が異なる。そして、上記した通り、引き込み電圧  $V_d$  分だけ、ソース電圧の値を補正するた

50

め、高輝度ソース電圧  $V_{S(B)}$  と低輝度ソース電圧  $V_{S(D)}$  とで補正量が異なる。

【0197】

従って、ソースラインに高輝度ソース電圧  $V_{S(B)}$  が与えられる場合のチャージシェア電圧  $V_{CSH(B)}$  と低輝度ソース電圧  $V_{S(D)}$  が与えられる場合のチャージシェア電圧  $V_{CSH(D)}$  とは、互いに異なっている。すなわち、表示階調によってチャージシェア電圧  $V_{CSH}$  が異なる。

【0198】

本実施の形態の液晶表示装置では、図1に示したように、チャージシェア期間  $T_{sh}$  のソース電圧であるチャージシェア電圧(図1(a)(c))に示されている電圧  $V_{Sdc}$  が黒表示に相当する電圧となることから、チャージシェア期間  $T_{sh}$  でHレベルとなる黒電圧印加パルス  $P_b$  をゲートライン  $GL_j$  に印加することで黒挿入を行い( $j = 1 \sim m$ )、これにより表示をインパルス化している。

10

【0199】

ここで、黒電圧印加パルス  $P_b$  のパルス幅が短いことから、黒電圧の書き込み不足を補うべく複数のチャージシェア期間  $T_{sh}$  (図1(e)(f))に示した例では3つのチャージシェア期間  $T_{sh}$  で黒挿入を行っている。ところで、チャージシェア電圧  $V_{CSH}$  は、黒表示に相当する電圧であっても、上記のようにソース電圧の値が補正されることから、表示階調によって異なる(図8参照)。

【0200】

以上のようにチャージシェア電圧  $V_{CSH}$  が表示階調によって異なるため、表示パターンによっては、当該パターンの影が視認される場合がある。例えば、図10に示すように、液晶表示装置の画面において本来の表示パターン  $D_{pat}$  の下方に、黒電圧としてのチャージシェア電圧  $V_{CSH}$  の書き込みに基づき表示パターン  $D_{pat}$  に相当する影のパターン  $S_{pat}$  が現れ、これが表示パターン  $D_{pat}$  の影として視認されることがある。

20

【0201】

これに対して、黒信号挿入期間において、各ソースライン  $SL_i$  に黒表示に相当する固定電圧を与えることが好ましい。各ソースライン  $SL_i$  に黒表示に相当する固定電圧を与えるれば、各画素形成部5内の寄生容量  $C_{gd}$  に基づく引き込み電圧の階調依存性を補償するためにデータ信号の補正量が表示階調によって異なっても、黒信号挿入期間における各ソースライン  $SL_i$  の電圧が常に同一の電圧となるため、パターンの影が視認されるという、問題を改善することができる。

30

【0202】

このような固定電圧を各ソースライン  $SL_i$  に与えるソースドライバ3の出力部13の具体的な構成について図面を用いて説明する。つまり、ソースドライバ3の出力部13の構成は、上記の図4に示した構成に限らず、次に示すような構成でもよい。

【0203】

図11は、ソースドライバの出力部の他の構成を示す回路図である。

【0204】

図11に示す出力部は、 $n$ 個の出力バッファ31と、スイッチング素子としての $n$ 個の第1のMOSトランジスタ  $SW_a$ 、( $n - 1$ )個の第2のMOSトランジスタ  $SW_b$ 、およびインバータ33からなるスイッチ回路と、を含んでおり、この点では、図4に示したソースドライバ3の出力部4の構成と同様である。

40

【0205】

さらに、図11に示す出力部は、上記したソースドライバ3の出力部13と異なり、チャージシェア電圧固定用電源35および第3のMOSトランジスタ  $SW_b$  2を有しており、チャージシェア電圧固定用電源35の正極がスイッチング素子としての第3のMOSトランジスタ  $SW_b$  2を介して、いずれかのソースライン  $SL_i$  に接続されるべきソースドライバ3の出力端子に接続されている(図11に示した例では、 $n$ 番目のソースライン  $SL_n$  に接続されるべき出力端子に接続されている)。

【0206】

50

そして、第3のMOSトランジスタSWb2のゲート端子には、チャージシェア制御信号Cshが入力され、チャージシェア電圧固定用電源35の負極は接地されている。

#### 【0207】

このチャージシェア電圧固定用電源35は、液晶をプレチルトさせる液晶プレチルト電圧に相当する固定電圧Eshpを与える電圧供給部であることが好ましい。

#### 【0208】

なお、この固定電圧Eshpは、チャージシェア期間Tshにおいて黒電圧印加パルスPbにより画素電極に印加されるが（図1参照）、上記のとおり画素電圧が厳密に黒表示に相当する電圧ではない。しかしながら、大部分の階調領域において表示すべき画素の階調に対して、Eshpによる書き込みは低輝度表示（低階調表示）となるため、インパルス効果を得ることが可能である。

10

#### 【0209】

上記の図11に示す出力部によても、上記した図4に示すソースドライバ3の出力部13と同様、チャージシェア制御信号Cshに基づき、チャージシェア期間Tsh以外（の有効走査期間）では、データ信号生成部12で生成されたアナログ電圧信号d(1)～d(n)が出力バッファ31を介してデータ信号S(1)～S(n)として出力されてソースラインSL1～SLnに印加され、チャージシェア期間Tshでは、データ信号S(1)～S(n)のソースラインSL1～SLnへの印加が遮断されると共に隣接するソースラインSL1～SLnが互いに短絡される。結果的に、全ソースラインSL1～SLnが互いに短絡される。

20

#### 【0210】

これに加えて、図11に示す構成によれば、チャージシェア期間Tshにおいて各ソースラインSLi(i=1～n)にチャージシェア電圧固定用電源35の電圧Eshpが与えられる。このため、引き込み電圧Vdの階調依存性を補償するためにソース電圧の補正量が表示階調によって異なっても、黒信号挿入期間としてのチャージシェア期間Tshにおいてチャージシェア電圧を常に同一の電圧Eshpとすることができます。これにより、図10に示したようなパターンの影の発生を抑制することができる。

#### 【0211】

さらに、固定電圧Eshpとして液晶をプレチルトさせる液晶プレチルト電圧を与えることで、次フレームに高輝度画素電圧を書き込む場合や、オーバーシュート駆動を行う場合など、黒表示に相当するような低輝度画素電位に電位差の大きな電圧を印加するときの液晶の応答速度低下を改善することができる（詳細については後述）。

30

#### 【0212】

しかし、図11に示す構成例では、多くのソースラインは複数個のMOSトランジスタSWbを介してチャージシェア電圧固定用電源35に接続されている。このため、全てのソースラインSL1～SLnの電圧が同一のチャージシェア電圧Eshに落ち着くまでにある程度の時間を要する。その結果、チャージシェア期間Tshの長さによっては、黒挿入において各画素形成部5の画素容量に保持されるべき黒電圧を同一にすることはできず、上記パターンの影の発生を十分に抑制できないことも考えられる。

#### 【0213】

40

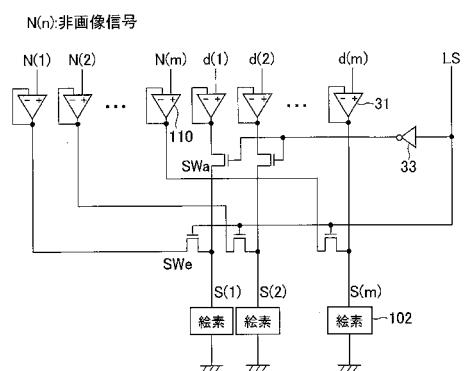

これに対して、チャージシェア期間Tshにおいて全てのソースラインSL1～SLnが短時間で同一の電圧Eshとなるように構成されたソースドライバ3の出力部の構成例について図12を用いて説明する。

#### 【0214】

図12は、上記したソースドライバ3の出力部13のさらに他の出力部の構成を示す回路図である。同図に示す出力部13における構成要素のうち、図11に示す構成要素と同一の構成要素については、同一の参照符号を付して説明を省略する。図12に示す出力部も、図11に示す出力部の構成と同様、各ソースラインSLi(i=1～n)に対しスイッチング素子としての第2のMOSトランジスタSWcが1個ずつ設けられている。しかし、図11に示す出力部13の構成では、隣接ソースラインSL1～SLn間に1個ずつ

50

第2のMOSトランジスタSWbが挿入されるようにスイッチ回路が構成されるのに対し、図12に示す構成では、各ソースラインSLiとチャージシェア電圧固定用電源35との間に1個ずつ第2のMOSトランジスタSWcが挿入されるようにスイッチ回路が構成されている。すなわち図12に示す構成では、各ソースラインSLiに接続されるべきソースドライバの出力端子は、これら第2のMOSトランジスタSWcのいずれか1つを介してチャージシェア電圧固定用電源35の正極に接続されている。

そして、これら第2のMOSトランジスタSWcのゲート端子のいずれにもチャージシェア制御信号Cshが与えられる。

#### 【0215】

上記のような図12に示す構成によっても、図11に示す構成や図4に示す構成におけるソースドライバ3の出力部と同様、チャージシェア制御信号Cshに基づき、チャージシェア期間Tsh以外（の有効走査期間）では、データ信号生成部12で生成されたアナログ電圧信号d(1)～d(n)が出力バッファ31を介してデータ信号S(1)～S(n)として出力されてソースラインSL1～SLnに印加され、チャージシェア期間Tshでは、データ信号S(1)～S(n)のソースラインSL1～SLnへの印加が遮断されると共に隣接ソースラインが互いに短絡される（結果的に全ソースラインSL1～SLnが互いに短絡される）。

#### 【0216】

これに加えて、この図12に示す構成によれば、チャージシェア期間Tshにおいて各ソースラインSLi(i=1～n)にチャージシェア電圧固定用電源35の電圧Eshが与えられる。このため、引き込み電圧Vdの階調依存性を補償するためにソース電圧の補正量が表示階調によって異なっても、黒信号挿入期間としてのチャージシェア期間Tshにおいてチャージシェア電圧を常に同一の電圧Eshとすることができる。しかも、チャージシェア期間Tshにおいて各ソースラインSLi(i=1～n)には、1つのMOSトランジスタSWcのみを介してチャージシェア電圧固定用電源35の電圧Eshpが与えられる。したがって、黒信号挿入期間としてのチャージシェア期間Tshにおいて各ソースラインSLiの電圧を短時間で同一の電圧Eshにすることができ、これにより、図10に示したようなパターンの影の発生を確実に抑制することができる。

#### 【0217】

次に、図11および図12に示す、チャージシェア電圧固定用電源35の電圧Eshpの好適な値について説明する。

#### 【0218】

電圧印加に対する液晶分子の挙動としては、液晶表示装置では上下基板間に電圧を印加することにより、誘電率異方性をもつ液晶分子の配向方向が制御される。垂直配向モード（VAモード）において、上下基板間にかかる電圧が低い場合（本実施の形態のようにチャージシェア電位を用いて黒書き込みをする場合）、図13（a）に示すように液晶分子20は、垂直配向状態となり、この垂直配向状態から上下基板間に高電圧を印加すると、図13（b）に示すように、液晶分子20が倒れて水平配向状態となる。

#### 【0219】

但し、液晶分子20に対してかかる電圧が低いほど、つまり、液晶分子20が垂直配向に近いほど、この垂直配向状態から高電圧を印加して液晶分子を転倒させると、図14に示すように、液晶分子20の基板に対する垂直軸21からの傾斜角は制御できるが、液晶分子20が転倒する方向（水平方位角方向）までは制御することができず、図15に示すように、いずれの方向に転倒するかわからないという問題がある。

#### 【0220】

すなわち、液晶分子20は、その時にエネルギー的に安定な様々な方向に倒れる。その後、図15中に矢印にて示すように、各液晶分子が正解方向に向かって移動するが、液晶分子20は互いに排除体勢にあるため（つまり互いにすり抜けることができないため）、液晶分子が正解方向に配向されるまで、非常に時間がかかる、という問題が生じる。さらにクロスニコルをなす偏光板の吸収軸方向から45度方向に配向しない液晶分子は透過率

10

20

30

40

50

を低下させる。

【0221】

上記したような問題が生じるのは、主として、ある種の配向状態をもつ、VAモードの液晶表示装置の場合である。つまり、このような液晶表示装置は、図16に示すように、リップ領域、および、電極スリット領域を有している。リップ領域には、同図に示すように、基板と平行な面に対して斜めの傾斜面を持つテーパー部22が配設されており、このテーパー部22に沿って、液晶分子20が傾斜配向するようになっている。一方、電極スリット領域には、同図に示すように、スリット23が設けられており、このスリット23には電極印加時に斜め電界がかかり液晶分子20が傾斜配向し易くなっている。

【0222】

このリップ領域とスリット領域との間のプレチルトが非常に小さい領域に配された液晶分子20は、リップ領域やスリット領域に配された液晶分子20の配向方向にならって傾斜配向しようとするが、リップ領域やスリット領域から離れれば離れるほど、液晶分子20が傾斜しようとする働きが弱く、より垂直配向に近い形となり、上記のように、液晶分子20が正解方向に配向されるまでに時間がかかる。なお、図16では、リップ領域とスリット領域が設けられている構成について説明したが、これに限らず、リップ領域のみの場合やスリット領域のみの場合でもよい。

【0223】

次に、液晶分子の応答駆動について説明する。図17(a)に示すような所望の黒信号の電位V1から点灯状態の電位V2に移行する場合、図17(b)に実線にて示すように、点灯状態の目的の階調(透過率)に比較的早く達する。これに対して、図17(a)に示すような黒信号の電位V1よりも電位が低い黒書き込みの電位V3(図17(a)中的一点鎖線)から点灯状態の電位V2に移行する場合、上記したように、液晶分子20が正解方向に配向されるまで、非常に時間がかかるため、応答速度が遅くなり、図17(b)に一点鎖線にて示すように、目的の階調(目的階調)に達するまでに非常に時間がかかる、という問題がある。

【0224】

次に、この液晶分子20の応答駆動に基づいて、チャージシェアインパルス駆動についての応答拳動について説明する。図18(a)に示すように、所望の黒信号の電位V1よりも低い黒書き込みの電位V3から、点灯状態の電位V2に移行する場合、図18(b)に示すように、黒書き込みと点灯状態とが交互に繰り返され、黒書き込みの電位V3が所望の黒信号の電位V1よりも低いため、点灯状態を表す目的階調にいっこうに達しない。そのため、数フレームにわたる応答破綻となり、尾引きが生じる。

【0225】

これに対して、本実施の形態では、上記した所望の黒信号の電位V1を、液晶分子20をプレチルトさせるための電位とし、より具体的には、次に示すように、階調および/または規格化輝度にて表現している。チャージシェア電圧固定用電源35にて、データ信号S(1)~S(n)の極性反転時にソースラインSL1~SLnに供給されるデータ信号(非画像信号；プレチルト信号)を次のように設定している。

【0226】

図19に示すように、縦軸を規格化輝度とする一方、横軸を階調とする。この場合、上記の非画像信号が、特性2.2、8ビット階調表現(256階調)のうちの、12階調以上であること、および/または、白レベルを100%、黒レベルを0%と規格化した輝度で、0.1%以上であることが好ましい。なお、これらの好ましい値は、本発明者らが、プレチルト信号レベルを変えながら、尾引き残像のレベルを検証し、12階調以上(および/または0.1%以上)に設定すれば、尾引き残像を改善できる。

【0227】

図20(a)および図20(b)は、プレチルト信号を特性2.2、表示階調256階調のうちの、12階調以上に設定した場合についての液晶分子の応答駆動について説明するグラフである。図20(a)に示すように、プレチルト信号を特性2.2、表示階

10

20

30

40

50

調 256 階調のうちの、12 階調以上に設定した電位  $V_3$  にて黒書き込みを行なった場合、図 20 (b) に実線にて示すように、黒書き込みから点灯状態にする度に目的の階調に達するので、つまり、応答破綻が生じない黒書き込み電位  $V_3$  から応答することになるので、尾引き改善がなされる。

## 【0228】

つまり、プレチルト信号を 特性 2.2、表示階調 256 階調のうちの、12 階調以上に設定して黒書き込みを行なうことにより、図 21 に示すように、液晶分子 20 が垂直配向状態からやや傾斜する。そのため、この状態から高電圧を印加すると、液晶分子 20 は、所望の方向 (正解方向) へ転倒する。従って、応答破綻を防止することができる。

## 【0229】

また、上記以外でも、例えば、白輝度レベルを 1 とし、黒輝度レベルを 0 とした場合の表示輝度  $T$  が、表示階調  $L$ 、白表示階調  $L_w$ 、および 特性 に関して、 $T = (L / L_w)^{2.2}$  と略近似できるときに、上記のプレチルト信号を、 $L_w \times 10^{(1/2.2)}$  以上を示す信号としてもよい。さらに、白輝度レベルを 1 とし、黒輝度レベルを 0 とした場合の表示輝度  $T$  を示す表示階調  $L$  を 特性 に関して、 $L = 255 \times T^{(1/2.2)}$  と定義し、上記プレチルト信号を、 $L = 12$  のときの階調電圧より大きい階調電圧を発生する信号としてもよい。これらの場合でも、尾引きを改善することができる。

## 【0230】

なお、本明細書においては、上記のように 2.2 を表式化している。2.2 のカーブは、少なくとも次の 2 種類の波形が挙げられる。

- (i)  $T = (L / 255)^{2.2}$ 、

- (ii)  $T = (L / 255) / 4.5$ 、または、 $(L / 255 + 0.099) / 1.099$

また、プレチルト信号を 特性 2.2、表示階調 256 階調のうちの、12 階調以上に設定して黒書き込みを行なった場合、オーバーシュート駆動 (OS 駆動) を実行する場合にも次のような効果を奏する。OS 駆動は、目的の階調電圧よりも過剰な電圧を印加することによって、応答が遅い階調遷移を補償する技術である。通常、OS 駆動は、開始階調と目的階調とから、適切な OS 量 (階調補正量) を演算して駆動する。すなわち、次式の関数にて演算処理する。

## 【0231】

$$OS\text{ 量} = \text{目的階調} + (\text{開始階調} - \text{目的階調}) ( \quad \text{は関数} )$$

それゆえ、上記したような電圧の印加によって水平方位角方向を制御できない局面の場合、OS 駆動を実行しても、液晶表示装置の応答特性を制御できない。つまり、OS 駆動を実行する際に、電圧あるいは階調で制御できない成分を考慮しなければならず、特別な補正アルゴリズムの構築が必要となる。このため、OS 駆動を行なうためには、図 22 に示すように、通常の OS 駆動を行なう液晶表示装置に備えられている前回のデータを記憶しておくフレームメモリ 71 と、制御部 72 と、に加えて、複雑な演算を必要とする補正アルゴリズムを組み込んだ回路規模の大きい、OS 演算部 73 を設ける必要があった。そのため、回路規模が大きくなり、リアルタイムでの演算が困難となるという問題がある。

## 【0232】

これに対して、上記のように、プレチルト信号を 256 階調 (2.2) 中、12 階調以上に設定して黒書き込みを行なった場合、液晶分子の配向を階調 (すなわち電圧) で制御できるため、 $\text{L} = \text{L}_w \times 10^{(1/2.2)}$  は、簡単な近似式、または、ルックアップテーブルにより補正できるため、図 23 に示すように、OS 演算部 73 の駆動回路を比較的小規模のものにすることができる。

## 【0233】

さらに、上記では、プレチルト信号を、特性 2.2、表示階調 256 階調のうちの、12 階調以上を示す信号であるとしたが、これに限定されず、例えば、特性 2.2、表示階調 1024 階調のうちの、45 階調以上を示す信号でもよい。この場合でも上記と同様の効果を得ることができる。

10

20

30

40

50

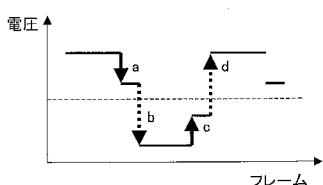

## 【0234】

上記のように、チャージシェア電圧固定用電源35を用いて黒書き込む電位を固定とした場合からのさらなる改善策について説明する。まず、黒書き込みを行なう場合の、理想的な電圧とフレームとの関係について説明する。理想的な電圧とフレームとの関係では、図24に示すように、映像信号を書き込む段階の極性反転する電位差a・cが互いに等しいと共に、黒書き込みする段階の極性反転する電位差b・dが互いに等しくなっている。従って、それぞれの状態で電位差が揃うため、応答速度を高めることができる。また、黒書き込む電位の極性がそれぞれ異なっているため極性に偏りがなく、電気的にオフセットする事なく、信頼性を高めることができる。また、フレームの最後において画素に印加するプレチルト信号の極性は、次のフレームのデータ信号の極性にあわせることができる。こうすることで、画素をプレ充電することができ、画素の充電率向上の観点から有利となる。

## 【0235】

これに対して、上記したように、黒書き込みが固定値の場合、図25に示すように、映像信号を書き込む段階の極性が反転する電位差e・fが互いに異なり、黒書き込みする段階の極性反転する電位差g・hが互いに異なっている。液晶の応答特性は電位差によって変わるため、応答特性が異なり、極性によって輝度が異なってしまう。このため、例えば、ドット反転駆動の場合、市松状の応答むらが生じる。また、黒書き込みが固定値の場合、図25に示すように、画素の極性に偏りが生じる。つまり、黒書き込みの電位が片側極性となり、電気的にオフセットしてしまい、信頼性上の懸念が生じる。

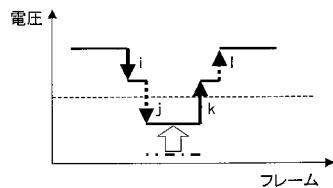

## 【0236】

これに対して、本実施の形態では、図26に示すように、アナログ電圧を調整してプラス極性とマイナス極性での実効値を補正している。これにより、信頼性を向上させることができると共に、焼き付きを防止することができる。また、このアナログ補正と共に、または、アナログ補正の代わりに、表示部1の各画素へ供給する映像信号に極性反転情報に応じた補正を行なうことにより、適切なOS駆動をするデジタル補正を行なってもよい。

## 【0237】

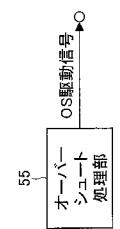

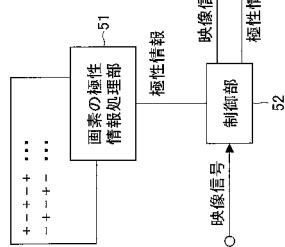

このデジタル補正を行なうためのオーバーシュート駆動回路(OS駆動回路)の構成について、ブロック図を用いて説明する。このOS駆動回路は、表示制御回路2(図2)の前段に配されており、図27に示すように、画素の極性情報処理部(極性情報処理部)51、制御部52、補正量演算部53、ルックアップテーブル(LUT)54、およびオーバーシュート処理部55を備えている。

## 【0238】

極性情報処理部51は、予め設計された例えばドット反転駆動などの反転駆動条件と表示部1(パネル内)の画素の位置情報と、から当該画素が+または-のどちらの極性をとるかの極性情報を検知する。一例として、反転駆動条件がドット反転方式である場合について説明する。画素の極性情報と画素の位置情報である番地を示す(x, y)との関係は、図28に示すように、(x, y)の偶奇が一致する場合には画素の極性情報が+となり、(x, y)の偶奇が異なる場合には画素の極性情報が-となる。つまり、反転駆動条件が決まれば、画素の位置情報から一義的に画素の極性情報を得ることができる。

## 【0239】

制御部52は、外部から映像信号(デジタル画像信号DA;図2)を受け取ると共に、極性情報処理部51から、画素の極性情報(+または-)の情報を受け取る。補正量演算部53は、制御部52から映像信号および極性状態の情報を受け取り、LUT54を参照して、補正值を得る。補正量演算部53は、この補正值を補正映像信号として、次段のオーバーシュート処理部55に送信する。ここで、図29にLUT54の一例を示す。同図に示すように、LUT54には、画素の極性情報および映像信号に対して、補正值が割り当てられている。そのため、例えば、(映像信号, 極性情報) = (5, +)の場合、「8」という補正值を得ることができる。

## 【0240】

10

20

30

40

50

オーバーシュート処理部 55 は、補正量演算部 53 から受け取った今回の補正映像信号と、図示しないフレームメモリに格納しておいた前回の補正映像信号とを互いに比較して、今回の補正映像信号を適切に強調した OS 駆動信号をディスプレイ駆動部である、表示制御回路 2 へ送信する。

【 0 2 4 1 】

なお、OS 駆動回路の各部材の配置は、図 27 に示す配置に限らず、次のような配置でもよい。図 27 では、各部材は、OS 駆動回路の前段から後段に向かって、画素の極性情報処理部 51 および制御部 52 補正量演算部 53 およびルックアップテーブル 54 オーバーシュート駆動部 55 の順で配されている。これに対して、図 30 に示すように、OS 駆動回路の前段から後段に向かって、オーバーシュート駆動部 55 画素の極性情報処理部 51 および制御部 52 補正量演算部 53 およびルックアップテーブル 54 の順に配されていてもよい。つまり、デジタル補正と、オーバーシュート駆動との順序を入れ替えてもよい。

10

【 0 2 4 2 】

この図 30 に示す OS 駆動回路の動作について説明する。なお、すでに説明した事項と同様の事項については適宜その説明を省略する。

【 0 2 4 3 】

オーバーシュート駆動部 55 は、外部から映像信号を受け取り、今回の映像信号と前回の映像信号とを互いに比較して、今回の映像信号を適切に強調した、オーバーシュート補正量としての OS 補正信号を制御部 52 へ送る。この OS 補正信号を受け取った制御部 52 は、極性情報処理部 51 から画素の極性情報 (+ または -) の情報を受け取る。

20

【 0 2 4 4 】

補正量演算部 53 は、制御部 52 から OS 補正信号および極性情報を受け取り、LUT 54 を参照して、階調補正量としての補正值を得る。補正量演算部 53 は、この補正值を補正駆動信号として、ディスプレイ駆動部である、表示制御回路 2 へ送信する。

【 0 2 4 5 】

次に、図 31 に、図 30 に示す LUT 54 の一例を示す。同図に示すように、LUT 54 には、画素の極性情報および OS 補正信号に対して、補正值が割り当てられている。そのため、例えば、(OS 補正信号, 極性情報) = (5, +) の場合、「6」という補正值を得ることができる。

30

【 0 2 4 6 】

以上のようなデジタル補正によって、図 32 に示すような階調の補正を行うことができる。これにより、黒を書き込むための固定としたままで、映像信号を書き込む段階の極性反転する電位差  $i \cdot j$  をほぼ等しくすることができると共に、黒書き込みする段階の極性反転する電位差  $k \cdot l$  をほぼ等しくすることができる。これにより、それぞれの状態で電位差が揃うため、応答速度を高めることができる。

【 0 2 4 7 】

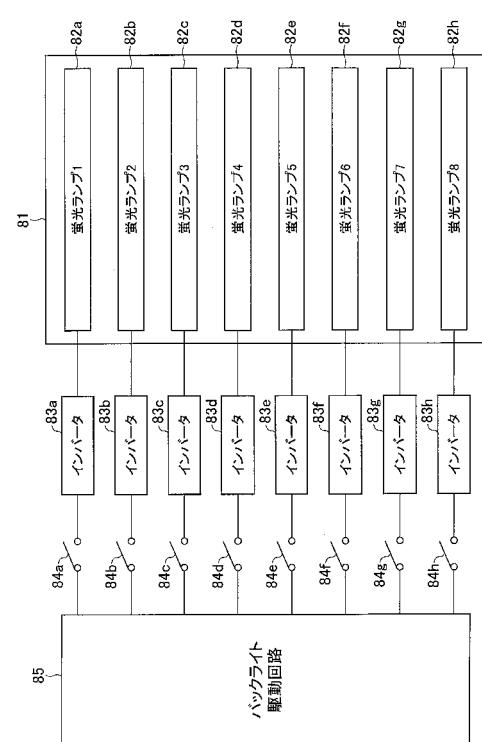

さらに、黒を書き込むタイミングと同期させて、液晶表示装置に設けられたバックライトを消灯させてもよい。バックライトは、液晶表示装置の液晶表示パネル 81 の裏面に配されており、図 33 に示すように、複数の (8 本の) 直下型蛍光ランプ (バックライト) 82a ~ 82h と、各蛍光ランプ 82a ~ 82h に接続された複数のインバータ 83a ~ 83h、これらのインバータ 83a ~ 83h にそれぞれ接続された複数の切り替えスイッチ 84a ~ 84h と、これらの切り替えスイッチ 84a ~ 84h を統合するバックライト駆動回路 85 と、を備えている。

40

【 0 2 4 8 】

各蛍光ランプ 82a ~ 82h は、ゲートライン  $GL_1 \sim GL_m$  (図 2) に平行な方向に配されており、走査信号  $G(1) \sim G(m)$  (図 2) に同期させて、配された順に、点灯・消灯するようになっている。また、上記したように、各蛍光ランプ 82a ~ 82h には、インバータ 83a ~ 83h および切り替えスイッチ 84a ~ 84h が備えられており、各蛍光ランプ 82a ~ 82h は互いに独立して点灯・消灯させることが可能となっている

50

。蛍光ランプ 82a～82h は、それぞれ図33に示すように、液晶表示パネル81を垂直方向に8分割した8つの分割表示領域に対応して設けられている。なお、各蛍光ランプ82a～82hには、例えば、冷極陰管を用いることができる。

#### 【0249】

バックライト駆動回路85は、外部から入力される走査信号G(1)～G(m)に同期させて、切り替えスイッチ84a～84hをオン・オフさせて、各蛍光ランプ82a～82hの点灯・消灯を制御する。

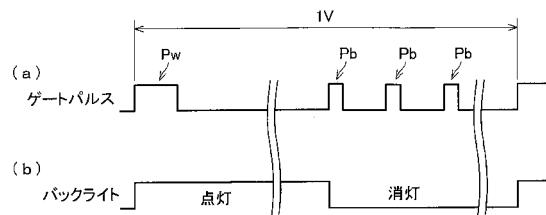

#### 【0250】

次に、バックライトの動作について説明する。図34(a)は、1垂直走査期間(1V)における、あるゲートラインGLjに印加される走査信号の波形図であり、図34(b)は、1垂直走査期間(1V)における、バックライトの点灯・消灯とを示す波形図である。なお、図34(b)において、バックライトは、ハイレベルのとき点灯し、ローレベルのとき消灯とする。例えば、図34(a)に示すように、分割領域の1番目(一番上)に配されたゲートラインGL1に画素データ書込パルスPwが印加されると、この画素データ書込パルスPwに同期してバックライト駆動回路85は、蛍光ランプ82aに対応して設けられた切り替えスイッチ84aをオンして、図34(b)に示すように、蛍光ランプ82aを点灯する。

10

#### 【0251】

次に、図34(a)に示すように、ゲートラインGL1に黒電圧印加パルスPbが印加されると、該黒電圧印加パルスPbの印加に同期してバックライト駆動回路85は、蛍光ランプ82aに対応して設けられた切り替えスイッチ84aをオフして、図34(b)に示すように、蛍光ランプ82aを消灯する。そして、この蛍光ランプ82aは、次フレームにおいてゲートラインGL1に画素データ書込パルスPwが印加されるまで消灯状態を維持する。

20

#### 【0252】

同様にして、各分割表示領域において、上記の動作を行なう。つまり、各分割表示領域において、該分割表示領域に配された蛍光ランプ82a～82hを点灯・消灯する動作を1垂直走査期間に繰り返す。以上のように、黒電圧印加パルスPbを印加するタイミングと同期させて蛍光ランプ82a～82hを消灯させれば、例えば、完全な黒電圧が印加されずに、液晶表示パネルの81画素透過率が十分に下がらない場合でも、透過光を低下させて、インパルス効果を高めることができる。つまり、液晶の応答速度改善を主眼として、プレチルト電圧を独立に決定することが可能となる。

30

#### 【0253】

なお、上記の例では、蛍光ランプ82a～82hの本数を8本としたが、これに限定されない。また、蛍光ランプ82a～82hの本数が多ければ、多いほど、1本の蛍光ランプに対応するゲートラインの本数が少なくなるので、各ゲートラインGLjで画素データ書込パルスPwおよび黒電圧印加パルスPbを印加時間が異なることにより生じる輝度ムラが軽減するが、蛍光ランプ82a～82h、インバータ83a～83h、切り替えスイッチ84a～84hなどの数も増えるためコストおよび消費電力が増加する。

#### 【0254】

40

また、蛍光ランプ82a～82hが少なすぎれば、所望の表示輝度が得られない場合もあるが、この場合には、蛍光ランプ82a～82hの発光効率を高めるために、蛍光ランプ82a～82hとして、熱陰極管を用いてもよい。蛍光ランプ82a～82hとしては、その他、LEDなどの光源を用いてもよく、蛍光ランプ82a～82hが、LEDであれば、分割表示領域をよりフレキシブルに分割することができる。

#### 【0255】

また、上記では、蛍光ランプ82a～82hを切り替えスイッチ84a～84hにより完全に消灯したが、点灯状態で、蛍光ランプ82a～82hへ流れるランプ電流を制御し、蛍光ランプの輝度、つまりランプ輝度を低減してもよい。さらに、上記では、各分割表示領域に対応する1ライン目(1番目)のゲートラインGL1の画素データ書込パルスP

50

w および黒電圧印加パルス P b に同期させて、蛍光ランプ 8 2 a ~ 8 2 h を点灯および消灯させたが、各分割表示領域内で蛍光ランプ 8 2 a ~ 8 2 h の消灯によるインパルス効果の均一性を上げるために、各分割表示領域内の中央のゲートラインの画素データ書き込みパルス P w および黒電圧印加パルス P b に同期させて、蛍光ランプ 8 2 a ~ 8 2 h を点灯および消灯させることが好ましい。但し、どのゲートラインの画素データ書き込みパルス P w および黒電圧印加パルス P b に同期に同期させてもよい。

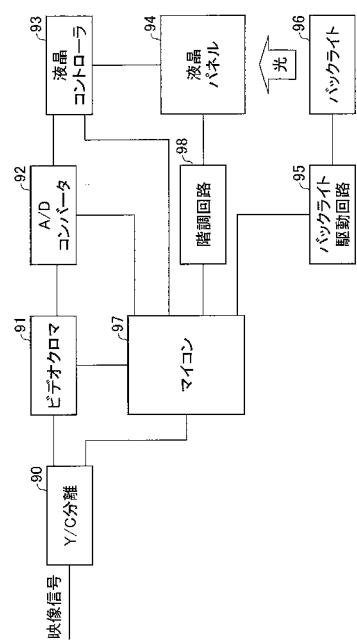

#### 【 0 2 5 6 】

さらに、上記の液晶表示装置を適用したテレビジョン受信機について、図 3 5 ~ 図 3 7 を参照しながら以下に説明する。つまり、上記した各液晶表示装置はテレビジョン受信機にも用いることができる。

10

#### 【 0 2 5 7 】

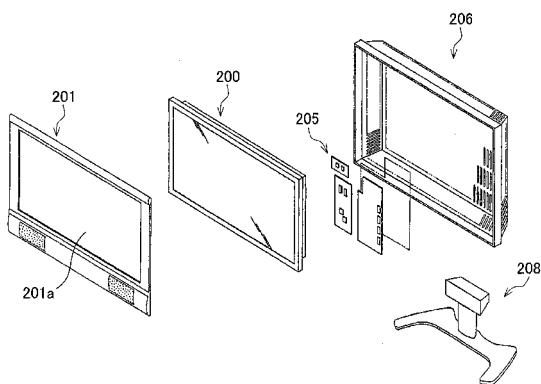

図 3 5 は、テレビジョン受信機用の液晶表示装置の回路ブロックを示す。液晶表示装置は、図 3 5 に示すように、Y / C 分離回路 9 0 、ビデオクロマ回路 9 1 、A / D コンバータ 9 2 、液晶コントローラ 9 3 、液晶パネル 9 4 、バックライト駆動回路 9 5 、バックライト 9 6 、マイコン 9 7 、階調回路 9 8 を備えた構成となっている。

#### 【 0 2 5 8 】

上記液晶パネル 9 4 は、上述した各実施の形態で説明した何れの構成であってもよい。上記構成の液晶表示装置において、まず、テレビ信号の入力映像信号は、Y / C 分離回路 9 0 に入力され、輝度信号と色信号に分離される。輝度信号と色信号はビデオクロマ回路 9 1 にて光の 3 原色である、R · G · B に変換され、さらに、このアナログ R G B 信号は A / D コンバータ 9 2 により、デジタル R G B 信号に変換され、液晶コントローラ 9 3 に入力される。

20

#### 【 0 2 5 9 】

液晶パネル 9 4 では液晶コントローラ 9 3 からの R G B 信号が所定のタイミングで入力されると共に、階調回路 9 8 からの R · G · B それぞれの階調電圧が供給され、画像が表示されることになる。これらの処理を含め、システム全体の制御はマイコン 9 7 が行うことになる。なお、映像信号として、テレビジョン放送に基づく映像信号、カメラにより撮像された映像信号、インターネット回線を介して供給される映像信号など、様々な映像信号に基づいて表示可能である。

30

#### 【 0 2 6 0 】

さらに、図 3 6 に示すチューナー部 9 9 ではテレビジョン放送を受信して映像信号を出力し、液晶表示装置（表示装置） 1 0 0 ではチューナー部 9 9 から出力された映像信号に基づいて画像（映像）表示を行う。

#### 【 0 2 6 1 】

また、上記構成の液晶表示装置をテレビジョン受信機とするとき、例えば、図 3 7 に示すように、液晶表示装置 1 0 0 を第 1 筐体 1 0 1 と第 2 筐体 1 0 6 とで包み込むようにして挟持した構成となっている。第 1 筐体 3 0 1 には、液晶表示装置 1 0 0 で表示される映像を透過させる開口部 1 0 1 a が形成されている。また、第 2 筐体 1 0 6 は、液晶表示装置 1 0 0 の背面側を覆うものであり、該液晶表示装置 1 0 0 を操作するための操作用回路 1 0 5 が設けられるとともに、下方に支持用部材 1 0 8 が取り付けられている。

40

#### 【 0 2 6 2 】

また、上記ゲートドライバ 4 は、図 5 ( a ) および図 5 ( b ) に示した構成に限定されるものではなく、図 1 ( d ) ( e ) に示すような走査信号 G ( 1 ) ~ G ( m ) を生成するものであれば何でもよい。また、上記では、図 1 ( d ) ( e ) に示すように、各ゲートライン G L j には 1 フレーム期間毎に 3 個の黒電圧印加パルス P b が印加されるが、1 フレーム期間における黒電圧印加パルス P b の個数すなわち 1 つのゲートラインが黒信号挿入期間で選択状態となる 1 フレーム期間当たりの回数は 3 回に限定されるものではなく、表示を黒レベルとすることができますのような 1 以上の数であればよい。図 1 ( f ) からわかるように、1 フレーム期間における黒電圧印加パルス P b の個数を変えることにより黒表示期間 T b k における黒レベル（表示輝度）を所望の値に設定することができる。

50

## 【0263】

また、上記実施形態では、各ゲートライン  $G_L j$  に対し、画素データ書込パルス  $P_w$  が印加されてから  $2/3$  フレーム期間の長さの画素データ保持期間  $T_{hd}$  が経過した時点で黒電圧印加パルス  $P_b$  が印加され（図1（d）（e））、各フレームにつき、ほぼ  $1/3$  フレーム期間程度の黒挿入が行われるが、黒表示期間  $T_{bk}$  は  $1/3$  フレーム期間に限定されるものではない。黒表示期間  $T_{bk}$  を長くすればインパルス化の効果が大きくなり動画表示性能の改善（尾引残像の抑制等）には有効であるが、表示輝度が低下することになるので、インパルス化の効果と表示輝度とを勘案して適切な黒表示期間  $T_{bk}$  が設定されることになる。

## 【0264】

なお、上記では、図11および図12に示すように、第1のMOSトランジスタ  $SW_a$  と、第2のMOSトランジスタ  $SW_b$  および第3のMOSトランジスタ  $SW_b 2$  または第2のMOSトランジスタ  $SW_c$  と、インバータ33とにより、チャージシェア期間  $T_{sh}$  においてソースライン  $SL_1 \sim SL_n$  へのデータ信号  $S(1) \sim S(n)$  の印加を遮断すると共にそれらのソースライン  $SL_1 \sim SL_n$ （各隣接ソースライン）を互いに短絡するスイッチ回路が構成され、このスイッチ回路はソースドライバ3に含まれる。しかし、このスイッチ回路の一部または全部をソースドライバ3の外部に設ける構成、例えば  $TTT$  を用いて表示部1内に画素アレイと一体化して設ける構成としてもよい。

## 【0265】

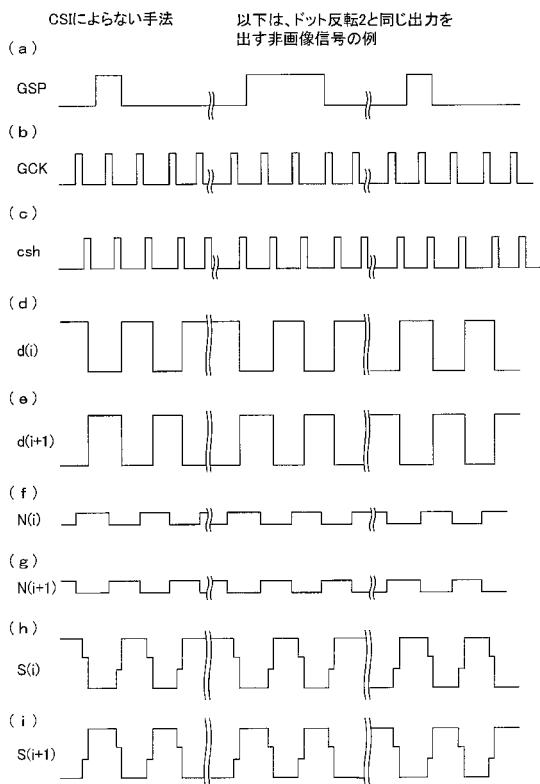

図38は、ソースドライバ3の出力部13の他の構成を示す回路図である。図39（a）～（d）は、図38に示す出力部13を備えたソースドライバ3の駆動方法を説明するための波形図である。

## 【0266】