(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4277148号

(P4277148)

(45) 発行日 平成21年6月10日(2009.6.10)

(24) 登録日 平成21年3月19日(2009.3.19)

(51) Int.Cl.

F 1

G02F 1/133 (2006.01)

G02F 1/133 550

G09G 3/20 (2006.01)

G09G 3/20 623D

G09G 3/36 (2006.01)

G09G 3/36

請求項の数 4 (全 20 頁)

(21) 出願番号 特願2000-1490 (P2000-1490)

(22) 出願日 平成12年1月7日 (2000.1.7)

(65) 公開番号 特開2001-194644 (P2001-194644A)

(43) 公開日 平成13年7月19日 (2001.7.19)

審査請求日 平成18年8月10日 (2006.8.10)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100101214

弁理士 森岡 正樹

(72) 発明者 拠山 和宏

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 形川 晃一

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 鈴木 俊光

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその駆動方法

## (57) 【特許請求の範囲】

## 【請求項1】

表示データの入力に対応して入力されるデータイネーブル信号に基づいて前記表示データを所定の画素に出力する出力タイミングを制御する液晶表示装置の駆動方法において、前記データイネーブル信号の周期を水平周期として計測し、前記水平周期に基づいて垂直プランキング期間中に仮想イネーブル信号を生成し、前記データイネーブル信号と仮想イネーブル信号の合計を垂直周期として保持し、少なくとも表示開始ラインの画素に対して、前記垂直周期より前記水平周期の整数倍短い時点で、前記表示データの予備書き込みを行うこと

を特徴とする液晶表示装置の駆動方法。

10

## 【請求項2】

表示データの入力に対応して入力されるデータイネーブル信号に基づいて前記表示データを所定の画素に出力する出力タイミングを制御するタイミングコントローラを備えた液晶表示装置において、

前記タイミングコントローラは、

前記データイネーブル信号の周期を水平周期として計測し、前記水平周期に基づいて垂直プランキング期間中に仮想イネーブル信号を生成する水平カウンタ部と、

前記データイネーブル信号と仮想イネーブル信号の合計を垂直周期として保持する垂直カウンタ部を有し、

少なくとも表示開始ラインの画素に対して、前記垂直周期より前記水平周期の整数倍短

20

い時点で、前記表示データの予備書き込みを行うこと

を特徴とする液晶表示装置。

【請求項 3】

複数の薄膜トランジスタのゲート電極と接続するゲートバスラインにゲート信号を出力するゲートドライバと、前記複数の薄膜トランジスタのドレイン電極にそれぞれ接続された複数のデータバスラインにデータを出力する複数のデータドライバと、前記データドライバにデータ出力用のラッチパルスを出力するタイミングコントローラとを有する液晶表示装置において、

前記タイミングコントローラは、前記複数のデータドライバに対し、前記ゲートドライバからの距離に応じて前記ラッチパルスの出力タイミングを変化させて供給するため、

前記ゲートドライバから引き出されて前記ゲートバスラインとほぼ平行に配線されたラッ

チパルス供給用ラインを有していること

を特徴とする液晶表示装置。

【請求項 4】

複数の薄膜トランジスタのゲート電極と接続するゲートバスラインにゲートドライバからゲート信号を出力し、複数のデータドライバにデータ出力用のラッチパルスを出力して前記複数の薄膜トランジスタのドレイン電極にそれぞれ接続された複数のデータバスラインにデータを出力する液晶表示装置の駆動方法において、

前記複数のデータドライバに対し、前記ゲートドライバからの距離に応じてそれぞれ出力タイミングを変化させた前記ラッチパルスを、前記ゲートドライバから引き出されて前記ゲートバスラインとほぼ平行に配線されたラッ

チパルス供給用ラインから供給すること

を特徴とする液晶表示装置の駆動方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、液晶表示装置及びその駆動方法に関し、特に、薄膜トランジスタ(TFT)をスイッチング素子に用いたアクティブマトリクス型液晶表示装置(以下、TFT-LCDという)及びその駆動方法に関する。

【0002】

【従来の技術】

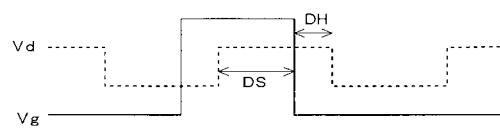

近年、TFT-LCDの高精細化に伴い、各TFTのゲートに印加されるゲートパルスの駆動周波数が高くなっている。また、TFT-LCDの大画面化に伴い、マトリクス状に配列された複数の画素にゲートパルスを供給するゲートバスラインや階調データを出力するデータバスラインの配線長は長くなりそれらの配線抵抗が高くなる傾向にある。このため、ゲートバスラインの配線抵抗によりゲート波形が鈍り、ゲートドライバから遠ざかる領域でゲートオフのタイミングが遅延する問題が生じる。これを回避するため従来、図15に示すような駆動方式がとられている。この駆動方法は、データドライバからデータバスラインに出力されるデータ電圧Vdのデータ切り替えのタイミングを、ゲートドライバからゲートバスラインに出力されたゲートパルスVgのゲートオフのタイミングよりも後にずらすようにしている。つまり、ゲートオンの後のデータセットアップ時間DS内に所定の階調電圧をTFTのドレイン電極に印加すると共に、その状態をゲートオフ後もデータ保持期間DHだけ維持するようにしている。こうすることにより、ゲート波形の鈍りによるゲートオフのタイミングの遅れがデータ保持期間DH内であれば、確実にデータ電圧Vdを画素に書き込むことができるようになる。

【0003】

ところが、このデータ保持時間DHはTFT-LCDの大画面化が進みパネルサイズが大きくなるほど長くしなければならない。またデータバスラインの配線抵抗が高くなるに従って、データドライバの出力遅延時間が長くなるため、データセットアップ時間DSもパネルサイズが大きくなるほど長くしなければならなくなる。一方、パネルの高精細化に伴ってゲートバスライン数が増えると、データセットアップ時間DSとデータ保持期間DH

10

20

30

40

50

との合計である水平周期は短くせざるを得ない。つまり従来のデータ駆動方法では、TFT-LCDの高精細化及び大画面化の要求を同時に満足させるには、水平周期を短くさせ且つデータ保持期間DH及びデータセットアップ時間DSを長くさせるという矛盾が生じる。

#### 【0004】

ちなみにSVGA(画素数が $800 \times 600$ )や、XGA(画素数が $1024 \times 768$ )では水平周期が標準でそれぞれ $26.4\mu s$ (マイクロ秒)、 $20.7\mu s$ である。このため、画面サイズが対角15インチでXGA程度までのパネルであれば、図15に示したような1フレーム中にゲートオンが1回の通常駆動でデータ書き込み時間が不足することはない。しかし、対角15インチを越える画面サイズでSXGA(画素数が $1280 \times 1024$ )以上の高精細大画面になると、通常駆動では、階調データを満足に書き込めない可能性が生じてくる。例えば、SXGAでは水平周期が標準で $15.6\mu s$ 必要であるが、画面サイズが対角 $17 \sim 18$ インチ程度で後述のドット反転駆動方式を用いたSXGAパネルでは、 $3\mu s$ 以上のデータホールド時間DHと $10\mu s$ 以上のデータセットアップ時間DSが必要になる。このため、十分なデータ書き込みのためのマージンが得られなくなる可能性がある。

#### 【0005】

そこで従来は、データ電圧の書き込み不足による表示ムラやフリッカ等の表示不具合を解決する手段として、本来の表示データを書き込む前に同極性の表示データを予備書き込みする手法が用いられている。

#### 【0006】

この予備書き込みの手法について、ゲートバスライン方向及びデータバスライン方向の双方に関し、隣接画素(サブピクセル)間で階調データの極性が反転しているドット反転駆動を例にとって説明する。ドット反転駆動では、ある画素に書き込まれる階調データの極性は、同一データバスライン上で2ライン前のゲートバスラインに接続されている画素に書き込まれる階調データの極性と同一になる。従って、当該画素への予備書き込みは、当該画素への本来のデータ書き込みの2ライン前に行う。例えば表示開始ラインから3ライン目のゲートバスライン上の画素は、表示開始ライン(1ライン目)の画素に階調データが書き込まれる際に同時に当該階調データが予備書き込みされ、その後本来の階調データが書き込まれるようになる。従って、この駆動方式では表示開始ラインからn-2ライン目とnライン目のゲートが同時にオン状態となる。以上のような予備書き込み方式の駆動方法については、例えば特開平11-142807号公報や特開平5-265411号公報等に開示されている。なお、予備書き込みを用いずに書き込みマージンを確保するには、フレーム反転駆動にしてバスラインのデータ電圧確定を早くする方法も考えられるが、フレーム反転駆動の際には、データバスラインと画素電極の間に生じるクロストークが問題となるため好ましくない。

#### 【0007】

##### 【発明が解決しようとする課題】

以上説明したように、TFT-LCDが高精細化してゲート走査周期が短くなり、大画面化によりデータ書き込み時間が短くなってしまっても、予備書き込みを行うことにより十分な書き込みマージンを得ることができるようになる。

#### 【0008】

ところが、従来の予備書き込みによる駆動方法、例えば上述のドット反転駆動の場合は、ゲートバスラインにおける表示開始ラインである第1ライン目とその次の第2ライン目の予備書き込みについて何ら規定していない。ゲートバスラインの第1ライン目と第2ライン目の予備書き込みは、前フレームの表示期間内あるいは表示終了直後、または垂直ブランкиング期間中に行うことが考えられる。

#### 【0009】

前フレームの表示期間内あるいは表示終了直後に第1及び第2ライン目の予備書き込みを行う場合は、前フレームでの予備書き込みから当該フレームでの本書き込みまでの時間は

10

20

30

40

50

偽のデータを表示し続けることになる。垂直プランキング期間がフレームの表示期間に対して比較的長い場合には、第1及び第2ラインの予備書き込みによる他のラインとの境界が明確に視認されて表示品質が低下してしまうという問題が発生する。

#### 【0010】

垂直プランキング期間中に第1及び第2ライン目の予備書き込みを行う場合は、予備書き込みを開始するための仮想ゲートバスラインの取り扱いが面倒であるという問題が生じる。垂直同期信号（Vsync）と水平同期信号（Hsync）がシステム側から入力される場合には、VsyncとHsyncとから表示開始時点が分かるため、表示開始時点より2ライン前から予備書き込みを開始することができる。

#### 【0011】

ところが、近年のLCDの標準仕様はHsync及びVsyncを用いずに、システム側から入力するデータイネーブル信号Enableのみで画面表示位置を決定するようになってきている。このため、データイネーブル信号Enableに基づいて垂直プランキング期間中に第1及び第2ライン目の予備書き込みをしなければならないという困難が生じる。

#### 【0012】

本発明の目的は、システム側からのデータイネーブル信号に基づいて垂直プランキング期間中に少なくとも第1ライン目の予備書き込みを最適に行える液晶表示装置の駆動方法を提供することにある。

#### 【0013】

##### 【課題を解決するための手段】

上記目的は、表示データの入力に対応して入力されるデータイネーブル信号に基づいて前記表示データを所定の画素に出力する出力タイミングを制御する液晶表示装置の駆動方法において、前記データイネーブル信号の周期を水平周期として計測し、前記水平周期に基づいて垂直プランキング期間中に仮想イネーブル信号を生成し、前記データイネーブル信号と仮想イネーブル信号の合計を垂直周期として保持し、少なくとも表示開始ラインの画素に対して、前記垂直周期より前記水平周期の整数倍短い時点で、前記表示データの予備書き込みを行うことを特徴とする液晶表示装置の駆動方法によって達成される。

#### 【0014】

また、上記目的は、表示データの入力に対応して入力されるデータイネーブル信号に基づいて前記表示データを所定の画素に出力する出力タイミングを制御するタイミングコントローラを備えた液晶表示装置において、前記タイミングコントローラは、前記データイネーブル信号の周期を水平周期として計測し、前記水平周期に基づいて垂直プランキング期間中に仮想イネーブル信号を生成する水平カウンタ部と、前記データイネーブル信号と仮想イネーブル信号の合計を垂直周期として保持する垂直カウンタとを有し、少なくとも表示開始ラインの画素に対して、前記垂直周期より前記水平周期の整数倍短い時点で、前記表示データの予備書き込みを行うことを特徴とする液晶表示装置。

#### 【0015】

さらに上記目的は、複数の薄膜トランジスタのゲート電極と接続するゲートバスラインにゲート信号を出力するゲートドライバと、前記複数の薄膜トランジスタのドレイン電極にそれぞれ接続された複数のデータバスラインにデータを出力する複数のデータドライバと、前記データドライバにデータ出力用のラッチパルスを出力するタイミングコントローラとを有する液晶表示装置において、前記タイミングコントローラは、前記複数のデータドライバに対し、前記ゲートドライバからの距離に応じて前記ラッチパルスの出力タイミングを変化させて供給するラッチパルス供給用ラインを有していることを特徴とする液晶表示装置によって達成される。

#### 【0016】

複数の薄膜トランジスタのゲート電極と接続するゲートバスラインにゲートドライバからゲート信号を出力し、複数のデータドライバにデータ出力用のラッチパルスを出力して前記複数の薄膜トランジスタのドレイン電極にそれぞれ接続された複数のデータバスラインにデータを出力する液晶表示装置の駆動方法において、前記複数のデータドライバに対し

10

20

30

40

50

、前記ゲートドライバからの距離に応じてそれぞれ出力タイミングを変化させた前記ラッチパルスをラッチパルス供給用ラインから供給することを特徴とする液晶表示装置の駆動方法。

#### 【0017】

##### 【発明の実施の形態】

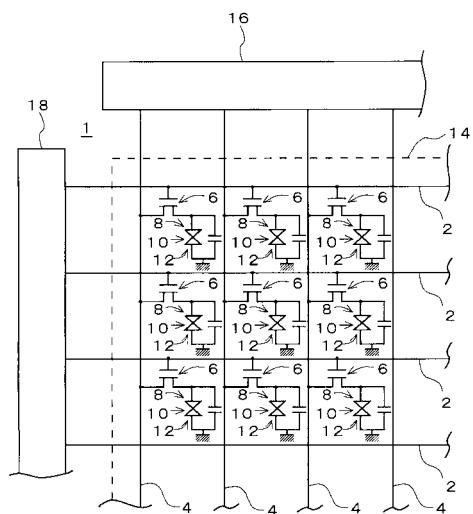

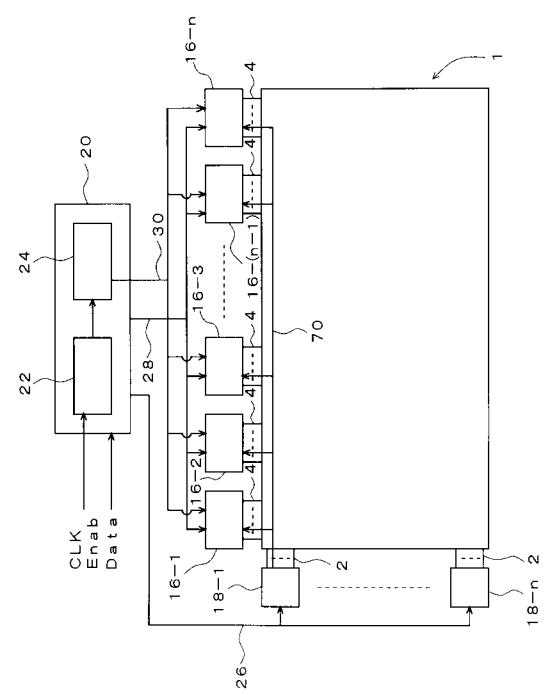

本発明の第1の実施の形態による液晶表示装置の駆動方法を図1乃至図7を用いて説明する。まず、本実施の形態によるアクティブマトリクス型の液晶表示装置として、薄膜トランジスタ(TFT:Thin Film Transistor)をスイッチング素子に用いた液晶表示装置の構造を図1を用いて簡単に説明する。図1は液晶表示装置をパネル上面から見た状態を示しており、アレイ基板1と対向基板14の2枚のガラス基板間に液晶が封入されている。アレイ基板1上には例えば図面左右方向に延びるゲートバスライン2が上下方向に平行に複数形成されている。図示しない絶縁膜を介して図面上下方向に延びるデータバスライン4が左右方向に平行に複数形成されている。このように縦横に形成されたゲートバスライン2とデータバスライン4とで画定されたマトリクス状の複数の領域のそれぞれは、画素領域として画素電極8が形成されている。

10

#### 【0018】

各画素領域のゲートバスライン2とデータバスライン4との交差点近傍にはTFT6が形成され、TFT6のゲート電極はゲートバスライン2に、ドレイン電極はデータバスライン4にそれぞれ接続されている。また、ソース電極は画素電極8に接続されている。ゲートバスライン2はゲートドライバ18により駆動され、データバスライン4はデータドライバ16により駆動される。データドライバ16から各データバスライン4に対して階調電圧が出力され、いずれかのゲートバスライン2にゲート信号が出力されると、当該ゲートバスライン2にゲート電極が接続された一連のTFT6がオンになって、それらのTFT6のソース電極に接続された画素電極8に階調電圧が印加される。

20

#### 【0019】

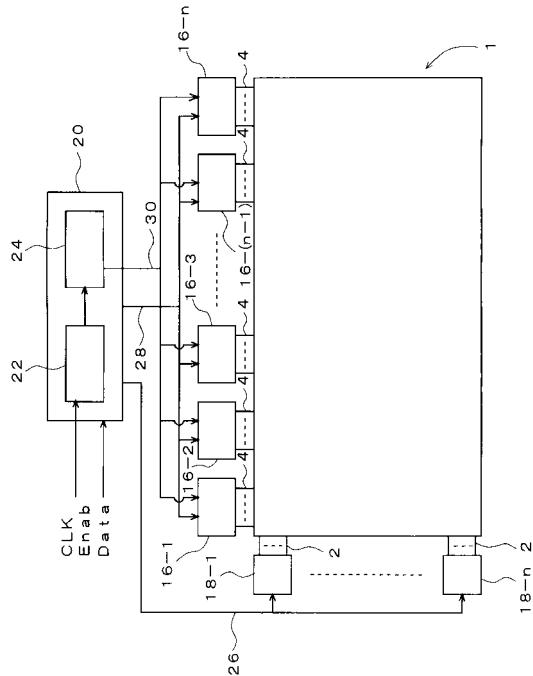

次に、本実施の形態による液晶表示装置の表示駆動系の概略構成について図2を用いて説明する。図2は、液晶表示装置をパネル上面から見た状態を示しており、アレイ基板1上の画素の構成等は図1に示したものと同様であるのでそれらの図示は省略している。

#### 【0020】

図2に示すように、複数のデータバスライン4にそれぞれデータ信号を出力する複数のデータドライバ16-1~16-nがパネル上方左から右に順に例えばTAB(Tape Automated Bonding)実装によりアレイ基板1と接続されている。同様にしてパネル左方上から下に向かって複数のゲートドライバ18-1~18-nが設けられている。

30

#### 【0021】

各データ・ドライバ16-1~16-nに接続された複数のデータバスライン4は、データドライバ16-1~16-nの順にゲートドライバ18-1~18-nから遠ざかるように配置されている。ゲートドライバ18-1~18-nはゲートドライバ制御信号を出力するタイミングコントローラ20に信号線26を介して接続されている。

#### 【0022】

40

タイミングコントローラ20には、PC(パーソナル・コンピュータ)等のシステム側から出力されたクロックCLK及びデータタイマーブル信号Enab、並びに階調データData等が入力する。

#### 【0023】

タイミングコントローラ20は、水平カウンタ22及び垂直カウンタ24を有している。水平カウンタ22は、外部クロックCLKに基づいて生成されたドットクロックDCLKの数をカウントする。垂直カウンタ24は、データタイマーブル信号Enabの数をカウントする。水平、垂直カウンタ22、24の出力値はデコーダ(図示せず)に入力されて種々の制御信号が出力されるようになっている。

#### 【0024】

50

タイミングコントローラ20は、ゲートドライバ制御信号としてゲートクロックGCLKとゲートスタート信号GSTを出力する。ゲートクロックGCLKとゲートスタート信号GSTは、水平カウンタ22でデータタイネーブル信号Enabの立ち下がり（または立ち上がり；以下、代表して「立ち下がり」という）エッジからのドットクロックDCLKの数をカウントして得られる水平周期に基づいて出力される。ゲートスタート信号GSTは、表示フレーム内の特定位置で通常1回または2回出力させるため、さらにデータタイネーブル信号Enabの数を垂直カウンタ24でカウントして得られる垂直周期に基づいて出力される。

#### 【0025】

タイミングコントローラ20は、データドライバ制御信号としてドットクロックDCLK、ラッチパルスLP、極性信号POL、及びデータスタート信号DSTを出力する。ラッチパルスLP、極性信号POL、及びデータスタート信号DSTは上述の水平カウンタ22で得られる水平周期に基づいて出力される。なお、フレーム先頭の認識は、データタイネーブル信号Enabの“L（ロー）”期間においてドットクロックDCLKが所定クロック数を越えてカウントされることにより判定される。これらの制御信号は制御線30を介してデータドライバ16-1~16-nに出力される。また、階調データDataはデータ線28を介してデータドライバ16-1~16-nに入力される。

10

#### 【0026】

次に、本実施の形態による液晶表示装置の表示駆動方法について、図3乃至図7を用いて説明する。本実施の形態は、上述のドット反転駆動における第1及び第2ライン目の予備書き込み動作について説明するが、他の種々の反転駆動方式にも同様に適用可能である。

20

#### 【0027】

表示ライン先頭の第1ライン及びその次の第2ラインに対する予備書き込みは垂直プランキング期間に行うが、予備書き込みデータの表示期間を短くするため、当該表示フレーム先頭の第1ラインの本書き込み時期にできるだけ近い時点の垂直プランキング期間内で予備書き込みを開始させる必要がある。ドット反転駆動では2ライン周期でデータラインの極性が変わるため、先頭のデータタイネーブル信号Enabより2水平周期だけ手前から予備書き込みを開始するようとする。

#### 【0028】

ところが、垂直プランキング期間中は、システム側からデータタイネーブル信号Enabが入力されない。そのため、まず、垂直プランキング期間VBの長さと1水平周期1Hの長さを計測して保持しておく必要がある。

30

#### 【0029】

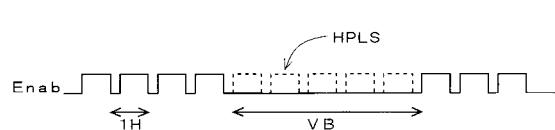

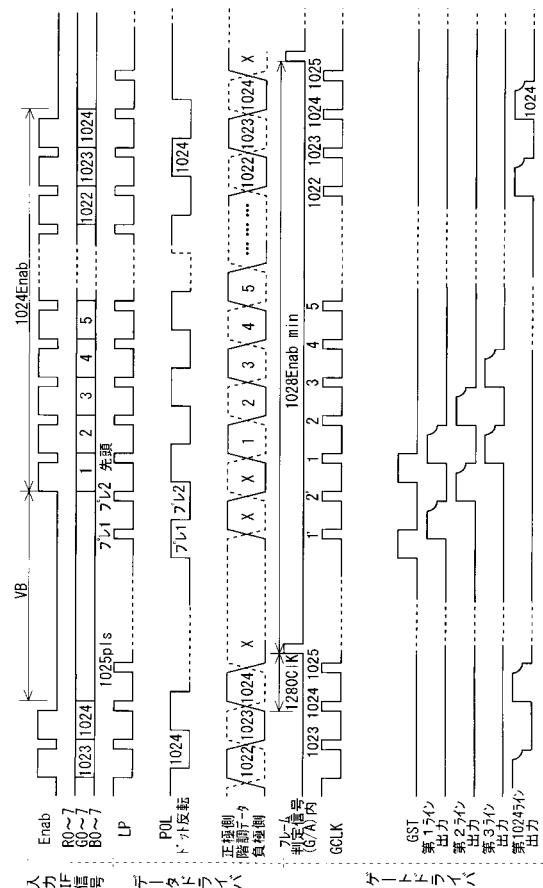

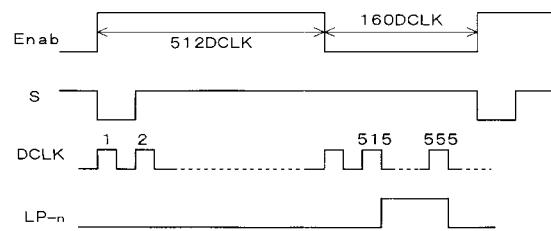

図3は垂直プランキング期間を含むデータタイネーブル信号Enabを示している。図3に示すようにデータタイネーブル信号Enabの立ち下がりエッジから次の立ち下がりエッジまでが1水平周期1Hである。また、垂直プランキング期間VB中にはデータタイネーブル信号Enabは出力されない。

#### 【0030】

このようなデータタイネーブル信号Enabに基づいて、以下に示す手順で予備書き込み位置を特定する。

40

(1) 水平カウンタ22を用い、ある時点のデータタイネーブル信号Enabの立ち下がりエッジから次の立ち下がりエッジまでのドットクロックDCLKのクロック数をカウントして、1水平周期1Hに対応するドットクロックDCLKのクロック数を1H保持回路(図示せず)に保持しておく。

#### 【0031】

そして、垂直プランキング期間VB中においては、水平カウンタ22でカウントされるドットクロックDCLKの数が上記1水平周期1Hに達する毎に水平カウンタ22をリセットし、リセットの際にデータタイネーブル信号Enabの立ち下がりエッジの代わりとして仮想イネーブル信号HPLS(図3中破線で示している)を垂直カウンタ24に出力する。

50

**【0032】**

(2) 垂直カウンタ24は、1表示フレーム中のデータイネーブル信号E<sub>nab</sub>の数（すなわち、1水平周期1Hの数）と垂直プランキング期間VB中の仮想イネーブル信号HPLSの数をカウントする。SXGAの場合は1フレーム中のデータイネーブル信号E<sub>nab</sub>の数は1024であり、垂直プランキング期間VB中の仮想イネーブル信号HPLSの数は4～42程度である。図3ではHPLS=5を例示している。

**【0033】**

このように本実施の形態における垂直カウンタ24は、垂直プランキング期間VBでの仮想イネーブル信号HPLSの数をカウントするため非表示期間も動作するようになっている。1表示フレーム中のデータイネーブル信号E<sub>nab</sub>の数と垂直プランキング期間VB中の仮想イネーブル信号HPLSの数を合わせて1垂直周期1Vとし、1V保持回路に保持しておく。

10

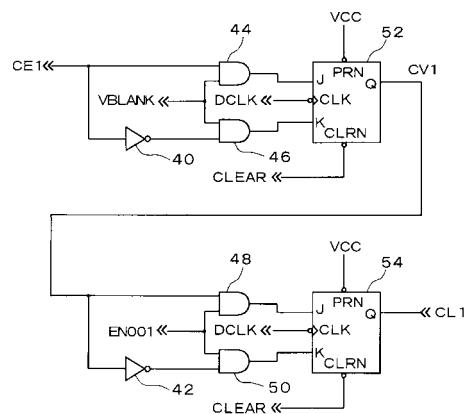

**【0034】**

ここで、1V保持回路の回路構成例について図4を用いて説明する。図4に示す回路例は、1V保持回路における最下位ビットの保持回路を示している。保持するビット数に応じて図4に示す回路が複数配置されて1V保持回路が構成される。図4において、垂直カウンタ24の最下位ビットCE1の出力端が、2入力AND回路44の一入力端子と、インバータ40を介して2入力AND回路46の一入力端子とに接続されている。2つのAND回路44、46の他入力端子には、垂直プランキング期間VBでの仮想イネーブル信号HPLSが入力される。

20

**【0035】**

AND回路44の出力端子はJKフリップフロップ(JKFF)52のJ入力端子に接続され、AND回路46の出力端子はJKFF52のK入力端子に接続されている。JKFF52のクロック入力端子CLKにはドットクロックDCLKが入力される。このような構成により、垂直プランキング期間VB内に垂直カウンタ24から1垂直周期1Vの値を取り込んで次の表示フレーム期間中保持することができる。JKFF52のQ出力端子からは、次の表示フレーム期間中に前フレームの1垂直周期1Vの最下位ビットの値CV1が出力される。

**【0036】**

JKFF52のQ出力端子は、2入力AND回路48の一入力端子と、インバータ42を介して2入力AND回路50の一入力端子とに接続されている。2つのAND回路48、50の他入力端子には、データホールド信号ENO01が入力される。AND回路48の出力端子はJKFF54のJ入力端子に接続され、AND回路50の出力端子はJKFF54のK入力端子に接続されている。JKFF54のクロック入力端子CLKにはドットクロックDCLKが入力される。

30

**【0037】**

このような構成により、垂直プランキング期間VB中に垂直カウンタ24から取り込んだ1垂直周期1Vの値を次の垂直周期（次の表示フレーム期間及び垂直プランキング期間）中保持することができる。JKFF54のQ出力端子には、次の垂直周期中に前の垂直周期内の1水平周期1Hの数及び仮想イネーブル信号HPLSの数の合計の最下位ビットの値CL1が保持される。

40

なお、説明は省略するが水平カウンタ22と接続される1H保持回路も同様の回路構成で実現可能である。

**【0038】**

(3) 次に、1V保持回路で保持された1垂直周期内の1水平周期1Hと仮想イネーブル信号HPLSの数の合計数から垂直プランキング期間VBで予備書き込みを実行するためには必要なラインの数を減算する。これは図5に例示する減算回路により実現される。図5は、ドット反転駆動において、表示開始ラインの第1ラインのデータの本書き込みより2水平周期分手前の時点で予備書き込みを開始させるために、1V保持回路の保持値から“2”を減算する処理を行う回路を示している。図5に示す減算回路は、図4で説明した1

50

V保持回路から出力される1垂直周期のカウント値の下位2ビット目から5ビット目について所定の処理を行いカウント値の減算をするようになっている。

#### 【0039】

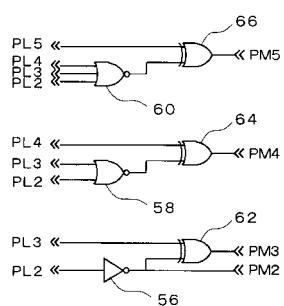

図5において、入力端PL2はインバータ56を介して、出力端PM2に接続されると共に排他的論理和回路(EXOR回路)62の一入力端子に接続されている。さらに入力端PL2は、2入力NOR回路58の一入力端子と3入力NOR回路60の第1入力端子に接続されている。入力端PL3はEXOR回路62の他入力端子、2入力NOR回路58の他入力端子、及び3入力NOR回路60の第2入力端子に接続されている。入力端PL4は、EXOR回路64の一入力端子に接続され、NOR回路60の第3入力端子に接続されている。入力端PL5は、EXOR回路66の一入力端子に接続されている。

10

#### 【0040】

NOR回路58の出力端子はEXOR回路64の他入力端子に接続されている。NOR回路60の出力端子は、EXOR回路66の他入力端子に接続されている。EXOR回路62の出力端子は出力端PM3に、EXOR回路64の出力端子は出力端PM4に、EXOR回路66の出力端子は出力端PM5にそれぞれ接続されている。

#### 【0041】

このような構成の回路の入力端PL2～PL5に、図4で説明したV保持回路から1垂直周期のカウント値の下位2ビット目から5ビット目の値として表1に示すD2～D5が入力されると、出力端PM2～PM5には、表2に示すQ2～Q5が出力される。なお、表1の“X”は“1”または“0”を示す。

20

#### 【0042】

【表1】

| D2 | D3 | D4 | D5 |

|----|----|----|----|

| 1  | X  | X  | X  |

| 0  | 1  | X  | X  |

| 0  | 0  | 1  | X  |

| 0  | 0  | 0  | 1  |

30

#### 【0043】

【表2】

| Q2 | Q3 | Q4 | Q5 |

|----|----|----|----|

| 0  | D3 | D4 | D5 |

| 1  | 0  | D4 | D5 |

| 1  | 1  | 0  | D5 |

| 1  | 1  | 1  | 0  |

40

#### 【0044】

このようにして、表示開始ラインである第1ラインのデータの本書き込みより2水平周期分手前の予備書き込みを開始させる時期を決定することができる。

このように本実施の形態によれば、1データイネーブル信号Enabの周期毎、すなわち水平周期毎にリセットされる水平カウンタ22と、垂直周期を決定するためにデータイネーブル信号Enabと仮想イネーブル信号HPLSの合計数をカウントする垂直カウンタ24とを有しているので、これら水平周期と垂直周期とに基づいて垂直ブランкиング期間VB内の所定時点でゲートスタート信号GSTを出力することができるようになる。なお

50

、各表示フレームでの水平周期の数は一定であることが望ましいが、通常はシステム側のP C等による制御で一定値が確保されているので問題は生じない。

#### 【0045】

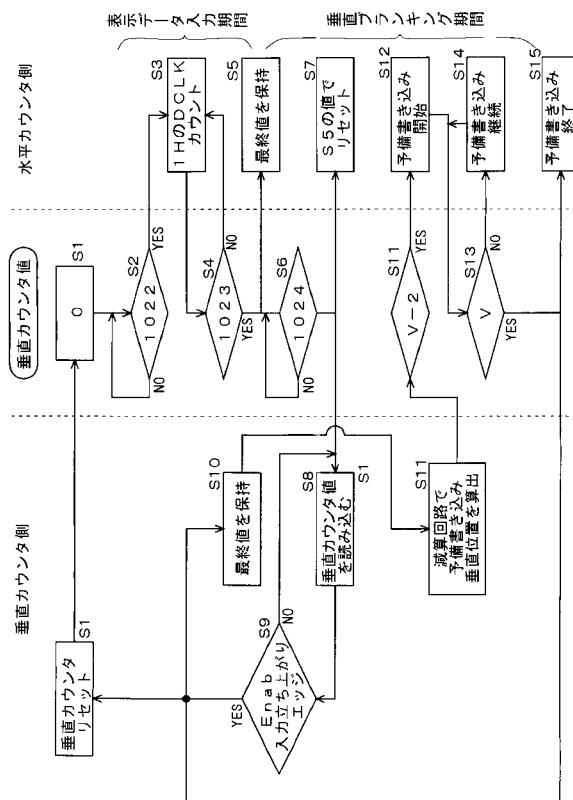

次に、図6及び図7を用いて本実施の形態による液晶表示装置の駆動方法をより具体的に実施例を用いて説明する。図6は、図7に示す動作タイミングにおける水平カウンタ22及び垂直カウンタ24の動作を示している。図7は、SXGAであってドット反転駆動の液晶表示装置に本実施の形態を適用したタイミングチャートを示している。

#### 【0046】

図6及び図7に示す例では、表示フレームは1024(H)であり垂直プランキング期間VBは図示していないが6(H)である。上述の通り、垂直カウンタ24は垂直プランキング期間VB中も動作して、データイネーブル信号Enabと仮想イネーブル信号HPLSをカウントする。従って、垂直カウンタ値は図6に示す例では1030まで進む。垂直カウンタ24は、垂直プランキング期間VB後の次の先頭のデータイネーブル信号Enabの入力でリセットされる(ステップS1参照)。なお、表示フレームの切り替わりはデータイネーブル信号Enabの“L”期間の長さで判定する。

10

#### 【0047】

本実施例では、図6のステップS2～S5に示すように、垂直カウンタ24のカウンタ値が1022になったら水平カウンタ22による1水平周期1Hの計測を開始するようにしている。1水平周期1Hの計測は、先頭のデータイネーブル信号Enabから1022番目のデータイネーブル信号Enabの立ち下がりエッジから、1023番目のデータイネーブル信号Enabの立ち下がりエッジまでのドットクロックDCLKの数をカウントすることにより行われる。計測した1水平周期1Hは図4に示したのと同様の回路構成を有する1H保持回路で保持される。

20

#### 【0048】

次いで、ステップS6で、1024番目のデータイネーブル信号Enabの入力があったら水平カウンタ22をリセットし、以後、水平カウンタ22によるドットクロックDCLKのカウント数がステップS5で保持している1水平周期1Hになる毎に水平カウンタ22をリセットする(ステップS7)。これに基づいて垂直プランキング期間VB中に仮想イネーブル信号HPLSが出力される。

#### 【0049】

30

一方、垂直カウンタ24は、1024個のデータイネーブル信号Enabをカウントした後、続いて仮想イネーブル信号HPLSをカウントする。このとき図4に示した1V保持回路には仮想イネーブル信号HPLSの入力タイミングで垂直カウンタ24のカウンタ値が読み込まれる(ステップS8)。

#### 【0050】

垂直カウンタ24による仮想イネーブル信号HPLSのカウント及び1V保持回路での垂直カウンタ24のカウンタ値の読み込みは、データイネーブル信号Enabの立ち上がりエッジの検出により終了する(ステップS9)。

#### 【0051】

40

データイネーブル信号Enabの立ち上がりエッジが検出されると図4に示す1V保持回路には垂直周期1Vが保持される(ステップS10)と共に、垂直カウンタ24はリセットされる(ステップS1)。

#### 【0052】

1V保持回路に保持された垂直周期1Vは図5に示す減算回路に出力されて、2水平周期分だけ減算されて予備書き込みの垂直位置が算出される(ステップS11)。本実施例では、先頭のデータイネーブル信号Enabの入力時点から1垂直周期1V経過するより1水平周期1Hの2倍だけ短い時点で、次画面の表示開始ラインである第1ラインの画素に対する予備書き込みが行われる。

#### 【0053】

次いで、先頭のデータイネーブル信号Enabの入力時点から1垂直周期1V経過するよ

50

り 1 水平周期 1 H 分だけ短い時点で、第 2 ラインについての予備書き込みが行われる（ステップ S 12）。すなわち、次画面の表示開始ラインである第 1 ラインより 2 水平周期分手前で第 1 ラインの予備書き込みが行われる。次いで、次の第 2 ラインより 2 水平周期分手前で第 2 ラインの予備書き込みが行われる。

#### 【0054】

次いで、予備書き込みをする毎に垂直カウンタ 24 のカウント値をインクリメントし、ステップ S 13 で垂直周期 1 V に戻っているかを判断する。戻っていないければ予備書き込みを継続し（ステップ S 14）、垂直カウンタ 24 のカウント値が垂直周期 1 V になったら予備書き込みを終了する（ステップ S 15）。なお、ステップ S 9 において、先頭のデータイネーブル信号 E n a b を検出した場合にも、予備書き込みは終了する（ステップ S 15）。

10

#### 【0055】

図 7 に示すように、予備書き込み時には、タイミングコントローラ 20 からゲートスタート信号 G S T がゲートドライバ 18 へ送出され、続いてゲートクロック G C L K がゲートドライバ 18 に出力される。ゲートドライバ 18 はゲートスタート信号 G S T により動作を開始し、ゲートクロック G C L K が入力される毎に順次開いたゲートを閉じ、次ラインのゲートを開くように機能する。一方、データドライバ 16 には、表示フレーム中での制御信号と同様にドットクロック D C L K、ラッチパルス L P、極性信号 P O L が出力される。極性信号 P O L は、データドライバの出力極性を制御し、各ラインの極性信号 P O L はフレーム毎に反転されるようになっている。

20

#### 【0056】

なお、図 7 に示されたフレーム判定信号は、データイネーブル信号 E n a b の“L”期間が所定のドットクロック D C L K 数に達し、かつライン数が 1024 に達しているとき、つまりデータイネーブル信号 E n a b の入力数が 1024 個であるときにフレーム終了と判定させるために用いる信号である。データイネーブル信号 E n a b の数が少ないとときは内部タイミングで 1024 ラインまで動作させ、多いときはそのデータイネーブル信号 E n a b を無効とするようになっている。

30

#### 【0057】

また、図 7 に示すデータドライバ 16 から出力される階調データは、画素（RGB のサブピクセルをまとめたもの）表示が黒となるように設定されている。こうすることにより、垂直プランギング期間 V B に予備書き込みを行うラインの 1 フレーム平均輝度の変化を最小減に抑えることができる。黒表示にすると（予備書き込みデータの表示時間 / 1 垂直周期）の輝度低下が生じるだけであり、本実施例のドット反転駆動では、2 / 1030 となり目視上は全く問題ない。なお、予備書き込みのデータの極性は本データを書き込む際の極性と同じにする。

#### 【0058】

以上説明したように、本実施の形態によれば、タイミングコントローラの回路規模をそれ程多くせずに、画面全体の書き込み不足、特定ラインのムラをなくすことができるようになる。

40

#### 【0059】

本発明は、上記実施の形態に限らず種々の変形が可能である。

例えば、上記実施の形態では 2 ライン周期でデータラインの極性が変化するドット反転駆動を例にしているので、先頭のデータイネーブル信号 E n a b より 2 水平周期だけ手前から予備書き込みを開始するようにしている。例えば、2 ドット反転駆動において本発明を適用する場合には、4 ライン周期でデータラインの極性が変化するので、先頭のデータイネーブル信号 E n a b より 4 水平周期だけ手前から予備書き込みを開始すればよい。また、フレーム反転駆動において本発明を適用する場合には、1 フレーム期間において極性が同じなので、先頭のデータイネーブル信号 E n a b より 1 水平周期だけ手前から予備書き込みを開始すればよい。

#### 【0060】

50

次に、本発明の第2の実施の形態による液晶表示装置を図8乃至図14を用いて説明する。上記第1の実施の形態では、液晶表示装置の大画面化、高精細化で生じる画素電極へのデータの書き込み不足を改善するために、予備書き込み方式の駆動方法を用いることを前提としている。これに対し本実施の形態による液晶表示装置は、予備書き込み方式とは独立して実施することができる。但し、予備書き込み方式を併用することはもちろん可能である。

#### 【0061】

上記第1の実施の形態における図1及び図2に示した液晶表示装置において表示画素数の大規模化を実現しようとすると、ゲートバスライン2の微細化、配線本数の増大、配線長さの延長等が必要になり、ゲートバスライン2の抵抗や負荷容量を増大させてゲート遅延が生じる。ゲート遅延が顕著になると表示画面の左右方向で輝度ムラが生じてしまう。10

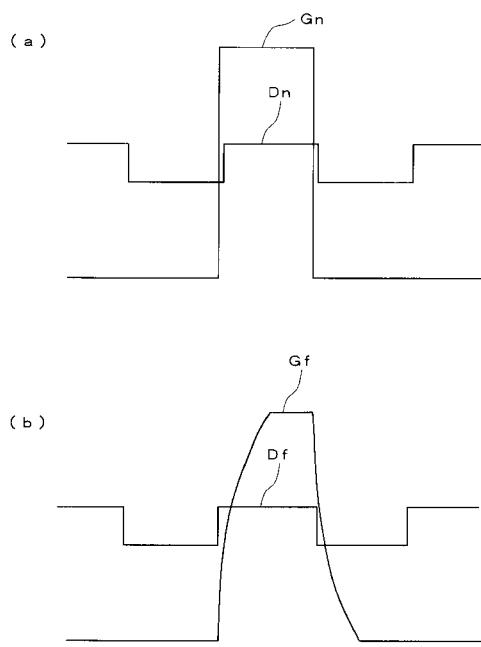

#### 【0062】

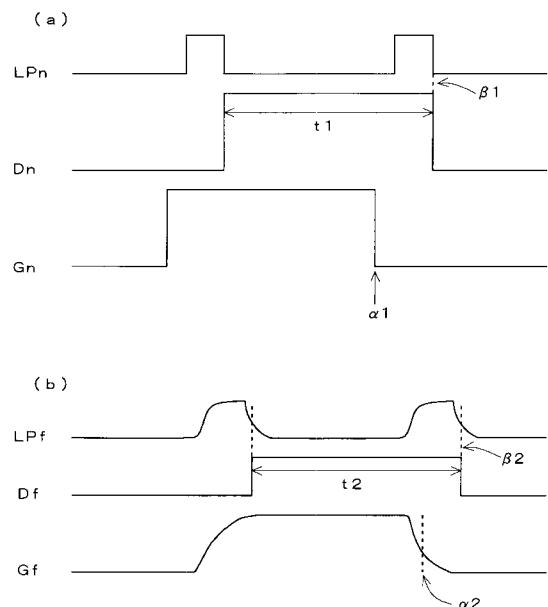

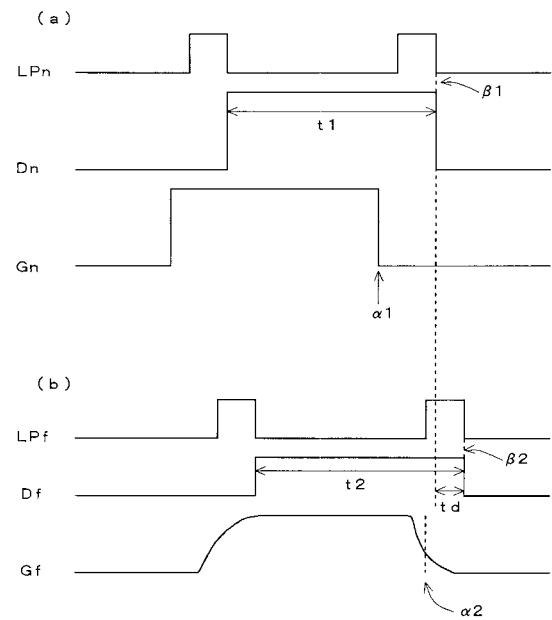

図8(a)は、図2に示したゲートバスライン2のゲートドライバ18側に近い位置にあるTFT6に入力するゲート信号Gnとデータ信号(階調信号)Dnを示している。横方向は時間を表し、縦方向は信号レベルを表している。図8(a)に示す状態はゲート遅延が生じていないので、ゲートバスライン2上のゲート信号Gnは矩形状である。このため、所定のデータ出力タイミングに従って、データ信号Dnがデータバスライン4に出力されている時間内にTFT6のゲートがオフになるので、正確にデータを画素電極8に書き込むことができる。

#### 【0063】

一方、図8(b)は、図2に示したゲートバスライン2のゲートドライバ18から離れた位置にあるTFT6に入力するゲート信号Gfとデータ信号Dfを示している。図8(b)に示す状態はゲート遅延が生じており、ゲートバスライン2上のゲート信号Gfは鈍っている。従って、データバスライン4に図8(a)に示すデータ信号Dnと同一のデータ出力タイミングでデータ信号Dfが出力されても、ゲート信号Gfの鈍りの分だけTFT6のゲートがオフになる時間が遅れてしまい、本来のデータ信号Dfのレベルと異なる不正確なデータを画素電極8に書き込んでしまう。このゲート信号Gfの鈍りによるTFT6のゲート・オフのタイミングは所定の1水平周期1Hより長くなり、ゲートドライバ18から遠ざかるにつれて顕著になる。20

#### 【0064】

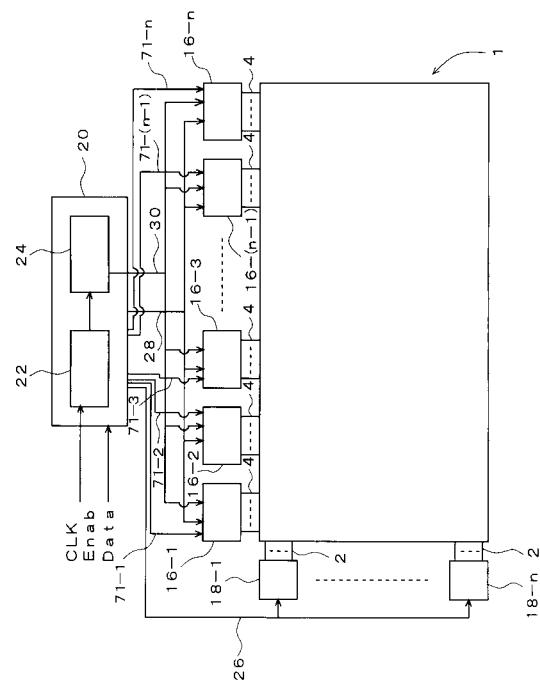

そこで本実施の形態では、図9に示す構成を採用して、ゲート信号に鈍りが生じても、データ信号を画素電極に十分書き込むことができるようになっている。図9は、本実施の形態による液晶表示装置の概略構成を示している。なお、本実施の形態において、第1の実施の形態で用いた図1及び図2に示す構成と同一の機能作用を奏する構成要素には同一の符号を付してその説明は省略する。30

#### 【0065】

図9に示すTFT-LCD1は、図1及び図2に示したTFT-LCDと比較して、ラッチパルス供給用ライン70が配線されている点に特徴を有している。ラッチパルス供給用ライン70は例えばゲートドライバ18-1から引き出され、図中最上方のゲートバスライン2のさらに上方にゲートバスライン2とほぼ平行に配線されている。そして、ラッチパルス供給用ライン70の途中から分岐した分岐ラインがデータドライバ16-1~16-nのそれぞれに配線されている。ラッチパルス供給用ライン70には、ゲートドライバ18-1及び制御線26を介してタイミングコントローラ20からラッチパルスLPが供給され、制御線30にはラッチパルスLP以外のドットクロックDCLK、極性信号POL、及びデータスタート信号DST等が出力される。40

#### 【0066】

従って、本実施の形態によるTFT-LCD1でのラッチパルスLPは、タイミングコントローラ20から制御線26及びゲートドライバ18-1を介してラッチパルス供給用ライン70に出力される。データドライバ16-1~16-nにはラッチパルス供給用ライン70nに接続された各分岐ラインから順次ラッチパルスLPが入力される。ラッチパル50

ス供給用ライン 7 0 の線幅及び長さはゲートバスライン 2 とほぼ同様でゲートバスライン 2 に平行に配線されている。従って、各データドライバ 1 6 - 1 ~ 1 6 - n に入力するラッチパルス L P に対してゲート鈍りと同様の波形鈍りを生じさせることができるようになる。

#### 【 0 0 6 7 】

図 1 0 ( a ) 上段は、ラッチパルス供給用ライン 7 0 からゲートドライバ 1 8 側に近い位置のデータドライバ 1 6 に入力するラッチパルス L P n を示している。図 1 0 ( a ) 中段は、図 1 0 ( a ) 上段のラッチパルス L P n の立ち下がりエッジに同期して出力されるデータ信号 D n を示している。また、図 1 0 ( a ) 下段は、ゲートバスライン 2 のゲートドライバ 1 8 側に近い位置にある T F T 6 に入力するゲート信号 G n を示している。横方向は時間を表し、縦方向は信号レベルを表している。図 1 0 ( a ) に示す状態では、ゲート遅延によるゲート鈍りは生じておらず、ラッチパルス L P n にも波形鈍りは生じていない。このラッチパルス L P n によりデータ信号 D n がデータバスライン 4 に出力されると、データ切り替わり時点(図中 1 で示す)手前のデータ信号 D n の出力期間 t 1 内に T F T 6 のゲートがオフになるため(図中 1 で示す)、正確にデータを画素電極 8 に書き込むことができる。10

#### 【 0 0 6 8 】

一方、図 1 0 ( b ) 上段は、ゲートドライバ 1 8 から離れた位置にあるデータドライバ 1 6 にラッチパルス供給用ライン 7 0 から入力するラッチパルス L P f を示している。図 1 0 ( b ) 中段は、図 1 0 ( b ) 上段のラッチパルス L P f により出力されるデータ信号 D f を示している。また、図 1 0 ( b ) 下段は、ゲートバスライン 2 のゲートドライバ 1 8 から離れた位置にある T F T 6 に入力するゲート信号 G f を示している。図 1 0 ( b ) に示す状態はゲート遅延が生じており、ゲートバスライン 2 上のゲート信号 G f は鈍っている。一方それに同期してラッチパルス L P f にも遅延が生じて波形が鈍っている。このため、遅延を生じているラッチパルス L P f に基づいて出力されるデータ信号 D f の出力タイミングにも遅れが生じる。データ信号 D f の出力が遅延することによりデータ信号 D n の切り替わり(図中 2 で示す)手前のデータ信号 D f の出力期間 t 2 内に T F T 6 のゲートがオフになるため(図中 2 で示す)、ゲート遅延が生じても正確にデータを画素電極 8 に書き込むことができる。20

#### 【 0 0 6 9 】

このように、ラッチパルス L P をゲート信号と同様にゲートドライバ 1 8 から液晶パネルに出力し、ゲート遅延によるゲート鈍りと同様の波形鈍りをラッチパルス L P に持たせて順次データドライバ 1 6 に入力することにより、ゲート鈍りに対応してデータ信号の出力をずらすことができるようになる。こうすることにより、高精細、大画面の液晶表示装置における表示ムラを解消して高画質で表示できるようになる。30

#### 【 0 0 7 0 】

次に、本実施の形態による液晶表示装置の変形例について図 1 1 乃至図 1 4 を用いて説明する。本変形例においても、データドライバ 1 6 全てから同時にデータ信号を出力させるのではなく、ゲート遅延によるゲート波形の鈍りに合わせてデータ信号の出力タイミングを順次ずらすようにしている。40

#### 【 0 0 7 1 】

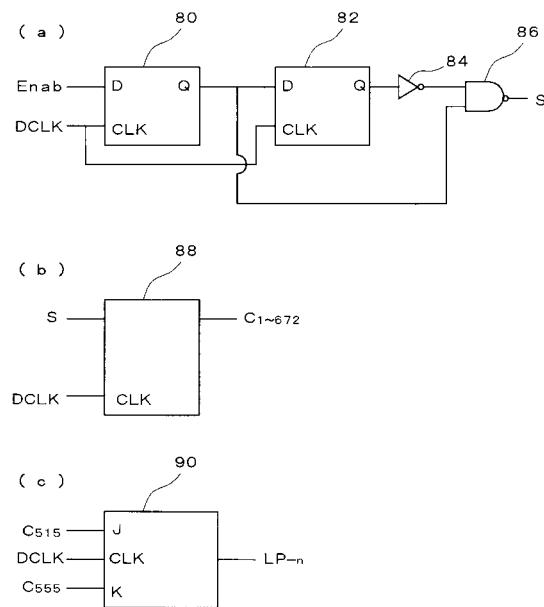

図 1 1 に示す T F T - L C D 1 は、図 9 に示した T F T - L C D 1 のラッチパルス供給用ライン 7 0 に代えて、データドライバ 1 6 - 1 ~ 1 6 - n のそれぞれにラッチパルス供給用ライン 7 1 - 1 ~ 7 1 - n が配線されている点に特徴を有している。ラッチパルス供給用ライン 7 1 - 1 ~ 7 1 - n には、タイミングコントローラ 2 0 内でゲート遅延に対応させて出力タイミングを順次ずらしたラッチパルス L P - 1 ~ L P - n がそれぞれ供給されるようになっている。従って、ゲート遅延に合わせてデータ信号を出力することができるようになる。

#### 【 0 0 7 2 】

図 1 2 及び図 1 3 を用いて、タイミングコントローラ 2 0 内に設けられたラッチパルス生50

成回路について説明する。図12はラッチパルス生成回路の概略の構成を示し、図13は当該回路中の各種信号のタイミングチャートを示している。図12(a)に示すようにラッチパルス生成回路は、入力端子にデータタイネーブル信号E<sub>nab</sub>が入力するDフリップフロップ(DFF)80を有している。データタイネーブル信号E<sub>nab</sub>は図13に示すように、信号E<sub>nab</sub>の“H(ハイ)”状態の期間は512ドットクロック数であり、“L”状態の期間は160ドットクロック数である。従って、データタイネーブル信号E<sub>nab</sub>の立ち上がりエッジから次の立ち上がりエッジまで672ドットクロック数ある。

#### 【0073】

図12に戻り、DFF80のクロック入力端子にはドットクロックDCLKが入力するようになっている。DFF80の出力端子は次段のDFF82の入力端子に接続されると共に、2入力NAND回路の一入力端子に接続されている。なお、DFF82のクロック入力端子にはドットクロックDCLKが入力するようになっている。DFF82の出力端子はインバータ84と接続され、インバータ84の出力端子は2入力NAND回路86の他入力端子に接続されている。このような構成によりNAND回路86の出力端子には、図13に示すようにデータタイネーブル信号E<sub>nab</sub>の立ち上がりエッジに同期して立ち下がるE<sub>nab</sub>検出信号Sが出力される。E<sub>nab</sub>検出信号Sは図12(b)に示すように、ドットクロックDCLKの数をカウントするカウンタ88に入力する。カウンタ88は、E<sub>nab</sub>検出信号Sの入力で毎にリセットされてドットクロックDCLKの数をカウントする。

#### 【0074】

カウンタ88から出力されるカウント値C1~672は図示しないデコーダに入力される。デコーダは所定のカウント値になるとJKFF90のJまたはK入力端子にパルスを出力するようになっている。例えば、カウント値がC515になるとJKFF90のJ入力端子にパルスを入力し、次いでカウント値がC555になるとK入力端子にパルスを入力する。このようにして、図13に示すように、データタイネーブル信号E<sub>nab</sub>の立ち上がりから次の立ち上がり、つまり1水平周期の515/672から555/672までの間にJKFF90の出力端子からラッチパルスLP-nを出力できるようになる。ゲート遅延に対応させてデコーダからJKFF90のJ、K入力端子へのパルス入力タイミングを制御することにより出力タイミングを順次ずらされたラッチパルスLP-1~LP-nを供給することができる。

#### 【0075】

図14(a)上段は、ラッチパルス供給用ライン71-1~71-nのうちゲートドライバ18側に近い位置のデータドライバ16に入力するラッチパルスLPnを示している。図14(a)中段は、図14(a)上段のラッチパルスLPnの立ち下がりエッジに同期して出力されるデータ信号Dnを示している。また、図14(a)下段は、ゲートバスライン2のゲートドライバ18側に近い位置にあるTFT6に入力するゲート信号Gnを示している。横方向は時間を表し、縦方向は信号レベルを表している。図14(a)に示す状態では、ゲート遅延によるゲート鈍りは生じておらず、ラッチパルスLPnにも波形鈍りは生じていない。このラッチパルスLPnによりデータ信号Dnがデータバスライン4に出力されると、データ切り替わり時点(図中1で示す)手前のデータ信号Dnの出力期間t1内にTFT6のゲートがオフになるため(図中1で示す)、正確にデータを画素電極8に書き込むことができる。

#### 【0076】

一方、図14(b)上段は、ラッチパルス供給用ライン71-1~71-nのうちゲートドライバ18から離れた位置にあるデータドライバ16に入力するラッチパルスLPfを示している。図14(b)中段は、図14(b)上段のラッチパルスLPfにより出力されるデータ信号Dfを示している。また、図14(b)下段は、ゲートバスライン2のゲートドライバ18から離れた位置にあるTFT6に入力するゲート信号Gfを示している。図14(b)に示す状態はゲート遅延が生じており、ゲートバスライン2上のゲート信号Gfは鈍っている。一方ゲート信号Gfの鈍りに対応させてラッチパルスLPfの出力

10

20

30

40

50

タイミングを時間  $t_d$ だけずらすことにより、出力されるデータ信号  $D_f$  の出力タイミングも時間  $t_d$ だけ遅らせることができる。データ信号  $D_f$  の出力が遅れることによりデータ信号  $D_n$  の切り替わり(図中 2で示す)手前のデータ信号  $D_f$  の出力期間  $t_2$ 内に TFT6 のゲートがオフになるため(図中 2で示す)、ゲート遅延が生じていても正確にデータを画素電極 8に書き込むことができる。

#### 【0077】

このように、ラッチパルス LP をデータドライバ 16 の数だけ分割して、それぞれのラッチパルス LP にゲート遅延に対応させた時間ずれを持たせることにより、ゲート鈍りに対応してデータ信号の出力をずらすことができるようになる。こうすることにより、高精細、大画面の液晶表示装置における表示ムラを解消して高画質で表示できるようになる。なお、ラッチパルス供給用ライン 71-1 ~ 71-n のそれぞれにコンデンサや抵抗を接続して信号の時間遅れを微調整できるようにしてもらちろんよい。

10

#### 【0078】

本発明は、上記実施の形態に限らず種々の変形が可能である。

例えば、上記第 2 の実施の形態ではゲート遅延による輝度ムラを防止させることを目的としているが、本発明はこれに限らず、例えば、画素欠陥修復に用いられるリペア配線において、長い配線長によるデータ遅延で生じる輝線の発生を防止することにも適用可能である。

#### 【0079】

データバスラインの欠陥を修復するためのリペア配線は、表示領域を挟んでデータドライバと対向する領域までゲートドライバ側基板を通って配線されている。このためリペア配線の配線長はデータバスラインよりかなり長い。従って、欠陥修復のためにリペア配線を用いると、リペア配線に出力されるデータ信号は遅延が生じて波形が鈍る。このデータ信号鈍りによりリペア配線でのデータ出力期間はデータバスラインのそれより長くなる。このため、ゲート遅延が生じている場合には、データバスラインよりリペア配線上の TFT に十分なデータ書き込みが行われるのでリペア配線に接続された画素の輝度が相対的に高くなってしまい輝線として視認される。これに対し、上記本発明の実施形態を利用することにより、リペア配線での輝線を目立たなくすることができますようになる。

20

#### 【0080】

#### 【発明の効果】

30

以上の通り、本発明によれば、システム側からのデータタイネーブル信号に基づいて垂直ブランкиング期間中に少なくとも第 1 ライン目の予備書き込みを最適に行うことができる。また、本発明によれば、ゲート信号に鈍りが生じても、データ信号を画素電極に十分書き込むことができるようになる。

#### 【図面の簡単な説明】

【図 1】本発明の第 1 の実施の形態による液晶表示装置の概略構成を示す図である。

【図 2】本発明の第 1 の実施の形態による表示駆動方法を利用した液晶表示装置の概略構成を示す図である。

【図 3】システム側から入力されるデータタイネーブル信号  $E_{nab}$  を説明する図である。

【図 4】本発明の第 1 の実施の形態による液晶表示装置の駆動方法における垂直周期  $V$  保持回路を示す図である。

40

【図 5】本発明の第 1 の実施の形態による液晶表示装置の駆動方法における減算回路を示す図である。

【図 6】本発明の第 1 の実施の形態による液晶表示装置の駆動方法における水平カウンタ 22 及び垂直カウンタ 24 の動作手順を主として説明する図である。

【図 7】本発明の第 1 の実施の形態による液晶表示装置の駆動方法を説明するタイミングチャートを示す図である。

【図 8】ゲート遅延について説明する図である。

【図 9】本発明の第 2 の実施の形態による液晶表示装置の概略構成を示す図である。

【図 10】本発明の第 2 の実施の形態による液晶表示装置の駆動方法を説明するタイミン

50

グチャートを示す図である。

【図11】本発明の第2の実施の形態の変形例に係る液晶表示装置の概略構成を示す図である。

【図12】本発明の第2の実施の形態の変形例に係る液晶表示装置のラッチパルス生成回路の概略構成を示す図である。

【図13】本発明の第2の実施の形態の変形例に係る液晶表示装置のラッチパルス生成回路の動作を示すタイミングチャートを示す図である。

【図14】本発明の第2の実施の形態の変形例に係る液晶表示装置の駆動方法を説明するタイミングチャートを示す図である。

【図15】従来の液晶表示装置の駆動方法を説明する図である。

10

【符号の説明】

|             |              |    |

|-------------|--------------|----|

| 1           | アレイ基板        |    |

| 2           | ゲートバスライン     |    |

| 4           | データバスライン     |    |

| 6           | TFT          |    |

| 8           | 画素電極         |    |

| 10          | 液晶           |    |

| 14          | 対向基板         |    |

| 16          | データドライバ      |    |

| 18          | ゲートドライバ      | 20 |

| 20          | タイミングコントローラ  |    |

| 22          | 水平カウンタ       |    |

| 26          | 信号線          |    |

| 24          | 垂直カウンタ       |    |

| 28、30       | 制御線          |    |

| 40、42、56    | インバータ        |    |

| 44、46、48、50 | AND回路        |    |

| 52、54       | KJFF         |    |

| 58、60       | NOR回路        |    |

| 62、64、66    | EXOR回路       | 30 |

| 70、71       | ラッチパルス供給用ライン |    |

| 80、82       | DFF          |    |

| 84          | インバータ        |    |

| 86          | NAND回路       |    |

| 88          | イネーブルカウンタ    |    |

| 90          | JKFF         |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【 図 6 】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(56)参考文献 特開平11-133922(JP,A)

特開昭62-269995(JP,A)

特開平11-142807(JP,A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/133

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 公开(公告)号        | <a href="#">JP4277148B2</a>                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2009-06-10 |

| 申请号            | JP2000001490                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2000-01-07 |

| [标]申请(专利权)人(译) | 富士通株式会社                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 富士通株式会社                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 当前申请(专利权)人(译)  | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 拔山和宏<br>形川晃一                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 发明人            | 拔山 和宏<br>形川 晃一                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| CPC分类号         | G09G3/3648 G09G3/3614 G09G2310/0251                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G02F1/133.550 G09G3/20.623.D G09G3/36                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA31 2H093/NA45 2H093/NB16 2H093/NC16 2H093/NC21 2H093/NC49 2H093/ND09 2H093/ND34 2H093/ND36 2H093/ND43 2H193/ZC26 2H193/ZD32 5C006/AA16 5C006/AC11 5C006/AC21 5C006/AF44 5C006/AF73 5C006/BB16 5C006/BC11 5C006/BF04 5C006/BF06 5C006/BF22 5C006/BF26 5C006/BF27 5C006/FA15 5C080/AA10 5C080/BB05 5C080/BB07 5C080/DD07 5C080/DD08 5C080/EE29 5C080/FF11 5C080/GG12 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ07 |         |            |

| 代理人(译)         | 盛冈正树                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 审查员(译)         | 铃木俊光                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | JP2001194644A                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

## 摘要(译)

要解决的问题：提供一种用于驱动液晶显示装置的方法，该方法能够基于来自系统侧的数据使能信号在垂直消隐期间优化第一线的预写。解决方案：该方法用于驱动液晶显示装置，其中基于数据使能信号Enab控制用于将灰度级数据输出到规定像素的输出定时，以便测量（步骤S2-S5）数据使能的周期。信号为水平周期；基于水平周期，在垂直消隐期间生成（步骤S6-S8）虚拟使能信号；保持（步骤S10）数据使能信号和虚拟使能信号之和作为垂直周期；并且至少在显示起始行上的像素中以比垂直周期短的定时执行灰度级数据的初步写入（步骤S11-S15），作为水平周期的整数倍。

| Q 2 | Q 3 | Q 4 | Q 5 |

|-----|-----|-----|-----|

| 0   | D 3 | D 4 | D 5 |

| 1   | 0   | D 4 | D 5 |

| 1   | 1   | 0   | D 5 |

| 1   | 1   | 1   | 0   |