(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-304613

(P2007-304613A)

(43) 公開日 平成19年11月22日(2007.11.22)

| (51) Int.CI.                | F 1       | テーマコード(参考) |

|-----------------------------|-----------|------------|

| <b>G09G 3/36 (2006.01)</b>  | G09G 3/36 | 2 H 093    |

| <b>G09G 3/20 (2006.01)</b>  | G09G 3/20 | 5 C 006    |

| <b>G02F 1/133 (2006.01)</b> | G09G 3/20 | 5 C 080    |

|                             | G09G 3/20 | 6 2 2 C    |

|                             | G09G 3/20 | 6 2 2 G    |

審査請求 有 請求項の数 14 O L (全 28 頁) 最終頁に続く

|              |                             |          |                                                                                    |

|--------------|-----------------------------|----------|------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2007-168308(P2007-168308) | (71) 出願人 | 599127667<br>エルジー フィリップス エルシーティー<br>カンパニー リミテッド<br>大韓民国 ソウル, ヨンドンポーク,<br>ヨイドードン 20 |

| (22) 出願日     | 平成19年6月27日(2007.6.27)       | (74) 代理人 | 100109726<br>弁理士 園田 吉隆                                                             |

| (62) 分割の表示   | 特願平11-264762の分割             | (74) 代理人 | 100101199<br>弁理士 小林 義教                                                             |

| 原出願日         | 平成11年9月20日(1999.9.20)       | (72) 発明者 | ヒュン チャン リー<br>大韓民国 キュンサンブクードー クミ市<br>ヒュンゴクードン 146 ブーングリ<br>ム アパート 101-603号         |

| (31) 優先権主張番号 | 1998-38842                  |          |                                                                                    |

| (32) 優先日     | 平成10年9月19日(1998.9.19)       |          |                                                                                    |

| (33) 優先権主張国  | 韓国(KR)                      |          |                                                                                    |

| (31) 優先権主張番号 | 1999-29144                  |          |                                                                                    |

| (32) 優先日     | 平成11年7月19日(1999.7.19)       |          |                                                                                    |

| (33) 優先権主張国  | 韓国(KR)                      |          |                                                                                    |

最終頁に続く

(54) 【発明の名称】アクティブマトリックス液晶表示装置

(57) 【要約】 (修正有)

【課題】アクティブマトリックス液晶表示装置のフリッカ及び残像を除去することと併せて回路構成を簡素化する。

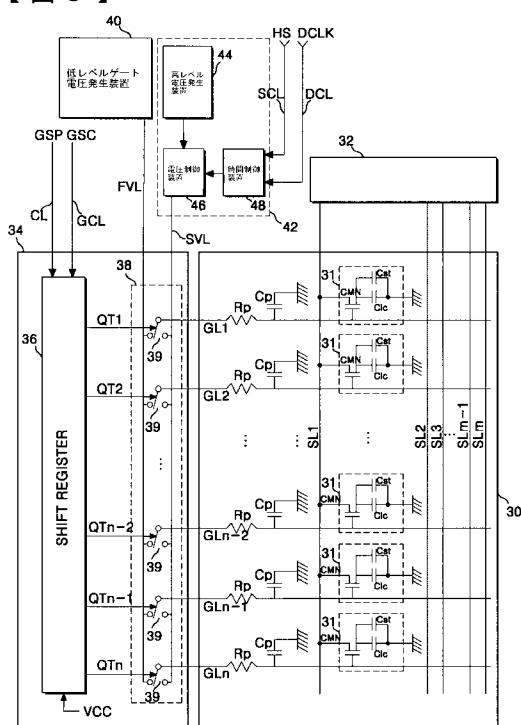

【解決手段】ゲートドライバ34はシフトレジスタ36と、レベルシフト38で構成され、レベルシフト38はシフトレジスタ36のn個の出力端子Q T 1 ~ Q T nとn個のゲートラインG L 1 ~ G L n間にそれぞれ接続されて第1及び第2電圧ラインF V L、S V Lからの低電位及び高電位ゲート電圧を切り換えるためのn個の制御用スイッチ39を具備する。高電位ゲート電圧発生器42は、高電位電圧発生器44と電圧調節器46、及び電圧調節器46のレベル調整タイミングを制御するためのタイミング制御器48で構成され、漸進的に緩やかに変化する立下がり部を有する高電位ゲート電圧を第2電圧ラインS V Lに供給する。これにより液晶パネル30のゲートラインG Lに供給されるスキャニング信号の立下がり部が緩やかに変化する。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

ゲート電極及び第1電極と画素電極に接続された第2電極を有するスイッチトランジスタをそれぞれ含むこととともにマトリックス形態で配列された多数の画素と；

前記多数のトランジスタの中の一つに対応する前記第1電極にそれぞれ接続された多数のデータ信号ラインと；

前記多数のトランジスタの中の一つに対応する前記ゲート電極に接続された多数のゲート信号ラインと；

前記多数のゲート信号ラインと接続されて、第1及び第2電圧を入力して、前記ゲート信号ラインが順次的に駆動するように前記第1及び第2電圧の中のいずれかの一つを出力するゲートドライバとを具備するアクティブマトリックス液晶表示装置において；

前記ゲートドライバは、前記ゲートラインそれぞれに供給されるスキヤニング信号を発生するシフトレジスタと、前記第1及び第2電圧を利用して前記シフトレジスタからのスキヤニング信号それぞれの電圧レベルをシフトさせるレベルシフトと、前記レベルシフトに供給される第1電圧を前記スキヤニング信号が使用不可能にされる前に変化させる電圧調節器とを具備し、

前記第1電圧が連続されたゲート信号ラインが活性化される前に降下し、前記第1電圧の最小値が前記第2電圧の最大値より高い、ことを特徴とするアクティブマトリックス液晶表示装置。

**【請求項 2】**

前記電圧調節器は、前記スキヤニング信号が使用不可能にされる前に前記レベルシフトに供給される前記第1電圧を遮断するためのスイッチと、前記スイッチによって前記スキヤニング信号が遮断される間前記レベルシフトに提供される放電通路とを具備することを特徴とする請求項1記載のアクティブマトリックス液晶表示装置。

**【請求項 3】**

前記スイッチが前記シフトレジスタとともにゲートスキヤンクロックに応答することを特徴とする請求項2記載のアクティブマトリックス液晶表示装置。

**【請求項 4】**

前記スイッチを制御するためのタイミング制御器とを追加で具備することを特徴とする請求項2記載のアクティブマトリックス液晶表示装置。

**【請求項 5】**

前記電圧調節器が、第1電圧を入力するための入力端子と、前記入力端子と前記レベルシフトの入力端子の間に接続された第1抵抗と、前記レベルシフトの入力端子と基底電圧ラインの間に直列接続された第2抵抗及び第1制御用のスイッチと、前記第1抵抗と並列接続されて前記第1制御用のスイッチと相互補完的に駆動される第2制御用のスイッチとを具備することを特徴とする請求項1記載のアクティブマトリックス液晶表示装置。

**【請求項 6】**

前記シフトレジスタ及び前記レベルシフトが一つの集積回路のチップで製作されたことを特徴とする請求項1記載のアクティブマトリックス液晶表示装置。

**【請求項 7】**

前記シフトレジスタ、前記レベルシフト及び前記電圧調節器が一つの集積回路のチップで製作されたことを特徴とする請求項1記載のアクティブマトリックス液晶表示装置。

**【請求項 8】**

ゲート電極及び第1電極と画素電極に接続された第2電極を有するスイッチトランジスタをそれぞれ含むこととともにマトリックス形態で配列された多数の画素と；

前記多数のトランジスタの中の一つに対応する前記第1電極にそれぞれ接続された多数のデータ信号ラインと；

前記多数のトランジスタの中の一つに対応する前記ゲート電極に接続された多数のゲート信号ラインと；

前記多数のゲート信号ラインと接続されて、第1電圧及び第1電圧より低い第2電圧を

10

20

30

40

50

入力して、前記ゲート信号ラインが順次的に駆動するように前記第1及び第2電圧の中のいずれかの一つを出力するゲートドライバとを具備するアクティブマトリックス液晶表示装置において、

第1電圧を発生する高電位ゲート電圧発生回路と第2電圧を発生する低電位ゲート電圧発生回路とを具備し、

前記ゲートドライバは、ゲートスキャニングクロック信号を受け、前記ゲート信号ラインそれぞれに供給されるスキャニング信号を発生するシフトレジスタと、前記シフトレジスタからのスキャニング信号それぞれの電圧レベルを受けて第1及び第2電圧のいずれか一方を出力させる第1制御スイッチとを有し、

前記高電位ゲート電圧発生回路は第1高電位電圧を発生する高電位電圧発生回路と電圧調節回路とを有し、

前記電圧調節回路は、第2制御スイッチであって、前記ゲートスキャニングクロック信号レベルに依存して第1高電位電圧と第1高電位電圧より低電圧であるが第2電圧よりも高電圧である第2高電位電圧とのいずれか一方を出力させるように接続して第1電圧を出力するが、第1制御スイッチによって出力させる電圧が第1電圧から第2電圧へ切り替わる前には、出力する第1電圧を第1高電位電圧から第2高電位電圧に変化するように接続する第2制御スイッチを有することを特徴とする、アクティブマトリックス液晶表示装置。

#### 【請求項9】

第2高電位電圧が接地電位であることを特徴とする、請求項8記載のアクティブマトリックス液晶表示装置。

#### 【請求項10】

寄生容量、寄生抵抗のため、前記ゲート信号ラインの前記ゲート電極においては、第1高電位電圧から第2高電位電圧へ向かって徐々に変化することを特徴とする、請求項8または9に記載のアクティブマトリックス液晶表示装置。

#### 【請求項11】

第2制御スイッチが第2高電位電圧を出力させると、第2高電位電圧を抵抗素子を介して出力させることを特徴とする請求項8ないし10の何れか1項記載のアクティブマトリックス液晶表示装置。

#### 【請求項12】

第2制御スイッチが第2高電位電圧を出力させると、第2高電位電圧を前記ゲートスキャニングクロック信号によって起動されたTFTを介して出力させることを特徴とする請求項8ないし10の何れか1項記載のアクティブマトリックス液晶表示装置。

#### 【請求項13】

前記電圧調節回路が前記ゲートスキャニングクロック信号の反転信号を受けることを特徴とする、請求項8ないし11の何れか1項記載のアクティブマトリックス液晶表示装置。

#### 【請求項14】

前記高電位電圧発生回路がさらに、第2高電位電圧を発生することを特徴とする請求項8記載のアクティブマトリックス液晶表示装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明はアクティブマトリックス液晶表示装置に関し、特に液晶で構成された画素に接続されたトランジスタにゲートパルスを供給する手段を具備するアクティブマトリックス液晶表示装置に関する。

#### 【背景技術】

#### 【0002】

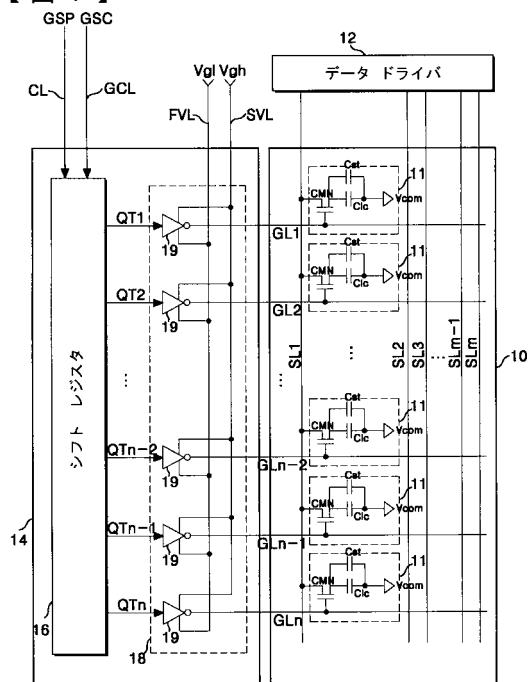

通常のアクティブマトリックス液晶表示装置は電界を利用して液晶の光透過率を調節することで画像を表示する。このような液晶表示装置は図1に図示されたように液晶パネル(

10

20

30

40

50

10 ) 上の信号ライン ( S L 1 乃至 S L m ) を駆動するデータドライバ ( 12 ) と、液晶パネル ( 10 ) 上のゲートライン ( G L 1 乃至 G L n ) を駆動するためのゲートドライバ ( 14 ) とを具備する。液晶パネル ( 10 ) には信号ライン ( S L ) 及びゲートライン ( G L ) に接続される画素 ( 11 ) がアクティブマトリックス形態で配列される。画素 ( 11 ) それぞれは信号ライン ( S L ) からのデータ電圧信号 ( D V S ) に応答して透過光量を調節する液晶セル ( C 1 c ) と、ゲートライン ( G L ) からのスキャニング信号 ( S C S ) に応答して信号ライン ( S L ) から液晶セル ( C 1 c ) に供給されるデータ電圧信号 ( D V S ) を切り換える薄膜トランジスタ ( 以下 TFT という ) ( C M N ) で構成される。データドライバ ( 12 ) はゲートライン ( G L 1 乃至 G L n ) が順次的に駆動されることによって信号ライン ( S L 1 乃至 S L m ) すべてにデータ電圧信号 ( D V S ) を供給する。一方、ゲートドライバ ( 14 ) はスキャニング信号 ( S C S ) をゲートライン ( G L 1 乃至 G L n ) に順次的に供給することでゲートライン ( G L 1 乃至 G L n ) が水平同期期間ずつ順次駆動される。このために、制御ライン ( C L ) からのゲートスタートパルス ( G S P ) 及びゲートクロックライン ( G C L ) からのゲートスキャニングクロック ( G S L ) からのゲートスキャニングクロック ( G S L ) に応答するシフトレジスタ ( 16 ) と、シフトレジスタ ( 16 ) とゲートライン ( G L 1 乃至 G L n ) の間に接続されたレベルシフト ( 18 ) で構成される。シフトレジスタ ( 16 ) は制御ライン ( C L ) からのゲートスタートパルス ( G S P ) を n 個の出力端子 ( Q T 1 乃至 Q T n ) の中のいずれか一つの出力端子側に出力することと併せてゲートスキャニングクロック ( G S C ) に応答してゲートスタートパルス ( G S P ) を第 1 出力端子 ( Q T 1 ) から第 n 出力端子 ( Q T n ) 側に順次的に移動させる。レベルシフト ( 18 ) はシフトレジスタ ( 16 ) の出力信号の電圧レベルをシフトさせることで n 個のスキャニング信号 ( S C S ) が発生させる。このために、レベルシフト ( 18 ) はシフトレジスタ ( 16 ) の n 個の出力端子 ( Q T 1 乃至 Q T n ) と n 個のゲートライン ( G L ) の間にそれぞれ接続されることと併せて第 1 及び第 2 電圧ライン ( F V L 、 S V L ) からの直流形態の低電位及び高電位電圧 ( V g 1 、 V g h ) の供給を受ける n 個のインバータ ( 19 ) で構成される。インバータ ( 19 ) はシフトレジスタ ( 16 ) の出力端子 ( Q T ) からの論理状態によって低電位及び高電位電圧 ( V g 1 、 V g h ) の中のいずれか一つを選択的にゲートライン ( G L ) に供給する。これによって、 n 個のスキャニング信号 ( S C S ) の中のいずれ一つだけが高電位ゲート電圧 ( V g h ) を有する。この高電位ゲート電圧 ( V g h ) を有するスキャニング信号 ( S C S ) をゲートライン ( G L ) から供給されると TFT ( C M N ) が起動 ( Turn-0 n ) され、 TFT ( C M N ) が起動される期間中液晶セル ( C 1 c ) はデータ電圧信号 ( D V S ) を充電する。このように液晶セル ( C 1 c ) に充電された電圧は TFT ( C M N ) が起動 ( Turn-On ) される時には下がるのでデータ電圧信号 ( D V S ) の電圧より低くなる。液晶セルに充電された電圧とデータ電圧信号 ( D V S ) との電位差に該当するフィードスルー電圧 ( Feed through Voltage 、 V p ) が発生する。このフィードスルー電圧 ( V p ) は TFT ( C M N ) のゲート端子と液晶セル ( C 1 c ) の間に存在する寄生容量によって発生することで液晶セル ( C 1 c ) の光透過量を周期的に変化させる。この結果、液晶パネル上に表示される画素でフリッカ及び残像が発生する。

## 【 0 0 0 3 】

このようなフィードスルー電圧 ( V p ) を抑制するための方法として、補助容量 ( C s t ) が図 1 でのように液晶セル ( C 1 c ) に並列に接続する。この補助容量 ( C s t ) は TFT ( C M N ) がターンオフされるときに減少する液晶セル電圧を補充することでフィードスルー電圧 ( V p ) が数 1 のように抑圧される。

10

20

30

40

【数1】

$$(V_{on} - V_{off}) \cdot Cgs$$

$$\Delta V_p = \frac{C_{lc} + C_{st} + Cgs}{C_{lc} + C_{st} + Cgs}$$

10

式1において、 $V_{on}$ はTFT(CMN)の起動時のゲートライン(GL)上の電圧であり、 $V_{off}$ はTFT(CMN)のターンオフ時のゲートライン(GL)上の電圧であり、 $Cgs$ はTFT(CMN)のゲート端子と液晶セルの間に存在する寄生容量の容量である。式1のように、フィードスルーレ電圧( $V_p$ )はTFT(CMN)の起動及びターンオフの時のゲートライン(GL)上の電圧差にしたがって大きくなる。このようなフィードスルーレ電圧( $V_p$ )を充分に抑圧するためには補助容量( $Cst$ )の容量が大きくならなければならない。これは表示領域の開口率(Aperture Ratio)が小さくなるので充分な表示コントラストが得られなくなる。これによって、補助容量( $Cst$ )によってはフィードスルーレ電圧( $V_p$ )を充分に抑圧することができない。

20

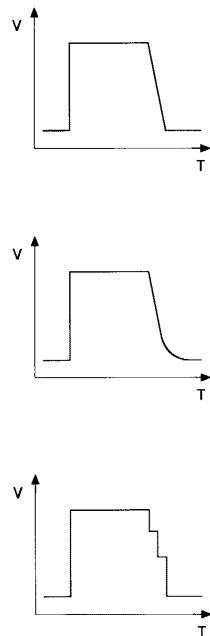

【0004】

フィードスルーレ電圧( $V_p$ )を抑制するための方法として、スキャニング信号(SCS)の立下がり部を緩やかにするスキャニング信号制御方式の液晶表示装置が提案されている。スキャニング信号制御方式の液晶表示装置では、スキャニング信号(SCS)の立下がり部が図2aのように線形関数、図2bでののような指數関数、または図2cでのような階段関数形態で変化する。このようなスキャニング信号制御方式の液晶表示装置は特開平6-110035号及び特開平9-258174号とアメリカ特許第5,587,722号に開示されている。しかし、これらのスキャニング信号制御方式の液晶表示装置ではゲートドライバの回路変形またはゲートドライバと液晶パネル上の各ゲートラインとの間に位置される新しい波形変形回路が必要である。また、アメリカ特許第5,587,722号に開示されたゲートドライバはスキャニング信号の立下がり部をステップワイズ(Step wise)するようにする機能を有する回路が一つのゲートドライバチップ内に形成されるので回路が複雑になり更に電力消費が大きい。

30

【0005】

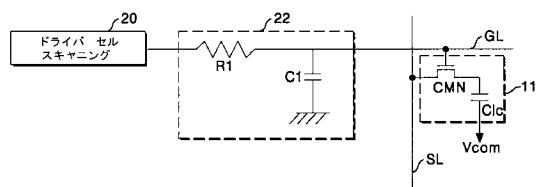

実際に、特開平6-110035号に開示されたスキャニング信号制御方式の液晶表示装置は図3に示したようにスキャニングドライバセル(20)とゲートライン(GL)の間に接続された積分器(22)を有する。積分器(22)はスキャニングドライバセル(20)とゲートライン(GL)の間に接続された抵抗(R1)と、ゲートライン(GL)及び基底電圧ライン(GVL)の間に接続された容量(C1)で構成される。このように構成された積分器(22)はゲートドライバセル(20)からゲートライン(GL)側に供給されるスキャニング信号を積分することでスキャニング信号(SCS)の立下がり部が指數関数的に変化する。画素(11)に含まれたTFT(CMN)はゲートライン(GL)からのスキャニング信号(SCS)の電圧が自分の臨界電圧以下に下がるときまで起動される。この時、液晶セル(C1c)に充電された電荷が寄生容量(Cgs)を経由してゲートライン(GL)側にポンピングされるので電荷量は極めて少なくなる。この結果、フィードスルーレ電圧( $V_p$ )が充分に抑圧される。

40

【特許文献1】特開平6-110035号公報

【特許文献2】特開平9-258174号公報

【特許文献3】米国特許第5,587,722号明細書

【発明の開示】

50

**【発明が解決しようとする課題】**

**【0006】**

以上のようなスキャニング信号制御方式の液晶表示装置では、フィードスルーレ電圧( $V_p$ )が充分に抑圧されることでフリッカ及び残像が著しく減るが、各ゲートライン毎に積分器のような波形変形回路が付加されなければならないので回路構成が大変複雑になる。これと併せて、波形変形回路によってスキャニング信号の立上がり部までの緩やかに変化するので液晶セルの充電開始の時点が遅延される。

**【0007】**

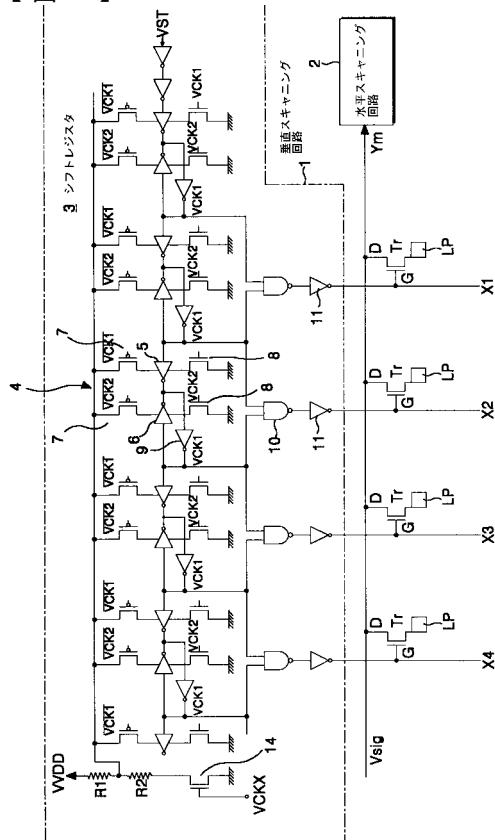

一方、アメリカ特許第5,587,722号は図4に図示されたように電源供給電圧( $V_{VDD}$ 及び $V_{VDD} \cdot R_1 / (R_1 + R_2)$ )を選択的に入力するシフトレジスタ(3)を開示する。シフトレジスタ(3)は電源供給電圧( $V_{VDD}$ 及び $V_{VDD} \cdot R_1 / (R_1 + R_2)$ )に応答して階段形パルスを発生する。しかし、シフトレジスタ(3)は電源供給電圧が液晶パネル上のゲートラインに供給される高レベルゲート電圧と同じなので高電圧で駆動されなければならない。即ち、シフトレジスタに含まれるインバータ(5、6、9)がTFTを起動させるための最大電圧が2.5Vである場合に大略25Vの駆動電圧で動作する。これによって、アメリカ特許第5,587,722号に開示されたアクティブマトリックス液晶表示装置は大電力を消耗する。

**【0008】**

従って、本発明の目的はフリッカ及び残像を除去することと併せて回路構成を簡素化するのに適合したアクティブマトリックス液晶表示装置及びその駆動方法を提供することにある。

**【課題を解決するための手段】**

**【0009】**

前記目的を達成するために、本発明によるアクティブマトリックス液晶表示装置はゲート電極及び第1電極と画素電極に接続された第2電極を有するスイッチトランジスタをそれぞれ含むこととともにマトリックス形態で配列された多数の画素と；多数のトランジスタの中の一つに対応する第1電極にそれぞれ接続される多数のデータ信号ラインと；多数のトランジスタの中の一つに対応するゲート電極に接続された多数のゲート信号ラインと；多数のゲート信号ラインと接続されて、第1及び第2電圧を入力して、そしてゲート信号ラインが順次駆動されるように第1及び第2電圧の中のいずれかの一つを出力するゲートドライバとを具備する。第1電圧が連続されたゲート信号ラインが活性化される前に変化する。

**【0010】**

本発明によるアクティブマトリックス液晶表示装置の駆動方法は第1電圧と周期的に変化する第2電圧を入力する段階と；スイッチ素子を経由してゲートラインに第2電圧を供給する段階と；スイッチを経由してゲートラインに前記第1電圧を供給する段階を含む。スイッチ素子はシフトレジスタによって制御されて併せて第2電圧の最小値が前記第1電圧の最大値より高く設定される。

**【発明の効果】**

**【0011】**

前記の構成によって、本発明によるアクティブマトリックス液晶表示装置ではゲートドライバのレベルシフトに高電位ゲート電圧が交流形態で供給されることでスキャニング信号の立下がり部が線形、指数または階段関数の中のいずれか一つの形態で変化する。これによって、本発明によるアクティブマトリックス液晶表示装置ではフィードスルーレ電圧( $V_p$ )が充分に抑圧されるようになり、更にフリッカ及び残像が発生しなくなる。併せて、本発明によるアクティブマトリックス液晶表示装置では高電位ゲート電圧の立下がり部が立上がり部より緩やかに変化することでゲートラインに供給されるスキャニング信号の立下がり部が立上がり部より緩やかに変化する。これによって、本発明によるアクティブマトリックス液晶表示装置ではフリッカ及び残像が発生されなくなることは勿論であり応答速度が早くなる。

10

20

30

40

50

## 【0012】

本発明によるアクティブマトリックス液晶表示装置は、ゲートドライバのレベルシフトに高電位ゲート電圧を交流形態で供給することでスキャニング信号の立下がり部が線形、指數または階段関数の中のいずれか一つの形態で変化する。これによって、本発明によるアクティブマトリックス液晶表示装置ではフィードスルー電圧( $V_p$ )を充分に抑圧し、さらにフリッカ及び残像の発生を抑制する。さらに、本発明によるアクティブマトリックス液晶表示装置では回路構成が極めて簡素化される。

## 【0013】

また、本発明によるアクティブマトリックス液晶表示装置は、高電位ゲート電圧の立下がり部が立上がり部より緩やかに変化することでゲートラインに供給されるスキャニング信号の立下がり部が立上がり部より緩やかに変化する。これによって、本発明によるアクティブマトリックス液晶表示装置では、フリッカ及び残像が発生しなくなることは勿論であり、さらに応答速度が早くなる。10

## 【発明を実施するための最良の形態】

## 【0014】

以下、本発明の実施例を添付した図5乃至図26を参照して詳細に説明する。

## 【実施例1】

## 【0015】

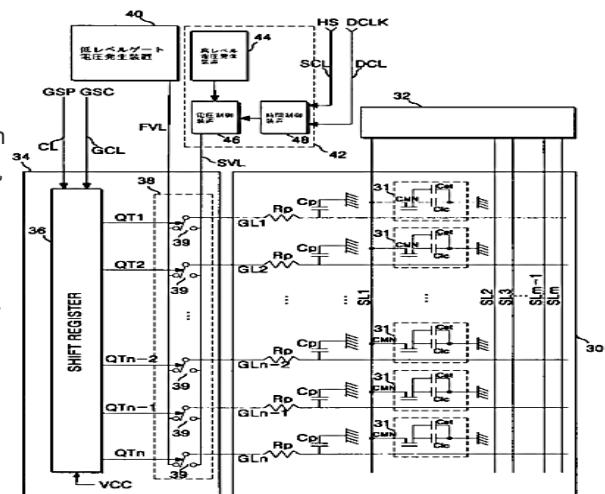

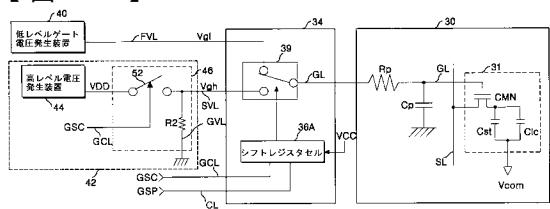

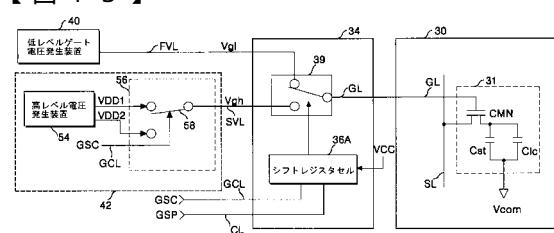

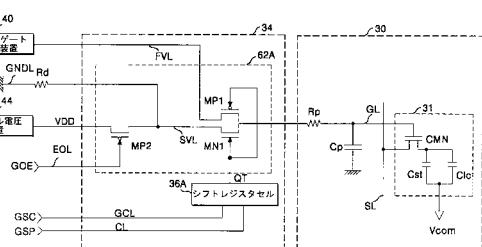

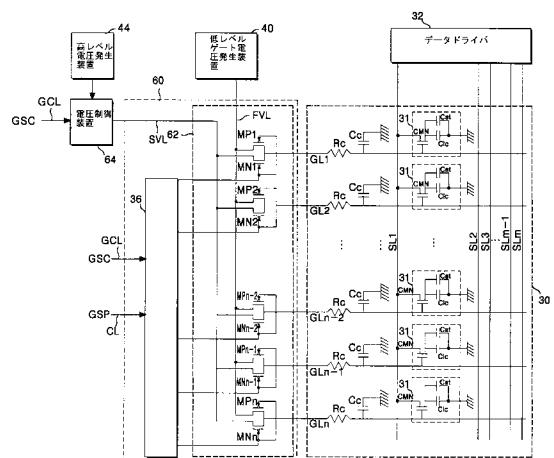

図5を参照すると、液晶パネル(30)上の信号ライン(SL1乃至SLm)を駆動するデータドライバ(32)と、液晶パネル(30)上のゲートライン(GL1乃至GLn)を駆動するためのゲートドライバ(34)とを具備する本発明の第1実施例によるアクティブマトリックス液晶表示装置が図示されている。液晶パネル(30)では信号ライン(SL)及びゲートライン(GL)に接続される画素(31)がアクティブマトリックス形態で配列される。画素(31)それぞれは信号ライン(SL)からのデータ電圧信号(DVS)に応答して透過光量を調節する液晶セル(CLc)と、ゲートライン(GL)からのスキャニング信号(SCS)に応答して信号ライン(SL)から液晶セル(CLc)に供給されるデータ電圧信号(DVS)を切り換えるTFT(CMN)で構成される。また、画素(31)それぞれでは補助容量(Cst)が液晶セル(CLc)に並列に接続される。この補助容量(Cst)は液晶セル(CLc)に充電された電圧を緩衝する。データドライバ(32)はゲートライン(GL1乃至GLn)すべてにデータ電圧信号(DVS)を供給する。ゲートドライバ(34)がスキャニング信号(SCS)をゲートライン(GL1乃至GLn)に順次供給することでゲートライン(GL1乃至GLn)が水平同期期間ずつ順次使用可能にされる。このために、ゲートドライバ(34)は制御ライン(CL)からのゲートスタートパルス(GSP)及びゲートクロックライン(GCL)からのゲートスキャニングクロック(GSC)に応答するシフトレジスタ(36)と、シフトレジスタ(36)とゲートライン(GL1乃至GLn)の間に接続されたレベルシフト(38)で構成される。シフトレジスタ(36)は制御ライン(CL)からのゲートスタートパルス(GSP)をn個の出力端子(QT1乃至QTn)の中のいずれか一つの出力端子側に出力されることと併せてゲートスキャニングクロック(GSC)に応答してゲートスタートパルス(GSP)を第1出力端子(QT1)から第n出力端子(QTn)側に順次移動させる。また、シフトレジスタ(36)はロジック電圧レベルに該当する5Vを有する集積回路駆動電圧で動作する。レベルシフトレジスタ(36)のn個の出力端子(QT1乃至QTn)とn個のゲートライン(GL)間にそれぞれ接続されることと併せて第1及び第2電圧ライン(FVL、SVL)からの低電位及び高電位ゲート電圧(Vg1、Vgh)を切り換えるためのn個の制御用スイッチ(39)とを具備する。制御用スイッチ(39)はシフトレジスタ(36)の出力端子(QT)からの論理状態によって低電位及び高電位ゲート電圧(Vg1、Vgh)の中のいずれか一つを選択的にゲートライン(GL)に供給する。これによって、n個のスキャニング信号(SCS)の中のいずれか一つだけが高電位ゲート電圧(Vgh)を有する。この高電位ゲート電圧(Vgh)が印可されるゲートライン(GL)上のTFT(CMN)が起動(Turn-On)されるようにな20304050

なり、TFT(CMN)が起動される期間の間液晶セル(Cl c)はデータ電圧信号(DVS)を充電する。制御用スイッチ(39)それぞれは低電位及び高電位ゲート電圧(Vg1、Vgh)を動作電圧とするバーパと対置されることもある。

#### 【0016】

また、本発明の第1実施例による液晶表示装置は第1電圧ライン(FVL)に接続された低電位ゲート電圧発生器(40)と、高電位ゲート電圧発生器(42)とを追加で具備する。低電位ゲート電圧発生器(40)は電圧レベルが一定に維持される低電位ゲート電圧(Vg1)を発生して第1電圧ライン(FVL)に接続されたn個の制御用スイッチ(39)に供給する。低電位ゲート電圧発生器(40)で発生される低電位ゲート電圧(Vg1)は一定の周期のパルス信号のような交流信号の形態を有することもある。高電位ゲート電圧発生器(42)は交流信号のように水平同期信号の周期毎に一定の形態で変化する高電位ゲート電圧(Vgh)を発生する。この高電位ゲート電圧(Vgh)は漸進的に緩やかに変化する立下がり部を有する。高電位ゲート電圧(Vgh)の立下がり部は線形関数の形態で変化するか、指数関数の形態で変化するか、または階段関数の形態で変化する。このような高電位ゲート電圧(Vgh)を発生するために、高電位ゲート電圧発生器(42)は高電位電圧(VDD)を発生する高電位電圧発生器(44)と、高電位電圧発生器(44)及び第2電圧ライン(SVL)の間に接続された電圧調節器(46)と、電圧調節器(46)のレベル調整タイミングを制御するためのタイミング制御器(48)で構成される。高電位電圧発生器(44)は一定の電圧レベルを安定されるように維持する直流形態の高電位電圧(VDD)を電圧調節器(46)に供給する。電圧調節器(46)は高電位電圧(VDD)を第2電圧ライン(SVL)に接続されたn個の制御用スイッチ(39)側に周期的に伝送することと併せて高電位電圧(VDD)が遮断される時に第2電圧ライン(SVL)に供給される電圧が上に言及された関数形態のいずれか一つの形態で低くなる。第2電圧ライン(SVL)上の電圧信号の立下がり部を緩やかに変化させるために、電圧調節器(46)は液晶パネル(30)のゲートライン(GL)に存在する寄生抵抗(Rp)及び寄生容量(Cp)を利用することもできる。タイミング制御器(48)は同期制御ライン(SCL)からの水平同期信号(HS)とデータクロックライン(DCL)からのデータクロック(DCLK)に応答して電圧調節器(46)の電圧切り換え時点と電圧調節時点を決定する。このために、タイミング制御器(48)は水平同期信号(HS)によって初期化されることと併せてデータクロック(DCLK)をカウンターするカウンター(図示しない)と、このカウンターの出力信号を論理組み合わせすることで電圧調節器(46)を制御する論理組み合わせ部(図示しない)で構成されることがある。

#### 【0017】

このように、第2電圧ライン(SVL)上の高電位ゲート電圧(Vgh)が交流形態で変化することと併せて緩やかに減少される立下がり部を有するなることで液晶パネル(30)のゲートライン(GL)に供給されるスキャニング信号(SCS)の立下がり部が緩やかに変化する。画素(31)に含まれたTFT(CMN)はゲートライン(GL)からのスキャニング信号(SCS)の電圧が自分の臨界電圧以下に下がるまで起動される。この時、液晶セル(Cl c)に充電された電荷がゲートライン(GL)側に流れる供給されたり信号ライン(SL)からTFT(CMN)を経由するデータ電圧信号(DVS)によって充分な電荷が液晶セル(Cl c)に充電される。これによって、液晶セル(Cl c)に充電された電圧は下がらなくなる。ゲートライン(GL)上のスキャニング信号(SCS)の電圧がTFT(CMN)の臨界電圧以下まで下がる場合にゲートライン(GL)からゲートライン(GL)での電圧変動量が最大TFT(CMN)の臨界電圧であるので液晶セル(Cl c)からゲートライン(GL)側に流れる電荷量は極めて少なくなる。この結果、フィードスルー電圧(Vp)が充分に抑圧される。

#### 【実施例2】

#### 【0018】

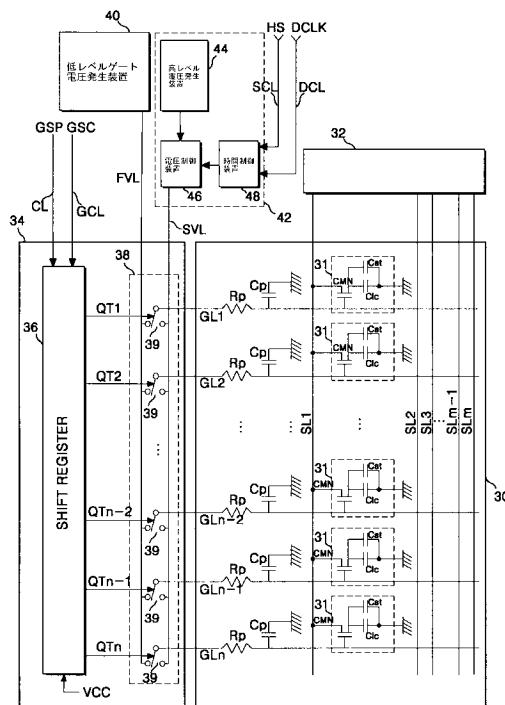

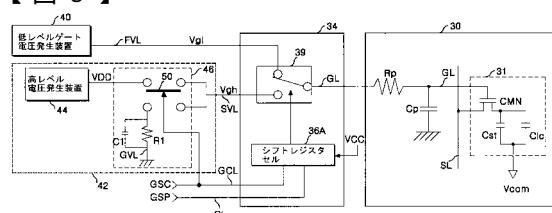

図6は本発明の第2実施例によるアクティブマトリックス液晶表示装置を概略的に図示する。図6のアクティブマトリックス液晶表示装置では電圧調節器(46)が液晶パネル(

10

20

30

40

50

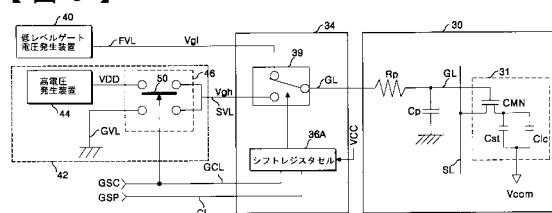

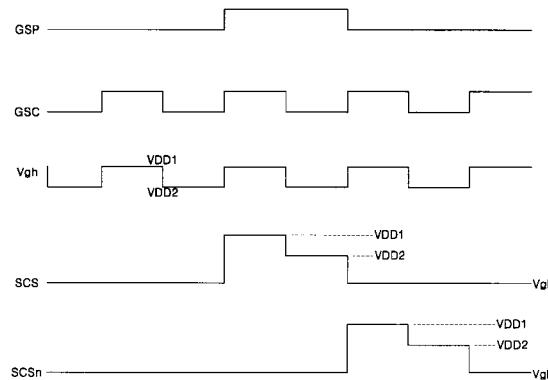

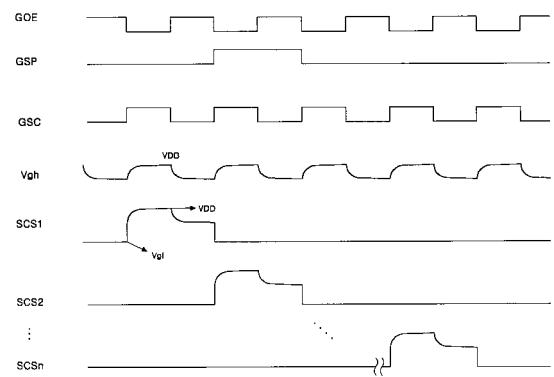

30) のゲートライン (G L) の寄生抵抗 (R p) 及び寄生容量 (C p) を利用して高電位ゲート電圧 (V g h) の立下がり部とスキャニング信号 (S C S) の立下がり部を指数電位ゲート電圧 (V g h) の立下がり部とスキャニング信号 (S C S) の立下がり部を指數関数形態で変化させる。図6の液晶表示装置では、液晶パネル (30) 上のゲートライン (G L) を駆動するためのゲートドライバ (34) が含まれる。液晶パネル (30) は信号ライン (S L) 及びゲートライン (G L) との接続に位置する画素 (31) を含む。画素 (31) は信号ライン (S L) からのデータ電圧信号 (D V S) に応答して透過光量を調節する液晶セル (C l c) と、ゲートライン (G L) からのスキャニング信号 (S C S) に応答して信号ライン (S L) から液晶セル (C l c) に供給されるデータ電圧信号 (D V S) を切り換える TFT (C M N) で構成される。また、画素 (31) では補助容量 (C s t) が液晶セル (C l c) に並列に接続される。ゲートドライバ (34) は制御ライン (C L) からのゲートスタートパルス (G S P) 及びゲートクロックライン (G C L) からのゲートスキャニングクロック (G S C) に応答するシフトレジスタセル (36 A) と、シフトレジスタセル (36 A) とゲートライン (G L) の間に接続された制御用のスイッチ (39) で構成される。シフトレジスタセル (36 A) は図7に図示されたようにゲートスキャニングクロック (G S C) の上昇エッジでゲートスタートパルス (G S P) を出力端子 (Q T) 側に出力する。制御用のスイッチ (39) はシフトレジスタセル (36 A) の出力信号の論理状態によって低電位及び高電位ゲート電圧 (V g l, V g h) の中のいずれか一つを選択的にゲートライン (G L) に供給する。これによって、ゲートライン (G L) では低電位ゲート電圧または高電位ゲート電圧 (V g h) を有するスキャニング信号 (S C S) が現れる。これを詳細に説明すると、制御用のスイッチ (39) はシフトレジスタセル (36 A) の出力信号がハイ論理を有する場合に高電位ゲート電圧 (V g h) がゲートライン (G L) に供給されるようとする一方、シフトレジスタセル (36 A) の出力信号がロー論理を有する場合に低電位ゲート電圧 (V g l) がゲートライン (G L) に供給されるようとする。図7に図示された S C S n は次のゲートラインに供給されるスキャニング信号の波形を現す。

## 【0019】

また、本発明の第2実施例によるアクティブマトリックス液晶表示装置は第1電圧ライン (F V L) に接続された低電位ゲート電圧発生器 (40) と、高電位ゲート電圧発生器 (42) とを追加で具備する。低電位ゲート電圧発生器 (40) は電圧レベルが一定に維持されたり周期的に交番される低電位ゲート電圧 (V g l) を第1電圧ライン (F V L) に接続されたn個の制御用のスイッチ (39) に供給する。高電位ゲート電圧発生器 (42) は図7に図示されたところのように変化する高電位ゲート電圧 (V g h) を発生する。この高電位ゲート電圧 (V g h) の立下がり部は指數関数の形態で緩やかに下がる。このように高電位ゲート電圧 (V g h) を発生するために、高電位ゲート電圧発生器 (42) が高電位電圧 (V D D) を発生する高電位電圧発生器 (44) と、高電位電圧発生器 (44) 及び第2電圧ライン (S V L) の間に接続された電圧調節器 (46) で構成される。高電位電圧発生器 (44) は一定の電圧レベルを安定に維持する直流形態の高電位電圧 (V D D) を電圧調節器 (46) に供給する。電圧調節器 (46) は第2電圧ライン (S V L) を高電位電圧発生器 (44) と基底電圧ライン (G V L) に交番的に接続することで第2電圧ライン (S V L) 上に図7に示したような高電位ゲート電圧 (V g h) を発生させる。このために、電圧調節器 (46) はゲートスキャニングクロック (G S C) に応答する2接点制御用スイッチ (50) を具備する。2接点制御用スイッチ (50) はゲートスキャニングクロック (G S C) のハイ論理区間では第1電圧ライン (S V L) を高電位電圧発生器 (44) に接続させることで第2電圧ライン (S V L) 及びゲートライン (G L) 上に高電位電圧 (V D D) が現れるようとする。ゲートスキャニングクロック (G S C) がハイ論理からロー論理で遷移する場合、2接点制御用スイッチ (50) は第2電圧ライン (S V L) を基底電圧ライン (G V L) に接続させることで第2電圧ライン (S V L) 及びゲートライン (G L) 上の電圧を高電位電圧レベル (V D D) から指數関数的に降下させる。この時、第2電圧ライン (S V L) 及びゲートライン (G L) 上の電圧が寄

10

20

30

40

50

生抵抗 ( $R_p$ ) 及び寄生容量 ( $C_p$ ) の時定数によって基底電圧ライン ( $GVL$ ) 側に放電されることで高電位ゲート電圧 ( $Vgh$ ) とスキャニング信号 ( $SCS$ ) の立下り部は図 7 に示したように指數関数の形態で緩やかに変化する。これによって、画素 (31) に含まれた TFT (CMN) はゲートライン ( $GL$ ) からのスキャニング信号 ( $SCS$ ) の電圧が臨界電圧の以下に下がるまで起動オン状態が維持される。この時、液晶セル ( $C_{1c}$ ) に充電された電荷がゲートライン ( $GL$ ) 側に流れるが、信号ライン ( $SL$ ) から TFT (CMN) を経由するデータ電圧信号 ( $DVS$ ) によって充分な電荷が液晶セル ( $C_{1c}$ ) に充電される。この結果、液晶セル ( $C_{1c}$ ) に充電された電圧は下がらなくなる。10 ゲートライン ( $GL$ ) 上のスキャニング信号 ( $SCS$ ) の電圧が TFT (CMN) の臨界電圧以下に下がる場合にゲートライン ( $GL$ ) での電圧変動量が最大 TFT (CMN) の臨界電圧であるので液晶セル ( $C_{1c}$ ) からゲートライン ( $GL$ ) 側に流れる電荷量は極めて少なくなる。この結果、フィードスルー電圧 ( $Vp$ ) が充分に抑圧される。更に、画素 (31) によって表示される画点ではフリッカ及び残像が発生しなくなる。

### 【実施例 3】

#### 【0020】

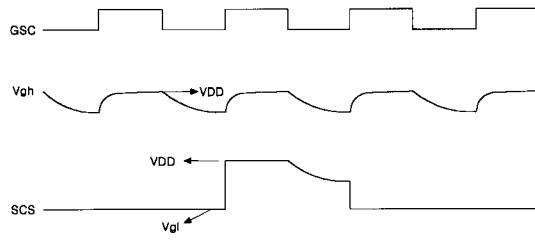

図 8 は本発明の第 3 実施例によるアクティブマトリックス液晶表示装置を概略的に図示する。図 8 のアクティブマトリックス液晶表示装置は電圧調節器 (46) が 2 接点制御用のスイッチ (50) と基底電圧ライン ( $GVL$ ) の間に抵抗 ( $R1$ ) 及び容量 ( $C1$ ) の並列回路とをさらに具備することを除いては図 6 の液晶表示装置と同一の回路構成を有する。抵抗 ( $R1$ ) 及び容量 ( $C1$ ) は第 2 電圧ライン ( $SVL$ ) 及びゲートライン ( $GL$ ) 上の電圧が基底電圧ライン ( $GVL$ ) 側に放電される場合に時定数を増加させる。これによって、第 2 電圧ライン ( $SVL$ ) 上の高電位ゲート電圧 ( $Vgh$ ) の立下がり部は図 9 でのように立上がり部よりもっと緩やかになる。これと併せて、ゲートライン ( $GL$ ) 上のスキャニング信号 ( $SCS$ ) の立下がり部も図 9 に示すように立上がり部よりもっと緩やかに変化する。抵抗 ( $R1$ ) と容量 ( $C1$ ) は必要に応じていずれか一つだけを使用してもよい。抵抗 ( $R1$ ) と容量 ( $C1$ ) は必要に応じていずれか一つだけを使用してもよい。このように高電位ゲート電圧 ( $Vgh$ ) 及びスキャニング信号 ( $SCS$ ) の立下がり部を立上がり部よりも緩やかに調節することで液晶表示装置はフィードスルー電圧 ( $Vp$ ) を充分に抑制することができることと併せて応答速度が速くなる。20

### 【実施例 4】

#### 【0021】

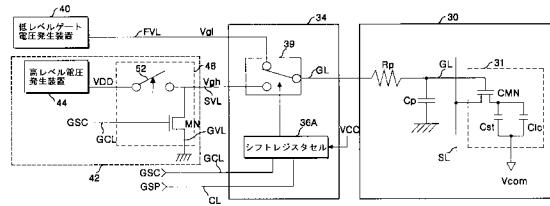

図 10 は第 4 実施例によるアクティブマトリックス液晶表示装置を概略的に図示する。図 10 のアクティブマトリックス液晶表示装置は電圧調節器 (46) が 2 接点制御用のスイッチ (50) 代わりに高電位電圧発生器 (44) 及び第 2 電圧ライン ( $SVL$ ) の間に接続された 1 接点制御用のスイッチ (52) と、第 2 電圧ライン ( $SVL$ ) 及び基底電圧ライン ( $GVL$ ) の間に接続された TFT (MN) とを具備することを除いては図 6 の液晶表示装置と同一な回路構成を有する。1 接点制御用のスイッチ (52) と TFT (MN) はゲートスキャニングクロック ( $GSC$ ) の論理状態によって相互補完的に起動される。これを詳細に説明すると、1 接点制御用のスイッチ (52) はゲートスキャニングクロック ( $GSC$ ) がハイ論理を維持する期間起動され、一方に TFT (MN) は TFT (MN) はゲートスキャニングクロック ( $GSC$ ) がハイ論理を維持する期間起動される。TFT (MN) はゲートスキャニングクロック ( $GSC$ ) によって第 2 電圧ライン ( $SVL$ ) 及びゲートライン ( $GL$ ) に放電通路を提供することで高電位ゲート電圧 ( $Vgh$ ) 及びスキャニング信号 ( $GL$ ) の立下がり部が指數関数的に変化する。また、TFT (MN) は起動時に現れる抵抗成分及び容量成分によって第 2 電圧ライン ( $SVL$ ) 及びゲートライン ( $GL$ ) 上の電圧が基底電圧ライン ( $GVL$ ) 側に放電される場合に時定数を増加させる。これによって、基底電圧ライン ( $GVL$ ) 上の高電位ゲート電圧 ( $Vgh$ ) 立下がり部は図 9 でのように立上がり部よりも緩やかになる。これと併せて、ゲートライン ( $GL$ ) 上のスキャニング信号 ( $SCS$ ) の立下がり部も図 9 でのように立上がり部よりもっと緩やかに変化する。このように高電位ゲート電圧 ( $Vgh$ ) 及びスキャニング信号 ( $SCS$ ) 4050

S ) の立下がり部が立上がり部よりもっと緩やかに調節されることで液晶表示装置はフィードスルー電圧 ( V<sub>p</sub> ) を充分に抑制することができることと併せて応答速度が速くなる。 TFT ( MN ) は抵抗成分の抵抗値及び容量成分の容量が適切に設定されるように適切なチャンネル幅を有する。更に、 TFT ( MN ) と基底電圧ライン ( GVL ) の間には時定数をもう少し増加させるための抵抗及び/または容量を付加することもできる。

#### 【実施例 5】

##### 【0022】

図 11 は本発明の第 5 実施例によるアクティブマトリックス液晶表示装置を概略的に図示する。図 11 のアクティブマトリックス液晶表示装置は TFT ( MN ) において抵抗 ( R2 ) が第 2 電圧ライン ( SVL ) 及び基底電圧ライン ( GVL ) の間に接続されたことを除いては図 10 の液晶表示装置と同一な回路構成を有する。抵抗 ( R2 ) は 1 接点制御用のスイッチ ( 52 ) がゲートスキャニングクロック ( GSC ) のハイ論理状態によって起動される場合に第 2 電圧ライン ( SVL ) 及びゲートライン ( GL ) に充電される電圧の漏泄を防止する。これとは異なり、 1 接点制御用のスイッチ ( 52 ) が起動される場合、抵抗 ( R2 ) は第 2 電圧ライン ( SVL ) 及びゲートライン ( GL ) 上の電圧が基底電圧ライン ( GVL ) 側に放電される時間が長くなることで高電位ゲート電圧 ( Vgh ) 及びスキャニング信号 ( SCS ) の立下がり部が指數関数の形態で変化させる。換言すれば、抵抗 ( R2 ) は第 1 接点制御用スイッチ ( 52 ) が起動される場合に第 2 電圧ライン ( SVL ) 及びゲートライン ( GL ) 上の高電位ゲート電圧 ( Vgh ) の立下がり部は図 9 でのように立上がり部よりもっと緩やかになる。これと併せて、ゲートライン ( GL ) 上のスキャニング信号 ( SCS ) の立下がり部も図 9 でのように立上がり部よりもっと緩やかに変化する。このように高電位ゲート電圧 ( Vgh ) 及びスキャニング信号 ( SCS ) の立下がり部が立上がり部よりもっと緩やかに調節されることで液晶表示装置はフィードスルー電圧 ( Vp ) を充分に抑制することができることと併せて応答速度が速くなる。

##### 【0023】

また、図 6 、図 8 、図 10 及び図 11 に図示された第 2 乃至第 5 実施例の液晶表示装置ではゲートスキャニングクロック ( GSC ) によって電圧調節器 ( 46 ) の切り換え動作が制御されることで図 5 でのタイミング制御器 ( 48 ) が除去される。この結果、図 6 、図 8 、図 10 及び図 11 に図示された第 2 乃至第 5 実施例のアクティブマトリックス液晶表示装置では回路構成が益々簡素化される。これと併せて、図 6 、図 8 、図 10 及び図 11 に図示された第 2 乃至第 5 実施例の液晶表示装置ではゲートスキャニングクロック ( GSC ) の衝撃係数が 50 % であることで表現されているが液晶セルに電圧が充分に充電されることができる範囲内で適切に調節されることができる。

##### 【0024】

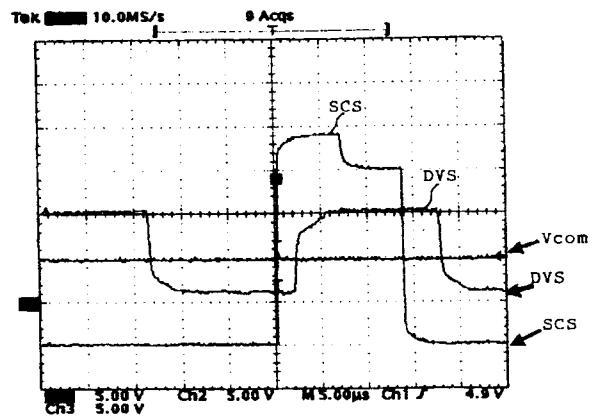

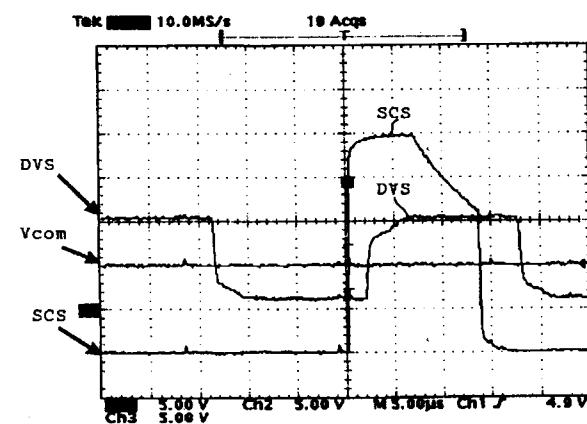

図 12 は本発明の第 1 乃至第 5 実施例によるアクティブマトリックス液晶表示装置のゲートライン ( GL ) 及び信号ライン ( SL ) 上に現れるスキャニング信号 ( SCS ) とデータ電圧信号 ( DVS ) を図示する。図 12 に図示されたスキャニング信号 ( SCS ) は下降エッジでデータ電圧信号 ( DVS ) にほとんど近接する電圧レベルを有する。これによって、液晶表示装置はフィードスルー電圧 ( Vp ) を充分に抑制することができることと併せて応答速度が速くなる。

#### 【実施例 6】

##### 【0025】

図 13 は本発明の第 6 実施例によるアクティブマトリックス液晶表示装置を概略的に図示する。図 13 のアクティブマトリックス液晶表示装置は第 1 電圧ライン ( FVL ) に接続された低電位ゲート電圧発生器 ( 40 ) と、高電位ゲート電圧発生器 ( 42 ) とを具備する。低電位ゲート電圧発生器 ( 40 ) は電圧レベルが一定に維持される低電位ゲート電圧 ( Vg1 ) を第 1 電圧ライン ( FVL ) に接続された n 個の制御用スイッチ ( 39 ) に供給する。高電位ゲート電圧発生器 ( 42 ) は図 14 に図示されたように第 1 及び第 2 高電位電圧 ( VDD1 、 VDD2 ) を交番的に有するパルス状の高電位ゲート電圧 ( Vgh ) を発生する。このような高電位ゲート電圧 ( Vgh ) を発生するために、高電位ゲート電

10

20

30

40

50

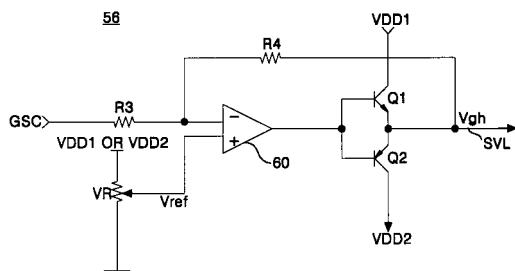

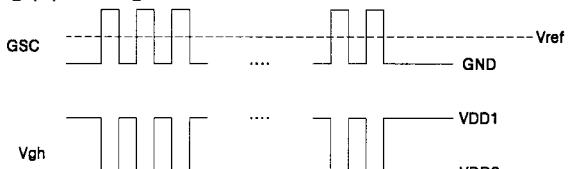

圧発生器(42)は第1及び第2高電位電圧(VDD1、VDD2)を発生する高電位電圧発生器(54)と、高電位電圧発生器(54)及び第2電圧ライン(SVL)の間に接続された電圧調節器(56)で構成される。高電位電圧発生器(54)で発生される第1高電位電圧(VDD1)は一定の電圧レベルを安定に維持して、第2高電位電圧(VDD2)は低電位ゲート電圧(Vg1)より高くて第1高電位電圧(VDD1)より低い電圧レベルを安定に維持する。これら第1及び第2高電位電圧(VDD1、VDD2)を電圧調節器(56)に供給する。電圧調節器(56)は高電位発生器(54)からの第1及び第2高電位電圧(VDD1、VDD2)を第2電圧ライン(SVL)側に交番的に供給することで第2電圧ライン(SVL)上に図14に示したような高電位ゲート電圧(Vgh)を発生させる。このために、電圧調節器(56)はゲートスキャニングクロック(GSC)に応答する第2制御用スイッチ(58)を具備する。第2制御用スイッチ(58)はゲートスキャニングクロック(GSC)のハイ論理区間で第1高電位電圧(VDD1)を第2電圧ライン(SVL)に供給することで第2電圧ライン(SVL)及びゲートライン(GL)上に第1高電位電圧(VDD1)が現れるようになる。これとは異なり、ゲートスキャニングクロック(GSC)がロー論理を有する場合、第2制御用スイッチ(58)は第2高電位電圧(VDD2)を第2電圧ライン(SVL)に供給することで第2電圧ライン(SVL)及びゲートライン(GL)上に第2高電位電圧(VDD2)が現れるようになる。この結果、高電位ゲート電圧(Vgh)はゲートスキャニングクロック(GSC)の周期ごとに第1高電位電圧(VDD1)と第2高電位電圧(VDD2)を順次有する。

10

20

30

40

#### 【0026】

図13のアクティブマトリックス液晶表示装置では液晶パネル(30)上のゲートライン(GL)を駆動するためのゲートドライバ(34)が含まれる。液晶パネル(30)は信号ライン(SL)及びゲートライン(GL)とに接続される画素(31)を含む。画素(31)は信号ライン(SL)からのデータ電圧信号(DVS)に応答して透過光量を調節する液晶セル(C1c)と、ゲートライン(GL)からのスキャニング信号(SCS)に応答して信号ライン(SL)から液晶セル(C1c)に供給されるデータ電圧信号(DVS)を切り換えるTFT(CMN)で構成される。また、画素(31)には補助容量(Cst)が液晶セル(C1c)に並列に接続される。ゲートドライバ(34)は制御ライン(CL)からのゲートスタートパルス(GSP)及びゲートクロックライン(GCL)からのゲートスキャニングクロック(GSC)に応答するシフトレジスタセル(36A)と、シフトレジスタセル(36A)とゲートライン(GL1)の間に接続された第1制御用スイッチ(39)で構成される。シフトレジスタセル(36A)は図14に図示されたようにゲートスキャニングクロック(GSC)の上昇エッジでゲートスタートパルス(GSP)を出力端子(QT)側に出力する。第1制御用スイッチ(39)はシフトレジスタセル(36A)の出力信号の論理状態によって低電位及び高電位ゲート電圧(Vg1、Vgh)の中いずれか一つを選択的にゲートライン(GL)に供給する。これによって、ゲートライン(GL)には低電位ゲート電圧(Vg1)または高電位ゲート電圧(Vgh)を有するスキャニング信号(SCS)が現れる。これらを詳細に説明すると、制御用のスイッチ(39)はシフトレジスタセル(36A)の出力信号がハイ論理を有する場合に第1及び第2高電位電圧(VDD1、VDD2)を順次有する高電位ゲート電圧(Vgh)がゲートライン(GL)に供給される一方、シフトレジスタセル(36A)の出力信号がロー論理を有する場合には低電位ゲート電圧(Vg1)がゲートライン(GL)に供給される。この結果、ゲートライン(GL)には立下がり部が階段形態に変化する図14のようなスキャニング信号(SCS)が現れる。図14に図示されたSCSnは次のゲートラインに供給されるスキャニング信号の波形を現す。

40

#### 【0027】

このようにスキャニング信号(SCS)の立下がり部が段階的に変化するために、画素(31)に含まれたTFT(CMN)はゲートライン(GL)からのスキャニング信号(SCS)の電圧が臨界電圧以下に下がるまで起動オン状態を維持する。この時、液晶セル(

50

C<sub>1c</sub>)に充電された電荷がゲートライン(G<sub>L</sub>)側に流れると同時に、信号ライン(S<sub>L</sub>)からTFT(CMN)を経由するデータ電圧信号(DVS)によって充分な電荷が液晶セル(C<sub>1c</sub>)に充電される。この結果、液晶セル(C<sub>1c</sub>)に充電された電圧は下がらなくなる。ゲートライン(G<sub>L</sub>)上のスキャニング信号(SCS)の電圧がTFT(CMN)の臨界電圧以下に下がる場合にゲートライン(G<sub>L</sub>)での電圧変動量が最大TFT(CMN)の臨界電圧であるので液晶セル(C<sub>1c</sub>)からゲートライン(G<sub>L</sub>)側に流れる電荷は極めて少なくなる。この結果、フィードスルー電圧(V<sub>p</sub>)は充分に抑圧される。更に、画素(31)によって表示される画点ではフリッカ及び残像が発生しなくなる。

## 【0028】

10

この場合、図5に図示された液晶パネル(30)のゲートライン(G<sub>L</sub>)上の寄生抵抗(R<sub>p</sub>)及び寄生容量(C<sub>p</sub>)は高電位ゲート電圧(V<sub>gh</sub>)に影響を与えるなくなる。このような背景から、寄生抵抗(R<sub>p</sub>)及び寄生容量(C<sub>p</sub>)が図13に図示されなかったことが理解される。図15は本発明の第6実施例によるアクティブマトリックス液晶表示装置のゲートライン(G<sub>L</sub>)及び信号ライン(S<sub>L</sub>)上に現れるスキャニング信号(SCS)とデータ電圧信号(DVS)を図示する。図15に図示されたスキャニング信号(SCS)は下降エッジが階段状に変化することでデータ電圧信号(DVS)にほとんど近接する電圧レベルを有する。これによって、液晶表示装置はフィードスルー電圧(V<sub>p</sub>)を充分に抑圧することができ、併せて応答速度が速くなる。

## 【0029】

20

図16は図13に図示された電圧調節器(56)の他の実施例を詳細に図示する。図16の電圧調節器(56)は抵抗(R3)を経由して反転端子(-)側にゲートスキャニングクロック(GSC)を入力受ける比較器(60)と、この比較器(60)の出力信号に相互補完的に応答する第1及び第2トランジスタ(Q1、Q2)とを具備する。比較器(60)は図17に図示したようなゲートスキャニングクロック(GSC)と可変抵抗(VR)からの基準電圧(V<sub>ref</sub>)を比較して、その結果によって論理状態が変化する比較信号を発生する。これを詳細に説明すると、比較器(60)はゲートスキャニングクロック(GSC)の電圧が基準電圧(V<sub>ref</sub>)より高い場合にロー論理の比較信号を第1及び第2トランジスタ(Q1、Q2)のベース端子に供給する一方、ゲートスキャニングクロック(GSC)の電圧が基準電圧(V<sub>ref</sub>)より低い場合にはハイ論理の比較信号を第1及び第2トランジスタ(Q1、Q2)のベース端子に供給する。この時、可変抵抗(VR)は図13に図示された第1または第2高電位電圧(VDD1またはVDD2)と基底電圧(GND)間の電位差を分圧してその分圧された電圧を基準電圧(V<sub>ref</sub>)として比較器(60)の非反転端子(+)に供給する。第1トランジスタ(Q1)は比較器(60)でハイ論理の比較信号が発生されると、図13の高電位電圧発生器(54)からの第1高電位電圧(VDD1)を第2電圧ライン(SVL)に供給する。一方に第2トランジスタ(Q2)は比較器(60)でロー論理の比較信号が発生されたときに図13の高電位電圧発生器(54)からの第2高電位電圧(VDD2)を第2電圧ライン(SVL)に供給する。この結果、第2電圧ライン(SVL)ではゲートスキャニングクロック(GSC)とは相反する形態で変化する図17に図示した高電位ゲート電圧(V<sub>gh</sub>)が発生する。この高電位ゲート電圧(V<sub>gh</sub>)はゲートスキャニングクロック(GSC)の論理状態によって第1及び第2高電位電圧(VDD1、VDD2)を交番される。また、この高電位ゲート電圧(V<sub>gh</sub>)は図13でのシフトレジスタセル(36A)がゲートスキャニングクロック(GSC)の立下がり部に応答する場合に使用される。更に、高電位ゲート電圧(V<sub>gh</sub>)は第1及び第2トランジスタ(Q1、Q2)の位置が変えられた場合または基準電圧(V<sub>ref</sub>)及びゲートスキャニングクロック(GSC)が比較器(60)の反転及び非反転端子(-、+)にそれぞれ供給される場合にゲートスキャニングクロック(GSC)と同一な形態で変化する。一方、第2電圧ライン(SVL)と比較器(60)の反転端子(-)の間に接続された抵抗(R4)は第2電圧ライン(SVL)上の電圧を比較器(60)の反転端子(-)側に帰還させることで高電位ゲート電圧(V<sub>gh</sub>)がゲー

30

40

50

トスキャニングクロック ( G S C ) に対して素早く応答するようとする。

【実施例 7】

【0030】

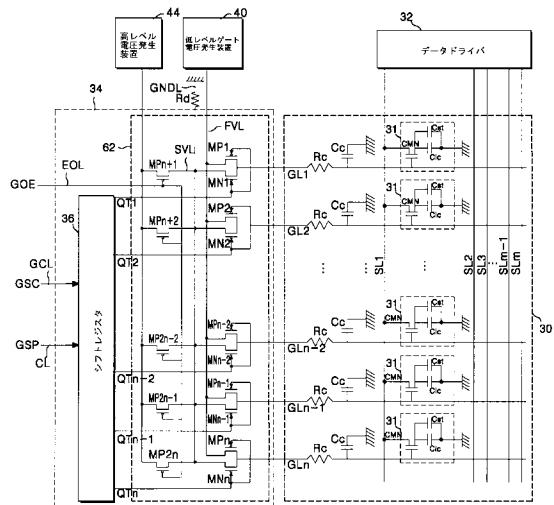

図18を参照すると、液晶パネル(30)上の信号ライン(SL1乃至SLm)を駆動するデータドライバ(32)と、液晶パネル(30)上のゲートライン(GL1乃至GLn)を駆動するためのゲートドライバ(34)とを具備する第7本発明の実施例によるアクティブマトリックス液晶表示装置が図示されている。液晶パネル(30)には信号ライン(SL)及びゲートライン(GL)に接続される画素(31)がアクティブマトリックス形態で配列される。画素(31)それぞれは信号ライン(SL)からのデータ電圧信号(DVS)に応答して透過光量を調節する液晶セル(CLc)と、ゲートライン(GL)からのスキャニング信号(SCS)に応答して信号ライン(SL)から液晶セル(CLc)に供給されるデータ電圧信号(DVS)を切り換えるTFT(CMN)で構成される。また、画素(31)それぞれには補助容量(Cst)が液晶セル(CLc)に並列に接続される。この補助容量(Cst)は液晶セル(CLc)に充電された電圧を緩衝する。データドライバ(32)はゲートライン(GL1乃至GLn)が順次駆動されることによって信号ライン(SL1乃至SLm)すべてにデータ電圧信号(DVS)を供給する。ゲートドライバ(34)がスキャニング信号(SCS)をゲートライン(GL1乃至GLm)に順次供給することでゲートライン(GL1乃至GLn)が水平同期期間ずつ順次使用可能にされる。このために、ゲートドライバ(34)は制御ライン(CL)からのゲートスタートパルス(GSP)及びゲートクロックライン(GCL)からのゲートスキャニングクロック(GSC)に応答するシフトレジスタ(36)と、シフトレジスタ(36)とゲートライン(GL1乃至GLn)の間に接続されたレベルシフト(62)で構成される。シフトレジスタ(36)は制御ライン(CL)からのゲートスタートパルス(GSP)をn個の出力端子(QT1乃至QTn)の内のいずれか一つの出力端子側に出力することと併せてゲートスキャニングクロック(GSC)に応答してゲートスタートパルス(GSP)を第1出力端子(QT1)から第n出力端子(QTn)側に順次移動させる。また、シフトレジスタ(36)はロジック電圧レベルに該当する5Vを有する集積回路駆動電圧で動作する。レベルシフト(62)はシフトレジスタ(36)の出力信号の電圧レベルをシフトさせることでn個のスキャニング信号(SCS)を発生させる。このために、レベルシフト(62)は第1電圧ライン(FVL)に共通に接続され、併せてゲートライン(GL1乃至GLn)それぞれに接続されたn個のPMOSトランジスタ(MP1乃至MPn)と、第2電圧ライン(SVL)に共通的に接続されることと併せてゲートライン(GL1乃至GLn)にそれぞれ接続されたn個のNMOSトランジスタ(MN1乃至MNN)とを具備する。

【0031】

第1電圧ライン(FVL)には低電位ゲート電圧発生器(40)で発生された低電位ゲート電圧(Vg1)が供給される。第1乃至第nPMOSトランジスタ(MP1乃至MPn)はシフトレジスタ(36)のn個の出力端子(QT1乃至QTn)それぞれに接続されたゲート電極を有する。同じく、第1乃至第nNMOSトランジスタ(MN1乃至MNN)もシフトレジスタ(36)のn個の出力端子(QT1乃至QTn)それぞれ接続されたゲート電極を有する。第1乃至第nPOMSトランジスタ(MP1乃至MPn)それぞれはシフトレジスタ(36)の出力端子上の信号に応答して第1乃至第nNMOSトランジスタ(MN1乃至MNN)それぞれと相互補完的に起動される。シフトレジスタ(36)の出力端子(QT1乃至QTn)からの信号にそれぞれ応答する第1乃至第nNMOSトランジスタ(MN1乃至MNN)は水平同期期間ずつ順次起動される。これによって、第1乃至第nPOMSトランジスタ(MP1乃至MPn)は水平同期期間ずつ順次起動される。この結果、第2電圧ライン(SVL)は第1乃至第nゲートライン(GL1乃至GLn)に水平同期期間づつ順次接続される。また、レベルシフト(62)は第2電圧ライン(SVL)と高電位電圧発生器(44)の間に並列接続されたn個のPMOSトランジスタ(MPn+1乃至MP2n)と、第2電圧ライン(SVL)と接地ライン(GNDL)50

の間に接続された放電抵抗 ( $R_d$ ) とをさらに具備する。これら  $n$  個の PMOS トランジスタ ( $M_{Pn+1}$  乃至  $M_{P2n}$ ) は使用可能化ライン (EOL) 上の図 19 に図示されたゲート出力使用可能化信号 (GOD) に共通に応答して毎水平同期周期の始点から水平同期周期の半分に該当する期間ずつ同時に起動される。これら  $n$  個の PMOS トランジスタ ( $M_{Pn+1}$  乃至  $M_{P2n}$ ) が起動されたとき、高電位電圧発生器 (44) で発生された高電位電圧 ( $VDD$ ) は  $n$  個の PMOS トランジスタ ( $M_{Pn+1}$  乃至  $M_{P2n}$ ) の並列回路及び第 2 電圧ライン (SVL) を経由して  $n$  個のゲートライン (GL1 乃至 GL $n$ ) 中のいずれか一つに供給される。一方、 $n$  個の PMOS トランジスタ ( $M_{Pn+1}$  乃至  $M_{P2n}$ ) が起動された時に  $n$  個のゲートライン (GL1 乃至 GL $n$ ) 中のいずれか一つのライン上の充電された電圧が第 2 電圧ライン (SVL) 及び放電抵抗 ( $R_d$ ) を経由して接地ライン (GNDL) 側に放電される。この時、ゲートライン (GL) 上の電圧の放電速度 (即ち、時定数) は放電抵抗 ( $R_d$ )、ゲートライン (GL) 上の寄生容量 ( $Cc$ ) 及び寄生抵抗 ( $Rc$ ) によって決定される。これによって、第 2 電圧ライン (SVL) では図 19 に図示されたようにゲートスキャニングクロック (GSC) のハイ論理区間 (即ち、水平同期信号の前半周期) では高電位電圧レベル ( $VDD$ ) を維持してゲートスキャニングクロック (GSC) のロー論理区間では高電位電圧レベル ( $VDD$ ) から指数関数的に徐々に減少する高電位ゲート電圧 ( $Vgh$ ) が発生する。

### 【0032】

第 1 乃至第  $n$  ゲートライン (GL1 乃至 GL $n$ ) それぞれは水平同期信号の周期づつ順次に起動される NMOS トランジスタ (GL1 乃至 GL $n$ ) それぞれは、水平同期信号の周期づつ順次に起動される NMOS トランジスタ (GL1 乃至 GL $n$ ) それぞれを経由して第 2 電圧ライン (SVL) 上の高電位ゲート電圧 ( $Vgh$ ) を水平同期信号の一周期の間に入力し、併せて残りの期間の間は PMOS トランジスタ ( $M_{P1}$  乃至  $M_{Pn}$ ) を経由して第 1 電圧ライン (FVL) 上の低電位ゲート電圧 ( $Vg1$ ) を入力する。この結果、第 1 乃至第  $n$  ゲートライン (GL1 乃至 GL $n$ ) は図 19 に図示されたスキャニング信号 (SCS1 乃至 SCS $n$ ) の供給を受ける。スキャニング信号 (SCS) はゲートスキャニングクロック (GSC) のハイ論理区間 (即ち、水平同期信号の前半周期) では高電位電圧を維持して、ゲートスキャニングクロック (GCS) のロー論理区間 (水平同期信号の後半周期) では高電位電圧から液晶パネル (30) 上の TFT (CMN) の臨界電圧 ( $Vth$ ) に近接した電圧まで指数関数的に減少する。また、スキャニング信号 (SCS) は次の水平同期周期の始点で TFT (CMN) の臨界電圧より低い電圧 (即ち、低電位ゲート電圧 ( $Vg1$ )) に急激に下がる。このように、液晶パネル (30) のゲートライン (GL) に供給されるスキャニング信号 (SCS) の立下がり部が緩やかに変化することで、画素 (31) に含まれた TFT (CMN) はゲートライン (GL) からのスキャニング信号 (SCS) の電圧が臨界電圧以下に下がるまでに起動される。この時、液晶セル (C1c) に充電された電荷がゲートライン (GL) 側に流れるが、信号ライン (SL) から TFT (CMN) を経由するデータ電圧信号 (DVS) によって充分な電荷が液晶セル (C1c) に充電される。これによって、液晶セル (C1c) に充電された電圧は下がらない。ゲートライン (GL) 上のスキャニング信号 (SCS) の電圧が TFT (CMN) の臨界電圧以下に下がる場合にゲートライン (GL) での電圧変動量が最大 TFT (CMN) の臨界電圧であるので液晶セル (C1c) からゲートライン (GL) 側に流れる電荷は極めて少なくなる。この結果、フィードスルー電圧 ( $Vp$ ) が充分に抑圧される。また、前記した  $n$  個の PMOS トランジスタ ( $M_{Pn+1}$  乃至  $M_{P2n}$ ) は高電位電圧発生器 (44) から第 2 電圧ライン (SVL) 側に供給される高電位電圧 ( $VDD$ ) の減殺量を最小化するために高電位電圧発生器 (44) と第 2 電圧ライン (SVL) の間の抵抗値を低くさせられる。従って、 $n$  個の PMOS トランジスタ ( $M_{Pn+1}$  乃至  $M_{P2n}$ ) の中  $n-1$  個の PMOS トランジスタは除去することができる。この場合、ゲートドライバ (34) の回路構成が簡素化される。更に、前記ゲートスタートパルス (GSP)、ゲートスキャニングクロック (GSC) 及びゲート使用可能化信号 (GOE) は図示しないタイミング制御器で発生される。

10

20

30

40

50

## 【0033】

図20は図18に図示されたところによるアクティブマトリックス液晶表示装置の中いずれか一つのゲートラインを駆動するためのライنسキャニング回路を図示する。図20に図示したライスキャニング回路は液晶パネル(30)上のゲートライン(GL)を駆動するためのゲートドライバ(34)を含む。液晶パネル(30)は信号ライン(SL)及びゲートライン(GL)とに接続される画素(31)を含む。画素(31)は信号ライン(SL)からのデータ電圧信号(DVS)に応答して透過光量を調節する液晶セル(CLc)と、ゲートライン(GL)からのスキヤニング信号(SCS)に応答して信号ライン(SL)から液晶セル(CLc)に供給されるデータ電圧信号(DVS)を切り換えるTFT(CMN)で構成される。また、画素(31)には補助容量(Cst)が液晶セル(CLc)に並列に接続される。ゲートドライバ(34)は制御ライン(CL)からのゲートスタートパルス(GSP)及びゲートクロックライン(GCL)からのゲートスキヤニングクロック(GSC)に応答するシフトレジスタセル(36A)と、シフトレジスタセル(36A)とゲートライン(GL)の間に接続されたレベルシフトセル(62A)で構成される。シフトレジスタセル(36A)は図19に示すゲートスキヤニングクロック(GSC)の上昇エッジで図19に示すゲートスタートパルス(GSP)を出力端子(QT)側に出力させる。レベルシフトセル(62A)はシフトレジスタセル(36A)の出力信号の電圧レベルをシフトさせることでスキヤニング信号(SCS)を発生する。このために、レベルシフトセル(62A)は第1電圧ライン(FVL)と液晶パネル(30)上のゲートライン(GL)の間に接続された第1PMOSトランジスタ(MP1)と、第2電圧ライン(SVL)とゲートライン(GL)の間に接続された第1NMOSトランジスタ(MN1)とを具備する。

10

20

## 【0034】

第1電圧ライン(FVL)には低電位ゲート電圧発生器(40)で発生された低電位ゲート電圧(Vg1)が供給される。第1PMOSトランジスタ(MP1)はシフトレジスタセル(36A)の出力端子(QT)に接続されたゲート電極を有する。同じく、第1NMOSトランジスタ(MN1)はシフトレジスタセル(36A)の出力端子(QT)に接続されたゲート電極を有する。第1PMOSトランジスタ(MP1)はシフトレジスタセル(36A)の出力端子上の信号に応答して第1NMOSトランジスタ(MN1)と相互補完的に起動される。シフトレジスタセル(36A)の出力端子(QT)からの信号にそれぞれ応答する第1NMOSトランジスタ(MN1)は任意の水平同期期間に起動される一方、第1PMOSトランジスタ(MP1)は任意の水平同期期間を除いては残りフレーム期間に起動される。この結果、第2電圧ライン(SVL)は任意の水平同期期間にだけゲートライン(GL)に接続されるようになり、第1電圧ライン(FVL)は任意の水平同期期間を除いた残りのフレーム期間にゲートライン(GL)に接続される。

30

## 【0035】

また、レベルシフトセル(62A)は高電位電圧発生器(44)と第2電圧ライン(SVL)の間に接続された第2PMOSトランジスタ(MP2)と、第2電圧ライン(SVL)と接地ライン(GNDL)の間に接続された放電抵抗(Rd)とをさらに具備する。第2PMOSトランジスタ(MP2)は使用可能化ライン(EOL)からの図18に図示されたゲート出力使用可能化信号(GOE)に応答して毎水平同期周期の始点から水平同期周期の半分に該当する期間に起動される。この第2PMOSトランジスタ(MP2)が起動された時、高電位電圧発生器(44)は高電位電圧(VDD)を第2電圧ライン(SVL)を経由してゲートライン(GL)に供給される。一方、第2PMOSトランジスタ(MP2)が起動された時にゲートライン(GL)上に充電された電圧が第2電圧ライン(SVL)及び放電抵抗(Rd)を経由して接地ライン(GNDL)側に放電される。この時、ゲートライン(GL)上の電圧の放電速度(即ち、時定数)は放電抵抗(Rd)、ゲートライン(GL)上の寄生容量(Cp)及び寄生抵抗(Rp)によって決定される。これによって、第2電圧ライン(SVL)には図19に図示されたゲートスキヤニングクロック(GSC)のハイ論理区間(即ち、水平同期信号の前半周期)では高電位電圧レベル

40

50

(VDD)を維持してゲートスキャニングクロック(GSC)のロー論理区間では高電位電圧レベル(VDD)から指数関数的に徐々に減少する高電位ゲート電圧(Vgh)が現れる。ゲートライン(GL)は任意の水平同期信号の周期の間起動される第1NMOSトランジスタ(MN1)を経由して第2電圧ライン(SVL)上の高電位ゲート電圧(Vgh)を水平同期信号の周期を除いた残りの期間の間には第1PMOSトランジスタ(MP1)を経由して第1電圧ライン(FVL)上の低電位ゲート電圧(Vgl)を入力する。この結果、ゲートライン(GL)には図19に図示されたスキャニング信号(SCS1乃至SCSn)の中いずれか一つが供給される。スキャニング信号(SCS)はゲートスキャニングクロック(GSC)のハイ論理区間(即ち、水平同期信号の前半周期)では高電位電圧を維持して、ゲートスキャニングクロック(GSC)のロー論理区間では(水平同期信号の後半周期)では高電位電圧から液晶パネル(30)上のTFT(CMN)の臨界電圧(Vth)に近接される電圧まで指数関数的に減少する。

10

20

**【0036】**

また、スキャニング信号(SCS)は次の水平同期周期の始点でTFT(CMN)の臨界電圧より低い電圧(即ち、低電位ゲート電圧(Vgl))に急激に下がる。このように、液晶パネル(30)のゲートライン(GL)に供給されるスキャニング信号(SCS)の立下がり部が緩やかに変化することで、画素(31)に含まれたTFT(CMN)はゲートライン(GL)からのスキャニング信号(SCS)の電圧が自分の臨界電圧以下で下がるまでに起動される。この時、液晶セル(ClC)に充電された電荷がゲートライン(GL)側に流れ信号ライン(SL)からTFT(CMN)を経由するデータ電圧信号(DVS)によって充分な電荷が液晶セル(ClC)に充電される。これによって、液晶セル(ClC)に充電された電圧は下がらない。ゲートライン(GL)上のスキャニング信号(SCS)の電圧がTFT(CMN)の臨界電圧以下に下がる場合にゲートライン(GL)での電圧変動量が最大TFT(CMN)の臨界電圧であるので液晶セル(ClC)からゲートライン(GL)側に流れる電荷量は極めて少なくなる。この結果、フィードスルー電圧(Vp)が充分に抑圧される。

30

40

50

**【実施例8】****【0037】**

図21は本発明の第8実施例によるアクティブマトリックス液晶表示装置を概略的に図示する。図21のアクティブマトリックス液晶表示装置は、図18で第2電圧ライン(SVL)と高電位電圧発生器(44)の間に並列に接続されたn個のPMOSトランジスタ(MPn+1乃至MP2n)とそして第2電圧ライン(SVL)と接地ライン(GNDL)の間に接続された放電抵抗(Rd)の代わりに高電位電圧発生器(44)と第2電圧ライン(SVL)の間に接続された電圧調節器(64)を有することを除いては図18のアクティブマトリックス液晶表示装置と同一な回路構成を有する。電圧調節器(64)はゲートクロックライン(GCL)からのゲートスキャニングクロック(GSC)に応答して高電位電圧発生器(44)を第2電圧ライン(SVL)に連結させ、第2電圧ライン(SVL)に放電通路を提供する。これを詳細に説明すると、電圧調節器(64)はゲートスキャニングクロック(GSC)がハイ論理値を有する期間には高電位発生器(44)からの高電位電圧(VDD)が第2電圧ライン(SVL)とn個のNMOSトランジスタ(MN1乃至MNN)の中いずれか一つを経由してゲートライン(GL)側に伝送される。一方、ゲートスキャニングクロック(GSC)がロー論理値を有する時に電圧調節器(64)は第2電圧ライン(SVL)に放電通路を提供してゲートライン(GL1乃至GLn)上に充電された電圧が第2電圧ライン(SVL)及び放電通路を放電されるようになる。この時、ゲートライン(GL)上の電圧の放電速度(即ち、時定数)は放電通路の抵抗値、ゲートライン(GL)上の寄生容量(CC)及び寄生抵抗(Rc)によって決定される。結果的に、電圧調節器(64)は図19に図示されたところのようにゲートスキャニングクロック(GSC)のハイ論理区間(即ち、水平同期信号の前半周期)では高電位電圧レベル(VDD)を維持してゲートスキャニングクロック(GSC)のロー論理区間では高電位電圧レベル(VDD)から指数関数的に徐々に減少する高電位ゲート電圧(Vgh)

50

が第2電圧ライン( S V L )上に現れる。

【0038】

また、第1乃至第nゲートライン( G L 1 至 G L n )それぞれは水平同期信号の周期づつ順次起動されるN M O Sトランジスタ( M N 1 至 M N n )をそれぞれ経由して第2電圧ライン( S V L )上の高電位ゲート電圧( V g h )を水平同期信号の一周期の間に入力することと併せて残りの期間の間はP M O Sトランジスタ( M P 1 至 M P n )を経由して第1電圧ライン( F V L )上の低電位ゲート電圧( V g l )を入力する。この結果、第1乃至第nゲートライン( G L 1 至 G L n )は図18に図示されたスキヤニング信号( S C S 1 至 S C S n )の供給を受ける。スキヤニング信号( S C S )はゲートスキヤニングクロック( G S C )のハイ論理区間( 即ち、水平同期信号の前半周期 )では高電位電圧を維持して、ゲートスキヤニングクロック( G C S )のロー論理区間( 水平同期信号の後半周期 )では高電位電圧から液晶パネル( 30 )上のTFT( C M N )の臨界電圧( V t h )に近接する電圧まで指數関数的に減少する。また、スキヤニング信号( S C S )は次の水平同期周期の始点でTFT( C M N )の臨界電圧より低い電圧( 即ち、低電位ゲート電圧( V g l ) )に急激に下がる。

10

【0039】

このように、液晶パネル( 30 )のゲートライン( G L )に供給されるスキヤニング信号( S C S )の立下がり部が緩やかに変化することで、画素( 31 )に含まれたTFT( C M N )はゲートライン( G L )からのスキヤニング信号( S C S )の電圧が臨界電圧以下に下がるまでに起動される。この時、液晶セル( C 1 c )に充電された電荷がゲートライン( G L )側に流れるが、信号ライン( S L )からTFT( C M N )を経由するデータ電圧信号( D V S )によって充分な電荷が液晶セル( C 1 c )に充電される。これによって、液晶セル( C 1 c )に充電された電圧は下がらなくなる。ゲートライン( G L )上のスキヤニング信号( S C S )の電圧がTFT( C M N )の臨界電圧以下に下がる場合にゲートライン( G L )での電圧変動量が最大TFT( C M N )の臨界電圧であるので液晶セル( C 1 c )からゲートライン( G L )側に流れる電荷量は極めて少なくなる。この結果、フィードスルーレ電圧( V p )が充分に抑圧される。

20

【0040】

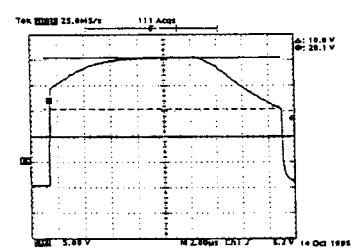

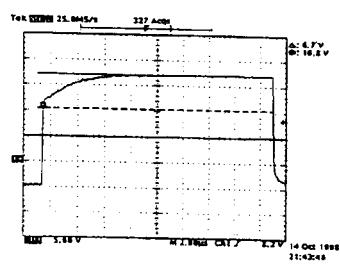

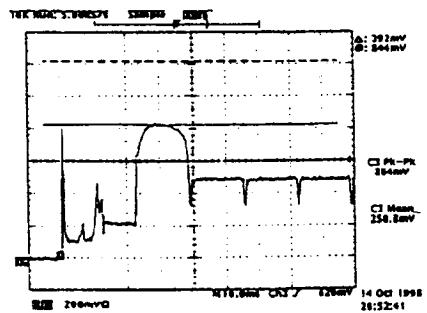

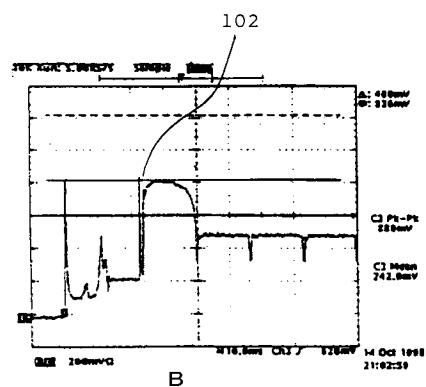

図22aは本発明によるアクティブマトリックス液晶表示装置によって提供されたスキヤニング信号の波形を現し、図22bは従来のアクティブマトリックス液晶表示装置で提供されるスキヤニング信号を現す。図22aのスキヤニング信号は図22bのスキヤニング信号とは異なり指數関数的に減少する下降エッジを有する。これによって、本発明によるアクティブマトリックス液晶表示装置はTFT( C M N )がターンオフされるときのTFT( C M N )のゲート電極とソース電極間の電位差が小さくなる。従って、TFT( C M N )がターンオフされるときに液晶セルから放電される電荷が著しく減少する。この結果、フィードスルーレ電圧( V p )が小さくなつて、更にフリッカが著しく減少する。図23aは本発明によるアクティブマトリックス液晶表示装置はTFT( C M N )が起動されるときの電流変化を、そして図23bは従来のアクティブマトリックス液晶表示装置はTFT( C M N )が起動されるときの電流変化をそれぞれ現す。図23a及び図23bは本発明によるアクティブマトリックス液晶表示装置は従来の液晶表示装置に比べて過渡雑音成分を大きく抑制されることを示している。

30

【0041】

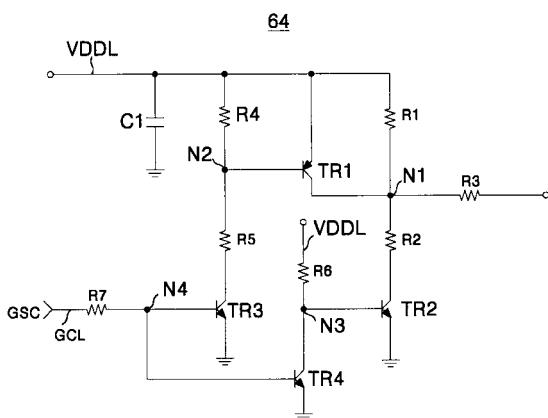

図24は図20に図示された電圧調節器( 64 )の実施例を詳細に図示するものである。図24において、電圧調節器( 64 )は高電位電圧ライン( V D D L )と接地ライン( G N D L )の間に直列接続された第1及び第2抵抗( R 1、R 2 )と、第1ノード( N 1 )と第2電圧ライン( S V L )の間に接続された第3抵抗( R 3 )とを具備する。第1及び第2抵抗( R 1、R 2 )は高電位電圧ライン( V D D L )上の高電位電圧( V D D )を分圧してその分圧された電圧が第1ノード( N 1 )上に現れるようにする。第3抵抗( R 3 )は第1ノード( N 1 )と第2電圧ライン( S V L )の間に電流量を制限する。電圧調節器( 64 )は高電位電圧ライン( V D D L )、第1及び第2ノード( N 1、N 2 )の間に

40

50

接続された第1トランジスタ( T R 1 )と、第2抵抗( R 2 )と接地ライン( G N D L )の間に接続された第2トランジスタ( T R 2 )とをさらに具備する。第1トランジスタ( T R 1 )は第2ノード( N 1 )上の電圧に応答して高電位電圧ライン( V D D L )上の高電位電圧( V D D )を第1ノード( N 1 )側に選択的に伝送する。

#### 【 0 0 4 2 】

これを詳細に説明すると、第1トランジスタ( T R 1 )は第2ノード( N 2 )上の電圧が臨界電圧( 即ち、0.7V )以下の時に起動されて第1ノード( N 1 )上の電圧が高電位電圧レベルを維持する。第2ノード( N 2 )上の電圧が臨界電圧以上である場合、第1トランジスタ( T R 1 )はターンオフされて高電位電圧ライン( V D D L )と第1ノード( N 1 )を開放させる。このために、第1トランジスタ( T R 1 )としてはP形ジョンショントランジスタが使用される。第2ノード( N 2 )上の電圧は第4ノード( N 4 )に接続されたベースを有する第3トランジスタ( T R 3 )によって変化する。第3トランジスタ( T R 3 )は第4ノード( N 4 )からのゲートスキャニングクロック( G S C )がハイ論理値を有する時に起動されて高電位電圧ライン( V D D L )から第4抵抗( R 4 )、第2ノード( N 2 )、第5抵抗( R 5 )、自分のコレクター及びエミッタを経由して接地ライン( G N D L )に至る電流通路を形成する。この場合、第2ノード( N 2 )にはトランジスタ( T R )の臨界電圧より低い電圧が現れる。これとは異なって、第4ノード( N 4 )上のゲートスキャニングクロック( G S C )がロー論理を有する場合に第3トランジスタ( T R 3 )はターンオフされて第2ノード( N 2 )の電圧が高電位電圧レベルを維持する。一方、第2トランジスタ( T R 2 )は第3ノード( N 3 )上の電圧に応答して第2抵抗( R 2 )を接地ラインに選択的に接続させる。この時、第2電圧ライン( S V L )上の高電位ゲート電圧( V g h )は第3抵抗( R 3 )、第1ノード( N 1 )第2抵抗( R 2 )予備トランジスタ( T R 2 )のコレクター及びエミッタを経由して接地ライン( G N D L )側に放電される。10

#### 【 0 0 4 3 】

一方、第3ノード( N 3 )上の電圧が臨界電圧より低い場合に、第2トランジスタ( T R 2 )はターンオフされて第2抵抗( R 2 )と接地ライン( G N D L )が開放される。このために、N形ジョンショントランジスタ( T R )が第2トランジスタ( T R )で使用される。第3ノード( N 3 )上の電圧は第4ノード( N 4 )に接続されたベースを有する第4トランジスタ( T R 4 )の動作状態によって変化する。第4トランジスタ( T R 4 )は第4ノード( N 4 )からのゲートスキャニングクロック( G S C )がハイ論理値を有する時に起動されて第3ノード( N 3 )を接地ライン( G N D L )に接続させる。これによって、第3ノード( N 3 )では接地電圧( G N D )が現れる。これとは異なって、第4ノード( N 4 )上のゲートスキャニングクロック( G S C )がハイ論理値を有する場合に第4トランジスタ( T R 4 )はターンオフされて第3ノード( N 3 )と接地ライン( G N D L )が開放される。30

#### 【 0 0 4 4 】

この時、高電位電圧ライン( V D D L )上の高電位電圧( V D D )が第6抵抗( R 6 )を経由して第3ノード( N 3 )に充電される。従って、第3ノード( N 3 )では高電位電圧( V D D )が現れる。結果的に、第2ノード( N 2 )上の電圧と第3ノード( N 3 )上の電圧が同一な形態で変化する。これら第2及び第3ノード( N 2 、 N 3 )上の電圧が同一な形態で変化することで第1及び第2トランジスタ( T R 1 、 T R 2 )が相互補完的に駆動される。換言すれば、第1トランジスタ( T R 1 )はゲートスキャニングクロック( G S C )のハイの論理区間に、第2トランジスタ( T R 2 )はゲートスキャニングクロック( G S C )のロー論理区間にそれぞれ起動される。これによって、第1ノード( N 2 )及び第2電圧ライン( S V L )上の電圧はゲートスキャニングクロック( G S C )のハイ論理区間では高電位電圧( V D D )を、ゲートスキャニングクロック( G S C )のロー論理区間では高電位電圧レベル( V D D )から分圧された電圧レベルまで指數関数的に減少させる。この結果、第2電圧ライン( s v l )には図18に示した波形を有する高電位ゲート電圧( V g h )が現れる。ゲートスキャニングクロック( G S C )はゲートクロックラ4050

イン ( G C L ) から第 7 抵抗 ( R 7 ) を経由して第 4 ノード ( N 4 ) に供給される。第 7 抵抗 ( R 7 ) はゲートクロックライン ( G C L ) から第 4 ノード ( N 4 ) 側に流れる電流を制限する。第 2 及び第 3 抵抗 ( R 2 、 R 3 ) は第 2 トランジスタ ( T R 2 ) が起動された時に図 20 に図示されたゲートライン ( G L ) 上の寄生容量 ( C p ) 及び寄生抵抗 ( R p ) と共にゲートライン ( G L ) 上の電圧の放電速度を決定する。

#### 【 0 0 4 5 】

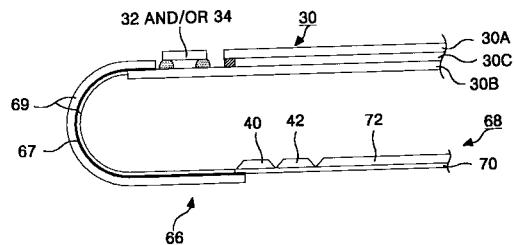

図 25 は本発明による TAB 形液晶表示装置を概略的に図示する。図 25 の TAB 形液晶表示装置で、液晶パネル ( 30 ) は上部ガラス基板 ( 30 A ) と下部ガラス基板 ( 30 B ) の間に密封された液晶層 ( 30 C ) で構成される。この液晶パネル ( 30 ) は FPC ( Flexible Printed Circuit ) フィルム ( 66 ) によって PCB ( Printed Circuit Board ) モジュール ( 68 ) に接続される。PCB モジュール ( 68 ) は PCB ( 70 ) の上面に搭載された制御回路部 ( 72 ) 、低電位及び高電位ゲート電圧発生器 ( 40 、 42 ) を有する。FPC フィルム ( 66 ) は下部ガラス基板 ( 30 B ) のペッド領域に接続された一段部と PCB ( 70 ) の底面の縁に接続された他段部を有する。また、FPC フィルム ( 66 ) の中間にはデータドライバ ( 32 ) 及び / またはゲートドライバ ( 34 ) が接地される。データドライバ ( 32 ) 及び / ゲートドライバ ( 34 ) は FPC フィルム ( 66 ) によって液晶パネル ( 30 ) 及び PCB モジュール ( 68 ) に接続される。このような FPC フィルム ( 66 ) は液晶パネル ( 30 ) をデータドライバ ( 32 ) 及び / またはゲートドライバ ( 34 ) に電気的に連結する第 1 導電層パターン ( 67 A ) と、データドライバ ( 32 ) 及び / またはゲートドライバ ( 34 ) を PCB モジュール ( 68 ) に電気的に連結する第 2 導電層パターン ( 67 B ) を有する。これら第 1 及び第 2 導電層パターン ( 67 A 、 67 B ) は両端部が露出されるように第 1 及び第 2 保護フィルム ( 69 A 、 69 B ) によって包まれる。

#### 【 0 0 4 6 】

図 26 は本発明による COG ( Chips On Glass ) 形液晶表示装置を概略的に図示する。図 26 の COG 形液晶表示装置は、上部ガラス基板 ( 30 A ) と下部ガラス基板 ( 30 B ) の間に密封された液晶層 ( 30 C ) とを具備する。この液晶パネル ( 30 ) は FPC ( Flexible Printed Circuit ) フィルム ( 66 ) によって PCB ( Printed Circuit Board ) モジュール ( 68 ) に接続される。PCB モジュール ( 68 ) は PCB ( 70 ) の上面に搭載された制御回路部 ( 72 ) 、低電位及び高電位ゲート電圧発生器 ( 40 、 42 ) を有する。また、下部ガラス基板 ( 30 B ) のペッド領域にはデータドライバ ( 32 ) 及び / またはゲートドライバ ( 34 ) が載せられている。これらデータドライバ ( 32 ) 及び / ゲートドライバ ( 34 ) は FPC フィルム ( 66 ) によって液晶パネル ( 30 ) 及び PCB モジュール ( 68 ) に接続される。FPC フィルム ( 66 ) はデータドライバ ( 32 ) 及び ゲートドライバ ( 34 ) が載せられた PCB モジュール ( 68 ) に接続させる。このために、FPC フィルム ( 66 ) は下部ガラス基板 ( 30 B ) のペッド領域に接続された一段部と PCB ( 70 ) の底面の縁に接続された他段部を有する。このような FPC フィルム ( 66 ) はデータドライバ ( 32 ) 及び / またはゲートドライバ ( 34 ) が搭載された液晶パネル ( 30 ) と PCB モジュール ( 68 ) を電気的に接続する導電層パターン ( 67 ) を有する。導電層パターン ( 67 ) は端部が露出するように保護フィルム ( 69 ) によって包まれる。

#### 【 0 0 4 7 】

本発明に開示された低電位ゲート電圧発生器と高電位ゲート電圧発生器は PCB モジュールに位置し、電圧制御器は LCD モジュール上に多様な形態で配置させることができる。まず、電圧制御器が PCB モジュールに配置されることができる。換言すれば、電圧制御器、高電位ゲート電圧発生器及び低電位ゲート電圧発生器すべてが PCB モジュール上に形成される。このような回路構造は図 1 に図示された通常のゲートドライバ IC にしてゲートパルスの立下がり部をスムーズ ( Smooth ) にすることができる。従って、本発明の目的はゲートドライバ IC を変形せずに達成される。次に、電圧制御器はゲートドライバ IC 内に載せられている。ゲートドライバ IC 内に載せられた電圧制御器は図 18 のように

10

20

30

40

50

高電位ゲート電圧発生器とババーの間に接続してもよい。異なる方法で、ゲートドライバIC内に含まれた電圧制御器は図5及び図21のように一つの高電位電圧発生器と多数のババーの間に接続してもよい。電圧制御器を含むゲートドライバICはPCBは電圧制御器がPCBモジュール上に配置された場合に比べてLCDモジュールの部品数を減少させることができ、更に部品のコストを低減することができる。

#### 【0048】

上述したように、本発明によるアクティブマトリックス液晶表示装置は、ゲートドライバのレベルシフトに高電位ゲート電圧を交流形態で供給することでスキャニング信号の立下がり部が線形、指数または階段関数の中のいずれか一つの形態で変化する。これによって、本発明によるアクティブマトリックス液晶表示装置ではフィードスルー電圧(  $V_p$  )を充分に抑圧し、さらにフリッカ及び残像の発生を抑制する。さらに、本発明によるアクティブマトリックス液晶表示装置では回路構成が極めて簡素化される。10

#### 【0049】

また、本発明によるアクティブマトリックス液晶表示装置は、高電位ゲート電圧の立下がり部が立上がり部より緩やかに変化することでゲートラインに供給されるスキャニング信号の立下がり部が立上がり部より緩やかに変化する。これによって、本発明によるアクティブマトリックス液晶表示装置では、フリッカ及び残像が発生しなくなることは勿論であり、さらに応答速度が早くなる。

#### 【0050】

以上説明した内容を通して当業者であれば本発明の技術思想を一脱しない範囲で多様な変更及び修正が可能であることが分かる。従って、本発明の技術的な範囲は明細書の詳細な説明に記載された内容に限らず特許請求の範囲によって定めなければならない。20

#### 【図面の簡単な説明】

#### 【0051】

【図1】図1は通常の液晶表示装置を概略的に図示する図面である。

【図2】図2は立下がり部が緩やかに変化するスキャニング信号の波形を図示する図面である。

【図3】図3は図2bに図示されたスキャニング信号を利用する従来の液晶表示装置を図示する図面である。

【図4】図4は通常の液晶表示装置の構造を図示する図面である。30

【図5】図5は本発明による第1実施例によるアクティブマトリックス液晶表示装置を概略的に図示する図面である。

【図6】図6は本発明による第2実施例によるアクティブマトリックス液晶表示装置を概略的に図示する図面である。

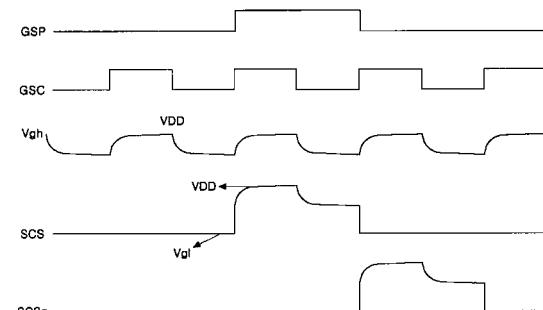

【図7】図7は図6に図示された重要部分に対する出力波形図である。

【図8】図8は本発明による第3実施例によるアクティブマトリックス液晶表示装置を概略的に図示する図面である。

【図9】図9は図8に図示された重要部分に対する出力波形図である。

【図10】図10は本発明による第4実施例によるアクティブマトリックス液晶表示装置を概略的に図示する図面である。40

【図11】図11は本発明による第5実施例によるアクティブマトリックス液晶表示装置を概略的に図示する図面である。

【図12】図12は本発明の第1乃至第5実施例による液晶表示装置のゲートライン及び信号ライン上でそれぞれ現すスキャニング信号及びデータ電圧信号の波形図である。

【図13】図13は本発明による第6実施例によるアクティブマトリックス液晶表示装置を概略的に図示する図面である。

【図14】図14は図13に図示された重要部分に対する出力波形図である。

【図15】図15は図13に図示された液晶パネルのゲートライン及び信号ライン上で現すスキャニング信号及びデータ電圧信号の波形図である。

【図16】図16は図13に図示された電圧調節器の異なる実施例を図示する図面である50

【図17】図17は図16に図示された電圧調節器の入力及び出力波形図である。

【図18】図18は本発明による第7実施例によるアクティブマトリックス液晶表示装置を概略的に図示する図面である。

【図19】図19は図18に図示された重要部分に対する出力波形図である。

【図20】図20は図18に図示された液晶表示装置の中一つのゲートラインを駆動するためのライスキャニング回路を図示する図面である。

【図21】図21は本発明による第8実施例によるアクティブマトリックス液晶表示装置を概略的に図示する図面である。

【図22】図22は本発明aおよび従来のbアクティブマトリックス液晶表示装置によるスキャニング信号の波形図である。 10

【図23】図23は本発明aおよび従来bのアクティブマトリックス液晶表示装置によってTFT(CMN)が起動される時の電流変化を図示する図面である。

【図24】図24は図21に図示された電圧調節器を詳細に図示する図面である。

【図25】図25は本発明によるタップ形液晶表示装置を図示する図面である。

【図26】図26は本発明によるCOG形液晶表示装置を図示する図面である。

#### 【符号の説明】

##### 【0052】

|                                                            |    |

|------------------------------------------------------------|----|

| 10 : 液晶パネル                                                 | 20 |

| 11、31 : 画素                                                 |    |

| 12、32 : データドライバ                                            |    |

| 14、34 : ゲートドライバ                                            |    |

| 3、16、36 : シフトレジスタ                                          |    |

| 11、8、38、62 : レベルシフト                                        |    |

| 5、6、9、19 : インバータ                                           |    |

| 20 : スキャニングドライバセル                                          |    |

| 22 : 積分器                                                   |    |

| 30A : 上部ガラス基板                                              |    |

| 30B : 下部ガラス基板                                              |    |

| 30C : 液晶層                                                  | 30 |

| 36A : シフトレジスタセル                                            |    |

| 39、58 : 制御用スイッチ                                            |    |

| 40 : 低電位ゲート電圧発生器                                           |    |

| 42 : 高電位ゲート電圧発生器                                           |    |

| 44、54 : 高電位電圧発生器                                           |    |

| 46、56、64 : 電圧調節器                                           |    |

| 48 : タイミング制御器                                              |    |

| 50 : 2接点制御用スイッチ                                            |    |

| 52 : 1接点制御用スイッチ                                            |    |

| 60 : 比較器                                                   | 40 |

| 62A : レベルシフトセル                                             |    |

| 66 : FPCフィルム                                               |    |

| 67、67A、67B : 導電層パターン                                       |    |

| 68 : PCBモジュール                                              |    |

| 69、69A、69B : 保護フィルム                                        |    |

| 70 : PCB                                                   |    |

| 72 : 制御回路部                                                 |    |

| S <sub>L</sub> 、S <sub>L1</sub> 乃至S <sub>Lm</sub> : 信号ライン  |    |

| G <sub>L</sub> 、G <sub>L1</sub> 乃至G <sub>Lm</sub> : ゲートライン |    |

| C <sub>1c</sub> : 液晶セル                                     | 50 |

C MN : 薄膜トランジスタ (TFT)

C L : 制御ライン

G CL : ゲートクロックライン

F VL : 第1電圧ライン

S VL : 第2電圧ライン

Cst : 補助容量

M P 1 乃至 M P n 、 M P n + 1 乃至 M P 2 n : PMOSトランジスタ

M N 1 乃至 M N n : NMOSトランジスタ

R p 、 R c : 寄生抵抗

C p 、 C c : 寄生容量

S CL : 同期制御ライン

D CL : データクロックライン

G VL : 基底電圧ライン

Q 1 、 Q 2 : トランジスタ

V R : 可変抵抗

G ND L : 接地ライン

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図14】

【図15】

【図12】

【図13】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

A

B

【図23】

【図24】

【図25】

【図26】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 2 1 L

G 0 9 G 3/20 6 2 1 F

G 0 2 F 1/133 5 5 0

F ターム(参考) 2H093 NA16 NA42 NB30 NC03 NC04 NC10 NC22 NC34 NC35 NC62

NC65 ND10 ND12 ND58

5C006 AC11 AC22 AF42 AF72 BB16 BC03 BC06 BF03 BF37 BF42

BF46 FA14 FA23 FA34 FA41

5C080 AA10 BB05 DD06 DD08 DD22 DD29 EE29 FF01 FF07 FF11

JJ02 JJ03 JJ04 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 公开(公告)号        | <a href="#">JP2007304613A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2007-11-22 |

| 申请号            | JP2007168308                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2007-06-27 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | Eruji飞利浦杜迪股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | ヒュンチャンリー                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | ヒュン チャン リー                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133 G02F1/136 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| CPC分类号         | G09G3/3696 G09G3/3648 G09G3/3677 G09G2310/0289 G09G2310/066 G09G2320/0219 G09G2320/0223 G09G2320/0247 H03K17/164                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G09G3/36 G09G3/20.611.E G09G3/20.670.K G09G3/20.622.C G09G3/20.622.G G09G3/20.621.L G09G3/20.621.F G02F1/133.550                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA42 2H093/NB30 2H093/NC03 2H093/NC04 2H093/NC10 2H093/NC22 2H093/NC34 2H093/NC35 2H093/NC62 2H093/NC65 2H093/ND10 2H093/ND12 2H093/ND58 5C006/AC11 5C006/AC22 5C006/AF42 5C006/AF72 5C006/BB16 5C006/BC03 5C006/BC06 5C006/BF03 5C006/BF37 5C006/BF42 5C006/BF46 5C006/FA14 5C006/FA23 5C006/FA34 5C006/FA41 5C080/AA10 5C080/BB05 5C080/DD06 5C080/DD08 5C080/DD22 5C080/DD29 5C080/EE29 5C080/FF01 5C080/FF07 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 2H193/ZA04 2H193/ZC22 2H193/ZF03 2H193/ZF22 2H193/ZH40 |         |            |

| 优先权            | 1019980038842 1998-09-19 KR<br>1019990029144 1999-07-19 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 其他公开文献         | <a href="#">JP4764856B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

### 摘要(译)

要解决的问题：为了简化电路结构，同时消除有源矩阵液晶显示装置的闪烁和余像。栅极驱动器包括移位寄存器和电平移位，并且该电平移位分别连接在移位寄存器的n个输出端子QT1至QTn与n条栅极线GL1至GLn之间。n个控制开关39用于切换来自第一和第二电压线FVL和SVL的低电位和高电位栅极电压。高电位栅极电压产生器42包括高电位电压产生器44，电压调节器46和用于控制电压调节器46的电平调节定时的定时控制器48，并且逐渐地和逐渐地改变。并将具有下降部分的高电势栅极电压提供给第二电压线SVL。结果，提供给液晶面板30的栅极线GL的扫描信号的下降沿缓慢地变化。[选择图]图5