特開2003 - 107528

(P2003 - 107528A)

(43)公開日 平成15年4月9日(2003.4.9)

| (51) Int.CI <sup>7</sup> | 識別記号   | F I            | テ-マコード (参考) |

|--------------------------|--------|----------------|-------------|

| G 0 2 F 1/1368           |        | G 0 2 F 1/1368 | 2 H 0 9 2   |

|                          | 1/1345 | 1/1345         | 5 F 0 3 8   |

| H 0 1 L 21/822           |        | H 0 1 L 27/04  | H 5 F 1 1 0 |

|                          | 27/04  | 29/78          | 623 Z       |

|                          | 29/786 |                |             |

審査請求 未請求 請求項の数 170 L (全 7 数)

(21)出願番号 特願2002 - 190048(P2002 - 190048)

(22)出願日 平成14年6月28日(2002.6.28)

(31)優先権主張番号 2001 - 041251

(32)優先日 平成13年7月10日(2001.7.10)

(33)優先権主張国 韓国(KR)

(71)出願人 501426046

エルジー・フィリップス エルシーデー

カンパニー, リミテッド

大韓民国 ソウル, ヨンドゥンポ-ク, ヨイ

ド-ドン 20

(72)発明者 李 玄 揆

大韓民国 ソウル特別市 銅雀區 舍堂洞

アパート 112 - 403

(72)発明者 金 榮 九

大韓民国 忠清北道 清州市 興徳區 社

稷1洞 206 - 18

(74)代理人 100064447

弁理士 岡部 正夫 (外10名)

最終頁に続く

(54)【発明の名称】 液晶表示素子の静電放電防止回路及びその防止方法

## (57)【要約】

【課題】 ゲート・ラインおよびデータ・ラインへ、また、ゲート・ラインおよびデータ・ラインから静電気をより有効に分散させる、TFT-LCDのための静電放電防止回路を提供すること。

【解決手段】 液晶ディスプレイのための静電放電防止回路である。液晶ディスプレイは、第1の基板上の交差した複数のゲート・ラインおよびデータ・ラインと、データ短絡ラインと、ゲート短絡ラインとを備えている。複数の第1のESD防止ユニットがゲート短絡ラインをゲート・ラインに接続し、複数の第2のESD防止ユニットがデータ短絡ラインをデータ・ラインに接続している。第3の防止ユニットは、ゲート短絡ラインをデータ短絡ラインに接続している。共通電極は、第2の基板上に形成されている。第4のESD防止ユニットは、共通電極をデータ短絡ラインに直接接続している。

## 【特許請求の範囲】

【請求項1】 第1の基板上に行方向に形成された複数のゲート・ラインと、

第1の基板上に列方向に形成された複数のデータ・ライ

ンと、

第1の基板上に形成されたゲート短絡ラインと、

第1の基板上に形成されたデータ短絡ラインと、

第2の基板上に形成された共通電極と、

各ゲート・ラインをゲート短絡ラインに接続する複数の

第1のE S D防止ユニットと、

各データ・ラインをデータ短絡ラインに接続する複数の

第2のE S D防止ユニットと、

ゲート短絡ラインをデータ短絡ラインに接続する第3の

E S D防止ユニットと、

データ短絡ラインを共通電極に接続する第4のE S D防

止ユニットとを備える、液晶ディスプレイのための静電

放電防止回路。

【請求項2】 第1、第2、第3、および第4のE S D防

止ユニット同一デバイスである、請求項1に記載の回

路。

【請求項3】 第1のE S D防止ユニットが複数のト

ランジスタからなる、請求項1に記載の回路。

【請求項4】 E S D防止ユニットが、

それぞれ第1のラインに接続された第1のゲートおよび

第1のソース、および第1のドレインからなる第1のト

ランジスタと、

第1のドレインに接続された第2のゲート、第2のライ

ンに接続された第2のドレイン、および第1のラインに

接続された第2のソースからなる第2のトランジスタ

と、

第1のドレインに接続された第3のソース、それぞ

れ第2のラインに接続された第3のゲートおよび第3のド

レインからなる第3のトランジスタとを備える、請求項3

に記載の回路。

【請求項5】 E S D防止ユニットが、少なくとも2つ

のダイオードからなる、請求項1に記載の回路。

【請求項6】 防止ユニットが、

第1のラインに接続された陽極、および第2のラインに

接続された陰極を有する第1のダイオードと、

第1のラインに接続された陰極、および第2のラインに

接続された陽極を有する第2のダイオードとを備える、

請求項5に記載の回路。

【請求項7】 第1のE S D防止ユニットが、ゲート短

絡ラインに並列に接続される、請求項1に記載の回路。

【請求項8】 複数のE S D防止ユニットが、各ゲート

・ラインをゲート短絡ラインに接続する、請求項1に記

載の回路。

【請求項9】 第2のE S D防止ユニットが、ゲート短

絡ラインに並列に接続される、請求項1に記載の回路。

【請求項10】 複数のE S D防止ユニットが、各ゲート

・ラインをゲート短絡ラインに接続する、請求項1に記載の回路。

\*タ・ラインをデータ短絡ラインに接続する、請求項1に

記載の回路。

【請求項11】 ゲート・ロー・レベル電圧がゲート短

絡ラインに印加される、請求項1に記載の回路。

【請求項12】 共通電圧がデータ短絡ラインに印加さ

れる、請求項1に記載の回路。

【請求項13】 第1のE S D防止ユニットを介して、

ゲート・ラインとゲート短絡ラインの間の静電気を分散

させるステップと、

10 第2のE S D防止ユニットを介して、データ・ラインと

データ短絡ラインの間の静電気を分散させるステップ

と、

第3のE S D防止ユニットを介して、ゲート短絡ライン

とデータ短絡ラインの間の静電気を分散させるステップ

と、

第4のE S D防止ユニットを介して、データ短絡ライン

と共通電極の間の静電気を直接分散させるステップとを

含む、静電放電から液晶ディスプレイ装置を保護する方

法。

20 第3のE S D防止ユニットからの静電

気が、データ・ラインと共通電極の間をほぼ均等に分散

する、請求項13に記載の方法。

【請求項15】 データ・ライン中に静電気を発生させ

るステップと、

データ・ラインに接続されたE S D防止ユニットを介

して、データ短絡ラインに静電気を分散させるステップ

と、

データ短絡ラインに接続されたE S D防止ユニットを介

して、データ短絡ラインからの静電気をすべてのデータ

・ラインに分散させるステップと、

E S D防止ユニットを介して、データ短絡ラインからの

静電気を共通電極に直接分散させるステップとを含む、

液晶ディスプレイ装置の静電放電を防止する方法。

【請求項16】 データ短絡ラインを通過する静電気

が、データ・ラインと共通電極の間をほぼ均等に分散す

る、請求項15に記載の方法。

【請求項17】 第1のE S D防止ユニットを介して、

ゲート・ラインとゲート短絡ラインの間の静電気を分散

させるステップと、

第2のE S D防止ユニットを介して、データ・ラインと

データ短絡ラインの間の静電気を分散させるステップ

と、

第3のE S D防止ユニットを介して、ゲート短絡ライン

とデータ短絡ラインの間の静電気を分散させるステップ

と、

第4のE S D防止ユニットを介して、データ短絡ライン

とデータ短絡ラインに直接接続された共通電極との間の

静電気を均等に分散させるステップとを含む、静電放電

から液晶ディスプレイ装置を保護する方法。

【発明の詳細な説明】

## 【0001】

【発明の属する技術分野】本発明は、液晶ディスプレイ（LCD）装置の薄膜トランジスタ（TFT）を静電放電から保護する回路に関する。

【0002】陰極線管（CRT）は、多くのアプリケーションに対するディスプレイ装置の主流であったが、より小型、軽量、かつ、消費電力の少ない様々なフラット・パネル・ディスプレイ装置が開発されている。詳細には、極めて薄く、かつ、優れたカラー特性を有する薄膜トランジスタ液晶ディスプレイ装置（TFT-LCD）が広く開発され、当たり前になっている。

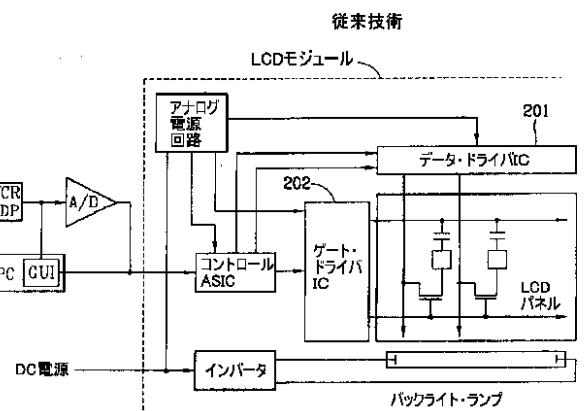

【0003】一般的には、液晶ディスプレイ装置は、マトリックス状に整列された画素に個別に印加されるデータ信号に対応するイメージを表示するための装置である。画素は光透過率を制御し、イメージを生成している。したがって、液晶ディスプレイ装置は、画素マトリックスおよび画素をドライブするためのドライバ集積回路（IC）の両方を備えている。

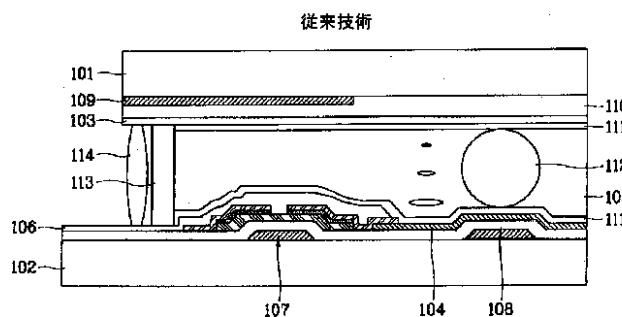

【0004】図1は、TFT-LCDディスプレイの部分切欠図を示す断面図であり、図2は、TFT-LCDを示す概略回路図である。以下、それぞれのコンポーネントについて、図面に照らして説明する。

【0005】TFT-Arrayディスプレイでは、TFT基板（図1の下部基板）が、1つまたは複数の金属層で形成され、絶縁層、アモルファス・シリコン層、インジウム・すず酸化物層（ITO）、および他の必要な元素がガラス基板102に蒸着されてTFT107を形成し、記憶コンデンサ108、画素電極104、および他の構造物が個々の画素を形成している。また、TFT基板は、画素マトリックスを形成するための、多重画素を相互接続するデータ・ラインを備えている。さらに、データ信号を印加するためのボンディング・パッド106が、各データ・ラインの端部に使用されている。

【0006】また、図1には、ガラス基板101上に形成されたカラー・フィルタ基板（図1の上部基板）が示されている。カラー・フィルタ基板は、選択的に光をブロックするブラック・マトリックス109（Crで有利に形成されている）、およびTFT基板の各画素を覆うRGBカラー・フィルタ110を備えている。さらに、共通電極を形成するITO薄膜103が、カラー・フィルタ基板の底部全体に蒸着されている。

【0007】基板上は、液晶分子を所定の方向に整列させるためのアインメント・フィルム111になっている。TFTおよびカラー・フィルタ基板は、スペーサ112によって均一に維持された間隙を形成している。液晶は、この間隙中に配置されている。

【0008】電気接続は、シルバー・ドット114によって、TFT基板の電圧印加端子とITO薄膜103の間に形成され、それにより共通電極（ITO薄膜103）への電圧の印加を可能にしている。

10

【0009】基板の円周の周りに配置されたパターン化シール113は、TFT-Array基板とカラー・フィルタ基板を固定する接着剤の役割を果たしている。また、シール113は、液晶を2つの基板の間に維持している。

【0010】図2を参照すると、TFT基板102上に、データ・ドライバ集積回路201から印加されるデータ信号を画素へ送信するための複数のデータ・ライン、およびゲート・ドライバ集積回路202から印加されるゲート信号を画素へ送信するための複数のゲート・ラインがある。データ・ラインおよびゲート・ラインは、直交状に形成されている。データ信号およびゲート信号が印加されるボンディング・パッド106（図1参照）は、データ・ラインおよびゲート・ラインの端部に形成されている。個々の画素は、データ・ラインとゲート・ラインの交点の近傍に配置されている。

【0011】ゲート・ドライバ集積回路202は、ライン毎に画素が選択されるように、複数のゲート・ラインにゲート信号を印加し、その選択されたライン内の画素にデータ信号が印加される。

【0012】TFT107（図1参照）は、スイッチング・デバイスとして使用され、個々の画素中に形成されている。ゲート信号がゲート・ラインを介してTFTのゲート電極に印加されると、TFTのソース電極とドレイン電極の間に導電チャネルが形成され、データ・ラインを介してTFTのドレイン電極に印加される印加データ信号が、その画素の光透過率を制御する。

【0013】ガラス基板101および102は絶縁体であるため、TFT-Arrayの製造プロセスの間に発生する静電気がガラス上に集中することになる。また、静電気は、様々な基板に加えられる様々な処理によっても発生する。このような静電気は、TFT-Arrayに対する静電放電損傷の原因となる。また、静電気は埃粒子をガラス基板に引き寄せ、TFT-Arrayおよびカラー・フィルタ・アレイの汚染の原因にもなっている。

【0014】静電気を少なくするために、TFT-LCDの製造に使用される製造設備および様々なプロセスを処理し、静電気を最少にすることもできるが、それでも、適切に設計されるTFT-Arrayは、静電放電に対する保護を組み込まなければならない。

【0015】TFT-Arrayに使用されるTFTデバイスは、相対エネルギー・レベルによってゲート絶縁膜が容易に破壊されるため、静電損傷を受けやすく、そのため、静電気は特に問題である。したがってTFT-Arrayを保護するためには、ゲート・ラインおよびデータ・ライン中への静電気の誘導を回避しなければならない。そのための方法の1つは、ゲート信号ラインとデータ信号ラインを電気的に短絡させることである。例えばゲート・ラインと隣接するデータ・ラインとの間に

50

静電気が発生する場合、その2本のラインを等電位にすることによって損傷を回避することができる。

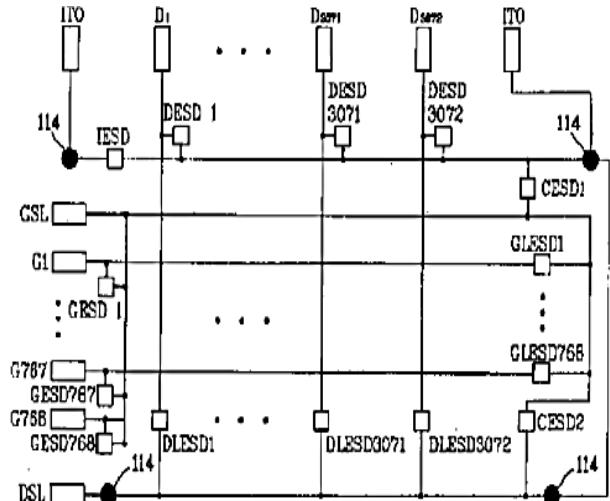

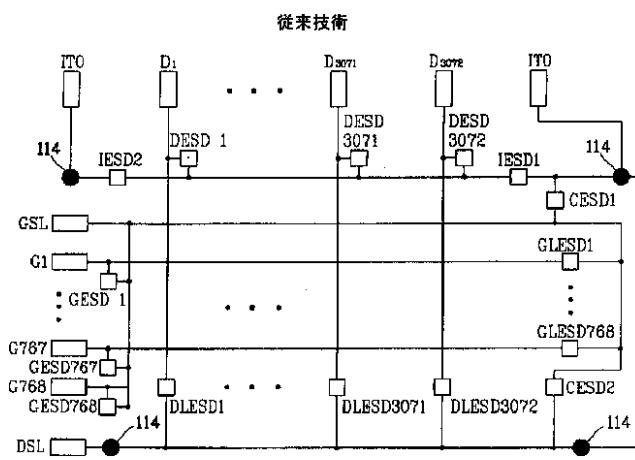

【0016】ゲート・ラインとデータ・ラインを直接接続することは有効ではあるが、このような直接接続は、信号ラインの断線、すなわち欠陥TFTを決定するための電気試験を妨げることになる。また、動作試験を実施することができない。そのために、静電放電損傷から保護し、かつ、個々の画素の試験を可能にする防止回路が開発されている。この防止回路は、各ゲート・ラインとゲート短絡ラインの間、および各データ・ラインとデータ短絡ラインの間に設けられるエレメントからなっている。図3は、防止回路を示したものである。

【0017】図3には、基板102上の行方向に形成された複数のゲート・ライン(G1～G768)が示されている。また、図3には、基板102上の列方向に形成された複数のデータ・ライン(D1～D3072)が示されている。さらに、ゲート短絡ラインGSL、データ短絡ラインDSL、および共通電極を形成しているITO層が示されている。ゲート短絡ラインはゲート・ロー・レベル電圧(Vg1)を受け取り、データ短絡ラインは共通電圧(Vcom)を受け取っている。

【0018】また、図3には、複数のゲート・ラインESD防止ユニットGESD1～GESD768、およびGLES1～GLES768、および複数のデータ・ラインESD防止ユニットDES1～DES3072、およびDLES1～DLES3072が示されている。ゲート・ラインESD防止ユニットは、ゲート・ラインG1～G768の前端部をゲート短絡ラインGSLに接続し、データ・ラインESD防止ユニットは、データ・ラインD1～D3072の前端部をデータ短絡ラインDSLに接続している。また、ESD防止連結ユニットCESD1およびCESD2は、ゲート短絡ラインGSLをデータ短絡ラインDSLに接続している。最後に、ESD防止誘導ユニットIESD1およびIESD2は、データ・ラインESD防止ユニットDES1～DES3072をITOに接続している。

【0019】イメージが生成されている間、現在ドライブされているゲート・ラインを除くすべてのゲート・ラインにロー・レベル電圧Vg1が印加される。現在ドライブされているラインは、ハイ・ゲート電圧を受け取り、そのラインに接続されているTFTをターン・オンさせる。したがってゲート・ライン電圧は、Vg1であるあるいはハイ・ゲート電圧であるかのいずれかである。図3に示す防止回路は、高(静的)電圧に対する保護であるため、ゲート短絡ラインGSLをゲート・ロー・レベル電圧Vg1に接続することが有利である。それにより防止デバイス(GESD1～GESD768など)に、ハイ・ゲート電圧とVg1の差(ハイ・ゲート電圧と接地の差ではなく)によるストレスがかかる。ESD防止ユニットの両端間に、雑音などの異常信号、あ

るいはロー・レベルの静電気が発生すると、ESD防止ユニットは、隣接するゲート・ラインに導き、かつ、衝撃を与えることができる。あるいは、ゲート電圧Vg1をゲート短絡ラインGSLに印加することにより、ESD防止ユニット(ハイ・レベル電圧を受け取っているESD防止ユニットを除く)の両端間の電圧が解消し、ESD防止ユニットの状態が安定する。また、データ短絡ラインDSLにVcomを印加することにより、DSLに接続されているESD防止ユニットが安定する。

【0020】以下、図3に示すESD防止回路の動作について説明する。先ず、ゲート・ラインG1～G768の1本に高電圧静電気が発生すると、ゲート・ラインG1～G768の前端部に取り付けられた関連するゲート・ラインESD防止ユニットGESD1～GESD768がターン・オンし、したがって、ゲート短絡ラインGSLおよび他のESD防止ユニット(双方向に作用する)により、静電気はすべてのゲート・ラインに分散される。さらに、ゲート・ラインG1～G768の後端部に接続されたゲート・ラインESD防止ユニットGLES1～GLES768がターン・オンし、したがって、静電気はゲート短絡ラインGSL(および、したがって他のゲート・ライン)に分散される。また、静電気は、連結ESD防止ユニットCESD1およびCESD2によってデータ短絡ラインDSLに分散される。

【0021】連結ESD防止ユニットCESD1およびCESD2を通過した電荷は、次にデータ短絡ラインDSLを介して、誘導ESD防止ユニットIESD1を通ってデータ・ラインD1～D3072へ、データ防止ユニットDES1～DES3072を介して分散される。また、データ短絡ラインDSL上の電荷は、データ・ラインESD防止ユニットDLES1～DLES3072を通して、データ・ラインD1～D3072へ分散される。したがって上記のプロセスにより、ゲート・ライン上の電荷は、すべてのゲート・ラインおよびデータ・ラインに分散される。さらに、防止ユニットはすべて双方向性であるため、データ・ライン上の電荷は、すべてのゲート・ラインおよびデータ・ラインに分散される。

【0022】図3に示す防止スキームは、有用であることが証明されているが、問題のあることが分かっている。例えば、誘導ESD防止ユニットIESD1は、本質的にデータ・ラインESD防止ユニットDES1～DES3072を連結ESD防止ユニットCESD1に接続している。誘導ESD防止ユニットIESD1は内部抵抗を有している。また、実際には、連結ESD防止ユニットCESD1を通過する静電気発生電荷のほとんどが、Agドット114を介して上部基板(ITO)中に分散することが実験によって分かっている。これは、上部基板の静電荷に対する抵抗が、誘導ESD防止ユニットIESD1より小さいことによるものであると

されている。したがって静電気の分散が、最善の状態より小さく、そのために静電気による損傷の可能性が増加している。

【0023】したがって、改良型ESD防止が有利である。詳細には、データ・ラインへ、また、データ・ラインから静電電荷をより良好に分散させる改良型ESD防止回路が有利である。

#### 【0024】

【発明が解決しようとする課題】したがって本発明の目的は、ゲート・ラインおよびデータ・ラインへ、また、ゲート・ラインおよびデータ・ラインから静電気をより有効に分散させる、TFT-LCDのための静電放電防止回路を提供することである。

#### 【0025】

【課題を解決するための手段】本発明の目的による利点を達成するために、本明細書において具体化され、かつ、広く説明されているように、基板上に複数の交差ゲート・ラインおよびデータ・ラインを有するLCDのための静電放電防止回路が提供される。基板は、データ短絡ライン(DSL)と、ゲート短絡ライン(GSL)とをさらに備えている。基板は、ゲート短絡ラインをゲート・ラインに接続するための複数の第1のESD防止ユニットと、データ短絡ラインをデータ・ラインに接続するための複数の第2のESD防止ユニットと、ゲート短絡ラインをデータ短絡ラインに接続するための第3のESD防止ユニットと、第2の基板上に共通電極とをさらに備えている。防止回路は、共通電極を第3のESD防止ユニットに直接接続する第4のESD防止ユニットをさらに備えている。

【0026】本発明の前述およびその他の目的、特徴、様態、および利点については、添付の図面に照らして行う、本発明についての以下の詳細な説明から、より明確になるであろう。

【0027】本発明をより深く理解することを目的とし、かつ、本明細書に組み込まれ、本明細書の一部を構成する添付の図面は、本発明の実施形態を示したもので、説明と共に本発明の原理を示している。

#### 【0028】

【発明の実施の形態】次に、本発明の図解実施形態を詳細に参照することにする。添付の図面に本発明の実施例が示されている。

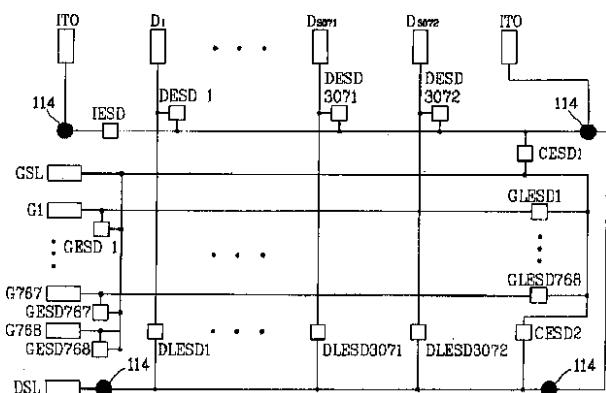

【0029】図4は、本発明の原理による薄膜トランジスタ液晶ディスプレイのためのESD防止回路を示す回路図である。便宜上、図1の参照番号が使用されている。

【0030】図に示すように、ESD防止回路は、複数のゲート・ラインG1～G768、およびゲート・ラインと交差するデータ・ラインD1～D3072を有する第1の基板を備えている。第1の基板は、ゲート・ロード・レベル電圧(Vg1)を受け取るゲート短絡ラインG

50 S L、および共通電圧(Vcom)を受け取るデータ短絡ラインDSLをさらに備えている。複数のゲート・ラインESD防止ユニットGESD1～GESD768は、ゲート・ライン(G1～G768)の前端部をゲート短絡ラインGSLに接続し、複数のゲート・ラインESD防止ユニットGLES1～GLES768は、ゲート・ライン(G1～G768)の後端部をゲート短絡ラインGSLに接続している。また、複数のデータ・ラインESD防止ユニットDES1～DES3072は、データ・ライン(D1～D3072)の前端部をデータ短絡ラインDSLに接続し、複数のデータ・ラインESD防止ユニットDLES1～DLES3072は、データ・ライン(D1～D3072)の後端部をデータ短絡ラインDSLに接続している。

【0031】さらに図4を参照すると、防止回路は、ゲート短絡ラインGSLをデータ短絡ラインDSLに接続する連結ESD防止ユニットCESD1およびCESD2をさらに備えている。また、共通電極ITOが第2の基板上に形成されている。共通電極ITOは、連結ESD防止ユニットCESD1およびCESD2に直接接続されている。さらに、誘導防止ユニットIESD1およびIESD2が、共通電極ITOを連結ESD防止ユニットCESD1およびCESD2に直接接続している。実際には、複数のシルバー・ドット114を使用して、第2の基板上にある共通電極と、第1の基板上にある連結ESD防止ユニットCESD1およびCESD2の間を接続している。

【0032】以下、図4に示す防止回路の動作を詳細に説明する。先ず、ゲート・ライン上に高電圧静電気が存在すると、ゲート・ラインESD防止ユニット(ユニットGESD1～GESD768のうちの1つ、およびユニットGLES1～GLES768のうちの1つ)によって、ゲート短絡ラインGSL上に電荷が分散される。さらに、ゲート・ラインESD防止ユニット(GESD1～GESD768、およびGLES1～GLES768)によって、ゲート短絡ラインGSLからゲート・ラインG1～G768中に電荷が分散される。したがって静電気は、すべてのゲート・ライン中に分散される。

【0033】また、ゲート短絡ラインGSL上の静電気は、連結ESD防止ユニットCESD1およびCESD2によってデータ短絡ラインDSL上に分散される。次に、データ短絡ラインDSL上に分散した静電気は、データ・ラインESD防止ユニットDES1～DES3071、およびユニットDLES1～DLES3072を介して、データ・ラインD1～D3072中に分散される。さらに、連結ESD防止ユニットCESD1およびCESD2を介して分散した静電気は、共通電極ITO中に直接引き渡されるか、あるいは誘導防止ユニットIESDの1つを介して、共通電極ITO中に直

接引き渡される。

【0034】有利なことには、誘導ESD防止ユニットIESD1が存在していないため、連結ESD防止ユニットCESD1およびCESD2を通過した電荷は、そのままデータ・ラインESD防止ユニット(DESD1～DESD3071、およびユニットDLESVD1～DLESVD3072)に直接印加される。従来技術で使用されている誘導ESD防止ユニットIESD1は、実際にESD防止の最大化を妨害し、静電気発生電荷を共通電極ITO中に導く傾向があることが実験で分かっている。

【0035】しかし、図4に示すように、誘導ESD防止ユニットIESD1を使用することなく、非対称構造を用いることにより、静電気をより安定かつ効率的に分散させることができる。つまり、データ・ラインD1～D3072を通って分散する静電気の量を増やすことができる。

【0036】すべての防止ユニットが双方向性であるため、データ・ライン上に発生する静電気も、同様に共通電極ITO、データ・ライン、およびゲート・ライン中に分散される。

【0037】本発明に従って動作するTFT-LCDは、耐静電気損傷が改善される。図5は、ESD防止ユニットの実施形態を示す回路図である。このESD防止ユニットは、TFT-Arrayと共に形成することができるTFTトランジスタからなっている。図に示すように、ESD防止ユニットは、第1のゲートG03、第1のソースS04、および第1のドレインD05を有する第1のトランジスタTR1を備えている。第1のゲートG03および第1のソースS04は、第1のラインL01に接続されている。ESD防止ユニットは、第1のドレインD05に接続された第2のゲートG06、第1のラインL01に接続された第2のソースS07、および第2のラインL02に接続された第2のドレインD08を有する第2のトランジスタTR2をさらに備えている。ESD防止ユニットは、第1のドレインD05および第2のゲートG06に接続された第3のソースS09、それぞれ第2のラインL02に接続された第3のゲートG10および第3のドレインD11を有する第3のトランジスタTR3をさらに備えている。

【0038】第1のトランジスタTR1のしきい電圧より高い電圧が第1のラインL01に印加される(例えば静電気などによって)と、第1のトランジスタTR1がターン・オンし、それにより第2のトランジスタTR2がターン・オンする。したがって、第1のラインL01および第2のラインL02が接続され、等電位が形成される。第3のトランジスタTR3のしきい電圧より高い\*

\*電圧が第2のラインL02に印加される(例えば静電気などによって)と、第3のトランジスタTR3がターン・オンし、それにより第2のトランジスタTR2がターン・オンする。したがって、第1のラインL01および第2のラインL02が接続され、等電位が形成される。しかし、第1のトランジスタTR1および第3のトランジスタTR3の両方がターン・オンしない場合は、第1のラインL01および第2のラインL02は接続されない。

【0039】図6は、ESD防止ユニットの他の実施形態を示す回路図である。図に示すように、ESD防止ユニットは、第1のラインL01と第2のラインL02の間に、並列かつ互いに逆極性に接続されたダイオードD1およびD2からなっている。ダイオードは、正常状態では動作しないが、ダイオードのしきい電圧より高い電圧が印加されると、第1のラインL01と第2のラインL02の間を電荷が流れる。

【0040】ESD防止ユニットの2つの実施例を示したが、本発明の原理は、他のESD防止ユニットにもそのまま適用することができる。

【0041】本発明によるTFTディスプレイ装置は、印加される静電気を有效地に分散させるESD防止回路を備えている。

【0042】本発明は、本発明の精神あるいは本質的な特徴を逸脱することなく、いくつかの形態で具体化することができるため、上で記述した実施形態は、他に特記なき場合、前述の説明の詳細に何ら制限されるものではなく、特許請求の範囲の各クレームの中で定義されている本発明の精神および範囲内において広義に解釈すべきものであり、したがって、各クレームの確立された限界の範疇であるすべての変更および改変、あるいはこのような確立された限界の等価物は、特許請求の範囲の各クレームに包含されるべきものであることを理解すべきである。

#### 【図面の簡単な説明】

【図1】薄膜トランジスタ液晶ディスプレイ(TFT-LCD)パネルの横断面図である。

【図2】TFT-LCDの概略回路図である。

【図3】従来技術による静電放電(ESD)防止を示す概略回路図である。

【図4】本発明の原理による静電放電(ESD)防止を示す概略回路図である。

【図5】図4に使用されているESD防止ユニットの実施形態を示す回路図である。

【図6】図4に使用されているESD防止ユニットの他の実施形態を示す回路図である。

【図1】

【図2】

【図3】

|                |                                                                                                                                                                                                                  |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示元件的静电放电防止电路及其防止方法                                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP2003107528A</a>                                                                                                                                                                                    | 公开(公告)日 | 2003-04-09 |

| 申请号            | JP2002190048                                                                                                                                                                                                     | 申请日     | 2002-06-28 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | Eruji. 菲利普斯杜天公司, 有限公司                                                                                                                                                                                            |         |            |

| [标]发明人         | 李玄揆<br>金榮九                                                                                                                                                                                                       |         |            |

| 发明人            | 李 ▼玄▲揆<br>金 榮 九                                                                                                                                                                                                  |         |            |

| IPC分类号         | G02F1/1368 G02F1/1345 G02F1/1362 H01L21/822 H01L27/04 H01L27/06 H01L29/786                                                                                                                                       |         |            |

| CPC分类号         | G02F1/136204                                                                                                                                                                                                     |         |            |

| FI分类号          | G02F1/1368 G02F1/1345 H01L27/04.H H01L29/78.623.Z                                                                                                                                                                |         |            |

| F-TERM分类号      | 2H092/JA01 2H092/JA24 2H092/JB79 2H092/NA14 5F038/BH04 5F038/BH07 5F038/BH13 5F038/EZ20 5F110/AA22 5F110/BB01 5F110/CC07 5F110/DD02 5F110/EE02 5F110/GG02 5F110/GG15 5F110/HK07 5F110/NN73 2H192/AA24 2H192/GA15 |         |            |

| 优先权            | 1020010041251 2001-07-10 KR                                                                                                                                                                                      |         |            |

| 其他公开文献         | JP4439163B2                                                                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                        |         |            |

## 摘要(译)

要解决的问题：提供一种用于TFT-LCD的防静电放电电路，该电路可以更有效地将静电分散至栅极线和数据线以及从栅极线和数据线中散出。用于液晶显示器的防静电放电电路。液晶显示器包括在第一基板上的多个相交的栅极线和数据线，数据短路线和栅极短路线。多个第一ESD保护单元将栅极短路线连接到栅极线，并且多个第二ESD保护单元将数据短路线连接到数据线。第三保护单元将栅极短路线连接到数据短路线。公共电极形成在第二基板上。第四ESD保护单元将公共电极直接连接到数据短路线。