(19)日本国特許庁( J P )

# 公開特許公報 ( A ) (11)特許出願公開番号

特開2002 - 258817

(P2002 - 258817A)

(43)公開日 平成14年9月11日(2002.9.11)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I           | テ-マコード <sup>*</sup> (参考) |

|--------------------------|------|---------------|--------------------------|

| G 0 9 G 3/36             |      | G 0 9 G 3/36  | 2 H 0 9 3                |

| G 0 2 F 1/133            | 550  | G 0 2 F 1/133 | 5 C 0 0 6                |

| G 0 9 G 3/20             | 612  | G 0 9 G 3/20  | 5 C 0 8 0                |

|                          | 621  | 612 U         | 621 A                    |

|                          |      |               | 621 F                    |

審査請求 未請求 請求項の数 19 O L (全 11数) 最終頁に続く

(21)出願番号 特願2001 - 142852(P2001 - 142852)

(71)出願人 390019839

三星電子株式会社

(22)出願日 平成13年5月14日(2001.5.14)

大韓民国京畿道水原市八達区梅灘洞416

(31)優先権主張番号 2001 - 7453

(72)発明者 李昇祐

(32)優先日 平成13年2月15日(2001.2.15)

大韓民国ソウル市錦泉区禿山1洞293 - 10番

(33)優先権主張国 韓国(KR)

地禿山現代アパート102棟1008号

(72)発明者 権秀現

大韓民国京畿道水原市勸善区金谷洞シンミ

ジュアパート1棟1010号

(74)代理人 100094145

弁理士 小野由己男 (外1名)

最終頁に続く

(54)【発明の名称】 液晶表示装置とその駆動装置及び駆動方法

(57)【要約】

【課題】 ランダムデータイネーブルモードでもプリチャージング方式の具現が可能な液晶表示装置とその駆動装置及び方法を提供する。

【解決手段】 データイネーブル信号のブランク区間に連動する発生間隔を有する垂直同期開始信号を不規則な出力区間に連動するデータイネーブル信号の印加により出力するタイミング制御部と；画像データを変換して出力するデータドライバー部と；現在ラインに最も近接する同一極性の以前ラインの駆動のための第1ゲートオン電圧と、現在ラインの駆動のための第2ゲートオン電圧とを同一ゲートラインに順次出力するスキャンドライバー部と；第1ゲートオン電圧によって第1充電され、第2ゲートオン電圧によって第2充電され、第2充電時に前記データドライバー部から提供される画像データをディスプレーするLCDパネルとを含む。

## 【特許請求の範囲】

【請求項1】外部から画像データの提供を受け、不規則な出力区間に連動し前記画像データの出力を制御するデータタイナーブル信号の印加によって前記データタイナーブル信号のブランク区間に連動する発生間隔を有する垂直同期開始信号を出力するタイミング制御部と、前記画像データを変換して出力するデータドライバー部と、

現在ラインに最も近接する同一極性の以前ラインの駆動のための第1ゲートオン電圧と、現在ラインの駆動のための第2ゲートオン電圧とを同一ゲートラインに順次出力するゲートドライバー部と、

前記ゲートドライバー部から提供される第1ゲートオン電圧によって第1充電され、前記第2ゲートオン電圧によって第2充電され、前記第2充電時に前記データドライバー部から提供される画像データをディスプレーするLCDパネルと、を含む液晶表示装置。

【請求項2】前記垂直同期開始信号は、前記第1ゲートオン電圧を発生するための信号と前記第2ゲートオン電圧を発生するための信号とを備えることを特徴とする請求項1に記載の液晶表示装置。

【請求項3】前記タイミング制御部は、

前記不規則な出力区間に有するデータタイナーブル信号を受信して所定ラインシフトされた内部データタイナーブル信号を出力する内部データタイナーブル変換部と、前記内部データタイナーブル変換部に印加されるデータタイナーブル信号の入力をチェックして第1スイッチング信号及び第2スイッチング信号を出力するカウンターと、前記所定ラインシフトされた内部データタイナーブル信号を受信して前記LCDパネルの駆動のための制御信号を30出力する制御信号生成部と、

一つの入力経路と複数の出力経路とを備え、前記第1スイッチング信号に応答して前記画像データ信号の出力経路を設定する第1スイッチング部と、

前記第1スイッチング部を経由して入力される画像データを各々保存した後、次のラインの画像データが印加されることにより既保存された画像データを各々出力する複数のメモリを備えるメモリ部と、

複数の入力経路と一つの出力経路とを備え、前記第2スイッチング信号に応答して前記メモリ部から出力される画像データの入力経路を設定し前記データドライバー部に前記画像データを出力する第2スイッチング部と、を含むことを特徴とする請求項1に記載の液晶表示装置。

【請求項4】前記所定ラインは少なくとも1ライン以上であることを特徴とする請求項3に記載の液晶表示装置。

【請求項5】前記内部データタイナーブル信号は同一極性的所定のライン数だけシフトされた入力データタイナーブル信号のライジングに同期して出力されることを特徴とする請求項3または請求項4に記載の液晶表示装置。

【請求項6】前記メモリはラインメモリであることを特徴とする請求項3に記載の液晶表示装置。

【請求項7】複数のデータラインと複数のゲートラインとを備えるLCDパネルを含み、特定画素の充電前に極性が同一な近接画素のデータで予め充電して画素の極性を予め変更した後に該当画素のデータで充電する液晶表示装置の駆動装置において、

外部から画像データの提供を受け、不規則な出力区間に連動して前記画像データの出力を制御するデータタイナーブル信号の印加によって前記データタイナーブル信号のブランク区間に連動する発生間隔を有する垂直同期開始信号を出力するタイミング制御部と、

前記画像データを変換して前記LCDパネルのデータラインに出力するデータドライバー部と、

前記垂直同期開始信号をもとに現在ラインに最も近接する同一極性の以前ラインの駆動のための第1ゲートオン電圧を前記LCDパネルのゲートラインに印加して第1充電し、現在ラインの駆動のための第2ゲートオン電圧を前記ゲートラインに印加して第2充電し、前記第2充電時に前記データドライバー部から提供される変換された画像データのディスプレイを制御するゲートドライバー部と、を含む液晶表示装置の駆動装置。

【請求項8】前記垂直同期開始信号は、前記第1ゲートオン電圧を発生するための信号と前記第2ゲートオン電圧を発生するための信号とを備えることを特徴とする請求項7に記載の液晶表示装置の駆動装置。

【請求項9】前記タイミング制御部は、

前記不規則な出力区間に有するデータタイナーブル信号を受信して所定ラインシフトされた内部データタイナーブル信号を出力する内部データタイナーブル変換部と、前記内部データタイナーブル変換部に印加されるデータタイナーブル信号の入力をチェックして第1スイッチング信号及び第2スイッチング信号を出力するカウンターと、前記所定ラインシフトされた内部データタイナーブル信号を受信して前記LCDパネルの駆動のための制御信号を出力する制御信号生成部と、

一つの入力経路と複数の出力経路とを備え、前記第1スイッチング信号に応答して前記画像データ信号の出力経路を設定する第1スイッチング部と、

前記第1スイッチング部を経由して入力される画像データを各々保存した後、次のラインの画像データが印加されることにより既保存された画像データを各々出力する複数のメモリを備えるメモリ部と、

複数の入力経路と一つの出力経路とを備え、前記第2スイッチング信号に応答して前記メモリ部から出力される画像データの入力経路を設定し前記データドライバー部に前記画像データを出力する第2スイッチング部と、を含むことを特徴とする請求項7に記載の液晶表示装置の駆動装置。

50 【請求項10】前記所定ラインは少なくとも1ライン以

上であることを特徴とする請求項9に記載の液晶表示装置の駆動装置。

【請求項11】前記内部データイネーブル信号は、同一極性の所定ライン数だけシフトされた入力データイネーブル信号のライジングに同期して出力されることを特徴とする請求項9または請求項10液晶表示装置の駆動装置。

【請求項12】前記メモリはラインメモリであることを特徴とする請求項9に記載の液晶表示装置の駆動装置。

【請求項13】複数のデータラインと複数のゲートラインとを備えるLCDパネルを含み、特定画素の充電前に極性が同一な近接画素のデータで予め充電して画素の極性を予め変更した後に該当画素のデータで充電する液晶表示装置の駆動方法において、

(a) 外部の画像信号ソースから画像データと、前記画像データの出力を制御するデータイネーブル信号とを受信する段階と、

(b) 前記データイネーブル信号の入力如何をチェックし、前記データイネーブル信号が入力されることにより内蔵された所定個数のメモリに前記画像データを順次記録し、記録された画像データを順次抽出し、前記画像データの抽出によって内部データイネーブル信号を発生して前記データイネーブル信号のブランク区間に連動する発生間隔を有する垂直同期開始信号を出力する段階と、

(c) 前記画像データに対応する電圧を前記データラインに供給する段階と、

(d) 前記垂直同期開始信号をもとに現在ラインに最も近接する同一極性の以前ラインの駆動のための第1ゲートオン電圧と、現在ラインの駆動のための第2ゲートオン電圧とを同時に順次供給する段階とを含む液晶表示装置の駆動方法。

【請求項14】前記メモリはラインメモリであることを特徴とする請求項13に記載の液晶表示装置の駆動方法。

【請求項15】前記垂直同期開始信号は、前記第1ゲートオン電圧を発生するための信号と前記第2ゲートオン電圧を発生するための信号とを備えることを特徴とする請求項13に記載の液晶表示装置の駆動方法。

【請求項16】前記所定個数は少なくとも1以上あることを特徴とする請求項13に記載の液晶表示装置の駆動方法。

【請求項17】前記内部データイネーブル信号は、同一極性の所定ライン数だけシフトされた入力データイネーブル信号のライジングに同期して出力されることを特徴とする請求項16に記載の液晶表示装置の駆動方法。

【請求項18】前記段階(b)でのデータ抽出時の前記垂直同期開始信号の出力は、

(b-11) ラインカウント値及び内部フラッグを初期化する段階と、

(b-12) 前記データイネーブル信号の存在如何をチ

\*エックする段階と、

(b-13) 前記段階(b-12)で前記データイネーブル信号が存在する場合には前記ラインカウント値を増加させて更新し、更新されたラインカウント値がゲートライン数に1を加算して得られる第1ライン数より大きいかどうかをチェックする段階と、

(b-14) 前記段階(b-13)で更新されたラインカウント値が前記第1ライン数より小さいか同じ場合には前記段階(b-12)にフィードバックし、更新されたラインカウント値が前記第1ライン数より大きいと判定される場合にはメモリ抽出フラッグ信号を生成した後にデータを抽出する段階と、

(b-15) 前記更新されたラインカウント値とゲートライン数とが同一であるかどうかをチェックし、同一でない場合には前記段階(b-12)にフィードバックする段階と、

(b-16) 前記更新されたラインカウント値とゲートライン数とが同一な場合及び前記段階(b-12)でデータイネーブル信号が存在しない場合には内部フラッグ信号を生成し、内部フラッグカウント値を増加させて更新する段階と、

(b-17) 前記更新された内部フラッグカウント値と前記第1ライン数とを比較して、前記内部フラッグカウント値が前記第1ライン数より大きい場合には終了し、前記内部フラッグカウント値が前記第1ライン数より小さいか同じ場合には前記段階(b-16)にフィードバックする段階とを含むことを特徴とする請求項13に記載の液晶表示装置の駆動方法。

【請求項19】前記段階(b)でのデータ記録時の垂直同期開始信号の出力は、

(b-21) ラインカウント値を初期化する段階と、

(b-22) 前記データイネーブル信号の存在如何をチェックし、前記データイネーブル信号が存在しない場合には終了し、前記データイネーブル信号が存在する場合にはラインカウント値を増加させて更新する段階と、

(b-23) メモリ記録フラッグ信号を生成してデータを記録する段階と

(b-24) 前記段階(b-22)で更新されたラインカウント値とゲートライン数とが同一であるかどうかをチェックし、同一である場合には終了し、同一でない場合には前記段階(b-22)にフィードバックする段階とを含むことを特徴とする請求項13に記載の液晶表示装置の駆動方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は液晶表示装置とその駆動装置及び駆動方法に係り、より詳しくは、ランダムデータイネーブルモードでもプリチャージング方式の具現が可能な液晶表示装置とその駆動装置及び方法に関する。

## 【0002】

【従来の技術】一般に、LCDは二枚の基板の間に注入された異方性誘電率を有する液晶物質に電界(Electric field)を印加し、この電界の強さを各画素毎に調節して基板を透過する光量を調節することによって所望の画像を得る表示装置である。このようなLCDは携帯容易なフラットパネル型ディスプレイ(FPD)のうち代表的なものであって、その中でも薄膜トランジスタ(Thin Film Transistor:TFT)をスイッチング素子として使用したTFTLCD 10Dが主に利用されている。

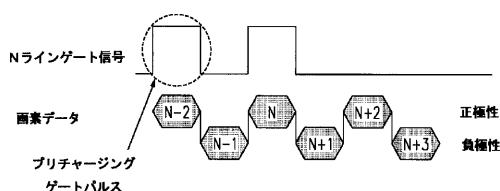

【0003】LCDの解像度が向上することに伴って画素の許容充電時間が急激に減少している。減少した充電時間を補償するために図1に示したようなプリチャージング(pre-charging)方法を用いる。ここで、プリチャージング方法とは、ある特定画素を時間によって極性を反転しながら充電させる時、極性が同一であり直後に充電されるべき近接画素に予め適当な電圧、例えば現在の画素データを充電して画素の極性を変えた後、該当画素のデータで充電する方法である。

【0004】一方、従来のゲート信号は一つのフレームに一度のみ現れるようになっている。しかし、図1に示したように、Nラインの画素に関する一般的なプリチャージング方法は、プリチャージングゲートパルスを追加してNラインの画素データで充電する前に極性が同一で直前に充電されるべきN-2ラインの画素データで予め充電することによって充電時間を補償する。

【0005】より詳しくは、プリチャージングゲートパルスを発生させることはゲートドライバーに入力される垂直同期開始信号STVを2つ続けて出力することでよく、このためにフレームブランク区間の間にカウンターを用いて指定された位置にSTVを予め発生させる方式を用いる。

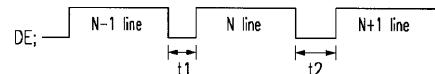

【0006】ところが、DEモード(Data Enable Mode)とは有効データが存在する区間にのみデータイネーブル信号DEをハイレベルとするものであって、前記有効データが存在する区間が不規則であってもLCDを駆動するのに問題があつてはならないが、実際に有効データが存在する区間が不規則になると既存のカウンターによる方法では問題が発生し、LCDが画面を表示できなくなる。

【0007】有効データの出力区間が不規則な場合、即ち、ランダムDEモード時には、図2に示したように、データイネーブル信号が低(LOW)となるブランク区間(例えば、t1、t2)が互いに一致しないため正常にLCD画面をディスプレイするのが難しいという問題点がある。

## 【0008】

【発明が解決しようとする課題】本発明はこのような従来の問題点を解決するためのものであって、本発明の目 50

的是データイネーブル信号が任意のタイミング(区間)に無作為入力されても全てのデータを異常無くディスプレイすることができる液晶表示装置を提供することにある。

【0009】また、本発明の他の目的は前記液晶表示装置の駆動装置を提供することにある。

【0010】また、本発明の他の目的は前記液晶表示装置の駆動方法を提供することにある。

## 【0011】

【課題を解決するための手段】前記本発明の目的を実現するための一つの特徴による液晶表示装置は、外部から画像データの提供を受け、不規則な出力区間に連動して前記画像データの出力を制御するデータイネーブル信号の印加によって前記データイネーブル信号のブランク区間に連動する発生間隔を有する垂直同期開始信号を出力するタイミング制御部と、前記画像データを変換して出力するデータドライバー部と、現在ラインに最も近接する同一極性の以前ラインの駆動のための第1ゲートオン電圧と、現在ラインの駆動のための第2ゲートオン電圧とを同一ゲートラインに順次出力するゲートドライバー部と、前記ゲートドライバー部から提供される第1ゲートオン電圧によって第1充電され、前記第2ゲートオン電圧によって第2充電され、前記第2充電時に前記データドライバー部から提供される画像データをディスプレーするLCDパネルとを含む。なお、ここで画像データとは、少なくとも1個の画素データを含む信号をいう。

【0012】また、前記本発明の他の目的を実現するための一つの特徴による液晶表示装置の駆動装置は、複数のデータラインと複数のゲートラインとを備えるLCDパネルを含み、特定画素の充電時に極性が同一な近接画素のデータに予め充電して画素の極性を予め変更した後に該当画素のデータに充電する液晶表示装置の駆動装置において、外部から画像データの提供を受け、不規則な出力区間を有して前記画像データの出力を制御するデータイネーブル信号の印加によって前記データイネーブル信号のブランク区間に連動する発生間隔を有する垂直同期開始信号を出力するタイミング制御部と、前記画像データを変換して前記LCDパネルのデータラインに出力するデータドライバー部と、前記垂直同期開始信号をもとにして現在ラインに最も近接する同一極性の以前ラインの駆動のための第1ゲートオン電圧を前記LCDパネルのゲートラインに印加して第1充電し、現在ラインの駆動のための第2ゲートオン電圧を前記ゲートラインに印加して第2充電し、前記第2充電時に前記データドライバー部から提供される変換された画像データのディスプレイを制御するスキャンドライバー部とを含む。

【0013】前記本発明の目的及び他の目的を実現するための一つの特徴によるタイミング制御部は、前記不規則な出力区間を有するデータイネーブル信号を受信して所定ラインシフトされた内部データイネーブル信号を出

力する内部D E 変換部と；前記内部D E 変換部に印加されるデータイネーブル信号の入力をチェックして第1スイッチング信号及び第2スイッチング信号を出力するカウンターと；前記所定ラインシフトされた内部イネーブル信号を受信して前記LCDパネルの駆動のための制御信号を出力する制御信号生成部と；一つの入力経路と複数の出力経路とを備え、前記第1スイッチング信号に応答して前記画像データ信号の出力経路を設定する第1スイッチング部と；前記第1スイッチング部を経由して入力される画像データを各々保存した後、次のラインの画像データが印加されることにより既保存された画像データを各々出力する複数のメモリを備えるメモリ部と；複数の入力経路と一つの出力経路とを備え、前記第2スイッチング信号に応答して前記メモリ部から出力される画像データの入力経路を設定して前記データドライバー部に前記画像データを出力する第2スイッチング部とを含むのが好ましい。

【0014】また、前記本発明の他の目的を実現するための一つの特徴による液晶表示装置の駆動方法は、複数のデータラインと複数のゲートラインとを備えるLCDパネルを含み、特定画素の充電前に極性が同一な近接画素のデータで予め充電して画素の極性を予め変更した後に該当画素のデータで充電する液晶表示装置の駆動方法において、(a)外部の画像信号ソースから画像データと、前記画像データの出力を制御するデータイネーブル信号を受信する段階と、(b)前記データイネーブル信号の入力如何をチェックし、前記データイネーブル信号が入力されることにより内蔵された所定個数のメモリに前記画像データを順次記録し、記録された画像データを順次抽出し、前記画像データの抽出によって内部データイネーブル信号を発生して前記データイネーブル信号のブランク区間に連動する発生間隔を有する垂直同期開始信号を出力する段階と、(c)前記画像データに対応する電圧を前記データラインに供給する段階と、(d)前記垂直同期開始信号をふまえて現在ラインに最も近接する同一極性の以前ラインの駆動のための第1ゲートオン電圧と、現在ラインの駆動のための第2ゲートオン電圧とを同時に順次供給する段階とを含む。

【0015】ここで、前記段階(b)でのデータ抽出時の前記垂直同期開始信号の出力は、(b-11)ラインカウント値及び内部フラグを初期化する段階と；(b-12)前記データイネーブル信号の存在如何をチェックする段階と；(b-13)前記段階(b-12)で前記データイネーブル信号が存在する場合には前記ラインカウント値を増加させて更新し、更新されたラインカウント値がゲートライン数に1を加算した第1ライン数より大きいかどうかをチェックする段階と；(b-14)前記段階(b-13)で更新されたラインカウント値が前記第1ライン数より小さいか同じ場合には前記段階(b-12)にフィードバックし、更新されたラインカ

10 ウント値が前記第1ライン数より大きいと判定される場合にはメモリ抽出フラグ信号を生成した後、データを抽出する段階と；(b-15)前記更新されたラインカウント値とゲートライン数とが同一であるかどうかをチェックし、同一でない場合には前記段階(b-12)にフィードバックする段階と；(b-16)前記更新されたラインカウント値とゲートライン数とが同一である場合及び前記段階(b-12)でデータイネーブル信号が存在しない場合には内部フラグ信号を生成し、内部フラグカウント値を増加させて更新する段階と、(b-17)前記更新された内部フラグカウント値と前記第1ライン数とを比較して、前記内部フラグカウント値が前記第1ライン数より大きい場合には終了し、前記内部フラグカウント値が前記第1ライン数より小さいか同じ場合には前記段階(b-16)にフィードバックする段階とを含むのが好ましい。

【0016】また、前記段階(b)でのデータ記録時の垂直同期開始信号の出力は、(b-21)ラインカウント値を初期化する段階と；(b-22)前記データイネーブル信号の存在如何をチェックして、前記データイネーブル信号が存在しない場合には終了し、前記データイネーブル信号が存在する場合にはラインカウント値を増加させて更新する段階と；(b-23)メモリ記録フラグ信号を生成してデータを記録する段階と；(b-24)前記段階(b-22)で更新されたラインカウント値とゲートライン数との同一如何をチェックして、同一の場合には終了し、同一でない場合には前記段階(b-22)にフィードバックする段階とを含むのが好ましい。

【0017】このような液晶表示装置及びその駆動装置及び駆動方法によると、入力されるデータイネーブル信号に依存しながらカウンターを使用するので入力データイネーブル信号が揺れても正確な位置にLCD制御信号を出力することができ、どんなに入力D Eが無作為に入力されても全てのデータを異常無くディスプレーすることができる。

#### 【0018】

【発明の実施の形態】以下、通常の知識を有する者が本発明を容易に実施することができるよう実施例について説明する。

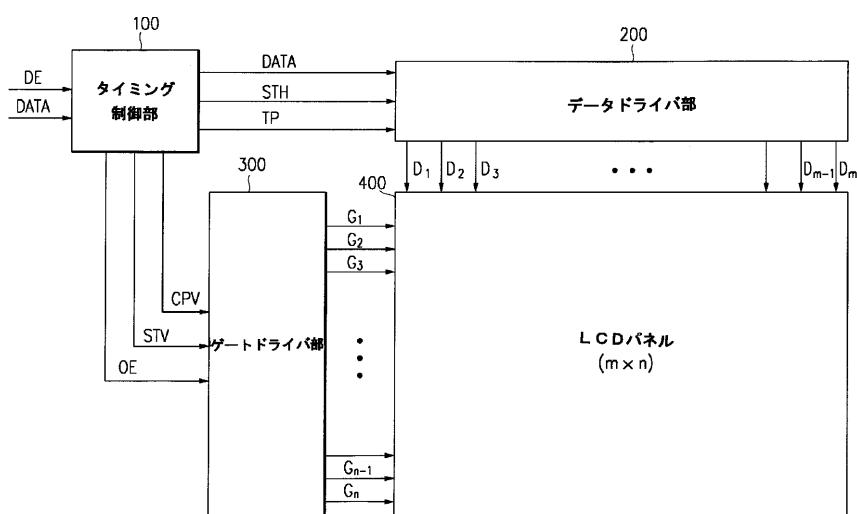

【0019】図3は本発明の実施例によるプリチャージング方式を有する液晶表示装置を説明するための図面である。

【0020】図3に示されているように、本発明の実施例によるプリチャージング方式を有する液晶表示装置はタイミング制御部100、データドライバー部200、ゲートドライバー部300及びLCDパネル400を含む。

【0021】タイミング制御部100は、外部のグラフィック制御機(図示せず)から印加されるRGBデータ

信号 (DATA) 及びデータイネーブル信号 (DE) を受信して、該当RGBデータ信号 (DATA)、RGBデータを伝送するための水平同期開始信号 (Start Horizontal; STH)、RGBデータ伝送完了後にデータドライブICへの出力を始めるためのTP (またはLOAD) 信号をデータドライバー部200に出力する。

【0022】また、タイミング制御部100は、外部のグラフィック制御機 (図示せず) から印加されるRGBデータ信号 (DATA) 及びデータイネーブル信号 (DE) を受信して、次のゲートラインを選択するゲートクロック信号 (CPV)、1番目のゲートラインの選択のための垂直同期開始信号 (Start Vertical; STV)、ゲートドライブICの出力を制御する出力イネーブル信号 (Out Enable; OE) をゲートドライバー部300に各々出力する。

【0023】特に、本発明によってタイミング制御部100から出力される垂直同期開始信号 (STV) は、実質的にゲートラインの駆動のためのゲートパルスと共に現在のゲートライン $G_n$ と極性の同一な最近接するゲートライン、例えば、(N-2)番目のゲートライン $G_{n-2}$ に印加される画素データのためのゲートパルス、即ちプリチャージングゲートパルスをさらに含む。

【0024】データドライバー部200は複数のデータドライブICからなり、タイミング制御部100から複数の制御信号 (STH、TP) によって複数のデータ信号をLCDパネル400に出力する。例えば印加されるTP信号に合せて順次に入るRGBそれぞれのデータをラッ칭 (Latching) して点順次方式 (Dot at a time scanning) のタイミング体系を線順次方式 (Line at a timescanning) に変えて複数のデータ信号 (D1、D2、...、D<sub>m-1</sub>、D<sub>m</sub>) をLCDパネル400のデータラインに出力する。

【0025】ゲートドライバー部300は複数のゲートドライブICからなり、タイミング制御部100から印加される制御信号 (CPV、STV、OE) によってゲートラインに順次にゲートオン電圧を印加し、TFTをターンオンさせる。

【0026】特に、本発明によってタイミング制御部100から印加される垂直同期開始信号 (STV) は、現在のゲートラインにゲートパルスを出力せよとの制御信号だけでなく、現在のゲートラインに最近接する同一極性の画素データに対するゲートパルスを出力せよとの制御信号まで含んでいるので、ゲートドライバー部300から出力されるゲートオン電圧は一つのフレームに2個を含まれている。したがって以前の最近接ラインのゲートパルスを用いて予め充電させた後に現在のラインのゲートパルスを用いてLCDパネルのゲートラインを実質的に駆動する。

【0027】ここで、最近接ラインが現在のラインの極性と同一な極性を有する以前の1番目のラインであることも可能で、以前の2番目或いは3番目などのラインであることも可能である。

【0028】LCDパネル400にはゲートドライバー部300から提供されるゲートオン信号を伝達するための多数のゲートラインが形成されており、データドライバー部200から提供されるデータ電圧を伝達するためのデータラインも形成されている。また、ゲートライン及びデータラインによって囲まれた領域は各々画素をなし、各画素はゲートライン及びデータラインに各々ゲート電極及びソース電極が連結される薄膜トランジスタ (TFT) (図示せず) と薄膜トランジスタのドレーン電極に連結される画素キャパシター (図示せず) とストレージキャパシター (図示せず) を含んで所定の画像情報を保持しながらディスプレイする。

【0029】特に、本発明の実施例によると、ゲートドライバー部300から印加されるゲートオン電圧は一つのフレームに2個のゲートパルスを備えているので、現在のフレームの駆動時に現在のゲートラインに印加されるデータの極性と同一な極性を有する最近接ラインのゲートパルスを用いて予め充電した後、現在のラインの駆動時にデータドライバー部200から印加されるRGB画像データをディスプレイする。

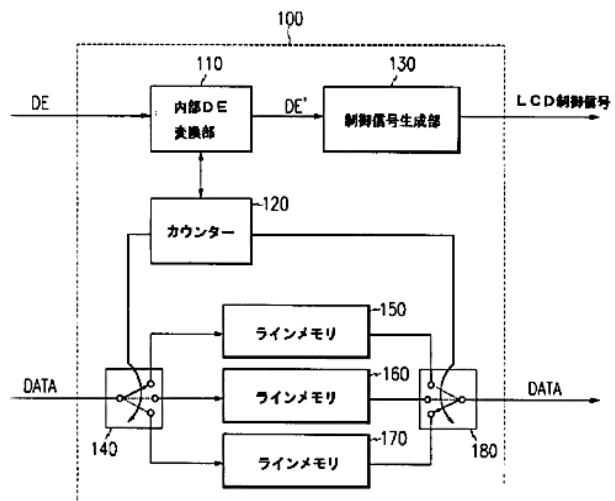

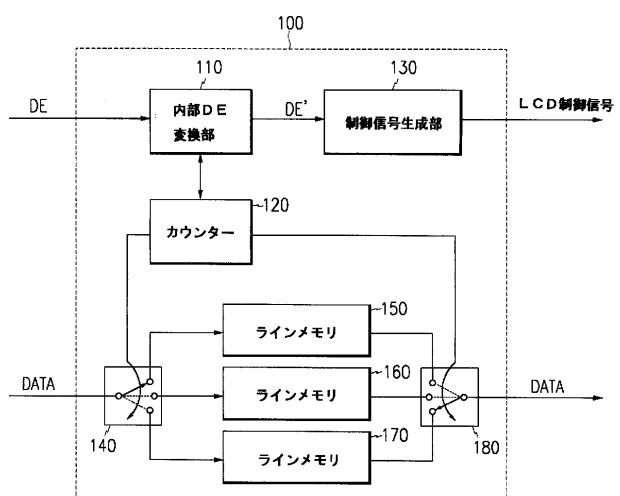

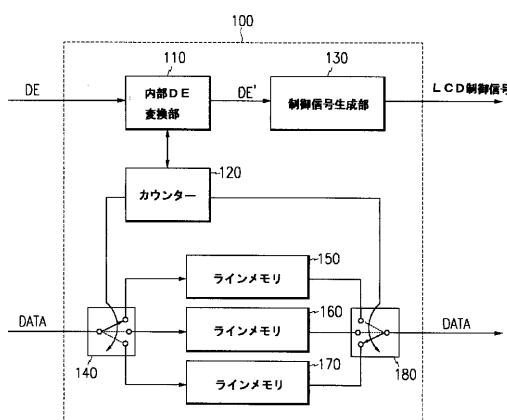

【0030】図4は前記タイミング制御部をより詳細に説明するための図面であり、図5は本発明の実施例によって出力されるランダムDEモードでプリチャージングのための垂直同期開始信号を説明するための波形図である。

【0031】図4を参照すると、本発明の実施例によるタイミング制御部100は、内部DE変換部110、カウンター120、制御信号生成部130、第1スイッチング部140、第1メモリ150、第2メモリ160、第3メモリ170、及び第2スイッチング部180を含む。

【0032】内部DE変換部110は、グラフィック制御機 (図示せず) から印加されるデータイネーブル信号 (DE)、より詳しくはランダムDE信号を受信して2ラインシフトされた内部データイネーブル信号 (DE') を制御信号生成部130に出力する。この時、内部データイネーブル信号 (DE') の出力タイミングはカウンター120のカウント動作に連動し、更に、内部データイネーブル信号 (DE') はランダムDE信号の3ライン目から入力DEのライジング (rising) に同期して出力される。ここで、連動とは信号の波形、遅延などは無視して、場合によっては低周波、高周波の関係で、緩やかな同期状態にあることを意味する。

【0033】カウンター120は、内部DE変換部110に印加されるランダムDE信号の入力をチェックし

て、各フレームのランダムDE信号の印加時に第1スイッチング信号を内部DE変換部110及び第1スイッチング部140に出力し、前記第1スイッチング信号と連動する第2スイッチング信号を第2スイッチング部180に出力する。

【0034】また、カウンター120から第1スイッチング信号を内部DE変換部110に出力して内部データタイネーブル信号の出力を制御し、内部データタイネーブル信号の生成時、最後の2ラインに該当する内部データタイネーブル信号については自動的に発生させることによって、損失された2ラインだけの内部データタイネーブル信号を補償することができる。この時のタイミング制御にはPLL(Phase Locked Loop)などを利用すれば、フライホイール効果により安定なタイミングが得られる。

【0035】この時、自動発生する内部データタイネーブル信号のブランク区間は特定内部データタイネーブル信号(例えば、直前のラインに対応して複写された内部データタイネーブル信号)の区間とすることことができ、または常に一定するように設定された区間とすることもできる。

【0036】制御信号生成部130は、内部DE生成部110から印加される2ラインシフトされた内部イネーブル信号(DE')を受信してLCDパネル400を駆動するための制御信号(STH、TP、CPV、STV、OEなど)をデータドライバー部200及びゲートドライバー部300に出力する。

【0037】特に、本発明の実施例によるプリチャージ方式を具現するための垂直同期開始信号(STV)は現在のゲートラインにゲートパルスを出力せよとの制御信号だけでなく、2ライン以前の画素のデータに対するゲートパルスを出力せよとの制御信号まで含んでゲートドライバー部300に印加される。

【0038】第1スイッチング部140は1ポート入力端子と3ポート出力端子とから構成され、グラフィック制御機(図示せず)から印加されるRGB画像データ信号をカウンター120から提供される第1スイッチング信号に応答して3ポート出力端子のうちのいずれか一つを通じて第1乃至第3メモリ150、160、170に順次に出力する。

【0039】第1乃至第3メモリ150、160、170は各々第1スイッチング部140を経由して入力されるRGB画像データを順次に保存した後、次のラインのRGB画像データが印加されることにより既保存されたRGB画像データを第2スイッチング部180に出力する。

【0040】より詳しくは、読み取り/書き取りが同時に行われるデュアルポートメモリで第1乃至第3メモリ150、160、170が構成される場合には、1番目乃至3番目画像データが第1乃至第3メモリ150、160、170に各々保存された後、4番目画像データが第50

1メモリに保存されることにより既保存された第1画像データを出力する方式が採用される。

【0041】一方、読み取り/書き取りが互いに独立して行われるシングルポートメモリで第1乃至第3メモリ150、160、170が構成される場合には、第1乃至第2画像データが第1乃至第2メモリ150、160に各々保存された後、3番目の画像データが第3メモリ170に保存されることにより既保存された第1画像データを出力する方式が採用される。

【0042】ここで、メモリは一つのゲートライン別に保存されたRGB画像データを同時に印加することができるラインメモリである。

【0043】第2スイッチング部180は3ポート入力端子と1ポート出力端子とから構成され、カウンター120から出力される第2スイッチング信号に応答して第1乃至第3メモリ150、160、170から印加されるRGB画像データをデータドライバー部200に各々出力する。

【0044】以上に説明したような本発明によるランダムDEモード下でプリチャージ方式を具現するための垂直同期開始信号(STV)の発生アルゴリズムは次の通りである。

【0045】まず、3個のラインメモリ150、160、170を用いて順次にRGB画像データを保存し、二つのライン(k、k+1番目のライン)に対するRGB画像データを第1及び第2メモリ150、160に各々保存する。

【0046】その次に、3番目のライン(k+2)に対するRGB画像データが第3ラインメモリ170に保存のため入力される間、第1メモリ150に保存された2ライン以前のデータ(k)をデータドライバー部200に出力する。

【0047】その次に、入力DE信号の3番目ラインから入力DE信号のライジング(rising)に同期して内部DE(DE')を生成する。その理由は、全てのLCD制御信号(STH、HCLK、OE、CPVなど)はDE信号を基準に生成されるので内部的に用いられるDE信号(DE')も2ライン後に発生しなければならないためである。

【0048】しかし、このような方式によって内部データタイネーブル信号(DE')を発生させると、最後の二つのラインに該当する内部DEは生成することができない。これを解決するために、カウンター120を用いて現在入力されるデータに対して何番目の内部DEが生成されたか確認し、最後の二つのラインに該当する内部データタイネーブル信号(DE')を生成しなければならない時、自動的に内部データタイネーブル信号(DE')を生成させる。この時、内部データタイネーブル信号(DE')のブランク幅は一般的なデータタイネーブル信号のブランク幅とする。

【0049】以下、前記ランダムDEモード下でプリチャージング方式を具現するための垂直同期開始信号の発生アルゴリズムに基づいてラインメモリからデータを抽出するための方法及びラインメモリにデータを記録するための方法を各自説明する。

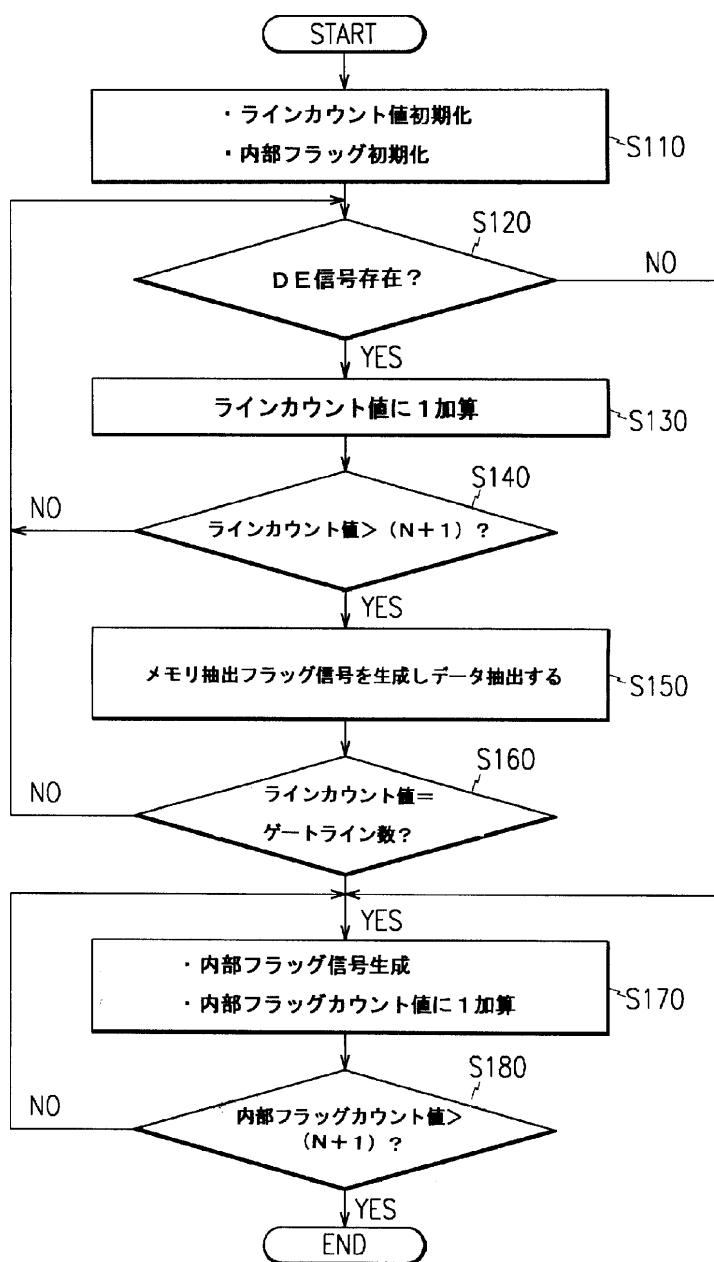

【0050】図6は本発明の実施例によるラインメモリからのデータ抽出時の垂直同期開始信号の発生を説明するためのフローチャートである。

【0051】図6を参照すると、まず、ラインカウント値を‘0’で初期化し、内部フラッグも‘0’で初期化する(段階S110)。ここで、内部フラッグはデータイネーブル(DE)信号のない区間でメモリの抽出部分を作るために形成される信号である。

【0052】その次に、データイネーブル(DE)信号が存在するかどうかをチェックして(段階S120)、DE信号が存在する場合にはラインカウント値に‘1’を追加して更新した後(段階S130)、更新されたラインカウント値がゲートライン数に1を加算した数(N+1)より大きいかどうかをチェックする(段階S140)。ここで、ゲートライン数は連続する二つの垂直同期開始信号(STV)の間に順次起動されるべきゲートラインの数である。

【0053】段階S140で更新されたラインカウント値がゲートライン数に1を加算した数(N+1)より大きないと判定される場合には段階S120にフィードバックし、更新されたラインカウント値がゲートライン数に1を加算した数(N+1)より大きいと判定される場合にはメモリ抽出フラッグ信号を生成してデータを抽出する(段階S150)。

【0054】その次に、ラインカウント値がゲートライン数と同一であるかどうかをチェックして(段階S160)、同一でないと判定される場合には段階S120にフィードバックする。

【0055】また、段階S160でラインカウント値がゲートライン数と同一であると判定される場合及び段階S120でデータイネーブル信号(DE)が存在しないとチェックされる場合には内部フラッグ信号を生成し、内部フラッグカウント値を‘1’追加して更新する(段階S170)。

【0056】その次に、更新された内部フラッグカウント値がラインメモリの数に1を加算した数(N+1)より大きいかどうかをチェックして(段階S180)、内部フラッグ値がゲートライン数に1を加算した数(N+1)より小さい場合には段階S170にフィードバックし、内部フラッグ値がゲートライン数に1を加算した数(N+1)より大きいと同じ場合には終了する。

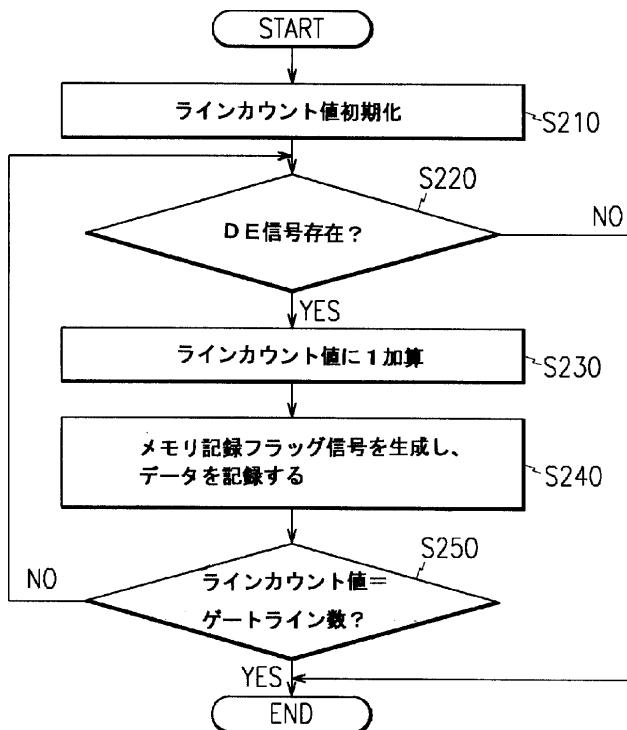

【0057】図7は本発明の実施例によるラインメモリにデータ記録時の垂直同期開始信号の発生を説明するためのフローチャートである。

【0058】図7を参照すると、まず、ラインカウント\*

\*値を初期化した後(段階S210)、データイネーブル信号(DE)が存在するかどうかをチェックする(段階S220)。

【0059】段階S220でデータイネーブル信号(DE)が存在すると判定される場合にはラインカウント値を‘1’追加して更新し(段階S230)、メモリ記録フラッグ信号を生成してデータを記録する(段階S240)。

【0060】その次に、更新されたラインカウント値がゲートライン数と同一であるかどうかをチェックして(段階S250)、更新されたラインカウント値が垂直ライン数と同一でないと判定される場合には段階S220にフィードバックし、更新されたラインカウント値がゲートライン数と同一であると判定される場合には終了する。

【0061】以上に説明したように、プリチャージング方法を用いる液晶表示装置でRGB画像データの出力を制御するデータイネーブル信号がランダム(無作為)に印加されても内部データイネーブル信号を入力データイネーブル信号に対して2ライン後段で入力されるデータイネーブル信号のライジングに同期して発生することにより、LCD制御信号の発生間隔を変更することができて正常に画像表示を遂行することができる。

【0062】ここで、内部データイネーブル信号の生成時、最後の2ラインに該当する内部データイネーブル信号に対しては内蔵されたカウンターを用いて自動的に発生させることによって、失われた2ラインだけの内部データイネーブル信号を補償することができる。この時、自動発生する内部データイネーブル信号のブランク区間は常に一定となるようになることが好ましい。

【0063】前記では本発明の好ましい実施例を参照して説明したが、該当技術分野の熟練した当業者は下記の特許請求の範囲に記載された本発明の思想及び領域から離れない範囲内で本発明を多様に修正及び変更させ得ることを理解することができる。

【0064】

【発明の効果】以上のように、本発明によると外部のグラフィック制御機から印加される入力データイネーブル信号に依存しながら内蔵されたカウントを用いることによって入力データイネーブル信号の位置がランダム(無作為)に入力されても正確な位置にLCD制御信号を出力することができるので、データイネーブル信号が無作為に入力されても全てのデータを異常無くディスプレーすることができる。

【図面の簡単な説明】

【図1】プリチャージングゲートパルスを説明するための波形図である。

【図2】ランダムDEモードでデータイネーブル信号のブランク区間を説明するための波形図である。

【図3】本発明の実施例によるプリチャージング方式を

有する液晶表示装置を説明するための図面である。

【図4】前記タイミング制御部をより詳細に説明するための図面である。

【図5】本発明の実施例によって出力されるランダムDEモードでプリチャージングのための垂直同期開始信号を説明するための波形図である。

【図6】本発明の実施例によるメモリからのデータ抽出時の垂直同期開始信号発生を説明するためのフローチャートである。

【図7】本発明の実施例によるメモリへのデータ記録時の垂直同期開始信号発生を説明するためのフローチャートである。

【符号の説明】

- \* 100 タイミング制御部

- 110 内部DE変換部

- 120 カウンター

- 130 制御信号生成部

- 140 第1スイッチング部

- 150 第1メモリ

- 160 第2メモリ

- 170 第3メモリ

- 180 第2スイッチング部

- 200 データドライバ部

- 300 ゲートドライバ部

- 400 LCDパネル

\*

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

フロントページの続き

|                                           |                        |                     |                                              |

|-------------------------------------------|------------------------|---------------------|----------------------------------------------|

| (51) Int.CI. <sup>7</sup><br>G 0 9 G 3/20 | 識別記号<br>6 2 2<br>6 2 3 | F I<br>G 0 9 G 3/20 | テマコト <sup>®</sup> (参考)<br>6 2 2 Q<br>6 2 3 Y |

|-------------------------------------------|------------------------|---------------------|----------------------------------------------|

|                                                            |                                                                                                                                                                                                        |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (72)発明者 田 萬 福<br>大韓民国京畿道龍仁市器興邑舊葛里405 -<br>1番地舊葛豊林アパート1108号 | F ターム(参考)<br>2H093 NA31 NC27 NC34 ND41<br>5C006 AC23 AC24 AC27 AF42 AF44<br>AF51 AF53 AF54 AF61 AF71<br>BB11 BC03 BC12 BF05 BF14<br>BF22 FA11<br>5C080 AA10 BB05 DD07 DD08 FF09<br>GG12 JJ02 JJ04 JJ07 |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置，驱动装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP2002258817A</a>                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2002-09-11 |

| 申请号            | JP2001142852                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2001-05-14 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 李昇祐<br>權秀現<br>田萬福                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 发明人            | 李昇祐<br>權秀現<br>田萬福                                                                                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                        |         |            |

| CPC分类号         | G09G3/3677 G09G2310/0251 G09G2320/0252 G09G2340/16                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.612.U G09G3/20.621.A G09G3/20.621.F G09G3/20.622.Q<br>G09G3/20.623.Y                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号      | 2H093/NA31 2H093/NC27 2H093/NC34 2H093/ND41 5C006/AC23 5C006/AC24 5C006/AC27 5C006<br>/AF42 5C006/AF44 5C006/AF51 5C006/AF53 5C006/AF54 5C006/AF61 5C006/AF71 5C006/BB11<br>5C006/BC03 5C006/BC12 5C006/BF05 5C006/BF14 5C006/BF22 5C006/FA11 5C080/AA10 5C080<br>/BB05 5C080/DD07 5C080/DD08 5C080/FF09 5C080/GG12 5C080/JJ02 5C080/JJ04 5C080/JJ07<br>2H193/ZA04 |         |            |

| 优先权            | 1020010007453 2001-02-15 KR                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                          |         |            |

## 摘要(译)

提供一种即使在随机数据使能模式下也能够实现预充电方法的液晶显示装置及其驱动装置和方法。定时控制单元，通过施加以不规则的输出间隔互锁的数据使能信号，来输出具有与数据使能信号的空白间隔互锁的生成间隔的垂直同步开始信号；并转换并输出图像数据。扫描驱动器，其将第一栅极导通电压顺序输出至同一栅极线，该第一栅极导通电压用于驱动与当前线最接近的相同极性的前一条线；以及第二栅极导通电压，用于驱动当前线。以及一种LCD面板，其首先由第一栅极导通电压充电，然后由第二栅极导通电压充电，并且在第二充电期间显示从数据驱动器单元提供的图像数据。