(19)日本国特許庁 (JP)

(12) 公開特許公報 (A) (11)特許出願公開番号

特開2001 - 56475

(P2001 - 56475A)

(43)公開日 平成13年2月27日(2001.2.27)

(51) Int.CI<sup>7</sup>

識別記号

庁内整理番号

F I

技術表示箇所

G 02 F 1/1343

G 02 F 1/1343

1/1368

1/136 500

審査請求 未請求 請求項の数 60 L (全 6 数)

(21)出願番号 特願2000 - 197138(P2000 - 197138)

(71)出願人 591024111

現代電子産業株式会社

大韓民国京畿道利川市夫鉢邑牙美里山136 - 1

(22)出願日 平成12年6月29日(2000.6.29)

(72)発明者 金恩植

大韓民国 京畿道 利川市 大月面 441 - 1番地 現代電子アパート 106 - 702

(31)優先権主張番号 1999/P25223

(72)発明者 李泳根

大韓民国 京畿道 利川市 夫鉢邑 牙美 3里 現代3次アパート 301 - 1201

(32)優先日 平成11年6月29日(1999.6.29)

(74)代理人 100093399

弁理士 濑谷徹 (外1名)

(33)優先権主張国 韓国(KR)

(54)【発明の名称】 フリンジフィールド駆動液晶表示装置

(57)【要約】

【目的】 本発明は、フリンジフィールドの垂直成分を最小化して、画質特性を改善できるフリンジフィールド駆動液晶表示装置を提供する。

【構成】 本発明は、下部基板；前記下部基板上に所定方向に延長されたゲートバスライン；前記ゲートバスラインと交差するように配置されて単位画素を限定するデータバスライン；前記ゲートバスラインとデータバスラインの交差部に各々配置された薄膜トランジスタ；前記単位画素空間に各々形成され、共通信号を印加し続ける四角板状のカウンタ電極；及び、前記薄膜トランジスタと電気的に連結して、前記カウンタ電極と共にフリンジフィールドを形成するように前記カウンタ電極上にオーバーラップされる多数の櫛歯部を含む画素電極を含み、前記カウンタ電極は多数のスリットを含み、前記スリットは画素電極の櫛歯部間に各々備えられ、前記カウンタ電極及び画素電極は透明導電体で形成されることを特徴とする。

**【特許請求の範囲】**

【請求項1】 下部基板；前記下部基板上に所定方向に延長されたゲートバスライン；前記ゲートバスラインと交差するように配置されて単位画素を限定するデータバスライン；前記ゲートバスラインとデータバスラインの交差部に各々配置された薄膜トランジスタ；前記単位画素空間に各々形成され、共通信号を印加し続ける四角板状のカウンタ電極；及び、

前記薄膜トランジスタと電気的に連結して、前記カウンタ電極と共にフリンジフィールドを形成するように前記カウンタ電極上にオーバーラップされる多数の櫛歯部を含む画素電極を含み、

前記カウンタ電極は多数のスリットを含み、前記スリットは画素電極の櫛歯部間に各々備えられ、

前記カウンタ電極及び画素電極は透明導電体で形成されることを特徴とする、フリンジフィールド駆動液晶表示装置。

【請求項2】 前記スリットの長軸が前記櫛歯部と平行であることを特徴とする、請求項1記載のフリンジフィールド駆動液晶表示装置。

【請求項3】 前記スリットの長軸及び前記櫛歯部の長軸はデータバスラインと平行であることを特徴とする、請求項1記載のフリンジフィールド駆動液晶表示装置。

【請求項4】 前記カウンタ電極のスリットの短縮幅は前記画素電極の櫛歯部間の間隔より小であることを特徴とする、請求項1記載のフリンジフィールド駆動液晶表示装置。

【請求項5】 下部基板；前記下部基板上に所定方向に延長されたゲートバスライン；前記ゲートバスラインと交差するように配置されて単位画素を限定するデータバスライン；前記ゲートバスラインとデータバスラインの交差部に各々配置された薄膜トランジスタ；前記単位画素空間に各々形成され、共通信号を印加し続ける四角板状のカウンタ電極；及び、

前記薄膜トランジスタと電気的に連結して、前記カウンタ電極と共にフリンジフィールドを形成するように、前記カウンタ電極上にオーバーラップされながら前記データバスラインと平行な多数の櫛歯部を含む画素電極を含み、

前記カウンタ電極は前記櫛歯部と平行な多数のスリットを含み、前記スリットは画素電極の櫛歯部間に各々備えられ、

前記カウンタ電極及び画素電極は透明導電体で形成されることを特徴とする、フリンジフィールド駆動液晶表示装置。

【請求項6】 前記カウンタ電極のスリットの短縮幅は前記画素電極の櫛歯部間の間隔より小であることを特徴とする、請求項5記載のフリンジフィールド駆動液晶表示装置。

**【発明の詳細な説明】**

**【0001】**

【発明の属する技術分野】本発明は、フリンジフィールド駆動液晶表示装置に関し、より詳しくはカウンタ電極と画素電極との間に発生するフリンジフィールドの垂直成分を低減できるフリンジフィールド駆動液晶表示装置に関する。

**【0002】**

【従来の技術】一般に、フリンジフィールド駆動液晶表示装置(以下、FFS-LCD)は、IPS(inplane switching)-LCDの低い開口率及び透過率を改善させるために提案されたもので、これに対する大韓民国特許出願第98-9243号が出願された。

【0003】こうしたFFS-LCDは、所定セルギャップをおいて離れた上部及び下部基板、上部及び下部基板間に介在された液晶層、並びに下部基板の内側面に形成されたカウンタ電極及び画素電極を含む。カウンタ電極及び画素電極は透明導電体で形成され、カウンタ電極と画素電極との間隔はセルギャップより狭い。これにより、電極間及び電極上にフリンジフィールドが形成される。

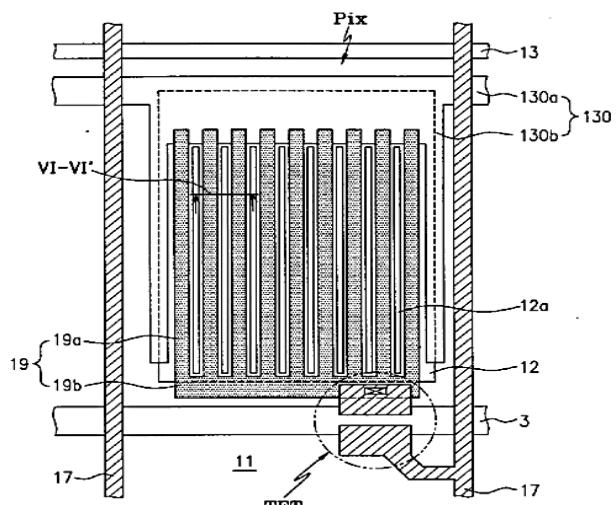

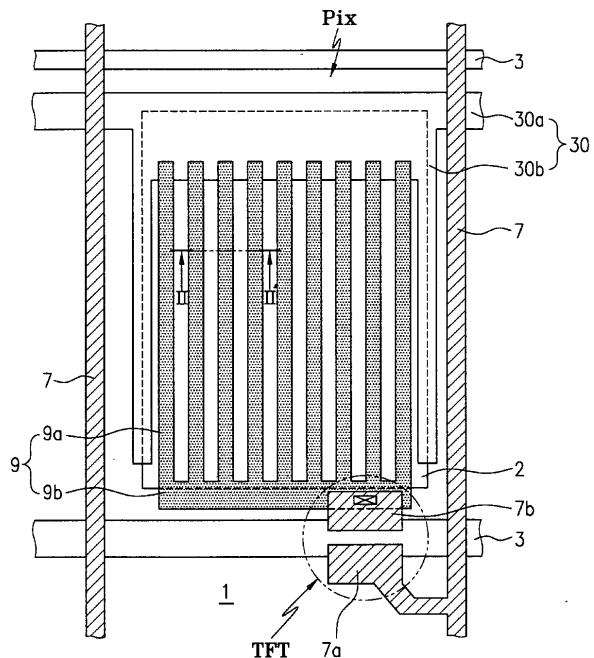

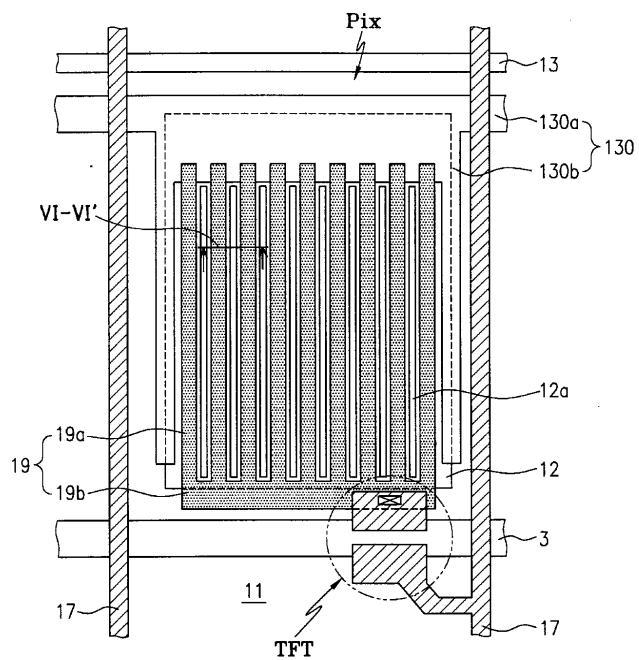

【0004】図1はFFS-LCDの下部基板構造を示す平面図である。図1を参照して、ゲートバスライン3及びデータバスライン7は、下部基板1上に交差配列されて単位画素 $P_{i\times}$ が限定される。薄膜トランジスタTFTはゲートバスライン3とデータバスライン7の交点近傍に配置される。カウンタ電極2は透明導電体で形成され、単位画素 $p_{i\times}$ 別にそれぞれ形成される。このとき、カウンタ電極2は四角板状あるいは櫛形状で形成できる。共通信号線30はカウンタ電極2に持続的に共通信号を供給する為に、カウンタ電極2とコンタクトされるように配置される。このとき、共通信号線30は信号伝達特性が優秀な金属膜で形成され、一般にはゲートバスライン用金属膜で形成される。しかも、共通信号線30は、ゲートバスライン3と平行でカウンタ電極2の所定部分とコンタクトされる第1部分30aと、第1部分30aからデータバスライン7と平行に延長されながらカウンタ電極2とデータバスライン7との間に各々配置される第2部分30bとを含む。画素電極9はカウンタ電極2とオーバーラップされるように単位画素 $p_{i\times}$ に形成される。このとき、画素電極9とカウンタ電極2は電気的に絶縁される。画素電極9は櫛形状で形成され、データバスライン7と平行で等間隔に形成された多数の櫛歯部9aと、櫛歯部9aの一端を連結しながら薄膜トランジスタTFTの所定部分とコンタクトされるバー9bとを含む。一方、図には示さないが、下部基板1と対向する上部基板は画素電極9とカウンタ電極2との距離よりも大きく対向する。

【0005】こうしたフリンジフィールド駆動液晶表示装置は、次のように動作する。カウンタ電極2と画素電極9との間に電界が形成されると、カウンタ電極2と画

素電極9との間の距離、すなわちゲート絶縁膜の厚さより上部及び下部基板の距離が大きいので、両電極間及び電極上にフリンジフィールドが形成される。このフリンジフィールドはカウンタ電極2及び画素電極9上の全域に渡っているため、電極上にある液晶分子らを共に動作させる。これにより、高開口率及び高透過率を実現できる。

#### 【0006】

【発明が解決しようとする課題】しかしながら、従来のフリンジフィールド駆動液晶表示装置は、次の様な問題点を有する。まず、フリンジフィールド駆動液晶表示装置は、画素電極の櫛歯9aとカウンタ電極との間の距離が、セルギャップ(上部及び下部基板間の距離)より狭く配置されるので、フリンジフィールドに垂直成分が存在することになる。

【0007】こうしたフリンジフィールドの垂直成分は電極上の領域で発生し、基板と長軸が略平行に配列されるべき液晶分子らが、基板と長軸が略垂直に配列される。これにより、液晶分子らが非正常に配列されて画質欠陥を発生させる。

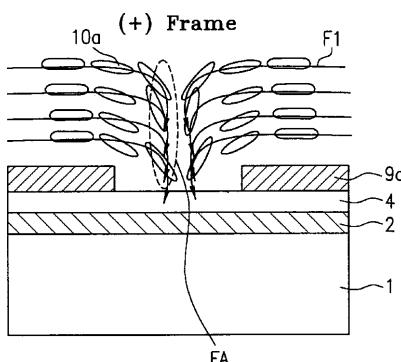

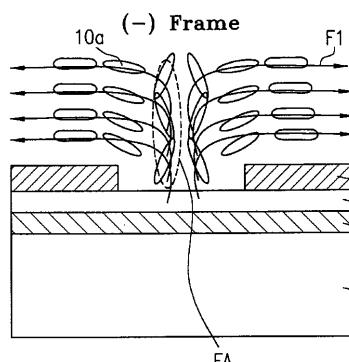

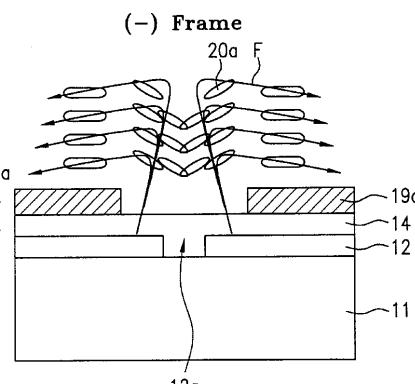

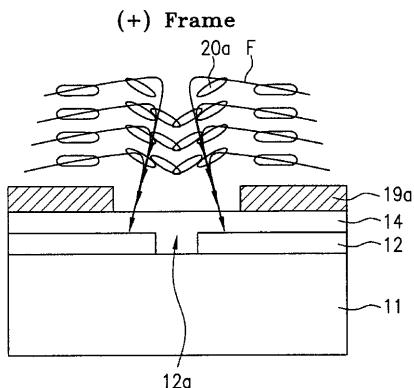

【0008】さらに、フリンジフィールドの垂直成分FAは、図2及び図3に示すように、LCDの(+)フレームと(-)フレーム別に互いに異なる形態で形成される。これにより、(+)フレーム状態における液晶分子10aの配列と、(-)フレーム状態における液晶分子10aの配列とが互いに異なり、互いに輝度差が発生する。この輝度差の発生のため、液晶層に直流電圧(DC bias)が印加されて液晶分子を劣化させる。これにより、画質欠陥が発生する。

【0009】従って、本発明の目的は、フリンジフィールドの垂直成分を最小化して、画質特性を改善できるフリンジフィールド駆動液晶表示装置を提供することにある。

#### 【0010】

【課題を解決するための手段】前記目的を達成するため、本発明は、下部基板；前記下部基板上に所定方向に延長されたゲートバスライン；前記ゲートバスラインと交差するように配置されて単位画素を限定するデータバスライン；前記ゲートバスラインとデータバスラインの交差部に各々配置された薄膜トランジスタ；前記単位画素空間に各々形成され、共通信号を印加し続ける四角板状のカウンタ電極；及び、前記薄膜トランジスタと電気的に連結して、前記カウンタ電極と共にフリンジフィールドを形成するように前記カウンタ電極上にオーバーラップされる多数の櫛歯部を含む画素電極を含み、前記カウンタ電極は多数のスリットを含み、前記スリットは画素電極の櫛歯部間に各々備えられ、前記カウンタ電極及び画素電極は透明導電体で形成されることを特徴とする。

#### 【0011】

上に所定方向に延長されたゲートバスライン；前記ゲートバスラインと交差するように配置されて単位画素を限定するデータバスライン；前記ゲートバスラインとデータバスラインの交差部に各々配置された薄膜トランジスタ；前記単位画素空間に各々形成され、共通信号を印加し続ける四角板状のカウンタ電極；及び、前記薄膜トランジスタと電気的に連結して、前記カウンタ電極と共にフリンジフィールドを形成するように、前記カウンタ電極上にオーバーラップされながら前記データバスラインと平行な多数の櫛歯部を含む画素電極を含み、前記カウンタ電極は前記櫛歯部と平行な多数のスリットを含み、前記スリットは画素電極の櫛歯部間に各々備えられ、前記カウンタ電極及び画素電極は透明導電体で形成されることを特徴とする。

#### 【0012】

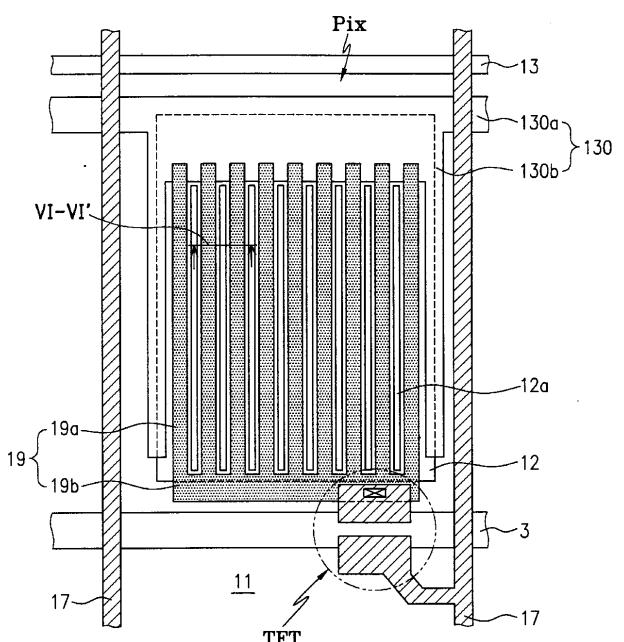

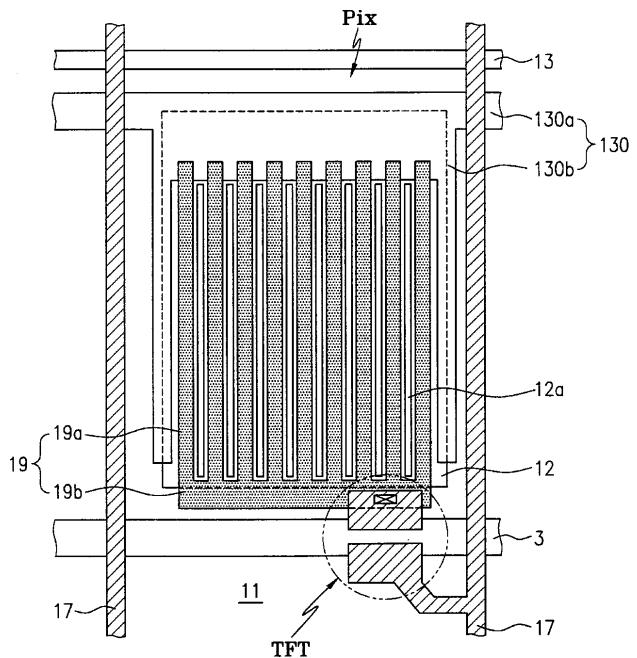

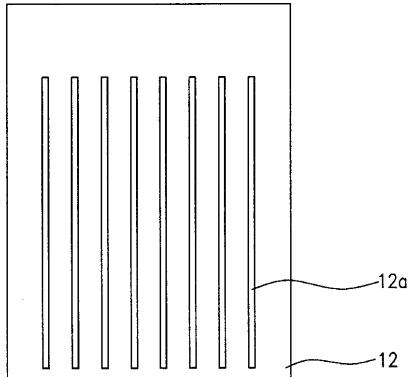

【発明の実施の形態】以下、添付図面に基づき、本発明の好適実施例を詳細に説明する。まず、図4を参照して、ゲートバスライン13は図のx方向に下部基板11上に延長され、データバスライン17はゲートバスライン13と実質的に垂直なy方向に延長され、下部基板11に矩形の単位画素pixが限定される。ここで、ゲートバスライン13とデータバスライン17は、公知のように、ゲート絶縁膜(不図示)によって絶縁される。ゲートバスライン13とデータバスライン17の交点近傍には薄膜トランジスタTFTが各々配置される。カウンタ電極12はそれぞれの単位画素に形成される。カウンタ電極12は透明導電層例えばITO物質で形成され、板状ましくは四角板状で形成される。また、カウンタ電極12は多数のスリット12aを含む。このとき、スリット12aの長軸がデータバスライン17と平行で、各スリット12aは等間隔に平行に配置される。この様なカウンタ電極12だけの形状を図5に示している。一方、共通信号線130はカウンタ電極12の所定部分とコンタクトされてカウンタ電極12に共通信号を伝達する。共通信号線130はゲートバスライン13と平行でカウンタ電極12の所定部分とコンタクトされる第1部分130aと、第1部分130aからデータバスライン17と平行に延長され、カウンタ電極12とデータバスライン17との間に各々配置される第2部分130bとを含む。このとき、共通信号線130はゲートバスライン13及びデータバスライン17共に絶縁される。画素電極19はカウンタ電極12とオーバーラップされるように、単位画素pixに各々形成される。画素電極19はデータバスライン17と平行でスリット12a間に各々配列される多数の櫛歯部19aと、櫛歯部19aの一端を連結しながら薄膜トランジスタTFTのドレイン電極とコンタクトされるバー19bとを含む。このとき、櫛歯部19a間の間隔はスリット12aの線幅より大きい。これにより、櫛歯部19a間の空間を介してスリット12aが露出する。しかも、画素電極19はカウンタ

電極12と同様に透明導電体、例えばITO物質で形成される。また、画素電極19の櫛歯部19aとカウンタ電極12との間の間隔は上部及び下部基板11間の距離より小さい。さらに、画素電極19の櫛歯部19aの幅及び露出したカウンタ電極12の幅は、フリンジフィールドが電極上部まで及ぼす程度である。

【0013】この本発明のフリンジフィールド駆動液晶表示装置は、次の通り動作する。カウンタ電極12と画素電極19との間に電圧差が発生すれば、カウンタ電極12と画素電極19の櫛歯部19aとの間にフリンジフィールドFが形成される。このとき、フリンジフィールドFはスリット12a両側の露出したカウンタ電極12と画素電極19の櫛歯部19aとの間で形成されるので、垂直成分が存在しなくなる。すなわち、垂直形態のフリンジフィールド部分がスリット12aによってスリット12a外側に曲がる。よって、誘電率異方性が正の液晶物質を使用するとき、露出したカウンタ電極12の上部で液晶分子らがほぼ基板と平行な形態に配列される。よって、画質欠陥が減少される。尚、未説明の図面符号14はゲート絶縁膜を示す。

【0014】さらに、本発明のように、露出したカウンタ電極12にスリット12aが形成されると、図6及び図7に示すように、(+)フレームと(-)フレームの各々の電界がほぼ同様に形成されて輝度差が発生しない。しかも、輝度差が発生しないので、液晶分子に直流電圧が印加される現象も減少され、液晶分子の劣化を防止する。これにより、画質欠陥を防止する。

【0015】尚、本発明は、本実施例に限られるものではない。本発明の趣旨から逸脱しない範囲内で多様に変更実施することが可能である。

#### 【0016】

【発明の効果】以上から説明した様に、本発明によれば、フリンジフィールド駆動液晶表示装置において、画素電極の櫛歯部によって露出するカウンタ電極部分に櫛歯部間の間隔より狭幅を持つスリットを形成する。これ\*

\*により、画素電極の櫛歯部とカウンタ電極間に垂直成分のフリンジフィールドを除去して、液晶分子らが非定常に配列されるのを防止する。しかも、(+)フレームと(-)フレーム間のフリンジフィールドが同様な形態で形成され、液晶分子配列の差を低減できる。これにより、液晶表示装置の画質特性が大きく改善される。

#### 【図面の簡単な説明】

【図1】一般的のフリンジフィールド駆動液晶表示装置の平面図である。

【図2】図1のII-II線に沿う断面図であって、(+)フレーム時のフィールド及び液晶分子の配列を示す断面図である。

【図3】図1のII-II線に沿う断面図であって、(-)フレーム時のフィールド及び液晶分子の配列を示す断面図である。

【図4】本発明によるフリンジフィールド駆動液晶表示装置の平面図である。

【図5】本発明によるフリンジフィールド駆動液晶表示装置のカウンタ電極を示す平面図である。

【図6】図4のVI-VI線に沿う断面図であって、(+)フレーム時のフィールド及び液晶分子の配列を示す断面図である。

【図7】図4のVI-VI線に沿う断面図であって、(-)フレーム時のフィールド及び液晶分子の配列を示す断面図である。

#### 【符号の説明】

11 下部基板

12 カウンタ電極

12a カウンタ電極のスリット

30 13 ゲートバスライン

14 ゲート絶縁膜

19 画素電極

19a 画素電極の櫛歯部

19b 画素電極のバー

130 共通電極線

【図2】

【図3】

【図7】

【図1】

【図4】

【図5】

【図6】

## 【手続補正書】

【提出日】平成12年6月30日(2000.6.30)

## 【手続補正1】

【補正対象書類名】図面

【補正対象項目名】図4

【補正方法】変更

【補正内容】

【図4】

|                |                                                                                                                                     |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 边缘场驱动液晶显示装置                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2001056475A</a>                                                                                                       | 公开(公告)日 | 2001-02-27 |

| 申请号            | JP2000197138                                                                                                                        | 申请日     | 2000-06-29 |

| [标]申请(专利权)人(译) | 海力士半导体有限公司                                                                                                                          |         |            |

| 申请(专利权)人(译)    | 现代电子工业有限公司                                                                                                                          |         |            |

| [标]发明人         | 金恩植<br>李泳根                                                                                                                          |         |            |

| 发明人            | 金恩植<br>李泳根                                                                                                                          |         |            |

| IPC分类号         | G02F1/1343 G02F1/136 G02F1/1368                                                                                                     |         |            |

| CPC分类号         | G02F1/134363                                                                                                                        |         |            |

| FI分类号          | G02F1/1343 G02F1/136.500 G02F1/1368                                                                                                 |         |            |

| F-TERM分类号      | 2H092/GA14 2H092/JA24 2H092/JB05 2H092/JB14 2H192/AA24 2H192/BB13 2H192/BB52 2H192/BB73 2H192/CB05 2H192/CC04 2H192/CC57 2H192/JA33 |         |            |

| 优先权            | 1999/P25223 1999-06-29 KR                                                                                                           |         |            |

| 其他公开文献         | JP3723911B2                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                           |         |            |

### 摘要(译)

本发明的目的是提供一种边缘场驱动液晶显示装置，其能够通过最小化边缘场的垂直分量来改善图像质量特性。根据本发明，下部基板；在下部基板上沿预定方向延伸的栅极总线；数据总线，被布置为与栅极总线相交以限制单位像素；栅极总线 薄膜晶体管布置在数据总线的交点处；分别具有矩形板形状并连续施加公共信号并形成在单位像素空间中的对电极；以及与电连接到该薄膜晶体管的计数器。包括多个梳齿的像素电极在对电极上重叠以与电极一起形成边缘场，该对电极包括多个缝隙，以及在像素电极的梳齿之间的缝隙。并且对电极和像素电极由透明导电材料形成。