(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

**特許第4381782号

(P4381782)**

(45) 発行日 平成21年12月9日(2009.12.9)

(24) 登録日 平成21年10月2日(2009.10.2)

(51) Int.CI.

F 1

G02F 1/1343 (2006.01)

G02F 1/1368 (2006.01)G02F 1/1343

G02F 1/1368

請求項の数 10 (全 17 頁)

(21) 出願番号 特願2003-387832 (P2003-387832)

(22) 出願日 平成15年11月18日 (2003.11.18)

(65) 公開番号 特開2005-148534 (P2005-148534A)

(43) 公開日 平成17年6月9日 (2005.6.9)

審査請求日 平成18年2月13日 (2006.2.13)

(73) 特許権者 502356528

株式会社 日立ディスプレイズ

千葉県茂原市早野3300番地

(74) 代理人 100083552

弁理士 秋田 収喜

小野 記久雄

千葉県茂原市早野3300番地 株式会社

日立ディスプレイズ内

(72) 発明者 永山 育子

千葉県茂原市早野3300番地 株式会社

日立ディスプレイズ内

(72) 発明者 桶 隆太郎

千葉県茂原市早野3300番地 株式会社

日立ディスプレイズ内

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

対向配置された第1の基板と第2の基板を有し、該第1の基板と第2の基板の間に液晶層を有し、

前記第1の基板上には、複数のゲート信号線と、該ゲート信号線と交差する複数のドレイン信号線を有し、

隣接する前記ゲート信号線と前記ドレイン信号線に囲まれた領域で画素領域を構成し、

前記各画素領域の前記第1の基板上には平面状且つ矩形状の対向電極を有する液晶表示装置において、

前記対向電極上に絶縁層を介して形成された画素電極を有し、

該画素電極は、前記画素領域で第1の画素電極と第2の画素電極から構成され、

前記第1の画素電極は、第1の薄膜トランジスタ素子に接続され、前記第2の画素電極は、第2の薄膜トランジスタ素子に接続され、前記第1の薄膜トランジスタ素子と前記第2の薄膜トランジスタ素子は、同じ前記ゲート信号線により制御され、且つ同じ前記ドレイン信号線に接続され、

前記第1の画素電極と前記第2の画素電極は、電極中に多数の並設されたスリットを有し、且つ該スリットの延在方向は、前記ゲート配線と前記ドレイン信号線のいずれの延在方向とも異なり、

且つ前記第1と第2の画素電極の隣接する辺は互いに平行で、且つ前記第1と第2の画素電極の隣接する辺の間が前記対向電極上に位置していることを特徴とする液晶表示装置

10

20

。

**【請求項 2】**

前記第1と第2の画素電極の隣接する辺が、前記ドレイン信号線と平行に配置されていることを特徴とする請求項1に記載の液晶表示装置。

**【請求項 3】**

前記第1の画素電極に形成された前記スリットと前記第2の画素電極に形成された前記スリットは、互いに延在方向が異なることを特徴とする請求項2に記載の液晶表示装置。

**【請求項 4】**

前記第1の画素電極に形成された前記スリットと前記第2の画素電極に形成された前記スリットは、前記ドレイン信号線の延在方向に対して対称となる方向に延在することを特徴とする請求項3に記載の液晶表示装置。

10

**【請求項 5】**

前記液晶層の液晶分子の配向方向が、前記ドレイン信号線と直交する方向であることを特徴とする請求項2に記載の液晶表示装置。

**【請求項 6】**

前記第1の画素電極と前記第2の画素電極の前記スリットの延在方向は、前記ゲート信号線の延在方向に対して時計回り或いは反時計回りに30度以内であることを特徴とする請求項5に記載の液晶表示装置。

20

**【請求項 7】**

前記ドレイン信号線の延在方向に隣接する前記画素領域において、各画素領域間の前記対向電極同士を接続する連結配線を有し、前記連結配線は、前記ゲート信号線を跨いで各対向電極に接続されることを特徴とする請求項1に記載の液晶表示装置。

**【請求項 8】**

前記対向電極に対向電圧を供給する複数の対向電圧信号線が前記第1の基板上に形成され、

前記対向電圧信号線は、前記ゲート信号線と平行に、且つ複数の前記画素領域を跨ぐように形成されることを特徴とする請求項1に記載の液晶表示装置。

**【請求項 9】**

前記対向電圧信号線は、前記ゲート信号線に隣接して形成され、前記対向電極の一方の前記ゲート信号線に隣接した一辺において、当該対向電圧信号線は対向電極と接続されることを特徴とする請求項8に記載の液晶表示装置。

30

**【請求項 10】**

前記対向電極は、透明導電膜によって形成され、

前記対向電極の前記対向電圧信号線が接続されていない他方の前記ゲート信号線に隣接した一辺において、当該対向電極に金属配線が接続されていることを特徴とする請求項9に記載の液晶表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、液晶表示装置に係り、液晶を介して対向配置される各基板のうち一方の基板の液晶の面側に画素電極と対向電極とが形成されている液晶表示装置に関するものである。

40

**【背景技術】**

**【0002】**

この種の液晶表示装置は、画素電極と対向電極の間の領域を透過する光に対して、その量を前記各電極の間に発生する電界が印加される液晶の駆動によって、制御するようになっている。

このような液晶表示装置は、表示面に対して斜めの方向から観察しても表示に変化のない、いわゆる広視野角特性に優れたものとして知られている。

そして、これまで、前記画素電極と対向電極は光を透過させることのない導電層で形成

50

されていた。

しかし、近年、画素領域の周辺を除く領域の全域に透明電極からなる対向電極を形成し、この対向電極上に絶縁膜を介して一方向に延在し該一方向に交差する方向に並設させた透明電極からなる帯状あるいは櫛歯状の画素電極を形成した構成のものが知られるに到った。

このような構成の液晶表示装置は、基板とほぼ平行な電界が画素電極と対向電極との間に発生し、依然として広視野角特性に優れるとともに、開口率が大幅に向上するようになる（下記特許文献参照）。

#### 【0003】

【特許文献1】特開平11-202356号公報

10

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0004】

しかしながら、このような液晶表示装置は、その画素領域の僅かな周辺を除く領域に形成された対向電極が、絶縁膜を介して形成される櫛歯状の画素電極と大きな面積で重畠されており、前記絶縁膜にピンホールがあった場合ショート不良が発生し表示上の黒色点欠陥となり画質が低下する課題があった。

#### 【0005】

また、薄膜トランジスタのソース電極あるいは画素電極とゲート信号配線がショートした場合は、輝点欠陥が発生し画質が低下する問題があった。

20

さらに、薄膜トランジスタのソース電極とドレイン電極がショートした場合には、輝点欠陥が発生し画質が低下する問題があった。

#### 【0006】

このような、ショート不良の対策としては、1画素に2個の薄膜トランジスタを形成し、さらに画素領域を2分割に分ける考えがある。一方の薄膜トランジスタあるいは画素領域が不良の場合に他方で正常動作をさせる冗長設計の考え方である。

#### 【0007】

しかしながら、このような冗長設計の場合、少なくとも一方は正常、他方は黒点欠陥に抑える必要がある、広視野角の液晶表示装置では修正画素も視野角の広い範囲で正常に動作する必要がある課題がある。

30

#### 【0008】

これに対して、画素領域では一方の矩形の透明の対向電極、絶縁膜を挟んで他方の櫛歯あるいは帯状の透明の画素電極から構成された広視野角の液晶表示装置において、上記の冗長設計の提案がない問題があった。特に、1つの画素領域に対して2つの区分された領域がある場合、その境界領域にて透過率あるいは開口率を低下させずに良好に遮光する構造の提案もないという問題もあった。また冗長で救済された画素が色シフトなどの視野角が低下する課題もあった。

#### 【0009】

また、このような冗長の画素構造が必要とされる液晶ディスプレイは画面の大きい液晶テレビに用いられる。このような用途では画像を表示する電圧が印加される画素電極と対向電極のうちで、対向電極の電圧歪みが問題になり、このため透過率や開口率を低下させずに電圧歪を小さくする対向電極及び対向電極配線のレイアウトが課題となる。

40

#### 【0010】

本発明は、このような課題を解決した液晶表示装置を提供することを目的とするものである。

また、本発明は、区分された各領域の境界において、駆動時の液晶のランダムな配置による輝度むらを回避した液晶表示装置を提供することを目的とするものである。

#### 【課題を解決するための手段】

#### 【0011】

前記課題に対して概略以下の手段を持ち、課題を解決する。

50

(1) 本発明による液晶表示装置は、たとえば、対向配置された第1の基板と第2の基板を有し、該第1の基板と第2の基板の間に液晶層を有し、前記第1の基板上には、複数のゲート信号線と、該ゲート信号線と交差する複数のドレイン信号線を有し、隣接する前記ゲート信号線と前記ドレイン信号線に囲まれた領域で画素領域を構成し、前記各画素領域の前記第1の基板上には平面状且つ矩形状の対向電極を有する液晶表示装置において、

前記対向電極上に絶縁層を介して形成された画素電極を有し、該画素電極は、前記画素領域で第1の画素電極と第2の画素電極から構成され、前記第1の画素電極は、第1の薄膜トランジスタ素子に接続され、前記第2の画素電極は、第2の薄膜トランジスタ素子に接続され、前記第1の薄膜トランジスタ素子と前記第2の薄膜トランジスタ素子は、同じ前記ゲート信号線により制御され、且つ同じ前記ドレイン信号線に接続され、前記第1の画素電極と前記第2の画素電極は、電極中に多数の並設されたスリットを有し、且つ該スリットの延在方向は、前記ゲート配線と前記ドレイン信号線のいずれの延在方向とも異なり、且つ前記第1と第2の画素電極の隣接する辺は互いに平行で、且つ前記第1と第2の画素電極の隣接する辺の間が前記対向電極上に位置していることを特徴とする。

#### 【0012】

(2) 本発明による液晶表示装置は、たとえば、(1)の構成を前提とし、前記第1と第2の画素電極の隣接する辺が、前記ドレイン信号線と平行に配置されていることを特徴とする。

#### 【0013】

(3) 本発明による液晶表示装置は、たとえば、(2)の構成を前提とし、前記第1の画素電極に形成された前記スリットと前記第2の画素電極に形成された前記スリットは、互いに延在方向が異なることを特徴とする。

#### 【0014】

(4) 本発明による液晶表示装置は、たとえば、(3)の構成を前提とし、前記第1の画素電極に形成された前記スリットと前記第2の画素電極に形成された前記スリットは、前記ドレイン信号線の延在方向に対して対称となる方向に延在することを特徴とする。

#### 【0015】

(5) 本発明による液晶表示装置は、たとえば、(2)の構成を前提とし、前記液晶層の液晶分子の配向方向が、前記ドレイン信号線と直交する方向であることを特徴とする。

#### 【0016】

(6) 本発明による液晶表示装置は、たとえば、(5)の構成を前提とし、前記第1の画素電極と前記第2の画素電極の前記スリットの延在方向は、前記ゲート信号線の延在方向に対して時計回り或いは反時計回りに30度以内であることを特徴とする。

#### 【0017】

(7) 本発明による液晶表示装置は、たとえば、(1)の構成を前提とし、前記ドレイン信号線の延在方向に隣接する前記画素領域において、各画素領域間の前記対向電極同士を接続する連結配線を有し、前記連結配線は、前記ゲート信号線を跨いで各対向電極に接続されることを特徴とする。

#### 【0018】

(8) 本発明による液晶表示装置は、たとえば、(1)の構成を前提とし、前記対向電極に対向電圧を供給する複数の対向電圧信号線が前記第1の基板上に形成され、

前記対向電圧信号線は、前記ゲート信号線と平行に、且つ複数の前記画素領域を跨ぐように形成されることを特徴とする。

#### 【0019】

(9) 本発明による液晶表示装置は、たとえば、(8)の構成を前提とし、前記対向電圧信号線は、前記ゲート信号線に隣接して形成され、前記対向電極の一方の前記ゲート信号線に隣接した一辺において、当該対向電圧信号線は対向電極と接続されることを特徴とする。

#### 【0020】

(10) 本発明による液晶表示装置は、たとえば、(9)の構成を前提とし、前記対向電

10

20

30

40

50

極は、透明導電膜によって形成され、前記対向電極の前記対向電圧信号線が接続されていない他方の前記ゲート信号線に隣接した一辺において、当該対向電極に金属配線が接続されていることを特徴とする。

【発明を実施するための最良の形態】

【0022】

実施例1.

図2(a)は、本発明の一実施例における液晶表示パネルの等価回路を該液晶表示パネルの外付け回路とともに示した図である。

図2中、x方向に延在されy方向に並設される各ゲート信号線GLには垂直走査回路Vによって順次走査信号(電圧信号)が供給されるようになっている。

10

【0023】

走査信号が供給されたゲート信号線GLに沿って配置される各画素領域の薄膜トランジスタTFTは該走査信号によってオンするようになっている。

そして、このタイミングにあわせて映像信号駆動回路Hから各ドレイン信号線DLに映像信号が供給されるようになっている。各ドレイン信号線DLは、図中、y方向に延在されx方向に並設されている。前記映像信号は各画素領域の該薄膜トランジスタを介して各画素電極PXに印加されるようになっている。

【0024】

各画素領域において、画素電極PXとともに形成されている対向電極CTには対向電圧信号線CLを介して対向電圧が印加されるようになって、それら各電極の間に電界を発生させるようになっている。画素電極PXおよび対向電極CTはそれぞれ、ドレイン信号線DLからの映像情報電圧をゲート信号線GLがオン電圧を印加されたタイミングで薄膜トランジスタTFTがオンされて画素電極PXへ印加される一方において、外部電源につながれた対向電圧信号線CLから各画素領域で対向電極CTへ伝播され、これによって液晶容量へ電圧を印加する働きをする。上記画素電極PXおよび対向電極CTは薄膜トランジスタTFTの形成された第1の透明基板SUB1上に形成される。これら画素電極PXおよび対向電極CTは絶縁膜を挟んで形成された保持容量素子Cstgと画素電極PXと対向電極CT間の電界が液晶部を通過することによる液晶容量Clcの二つ容量の和である画素容量CPを構成している。そして、この電界のうち透明基板SUB1と平行な成分を有する電界によって液晶LCの光透過率を制御するようになっている。本発明の液晶モードは絶縁膜を挟んで対向電極CTと画素電極PXが積層される面積が大きくそのため1画素の保持容量素子Cstgが大きな値を有する特徴がある。

20

【0025】

一方、対向電圧信号線CLは第1の透明基板SUB1上で、ゲート信号線GLと平行に配置された横方向の配線として形成され、ゲート信号線GLに対して第1の基板SUB1の絶縁を挟んでこれを横断するような縦方向の配線によっても接続され、いわば網の目状に接続されている。この網の目状配線により、外部電源から遠い画面中央領域においても、ゲート信号線GLの大きな電圧振幅が1画素内の寄生容量を介して変動し、これが対向電圧配線CLの電圧を不安定にして、残像、フリッカなどの直流電圧が液晶に印加することによる表示不良を著しく低減する。結果的に本網の目状結線によりゲート信号配線GLと並走する対向電圧配線CLの抵抗仕様は緩和され、そのレイアウト上の幅を細くでき透過率を向上させることができる。ゲート信号配線GLと並走する対向電圧配線CL間はゲート信号配線GLに対して絶縁膜を介して保護膜PASに配置された連結配線SEで接続されている。上記1画素内の対向電極CTおよび配線CLの結線方法は以下で詳細を示す。

30

【0026】

なお、同図において各画素領域に示したR、G、Bの各符号は、各画素領域にそれぞれ赤色用フィルタ、緑色用フィルタ、青色用フィルタが形成されていることを示している。上記で、1画素の領域は隣り合うドレイン信号線DLおよび隣り合うゲート信号線GL内に囲まれた領域であり、その領域に前述のように、薄膜トランジスタTFT、画素電極PX

40

50

X、対向電極 C T が形成されている。

**【0027】**

各画素の詳細な等価回路を図 2 ( b ) に示す。1 画素領域は 2 つの薄膜トランジスタ TFT と 2 つの容量素子 C P で構成されており、一方が薄膜トランジスタあるいは画素領域が不良の場合にて、他方の薄膜トランジスタおよびこの画素領域で正常動作を維持させる。

**【0028】**

図 1 は、本発明による液晶表示装置（パネル）の画素領域における構成図であり、液晶を介して互いに対向配置される各透明基板のうちで一方の透明基板を液晶側から観た平面図である。

10

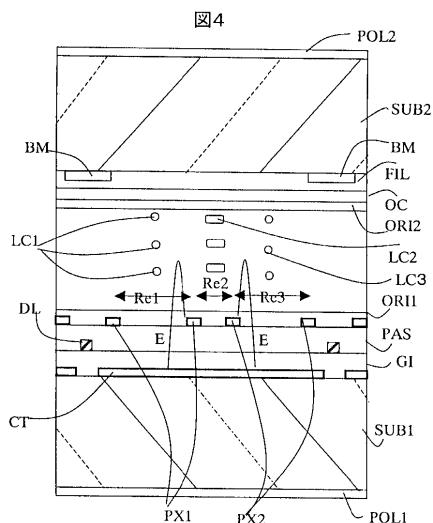

図 1 の I ( a ) - I ( b ) 線における断面図を図 3 に、II ( a ) - II ( b ) 線における断面図を図 4 に、III ( a ) - III ( b ) 線における断面図を図 6 に示している。

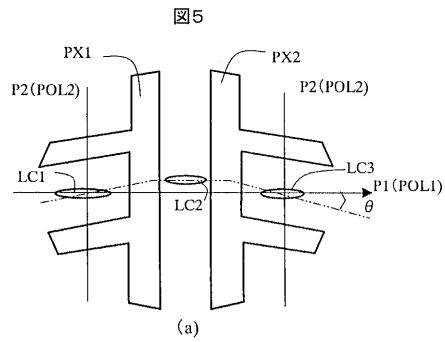

図 5 は、本液晶モードの図 1 の二点鎖線枠 IV 内で 1 画素内の 2 つの画素領域の境界近傍における液晶分子の電圧オン、オフ時における動作を模式的に表す平面図である。

**【0029】**

まず、図 1 において、図中 x 方向に延在され y 方向に並設されるゲート信号線 G L が薄膜トランジスタ TFT 1 及び薄膜トランジスタ TFT 2 のゲートオン電圧を供給する。このオン電圧により、たとえばアモルファスシリコン半導体層 A S とゲート信号配線 G L を被覆するゲート絶縁膜 G I 界面に電子が誘起されトランジスタがオンし、第 1 の画素電極 P X 1 及び第 2 の画素電極 P X 2 と同一基板上に形成された対向電極 C T をそれぞれの電極とする容量素子を充電する。薄膜トランジスタ TFT 1 および TFT 2 はドレイン信号線 D L から伝えられた映像信号に応じた電荷を前記容量素子に充電する。上記のように薄膜トランジスタ TFT 1 及び TFT 2 は時間タイミングに対して同じ動作をする。

20

**【0030】**

上記ゲート信号線 G L は、たとえば第 1 の透明基板側からモリブデン (Mo)、アルミニウム (Al)、モリブデン (Mo) の 3 層積層膜で形成されている。このゲート信号線 G L は後述するドレイン信号線 D L とで矩形状の領域を形成し、その領域は画素領域を構成するようになっている。

そして、この画素領域には、後述する画素電極 P X との間で電界を発生せしめる対向電極 C T が形成され、この対向電極 C T は該画素領域の周辺を除く全域に形成され、透明導電体であるたとえば ITO (Indium-Tin-Oxide) から構成されている。

30

**【0031】**

この対向電極 C T は、隣り合うゲート信号線 G L の近傍に前述のゲート信号線 G L と平行に配置された対向電圧信号線 C L と接続され、この対向電圧信号線 C L は対向電極 C T と一体的に形成されている。

この対向電圧信号線 C L は、たとえばモリブデン (Mo)、アルミニウム (Al)、モリブデン (Mo) の 3 層積層膜からなる不透明の材料で形成されている。

また、上述したように、対向電圧信号線 C L の材料をゲート信号線 G L と同一の材料とすることにより、それらを同一の工程で形成でき製造工数の増大を回避させることができる。

40

**【0032】**

ここで、前記対向電圧信号線 C L は、上記三層膜に限定されることなく、たとえば Cr、Ti、Mo の単層膜あるいは、これらと Al を含有する材料との 2 層膜あるいは 3 層膜で形成するようにしてもよいことはいうまでもない。

しかし、この場合、この対向電圧信号線 C L は対向電極 C T に対して上層に位置づけるのが効果的となる。けだし、対向電極 C T を構成する ITO 膜の選択エッチング液（たとえば HBr）は容易に Al を溶解してしまうからである。

**【0033】**

さらに、対向電圧信号線 C L の対向電極 C T との少なくとも接触面には Ti、Cr、Mo、Ta、W 等の高融点金属を介在させることが効果的となる。けだし、対向電極 C T を

50

構成するITOは対向電圧信号線CL中のA1を酸化させて高抵抗層を生成させてしまうからである。

#### 【0034】

このため、一実施例として、A1、あるいはA1を含有する材料からなる対向電圧信号線CLを形成する場合、前記高融点金属を一層目とする多層構造とすることが好ましい。

そして、このように対向電極CT、対向電圧信号線CL、およびゲート信号線GLが形成された透明基板SUB1の上面には、それらをも被ってたとえばSiNからなる絶縁膜GIが形成されている。

#### 【0035】

この絶縁膜GIは、後述のドレイン信号DLに対しては対向電圧信号線CLおよびゲート信号線GLの層間絶縁膜としての機能を、後述の薄膜トランジスタTFTの形成領域においてはそのゲート絶縁膜としての機能を、後述の容量素子の形成領域においてはその誘電体膜としての機能を有するようになっている。 10

#### 【0036】

そして、絶縁膜GIを介してゲート信号線GLの一部に重畠されて薄膜トランジスタTFT1及びTFT2が形成されているが、半導体層ASの上面に薄膜トランジスタTFT1に対してはドレイン電極SD11およびソース電極SD12が、薄膜トランジスタTFT2に対してはドレイン電極SD21およびソース電極SD22が形成されることによって、ゲート信号線GLの一部をゲート電極とする逆スタガ構造のMIS型トランジスタが形成されることになる。そして、このドレイン電極SD11、SD21およびソース電極SD12、SD22はドレイン信号線DLと同時に形成されるようになっている。 20

#### 【0037】

すなわち、図1中y方向に延在されx方向に並設されたドレイン信号線DLが形成され、このドレイン信号線DLの一部が前記薄膜トランジスタTFTの半導体層ASの表面にまで延在されることによって薄膜トランジスタTFTのドレイン電極SD11及びSD21を構成するようになっている。

#### 【0038】

また、該ドレイン信号線DLの形成の際にソース電極SD12およびSD22が形成され、このソース電極SD12、SD22は画素領域内にまで延在されて後述の画素電極PX1および画素電極PX2との接続を図るコンタクト部CN1およびCN2をも一体的に形成されるようになっている。 30

#### 【0039】

なお、図3に示すように、半導体層ASの前記ソース電極SD12、SD22およびドレイン電極SD11、SD21との界面にはたとえばn型不純物がドーピングされたコンタクト層d0が形成されている。

#### 【0040】

このコンタクト層d0は、半導体層ASの表面の全域にn型不純物ドーピング層を形成し、さらにソース電極SD12、SD22およびドレイン電極SD11、SD21の形成後において、該各電極をマスクとしてこれら各電極から露出された半導体層ASの表面のn型不純物ドーピング層をエッチングすることによって形成されるようになっている。 40

#### 【0041】

そして、このように薄膜トランジスタTFTが形成された透明基板SUB1の表面には、該薄膜トランジスタTFTをも被ってたとえばSiNからなる保護膜PASが形成されている。薄膜トランジスタTFTの液晶LCとの直接の接触を回避するためである。

#### 【0042】

さらに、この保護膜PASの上面には画素電極PXがたとえばITO(Indium-Tin-Oxide)からなる透明な導電膜によって形成されている。

この場合の画素電極PXは、たとえば図1に示すように、画素領域の中央を図中y方向に延在する仮想の線を境に区分された2つの領域にそれぞれ画素電極PX1および画素電極PX2が形成されて構成されている。これら画素電極PX1、PX2は電気的に分離さ

10

20

30

40

50

れたもので、後述するように別個の薄膜トランジスタ TFT 1、TFT 2 を介して同一のドレイン信号線 DL からの映像信号が供給されるようになっている。

【0043】

たとえば図中左側に位置づけられる画素電極 PX は、ゲート信号線 GL の走行方向にはほぼ平行（約 10° の傾きを有する）に配置される帯状の電極がドレイン信号線 DL の走行方向に沿って複数並設されて構成されている。この場合、各電極は薄膜トランジスタ TFT 1 からの映像信号がそれぞれにおいて供給されなければならないことから、ドレイン信号線 DL 側の端部において共通に接続されたパターンをなし、その接続部はドレイン信号線 DL と近接しつつ平行に形成されている。

【0044】

そして、さらに、前記各電極の前記ドレイン信号線 DL とは反対側の端部、すなわち、当該領域と隣接する他の領域側に指向された端部においても、共通に接続されたパターンをなし、その接続部はドレイン信号線 DL と平行に形成されている。

【0045】

この接続部は、それを形成しない場合において、画素領域のほぼ中央の位置にて電極群からなる各画素電極の端部が位置づけられることなり、それら端部で不均一な電界による液晶の分子の複雑な挙動を回避せんがために設けられるものである。

【0046】

当該領域に隣接する他の領域においても、同様のパターンからなる画素電極 PX 2 が形成され、該各領域を区分する仮想の線に対して対称な形状で形成されている。このため、該画素電極 PX 2 においても、それを構成する電極群の各電極は、一方の領域側に指向された端部においても、共通に接続されたパターンをなし、その接続部はドレイン信号線 DL と平行に形成されている。

【0047】

上述したように、該接続部は、それを形成しない場合において、画素領域のほぼ中央の位置にて電極群からなる各画素電極の端部が位置づけられることなり、それら端部で不均一な電界による液晶の分子の複雑な挙動を回避せんがためである。

【0048】

これにより、画素領域の中央部において、ドレイン信号線 DL とほぼ平行に画素電極 PX 1 と画素電極 PX 2 との分離個所が形成され、この分離個所は、画素電極 PX 1 の各電極の画素電極 PX 2 側に設けた接続部と、画素電極 PX 2 の各電極の画素電極 PX 1 の側に設けた接続部によって、電界の方向がほぼ均一になるように構成できる。

【0049】

ちなみに、この実施例では、隣り合う画素電極 PX 1 あるいは PX 2 における各櫛歯間の間隔 L はたとえば 3 ~ 10 μm、幅 W はたとえば 2 ~ 6 μm の範囲で設定されるようになっている。

【0050】

この場合、各画素電極 PX 1 および PX 2 の下端の同材料層は、それぞれ前記保護膜 PAS に形成されたコンタクト孔 CN 1 および CN 2 を通して前記薄膜トランジスタ TFT のソース電極 SD 1 2、SD 2 2 のコンタクト部と接続されるようになっており、また、上端の同材料層は前記対向電極 CT と重畠されて形成されている。

このように構成した場合、対向電極 CT と各画素電極 PX との重畠部には絶縁膜 GI と保護膜 PAS との積層膜を誘電体膜とする容量素子が形成されるようになっている。

【0051】

この容量素子は、図 3 あるいは図 4 の断面図に示すように、保護膜 PAS 上の ITO で構成された画素電極 PX 1 あるいは PX 2 が一旦液晶 LC、保護膜 PAS およびゲート絶縁膜 GI を経由して ITO で構成された対向電極 CT へいたる電気力線と、画素電極 PX 1 あるいは PX 2 から直接下部の対向電極へ至る電気力線による容量素子から構成されている。後者は保持容量 Cstg である。この保持容量 Cstg は薄膜トランジスタ TFT を介してドレイン信号線 DL からの映像信号が画素電極 PX に印加された後に、該薄膜ト

ランジスタ TFT がオフとなつても該映像信号が画素電極 PX に比較的長く蓄積される等のために設けられたものとなつてゐる。

#### 【0052】

ここで、この容量素子 Cstg の容量は、対向電極 CT と各画素電極 PX との重畠面積に比例し、その面積が比較的大きくなつてしまふ。該容量の誘電体膜は絶縁膜 GI と保護膜 PAS との積層膜である。

#### 【0053】

なお、前記保護膜 PAS としては、SiN に限定されることなく、たとえば合成樹脂によって形成されてもよいことはいうまでもない。この場合、塗布により形成することから、その膜厚を大きく形成する場合においても製造が容易であるという効果を奏する。

10

#### 【0054】

そして、このように画素電極 PX1 あるいは PX2 が形成された透明基板の表面には該画素電極 PX をも被つて配向膜 ORI1 が形成されている。この配向膜 ORI1 は液晶 LC と直接に接触する膜で該液晶 LC の初期配向方向を決定づけるものとなつてゐる。

#### 【0055】

一方、対向電圧信号線 CL は第 1 の透明基板 SUB1 で、ゲート信号線 GL と平行に配置された横方向の配線に対して、ゲート信号線 GL に対して第 1 の基板 SUB1 の絶縁を挟んでこれを横断するような縦方向の配線によっても接続され、いわば網の目状に接続されている。この網の目状配線により、外部電源から遠い画面中央領域においても、ゲート信号線 GL の大きな電圧振幅が 1 画素内の寄生容量を介して変動し、これが対向電圧配線 CL の電圧を不安定にして、残像、フリッカなどの直流電圧が液晶に印加することによる表示不良を著しく低減する。結果的に本網の目状結線によりゲート信号配線 GL と並走する対向電圧配線 CL の抵抗仕様は緩和され、そのレイアウト上の幅を細くでき透過率を向上させることができる。ゲート信号配線 GL と並走する対向電圧配線 CL 間はゲート信号配線 GL に対して絶縁膜を介して保護膜 PAS に配置された連結配線 SE で接続する。

20

#### 【0056】

本実施例では図 1 における平面図の右下あるいは右上の連結配線 SE で上下の隣り合う対向電極 CT を連結することにより、対向電圧配線 CL 幅が狭く抵抗が高くても画質劣化を起こさない。結果として透過率を向上させることができる。

#### 【0057】

30

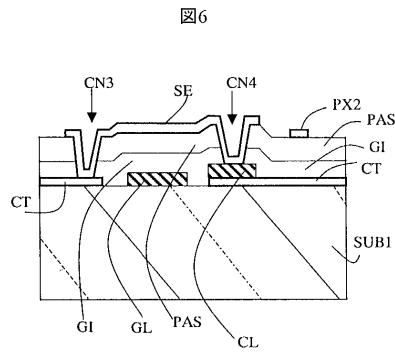

図 6 は図 1 の III(a) - III(b) の切断線に沿つたこの連結配線 SE の断面図である。連結配線 SE は上下に隣接する画素領域のそれぞれの対向電極 CT を接続する配線である。図 6 の断面構造でもわかるように、ゲート信号配線 GL を挟むように 1 画素内に矩形に配置された対向電極 CT 上のゲート絶縁膜 GI 及び保護膜 PAS にコンタクトホール CN3 及び CN4 を開口し、これを介して、画素電極 PX1 および PX2 と同一工程で成膜されたITO からなる連結配線 SE で接続する。コンタクトホール CN4 の下部にはゲート信号配線 GL と同一工程で成膜された対向電極配線 CL がある。他方のコンタクトホール CN3 は対向電極 CT と接続されている。対向電極 CT は対向電極配線 CL と直接接続されている。したがつて、ゲート信号配線 GL と並走する対向電極配線 CL は対向電極 CT、連結配線 SE の繰り返し構成で互いに電気的に接続されている。これにより対向電極配線 CL の配線時定数は、連結配線 SE で接続しない場合に比べて飛躍的に低減される。

40

上記実施例において、透明導電膜として ITO を用いて説明したが、たとえば IZO (Indium-Zinc-Oxide) でも同様の効果が得られることはいうまでもない。

#### 【0058】

このように構成された第 1 の透明基板 SUB1 は TFT 基板と称され、この TFT 基板と液晶 LC を介して対向配置される第 2 の透明基板 SUB2 はフィルタ基板と称されている。

フィルタ基板は、図 3 あるいは図 4 に示すように、その液晶側の面に、まず、各画素領域を画するようにしてブラックマトリックス BM が形成され、このブラックマトリックス BM の実質的な画素領域を決定する開口部にはそれを被つてフィルタ FILL が形成される

50

ようになっている。

そして、ブラックマトリックスB MおよびフィルタF I Lを被ってたとえば樹脂膜からなるオーバーコート膜O Cが形成され、このオーバーコート膜の上面には配向膜O R I 2が形成されている。上記が本実施例1の概略の平面および断面構成である。

#### 【0059】

次に本液晶モードの冗長構造における動作を図1、図4および図5を用いて説明する。本実施例では液晶としては電界方向に液晶分子の長軸方向が揃う、いわゆるポジ型のネマチック液晶を使用している。液晶表示のオン、オフは、無電界で黒状態、電圧を印加すると白状態へと遷移するノーマリブラックの電圧 透過率特性を持つ挙動を示す。

#### 【0060】

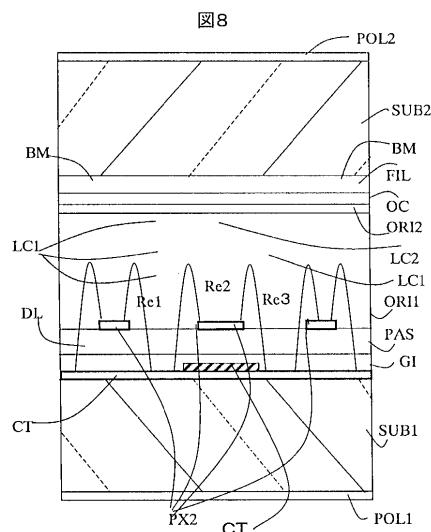

図4は図1のII(a)からII(b)をつなぐ2点破線上の断面図である。図4の正面から見て左手側がII(a)、右手側がII(b)である。本インプレーン表示モード(すなわち第1の基板S U B 1側に画素電極P X 1あるいはP X 2および対向電極C Tを有する)では、櫛歯状の画素電極P X 1あるいはP X 2からの電気力線(図4のE)が液晶L C中へ印加され、その電気力線は液晶L C中を経て上記櫛歯の隙間の保護膜P A S、絶縁膜G Iを通過し、画素領域でほぼ方形に全面に形成された対向電極C Tへ至る。図4において、中央の対向電圧配線C Lに対して左手側領域(図4におけるR e 1の領域)の液晶分子L C 1では第1の基板S U B 1にほぼ平行方向に対して時計回りに回転、図4の右側の領域(R e 3)においてはその液晶分子L C 3は反時計回り回転する。その回転により透過率が変化し表示が可能となる。

#### 【0061】

一方、図4の中央領域(R e 2)では、画素電極P X 1及びP X 2から液晶領域を経て対向電極C Tへ電気力線が至るが光学的には光が透過しない。この領域は図1の平面構造でわかるように、2つの画素電極P X 1及びP X 2がドレイン信号線D Lと平行に延在し、その2つの領域にはさまれた対向電極C T上の領域であるからである。すなわち、本液晶表示装置では、ゲート信号線G Lと平行にラビングが施されているため、この画素電極P X 1およびP X 2に挟まれた領域では、電界方向と液晶分子の長軸方向が一致しており、例え、電界が印加されても液晶分子が回転せず、透明な画素電極C T上であっても黒表示のままである。従って、この領域は、冗長画素の効果で2つの画素領域である画素電極P X 1及びP X 2のいずれか一方の画素電極が不良となつても、すなわち画素電極P X 1とP X 2が異なる電位が印加されても黒表示を維持する。従来の液晶表示装置では、2つの画素領域の間を金属電極で遮光して、境界を分離していたが、本液晶表示装置では、これらが不要であるため、遮光電極と透明な画素電極を重ね合わせて逆に正常な画素の透過率さえも下げていた。本液晶表示装置ではこれを防ぐことができ明るい液晶表示装置を提供できる。

#### 【0062】

さらに、図5の模式的な平面図でその光学的動作を説明する。同図の(a)及び(b)はそれぞれ図3あるいは図4の画素電極P X 1及びP X 2と対向電極C T間に電界が印加されていない時の液晶分子の動作、電界が印加されているときの動作状態を示す。ここで第1基板S U B 1側の偏光板P O L 1の偏光軸P 1は第1のゲート信号線G L方向に設定してあり、一方第2基板S U B 2側の偏光板P O L 2の偏光軸P 2は図1のドレイン信号線D Lに沿って配置されている。すなわち、クロスニコルの偏光軸配置である。ラビングは第1の偏光軸すなわちゲート信号線G Lと平行な方向に第1および第2基板の配向膜O R L 1、O R L 2共に施されている。

#### 【0063】

図1の画素電極P X 1の領域では、櫛歯状の画素電極P X 1はゲート信号線G Lすなわち偏光軸P 1に対して反時計まわりに約10度の傾きを持つように延在し、一方、画素電極P X 2の領域では、画素電極P X 2は偏光軸P 1に対して時計回りに約10度の方向に延在するように配置されている。

#### 【0064】

10

20

30

40

50

液晶の印加電圧がないか、あるいは小さい時は、ゲート信号配線 G L の延在方向にその液晶分子 L C 1 および L C 3 の長軸がそろう。液晶分子 L C 1 は（図 4 の R e 1 領域）これに追従し電界方向すなわち時計回りに回転し、偏光板の偏光軸と - 45 度方向に長軸が一致するように回転した際に透過率が最大となる。液晶分子 L C 3 は（図 4 の R e 1 3 領域）逆に反時計回りとなり、偏光軸と 45 度方向に長軸が一致した時に最大透過率を示す。本実施例ではこのように 1 画素の液晶分子を時計回りと反時計回りの 2 つの領域に分けているため、画面の視野角はどの方向から見ても反転することがなく、また色変化が小さい広視野角の表示が可能となる。また、画素電極 P X および対向電極 C T が透明の I T O で形成され、さらに液晶 L C に充分な電界が印加されるのでブラックマトリクス B M の内側の画素領域ではほぼ全面に透過して明るい画像が表示できる。

10

#### 【 0 0 6 5 】

一方、2 つの画素電極 P X 1 および P X 2 に囲まれた境界領域では（図 4 の R e 2 領域）では無電界状態ではラビング方向すなわち第 1 の偏光軸 P 1 にそって液晶分子 L C 2 の長軸がそろっているのでクロスニコルの黒状態を維持する。さらに、電界が印加された場合でも、図 4 の断面に示すような画素電極 P X 1 あるいは P X 2 から液晶層を経て対向電極 C T に至る電気力線は平面的にみるとゲート信号線すなわち第 1 の偏光軸にそった方向となる。これは、2 つの画素電極 P X 1 および P X 2 は第 1 図の平面図に示すようにドレイン信号線 D L と平行に延在するように配置されているからである。電界方向が第 1 の偏光軸 P 1 と平行であるためにこの液晶分子 L C 2 はいかなる電界が印加されも黒状態を維持する。すなわち、正常動作で画素電極 P X 1 及び P X 2 が同電位で対向電極 C T と電界を形成している場合でも、一方の電極が不良で画素電極 P X 1 と P X 2 が異なる電位となつてもこの電界方向に変化がなく、冗長設計を施した画素電極 P X 1 と P X 2 の境界領域は常に黒状態を維持する。

20

#### 【 0 0 6 6 】

##### 実施例 2 .

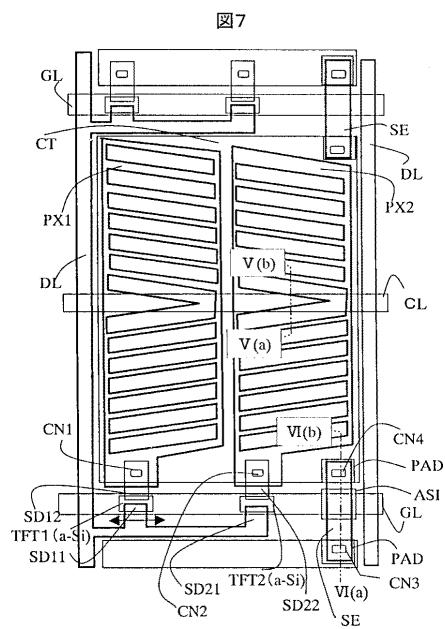

図 7 は、本発明による液晶表示装置の他の実施例を示す平面図で、同図の V ( a ) - V ( b ) 線における断面図、VI ( a ) - VI ( b ) 線における断面図をそれぞれ図 8、図 9 に示している。

#### 【 0 0 6 7 】

図 7 の平面図の構成は、本発明の 1 つの目的である冗長画素構造において、薄膜トランジスタ T F T 1 からコンタクト C N 1 を介して画素電極 P X 1 にドレイン信号線 D L のデータが供給される画素領域と薄膜トランジスタ T F T 2 からコンタクト C N 2 を介して画素電極 P X 2 にドレイン信号線 D L のデータが供給される画素領域を有する。1 方の画素領域が不良となつても他方の画素領域が正常の電位動作するだけなく、視野角方向に色シフトのない冗長となっているのが特徴である。

30

#### 【 0 0 6 8 】

大型液晶テレビは画素サイズが大きく点欠陥不良が目立やすい。しかも広視野角の性能の要求も高い。本実施例は 1 画素に 2 個の薄膜トランジスタ T F T 及び 2 つの画素領域を有する。第 1 の実施例とその点は同じである。第 1 の実施例では 1 画素の 2 つの画素領域が液晶分子の回転方向が画素分割のそれぞれの領域、すなわち、各画素の中央領域に対して左右の領域に対して液晶分子の回転方向が時計および反時計回りに回転することで、視野角方向から見た際に青く着色する変化と黄色く着色する効果を相殺してきた。いわゆる 2 ドメインの画素となっていた。ただし実施例 1 では、一方の画素領域が不良でこれが黒表示の欠陥の場合、他方の正常画素では液晶ディスプレイを左から見たときと右から見たときそれぞれ黄色あるいは青色着色の点に見えてしまう。

40

#### 【 0 0 6 9 】

本実施例では隣り合うゲート信号線 G L およびドレイン信号線 D L に囲まれた 1 画素領域が、まず第 1 の薄膜トランジスタ T F T 1 及び第 1 の画素電極 P X 1 で駆動される領域と第 2 の薄膜トランジスタ T F T 2 及び第 2 の画素電極 P X 2 で駆動される領域に分かれている。さらに、隣り合うゲート信号配線 G L のほぼ中央領域にゲート信号線 G L と平行

50

に対向電極配線 C L が延在している。この対向電極配線 C L は対向電極 C T と直接接続されており、それぞれの画素電極 P X 1 および P X 2 との間に電界を発生させ画像を表示している。

#### 【 0 0 7 0 】

前記、画素電極 P X 1 および P X 2 はそれぞれ対向電極配線 C L に対してその櫛歯状の電極が対向電極配線 C L に対して対称の配置になるように傾いている。その角度は 5 から 30 度の間に設定される。これは前述の図 5 により液晶の光学動作を説明したと同様に、それぞれの画素電極 P X 1 および P X 2 の領域がさらに液晶分子が時計まわりと反時計回りに回転する 2 度ドメインの領域を持つことを意味する。従って、図 9 の断面構造において、対向電極配線 C L を挟む 2 つの透過領域 ( R e 1 および R e 3 ) では液晶分子の回転方向が異なる。それぞれの画素領域が 2 ドメインの構成を持つわけである。これにより、画素分割した一方の領域が欠陥により黒点になったときにも他方の画素電極の領域は視野角のどの方向から見ても着色がなく正常動作し、広視野角が必要な液晶テレビへの応用においても好適な画質を提供することができる。10

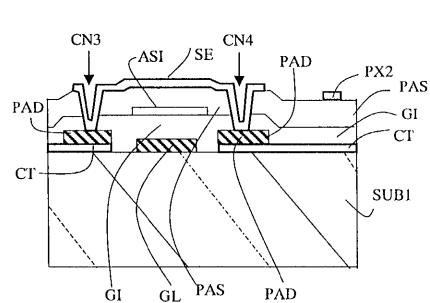

#### 【 0 0 7 1 】

図 9 は連結配線 S E の断面図である。連結配線 S E は隣接する上下の各画素領域の対向電極 C T を接続する配線である。その断面構造でもわかるように、ゲート信号配線 G L を挟むように 1 画素内に矩形に配置された対向電極 C T 上のゲート絶縁膜 G I 及び保護膜 P A S にコンタクトホール C N 3 及び C N 4 を開口し、これを介して、画素電極 P X と同一工程で成膜された I T O からなる連結配線 S E で接続する。コンタクトホール C N の下部にはゲート信号配線 G L と同一工程で成膜されたパッド領域 P A D がありこれは第 2 のコンタクトホール C N 2 及び第 3 のコンタクトホール C N 3 より広めの面積を持つ。この P A D はコンタクトホールの段差でラビング不十分な場合に発生する光漏れを遮光する効果がある。このように、ゲート信号配線 G L と並走する対向電極配線 C L は対向電極 C T 、パッド領域 P A D 、連結配線 S E の繰り返し構成で互いに電気的に接続されている。20

#### 【 0 0 7 2 】

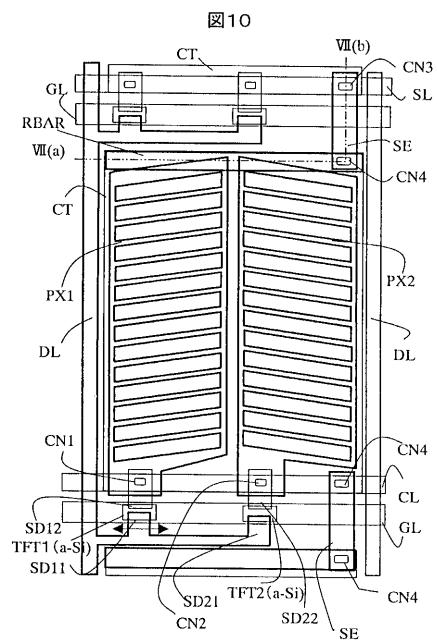

実施例 3 .

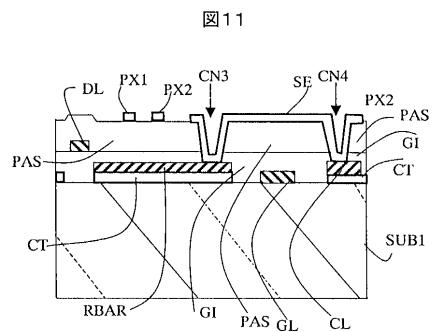

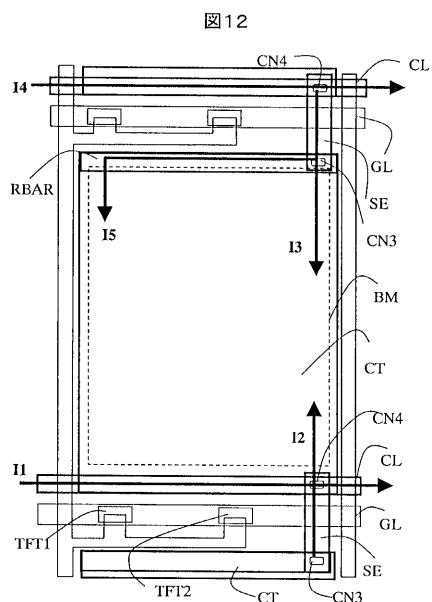

図 10 は、本発明による液晶表示装置の他の実施例を示す平面図で、同図のVII ( a ) - VII ( b ) 線における断面図を図 11 に示している。図 12 は対向電極 C T 及びこれと接続された対向電極配線 C L の電気的連結状況を表し、図 10 の画素平面図のレイアウトにおける各薄膜層の一部を用いてこれを概略説明した図面である。30

#### 【 0 0 7 3 】

本実施例における 1 画素の平面図は基本的には実施例 1 における液晶表示装置と同様の動作を行う。新たな効果を生み出す構造は、隣合うゲート信号配線 G L と隣り合うドレイン信号線 D L に挟まれた 1 画素領域に矩形状に配置された透明電極で構成された対向電極 C T に対して、ゲート配線 G L に隣接する一方の端部にドレイン信号線 D L を交差して横断する対向電極配線 C L の他方端部に抵抗低減電極 R B A R を形成した点にある。抵抗低減電極 R B A R は以下の構造が特徴であり、特有の作用効果を生み出す。抵抗低減電極 R B A R はゲート信号配線 G L 及び対向電極配線 C L と平行な方向に延在している。しかし、大きく異なるのは抵抗低減電極 R B A R はドレイン信号配線 D L とは交差せず 1 画素内に留まっている。ゲート信号配線 G L あるいは対向電極配線 C L は断面構造的にはゲート絶縁膜 G I で分離されている。しかし、製造工程中のダストなどによりこの部分の絶縁膜が不良になると線欠陥となる。交差しなければこの不良は発生しない。この抵抗低減電極 R B A R はドレイン信号線 D L と交差しなくても対向電極 C T と対向電極配線 C L のつくり出す配線ネットワークの抵抗を下げることができる。40

#### 【 0 0 7 4 】

図 11 は、抵抗低減電極 R B A R 及びこれが接続された対向電極 C T がゲート信号配線 G L をまたぐように形成された連結配線 S E と接続された部分の断面構造を示す。抵抗低減電極 R B A R は、 I T O で構成された対向電極 C T 上にゲート信号配線 G L あるいは対向電極配線 C L と同一工程で形成した金属配線材料である。抵抗低減電極 R B A R はゲー50

ト信号配線 G L を跨ぐように、ゲート絶縁膜 G I および保護膜 P A S に開口されたコンタクトホール C N 3 及び C N 4 に対して、画素電極 P X と同一工程で形成された透明電極材料の I T O で構成された連結配線 S E で接続されている。

#### 【 0 0 7 5 】

図 12 は抵抗低減電極 R B A R の効果を表す画素平面図で、装置を構成する薄膜層の内、説明に必要な層のみが記載されている。対向電極配線 C L は低抵抗の金属配線で形成されており、これは記号 I 1 の経路での低抵抗成分（電流の流れ）を持っている。これは I T O で構成された高抵抗の矩形の対向電極 C T に連結される。ゲート配線 G L を跨ぐ前段の対向電極配線 C L の電流経路 I 4 は連結配線 I 3 で自身の画素の対向電極 C T の電圧歪を低減する。抵抗低減電極 R B A R の効果により電流経路 I 5 の広がり抵抗ができ、抵抗低減電極 R B A R が無い場合には、コンタクトホール C N 3 近傍付近での電流経路のみであったものに対して、対向電極 C T 全面に電流が広がり電圧歪を緩和する。10

#### 【 0 0 7 6 】

上記低減効果、結果として、連結配線 S E や抵抗低減配線 R B A R が無い場合に比べて対向電極配線 C L 自体の配線幅を狭くできるのでブラックマトリクス B M の覆われていない領域を大きくできるので開口率を上げることができる。

#### 【 0 0 7 7 】

次に、ゲート信号線 G L をまたぐ抵抗低減配線 R B A R 及び対向電極配線 R B A R の他の透過率向上の役割を示す。ゲート信号配線 G L と対向電極 C T は同層である。もちろん、これがショートすると線欠陥不良となる。従ってゲート信号配線 G L と対向電極 C T は平面的に一定の間隔をあける必要がある。抵抗低減配線 R B A R と対向電極配線 C L はこの間隙から下部バックライトの光が斜め方向から抜ける不要光を効率よく遮光することができる。これは、従来、ゲート配線 G L を対向電極配線 C L でまたぐように形成していた装置に比べ、抵抗低減電極 R B A R がドレイン信号線 D L と交差していないためにショート不良による歩留まり低下がない特徴を持つ。20

#### 【 図面の簡単な説明 】

#### 【 0 0 7 8 】

【図 1】本発明による液晶表示装置の画素領域の一実施例を示す平面図である。

【図 2】本発明による液晶表示装置の一実施例を示す等価回路図である。

【図 3】図 1 の I ( a ) - I ( b ) 線における断面図である。30

【図 4】図 1 の II ( a ) - II ( b ) 線における断面図である。

【図 5】第 1 の実施例における液晶分子の偏光挙動を示す模式図である。

【図 6】図 1 の III ( a ) - III ( b ) 線における断面図である。

【図 7】本発明による液晶表示装置の画素領域における他の実施例を示す平面図である。

【図 8】図 7 の V ( a ) - V ( b ) 線における断面図である。

【図 9】図 7 の VI ( a ) - VI ( b ) 線における断面図である。

【図 10】本発明による液晶表示装置の画素領域における他の実施例を示す平面図である。

。

【図 11】図 10 の VII ( a ) - VII ( b ) 線における断面図である。

【図 12】実施例における抵抗低減の効果を表す画素の概略平面図である。40

#### 【 符号の説明 】

#### 【 0 0 7 9 】

S U B 1 ... 第 1 の透明基板、S U B 2 ... 第 2 の透明基板、P O L 1 ... 第 1 の透明基板の偏光板、P O L 2 ... 第 2 の透明基板の偏光板、B M ... ブラックマトリクス、F I L ... カラーフィルタ層、O C ... オーバコート膜、O I L 1 ... 第 1 の透明基板の配向膜、O I L 2 ... 第 2 の透明基板の配向膜、L C ... 液晶層あるいは液晶分子、G L ... ゲート信号配線、C L ... 対向電極配線、D L ... ドレイン信号配線、C T ... 対向電極、P X ... 画素電極、T F T ... 薄膜トランジスタ、A S ... 半導体層、S D 1 ... ドレイン電極、S D 2 ... ソース電極、C N ... コンタクトホール、S E ... 連結配線、P A D ... パッド領域、G I ... ゲート絶縁膜、P A S ... 保護膜、R B A R ... 抵抗低減電極50

【 図 1 】

【 図 2 】

〔 3 〕

( 4 )

【図5】

( 义 7 )

【 四 6 】

( 8 )

【圖 9】

【図10】

【図11】

【図12】

---

フロントページの続き

(72)発明者 鎌田 浩幸

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

審査官 前川 慎喜

(56)参考文献 特開2002-182230(JP,A)

特開2001-109018(JP,A)

特開2002-202736(JP,A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1343

G02F 1/1362 - 1/1368

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP4381782B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2009-12-09 |

| 申请号            | JP2003387832                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2003-11-18 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 日立显示器有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 当前申请(专利权)人(译)  | 日立显示器有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 小野記久雄<br>永山育子<br>桶隆太郎<br>鎗田浩幸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 小野 記久雄<br>永山 育子<br>桶 隆太郎<br>鎗田 浩幸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368 G02F1/133 G02F1/136 G02F1/1362 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| CPC分类号         | G02F1/136259 G02F1/134363 G02F1/13624 G02F2201/508                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 2H092/GA13 2H092/GA14 2H092/GA25 2H092/GA26 2H092/GA29 2H092/GA30 2H092/HA04 2H092/JA26 2H092/JA28 2H092/JA34 2H092/JA41 2H092/JA46 2H092/JB11 2H092/JB24 2H092/JB33 2H092/JB42 2H092/JB52 2H092/JB56 2H092/JB61 2H092/KA05 2H092/KA12 2H092/KA18 2H092/MA02 2H092/MA12 2H092/MA17 2H092/MA27 2H092/NA01 2H092/NA07 2H092/NA12 2H092/NA28 2H092/PA11 2H092/QA06 2H092/QA09 2H192/AA24 2H192/BB13 2H192/BB53 2H192/BB73 2H192/BB84 2H192/BB86 2H192/BC12 2H192/BC42 2H192/CB05 2H192/CB12 2H192/CC04 2H192/CC32 2H192/DA32 2H192/DA43 2H192/EA04 2H192/EA22 2H192/EA43 2H192/JA33 |         |            |

| 其他公开文献         | JP2005148534A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

## 摘要(译)

提供一种能够提高冗余像素的透射率和视角的液晶显示装置。— 在一个像素中的两个像素区域的结构中，具有这样的结构，其中由透明材料构成并且具有矩形平面图案的平面图案和梳齿形状的透明像素电极彼此重叠，其中绝缘膜插入在一个像素区域的一个基板上在宽视角液晶显示装置中，使电场方向和摩擦方向与两个像素区域的边界区域一致。点域1

【图 1】