(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4209378号

(P4209378)

(45) 発行日 平成21年1月14日(2009.1.14)

(24) 登録日 平成20年10月31日(2008.10.31)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

G02F 1/1343 (2006.01)G02F 1/1368

G02F 1/1343

請求項の数 10 (全 13 頁)

(21) 出願番号 特願2004-316013 (P2004-316013)

(22) 出願日 平成16年10月29日 (2004.10.29)

(65) 公開番号 特開2005-134914 (P2005-134914A)

(43) 公開日 平成17年5月26日 (2005.5.26)

審査請求日 平成16年10月29日 (2004.10.29)

(31) 優先権主張番号 2003-076079

(32) 優先日 平成15年10月29日 (2003.10.29)

(33) 優先権主張国 韓国 (KR)

前置審査

(73) 特許権者 501426046

エルジー ディスプレイ カンパニー リ

ミテッド

大韓民国 ソウル, ヨンドゥンポーク, ヨ

イドードン 20

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100096943

弁理士 白井 伸一

(74) 代理人 100101498

弁理士 越智 隆夫

(74) 代理人 100104352

弁理士 朝日 伸光

最終頁に続く

(54) 【発明の名称】インプレーンスイッチング方式の液晶表示素子及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1及び第2基板と、

前記第1基板に横方向に配置された複数のゲートラインと、

前記第1基板に縦方向に配置され、前記ゲートラインと共に $2 \times 2$ 配列を有する赤(R)、緑(G)、青(B)及び白(W)の4サブ画素を定義するデータラインと、

前記サブ画素内に配置された少なくとも1対の第1及び第2電極と、

前記緑(G)サブ画素に対する赤(R)サブ画素の第1面積比(R/G)によって、前記赤(R)及び緑(G)サブ画素間に配置され、前記前記赤(R)及び緑(G)サブ画素内に形成された第1電極と接続する第1共通ラインと、

前記第1面積比より大きい、白(W)サブ画素に対する青(B)サブ画素の第2面積比(B/W)によって、前記青(B)及び白(W)サブ画素間に配置され、前記前記青(B)及び白(W)サブ画素内に形成された第1電極と接続し、前記第1面積比と第2面積比が相異なるように形成された第2共通ラインと、ここで、前記赤(R)及び緑(G)サブ画素の面積は等しく、前記青(B)サブ画素の面積は前記赤(R)及び緑(G)サブ画素の面積よりも大きく構成され、それにより、白(W)サブ画素の輝度が赤(R)、緑(G)、青(B)サブ画素の輝度の合計と等しくされ、

前記ゲートライン及びデータラインの交差領域に形成されたスイッチング素子と、

前記第1と第2基板間に形成された液晶層と、

を含んで構成されることを特徴とするインプレーンスイッチング方式の液晶表示素子。

## 【請求項 2】

前記第1～第4サブ画素は、それぞれ赤(R)、緑(G)、青(B)、白(W)画素であることを特徴とする請求項1に記載のインプレーンスイッチング方式の液晶表示素子。

## 【請求項 3】

前記第1面積比及び第2面積比は、前記赤(R)、緑(G)、青(B)サブ画素の輝度の和が白(W)サブ画素の輝度と同一であるという関係を満足するように定義されることを特徴とする請求項2に記載のインプレーンスイッチング方式の液晶表示素子。

## 【請求項 4】

前記第1及び第2電極は、共通電極及び画素電極であることを特徴とする請求項1に記載のインプレーンスイッチング方式の液晶表示素子。

10

## 【請求項 5】

前記第1共通ライン及び第2共通ラインは、電気的に連結されることを特徴とする請求項1に記載のインプレーンスイッチング方式の液晶表示素子。

## 【請求項 6】

前記薄膜トランジスタは、

ゲート電極と、

該ゲート電極を含む基板全面に形成されたゲート絶縁膜と、

該ゲート絶縁膜上に形成された半導体層と

該半導体層上に形成されたソース/ドレイン電極と、を含んで構成されることを特徴とする請求項1に記載のインプレーンスイッチング方式の液晶表示素子。

20

## 【請求項 7】

前記第1及び第2共通ラインと重畠し、それぞれのサブ画素内に配置された第2電極と接続する画素電極ラインをさらに含むことを特徴とする請求項1に記載のインプレーンスイッチング方式の液晶表示素子。

## 【請求項 8】

前記第1共通ラインは、前記第1及び第2サブ画素が共有することを特徴とする請求項1に記載のインプレーンスイッチング方式の液晶表示素子。

## 【請求項 9】

前記第2共通ラインは、前記第3及び第4サブ画素が共有することを特徴とする請求項1に記載のインプレーンスイッチング方式の液晶表示素子。

30

## 【請求項 10】

前記第1及び第2電極は、ジグザグ構造であることを特徴とする請求項1に記載のインプレーンスイッチング方式の液晶表示素子。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、液晶表示素子に関し、特に、 $2 \times 2$ 配列を有するR(赤: Red)、G(緑: Green)、B(青: Blue)、W(白: White)サブ画素の面積を容易に調節し得るインプレーンスイッチング方式の液晶表示素子及びその製造方法に関する。

## 【背景技術】

40

## 【0002】

高画質、低電力の平板表示素子として主に用いられるねじれネマチック方式(Twisted Nematic Mode)の液晶表示素子は、視野角が狭いという欠点がある。これは、液晶分子の屈折率異方性に起因するもので、基板と水平に配向された液晶分子が、液晶パネルに電圧が印加されるときに基板とほぼ垂直な方向に配向されるためである。

## 【0003】

従って、最近、液晶分子を基板とほぼ水平な方向に配向して視野角の問題を解決するインプレーンスイッチング方式(In Plane Switching Mode)の液晶表示素子が活発に研究されている。

## 【0004】

50

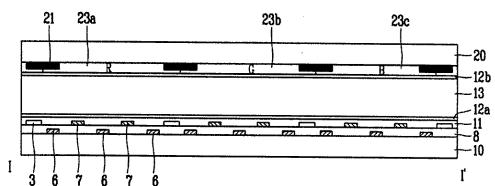

図7は、関連技術のインプレーンスイッチング方式の液晶表示素子の単位画素を概略的に示すもので、図7aは平面図、図7bは図7aのI-I'線断面図である。

【0005】

図に示すように、R (Red)、G (Green)、B (Blue)のサブ画素が一つの単位画素を構成し、それぞれのサブ画素は、透明な第1基板10上に縦横に配列されたゲートライン1及びデータライン3により定義される。実際の液晶表示素子においては、n個のゲートライン1とm個のデータライン3とが交差して  $n \times m$  個のサブ画素が存在するが、図においては、説明の便宜のために、R、G、Bサブ画素のみを示す。以下、R、G、Bサブ画素を単位画素と定義して説明する。

【0006】

前記サブ画素を定義するゲートライン1とデータライン3との交差点には、薄膜トランジスタ9が配置され、前記薄膜トランジスタ9は、ゲート電極1a、半導体層5及びソース/ドレイン電極2a、2bにより構成される。

【0007】

また、前記サブ画素内には、前記ゲートライン1と平行に共通ライン4が配列され、液晶分子をスイッチングさせる少なくとも一対の電極、即ち、共通電極6(6a～6c)及び画素電極7(7a、7b)がデータライン3と平行に配列される。このとき、前記共通電極6及び画素電極7は、前記共通ライン4及びドレイン電極2bにそれぞれ接続される。且つ、前記ソース及びドレイン電極2a、2bを含む第1基板10の上部には、保護膜11及び第1配向膜12aが塗布されている。

【0008】

また、前記共通ライン4、前記共通ライン4と重畳して形成され、画素電極7と接続される画素電極ライン14、及びこれらの共通ライン4と画素電極ライン14との間に介在された絶縁膜8によりストレージキャパシタが形成される。

【0009】

一方、第2基板20には、光漏れを防止するためのブラックマトリックス21及びそれぞれのサブ画素に対応するR、G、Bのカラーフィルタ23a～23cが形成され、前記第1配向膜12aと共に液晶の初期配向状態を決定する第2配向膜12bが塗布される。また、前記第1基板10と第2基板20間には、前記共通電極6及び画素電極7に印加される電圧により光を透過させる液晶層13が形成されている。

【0010】

このような構造を有する関連技術のインプレーンスイッチング方式の液晶表示素子は、共通電極6及び画素電極7が同一平面上に配置されて横電界を発生するため、視野角を向上させることができるという利点を有する。

【発明の開示】

【発明が解決しようとする課題】

【0011】

しかしながら、このような関連技術のインプレーンスイッチング方式の液晶表示素子においては、画面が表示される画素領域内に共通電極6及び画素電極7が配置されているため、開口率が低下して輝度が減少するという問題点があった。

【0012】

本発明は、このような問題点を解決するために提案されたもので、R (Red)、G (Green)、B (Blue)、W (White)のサブ画素を1つの画素として構成して、画面の輝度を向上させることができるインプレーンスイッチング方式の液晶表示素子を提供することを目的とする。

【0013】

本発明の他の目的は、R、G、B、Wの4つのサブ画素をクワッドタイプ(2×2配列)に配置して、開口率を効果的に向上させることができるインプレーンスイッチング方式の液晶表示素子を提供することにある。

【0014】

10

20

30

40

50

本発明の更に他の目的は、上下に配置されたサブ画素間に共通ラインを配置して、前記2つのサブ画素が共通ラインを共有するようにすることにより、サブ画素の面積を容易に調節することができるインプレーンスイッチング方式の液晶表示素子及びその製造方法を提供することにある。

【課題を解決するための手段】

【0015】

このような目的を達成するための本発明によるインプレーンスイッチング方式の液晶表示素子は、第1及び第2基板と、前記第1基板に横方向に配置された複数のゲートラインと、前記第1基板に縦方向に配置され、前記ゲートラインと共に $2 \times 2$ 配列を有する第1～第4サブ画素を定義するデータラインと、前記サブ画素内に配置された少なくとも1対の第1及び第2電極と、第1面積比によって、前記第1と第2サブ画素間に配置され、前記第1及び第2画素内に形成された第1電極と接続する第1共通ラインと、第2面積比によって、前記第3と第4サブ画素間に配置され、前記第3及び第4サブ画素内に形成された第1電極と接続し、前記第1面積比と第2面積比が相異なるように形成された第2共通ラインと、前記ゲートライン及びデータラインの交差領域に形成されたスイッチング素子と、前記第1と第2基板間に形成された液晶層と、を含んで構成される。

【0016】

また、本発明によるインプレーンスイッチング方式の液晶表示素子は、第1及び第2基板と、前記第1基板に横方向に配置された複数のゲートラインと、前記第1基板に縦方向に配置された複数のデータラインと、前記ゲートライン及びデータラインによって定義され、 $2 \times 2$ 配列を有するR、G、B、Wサブ画素と、前記サブ画素内に配置された少なくとも1対の共通電極及び画素電極と、第1面積比( $R/G$ )によって、前記Rサブ画素とGサブ画素間に配置され、前記R及びGサブ画素内に配置された共通電極と接続する第1共通ラインと、1より大きい第2面積比( $B/W$ )によって、前記Bサブ画素とWサブ画素間に配置され、前記B及びWサブ画素内に配置された共通電極と接続する第2共通ラインと、前記第1及び第2共通ラインに重畠し、前記第1及び第2共通ラインと共にストレージキャパシタを形成し、前記各サブ画素内に配置された画素電極を電気的に連結する画素電極ラインと、前記ゲートライン及びデータラインの交差領域に形成されたスイッチング素子と、前記第1と第2基板間に形成された液晶層と、を含んで構成される。

【0017】

また、本発明によるインプレーンスイッチング方式の液晶表示素子は、第1及び第2基板と、前記第1基板に横方向に配置された複数のゲートラインと、前記第1基板に縦方向に配置された複数のデータラインと、前記ゲートライン及びデータラインによって定義され、一列に配列されたR、G、B、Wサブ画素と、前記各サブ画素内に配置された少なくとも1対の共通電極及び画素電極と、を含んで構成される。

【0018】

また、本発明によるインプレーンスイッチング方式の液晶表示素子の製造方法は、第1及び第2基板を用意する段階と、前記第1基板に、複数のゲートラインと、共通電極と、相互電気的に連結されるように前記ゲートライン間の中心を通過する第1共通ラインと、前記ゲートラインの中心から外れるように配置される第2共通ラインとを形成する段階と、前記ゲートラインと垂直に配置され、前記ゲートライン及び第1、第2共通ラインと共に4つのサブ画素を定義する複数のデータラインと、前記第1、第2共通ラインと重畠してストレージキャパシタを形成する画素電極ラインと、該画素電極ラインと電気的に連結され、共通ラインと並んで画素電極を形成する段階と、前記第1と第2基板間に液晶層を形成する段階と、からなる。

【発明の効果】

【0019】

本発明は、高開口率及び高輝度を有する液晶表示素子において、サブ画素の面積を相異なるように構成し得るインプレーンスイッチング方式の液晶表示素子を提供する。特に、上下に配置されたサブ画素が共通ラインを共有するようにし、Wサブ画素の面積を減少さ

10

20

30

40

50

せ、Bサブ画素の面積を増加させることにより、R、G、Bサブ画素の総輝度値をWサブ画素の輝度と同一にすることができる。

【発明を実施するための最良の形態】

【0020】

以下、図面を参照して本発明によるインプレーンスイッチング方式の液晶表示素子及びその製造方法に関して詳細に説明する。

【0021】

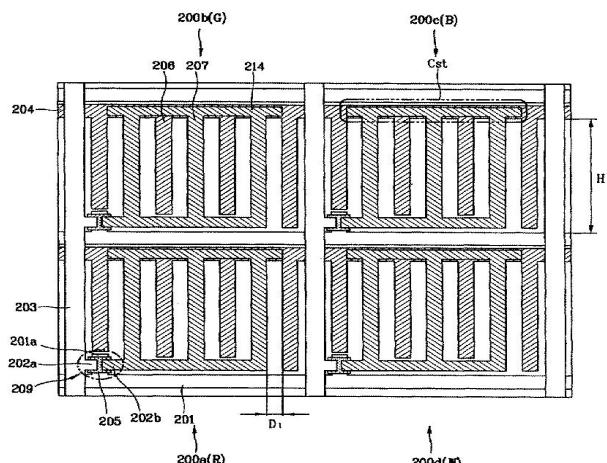

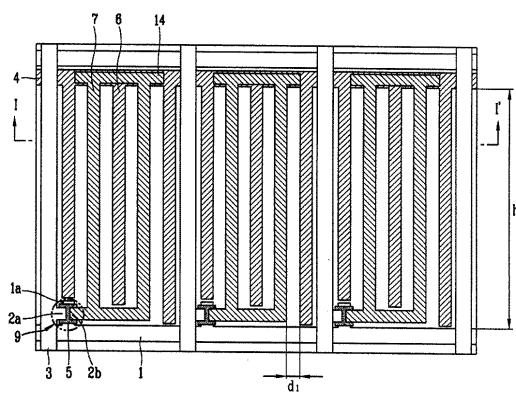

図1は、本発明の第1実施形態による、4ブロック光透過領域を有するインプレーンスイッチング方式の液晶表示素子を示す図である。

【0022】

図に示すように、本発明の第1実施形態によるインプレーンスイッチング方式の液晶表示素子は、既存のR、G、Bサブ画素100a、100b、100cにWサブ画素100dを追加するもので、元来のR、G、Bサブ画素から構成された単位画素の面積はそのまま維持し、それぞれのサブ画素の幅を減らすることで確保された空間にW画素100dを追加する。

【0023】

前記サブ画素100a、100b、100c、100dは、縦横に配列されたゲートライン101及びデータライン103によって定義され、それぞれのサブ画素100a、100b、100c、100d内には、共通ライン104及び画素電極ライン114から垂直分岐されて画素内で横電界を発生させる画素電極107及び共通電極106が交代に配置される。また、前記共通ライン104及び画素電極ライン114は、相互重畠し、ゲート絶縁膜(図示せず)を介在してストレージキャパシタ(Cst)を形成する。

【0024】

また、前記ゲートライン101上には、スイッチング素子として薄膜トランジスタ109が配置される。該薄膜トランジスタ109は、ゲートライン101上にパターン形態に形成された半導体層105と、該半導体層105上に形成され、データライン103から引出しされたソース電極102aと、該前記ソース電極102aと対向し、画素電極ライン114と電気的に連結されたドレイン電極102bと、から構成される。また、詳細に図示されてはいないが、前記ゲートライン101が形成された基板全面には、ゲート絶縁膜(図示せず)が塗布され、該ゲート絶縁膜は、共通電極106と画素電極107を電気的に絶縁させる。

【0025】

以下、関連技術に関する図7Aを引用して本発明の第1実施形態と関連技術との差異点を比較すると、関連技術の4ブロック光透過領域を有するインプレーンスイッチング方式の液晶表示素子において、画素電極7と共通電極6間の隔離距離をd1と定義し、Wサブ画素100dが追加された第1実施形態において、画素電極107と共通電極106間の隔離距離をd2と定義するとき、Wサブ画素100dが追加されることにより、d2=0.5d1になる。即ち、Wサブ画素100dを追加することにより、輝度をある程度向上させることができるが、光透過領域(ここでは、画素電極及び共通電極によって区画された領域を意味する。)は減少する。これは、関連技術のR、G、Bの3つサブ画素から構成された単位画素の面積の変化なしにR、G、B、Wの4つのサブ画素から構成することによって、Wサブ画素を形成する追加配線が増加したからである。

【0026】

一方、ねじれネマチック方式の液晶表示素子では、Wサブ画素を追加する場合、共通電極及び画素電極が相異なる基板上に別途配置されるため、30%以上輝度が向上するが、インプレーンスイッチング方式の液晶表示方式では、前述したように、画素電極及び共通電極が同一の基板上に配置されるため、光透過領域の減少によって輝度向上の大きい効果を期待することはできない。

【0027】

本発明の第2実施形態は、このような問題点を解決するインプレーンスイッチング方式

10

20

30

40

50

の液晶表示素子を示し、R、G、B、Wからなるサブ画素を $2 \times 2$ 形態に配列し、関連技術の4ブロックインプレーンスイッチング方式において共通電極及び画素電極の隔離距離をそのまま維持しながら、6ブロック光透過領域を有するように構成することで、輝度及び開口率の向上を図ることができる。

【0028】

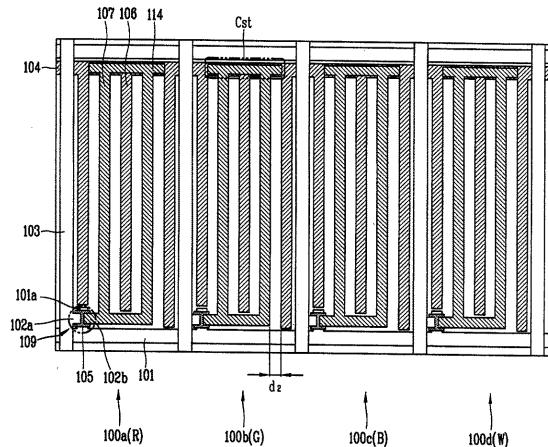

図2は、本発明の第2実施形態による、R、G、B、Wサブ画素が $2 \times 2$ 形態に配列されたインプレーンスイッチング方式の液晶表示素子を示す図である。

【0029】

図に示すように、本実施形態によるインプレーンスイッチング方式の液晶表示素子は、6ブロック光透過領域を有するR、G、B、Wサブ画素200a～200dが $2 \times 2$ 配列されて画素(P)を成す。サブ画素200a～200dは、縦横に配列されたゲートライン201及びデータライン203によって定義され、それぞれのサブ画素200a～200d内には共通ライン204及び画素電極ライン214から垂直分岐されて画素内で横電界を発生させる少なくとも1対以上の画素電極207及び共通電極206が交代に配置される。

【0030】

また、前記画素電極ライン214は、前記共通ライン204と重畠してストレージキャパシタ(Cst)を形成する。

【0031】

また、前記ゲートライン201上には、スイッチング素子として薄膜トランジスタ209が配置され、該薄膜トランジスタ209は、ゲートライン201上にパターン形態に形成された半導体層205と、該半導体層205上に形成され、データライン203から引出しされたソース電極202aと、該ソース電極202aと対向し、画素電極ライン214と電気的に連結されたドレイン電極202bと、から構成される。また、詳細に図示されてはいないが、前記ゲートライン201が形成された基板全面にはゲート絶縁膜(図示せず)が塗布され、これによって、画素電極207及び共通電極206が電気的に絶縁される。

【0032】

前述したような構造を有するインプレーンスイッチング方式の液晶表示素子は、画素電極207と共通電極206間の隔離距離D1が関連技術に関する図7Aの4ブロック液晶表示素子のd1と同一である。反面、それぞれのサブ画素200a～200dを $2 \times 2$ 構造に配列することにより、上下に配置されたサブ画素間にゲートライン及び共通ラインが追加されて垂直方向にHだけの開口率が減少する。このとき、Hは、概略関連技術に関する図7Aの垂直長さhに対して約15%程度減少される。しかしながら、水平方向は、2つのサブ画素が配置されるため、関連技術に比べて電極間の距離を増加させるか、共通電極及び画素電極をさらに追加することで光透過ブロックを増加させることができる。

【0033】

従って、サブ画素は、垂直方向に減少する開口率よりは、水平方向に増加する開口率がずっと大きいため、輝度及び開口率の向上を同時に図ることができる。

【0034】

このとき、上下方向に配置されたサブ画素が共通ラインを共有するように配置することで、開口率向上をもっと図ることができる。

【0035】

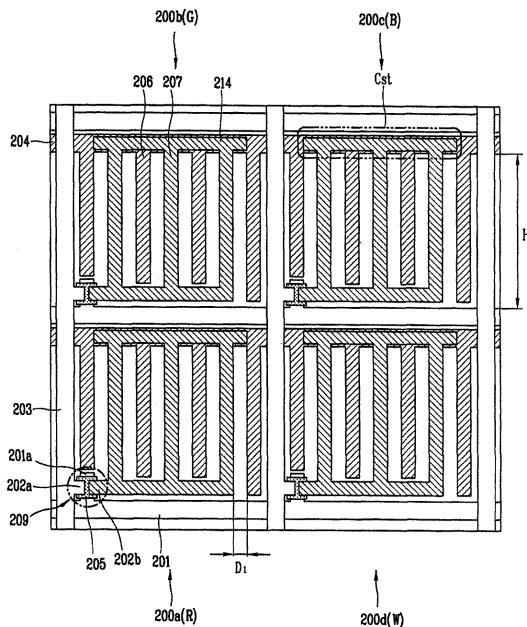

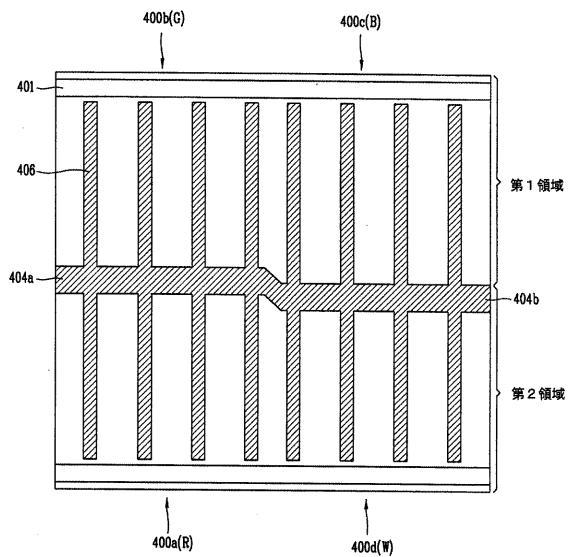

図3は、本発明の第3実施形態による、垂直に配列されたサブ画素が共通ラインを共有するインプレーンスイッチング方式の液晶表示素子を示す図である。

【0036】

本実施形態は、共通ラインの配置を除いて、全ての構成要素が第2実施形態(図2)と同一である。従って、以下、本実施形態と第2実施形態との差異点のみを説明する。

【0037】

図に示すように、本実施形態によるインプレーンスイッチング方式の液晶表示素子は、

10

20

30

40

50

ゲートライン 301 と平行して画素(P)の中心を通過する共通ライン 304 によってサブ画素が上下に分割され、R、G、B、Wサブ画素 300a～300d は、図2と同様に 2 × 2 形態に配列される。即ち、前記共通ライン 304 を基準にその上部領域を第1領域と言い、前記その下部領域を第2領域と言うと、前記第1領域には、G 及び B サブ画素 300b、300c が配置され、前記第2領域には、R 及び W サブ画素 300a、300d が配置される。

#### 【0038】

また、前記共通ライン 304 は、それぞれのサブ画素に配置された共通電極 306 と電気的に接続され、前記共通ライン 304 と重畳する画素電極ライン 314 と共にストレージキャパシタ(Cst)を形成する。

10

#### 【0039】

このとき、前記共通ライン 304 と重畳する画素電極ライン 314 は、第1領域に形成された画素電極 307 を電気的に連結する第1画素電極ライン 314a 及び第2領域に形成された画素電極 307 を電気的に連結する第2画素電極ライン 314b からなる。

#### 【0040】

前記のような構造を有するインプレーンスイッチング方式の液晶表示素子は、上下部に配置されたサブ画素間に1つの共通ラインを共有しているため、第2実施形態(図2)に比べて開口率が一層向上する。即ち、以前には、第1、第2領域にそれぞれ共通ラインが形成されたが、本実施形態は、第1、第2領域の境界面に共通ラインを配置し、垂直に配置されたサブ画素が前記共通ラインを共有しているため、配線形成面積を減少させることができる。

20

#### 【0041】

第1～第3実施形態を通じて説明したように、本発明は、Wサブ画素を追加して、R、G、B、Wそれぞれのサブ画素を 2 × 2 形態に配置することにより、輝度及び開口率を向上させることができる。あわせて、共通ラインを上下に配置された2つのサブ画素間に共有させることにより、開口率を一層向上させることができる。

#### 【0042】

一般的に、Wサブ画素の輝度は、R、G、Bサブ画素のそれぞれの輝度値の和より高い。しかしながら、駆動アルゴリズムを計算するとき、理論式では、前記 R、G、B サブ画素のそれぞれの輝度和が W サブ画素の輝度と同一であると見なして計算する。このため、実際 R、G、B サブ画素の輝度和が W サブ画素の輝度と同一になるように画素を設計する必要がある。

30

#### 【0043】

従って、本発明は、2 × 2 形態に配置されたインプレーンスイッチング方式の液晶表示素子のうち、特に、それぞれのサブ画素の面積を異にして構成し得るインプレーンスイッチング方式の液晶表示素子を提供する。

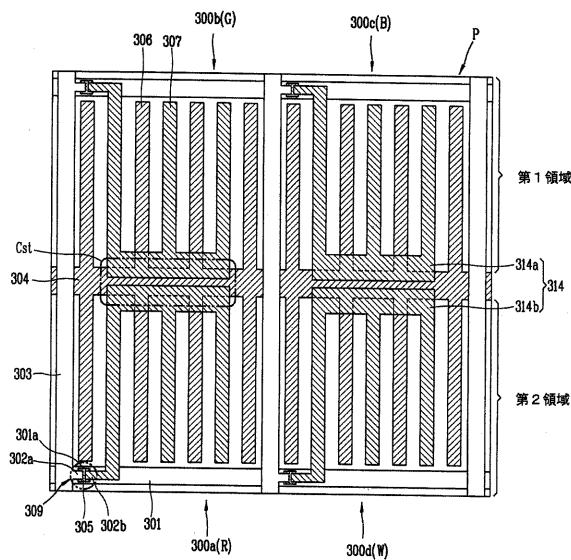

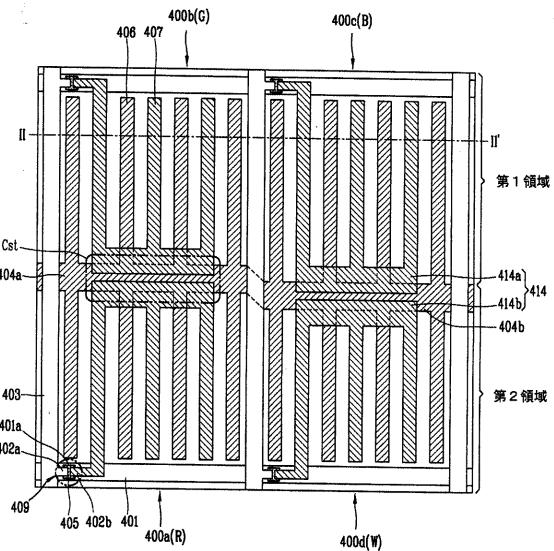

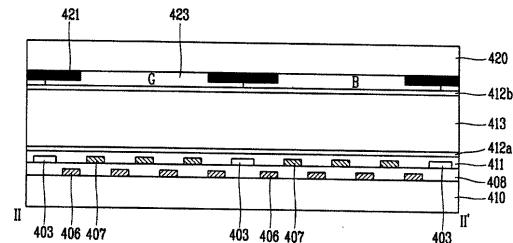

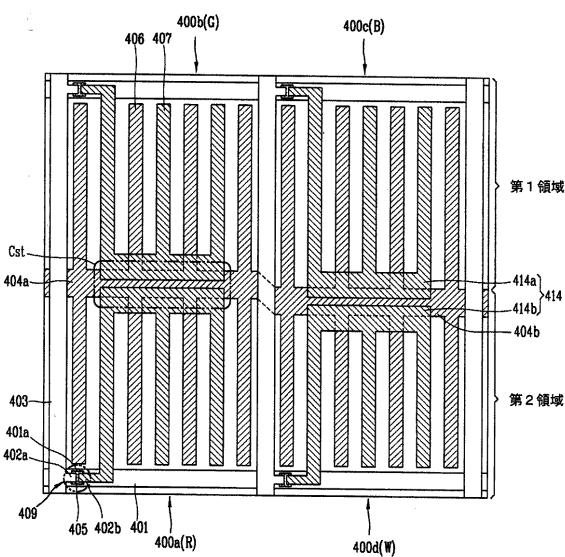

#### 【0044】

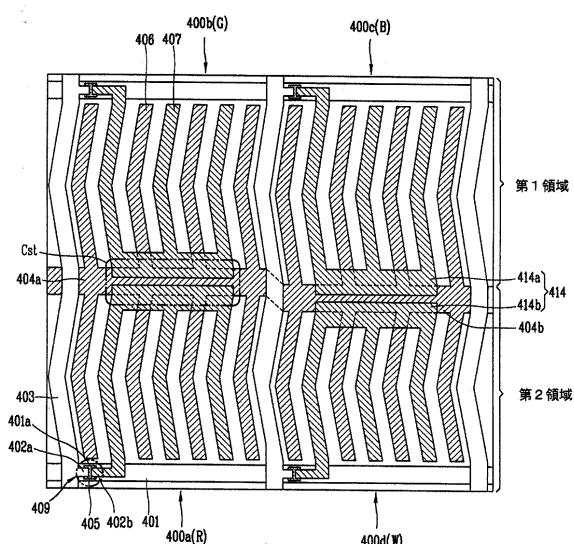

図4A及び図4Bは、本発明の第4実施形態による、サブ画素の面積が相異して構成されたインプレーンスイッチング方式の液晶表示素子を示す図である。図4Aは、平面図で、図4Bは、図4AのII-I'I'の断面図である。本実施形態は、第1領域及び第2領域を上下部に分割する第1及び第2共通ラインを除いて、全ての構成要素が第3実施形態(図3)と同一である。従って、本実施形態では、第3実施形態との差異点のみを説明する。

40

#### 【0045】

まず、図4Aに示すように、本実施形態によるインプレーンスイッチング方式の液晶表示素子は、第3の実施形態と同様に共通ラインを境界にサブ画素が上下に分割され、第1領域及び第2領域に分けられる。

#### 【0046】

前記第1領域は、G 及び B サブ画素 400b、400c から構成され、前記第2領域は、R 及び W サブ画素 400a、400d から構成される。また、前記第1領域の G サブ画

50

素 4 0 0 b 及び前記第 2 領域の R サブ画素 4 0 0 a は、第 1 共通ラインの 4 0 4 a によって分割され、R 及び G サブ画素 4 0 0 a、4 0 0 b の面積は同一である。また、前記第 1 領域の B サブ画素 4 0 0 c 及び前記第 2 領域の W サブ画素 4 0 0 d は、第 2 共通ライン 4 0 4 b によって分割され、その面積は、相異する。即ち、前記 B サブ画素 4 0 0 c の面積は、W サブ画素 4 0 0 d より広く形成される。これは、前記第 2 共通ライン 4 0 4 b を前記第 1 共通ラインの 4 0 4 a の位置より第 2 領域方向に偏って配置することによって可能である。即ち、前記第 2 共通ライン 4 0 4 b を前記第 1 共通ラインの 4 0 4 a の位置より下部方向にシフトさせることによって可能である。このとき、前記第 1 共通ラインの 4 0 4 a 及び第 2 共通ライン 4 0 4 b は、電気的に連結されるべきである。

## 【 0 0 4 7 】

10

前述したように、前記 B サブ画素 4 0 0 c 及び W サブ画素 4 0 0 d の面積を異にして分割することは、R、G、B サブ画素 4 0 0 a ~ 4 0 0 c の輝度和を W サブ画素 4 0 0 d の輝度と同一にするためであり、本発明では、W サブ画素 4 0 0 d の面積を減らすことによりこれを可能にする。

## 【 0 0 4 8 】

あわせて、前記 W サブ画素 4 0 0 d の面積が減少するによって、相対的に B サブ画素 4 0 0 c の面積が増加するようになるが、これは、R、G、B サブ画素 4 0 0 a ~ 4 0 0 c の総輝度値にほとんど影響を与えない。言い換えると、R、G、B サブ画素 4 0 0 a ~ 4 0 0 c 全体輝度に寄与する寄与度は、R、G、B 色相に対してそれぞれ 35%、55%、10% であり、前記 B サブ画素の輝度寄与度は、非常に少ない。従って、前記 B サブ画素 4 0 0 c の面積が減少しても、総輝度値がほとんど変化されずに W サブ画素 4 0 0 d の輝度を減らすことができる。これによって、R、G、B サブ画素 4 0 0 a ~ 4 0 0 c の総輝度値と W サブ画素 4 0 0 d の輝度値の差を最大限減少させることができる。

20

## 【 0 0 4 9 】

一方、前記 W サブ画素 4 0 0 d の面積を他のサブ画素の面積に比べて狭く形成さえすれば、R、G、B サブ画素の配置は、どのようになっても構わない。しかしながら、前述したように、B 色相のサブ画素が全体輝度寄与度が最小であるため、B サブ画素及び前記 W サブ画素が前記第 2 共通ラインによって上下領域に分割されることが望ましい。これは、前記第 2 共通ラインの垂直移動によって B 及び W サブ画素の面積が決定されるためである。

30

## 【 0 0 5 0 】

また、図 4 B に示すように、その断面構造を見ると、透明な第 1 基板 4 1 0 上に共通電極 4 0 6 が形成され、その上部にゲート絶縁膜 4 0 8 が塗布される。一方、前記ゲート絶縁膜 4 0 8 上には前記共通電極 4 0 6 と共に水平電界を発生させる画素電極 4 0 7 が形成される。また、その上部には、保護膜及び第 1 配向膜 4 1 2 a が塗布される。

## 【 0 0 5 1 】

あわせて、透明な第 2 基板 4 2 0 には、光漏れの防止のためのブラックマトリックス 4 2 1 及びカラーを実現のための R、G、B、W カラーフィルタ 4 2 3 が形成され、その上には第 2 配向膜 4 1 2 b が塗布される。また、前記第 1 及び第 2 基板 4 1 0、4 2 0 間には、前記画素電極 4 0 7 及び共通電極 4 0 6 間に発生される水平電界によって駆動が行われる液晶層 4 1 3 が形成される。

40

## 【 0 0 5 2 】

前述したような構造を有する本発明の第 4 実施形態は、共通ラインを上下部に配置されたサブ画素間に共有させ、前記共通ラインを所定間隔シフトさせることによって、サブ画素の面積を異に構成することができる。特に、B サブ画素及び W サブ画素によって共有される共通ラインをシフトさせることにより、R、G、B サブ画素の総輝度及び W サブ画素の輝度をほぼ同一にすることで、計算値による結果と実際製品の色相をほぼ一致するよう具現することができる。

## 【 0 0 5 3 】

一方、本発明は、共通電極及び画素電極の位置に限定せず、前記共通電極及び画素電

50

極を同一の平面上、特に、保護膜上に形成することもできる。前述したように、共通電極及び画素電極を同一の平面上に形成する場合、2つの電極間の電界がもっと強く生成され、このような強い電界によって液晶層内の液晶分子がもっと速い速度でスイッチングし得るという長所がある。

【0054】

また、前記2電極をITO(Indium Tin Oxide)またはIZO(Indium Zinc Oxide)のような透明な伝導性物質から形成することで開口率を一層向上させることができる。

【0055】

また、前記共通電極及び画素電極をジグザグ構造に形成することができる。即ち、図6に示すように、前記共通電極406及び画素電極407をジグザグ構造に形成することにより、マルチドメインを形成し、色特性を一層向上させることができる。

【0056】

以下、前記第4実施形態(図4A及び図4B)に示したインプレーンスイッチング方式の液晶表示素子の製造方法を簡略に説明する。

【0057】

図5A及び図5Bは、前記第4実施形態に示した液晶表示素子の製造方法を示す工程順序図で、平面図を示す。

【0058】

まず、図5Aに示すように、ガラスのような透明な絶縁基板410を用意した後、その上にCu、Ti、Cr、Al、Mo、Ta、Al合金のような金属をスパッタリング方法を通じて蒸着した後、パターニングゲートライン401、共通電極406、第1及び第2共通ライン404a、404bを形成する。このとき、前記第1共通ラインの404aは、ゲートライン401間の中心を通過するように形成し、第2共通ライン404bは、前記第1共通ラインの404aに比べて上部または下部側に偏るように形成し、これら2つの共通ライン404a、404bを相互電気的に連結させる。

【0059】

以後、前記ゲートライン401及び共通ライン404a、404bを含む基板410全面にSiNxまたはSiOxなどをプラズマCV方法によって蒸着してゲート絶縁膜(図示せず)を形成する。

【0060】

また、図5Bに示すように、前記ゲート絶縁膜(図示せず)上部に非晶質シリコン、n<sup>+</sup>非晶質シリコンを積層してパターニングすることで、ゲートライン401上に半導体層405を形成する。その次、前記半導体層405及びゲート絶縁膜(図示せず)上にCu、Mo、Ta、Al、Cr、Ti、Al合金のような金属をスパッタリング方法を通じて蒸着した後、これをパターニングしてゲートライン401と垂直に配置され、前記ゲートライン401及び第1、第2共通ラインの404a、404bと共に4つのサブ画素を定義するデータライン403と、前記半導体層405上に所定間隔離隔するソース/ドレイン電極402a/402bと、前記第1、第2共通ラインの404a、404bと重畠してストレージキャパシタ(Cst)を形成する画素電極ライン414と、該画素電極ライン414と電気的に連結され、共通ライン404と平行した画素電極407を形成する。

【0061】

その後、薄膜トランジスタ409が形成された基板上にSiNxやSiOxのような無機物またはベンゾシクロブテン(benzocyclobutene)やアクリルのような有機物を塗布して保護膜(図示せず)を形成する。

【0062】

次いで、カラーフィルタが形成された第2基板と共に合着して液晶表示素子のパネルを完成する。

【0063】

このとき、前記共通電極及び画素電極は、保護膜の上部に形成することもでき、前記2電極をITOやIZOのような透明な伝導性物質から形成することもできる。

10

20

30

40

50

## 【図面の簡単な説明】

【 0 0 6 4 】

【図1】本発明の第1実施形態によるインプレーンスイッチング方式の液晶表示素子を示す図である。

【図2】本発明の第2実施形態によるインプレーンスイッチング方式の液晶表示素子を示す図である。

【図3】本発明の第3実施形態によるインプレーンスイッチング方式の液晶表示素子を示す図である。

【図4A】本発明の第4実施形態によるインプレーンスイッチング方式の液晶表示素子を示す図である。

【図4B】本発明の第4実施形態によるインプレーンスイッチング方式の液晶表示素子を示す図である。

【図5A】本発明によるインプレーンスイッチング方式の液晶表示素子の製造方法を示す図である。

【図5B】本発明によるインプレーンスイッチング方式の液晶表示素子の製造方法を示す図である。

【図6】本発明の第5実施形態によるインプレーンスイッチング方式の液晶表示素子を示す図である。

【図7A】一般的なインプレーンスイッチング方式の液晶表示素子の構造を示す図である

【図7B】一般的なインプレーンスイッチング方式の液晶表示素子の構造を示す図である。

【 四 1 】

【 図 2 】

【図3】

【図4A】

【 図 4 B 】

【図5A】

【図5B】

【図6】

【図7 A】

【図7 B】

---

フロントページの続き

(72)発明者 白 欽 日

大韓民国 京畿道 安養市 東安區 虎溪2洞 ハンメウム イムクwan アパート 203-4

02

審査官 福島 浩司

(56)参考文献 特開2003-280037 (JP, A)

特開平09-090343 (JP, A)

特開平04-355722 (JP, A)

特開2000-187231 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1368

G 02 F 1 / 1343

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 面内切换型液晶显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP4209378B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2009-01-14 |

| 申请号            | JP2004316013                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2004-10-29 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | Eruji. 菲利普斯杜天公司，有限公司                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 当前申请(专利权)人(译)  | Eruji显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| [标]发明人         | 白欽日                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 白欽日                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G02F1/1368 G02F1/1343 G02F1/133 G02F1/136 G02F1/1362 H01L21/00 H01L29/786                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | G02F1/134363 G02F1/136213 G02F2201/52                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| FI分类号          | G02F1/1368 G02F1/1343                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 2H092/GA13 2H092/GA14 2H092/GA23 2H092/GA26 2H092/GA28 2H092/JA26 2H092/JA28 2H092/JA37 2H092/JA41 2H092/JA45 2H092/JB02 2H092/JB04 2H092/JB05 2H092/JB06 2H092/JB23 2H092/JB26 2H092/JB32 2H092/JB35 2H092/JB64 2H092/MA01 2H092/MA10 2H092/MA12 2H092/NA07 2H092/NA25 2H092/QA06 2H092/QA09 2H192/AA24 2H192/AA43 2H192/BB02 2H192/BB53 2H192/CB05 2H192/CC04 2H192/CC24 2H192/CC55 2H192/DA32 2H192/EA22 2H192/EA43 2H192/EA53 2H192/EA54 |         |            |

| 代理人(译)         | 臼井伸一<br>朝日伸光                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 审查员(译)         | 福岛浩二                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 优先权            | 1020030076079 2003-10-29 KR                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 其他公开文献         | JP2005134914A                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

## 摘要(译)

要解决的问题：提供一种面内切换模式液晶显示装置并提供其制造方法。解决方案：面内切换模式液晶显示装置包括第一和第二基板，分别水平设置在第一基板上的多条栅极线，垂直设置在第一基板上并限定排列在第一基板中的第一至第四子像素的数据线2x2矩阵形式与栅极线一起，至少一对第一和第二电极设置在每个子像素中，第一公共线以第一面积比设置在第一和第二子像素之间并连接到第一电极设置在第一和第二子像素中的第二公共线，以第二面积比设置在第三和第四子像素之间，连接到设置在第三和第四子像素中的第一电极，并且形成为第一和第二面积比彼此不同，形成在栅极线和数据线的交叉区域的开关器件和形成在第一和第二面积比之间的液晶层e第一和第二基板。Z

【图 2】