(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-264231

(P2007-264231A)

(43) 公開日 平成19年10月11日(2007.10.11)

(51) Int. Cl.

GO2F 1/1343 (2006.01)

GO2F 1/1368 (2006.01)

F 1

GO2F 1/1343

GO2F 1/1368

### テーマコード（参考）

2H092

審査請求 未請求 請求項の数 4 O L (全 15 頁)

(21) 出願番号

特願2006-88208 (P2006-88208)

(22) 出願日

平成18年3月28日(2006.3.28)

(71) 出願人 304053854

エプソンイメージングデバイス株式会社

長野県安曇野市豊科田沢6925

(74) 代理人 100095728

弃理士 上柳 雅誉

(74) 代理人 100107261

弁理士 須澤 修

(72) 発明者 金子 英樹

東京都港区浜松町二丁目4番1号 三洋工

プソンイメージングデバイス株式会社内

(73) 代理人 金子 英樹

(72) 発明者 城口 正寛

東京都港区浜松町二丁目4番1号 三洋エ

プソンイメージングデバイス株式会社内

F ターム (参考) 2H092 GA13 GA14 GA22 JA26 JB03

JB05 JB11 JB32 NA01 NA07

QA06

(54) 【発明の名称】 FFSモードの液晶表示パネル

(57) 【要約】

【課題】視角対称性を有し、横方向の斑の発生がなく、しかも広視野角で、透過率が高く明るい表示が可能で、表示画質が良好なFFSモードの液晶表示パネルを提供すること。

【解決手段】本発明は、平行に設けられた複数の走査線 12 及びコモン配線 13 と、前記走査線 12 と直交する方向にクランク状に設けられた複数の信号線 14 と、複数の前記走査線 12 及び信号線 14 の間にそれぞれ形成された画素電極 18<sub>1</sub>、18<sub>2</sub> とを有し、前記複数の画素電極 18<sub>1</sub>、18<sub>2</sub> をデルタ配置した FFS モードの液晶表示パネルにおいて、前記複数の画素電極 18<sub>1</sub>、18<sub>2</sub> のそれぞれは隣り合う前記走査線 12 の間に位置する前記走査線 12 に平行な軸に x 対して互いに異なる方向に傾いた複数のスリット 17<sub>1</sub>、17<sub>2</sub> を有し、前記画素電極は奇数行の画素電極 18<sub>1</sub> 及び偶数行の画素電極 18<sub>2</sub> とが前記軸 x に対して互いに反転した構造を備えていること。

**【特許請求の範囲】****【請求項 1】**

平行に設けられた複数の走査線及びコモン配線と、前記走査線と直交する方向にクランク状に設けられた複数の信号線と、複数の前記走査線及び信号線の間にそれぞれ形成された画素電極とを有し、複数の前記画素電極をデルタ配置したフリンジ・フィールド・スイッチングモードの液晶表示パネルにおいて、前記複数の画素電極のそれぞれは隣り合う前記走査線の間に位置する前記走査線に平行な軸に対して互いに異なる方向に傾いた複数のスリットを有し、前記画素電極は奇数行の画素電極と偶数行の画素電極とが前記走査線に垂直な軸に対して互いに反転した構造を備えていることを特徴とするフリンジ・フィールド・スイッチングモードの液晶表示パネル。

10

**【請求項 2】**

前記走査線に平行な軸の両側に設けられたスリットの数はそれぞれの側で同一数であることを特徴とする請求項 1 に記載のフリンジ・フィールド・スイッチングモードの液晶表示パネル。

**【請求項 3】**

前記走査線に平行な軸の前記画素電極の下部には、前記コモン配線が設けられていることを特徴とする請求項 1 に記載のフリンジ・フィールド・スイッチングモードの液晶表示パネル。

**【請求項 4】**

前記走査線に平行な軸に最も近接する両側のスリットの端部は前記走査線に平行な軸上で結合されていることを特徴とする請求項 1 ~ 3 のいずれかに記載のフリンジ・フィールド・スイッチングモードモードの液晶表示パネル。

20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、フリンジ・フィールド・スイッチング (Fringe Field Switching: 以下、「FFS」という。) モードの液晶表示パネルに関し、特に画素の配列をデルタ配置としたデュアルドメイン構造の FFS モードの液晶表示パネルに関する。

**【背景技術】****【0002】**

近年、情報通信機器のみならず一般の電気機器においても液晶表示パネルが多く利用されている。従来から多く用いられている液晶表示パネルは、表面に電極等が形成された一対のガラス等からなる基板と、この一対の基板間に形成された液晶層と、からなり、両基板上の電極に電圧が印加されることにより、液晶分子を再配列させて光の透過率を変えることにより種々の映像を表示する、言わば縦方向電界モードともいいうべきものである。このような縦方向電界モードの液晶表示パネルは、TN (Twisted Nematic) モードやVA (Vertical Alignment) モードのもの存在するが、視野角が狭いという問題点が存在するため、MVA (Multidomain Vertical Alignment) モード等種々の改良された縦方向電界モードの液晶表示パネルが開発されている。

30

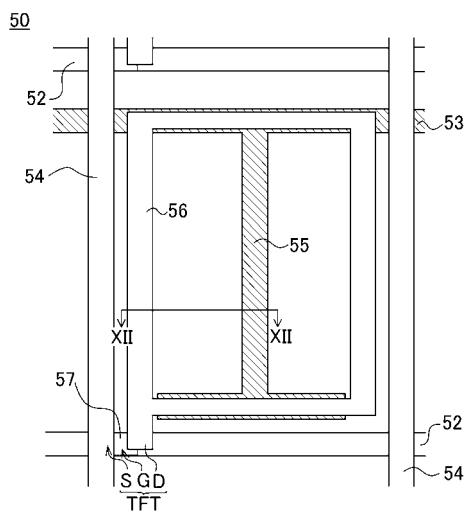

**【0003】**

一方、上述の縦方向電界モードの液晶表示パネルとは異なり、一方の基板にのみ電極を備えた横方向電界モードと言うべき液晶表示パネルも、IPS (In-Plane Switching) モードの液晶表示パネルとして知られている (下記特許文献 1 参照)。ここでこの IPS モードの液晶表示パネルの動作原理を図 11 及び図 12 を用いて説明する。なお、図 11 は IPS モードの液晶表示パネルの 1 画素分の概略平面図であり、図 12 は図 11 の XII-XII 線に沿った概略断面図である。

40

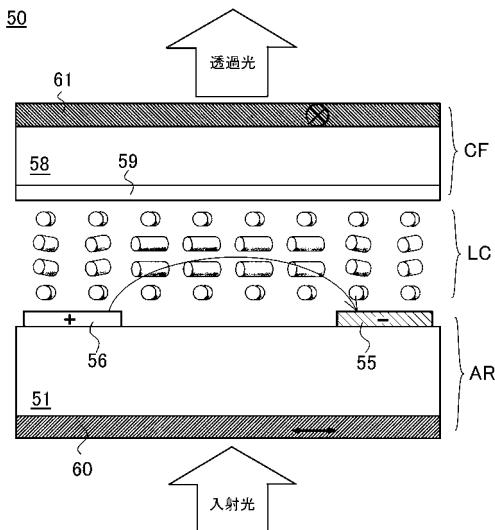

**【0004】**

この IPS モードの液晶表示パネル 50 は、アレイ基板 AR とカラーフィルタ基板 CF とを備えている。アレイ基板 AR は、第 1 の透明基板 51 の表面にそれぞれ平行に複数の走査線 52 及びコモン配線 53 が設けられ、これら走査線 52 及びコモン配線 53 に直交

50

する方向に複数の信号線 5 4 が設けられている。そして、各画素の中央部にコモン配線 5 3 から帯状に、図 1 1においては逆 T 字状に、対向電極 5 5 が設けられ、この対向電極 5 5 の周囲を囲むように画素電極 5 6 が設けられている。

#### 【 0 0 0 5 】

そして、走査線 5 2 と信号線 5 4との間にスイッチング素子としての TFT (Thin Film Transistor) が形成されている。この TFT は、走査線 5 2 と信号線 5 4との間に半導体層 5 7 が配置され、半導体層 5 7 上の信号線部分が TFT のソース電極 S を構成し、半導体層 5 7 の下部の走査線部分がゲート電極 G を構成し、また、半導体層 5 7 の一部分と重なる画素電極 5 6 の部分がドレイン電極 D を構成している。

#### 【 0 0 0 6 】

また、カラーフィルタ基板 C F は、第二の透明基板 5 8 の表面にカラーフィルタ層 5 9 が設けられた構成を有している。そして、アレイ基板 A R の画素電極 5 6 及び対向電極 5 5 とカラーフィルタ基板 C F のカラーフィルタ層 5 9 とが互いに対向するようにアレイ基板 A R 及びカラーフィルタ基板 C F を対向させ、その間に液晶 L C を封入するとともに、両基板のそれぞれ外側に偏光板 6 0 及び 6 1 を偏光方向が互いに直交する方向となるように配置することにより、IPS モードの液晶表示パネル 5 0 が形成される。

#### 【 0 0 0 7 】

この IPS モードの液晶表示パネル 5 0 は、図 1 2 に示したように、画素電極 5 6 と対向電極 5 5 との間に電界を形成すると、水平方向に配向していた液晶分子が水平方向に旋回することによりバックライトからの入射光の透過量を制御することができるようになる。この IPS モードの液晶表示パネル 5 0 は、広視野角で、高コントラストであり、また、画素電極 5 6 と対向電極 5 5 とが比較的狭い間隔で配置されているために保持容量が副次的に生じるという長所があるが、対向電極 5 5 がコモン配線 5 3 と同じ金属材料で形成されるために開口率及び透過率が低く、又、視角による色変化があるという問題点が存在する。

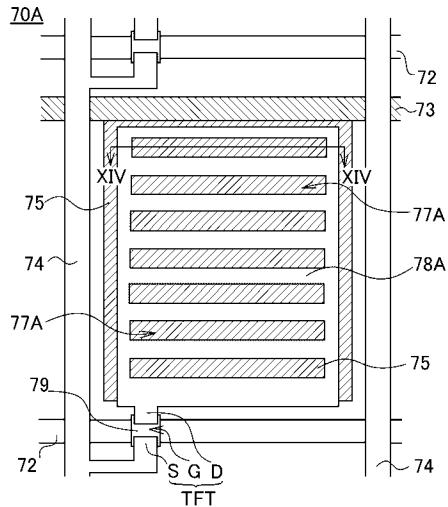

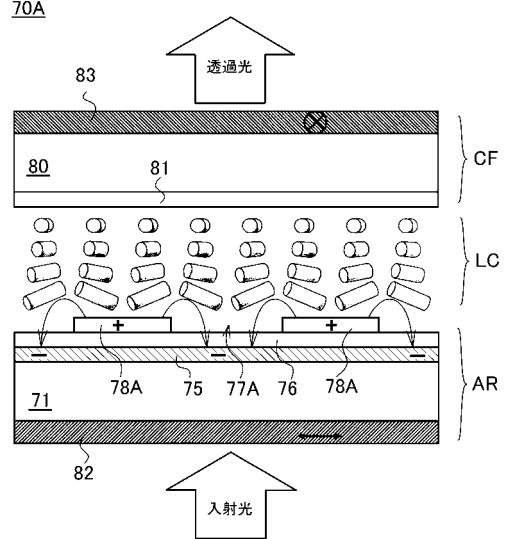

#### 【 0 0 0 8 】

このような IPS モードの液晶表示パネルの低開口率及び低透過率という問題点を解決するために、いわゆる斜め電界方式とも言うべき FFS モードの液晶表示装置が開発されている（下記特許文献 2 ~ 4 参照）。この FFS モードの液晶表示パネル動作原理を図 1 3 及び図 1 4 を用いて説明する。なお、図 1 3 は FFS モードの液晶表示パネルの 1 画素分の概略平面図であり、図 1 4 は図 1 3 の XIV-XIV 線に沿った概略断面図である。

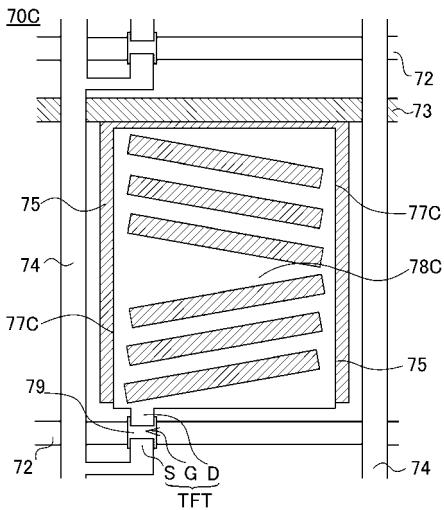

#### 【 0 0 0 9 】

この FFS モードの液晶表示パネル 7 0 A は、アレイ基板 A R とカラーフィルタ基板 C F とを備えている。アレイ基板 A R は、第 1 の透明基板 7 1 の表面にそれぞれ平行に複数の走査線 7 2 及びコモン配線 7 3 が設けられ、これら走査線 7 2 及びコモン配線 7 3 に直交する方向に複数の信号線 7 4 が設けられている。そして、各画素の表面全体を覆うようにコモン配線 7 3 に接続された ITO (Indium Tin Oxide) 等からなる透明材料で形成された対向電極 7 5 が設けられ、この対向電極 7 5 の表面に絶縁膜 7 6 を介してストライプ状に複数のスリット 7 7 A が形成された ITO 等の透明材料からなる画素電極 7 8 A が設けられている。

#### 【 0 0 1 0 】

そして、走査線 7 2 と信号線 7 4 との交点近傍にはスイッチング素子としての TFT が形成されている。この TFT は、走査線 7 2 の表面に半導体層 7 9 が配置され、半導体層 7 9 の表面の一部を覆うように信号線 7 4 の一部が延在されて TFT のソース電極 S を構成し、半導体層 7 9 の下部の走査線部分がゲート電極 G を構成し、また、半導体層 7 9 の一部分と重なる画素電極 7 8 A の部分がドレイン電極 D を構成している。

#### 【 0 0 1 1 】

また、カラーフィルタ基板 C F は、第二の透明基板 8 0 の表面にカラーフィルタ層 8 1 が設けられた構成を有している。そして、アレイ基板 A R の画素電極 7 8 A 及び対向電極 7 5 とカラーフィルタ基板 C F のカラーフィルタ層 8 1 とが互いに対向するようにアレイ

基板 A R 及びカラーフィルタ基板 C F を対向させ、その間に液晶 L C を封入するとともに、両基板のそれぞれ外側に偏光板 8 2 及び 8 3 を偏光方向が互いに直交する方向となるように配置することにより、FFS モードの液晶表示パネル 70A が形成される。

#### 【0012】

このFFS モードの液晶表示パネル 70A は、画素電極 78A と対向電極 75 の間に電界を形成すると、図 14 に示したように、この電界は画素電極 78A の両側で対向電極 75 に向かうため、画素電極 78A 間に存在する液晶分子だけでなく画素電極 78A 上に存在する液晶分子も動くことができる。そのため、FFS モードの液晶表示パネル 70A は、IPS モードの液晶表示パネル 50 よりも広視野角かつ高コントラストであり、更に高透過率であるため明るい表示が可能となるという特徴を備えている。加えて、FFS モードの液晶表示パネル 70A は、IPS モードの液晶表示パネル 50 よりも平面視で画素電極 78A と対向電極 75 との重複面積が大きいためにより大きな保持容量が副次的に生じ、別途補助容量線を設ける必要がなくなるという長所が存在する。

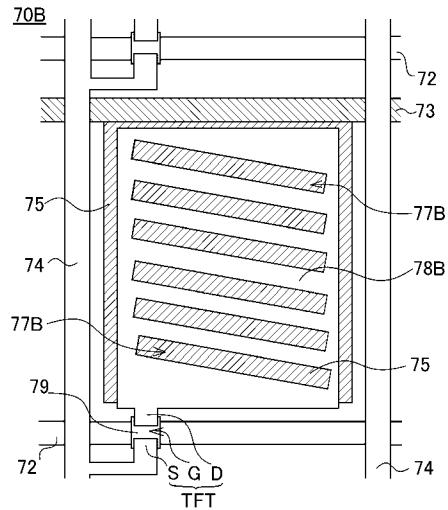

#### 【0013】

なお、FFS モードの液晶表示パネルにおいては、下記特許文献 1 に開示されている IPS モードの液晶表示パネルの場合と同様に、表示特性上、ラビング方向は信号線と直交するのがよく、また画素電極とラビング方向とは微小角度の傾きを設けた方がよいことから、図 15 に示した FFS モードの液晶表示パネル 70B のように画素電極 78B に設けるストライプ状のスリット 77B を走査線 72 ないしコモン配線 73 に対して傾いた構造とすることが行われてあり、同じく、視角によって色変化が認められなくなるようにするため、図 16 に示した FFS モードの液晶表示パネル 70C のように、画素電極 78C に設けるストライプ状のスリット 77C を「く」字状となるように配置してデュアルドメイン化することも行われている。なお、図 15 及び図 16 に示した FFS モードの液晶表示パネル 70B 及び 70C は、図 13 に示した FFS モードの液晶表示パネル 70A とは画素電極 78B ないし 78C に設けるスリット 77B ないし 77C の傾きが相違するのみであるので、図 13 に示した FFS モードの液晶表示パネル 70A と同一の構成部分については同一の参照符号を付与してその詳細な説明は省略する。

【特許文献 1】特開 2005-338256 号公報（段落 [0026] ~ [0060]、図 1、図 12 ~ 図 17）

【特許文献 2】特開 2000-131720 号公報（段落 [0002] ~ [0006]、図 1 ~ 図 3）

【特許文献 3】特開 2002-14363 号公報（特許請求の範囲、段落 [0002] ~ [0010]、[0019] ~ [0026]、図 1、図 2）

【特許文献 4】特開 2002-244158 号公報（特許請求の範囲、段落 [0002] ~ [0013]、[0023] ~ [0032]、図 1 ~ 図 4）

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0014】

上述のように、FFS モードの液晶表示パネルは、IPS モードの液晶表示パネルよりも広視野角かつ高コントラストであるとともに、高透過率であるため明るい表示が可能となり、更に低電圧駆動ができるとともににより大きな保持容量が副次的に生じるために別途補助容量線を設けなくても表示画質が良好となるという特徴を備えている。ところで、上記特許文献 2 ~ 4 に開示されている FFS モードの液晶表示パネルは、各画素が行方向及び列方向に整列されており、通常はストライプ配置のカラーフィルタないしはダイアゴナル配置のカラーフィルタと組み合わされて使用されるものであるが、特にデジタルスチルカメラなどの画像を主に表示する用途においては各画素を互い違いに配置するデルタ配置（トライアングル配置ともいう）が採用されることがある。

#### 【0015】

この場合、FFS モードの液晶表示パネルにおいては、各画素をデルタ配置とする場合、表示ムラを少なくするためにスリットの形状は全ての画素電極において同一形状とする

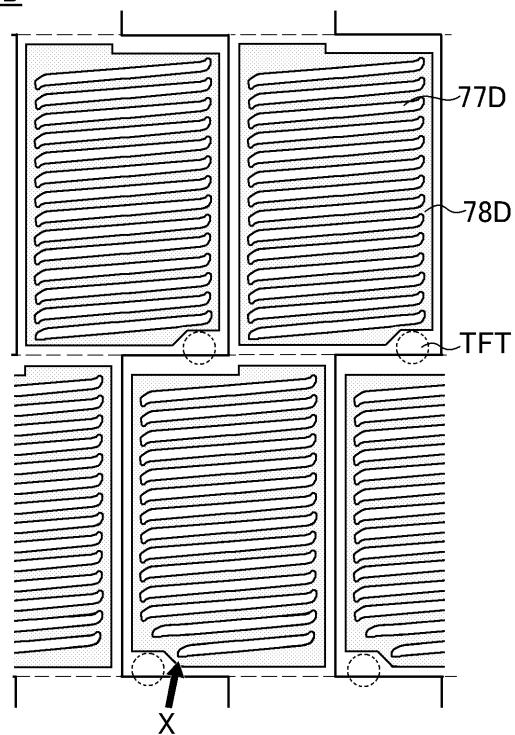

ことが好ましい。しかしながら、信号線をクランク状ではあるが実質的に走査線と直交する方向に配線長を短くして配置する必要があるため、奇数行と偶数行とでTFTの位置が異なってしまう。このような状態を図17を用いて説明する。なお、図17は、各画素をデルタ配置としたFFSモードの液晶表示パネル70Dの数画素分の概略平面図であって、画素電極78Dとこの画素電極78Dに設けられたスリット77Dのみを示し、その他の具体的構成は省略してある。また、図17における各画素間の破線は各画素の境界を示し、実線は信号線の経路を示し、また、破線丸印で囲んだ部分はそれぞれの画素のTFTが設けられている位置を示す。

#### 【0016】

図17に示したFFSモードの液晶表示パネル70Dは、奇数行の画素のTFTは図面上右下に位置するが、偶数行の画素のTFTは図面上左下に位置しているため、信号線をクランク状にではあるが縦方向に直線状にかつ配線長を短く配置することができる。しかしながら、このFFSモードの液晶表示パネル70Dは、奇数行の画素の画素電極に設けられたスリットの形状を表示開口を有効利用できるように最適な形状としたものであるが、偶数行の画素電極に設けられたスリットの形状は矢印Xで示す位置のスリットの形状が奇数行のものと異なってしまい、同じ形状にすることができないので、視角対称性が失われてしまう。そのため、このFFSモードの液晶表示パネル70Dを表示させた際には横方向に班が生じてしまう。逆に各画素の画素電極のスリットの形状を奇数行と偶数行とで同一になるようにすると、表示開口を有効に利用することができなくなる。このような状況は、画素電極に設けるスリットをデュアルドメイン構造とした各画素をデルタ配置したFFSモードの液晶表示パネルについても同様に生じる現象である。

#### 【0017】

本発明は、上述のような画素電極に設けるスリットをデュアルドメイン構造とした各画素をデルタ配置したFFSモードの液晶表示パネルにおける問題点を解決すべくなされたものであって、視角対称性を有し、横方向の斑の発生がなく、しかも広視野角で、透過率が高く明るい表示が可能で、表示画質が良好なFFSモードの液晶表示パネルを提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0018】

上記目的を達成するため、本願のFFSモードの液晶表示パネルの発明は、平行に設けられた複数の走査線及びコモン配線と、前記走査線と直交する方向にクランク状に設けられた複数の信号線と、複数の前記走査線及び信号線の間にそれぞれ形成された画素電極とを有し、複数の前記画素電極をデルタ配置したフリンジ・フィールド・スイッチングモードの液晶表示パネルにおいて、前記複数の画素電極のそれぞれは隣り合う前記走査線の間に位置する前記走査線に平行な軸に対して互いに異なる方向に傾いた複数のスリットを有し、前記画素電極は奇数行の画素電極と偶数行の画素電極とが前記走査線に垂直な軸に対して互いに反転した構造を備えていることを特徴とする。

#### 【0019】

また、本願のFFSモードの液晶表示パネルの発明は、上記FFSモードの液晶表示パネルにおいて、前記走査線に平行な軸の両側に設けられたスリットの数はそれぞれの側で同一数であることを特徴とする。

#### 【0020】

また、本願のFFSモードの液晶表示パネルの発明は、上記FFSモードの液晶表示パネルにおいて、前記走査線に平行な軸の前記画素電極の下部には、前記コモン配線が設けられていることを特徴とする。

#### 【0021】

また、本願のFFSモードの液晶表示パネルの発明は、上記FFSモードの液晶表示パネルにおいて、前記走査線に平行な軸に最も近接する両側のスリットの端部は前記走査線に平行な軸上で結合されていることを特徴とする。

#### 【発明の効果】

10

20

20

30

40

50

## 【0022】

本発明は上記構成を備えることにより以下に述べるような優れた効果を奏する。すなわち、上記のFFSモードの液晶表示パネルの発明によれば、奇数行の画素と偶数行の画素とで画素電極を駆動するためのスイッチング素子、例えば TFT が異なる位置に存在することとなるが、信号線の配線長を短くできるとともに、しかも各画素の画素電極に設けられたスリットの形状は、デッドスペースを最小限にしながら走査線に平行な軸に対して対称な実質的に同じ形状となっているとともに、行毎に走査線に垂直な軸に対して対称性を備えているから、表示開口を有効に利用しながら走査線に平行な方向及び垂直な方向ともに視角対称性が維持され、従来例のような横方向に班が生じることがなくなるとともに明るい表示のFFSモードの液晶表示パネルが得られる。

10

## 【0023】

また、上記発明によれば、走査線に平行な軸の両側に設けられた画素電極のスリットの数はそれぞれの側で同一数とされているから、画素電極の形状は一画素内で走査線と平行な軸に対して完全に近い対称性を有するようになり、走査線に垂直な方向の視角の対称性が高まり、より広視野角で表示画質が良好なFFSモードの液晶表示パネルが得られる。

20

## 【0024】

また、上記発明によれば、コモン配線は、通常は走査線と同材質の導電性材料から作製されるために不透明であるが、このコモン配線によって互いに異なる方向に傾いたスリット同士が隣り合う位置で発生するディスクリネーション部分を遮光することができ、表示画質が良好なFFSモードの液晶表示パネルが得られる。

20

## 【0025】

上記発明によれば、走査線に平行な軸に最も近接する両側のスリットの端部を走査線に平行な軸上で結合することによって、画素電極の面積を有効に利用することができ、しかも両スリットの結合点近傍のディスクリネーションの発生が抑制されるため、表示画質がより良好なFFSモードの液晶表示パネルが得られる。

30

## 【発明を実施するための最良の形態】

## 【0026】

以下、図面を参照して本発明の最良の実施形態を説明する。但し、以下に示す実施形態は、本発明の技術思想を具体化するためのFFSモードの液晶表示パネルの構成を製造工程順に例示するものであって、本発明をこのFFSモードの液晶表示パネルに特定することを意図するものではなく、特許請求の範囲に含まれる他の実施形態のものも等しく適応し得るものである。

30

## 【0027】

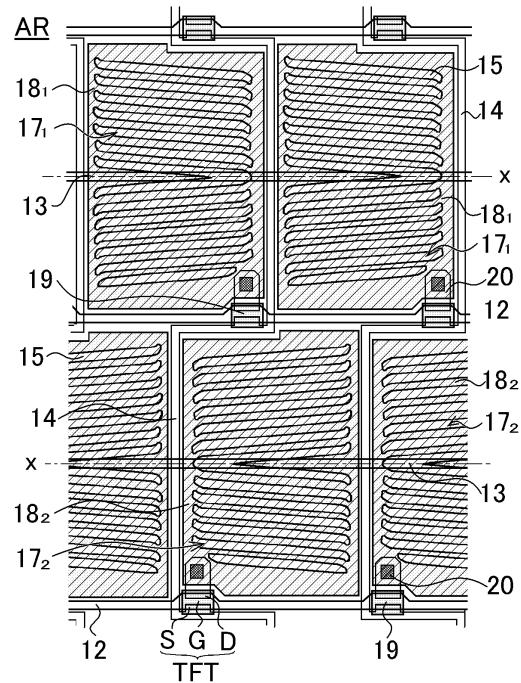

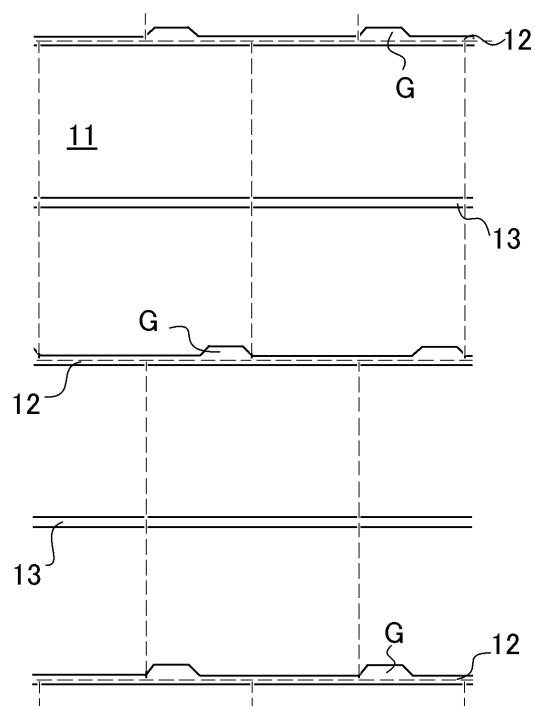

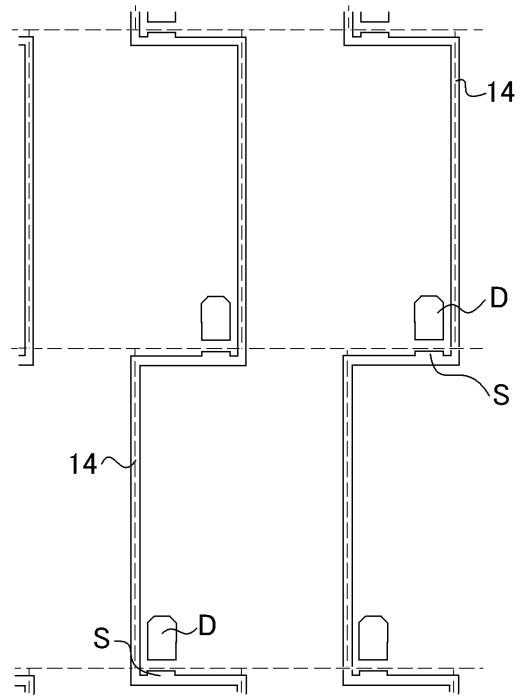

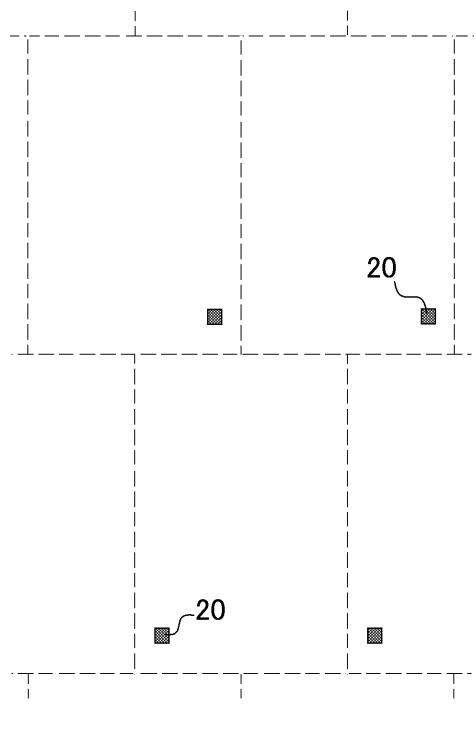

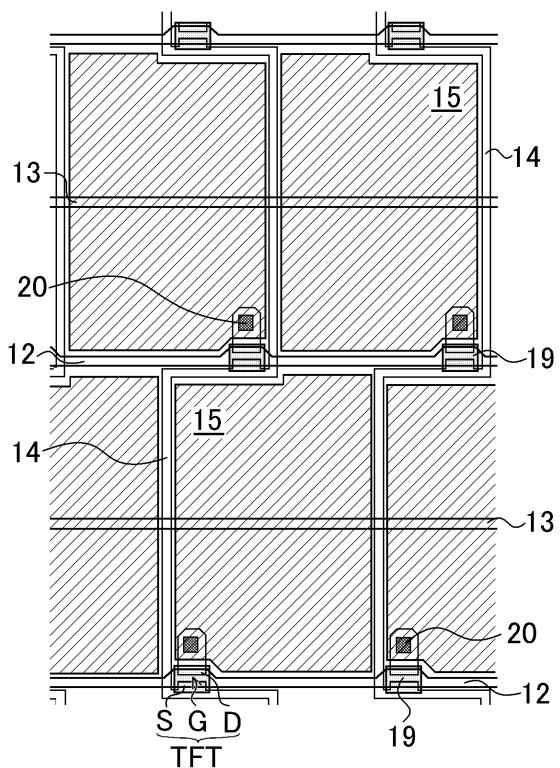

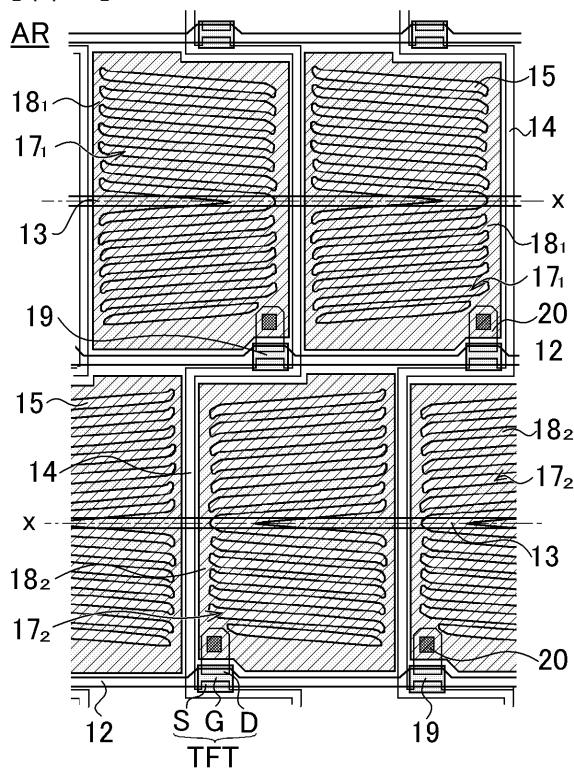

なお、図1は走査線及びコモン配線形成工程で形成された走査線及びコモン配線のパターンを示す図であり、図2は対向電極形成工程で形成された対向電極のパターンを示す図であり、図3は半導体層形成工程で形成された半導体層のパターンを示す図であり、図4は信号線及びドレイン電極形成工程で形成された信号線及びドレイン電極のパターンを示す図であり、図5はコンタクトホール形成工程で形成されたコンタクトホールのパターンを示す図であり、図6は図1～図5の全てパターンを上下関係を無視して重ねて表した平面図である。

40

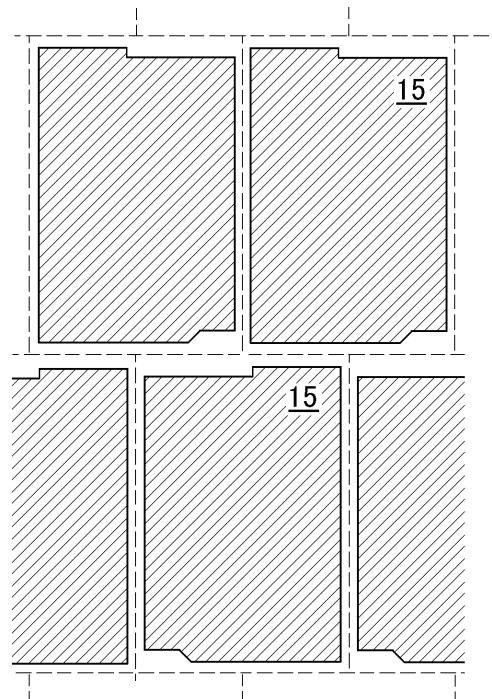

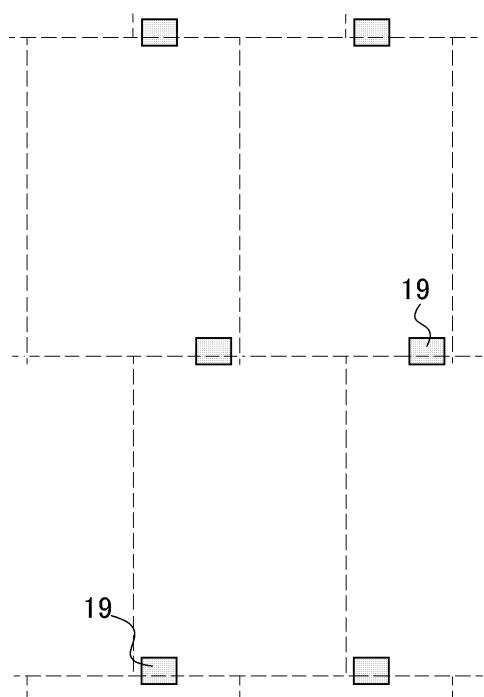

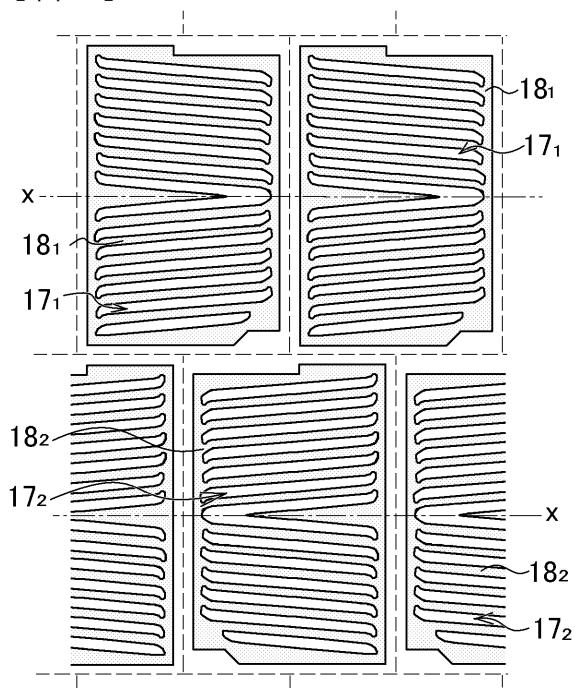

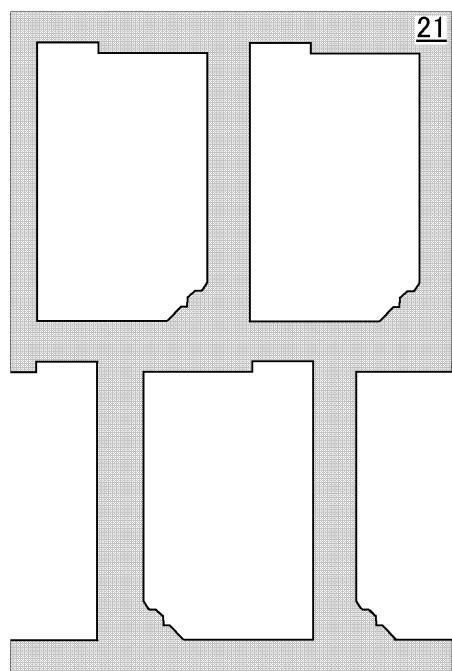

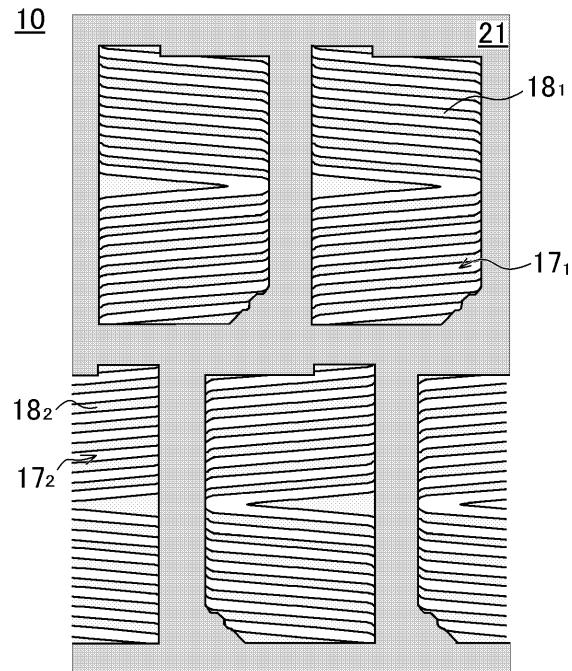

## 【0028】

更に、図7は画素電極形成工程で形成された画素電極のパターンを示す図であり、図8は図6及び図7のパターンを上下関係を無視して重ねて表した平面図であり、図9はカラーフィルタ基板に設けるブラックマトリクスのパターンを示す図であり、図10は図7のパターンの上に図9のパターンを重ねて表した図である。

## 【0029】

この実施例のFFSモードの液晶表示パネル10の製造工程を、アレイ基板の製造工程とカラーフィルタ基板の製造工程に分けて説明する。

## [アレイ基板製造工程]

## (1) 走査線・コモン配線形成工程

50

まず、ガラス基板等の透明基板11の表面全体に亘って下部がAl金属からなり表面がMo金属からなる2層膜を形成した後、フォトリソグラフィー法及びエッチング法によって、図1に示したようなパターンのそれぞれMo/Alの2層配線からなる複数の走査線12及び複数のコモン配線13を互いに平行に形成する。その際、走査線12の一部にTFTのゲート電極G部分を突出させておく。なお、コモン配線13は隣り合う走査線12の中間に設けられる。なお、図1において破線部分は各画素の境界部分を示す（以下、他の図面においても同じ。）

## 【0030】

## (2) 対向電極形成工程

次いで、ITOからなる透明導電性層を(1)の走査線・コモン配線形成工程を経た透明基板11の表面全体に亘って被覆し、同じくフォトリソグラフィー法及びエッチング法によって、図2に示したようなパターンの対向電極15を形成する。この対向電極15はコモン配線13とは電気的に接続されているが、走査線12ないしゲート電極Gとは接続されていない。

## 【0031】

## (3) 絶縁膜形成工程

次いで、窒化硅素層ないしは酸化硅素層からなる絶縁膜を(2)の対向電極形成工程を経た透明基板11の表面全体に亘って被覆する。

## 【0032】

## (4) 半導体層形成工程

次いで、CVD法によりアモルファス・シリコン（以下「a-Si」という。）層を(3)の絶縁膜形成工程を経た透明基板11の表面全体に亘って被覆し、同じくフォトリソグラフィー法及びエッチング法によって、図3に示したようなパターンのa-Si層からなる半導体層19をゲート電極G上に位置するように形成する。

## 【0033】

## (5) 信号線・ドレイン電極形成工程

次いで、Mo/Al/Moの3層構造の導電性層を(4)の半導体層形成工程を経た透明基板11の表面全体に亘って被覆し、同じくフォトリソグラフィー法及びエッチング法によって、図4に示したようなパターンの信号線14及びドレイン電極Dを形成する。この信号線14のソース電極S部分及びドレイン電極D部分は、いずれも半導体層19の表面に部分的に重なっている。

## 【0034】

## (6) パッシベーション膜形成工程

次いで、窒化硅素層からなるパッシベーション膜を(5)の信号線・ドレイン電極形成工程を経た透明基板11の表面全体に被覆する。

## 【0035】

## (7) コンタクトホール形成工程

次いで、(6)のパッシベーション膜形成工程を経た透明基板11に対し、同じくフォトリソグラフィー法及びエッチング法によって、パッシベーション膜の所定位置にコンタクトホール20を形成し、ドレイン電極Dの一部を露出させる。このコンタクトホール形成工程を経た透明基板11の平面図を、各層の上下関係を無視して透視して表すと図6に示したとおりとなる。

## 【0036】

## (8) 画素電極形成工程

更に、ITOからなる透明導電性層を(7)のコンタクトホール形成工程を経た透明基板11の表面全体に亘って被覆し、同じくフォトリソグラフィー法及びエッチング法によって、図7に示したパターンとなるようにスリット17<sub>1</sub>を有する奇数行の画素電極18<sub>1</sub>及びスリット17<sub>2</sub>を有する偶数行の画素電極18<sub>2</sub>を形成する。この画素電極18<sub>1</sub>及び18<sub>2</sub>はともにコンタクトホール20を介してドレイン電極Dと電気的に接続されている。この画素電極形成工程を経た透明基板11の平面図を、各層の上下関係を無視して

10

20

30

40

50

透視して表すと図 8 に示したとおりとなる。この後、表面全体に所定の配向膜（図示せず）を形成することによりアレイ基板 A R が完成される。なお、画素電極 1 8<sub>1</sub> 及び 1 8<sub>2</sub> に設けるそれぞれのスリット 1 7<sub>1</sub> 及び 1 7<sub>2</sub> の形状等については後述する。

#### 【 0 0 3 7 】

##### [ カラーフィルタ基板製造工程 ]

カラーフィルタ基板は、図示しないガラス基板等からなる透明基板の表面全体に例えれば感光性樹脂からなるブラックマトリクス形成材料の層を設け、フォトリソグラフィー法により図 9 に示すようなパターンのブラックマトリクス 2 1 を形成し、次いで、各画素に対応する位置にそれぞれ例えば R G B の 3 原色のカラーフィルタ層を形成し、次いで、カラーフィルタ層の表面に表面が平らになるようにオーバーコート層を形成する。更に、オーバーコート層の表面に所定の配向膜を形成するとともに所定位置にスペーサを形成することによりカラーフィルタ基板が完成される。

#### 【 0 0 3 8 】

その後、アレイ基板 A R 及びカラーフィルタ基板を対向させ、周囲をシール材でシールして両基板間に液晶を注入することにより実施例に係る F F S モードの液晶表示パネル 1 0 が得られる。なお、この実施例に係る F F S モードの液晶表示パネル 1 0 の画素電極 1 8<sub>1</sub> 及び 1 8<sub>2</sub> とブラックマトリクス 2 1 との配置関係は、ブラックマトリクス 2 1 側から見ると図 1 0 に示したとおりとなる。

#### 【 0 0 3 9 】

以下では、この実施例に係る F F S モードの液晶表示パネル 1 0 の画素電極 1 8<sub>1</sub> 及び 1 8<sub>2</sub> に設けるそれぞれのスリット 1 7<sub>1</sub> 及び 1 7<sub>2</sub> の形状について図 7、図 8 及び図 1 0 を参照しながら説明する。奇数行の画素電極 1 8<sub>1</sub> に設けられた複数のスリット 1 7<sub>1</sub> は、隣り合う走査線 1 2 の間に位置するコモン配線 1 3 が設けられている箇所に該当する走査線 1 2 に平行な軸 x（図 7 及び図 8 参照）に対して左上側及び左下側に傾いた状態に、実質的に軸 x に対して線対称となるように、同一の本数ずつ設けられている。同様に、偶数行の画素電極 1 8<sub>2</sub> に設けられた複数のスリット 1 7<sub>2</sub> は、軸 x に対して右上側及び右下側に傾いた状態に、実質的に軸 x に対して線対称となるように、同一の本数ずつ設けられている。従って、この実施例に係る F F S モードの液晶表示パネル 1 0 における全ての画素の画素電極は、画素電極単位で走査線 1 2 に平行な軸 x に対して対称性を備えているため、走査線 1 2 に直交する方向には表示画質に視角依存性が少なくなる。なお、軸 x の両側に設けられるスリットの本数は、互いに異なっていてもよいが、あえて異なるよう 30 にすることの利点はないので、視角対称性を確保するために同一の本数ずつ設けることが好ましい。

#### 【 0 0 4 0 】

加えて、この実施例に係る F F S モードの液晶表示パネル 1 0 においては、奇数行の画素電極 1 8<sub>1</sub> に設けられた複数のスリット 1 7<sub>1</sub> と偶数行の画素電極 1 8<sub>2</sub> に設けられた複数のスリット 1 7<sub>2</sub> とは走査線 1 2 に垂直な軸に対して互いに反転した構成となっている。このことは、奇数行の画素電極 1 8<sub>1</sub> の製造用マスクを反転（裏返す）させて使用することにより偶数行の画素電極 1 8<sub>2</sub> を製造できることを意味する。従って、この実施例に係る F F S モードの液晶表示パネル 1 0 においては行毎に走査線に垂直な軸に対して対称性を備えているから、走査線 1 2 に沿った方向においても表示画質に視角依存性が少なくなる。このように、実施例に係る F F S モードの液晶表示パネル 1 0 においては、表示開口を有効に利用しながら走査線に垂直な方向及び走査線に沿った方向ともに視角対称性が維持され、従来例のような横方向に班が生じることがなくなるとともに明るい表示の F S モードの液晶表示パネルが得られる。

#### 【 0 0 4 1 】

また、実施例に係る F F S モードの液晶表示パネル 1 0 においては、コモン配線 1 3 は走査線 1 2 と同材質の M o / A 1 の 2 層配線からなるため、遮光性である。そして走査線 1 2 に平行な軸 x に最も近接する両側のスリットの端部は、軸 x 上で、すなわちコモン配線 1 3 の上部で結合されて「く」字状とされている。この走査線 1 2 に平行な軸 x に最も

10

20

30

40

50

近接する両側のスリットは、それぞれ傾斜方向が異なるために軸Xを起点として液晶分子の配向方向が異なる状態となるので、軸Xに沿ってディスクリネーションが発生するが、このディクリネーション発生部分はコモン配線13によって遮光されている。そのため、発生したディスクリネーションは外部から視認し難くなるため、表示画質が向上する。

【図面の簡単な説明】

【0042】

【図1】走査線及びコモン配線形成工程で形成された走査線及びコモン配線のパターンを示す図である。

【図2】対向電極形成工程で形成された対向電極のパターンを示す図である。

10

【図3】半導体層形成工程で形成された半導体層のパターンを示す図である。

【図4】信号線及びドレイン電極形成工程で形成された信号線及びドレイン電極のパターンを示す図である。

【図5】コンタクトホール形成工程で形成されたコンタクトホールのパターンを示す図である。

【図6】図1～図5の全てパターンを上下関係を無視して重ねて表した平面図である。

【図7】画素電極形成工程で形成された画素電極のパターンを示す図である。

【図8】図6及び図7のパターンを上下関係を無視して重ねて表した平面図である。

【図9】カラーフィルタ基板に設けるブラックマトリクスのパターンを示す図である。

【図10】図7のパターンの上に図9のパターンを重ねて表した図である。

20

【図11】IPSモードの液晶表示パネルの1画素分の概略平面図である。

【図12】図10のXII-XII線に沿った概略断面図である。

【図13】FFSモードの液晶表示パネルの1画素分の概略平面図である。

【図14】図13のXIII-XIII線に沿った概略断面図である。

【図15】スリットを傾けて設けたFFSモードの液晶表示パネルの1画素分の平面図である。

【図16】デュアルドメイン化したFFSモードの液晶表示パネルの1画素分の平面図である。

【図17】画素をデルタ配置としたFFSモードの液晶表示パネル70Dの数画素分の概略平面図である。

【符号の説明】

30

【0043】

10 FFSモードの液晶表示パネル

11 透明基板

12 走査線

13 コモン配線

14 信号線

15 対向電極

17<sub>1</sub>、17<sub>2</sub> スリット

18<sub>1</sub>、18<sub>2</sub> 画素電極

19 半導体層

20 コンタクトホール

40

21 ブラックマトリクス

x 走査線に平行な軸

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図17】

70D

---

フロントページの続き

【要約の続き】

とを特徴とする。

【選択図】図 8

|                |                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | <无法获取翻译>                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2007264231A5</a>                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2008-05-15 |

| 申请号            | JP2006088208                                                                                                                                                                                                                                                                                             | 申请日     | 2006-03-28 |

| [标]申请(专利权)人(译) | 爱普生映像元器件有限公司                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 爱普生影像设备公司                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | 金子英樹<br>堀口正寛                                                                                                                                                                                                                                                                                             |         |            |

| 发明人            | 金子 英樹<br>堀口 正寛                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | G02F1/134363 G02F1/133707 G02F2001/134372 G02F2201/128 G02F2201/40                                                                                                                                                                                                                                       |         |            |

| FI分类号          | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 2H092/GA13 2H092/GA14 2H092/GA22 2H092/JA26 2H092/JB03 2H092/JB05 2H092/JB11 2H092/JB32 2H092/NA01 2H092/NA07 2H092/QA06 2H192/AA24 2H192/AA43 2H192/BB13 2H192/BB53 2H192/BB66 2H192/BB86 2H192/BC02 2H192/BC31 2H192/CB05 2H192/CC04 2H192/CC32 2H192/CC55 2H192/CC72 2H192/EA22 2H192/EA43 2H192/JA33 |         |            |

| 代理人(译)         | 须泽 修                                                                                                                                                                                                                                                                                                     |         |            |

| 其他公开文献         | JP4238877B2<br>JP2007264231A                                                                                                                                                                                                                                                                             |         |            |

### 摘要(译)

解决的问题：为了具有对称的视角，不会产生任何侧向斑点，宽视角和高透射率。提供一种FFS模式的液晶显示面板，其能够进行明亮的显示并且具有良好的显示质量。根据本发明，提供了平行设置的多条扫描线和公共配线。在与扫描线12和多条行进线正交的方向上以曲柄状设置的多条信号线14。分别在检查线12和信号线14之间形成的像素电极181和像素电极182。注意：在FFS模式液晶显示面板中，其中多个像素电极181和182呈三角形排列。多个像素电极181和182中的每一个位于相邻的扫描线12之间。多个狭缝17相对于与扫描线12平行的轴x在相互不同的方向上倾斜。1，172，像素电极是奇数行像素电极181和偶数行像素电极182具有其中它们相对于轴线x相互颠倒的结构。[选择图]图8