(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-94415

(P2007-94415A)

(43) 公開日 平成19年4月12日(2007.4.12)

(51) Int.C1.

F 1

テーマコード(参考)

**G09G** 3/36 (2006.01)

**G09G** 3/20 (2006.01)

**G02F** 1/133 (2006.01)

**G11C** 19/28 (2006.01)

G09G 3/36

G09G 3/20 622E

G09G 3/20 622C

G09G 3/20 622D

G09G 3/20 621M

2H093

5C006

5C080

審査請求 未請求 請求項の数 24 O L (全 17 頁) 最終頁に続く

(21) 出願番号

特願2006-262269 (P2006-262269)

(22) 出願日

平成18年9月27日 (2006.9.27)

(31) 優先権主張番号

10-2005-0089827

(32) 優先日

平成17年9月27日 (2005.9.27)

(33) 優先権主張国

韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区梅灘洞416

(74) 代理人 110000051

特許業務法人共生国際特許事務所

(72) 発明者 李洪雨

大韓民国忠清南道天安市斗井洞1

169番地 306号

(72) 発明者 李癸憲

大韓民国京畿道水原市八達区靈通

洞 ファンゴルマウル2団地アパート2

22棟 1906号

最終頁に続く

(54) 【発明の名称】シフトレジスタ及びこれを有する表示装置

## (57) 【要約】

【課題】表示板に必要なデータ線の数を減らすことができ、それによりデータ駆動部の数を減らすことができ、液晶表示装置に設置される駆動部に消費される製造費用を低減できるシフトレジスタ及びこれを有する表示装置を提供する。

【解決手段】基板と、基板上に形成される複数のゲート線と、ゲート線と交差する複数のデータ線と、ゲート線及びデータ線と連結される複数の薄膜トランジスタと、薄膜トランジスタと連結され行列状に配列されて、ゲート線に平行な第1辺、及び第1辺より長さが短く第1辺と隣接する第2辺を有する複数の画素電極と、ゲート線と連結されるゲート駆動部とを有し、ゲート駆動部は互いに連結されて順次に出力信号を生成する複数のステージを含み、各ステージは少なくとも二つのゲート線と各々連結されて薄膜トランジスタを導通させる第1出力電圧を少なくとも二つのゲート線に交互に出力する複数の出力端を有する。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

互いに連結されて順次に出力信号を生成する複数のステージを有し、前記各ステージは、交互に第1出力電圧を出力する第1及び第2出力端を有することを特徴とするシフトレジスタ。

**【請求項 2】**

前記各ステージは、出力開始信号または前段ステージのうちの何れか一つの出力信号に応答して前記第1出力電圧と第2出力電圧を生成する出力電圧生成部を含み、

前記第1出力電圧は第2出力電圧と大きさが異なることを特徴とする請求項1に記載のシフトレジスタ。10

**【請求項 3】**

前記各ステージは、前記第1出力電圧と前記第2出力電圧をスイッチングして前記第1出力端と前記第2出力端に交互に変えて出力する出力スイッチング部をさらに含むことを特徴とする請求項2に記載のシフトレジスタ。

**【請求項 4】**

前記出力スイッチング部は、第1スイッチング信号によって前記電圧生成部の出力をスイッチングする第1トランジスタと、

第2スイッチング信号によって前記電圧生成部の出力をスイッチングする第2トランジスタとを有することを特徴とする請求項3に記載のシフトレジスタ。

**【請求項 5】**

前記第1スイッチング信号と前記第2スイッチング信号の位相は互いに反対であることを特徴とする請求項4に記載のシフトレジスタ。20

**【請求項 6】**

前記出力スイッチング部は、前記第2スイッチング信号によって前記第2出力電圧を前記第1出力端に出力または遮断する第3トランジスタと、

前記第1スイッチング信号によって前記第2出力電圧を前記第2出力端に出力または遮断する第4トランジスタとをさらに有することを特徴とする請求項5に記載のシフトレジスタ。

**【請求項 7】**

前記第1及び第2スイッチング信号は1H(1水平周期)を周期として反転することを特徴とする請求項4に記載のシフトレジスタ。30

**【請求項 8】**

基板と、

前記基板上に形成される複数のゲート線と、

前記ゲート線と交差する複数のデータ線と、

前記ゲート線及び前記データ線と連結される複数の薄膜トランジスタと、

前記薄膜トランジスタと連結され行列状に配列されて、前記ゲート線に平行な第1辺、及び前記第1辺より長さが短く前記第1辺と隣接する第2辺を有する複数の画素電極と、

前記ゲート線と連結されるゲート駆動部とを有し、

前記ゲート駆動部は互いに連結されて順次に出力信号を生成する複数のステージを含み40

、前記各ステージは少なくとも二つのゲート線と各々連結されて前記薄膜トランジスタを導通させる第1出力電圧を前記少なくとも二つのゲート線に交互に出力する複数の出力端を有することを特徴とする表示装置。

**【請求項 9】**

前記各ステージは、出力開始信号または前段ステージのうちの何れか一つの出力信号に応答して前記第1出力電圧と第2出力電圧を生成する出力電圧生成部を含み、

前記第1出力電圧は第2出力電圧と大きさが異なることを特徴とする請求項8に記載の表示装置。

**【請求項 10】**

10

20

40

50

前記各ステージは、前記第1出力電圧と前記第2出力電圧をスイッチングして前記複数の出力端である第1出力端と第2出力端に交互に変えて出力する出力スイッチング部をさらに含むことを特徴とする請求項9に記載の表示装置。

【請求項11】

前記出力スイッチング部は、第1スイッチング信号によって前記出力電圧生成部の出力をスイッチングする第1トランジスタと、

第2スイッチング信号によって前記出力電圧生成部の出力をスイッチングする第2トランジスタとを有することを特徴とする請求項10に記載の表示装置。

【請求項12】

前記第1スイッチング信号と前記第2スイッチング信号の位相は互いに反対であることを特徴とする請求項11に記載の表示装置。

【請求項13】

前記出力スイッチング部は、前記第2スイッチング信号によって前記第2出力電圧を前記第1出力端に出力または遮断する第3トランジスタと、

前記第1スイッチング信号によって前記第2出力電圧を前記第2出力端に出力または遮断する第4トランジスタとをさらに有することを特徴とする請求項12に記載の表示装置。

【請求項14】

前記第1及び第2スイッチング信号は1Hを周期として反転することを特徴とする請求項11に記載の表示装置。

【請求項15】

列方向に隣接した画素電極は互いに異なるデータ線と連結されることを特徴とする請求項8乃至14の何れか一項に記載の表示装置。

【請求項16】

前記ゲート駆動部は互いに異なるゲート線に連結される第1及び第2シフトレジスタを有し、

前記第1及び第2シフトレジスタ各々は前記ステージを有することを特徴とする請求項15に記載の表示装置。

【請求項17】

基板と、

前記基板上に形成される複数のゲート線と、

前記ゲート線と交差する複数のデータ線と、

前記ゲート線及び前記データ線と連結される複数の薄膜トランジスタと、

前記薄膜トランジスタと連結され行列状に配列されて、前記ゲート線に平行な第1辺、及び前記第1辺より長さが短く前記第1辺と隣接する第2辺を有する複数の画素電極と、

前記基板の左右端部に配置されて、前記ゲート線と連結されるゲート駆動部とを有し、前記ゲート駆動部は互いに連結されて順次に出力信号を生成する複数のステージを含み、

前記各ステージは少なくとも二つのゲート線と各々連結されて前記薄膜トランジスタを導通させる第1出力電圧を前記少なくとも二つのゲート線に交互に出力する複数の出力端を有することを特徴とする表示装置。

【請求項18】

前記各ステージは、出力開始信号または前段ステージのうちの何れか一つの出力信号に応答して前記第1出力電圧と第2出力電圧を生成する出力電圧生成部を含み、

前記第1出力電圧は第2出力電圧と大きさが異なることを特徴とする請求項17に記載の表示装置。

【請求項19】

前記各ステージは、前記第1出力電圧と前記第2出力電圧をスイッチングして前記複数の出力端である第1出力端と第2出力端に交互に変えて出力する出力スイッチング部をさらに含むことを特徴とする請求項18に記載の表示装置。

10

20

30

40

50

**【請求項 2 0】**

前記出力スイッチング部は、第1スイッチング信号によって前記出力電圧生成部の出力をスイッチングする第1トランジスタと、

第2スイッチング信号によって前記出力電圧生成部の出力をスイッチングする第2トランジスタとを有することを特徴とする請求項19に記載の表示装置。

**【請求項 2 1】**

前記第1スイッチング信号と前記第2スイッチング信号の位相は互いに反対であることを特徴とする請求項20に記載の表示装置。

**【請求項 2 2】**

前記出力スイッチング部は、前記第2スイッチング信号によって前記第2出力電圧を前記第1出力端に出力または遮断する第3トランジスタと、

前記第1スイッチング信号によって前記第2出力電圧を前記第2出力端に出力または遮断する第4トランジスタとをさらに有することを特徴とする請求項21に記載の表示装置。

**【請求項 2 3】**

前記第1及び第2スイッチング信号は1Hを周期として反転することを特徴とする請求項22に記載の表示装置。

**【請求項 2 4】**

列方向に隣接した画素電極は互いに異なるデータ線と連結されることを特徴とする請求項17乃至23の何れか一項に記載の表示装置。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明はシフトレジスタ及びこれを有する表示装置に関し、特に表示板に必要なデータ線の数を減らすことができ、それによりデータ駆動部の数を減らすことのできるシフトレジスタ及びこれを有する表示装置に関する。

**【背景技術】****【0002】**

液晶表示装置は、現在最も広く使用されている平板表示装置のうちの一つであって、画素電極と共に通電極など電場を生成する電極が形成されている二枚の表示板とその間に入っている液晶層を含む。液晶表示装置は、電場生成電極に電圧を印加して液晶層に電場を生成し、これを通して液晶層の液晶分子の配向を決定して入射光の偏光を制御することによって画像を表示する。

液晶表示装置をはじめとする表示装置は、また、各画素電極に連結されているスイッチング素子及びスイッチング素子を制御して画素電極に電圧を印加するためのゲート線とデータ線などの複数の信号線を含む。

**【0003】**

このような信号線は、別途に備えられた駆動装置から信号の印加を受けて、スイッチング素子を通して当該画素に当該信号を印加する。従って、表示装置を駆動するためには駆動装置を表示装置に連結したり、表示装置に装着しなければならない。しかし、表示装置を製造において、このような駆動装置は費用が高くなるという問題がある。

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

そこで、本発明は上記従来の表示装置における問題点に鑑みてなされたものであって、本発明の目的は、表示板に必要なデータ線の数を減らすことができ、それによりデータ駆動部の数を減らすことができ、液晶表示装置に設置される駆動部に消費される製造費用を低減できるシフトレジスタ及びこれを有する表示装置を提供する。

**【課題を解決するための手段】**

## 【0005】

上記目的を達成するためになされた本発明によるシフトレジスタは、互いに連結されていて順次に出力信号を生成する複数のステージを有し、前記各ステージは交互に第1出力電圧を出力する第1及び第2出力端を有することを特徴とする。

## 【0006】

前記各ステージは、出力開始信号または前段ステージのうちの何れか一つの出力信号に応答して前記第1出力電圧と第2出力電圧を生成する出力電圧生成部を含み、前記第1出力電圧は第2出力電圧と大きさが異なることが好ましい。

前記各ステージは、前記第1出力電圧と前記第2出力電圧をスイッチングして前記第1出力端と前記第2出力端に交互に変えて出力する出力スイッチング部をさらに含むことが好ましい。 10

前記出力スイッチング部は、第1スイッチング信号によって前記電圧生成部の出力をスイッチングする第1トランジスタと、第2スイッチング信号によって前記電圧生成部の出力をスイッチングする第2トランジスタとを有することが好ましい。

前記第1スイッチング信号と前記第2スイッチング信号の位相は互いに反対であることが好ましい。

前記出力スイッチング部は、前記第2スイッチング信号によって前記第2出力電圧を前記第1出力端に出力または遮断する第3トランジスタと、前記第1スイッチング信号によって前記第2出力電圧を前記第2出力端に出力または遮断する第4トランジスタとをさらに有することが好ましい。 20

前記第1及び第2スイッチング信号は1H(1水平周期)を周期として反転することが好ましい。

## 【0007】

上記目的を達成するためになされた本発明による表示装置は、基板と、前記基板上に形成される複数のゲート線と、前記ゲート線と交差する複数のデータ線と、前記ゲート線及び前記データ線と連結される複数の薄膜トランジスタと、前記薄膜トランジスタと連結され行列状に配列されて、前記ゲート線に平行な第1辺、及び前記第1辺より長さが短く前記第1辺と隣接する第2辺を有する複数の画素電極と、前記ゲート線と連結されるゲート駆動部とを有し、前記ゲート駆動部は互いに連結されて順次に出力信号を生成する複数のステージを含み、前記各ステージは少なくとも二つのゲート線と各々連結されて前記薄膜トランジスタを導通させる第1出力電圧を前記少なくとも二つのゲート線に交互に出力する複数の出力端を有することを特徴とする。 30

## 【0008】

前記各ステージは、出力開始信号または前段ステージのうちの何れか一つの出力信号に応答して前記第1出力電圧と第2出力電圧を生成する出力電圧生成部を含み、前記第1出力電圧は第2出力電圧と大きさが異なることが好ましい。

前記各ステージは、前記第1出力電圧と前記第2出力電圧をスイッチングして前記複数の出力端である第1出力端と第2出力端に交互に変えて出力する出力スイッチング部をさらに含むことが好ましい。

前記出力スイッチング部は、第1スイッチング信号によって前記出力電圧生成部の出力をスイッチングする第1トランジスタと、第2スイッチング信号によって前記出力電圧生成部の出力をスイッチングする第2トランジスタとを有することが好ましい。 40

前記第1スイッチング信号と前記第2スイッチング信号の位相は互いに反対であることが好ましい。

前記出力スイッチング部は、前記第2スイッチング信号によって前記第2出力電圧を前記第1出力端に出力または遮断する第3トランジスタと、前記第1スイッチング信号によって前記第2出力電圧を前記第2出力端に出力または遮断する第4トランジスタとをさらに有するが好ましい。

前記第1及び第2スイッチング信号は1Hを周期として反転することが好ましい。

列方向に隣接した画素電極は互いに異なるデータ線と連結されることが好ましい。 50

前記ゲート駆動部は互いに異なるゲート線に連結される第1及び第2シフトレジスタを有し、前記第1及び第2シフトレジスタ各々は前記ステージを有することが好ましい。

【0009】

上記目的を達成するためになされた本発明による表示装置は、基板と、前記基板上に形成される複数のゲート線と、前記ゲート線と交差する複数のデータ線と、前記ゲート線及び前記データ線と連結される複数の薄膜トランジスタと、前記薄膜トランジスタと連結され行列状に配列されて、前記ゲート線に平行な第1辺、及び前記第1辺より長さが短く前記第1辺と隣接する第2辺を有する複数の画素電極と、前記基板の左右端部に配置されて、前記ゲート線と連結されるゲート駆動部とを有し、前記ゲート駆動部は互いに連結されて順次に出力信号を生成する複数のステージを含み、前記各ステージは少なくとも二つのゲート線と各々連結されて前記薄膜トランジスタを導通させる第1出力電圧を前記少なくとも二つのゲート線に交互に出力する複数の出力端を有することを特徴とする。

【0010】

前記各ステージは、出力開始信号または前段ステージのうちの何れか一つの出力信号に応答して前記第1出力電圧と第2出力電圧を生成する出力電圧生成部を含み、前記第1出力電圧は第2出力電圧と大きさが異なることが好ましい。

前記各ステージは、前記第1出力電圧と前記第2出力電圧をスイッチングして前記複数の出力端である第1出力端と第2出力端に交互に変えて出力する出力スイッチング部をさらに含むことが好ましい。

前記出力スイッチング部は、第1スイッチング信号によって前記出力電圧生成部の出力をスイッチングする第1トランジスタと、第2スイッチング信号によって前記出力電圧生成部の出力をスイッチングする第2トランジスタとを有することが好ましい。

前記第1スイッチング信号と前記第2スイッチング信号の位相は互いに反対であることが好ましい。

前記出力スイッチング部は、前記第2スイッチング信号によって前記第2出力電圧を前記第1出力端に出力または遮断する第3トランジスタと、前記第1スイッチング信号によって前記第2出力電圧を前記第2出力端に出力または遮断する第4トランジスタとをさらに有することが好ましい。

前記第1及び第2スイッチング信号は1Hを周期として反転することが好ましい。

列方向に隣接した画素電極は互いに異なるデータ線と連結されることが好ましい。

【発明の効果】

【0011】

本発明に係るシフトレジスタ及びこれを有する表示装置によれば、表示板に必要なデータ線の数を減らすことができ、それによりデータ駆動部の数を減らすことができるため、製造費用を低減できるという効果がある。

【発明を実施するための最良の形態】

【0012】

次に、本発明に係るシフトレジスタ及びこれを有する表示装置を実施するための最良の形態の具体例を図面を参照しながら説明する。

【0013】

図面では多様な層及び領域を明確に示すために厚さを拡大して示した。明細書全体にわたって類似する部分については同一図面符号を付けた。層、膜、領域、板などの部分が他の部分の“上”にあるとする時、これは他の部分の“直上”にある場合だけでなく、その中間に他の部分がある場合も含む。それとは異なってある部分が他の部分の“直上”にあるとする時には中間に他の部分がないことを意味する。

【0014】

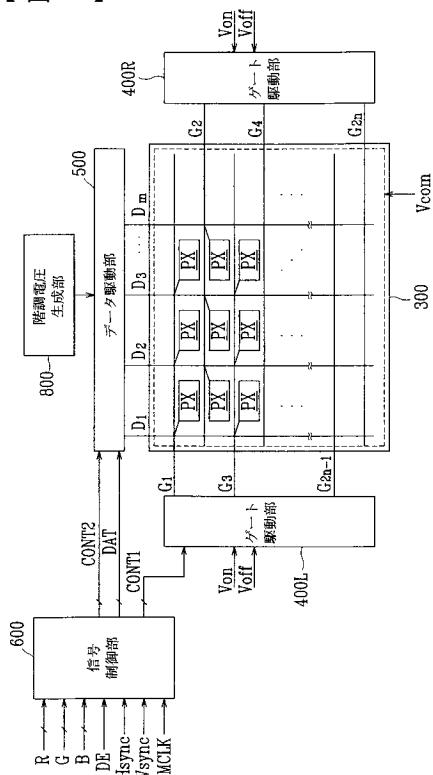

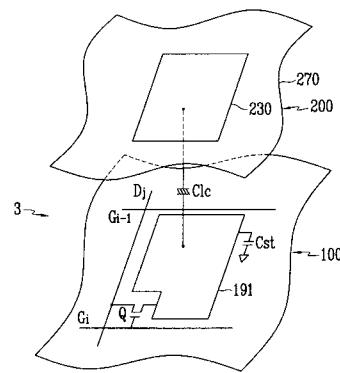

図1及び図2を参照して本発明の一実施形態による液晶表示装置について表示装置の一例として説明する。

図1は、本発明の一実施形態による液晶表示装置のブロック図であり、図2は本発明の一実施形態による液晶表示装置の一つの画素に対する等価回路図である。

10

20

30

40

50

## 【0015】

図1及び図2を参照すると、本発明の一実施形態による液晶表示装置は、液晶表示板組立体300、ゲート駆動部400L、400R、データ駆動部500、階調電圧生成部800、そして信号制御部600を含む。

液晶表示板組立体300は、等価回路で見ると、複数の表示信号線とこれに連結されて行列状に配列された複数の画素(PX)を含む。一方、図2に示した構造で見ると、液晶表示板組立体300は互いに対向する下部及び上部表示板100、200と両者の間に介在する液晶層3を含む。

## 【0016】

信号線( $G_1 - G_{2n}$ 、 $D_1 - D_m$ )は、ゲート信号(“走査信号”とも言う)を伝達する複数のゲート線( $G_1 - G_{2n}$ )とデータ信号を伝達する複数のデータ線( $D_1 - D_m$ )を含む。ゲート線( $G_1 - G_{2n}$ )は略行方向に延びて互いにほとんど平行し、データ線( $D_1 - D_m$ )は略列方向に延びて互いにほとんど平行する。

各画素(PX)、例えば、i番目( $i = 1, 2, \dots, 2n$ )のゲート線( $G_i$ )とj番目( $j = 1, 2, \dots, m$ )のデータ線( $D_j$ )に連結された画素(PX)は、信号線( $G_i$ 、 $D_j$ )に連結されたスイッチング素子(Q)とこれに連結された液晶キャパシタ( $C_{1c}$ )及びストレージキャパシタ( $C_{st}$ )を含む。図1を参照すると、同列で隣接した二つの画素(PX)は、互いに異なるデータ線( $D_1 - D_m$ )と連結されている。

## 【0017】

スイッチング素子(Q)は、下部表示板100に備えられている薄膜トランジスタなどの三端子素子であって、その制御端子はゲート線( $G_i$ )と連結されており、入力端子はデータ線( $D_j$ )と連結されており、出力端子は液晶キャパシタ( $C_{1c}$ )及びストレージキャパシタ( $C_{st}$ )と連結されている。

液晶キャパシタ( $C_{1c}$ )は、下部表示板100の画素電極191と上部表示板200の共通電極270を二つの端子として二つの電極(191、270)の間の液晶層3は誘電体として機能する。

## 【0018】

画素電極191はスイッチング素子(Q)と連結され、図1に示した画素(PX)のように、画素電極191の行方向長さは列方向長さより長い。

例えば、画素電極191の行方向長さが列方向長さの約3倍でありうる。

## 【0019】

共通電極270は上部表示板200の前面に形成されて共通電圧( $V_{com}$ )を印加される。図2とは異なって、共通電極270が下部表示板100に備えられる場合もあり、この時には二つの電極(191、270)のうち、少なくとも一つが線状または棒状で形成できる。

## 【0020】

液晶キャパシタ( $C_{1c}$ )の補助的な役割を果たすストレージキャパシタ( $C_{st}$ )は、下部表示板100に備えられた別の信号線(図示せず)と画素電極191とが絶縁体を間に置いて重なって構成され、この別の信号線には共通電圧( $V_{com}$ )などの決められた電圧が印加される。しかし、ストレージキャパシタ( $C_{st}$ )は、画素電極191が絶縁体を媒介として真上の前段ゲート線( $G_{i-1}$ )と重なって形成することもできる。ストレージキャパシタ( $C_{st}$ )は必要により省略できる。

## 【0021】

一方、色表示を実現するためには、各画素(PX)が基本色のうち一つを固有するように表示したり(空間分割)、各画素(PX)が時間によって交互に基本色を表示するように(時間分割)して、これら基本色の空間的、時間的合計として希望の色相が認識されるようにする。基本色の例としては、赤色、緑色、青色など三原色がある。

## 【0022】

図2は空間分割の一例で、各画素(PX)が画素電極191に対応する上部表示板200の領域に基本色のうち一つを示す色フィルタ230を備えることを示している。図2と

10

20

30

40

50

は異なって、色フィルタ 230 は下部表示板 100 の画素電極 191 の上、または下に形成することもできる。

図 1 を参照すると、色フィルタ 230 は画素電極 191 と同様に行方向に延びることができる。一つの画素行の色フィルタ 230 は同一基本色を示すことができて、互いに連結されて帯形態を有することができる。列方向には、互いに異なる基本色を示す色フィルタ 230 が交互に配列されている。この場合、列方向に隣接した三つの画素 (P X) が画像の基本単位のドットを構成できる。

#### 【 0 0 2 3 】

液晶表示板組立体 300 には、少なくとも一つの偏光子 (図示せず) が備えられている。

10

#### 【 0 0 2 4 】

再び図 1 を参照すると、階調電圧生成部 800 は画素 (P X) の透過率と関する二対の階調電圧集合 (または基準階調電圧集合) を生成する。二対のうちの一対は共通電圧 (V com) に対して正の値を有して他の一対は負の値を有する。

ゲート駆動部 400L、400R は、液晶表示板組立体 300 の左側周縁と右側周縁に配置されている。左側ゲート駆動部 400L は奇数番目のゲート線 (G<sub>1</sub>、G<sub>3</sub>、…、G<sub>2n-1</sub>) と連結されており、右側ゲート駆動部 400R は偶数番目のゲート線 (G<sub>2</sub>、G<sub>4</sub>、…、G<sub>2n</sub>) と連結されている。

#### 【 0 0 2 5 】

ゲート駆動部 400L、400R はゲートオン電圧 (V<sub>on</sub>) とゲートオフ電圧 (V<sub>off</sub>) の組み合わせで構成されたゲート信号をゲート線 (G<sub>1</sub> - G<sub>2n</sub>) に印加する。ゲート駆動部 400L、400R は、スイッチング素子 (Q) 及び信号線 (G<sub>1</sub> - G<sub>2n</sub>、D<sub>1</sub> - D<sub>m</sub>) などと共に液晶表示板組立体 300 に集積できる。しかし、ゲート駆動部 400L、400R は、少なくとも一つの集積回路チップの形態に液晶表示板組立体 300 上に直接装着されたり、可撓性印刷回路フィルム (図示せず) 上に装着されて T C P の形態に液晶表示板組立体 300 に付着できる。

20

#### 【 0 0 2 6 】

データ駆動部 500 は、液晶表示板組立体 300 のデータ線 (D<sub>1</sub> - D<sub>m</sub>) に連結されており、階調電圧生成部 800 からの階調電圧を選択してこれをデータ信号としてデータ線 (D<sub>1</sub> - D<sub>m</sub>) に印加する。しかし、階調電圧生成部 800 が全ての階調に対する電圧を全て提供するのではなく、限定された数の基準階調電圧のみを提供する場合には、データ駆動部 500 は基準階調電圧を分圧してデータ信号を生成する。データ駆動部 500 は、複数の集積回路チップの形態に液晶表示板組立体 300 上に直接装着されたり、可撓性印刷回路フィルム (図示せず) 上に装着されて、T C P の形態に液晶表示板組立体 300 に付着できる。

30

#### 【 0 0 2 7 】

信号制御部 600 は、ゲート駆動部 400L、400R 及びデータ駆動部 500 などを制御する。

#### 【 0 0 2 8 】

このように画素 (P X) の長辺が横になるように並べると、画素 (P X) の長辺が縦に伸びるように並べる場合に比べて、データ線 (D<sub>1</sub> - D<sub>m</sub>) の数が減るため、データ駆動集積回路チップの数を減らすことができる。反面ゲート線 (G<sub>1</sub> - G<sub>2n</sub>) の数が増えてもゲート駆動部 400L、400R は表示板組立体 300 内に集積できるため、製品の値段が安くなる。また、ゲート駆動部 400L、400R をチップに形成してもその値段がデータ駆動回路チップより安いので有利である。

40

#### 【 0 0 2 9 】

このような液晶表示装置の動作について詳細に説明する。

信号制御部 600 は、外部のグラフィック制御器 (図示せず) から入力画像信号 (R、G、B) 及びその表示を制御する入力制御信号を受信する。入力画像信号 (R、G、B) は、各画素 (P X) の輝度情報を含み、輝度は決められた数、例えば、1024 (= 2<sup>10</sup>)

50

<sup>0</sup> ) 、 256 ( = 2<sup>8</sup> ) または 64 ( = 2<sup>6</sup> ) 個の階調を有している。入力制御信号の例としては、垂直同期信号 ( V sync ) と水平同期信号 ( H sync ) 、メインクロック信号 ( MCLK ) 、データイネーブル信号 ( DE ) などがある。

### 【 0030 】

信号制御部 600 は、入力画像信号 ( R 、 G 、 B ) と入力制御信号に基づいて入力画像信号 ( R 、 G 、 B ) を液晶表示板組立体 300 の動作条件に合うように適切に処理してゲート制御信号 ( CONT1 ) 及びデータ制御信号 ( CONT2 ) などを生成した後、ゲート制御信号 ( CONT1 ) をゲート駆動部 400L 、 400R に出力してデータ制御信号 ( CONT2 ) と処理したデジタル画像信号 ( DAT ) をデータ駆動部 500 に出力する。信号制御部 600 のこのような画像信号処理には、図 1 に示した画素の配置によって入力画像信号 ( R 、 G 、 B ) を再配列する動作が含まれる。

### 【 0031 】

ゲート制御信号 ( CONT1 ) は、走査開始を指示する一対の走査開始信号 ( LSTV 、 RSTV ) とゲートオン電圧 ( Von ) の出力周期を制御する二対の ( 第 1 乃至第 4 ) クロック信号及びゲートオン電圧の出力を制御する一対の出力スイッチング信号を含む。ゲート制御信号 ( CONT1 ) は、また、ゲートオン電圧 ( Von ) の持続時間を限定する出力イネーブル信号 ( OE ) をさらに含むことができる。

### 【 0032 】

データ制御信号 ( CONT2 ) は、一行の画素に対するデジタル画像信号 ( DAT ) の伝送開始を知らせる水平同期開始信号 ( STH ) と、データ線 ( D<sub>1</sub> - D<sub>m</sub> ) にアナログデータ信号を印加することを指示するロード信号 ( LOAD ) 及びデータクロック信号 ( HCLK ) を含む。データ制御信号 ( CONT2 ) は、また、共通電圧 ( Vcom ) に対するアナログデータ信号の電圧極性 ( 以下、 “ 共通電圧に対するデータ信号の電圧極性 ” を略して “ データ信号の極性 ” という ) を反転させる反転信号 ( RVS ) をさらに含むことができる。

信号制御部 600 からのデータ制御信号 ( CONT2 ) によって、データ駆動部 500 は一行の画素に対するデジタル画像信号 ( DAT ) を受信して、各デジタル画像信号 ( DAT ) に対応する階調電圧を選択することによって、デジタル画像信号 ( DAT ) をアナログデータ信号に変換した後、これを該当データ線 ( D<sub>1</sub> - D<sub>m</sub> ) に印加する。

### 【 0033 】

ゲート駆動部 400L 、 400R は、信号制御部 600 からのゲート制御信号 ( CONT1 ) によってゲートオン電圧 ( Von ) をゲート線 ( G<sub>1</sub> - G<sub>2n</sub> ) に印加して、このゲート線 ( G<sub>1</sub> - G<sub>2n</sub> ) に連結されたスイッチング素子 ( Q ) を導通させる。以下、データ線 ( D<sub>1</sub> - D<sub>m</sub> ) に印加されたデータ信号が導通したスイッチング素子 ( Q ) を通して該当画素 ( PX ) に印加される。

### 【 0034 】

画素 ( PX ) に印加されたデータ信号の電圧と共通電圧 ( Vcom ) の差は、液晶キャパシタ ( C<sub>1c</sub> ) の充電電圧、つまり、画素電圧として現れる。液晶分子は、画素電圧の大きさによってその配列を異なるようにし、そのために液晶層 3 を通過する光の偏光が変化する。このような偏光の変化は、表示板組立体 300 に付着された偏光子によって光の透過率変化として現れ、これによって画素 ( PX ) はデジタル画像信号 ( DAT ) の階調が示す輝度を表示する。

### 【 0035 】

1 水平周期 [ “ 1H ” ともいい、水平同期信号 H sync 及びデータイネーブル信号 ( DE ) の一周期と同じである ] を単位としてこのような過程を繰り返すことによって、全てのゲート線 ( G<sub>1</sub> - G<sub>2n</sub> ) に対して順次ゲートオン電圧 ( Von ) を印加して全ての画素 ( PX ) にデータ信号を印加して 1 フレームの画像を表示する。

一つのフレームが終わると、次のフレームが始まって各画素 ( PX ) に印加されるデータ信号の極性が直前のフレームでの極性と反対になるように、データ駆動部 500 に印加される反転信号 ( RVS ) の状態が制御される ( “ フレーム反転 ” ) 。この時、一つのフレ

10

20

30

40

50

ーム内でも反転信号（RVS）の特性によって一つのデータ線を通して流れるデータ信号の極性が変わったり（例：行反転、点反転）、一つの画素行に印加されるデータ信号の極性も互いに異なりうる（例：列反転、点反転）。

#### 【0036】

上述したように、各画素列において隣接した二つの画素（PX）は、互いに反対側のデータ線と連結されている。データ駆動部500が列反転を行うと、行方向と列方向に隣接した二つの画素（PX）の画素電圧の極性が反対となる。つまり、液晶表示板組立体300に現れる外形反転の形は点反転となる。

#### 【0037】

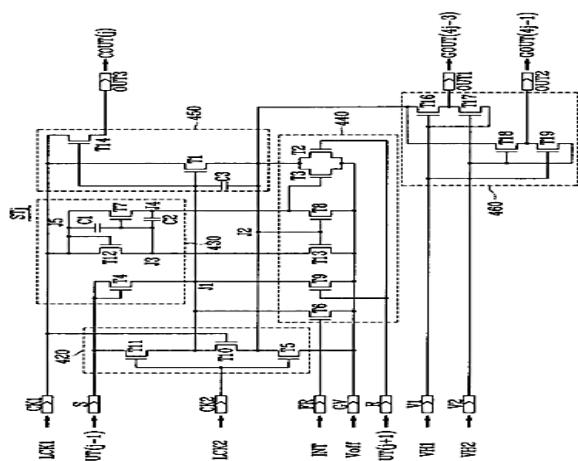

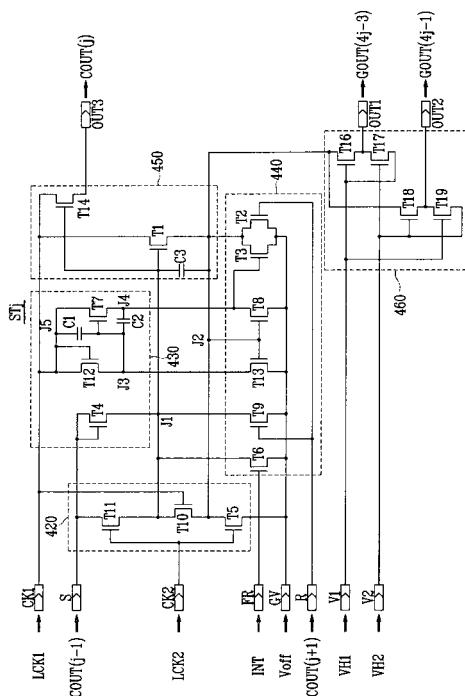

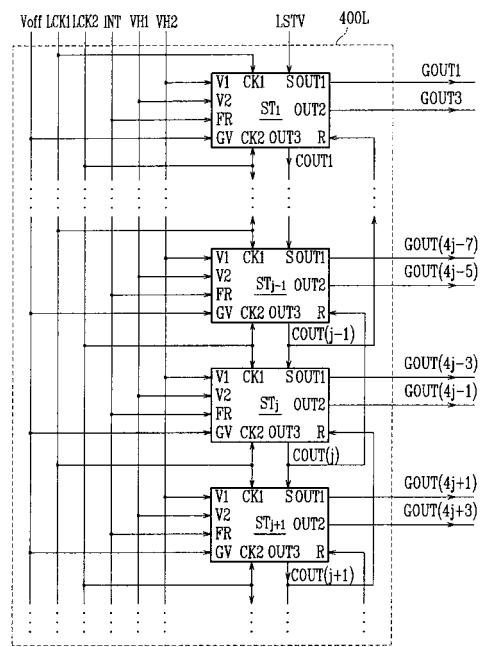

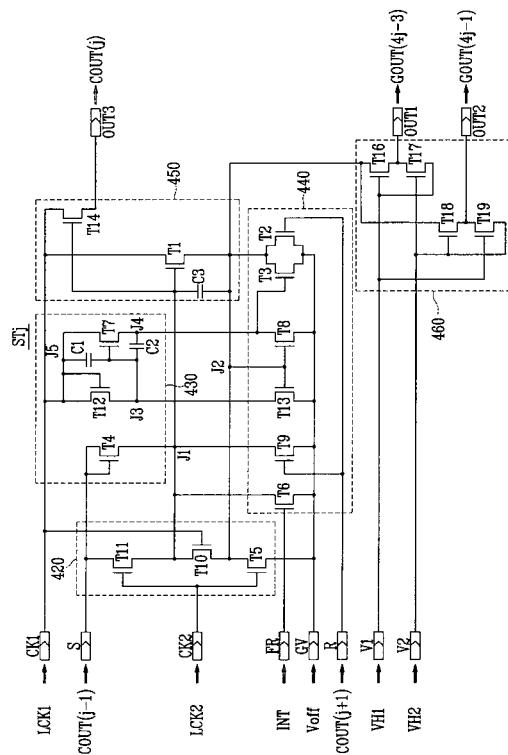

本発明の一実施形態によるゲート駆動部について、図3及び図4を参照してより詳細に説明する。

図3は図1に示したゲート駆動部を示したプロック図の一例であり、図4は図3に示したゲート駆動部の一つのステージの回路図の一例である。

#### 【0038】

図3及び図4を参照すると、各ゲート駆動部400L、400R、例えば、左側ゲート駆動部400Lは、互いに従属的に連結されて順次ゲート信号を出力する複数のステージ（ST<sub>1</sub>、ST<sub>2</sub>、…）を含み、ゲートオフ電圧（V<sub>off</sub>）、第1及び第2クロック信号（LCK1、LCK2）、第1及び第2スイッチング信号（VH1、VH2）、そして初期化信号（INT）が入力される。全てのステージ（ST<sub>1</sub>、ST<sub>2</sub>、…）はゲート線と一対一に連結されているが、最後のゲート線との連結されないダミーステージが付加されることもありうる。

#### 【0039】

各ステージ（ST<sub>1</sub>、ST<sub>2</sub>、…）は、第1クロック端子（CK1）、第2クロック端子（CK2）、セット端子（S）、リセット端子（R）、ゲート電圧端子（GV）、フレームリセット端子（FR）、第1スイッチング端子（V1）、第2スイッチング端子（V2）、そして第1及び第2ゲート出力端子（OUT1、OUT2）とキャリー出力端子（OUT3）を有している。

#### 【0040】

各ステージ、例えば、j番目のステージ（ST<sub>j</sub>）のセット端子（S）には、前段ステージ（ST<sub>j-1</sub>）のキャリー出力、つまり、前段キャリー出力「COUT（j-1）」が、リセット端子（R）には後段ステージ（ST<sub>j+1</sub>）のキャリー出力、つまり、後段キャリー出力「COUT（j+1）」が入力され、第1及び第2クロック端子（CK1、CK2）にはクロック信号（LCK1、LCK2）が入力され、ゲート電圧端子（GV）にはゲートオフ電圧（V<sub>off</sub>）が入力されて、フレームリセット端子（FR）には初期化信号（INT）が入力される。また、第1及び第2スイッチング端子（V1、V2）には、各々第2及び第1スイッチング信号（VH2、VH1）が入力される。第1及び第2ゲート出力端子（OUT1、OUT2）は、各々第1及び第2ゲート出力「GOUT（4j-3）、GOUT（4j-1）」を出力し、キャリー出力端子（OUT3）はキャリー出力「COUT（j）」を出力する。最後ステージのキャリー出力は、初期化信号（INT）として各ステージに提供できる。

#### 【0041】

但し、シフトレジスタ400L、400Rの第1ステージ（ST<sub>1</sub>）には、前段キャリー出力の代わりに走査開始信号（STV）が入力されて、最後ステージには後段ゲート出力の代わりに走査開始信号（STV）が入力できる。また、j番目のステージ（ST<sub>j</sub>）の第1クロック端子（CK1）に第2クロック信号（LCK2）が、第2クロック端子（CK2）に第1クロック信号（LCK1）が入力される場合、これに隣接した（j-1）番目及び（j+1）番目のステージ（ST<sub>j-1</sub>、ST<sub>j+1</sub>）の第1クロック端子（CK1）には第1クロック信号（LCK1）が、第2クロック端子（CK2）には第2クロック信号（LCK2）が入力される。

#### 【0042】

10

20

30

40

50

第1及び第2クロック信号（LCK1、LCK2）は、画素のトランジスタ（Tr）を駆動できるように、電圧レベルがハイの場合はゲートオン電圧（Von）と同一であって、ローの場合はゲートオフ電圧（Voff）と同一であるのが好ましい。第1及び第2クロック信号（LCK1、LCK2）は、デューティ比が50%であり、その位相差は180°でありうる。

【0043】

第1及び第2スイッチング信号（VH1、VH2）はまた、画素のトランジスタ（Tr）を駆動できるように、電圧レベルがハイの場合は、ゲートオン電圧（Von）と同一であって、ローの場合はゲートオフ電圧（Voff）と同一であるのが好ましい。第1及び第2スイッチング信号（VH1、VH2）は、デューティ比が50%であり、その位相差は180°でありうる。第1及び第2スイッチング信号（VH1、VH2）の周期は1フレームである。

【0044】

図4を参照すると、本発明の一実施形態によるゲート駆動部400L、400Rの各ステージ、例えば、j番目ステージ（ST<sub>j</sub>）は、入力部420、プルアップ駆動部430、プルダウン駆動部440、出力部450を含む電圧生成部と、出力部450に連結されている出力スイッチング部460を含む。

【0045】

これらは少なくとも一つのN型電界効果トランジスタ（T1～T14）を含み、プルアップ駆動部430には更にキャパシタC1及びC2を、出力部450にはキャパシタC3を更に含む。しかし、N型電界効果トランジスタの代わりにP型電界効果トランジスタを使用しても良い。また、キャパシタ（C1～C3）はゲート・ドレイン間／ゲート・ソース間の寄生容量のみでもよい。また、電圧生成部の構造は図4に示した例と異なっても良い。

【0046】

入力部420はセット端子（S）とゲート電圧端子（GV）に順次直列連結されている三つのトランジスタ（T11、T10、T5）を含む。トランジスタ（T11、T5）のゲートは、第2クロック端子（CK2）に連結されてトランジスタ（T5）のゲートは第1クロック端子（CK1）に連結されている。トランジスタ（T11）とトランジスタ（T10）の間の接続点は接続点（J1）に連結されており、トランジスタ（T10）とトランジスタ（T5）の間の接続点は接続点（J2）に連結されている。

【0047】

プルアップ駆動部430は、三つのトランジスタ（T4、T12、T7）と二つのキャパシタ（C1、C2）を含む。トランジスタ（T4）はセット端子（S）と接続点（J1）との間に連結されており、トランジスタ（T12）は第1クロック端子（CK1）と接続点（J3）との間に連結されており、トランジスタ（T7）は第1クロック端子（CK1）と接続点（J4）との間に連結されている。トランジスタ（T4）のゲートとドレインはセット端子（S）に共通に連結され、ソースは接続点（J1）に連結されており、トランジスタ（T12）のゲートとドレインは第1クロック端子（CK1）に共通に連結されており、ソースは接続点（J3）に連結されている。トランジスタ（T7）のゲートは接続点（J3）に連結されると同時に、キャパシタ（C1）を通して第1クロック端子（CK1）に連結されており、ドレインは第1クロック端子（CK1）に、ソースは接続点（J4）に連結されており、接続点（J3）と接続点（J4）との間にキャパシタ（C2）が連結されている。

【0048】

プルダウン駆動部440は、ソースを通してゲートオフ電圧（Voff）を受信してドレインを通して接続点（J1、J2、J3、J4）に出力する複数のトランジスタ（T9、T13、T8、T3、T2、T6）を含む。トランジスタ（T9）のゲートは、リセット端子（R）に、ドレインは接続点（J1）に連結されており、トランジスタ（T13、T8）のゲートは接続点（J2）に共通に連結されており、ドレインは各々接続点（J3

10

20

30

40

50

、 J 4 ) に連結されている。トランジスタ ( T 3 ) のゲートは接続点 ( J 4 ) に、トランジスタ ( T 2 ) のゲートはリセット端子 ( R ) に連結されており、二つのトランジスタ ( T 3 、 T 2 ) のドレインは接続点 ( J 2 ) に連結されている。トランジスタ ( T 6 ) のゲートはフレームリセット端子 ( F R ) に連結されており、ドレインは接続点 ( J 1 ) に、ソースはゲートオフ電圧端子 ( G V ) に連結されている。

#### 【 0 0 4 9 】

出力部 4 5 0 は、一対のトランジスタ ( T 1 、 T 1 4 ) とキャパシタ ( C 3 ) を含む。トランジスタ ( T 1 ) のドレインとソースは、第 1 クロック端子 ( C K 1 ) と出力端子 ( O U T 1 、 O U T 3 ) との間に連結されており、トランジスタ ( T 1 4 ) のドレインとソースは第 1 クロック端子 ( C K 1 ) とキャリー出力端子 ( O U T 3 ) との間に連結されている。トランジスタ ( T 1 、 T 1 4 ) のゲートは、接続点 ( J 1 ) に連結されている。キャパシタ ( C 3 ) はトランジスタ ( T 1 ) のゲートとドレインとの間、つまり、接続点 ( J 1 ) と接続点 ( J 2 ) との間に連結されている。トランジスタ ( T 1 ) のソースは、また、接続点 ( J 2 ) に連結されている。

#### 【 0 0 5 0 】

出力スイッチング部 4 6 0 は、第 1 及び第 2 スイッチング信号 ( V H 1 、 V H 2 ) に対して対称に連結されている 2 対の伝達及び遮断トランジスタ ( T 1 6 ~ T 1 9 ) を含む。各伝達トランジスタ ( T 1 6 、 T 1 8 ) の制御端子には第 1 、第 2 スイッチング信号 ( V H 1 、 V H 2 ) が印加され、入力端子には出力部 4 5 0 の出力が印加されて、出力端子はステージ ( S T j ) の第 1 、第 2 ゲート出力端子 ( O U T 1 、 O U T 2 ) に連結されている。

#### 【 0 0 5 1 】

各遮断トランジスタ ( T 1 7 、 T 1 9 ) の制御端子には第 2 、第 1 スイッチング信号 ( V H 2 、 V H 1 ) が印加され、入力端子には第 1 、第 2 スイッチング信号 ( V H 1 、 V H 2 ) が印加されて、出力端子はステージ ( S T j ) の第 1 、第 2 ゲート出力端子 ( O U T 1 、 O U T 2 ) に連結されている。

#### 【 0 0 5 2 】

このようなステージの動作について以下に説明する。

第 1 及び第 2 クロック信号 ( L C K 1 、 L C K 2 ) と第 1 及び第 2 スイッチング信号 ( V H 1 、 V H 2 ) のローレベル電圧の大きさはゲートオフ電圧 ( V o f f ) と同一であると仮定する。

#### 【 0 0 5 3 】

まず、第 2 クロック信号 ( L C K 2 ) 及び前段キャリー出力 [ C O U T ( j - 1 ) ] がハイになると、トランジスタ ( T 1 1 、 T 5 ) とトランジスタ ( T 4 ) が導通する。そうなると、二つのトランジスタ ( T 1 1 、 T 4 ) は高電圧を接続点 ( J 1 ) に伝達して、トランジスタ ( T 5 ) は低電圧を接続点 ( J 2 ) に伝達する。これによって、トランジスタ ( T 1 、 T 1 5 ) が導通して第 1 クロック信号 ( L C K 1 ) が出力端子 ( O U T 1 、 O U T 3 ) に出力されるが、この時、接続点 ( J 2 ) の電圧と第 1 クロック信号 ( L C K 1 ) が全て低電圧であるため、出力部 4 5 0 の出力は行われる。これと同時に、キャパシタ ( C 3 ) は高電圧と低電圧の差に該当する大きさの電圧を充電する。

この時、第 1 クロック信号 ( L C K 1 ) 及び後段キャリー出力 [ C O U T ( j + 1 ) ] はローであり、接続点 ( J 2 ) もローであるので、これにゲートが連結されているトランジスタ ( T 1 0 、 T 9 、 T 1 2 、 T 1 3 、 T 8 、 T 2 ) は全てオフ状態となる。

#### 【 0 0 5 4 】

次に、第 2 クロック信号 ( L C K 2 ) がローになると、トランジスタ ( T 1 1 、 T 5 ) が遮断されて、これと同時に第 1 クロック信号 ( L C K 1 ) がハイになるとトランジスタ ( T 1 ) の出力電圧及び接続点 ( J 2 ) の電圧が高電圧となる。この時、トランジスタ ( T 1 0 ) のゲートには高電圧が印加されるが、接続点 ( J 2 ) に連結されているソースの電位がまた、同一の高電圧であるため、ゲート - ソース間の電位差が 0 になって、トランジスタ ( T 1 0 ) は遮断状態を維持する。従って、接続点 ( J 1 ) は浮遊状態になって、

10

20

30

40

50

そのためにキャパシタ (C3) によって高電圧であるほど電位がさらに上昇する。

【0055】

一方、第1クロック信号 (LCK1) 及び接続点 (J2) の電位が高電圧であるため、トランジスタ (T12、T13、T8) が導通する。この状態でトランジスタ (T12) とトランジスタ (T13) が高電圧と低電圧との間で直列連結され、抵抗のように動作する。そのために接続点 (J3) の電位は、二つのトランジスタ (T12、T13) の導通時に抵抗状態の抵抗値によって分圧された電圧値を有する。

【0056】

しかし、トランジスタ (T13) の導通時に、抵抗状態の抵抗値がトランジスタ (T12) の導通時の抵抗状態の抵抗値に比べて、非常に大きく、例えば、約10、000倍程度に設定されているとすると、接続点 (J3) の電圧は高電圧とほとんど同一である。従って、トランジスタ (T7) が導通してトランジスタ (T8) と直列連結され、そのために接続点 (J4) の電位は二つのトランジスタ (T7、T8) の導通時に抵抗状態の抵抗値によって分圧された電圧値を有する。この時、二つのトランジスタ (T7、T8) の抵抗状態の抵抗値がほとんど同一に設定されると、接続点 (J4) の電位は高電圧と低電圧の中間値を有し、そのためにトランジスタ (T3) は遮断状態を維持する。

【0057】

この時、後段キャリー出力 [COUT (j+1)] が依然としてローであるため、トランジスタ (T9、T2) も遮断状態を維持する。従って、出力部450の出力は第1クロック信号 (LCK1) にだけ連結されて低電圧とは遮断されて高電圧を出力する。

一方、キャパシタ (C1) とキャパシタ (C2) は、両端の電位差に該当する電圧を各々充電するが、接続点 (J3) の電圧が接続点 (J5) の電圧より低い。

【0058】

次に、後段キャリー出力 [COUT (j+1)] 及び第2クロック信号 (LCK2) がハイになって第1クロック信号 (LCK1) がローになると、トランジスタ (T9、T2) が導通して接続点 (J1、J2) に低電圧を伝達する。この時、接続点 (J1) の電圧はキャパシタ (C3) が放電しながら低電圧に落ちる。

【0059】

ところが、キャパシタ (C3) の放電時間によって接続点 (J1) の電圧が低電圧に完全に落ちるまでには、ある程度時間を要する。従って、二つのトランジスタ (T1、T15) は後段キャリー出力 [COUT (j+1)] がハイになっても少しの間導通状態を維持し、そのために出力部450の出力が第1クロック信号 (LCK1) と連結されて低電圧を出力する。続いて、キャパシタ (C3) が完全に放電されて接続点 (J1) の電位が低電圧になると、トランジスタ (T15) が遮断されてキャリー出力端子 (OUT3) が第1クロック信号 (LCK1) から遮断されるので、キャリー出力 [COUT (j)] は浮遊状態になって低電圧を維持する。

【0060】

これと同時に、出力部450の他の出力、つまり、図4の下端のトランジスタ (T16 ~ T19)、すなわち、出力スイッチング部460に入力される出力は、トランジスタ (T1) が上記T15と同様に遮断されても、プルダウン駆動部440のトランジスタ (T2) を通して低電圧のVoffと連結されるので、出力端子 (OUT1) は引き続き低電圧を出力する。

【0061】

一方、トランジスタ (T12、T13) が遮断されるため、接続点 (J3) が浮遊状態となる。また、接続点 (J5) の電圧が接続点 (J4) の電圧より低くなるが、キャパシタ (C1) によって接続点 (J3) の電圧が接続点 (J5) の電圧より低い状態を維持するため、トランジスタ (T7) は遮断される。これと同時にトランジスタ (T8) も遮断状態になるため接続点 (J4) の電圧もその分低くなり、トランジスタ (T3) も遮断状態を維持する。また、トランジスタ (T10) は、ゲートが第1クロック信号 (LCK1) の低電圧に連結されて接続点 (J2) の電圧もローであるため、遮断状態を維持する。

10

20

30

40

50

## 【0062】

次に、第1クロック信号( $LCK_1$ )がハイになると、トランジスタ( $T_{12}$ 、 $T_7$ )が導通され、接続点( $J_4$ )の電圧が上昇してトランジスタ( $T_3$ )を導通させて低電圧を接続点( $J_2$ )に伝達するため、出力部450の出力は引続き低電圧を出力する。つまり、たとえ後段キャリー出力[ $COUT(j+1)$ ]の出力がローであっても、接続点( $J_2$ )の電圧が低電圧になるようにする。

一方、トランジスタ( $T_{10}$ )のゲートが第1クロック信号( $LCK_1$ )の高電圧と連結されて接続点( $J_2$ )の電圧が低電圧であるため、トランジスタ( $T_{10}$ )が導通して接続点( $J_2$ )の低電圧を接続点( $J_1$ )に伝達する。

## 【0063】

一方、二つのトランジスタ( $T_1$ 、 $T_{15}$ )のドレインには、第1クロック端子( $CK_1$ )が連結されていて第1クロック信号( $LCK_1$ )が引続き印加される。特に、トランジスタ( $T_1$ )は他のトランジスタに比べて相対的に大きくさせるが、これによってゲート-ドレイン間の寄生容量が大きくなってドレインの電圧変化がゲート電圧に影響を及ぼすことがある。従って、第1クロック信号( $LCK_1$ )がハイになると、ゲート-ドレイン間の寄生容量のため、ゲート電圧が上がりトランジスタ( $T_1$ )が導通することもありうる。従って、接続点( $J_2$ )の低電圧を接続点( $J_1$ )に伝達することによって、トランジスタ( $T_1$ )のゲート電圧を低電圧に維持してトランジスタ( $T_1$ )が導通することを防止する。

## 【0064】

以降、前段キャリー出力[ $COUT(j-1)$ ]がハイになるまで接続点( $J_1$ )の電圧は低電圧を維持し、接続点( $J_2$ )の電圧は第1クロック信号( $LCK_1$ )がハイで第2クロック信号( $LCK_2$ )がローの時は、トランジスタ( $T_3$ )を通して低電圧になり、その逆の場合にはトランジスタ( $T_5$ )を通して低電圧を維持する。

## 【0065】

一方、出力部450の出力が高電圧の時、第1スイッチング信号( $VH_1$ )がハイで第2スイッチング信号( $VH_2$ )がローの場合、出力スイッチング部460のトランジスタ( $T_{16}$ )は出力部450の出力によってトランジスタ( $T_{17}$ )はオフになる。これとは逆に、トランジスタ( $T_{18}$ )はオフされて、トランジスタ( $T_{19}$ )はオンされて、第2スイッチング信号( $VH_2$ )の値、つまり、低電圧を出力する。従って、第1ゲート出力端子( $OUT_1$ )の出力は高電圧となって、第2ゲート出力端子( $OUT_2$ )の出力は低電圧となる。

これと同様に、第1スイッチング信号( $VH_1$ )がローで第2スイッチング信号( $VH_2$ )がハイの場合、第1ゲート出力端子( $OUT_1$ )の出力は低電圧になって、第2ゲート出力端子( $OUT_2$ )の出力は高電圧となる。

## 【0066】

一方、トランジスタ( $T_6$ )は、最後のダミーステージのキャリー出力[ $COUT(n+1)$ ]の初期化信号( $INT$ )を受信してゲートオフ電圧( $Voff$ )を接続点( $J_1$ )に伝達して接続点( $J_1$ )の電圧を再び低電圧に設定する。

## 【0067】

このような方式で、ステージ( $ST_j$ )は前段キャリー信号[ $COUT(j-1)$ ]及び後段キャリー信号[ $COUT(j+1)$ ]に基づいて第1及び第2クロック信号( $LCK_1$ 、 $LCK_2$ )に同期してキャリー信号[ $COUT(j)$ ]及びゲート信号[ $GOUT(4j-3)$ 、 $GOUT(4j-1)$ ]を生成し、第1及び第2スイッチング信号( $VH_1$ 、 $VH_2$ )はステージ( $ST_j$ )の二つの出力が交互に出るように制御する。

このようにすると、4つのトランジスタと2つの信号線のみを追加することによって、二つのゲート線にゲートオン電圧を印加することができるため、シフトレジスタが占める面積が減る。

本実施形態では、一つのステージ( $ST_j$ )が二つのゲート線に供給するゲートオン電圧を生成する。しかし、ステージ( $ST_j$ )は幾つかのトランジスタと信号線を追加する

10

20

30

40

50

ことによって3つまたは4つ以上のゲート線に供給するゲートオン電圧を生成するように変形されることがある。

本実施形態では、ゲート線に順次にゲートオン電圧( $V_{on}$ )を印加する。つまり、ゲートオン電圧( $V_{on}$ )が印加される順序は、第1ゲート線、第2ゲート線、第3ゲート線、第4ゲート線、…の順である。

#### 【0068】

一方、第1及び第2クロック信号( $LCK1$ 、 $LCK2$ )の周期を1フレームとするところ、前半1/2フレームと後半1/2フレームの値が変わるので、前半1/2フレームの間は全てのステージが第1出力端を通してだけ出力し、後半1/2フレームの間は全てのステージが第2出力端を通してだけ出力する。従って、ゲートオン電圧( $V_{on}$ )を印加されるゲート線は、第1、第2、第5、第6、…、第3、第4、第7、第8、…の形態となる。

#### 【0069】

尚、本発明は、上述の実施形態に限られるものではない。本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

#### 【図面の簡単な説明】

#### 【0070】

【図1】本発明の一実施形態による液晶表示装置のブロック図である。

【図2】本発明の一実施形態による液晶表示装置の一つの画素に対する等価回路図である。

【図3】図1に示したゲート駆動部のブロック図の一例である。

【図4】図3に示したゲート駆動部の一つのステージの回路図の一例である。

#### 【符号の説明】

#### 【0071】

|       |         |

|-------|---------|

| 3     | 液晶層     |

| 1 0 0 | 下部表示板   |

| 2 0 0 | 上部表示板   |

| 1 9 1 | 画素電極    |

| 2 3 0 | 色フィルタ   |

| 2 7 0 | 共通電極    |

| 3 0 0 | 液晶表示板組立 |

10

20

30

【図1】

【図2】

【図3】

【図4】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 0 2 F 1/133 5 5 0

G 1 1 C 19/28 D

(72)発明者 李 鍾 煥

大韓民国 京畿道 安養市 東安区 達安洞 セッピヨルアパート 602棟 1705号

F ターム(参考) 2H093 NC16 NC22 NC34 NC35 ND39 ND49

5C006 AC22 AF42 AF71 BB16 BC02 BC03 BC22 BC23 BF03 BF06

BF34 BF37 FA41 FA51

5C080 AA10 BB05 DD22 DD27 FF11 JJ02 JJ03 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 移位寄存器和具有相同的显示设备                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2007094415A</a>                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2007-04-12 |

| 申请号            | JP2006262269                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2006-09-27 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 李洪雨<br>李癸憲<br>李鍾煥                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 李洪雨<br>李癸憲<br>李鍾煥                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133 G11C19/28                                                                                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | G09G3/3677 G09G2300/0439 G09G2310/0281 G09G2310/0286 G11C19/184                                                                                                                                                                                                                                                                                                                          |         |            |

| F1分类号          | G09G3/36 G09G3/20.622.E G09G3/20.622.C G09G3/20.622.D G09G3/20.621.M G02F1/133.550<br>G11C19/28.D G11C19/00 G11C19/00.J G11C19/28.230                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 2H093/NC16 2H093/NC22 2H093/NC34 2H093/NC35 2H093/ND39 2H093/ND49 5C006/AC22 5C006<br>/AF42 5C006/AF71 5C006/BB16 5C006/BC02 5C006/BC03 5C006/BC22 5C006/BC23 5C006/BF03<br>5C006/BF06 5C006/BF34 5C006/BF37 5C006/FA41 5C006/FA51 5C080/AA10 5C080/BB05 5C080<br>/DD22 5C080/DD27 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ06 2H193/ZA04 2H193/ZF24<br>5B074/AA10 5B074/CA01 5B074/EA01 |         |            |

| 优先权            | 1020050089827 2005-09-27 KR                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | JP2007094415A5<br>JP5110680B2                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                |         |            |

## 摘要(译)

解决的问题：减少显示板所需的数据线的数量，从而减少数据驱动单元的数量，并降低安装在液晶显示装置中的驱动单元所消耗的制造成本。提供一种寄存器和具有该寄存器的显示装置。基板，形成在基板上的多条选通线，与选通线相交的多条数据线，连接到选通线和数据线的多个薄膜晶体管以及连接到薄膜晶体管的矩阵。多个像素电极，具有平行于栅极线的第一侧和比第一侧短并且与第一侧相邻的第二侧；以及连接至栅极线的栅极驱动器。栅极驱动器包括彼此连接以顺序产生输出信号的多个级，并且每个级连接到至少两条栅极线并且具有至少两个用于导通薄膜晶体管的第一输出电压。它具有用于交替输出到栅极线的多个输出端子。[选择图]图4