(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-11273

(P2007-11273A)

(43) 公開日 平成19年1月18日(2007.1.18)

(51) Int.CI.

F 1

テーマコード(参考)

**G09G 3/36 (2006.01)**

G09G 3/36

2 H 09 3

**G02F 1/133 (2006.01)**

G02F 1/133

5 C 00 6

**G09G 3/20 (2006.01)**

G09G 3/20

5 C 08 0

G09G 3/20

6 1 2 U

G09G 3/20

6 2 3 C

G09G 3/20

6 2 3 R

審査請求 有 請求項の数 18 O L (全 15 頁) 最終頁に続く

(21) 出願番号

特願2005-379420 (P2005-379420)

(22) 出願日

平成17年12月28日 (2005.12.28)

(31) 優先権主張番号

10-2005-0056543

(32) 優先日

平成17年6月28日 (2005.6.28)

(33) 優先権主張国

韓国 (KR)

(71) 出願人 599127667

エルジー フィリップス エルシーティー

カンパニー リミテッド

大韓民国 ソウル, ヨンドンポーク,

ヨイドードン 20

(74) 代理人 100057874

弁理士 曾我 道照

(74) 代理人 100110423

弁理士 曾我 道治

(74) 代理人 100084010

弁理士 古川 秀利

(74) 代理人 100094695

弁理士 鈴木 憲七

(74) 代理人 100111648

弁理士 梶並 順

最終頁に続く

(54) 【発明の名称】 液晶表示装置とその駆動方法

## (57) 【要約】

【課題】本発明は、データ集積回路の発熱温度を下げ、消費電力を減らすようにした液晶表示装置とその駆動方法に関する。

【解決手段】本発明に従う液晶表示装置は、液晶セルに接続されるデータ出力ラインと、前記データ出力ラインに接続され、前記液晶セルに供給されるビデオデータ信号に対応するピックセル駆動信号を前記データ出力ラインに選択的に供給する出力駆動部と、前記データ出力ラインに接続され、前記ビデオデータ信号の値に応じて一つ以上の電圧レベルで前記データ出力ラインを選択的にプリチャージするプリチャージング回路とを備える。

【選択図】図6

**【特許請求の範囲】****【請求項 1】**

液晶セルに接続されるデータ出力ラインと、

前記データ出力ラインに接続され、前記液晶セルに供給されるビデオデータ信号に対応するピクセル駆動信号を前記データ出力ラインに選択的に供給する出力駆動部と、

前記データ出力ラインに接続され、前記ビデオデータ信号の値に応じて一つ以上の電圧レベルで前記データ出力ラインを選択的にプリチャージするプリチャージング回路と

を備えることを特徴とする液晶表示装置。

**【請求項 2】**

前記電圧レベルは、正極性プリチャージ電圧、前記正極性電圧より低い負極性プリチャージ電圧およびチャージシェア電圧を含み、

10

前記正極性プリチャージ電圧および負極性プリチャージ電圧の絶対値電圧は前記チャージシェア電圧より高いものを特徴とする請求項 1 に記載の液晶表示装置。

**【請求項 3】**

前記電圧レベルは、正極性プリチャージ電圧、前記正極性電圧より低い負極性プリチャージ電圧およびチャージシェア電圧を含み、

10

前記チャージシェア電圧は前記正極性プリチャージ電圧と前記負極性プリチャージ電圧との間の電圧であることを特徴とする請求項 1 に記載の液晶表示装置。

**【請求項 4】**

前記プリチャージング回路は、

前記ビデオデータ信号の値が所定の臨界値以上であるか、またはその未満であるかを指示する出力信号を発生するレベル検出回路と、

前記レベル検出回路の前記出力信号に応じて前記データ出力ラインに前記電圧レベルのうち一つを供給する電圧選択回路と

を備えることを特徴とする請求項 1 に記載の液晶表示装置。

20

**【請求項 5】**

前記電圧選択回路は、

各々ゲート信号に応じて前記電圧レベルのうち一つを前記データ出力ラインに供給する複数のスイッチングトランジスタと、

前記レベル検出回路の出力信号に応じて前記スイッチングトランジスタのゲート制御信号を発生することに用いられる出力イネーブル信号を出力するデマルチプレクサーと

30

を備えることを特徴とする請求項 4 に記載の液晶表示装置。

**【請求項 6】**

デジタルビデオデータ信号の値が所定の臨界値以上であるか、またはそれ未満であるかを指示する出力信号を発生する比較器と、

液晶セルのデータラインをチャージシェア電圧まで 1 次プリチャージした後、前記比較器の出力信号に応じて前記データラインを前記チャージシェア電圧より絶対値電圧が高いプリチャージ電圧まで 2 次プリチャージするプリチャージ制御部と

を備えることを特徴とする液晶表示装置。

40

**【請求項 7】**

前記プリチャージ制御部は前記比較器の出力信号が所定の臨界値以上のデジタルビデオデータ信号を指示する際、前記データラインを 2 次プリチャージすることを特徴とする請求項 6 に記載の液晶表示装置。

**【請求項 8】**

前記比較器と前記プリチャージ制御部は一つの半導体集積回路の内に実装されることを特徴とする請求項 6 に記載の液晶表示装置。

**【請求項 9】**

前記プリチャージ制御部は、

第 1 ソース出力イネーブル信号、前記第 1 ソース出力イネーブル信号より位相が遅い第 2 ソース出力イネーブル信号および前記データ信号の極性を制御する極性制御信号の入力

50

を受ける複数の入力ラインと、

前記比較器の出力と前記極性制御信号の出力に応じて前記第2ソース出力イネーブル信号を複数の出力端子のうち何れか一つに出力するデマルチプレクサーと、

前記デマルチプレクサーの出力、または前記第1ソース出力イネーブル信号に応じて前記データラインに前記チャージシェア電圧を供給する第1トランジスタと、

前記デジタルビデオデータの値が前記所定の臨界値以上であり、前記極性制御信号が正極性電圧出力を指示する際、前記デマルチプレクサーの出力に応じて正極性プリチャージ電圧を前記データラインに供給する第2トランジスタと、

前記デジタルビデオデータの値が前記所定の臨界値より小さくて、前記極性制御信号が負極性電圧出力を指示する際、前記デマルチプレクサーの出力に応じて負極性プリチャージ電圧を前記データラインに供給する第3トランジスタと

10

を備えることを特徴とする請求項7に記載の液晶表示装置。

#### 【請求項10】

前記比較器は前記デジタルビデオデータのビットのうち何れか一つを前記デマルチプレクサーに供給する信号配線を備えることを特徴とする請求項9に記載の液晶表示装置。

#### 【請求項11】

前記比較器は前記デジタルビデオデータの上位ビットを論理和演算する、少なくとも一つ以上の論理ゲート素子を備えることを特徴とする請求項9に記載の液晶表示装置。

#### 【請求項12】

前記比較器は

前記デジタルビデオデータの $2^5$ 加重値の第1上位ビットと $2^6$ 加重値の第2上位ビットとを論理和演算するORゲートと、

20

前記ORゲートの出力と前記データの $2^7$ 加重値の第3上位ビットとを論理積演算するANDゲートと

を備えることを特徴とする請求項11に記載の液晶表示装置。

#### 【請求項13】

前記比較器は前記デジタルビデオデータの $2^6$ 加重値の第1上位ビットと $2^7$ 加重値の第2上位ビットとを論理積演算するANDゲートとを備えることを特徴とする請求項11に記載の液晶表示装置。

#### 【請求項14】

前記比較器は

前記デジタルビデオデータの $2^5$ 加重値の第1上位ビットと $2^6$ 加重値の第2上位ビットとを論理和演算する第1ANDゲートと、

前記第1ANDゲートの出力と前記データの $2^7$ 加重値の第3上位ビットとを論理積演算する第2ANDゲートと

を備えることを特徴とする請求項11に記載の液晶表示装置。

#### 【請求項15】

前記所定の臨界値は128階調以上の階調レベル、160階調以上の階調レベル、192階調以上の階調レベル、224階調以上の階調レベルのうち何れか一つに対応することを特徴とする請求項6に記載の液晶表示装置。

#### 【請求項16】

デジタルビデオデータ信号の値を所定の臨界値と比較する段階と、

前記比較結果に基づいて、複数の互いに異なる電圧レベルのうち何れか一つの電圧で液晶セルのデータラインをプリチャージする段階と、

前記デジタルビデオデータを用いて前記液晶セルの画素駆動電圧を発生し、前記画素駆動電圧を前記データラインに供給する段階と

を含むことを特徴とする液晶表示装置の駆動方法。

#### 【請求項17】

デジタルビデオデータの入力を受ける段階と、

液晶セルのデータラインをチャージシェア電圧までプリチャージする段階と、

40

前記デジタルビデオデータの値が所定の臨界値以上であるとプリチャージ電圧まで前記データラインをプリチャージする段階と、

前記デジタルビデオデータを用いて前記液晶セルの画素駆動電圧を発生し、前記画素駆動電圧を前記データラインに供給する段階と

を含むことを特徴とする液晶表示装置の駆動方法。

#### 【請求項 1 8】

前記プリチャージ電圧の絶対値電圧は前記チャージシェア電圧より高いことを特徴とする請求項 1 7 に記載の液晶表示装置の駆動方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

本発明は、液晶表示装置に関し、特に、データ集積回路の動作温度を下げ、消費電力を減らすようにした液晶表示装置とその駆動方法に関する。

##### 【背景技術】

##### 【0 0 0 2】

液晶表示装置(Liquid Crystal Display)は、ビデオ信号によって液晶セルの光透過率を調節することで画像を表示するようになる。

##### 【0 0 0 3】

アクティブマトリックス(Active Matrix)型の液晶表示装置は、スイッチング素子の能動的な制御が可能であるため動画表現に有利である。アクティブマトリックス型の液晶表示素子に使用されるスイッチング素子には主に薄膜トランジスタ(Thin Film Transistor; TFT)(以下、TFTとする。)が用いられている。

##### 【0 0 0 4】

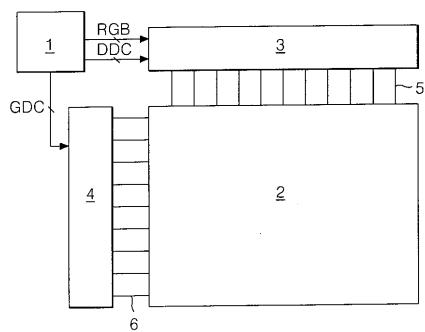

このような液晶表示装置は、図1のように、複数のデータライン5と複数のゲートライン6とが交差され、その交差部に液晶セルを駆動するためのTFTが形成された液晶表示パネル2と、データライン5にデータを供給するためのデータ駆動部3と、ゲートライン6にスキャンパルスを供給するためのゲート駆動部4と、データ駆動部3とゲート駆動部4とを制御するためのタイミングコントローラ1とを備える。

##### 【0 0 0 5】

液晶表示パネル2は、2枚のガラス基板の間に液晶が注入され、その下部ガラス基板上にデータライン5とゲートライン6とが直交される。データライン5とゲートライン6との交差部に形成されたTFTは、ゲートライン6からのスキャンパルスに応じて、データライン5からのデータを液晶セルに供給する。このために、TFTのゲート電極はゲートライン6に接続され、ソース電極はデータライン5に接続される。そして、TFTのドレーン電極は液晶セルの画素電極に接続される。尚、液晶表示パネル2の下部ガラス基板上には液晶セルの電圧を保持させるためのストレージキャパシタが形成される。

##### 【0 0 0 6】

タイミングコントローラ1は、デジタルビデオデータ(RGB)、水平同期信号(H)、垂直同期信号(H、V)およびクロック信号(CLK)の入力を受け、ゲート駆動部4を制御するためのゲート制御信号(GDC)を発生することと共に、データ駆動部3を制御するためのデータ制御信号(DDC)を発生する。尚、タイミングコントローラ1は、システムからのデータ(RGB)をデータ駆動部3に供給する。データ制御信号(DDC)は、ソースシフトクロック(SSC)、ソーススタートパルス(SSP)、極性制御信号(POL)およびソース出力イネーブル信号(SOE)等を含み、データ駆動部3に供給される。ゲート制御信号(GDC)は、ゲートスタートパルス(GSP)、ゲートシフトクロック(GSC)およびゲート出力イネーブル信号(GOE)等を含み、ゲート駆動部4に供給される。

##### 【0 0 0 7】

ゲート駆動部4は、タイミングコントローラ1からのゲート制御信号(GDC)に応じて、スキャンパルスを順次発生するシフトレジスタ、スキャンパルスのスイング幅を液晶セル(CLC)の駆動に適したレベルにシフトさせるためのレベルシフター、出力バッファな

10

20

30

40

50

どで構成される。このゲート駆動部4は、スキャンパルスをゲートライン6に供給することにより、そのゲートライン6に接続されたTFTをターンオン(Turn-on)させ、データの画素電圧、即ち、アナログガンマ補償電圧が供給される一水平ラインの液晶セルを選択する。データ駆動部3から発生されるデータは、スキャンパルスにより選択された水平ラインの液晶セルに供給される。

#### 【0008】

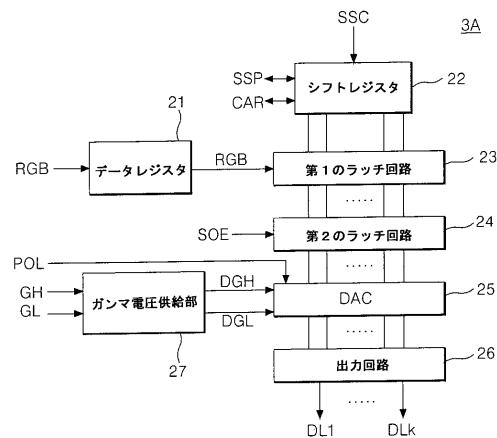

データ駆動部3は、タイミングコントローラ1から供給されるデータ駆動制御信号(DC)に応じて、データをデータライン5に供給する。このデータ駆動部3は、タイミングコントローラ1からのデジタルデータ(RGB)をサンプリングし、そのデータをラッチした後、アナログガンマ電圧に変換する。このデータ駆動部3は、図2のような構成を有する複数のデータ集積回路(Integrated Circuit; IC)3A(以下、データICとする。)に具現される。10

#### 【0009】

各々のデータIC3Aは、図2のように、タイミングコントローラ1からデジタルデータ(RGB)が入力されるデータレジスタ21と、サンプリングクロックを発生するためのシフトレジスタ22と、シフトレジスタ22とk(但し、kはmより小さな整数)個のデータライン(DL1~DLk)の間に接続された第1のラッチ回路23、第2のラッチ回路24、デジタル/アナログ変換器(Digital to Analog Converter: DAC)25(以下、DACとする。)および出力回路26と、ガンマ基準電圧発生部(図示せず)とDAC25の間に接続されたガンマ電圧供給部27とを備える。20

#### 【0010】

データレジスタ21は、タイミングコントローラ1からのデジタルデータ(RGB)を第1のラッチ回路23に供給する。シフトレジスタ22はタイミングコントローラ1からのソーススタートパルス(SSP)をソースサンプリングクロック信号(SSC)によってシフトさせ、サンプリング信号を発生する。尚、シフトレジスタ22はソーススタートパルス(SSP)をシフトさせ、次の段のシフトレジスタ22にキャリー信号(CAR)を伝達する。第1のラッチ回路23はシフトレジスタ22から順次入力されるサンプリング信号に応じて、データレジスタ21からのデジタルデータ(RGB)を順次サンプリングする。第2のラッチ回路24は第1のラッチ回路23から入力されるデータをラッチした後、ラッチされたデータをタイミングコントローラ1からのソース出力イネーブル信号(SOE)に応じて、同時出力する。DAC25は第2のラッチ回路24からのデータをガンマ電圧供給部27からのガンマ電圧(DGH、DGL)に変換する。ガンマ電圧(DGH、DGL)は、デジタル入力データの階調値の各々に対応するアナログ電圧である。出力回路26はデータラインの各々に接続された出力バッファを含む。ガンマ電圧供給部27はガンマ基準電圧発生部(図示せず)から入力されるガンマ基準電圧を細分化し、各階調に対応するガンマ電圧をDAC25に供給する。30

#### 【0011】

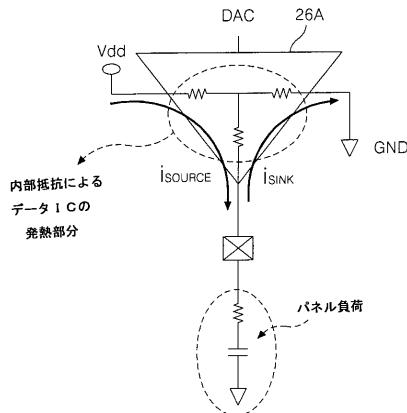

このようなデータIC3Aは、液晶表示装置が大型化、高精細化に発展することに応じて負荷が増加され、駆動周波数が上昇されて発熱量が多くなるようになった。このようなデータIC3Aの発熱によってデータIC3Aの駆動信頼性は落ちてしまい、さらに、発火されること等の安全上の危険性が増大されている。データIC3Aの発熱を起こす主要原因是、図3のように、出力バッファ26Aである。この出力バッファ26Aの内部抵抗成分を通じて流れる電流(isource、sink)による電力消耗によりデータIC3Aが発熱される。40

#### 【0012】

最近は、液晶セルの充電特性を改善し、消費電力を減らすために、隣接するデータラインを接続し、そのデータラインの間のチャージシェアにより発生されるチャージシェア電圧(Charge Share Voltage)でデータラインをプリチャージした後、データラインを分離した状態でデータ電圧を各データラインに供給するチャージシェア方式や、予め設定されている外部電圧であるプリチャージ電圧でデータラインをプリチャージ50

させた後、データ電圧をそのデータラインに供給するプリチャージ方式でデータICが具現されている。

【発明の開示】

【発明が解決しようとする課題】

【0013】

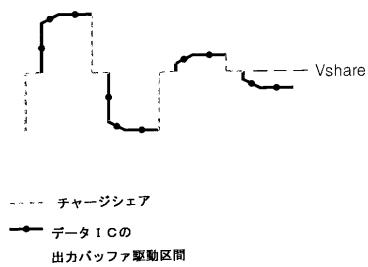

チャージシェア方式は、図4のように、チャージシェア電圧( $V\text{-share}$ )からデータ電圧に変わる出力バッファ駆動区間で、出力バッファ26Aに多くの電流が流れることにより発熱と消費電力が増大されるという問題点があった。

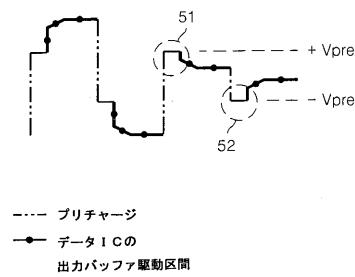

プリチャージ方式は、図5のように、データ電圧が高い際、例えば、ノーマリブラック(Normaly black)モードの液晶表示装置においてホワイト電圧である際、予め比較的に高い外部電圧として供給されるプリチャージ電圧(+ $V_{pre}$ 、- $V_{pre}$ )により出力バッファ26Aの駆動領域の電圧が減ってデータIC3Aの温度を下げる事はできるものの、平均以下のデータ電圧に対して外部から供給される高いプリチャージ電圧(+ $V_{pre}$ 、- $V_{pre}$ )により低いデータ電圧のプリチャージ駆動領域51、52で、データIC3Aの温度が上昇し、電力消費が急増するという問題点があった。

10

【0014】

従って、本発明は、かかる問題点を解決するためになされたものであり、データ集積回路の発熱温度下げ、消費電力を減らすようにした液晶表示装置とその駆動方法を提供することを目的としている。

【課題を解決するための手段】

【0015】

前記目的を達成するために、本発明に従う液晶表示装置は、液晶セルに接続されるデータ出力ラインと；前記データ出力ラインに接続され、前記液晶セルに供給されるビデオデータ信号に対応するピックセル駆動信号を前記データ出力ラインに選択的に供給する出力駆動部と；前記データ出力ラインに接続され、前記ビデオデータ信号の値に応じて一つ以上の電圧レベルで前記データ出力ラインを選択的にプリチャージするプリチャージング回路とを備える。

【0016】

本発明に従う液晶表示装置は、デジタルビデオデータ信号の値が所定の臨界値以上であるか、またはその未満であるかを指示する出力信号を発生する比較器と；液晶セルのデータラインをチャージシェア電圧まで1次プリチャージした後、前記比較器の出力信号に応じて前記データラインを前記チャージシェア電圧より絶対値電圧が高いプリチャージ電圧まで2次プリチャージするプリチャージ制御部とを備える。

30

【0017】

前記液晶表示装置の駆動方法は、デジタルビデオデータ信号の値を所定の臨界値と比較する段階と；前記比較結果に基づいて、複数の互いに異なる電圧レベルのうち何れか一つの電圧で液晶セルのデータラインをプリチャージする段階と；前記デジタルビデオデータを用いて前記液晶セルの画素駆動電圧を発生し、前記画素駆動電圧を前記データラインに供給する段階とを含む。

【0018】

前記液晶表示装置の駆動方法は、デジタルビデオデータの入力を受ける段階と；液晶セルのデータラインをチャージシェア電圧までプリチャージする段階と；前記デジタルビデオデータの値が所定の臨界値以上であるとプリチャージ電圧まで前記データラインをプリチャージする段階と；前記デジタルビデオデータを用いて前記液晶セルの画素駆動電圧を発生し、前記画素駆動電圧を前記データラインに供給する段階とを含む。

40

【発明の効果】

【0019】

本発明に従う液晶表示装置とその駆動方法は、データ集積回路のバッファ駆動区間を減少させることにより発熱温度を下げ、消費電力を減らすことが可能になる。

【発明を実施するための最良の形態】

10

20

30

40

50

## 【0020】

以下、図6ないし図13を参照し、本発明の好ましい実施の形態についての説明する。

## 【0021】

この発明に係る液晶表示装置は、液晶セルに接続されるデータ出力ラインと、データ出力ラインに接続され、液晶セルに供給されるビデオデータ信号に対応するピクセル駆動信号を前記データ出力ラインに選択的に供給する出力駆動部と、データ出力ラインに接続され、ビデオデータ信号の値に応じて一つ以上の電圧レベルで前記データ出力ラインを選択的にプリチャージするプリチャージング回路とを備えている。このデータ駆動部は、複数のデータ集積回路（以下、データI Cとする。）から構成される。

## 【0022】

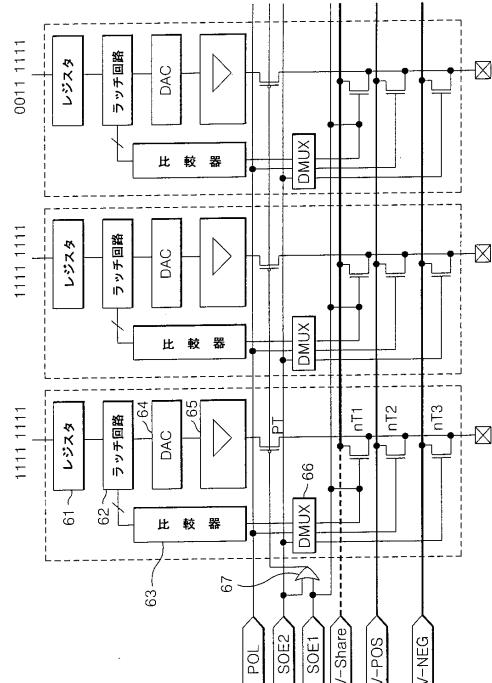

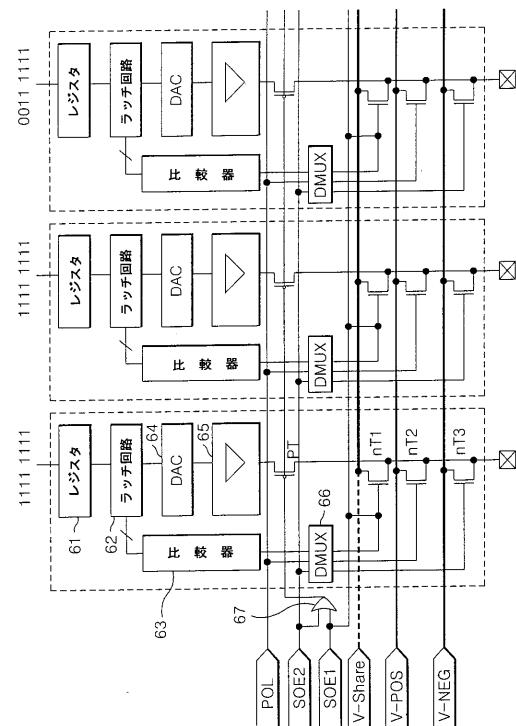

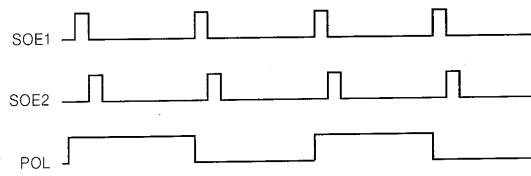

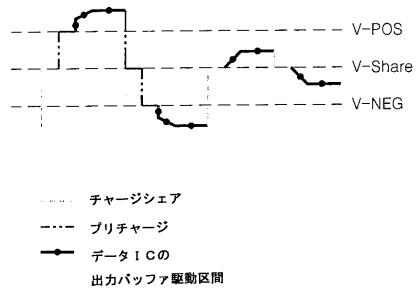

図6は本発明の実施の形態における液晶表示装置のデータI Cの回路構成を示す回路図であり、図7は図6に示したソース出力イネーブル信号（S O E 1、S O E 2）と極性制御信号（P O L）の波形を示す波形図である。

## 【0023】

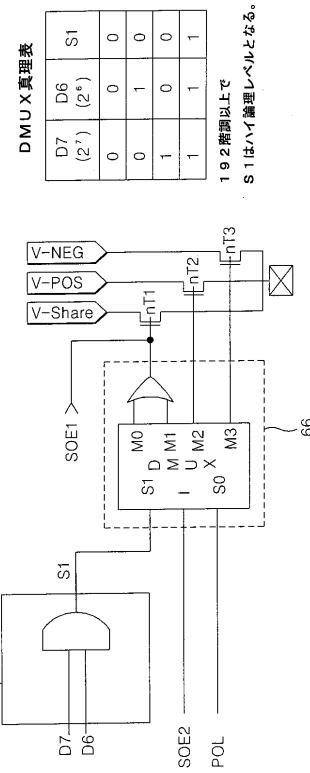

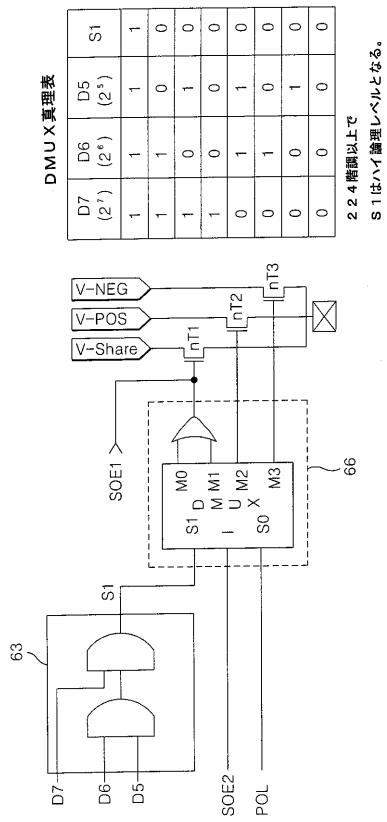

図6および図7を参照すると、本発明の実施の形態に従う液晶表示装置のデータI Cは、データレジスタ61、ラッチ回路62、比較器63、デジタル／アナログ変換器(Digital to Analog Converter : DAC)64（以下、D A Cとする。）、出力バッファ65、デマルチプレクサー(D M U X)66、ORゲート67およびトランジスタp T、n T1、n T2、n T3を備える。

## 【0024】

比較器63は、ビデオデータ信号の値が所定の臨界値以上であるか、またはそれ未満であるかを指示する出力信号を発生するレベル検出回路を構成している。また、複数のスイッチングトランジスタとデマルチプレクサーは、比較器63の出力信号に応じてデータ出力ラインに電圧レベルのうち一つを供給する電圧選択回路（プリチャージ制御部）を構成している。これらの複数のスイッチングトランジスタは、各々ゲート信号に応じて電圧レベルのうち一つをデータ出力ラインに供給する。デマルチプレクサーは、比較器63の出力信号に応じてこれらの複数のスイッチングトランジスタのゲート制御信号を発生することに用いられる出力イネーブル信号を出力する。

## 【0025】

プリチャージ制御部は、液晶セルのデータラインをチャージシェア電圧まで1次プリチャージした後、比較器63の出力信号に応じてデータラインをチャージシェア電圧より絶対値電圧が高いプリチャージ電圧まで2次プリチャージする。

プリチャージ制御部は、第1ソース出力イネーブル信号、第1ソース出力イネーブル信号より位相が遅い第2ソース出力イネーブル信号およびデータ信号の極性を制御する極性制御信号の入力を受ける複数の入力ラインと、比較器63の出力と極性制御信号の出力に応じて第2ソース出力イネーブル信号を複数の出力端子のうち何れか一つに出力するデマルチプレクサー66と、デマルチプレクサー66の出力、または第1ソース出力イネーブル信号に応じてデータラインにチャージシェア電圧を供給する第1トランジスタn T1と、デジタルビデオデータの値が所定の臨界値以上であり、極性制御信号が正極性電圧出力を指示する際、デマルチプレクサー66の出力に応じて正極性プリチャージ電圧をデータラインに供給する第2トランジスタn T2と、デジタルビデオデータの値が所定の臨界値より小さくて、極性制御信号が負極性電圧出力を指示する際、デマルチプレクサー66の出力に応じて負極性プリチャージ電圧をデータラインに供給する第3トランジスタn T3とを備えている。なお、比較器63は、デジタルビデオデータのビットのうち何れか一つをデマルチプレクサー66に供給する信号配線を備えているとともに、デジタルビデオデータの上位ビットを論理和演算する、少なくとも一つ以上の論理ゲート素子を備える。

## 【0026】

図7において、第1ソース出力イネーブル信号（S O E 1）はチャージシェア電圧（V - Share）の出力を指示する制御信号であり、第2ソース出力イネーブル信号（S O E 2）はデータの比較結果に応じてプリチャージ電圧（V - P O S、V - N E G）とチャ-

10

20

30

40

50

ジシェア電圧 (V - Share) との出力の可否を選択的に指示する制御信号である。ここで、正極性プリチャージ電圧 (V - POS) は液晶セルの共通電極に供給される共通電圧より高い所定の正極性電圧であり、負極性プリチャージ電圧 (V - NEG) は液晶セルの共通電極に供給される共通電圧より低い所定の負極性電圧である。そして、チャージシェア電圧 (V - Share) の電圧は正極性および負極性のプリチャージ電圧 (V - POS, V - NEG) の絶対値電圧より低い中間電圧である。

#### 【0027】

第2ソース出力イネーブル信号 (SOE2) は第1ソース出力イネーブル信号 (SOE1) の一パルス幅程シフトされる。このソース出力イネーブル信号 (SOE1, SOE2) は1水平期間の間隔に発生される。極性制御信号 (POL) は1水平期間の間隔にその論理値が反転され、液晶表示パネルのデータラインに供給されるデータ電圧の極性を制御する。このようなソース出力イネーブル信号 (SOE1, SOE2) と極性制御信号 (POL) はタイミングコントローラから発生される。10

#### 【0028】

データレジスタ61はタイミングコントローラからのデジタルデータをラッチ回路62に供給する。ラッチ回路62は、シフトレジスタから順次入力されるサンプリング信号に応じて、データレジスタ61からのデジタルデータを順次サンプリングしてラッチした後、同時出力し、データの直列体系を並列体系に変換する。DAC64は、ラッチ回路62からのデータをアナログガンマ電圧に変換する。出力バッファ65は、DAC64からのアナログ電圧を損失なしにp型トランジスタ(pT)のドレーン端子に供給する。p型トランジスタ(pT)はORゲート67の出力がロー論理電圧である際にターンオンされ、出力バッファ65からのアナログデータ電圧を液晶表示パネルのデータラインに出力する。ORゲート67は第1ソース出力イネーブル信号 (SOE1) と第2ソース出力イネーブル信号 (SOE2) とを論理和演算して出力信号を発生し、その出力信号でp型トランジスタ(pT)を制御する。20

#### 【0029】

比較器63はラッチ回路62からのデータの入力を受けてデジタルデータの階調値を判断し、そのデジタルデータに応じてDMUX66を制御する。この比較器63はデータ電圧が高い際、例えば、ノーマリブラックモードでホワイト階調電圧と、それに近い電圧からハイ論理電圧の出力信号を発生する反面、データ電圧が相対的に低い際、例えば、ノーマリブラックモードでブラック階調電圧と、それに近い電圧からロー論理電圧の出力信号を発生する。データ電圧が高い電圧区間は、デジタルデータが8ビットを含んで表現可能な階調数が256個であると仮定する際、127階調以上の電圧、160階調以上の電圧、191階調以上の電圧または224階調以上の電圧のうち何れか一つの階調電圧区間であり、データ電圧が相対的に低い電圧区間は、127階調未満の電圧、160階調未満の電圧、191階調未満の電圧または224階調未満の電圧である。比較される階調値に応じて、比較器63は入力されるデータの上位ビット数と回路の構成が区別され、これについて詳細な説明は図8～図11をと結び付いて後述する。30

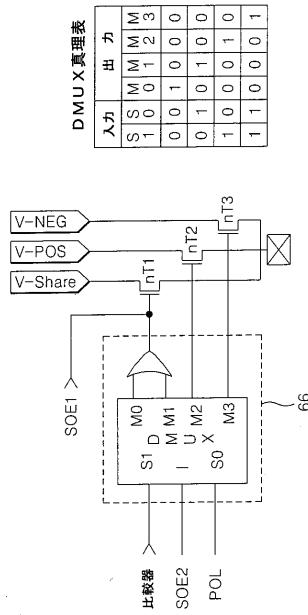

#### 【0030】

DMUX66は、図8のように、比較器63の出力信号と極性制御信号 (POL) に応じてソース出力イネーブル信号 (SOE) を複数の出力端子 (M0～M3) のうち何れか一つに出力する。DMUX66の第1および第2の出力端子 (M0, M1) にはORゲートが接続され、そのORゲートの出力端は第1のn型トランジスタ (nT1) のゲート端子に供給される。このようなDMUX66は図8の真理表のように、極性制御信号 (POL) の論理値に関係なく、比較器63の出力信号の電圧がロー論理電圧である際、即ち、データ電圧が低電圧である際、ハイ論理電圧の第2ソース出力イネーブル信号 (SOE2) をORゲートを経由し、第1のn型トランジスタ (nT1) のゲート端子に供給し、プリチャージ電圧 (V - POS, V - NEG) より低いチャージシェア電圧 (V - share) を液晶表示パネルのデータラインに供給する。これとは相反に、DMUX66は比較器63の出力信号の電圧がハイ論理電圧であり、極性制御信号 (POL) の電圧がロー論理電圧である際、即40

10

20

30

40

50

ち、データ電圧が相対的に高電圧であり、その極性が正極性である際、ハイ論理電圧の第2ソース出力イネーブル信号(SOE2)を第2のn型トランジスタ(nT2)のゲート端子に供給し、正極性プリチャージ電圧(V-POS)を液晶表示パネルのデータラインに供給する。尚、DMUX66は比較器63の出力信号の電圧がハイ論理電圧であり、極性制御信号(POL)の電圧がハイ論理電圧である際、即ち、データ電圧が相対的に高電圧であり、その極性が負極性である際、ハイ論理電圧の第2ソース出力イネーブル信号(SOE2)を第3のn型トランジスタ(nT3)のゲート端子に供給し、負極性プリチャージ電圧(V-NEG)を液晶表示パネルのデータラインに供給する。このようなDMUX66、トランジスタ(pT、nT1、nT2、nT3)および制御/駆動電圧(POL、SOE1、SOE2、V-Share、V-POS、V-NEG)はデータラインのプリチャージを制御するプリチャージ制御部の役割をする。

## 【0031】

第1ソース出力イネーブル信号(SOE1)は第2ソース出力イネーブル信号(SOE2)よりも先に第1のn型トランジスタ(nT1)のゲート端子に供給され、データ電圧が高電圧である際にもプリチャージ電圧(V-POS、V-NEG)よりも先にチャージシェア電圧(V-share)でデータラインをプリチャージさせる。

## 【0032】

一方、チャージシェア電圧(V-share)はデータICの外部に配置された電源回路から別途に発生されることもでき、データIC内でデータラインのチャージシェアリングによって生成されることもできる。このようなチャージシェア電圧(V-share)は、正極性プリチャージ電圧(V-POS)より低くて負極性プリチャージ電圧(V-NEG)より高い電圧の範囲内で一つに設定されるか、または2つ以上に分けられる可能性がある。

## 【0033】

図9～図12は比較器63の多様な実施の形態を示す図面である。

## 【0034】

本発明の第1の実施の形態における比較器63は、図9のように、ノーマリブラックモードで128と同じであるか、またはその以上の階調以上でハイ論理で発生され、127階調以下でロー論理で発生される<sup>27</sup>加重値のD7ビットをDMUX66のS1の入力端子に入力する。従って、本実施の形態の比較器63はD7ビットを供給するための配線のみで具現される。このような比較器63で具現される際、本発明に従うデータICは128階調以上のデータ電圧でプリチャージングされた後、高いプリチャージ電圧(V-POS、V-NEG)でデータラインを充電させ、データICの負担を低減させ、127階調以下のデータ電圧で低いチャージシェア電圧(V-share)のみでデータラインを充電させ、バッファの駆動期間を減少させることによってデータICの負荷を減らすことができる。

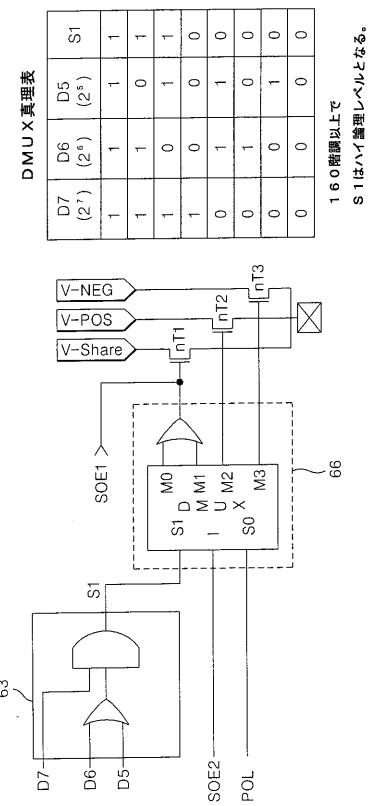

## 【0035】

本発明の第2の実施の形態における比較器63は、図10のように、2<sup>6</sup>加重値のD6ビットと2<sup>5</sup>加重値のD5ビットとを論理和するORゲートと、そのORゲートの出力と2<sup>7</sup>加重値のD7ビットを論理積するANDゲートで構成される。この比較器63のANDゲート出力は、ノーマリブラックモードで160階調以上でハイ論理で発生され、159階調以下でロー論理で発生され、DMUX66のS1入力端子に入力する。従って、本実施の形態の比較器63は、2つの論理ゲート素子で具現される。このような比較器63で具現される際、本発明に従うデータICは160階調以上のデータ電圧でチャージシェアリングされた後、高いプリチャージ電圧(V-POS、V-NEG)でデータラインを充電させ、データICの負担を低減させ、159階調以下のデータ電圧で低いチャージシェア電圧(V-share)のみでデータラインを充電させ、バッファの駆動期間を減少させることによってデータICの負荷を減らすことができる。

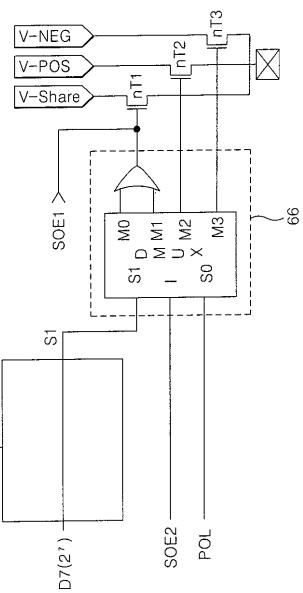

## 【0036】

本発明の第3の実施の形態における比較器63は、図11のように、2<sup>6</sup>加重値のD6ビットと2<sup>7</sup>加重値のD7ビットとを論理積するANDゲートで構成される。この比較器

63のANDゲート出力は、ノーマリブラックモードで191階調以上でハイ論理で発生され、191階調未満でロー論理で発生され、MUX66のS1入力端子に入力する。従って、本実施の形態の比較器63は、1つの論理ゲート素子で具現される。このような比較器63で具現される際、本発明に従うデータICは192階調以上のデータ電圧でチャージシェアリングされた後、高いプリチャージ電圧(V-POS、V-NEG)でデータラインを充電させ、データICの負担を低減させ、192階調より低い階調のデータ電圧で低いチャージシェア電圧(V-Share)のみでデータラインを充電させ、バッファの駆動期間を減少させることによってデータICの負荷を減らすことができる。

#### 【0037】

本発明の第4の実施の形態における比較器63は、図12のように、 $2^6$ 加重値のD6ビットと $2^5$ 加重値のD5ビットとを論理積する第1ANDゲートと、前記第1ANDゲートの出力と $2^7$ 加重値のD7ビットとを論理積する第2ANDゲートで構成される。この比較器63のANDゲート出力は、ノーマリブラックモードで224階調以上でハイ論理で発生され、224階調より低い階調でロー論理で発生され、MUX66のS1入力端子に入力する。従って、本実施の形態の比較器63は、2つの論理ゲート素子で具現される。このような比較器63で具現される際、本発明に従うデータICは224階調以上のデータ電圧でプリチャージされた後、高いプリチャージ電圧(V-POS、V-NEG)でデータラインを充電させ、データICの負担を低減させ、224階調より低い階調のデータ電圧で低いチャージシェア電圧(V-Share)のみでデータラインを充電させ、バッファの駆動期間を減少させることによってデータICの負荷を減らすことができる。

#### 【0038】

図6で8ビットの第1デジタルデータが256の階調(1111 1111)であると比較器63の出力がハイ論理電圧になり、極性制御信号(POL)がハイ論理電圧である際、第1ソース出力イネーブル信号(SOE1)によってチャージシェア電圧(V-Share)で液晶表示パネルの第1データラインが1次プリチャージされた後、正極性プリチャージ電圧(V-POS)で第1データラインが2次プリチャージされる。第1デジタルデータと隣接する第2デジタルデータが第1デジタルデータと同様に(1111 1111)であると、極性制御信号のみ反転され、チャージシェア電圧(V-Share)で液晶表示パネルの第2のデータラインが1次プリチャージされた後、負極性プリチャージ電圧(V-NEG)で第2データラインがプリチャージされる。第2デジタルデータと隣接する第3デジタルデータとその第3デジタルデータと隣接する第4デジタルデータが63階調(0011 1111)であると、比較器63の出力がロー論理電圧で反転され、チャージシェア電圧(V-Share)で液晶表示パネルの第3および第4データラインがプリチャージされる。

#### 【0039】

図13が図4および図5と同一なデータ電圧で本発明に従うデータICの出力波形を示す。

#### 【0040】

図13を参照すると、本発明に従うデータICは、高電圧のデータ電圧が入力されるとチャージシェアに続いてプリチャージ機能を使用し、相対的に低電圧のデータ電圧が入力される場合、チャージシェア機能を使用し、出力バッファの動作区間を最小化し、全体電流消費を減少させることは勿論、プリチャージ電圧を更に上昇させ、最高電圧でのデータIC発熱温度を下げることが可能になる。

#### 【0041】

上述したように、本発明に従う液晶表示装置とその駆動方法は、高電圧のデータでチャージシェア電圧でデータラインを1次プリチャージさせた後、そのチャージシェア電圧より高いプリチャージ電圧でデータラインを2次プリチャージさせる反面、低電圧のデータでチャージシェア電圧のみでデータラインをプリチャージさせることによって、バッファ駆動を減少させ、データ集積回路の発熱温度を低減させ、消費電力を下げることが可能になる。

10

20

30

40

50

**【0042】**

以上、説明した内容により、当業者であれば、本発明の技術思想を逸脱しない範囲内で種々なる変更および修正が可能であることが分かる。従って、本発明の技術的範囲は、明細書の詳細な説明に記載した内容に限定されるものではなく、特許請求の範囲により定めなければならない。

**【図面の簡単な説明】****【0043】**

【図1】液晶表示装置を概略的に示すブロック図である。

【図2】図1に示しているデータ駆動部を詳しく示すブロック図である。

【図3】出力バッファ内の内部抵抗と、その内部抵抗を通じて流れる電流を示す回路図である。

10

【図4】外部プリチャージ電圧でデータラインをプリチャージするプリチャージング方式の一例を示す波形図である。

【図5】チャージシェア電圧でデータラインをプリチャージするチャージシェア方式の一例を示す波形図である。

【図6】本発明の実施の形態における液晶表示装置のアナログサンプリング装置を示す回路図である。

【図7】図6に示しているソース出力イネーブル信号と極性制御信号を示す波形図である。

20

【図8】図6に示しているデマルチプレクサーを詳しく示す回路図である。

【図9】図6に示している比較器の第1の実施の形態を示す回路図である。

【図10】図6に示している比較器の第2の実施の形態を示す回路図である。

【図11】図6に示している比較器の第3の実施の形態を示す回路図である。

【図12】図6に示している比較器の第4の実施の形態を示す回路図である。

【図13】本発明の実施の形態に従う液晶表示装置のデータ集積回路から出力される波形の一例を示す波形図である。

20

**【符号の説明】****【0044】**

1 タイミングコントローラ、2 液晶表示パネル、3 データ駆動部、4 ゲート駆動部、21, 61 データレジスタ、22 シフトレジスタ、23, 24, 62 ラッチ回路、25, 64 デジタル/アナログ変換器、26A, 65 出力バッファ、27 ガンマ電圧供給部、63 比較器、66 デマルチプレクサー、pT, nT1, nT2, nT3 パソコン用トランジスタ。

30

【図1】

【図2】

【図3】

【図4】

【図5】

--- プリチャージ

● データ I.C の

出力バッファ駆動区间

【図6】

【図7】

【図8】

【図10】

【図9】

【図11】

【図12】

【図13】

## フロントページの続き

| (51)Int.Cl. | F I     | テーマコード(参考)   |

|-------------|---------|--------------|

|             | G 0 9 G | 3/20 6 2 1 B |

|             | G 0 9 G | 3/20 6 1 2 E |

|             | G 0 9 G | 3/20 6 2 3 D |

|             | G 0 9 G | 3/20 6 1 1 A |

|             | G 0 9 G | 3/20 6 7 0 L |

(72)発明者 シン - ホー・カン

大韓民国、キョンギ - ド、スオン - シ、パルダル - グ、インギュ - ドン 384、ジュゴン・アパートメント、112 - 105

(72)発明者 ジン - チョル・ホン

大韓民国、キヨングサンプク - ド、クミ - シ、オーテ - ドン、デドン・サードアパートメント、102 - 1105

(72)発明者 スン - チュル・ハ

大韓民国、キヨングサンプク - ド、チルゴク - グン、セクジョク - ミョン、ジュング - リ 224 - 1、204 - 518

F ターム(参考) 2H093 NA16 NA53 NB30 NC13 NC14 NC15 NC16 NC22 NC26 ND33

ND39 ND48

5C006 AA16 AA22 AC11 AC21 AC27 AF45 AF46 AF69 AF71 AF83

BB16 BC12 BF03 BF04 BF14 BF24 BF25 BF26 BF34 BF43

EB05 FA12 FA22 FA26 FA33 FA37 FA47

5C080 AA10 BB05 CC03 DD05 DD08 DD20 DD24 DD25 DD26 DD29

EE29 FF11 GG11 JJ02 JJ03 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2007011273A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 公开(公告)日 | 2007-01-18 |

| 申请号            | JP2005379420                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2005-12-28 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | Eruji飞利浦杜迪股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | シンホーカン<br>ジンチョルホン<br>スンチュルハ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 发明人            | シン-ホー・カン<br>ジン-チョル・ホン<br>スン-チュル・ハ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| CPC分类号         | G09G3/3688 G09G3/2011 G09G3/3614 G09G2310/0248 G09G2310/027 G09G2330/023                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.612.U G09G3/20.623.C G09G3/20.623.R G09G3/20.621.B<br>G09G3/20.612.E G09G3/20.623.D G09G3/20.611.A G09G3/20.670.L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA53 2H093/NB30 2H093/NC13 2H093/NC14 2H093/NC15 2H093/NC16 2H093/<br>/NC22 2H093/NC26 2H093/ND33 2H093/ND39 2H093/ND48 5C006/AA16 5C006/AA22 5C006/AC11<br>5C006/AC21 5C006/AC27 5C006/AF45 5C006/AF46 5C006/AF69 5C006/AF71 5C006/AF83 5C006<br>/BB16 5C006/BC12 5C006/BF03 5C006/BF04 5C006/BF14 5C006/BF24 5C006/BF25 5C006/BF26<br>5C006/BF34 5C006/BF43 5C006/EB05 5C006/FA12 5C006/FA22 5C006/FA26 5C006/FA33 5C006<br>/FA37 5C006/FA47 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD05 5C080/DD08 5C080/DD20<br>5C080/DD24 5C080/DD25 5C080/DD26 5C080/DD29 5C080/EE29 5C080/FF11 5C080/GG11 5C080<br>/JJ02 5C080/JJ03 5C080/JJ04 2H193/ZD23 2H193/ZH23 |         |            |

| 代理人(译)         | 英年古河<br>Kajinami秩序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 优先权            | 1020050056543 2005-06-28 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 其他公开文献         | <a href="#">JP4244228B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

## 摘要(译)

要解决的问题：提供一种通过降低数据集成电路的发热温度来降低功耗的液晶显示装置及其驱动方法。解决方案：液晶显示装置包括：数据线，连接以驱动液晶单元;输出驱动器，连接到数据输出线，并选择性地提供像素驱动信号，对应于提供给液晶单元的视频数据信号数据线连接到数据线，以及连接到数据输出线的预充电电路，用于根据数字视频数据信号的值选择性地将数据输出线预充电到多个电压电平中的一个或多个。ž