(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4157727号

(P4157727)

(45) 発行日 平成20年10月1日(2008.10.1)

(24) 登録日 平成20年7月18日(2008.7.18)

(51) Int.CI.

F 1

**G09G 3/36 (2006.01)**

**G02F 1/133 (2006.01)**

**G09G 3/20 (2006.01)**

GO9G 3/36

GO2F 1/133 550

GO9G 3/20 611D

GO9G 3/20 611J

GO9G 3/20 624D

請求項の数 9 (全 12 頁) 最終頁に続く

(21) 出願番号

特願2002-159667 (P2002-159667)

(22) 出願日

平成14年5月31日 (2002.5.31)

(65) 公開番号

特開2003-108100 (P2003-108100A)

(43) 公開日

平成15年4月11日 (2003.4.11)

審査請求日

平成17年2月22日 (2005.2.22)

(31) 優先権主張番号

2001-59319

(32) 優先日

平成13年9月25日 (2001.9.25)

(33) 優先権主張国

韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

SAMSUNG ELECTRONICS

CO., LTD.大韓民国京畿道水原市靈通区梅灘洞 416

416, Maetan-dong, Yeongtong-gu, Suwon-si,

Gyeonggi-do 442-742

(KR)

(74) 代理人 100094145

弁理士 小野 由己男

(74) 代理人 100106367

弁理士 稲積 朋子

最終頁に続く

(54) 【発明の名称】 液晶表示装置とその駆動装置及び駆動方法

(57) 【特許請求の範囲】

【請求項 1】

共通電極、走査信号を伝送する複数のゲートライン、前記複数のゲートラインと交差し、データ電圧を伝送する複数のデータライン、前記共通電極によって覆われ、前記複数のゲートラインと前記複数のデータラインとともに

マトリックス状に区切られた複数の画素領域のそれぞれに一つずつ形成され、一端

が前記共通電極に連結され、前記共通電極と他端との間の電圧に応じて光を透過する複数

の液晶キャパシター、前記複数の画素領域のそれぞれに一つずつ形成され、いずれかのゲートラインから伝送

される走査信号に従ってターンオンして、同じ画素領域の液晶キャパシターの他端をいずれかのデータラインに連結する複数のスイッチング素子、及び、前記複数の画素領域のそれぞれに一つずつ形成され、一端が同じ画素領域の液晶キャパ

シターの他端に連結されている複数のストレージキャパシター、

を備えた液晶パネル；走査信号を前記複数のゲートラインに順番に出力するゲートドライバー；データ電圧を前記複数のデータラインに出力するデータドライバー；前記共通電極に対して印加される電圧と前記共通電極の実際の電圧との間の差を感知して

共通電極歪曲電圧として出力する歪曲感知部；並びに、前記共通電極歪曲電圧の極性を反転させた電圧を相殺電圧として前記複数のストレージ

10

20

キャパシターの他端に出力する相殺電圧発生部；

を含む液晶表示装置。

【請求項 2】

前記歪曲感知部は、一端が前記共通電極に連結された感知抵抗を備え、前記感知抵抗を通して前記共通電極に対して電圧が印加されるときに前記感知抵抗の両端間の電位差を感じして前記共通電極歪曲電圧として出力することを特徴とする、請求項 1 に記載の液晶表示装置。

【請求項 3】

前記歪曲感知部は、前記共通電極に対して電圧が印加されるときに前記液晶パネルの内部抵抗の両端間の電位差を感じして前記共通電極歪曲電圧として出力することを特徴とする、請求項 1 に記載の液晶表示装置。

10

【請求項 4】

前記相殺電圧発生部は、

非反転入力端子が前記共通電極の電圧を受け、反転入力端子が前記共通電極歪曲電圧を受け、出力端子が前記相殺電圧を出力する O P アンプ、

を含む、請求項 1 に記載の液晶表示装置。

【請求項 5】

前記相殺電圧発生部は、

非反転入力端子が前記共通電極の電圧を受け、反転入力端子が前記共通電極歪曲電圧を受け、出力端子が出力電圧を出力する O P アンプ、及び、

前記出力電圧から直流成分を除去して、前記出力電圧の交流成分を前記相殺電圧として出力する直流成分除去部、

を含む、請求項 1 に記載の液晶表示装置。

20

【請求項 6】

前記相殺電圧は、同じ画素領域に含まれる液晶キャパシターとストレージキャパシターとの間の容量比によって決定されることを特徴とする、請求項 1 に記載の液晶表示装置。

【請求項 7】

共通電極、

走査信号を伝送する複数のゲートライン、

前記複数のゲートラインと交差し、データ電圧を伝送する複数のデータライン、

前記共通電極によって覆われ、前記複数のゲートラインと前記複数のデータラインとによってマトリックス状に区切られた複数の画素領域のそれぞれに一つずつ形成され、一端が前記共通電極に連結され、前記共通電極と他端との間の電圧に応じて光を透過する複数の液晶キャパシター、

前記複数の画素領域のそれぞれに一つずつ形成され、いずれかのゲートラインから伝送される走査信号に従ってターンオンして、同じ画素領域の液晶キャパシターの他端をいずれかのデータラインに連結する複数のスイッチング素子、及び、

前記複数の画素領域のそれぞれに一つずつ形成され、一端が同じ画素領域の液晶キャパシターの他端に連結されている複数のストレージキャパシター、

30

を備えた液晶パネル、

を含む液晶表示装置、を駆動する装置であり、

40

データ電圧を前記複数のデータラインに出力するデータドライバー；

走査信号を前記複数のゲートラインに順番に出力するゲートドライバー；

前記共通電極に対して印加される電圧と前記共通電極の実際の電圧との間の差を感じして共通電極歪曲電圧として出力する歪曲感知部；及び、

前記共通電極歪曲電圧の極性を反転させた電圧を相殺電圧として前記複数のストレージキャパシターの他端に出力する相殺電圧発生部；

を含む液晶表示装置の駆動装置。

【請求項 8】

共通電極、

50

走査信号を伝送する複数のゲートライン、

前記複数のゲートラインと交差し、データ電圧を伝送する複数のデータライン、

前記共通電極によって覆われ、前記複数のゲートラインと前記複数のデータラインとによってマトリックス状に区切られた複数の画素領域のそれぞれに一つずつ形成され、一端が前記共通電極に連結され、前記共通電極と他端との間の電圧に応じて光を透過する複数の液晶キャパシター、

前記複数の画素領域のそれぞれに一つずつ形成され、いずれかのゲートラインから伝送される走査信号に従ってターンオンして、同じ画素領域の液晶キャパシターの他端をいずれかのデータラインに連結する複数のスイッチング素子、及び、

前記複数の画素領域のそれぞれに一つずつ形成され、一端が同じ画素領域の液晶キャパシターの他端に連結されている複数のストレージキャパシター、

を備えた液晶パネル、

を含む液晶表示装置、を駆動する方法であり、

前記共通電極に対して電圧を印加する段階；

データ電圧を前記複数のデータラインに対して印加する段階；

走査信号をいずれかのゲートラインに対して印加することによって、そのゲートラインに連結されたスイッチング素子をターンオンさせ、前記複数のデータラインに対して印加されたデータ電圧を、ターンオンしたスイッチング素子を通して同じ画素領域の液晶キャパシターとストレージキャパシターとに対して印加する段階；

前記共通電極に対して印加される電圧と前記共通電極の実際の電圧との間の差を感知して共通電極歪曲電圧として出力する段階；

前記共通電極歪曲電圧の極性を反転させた電圧を相殺電圧として生成する段階；及び、

前記相殺電圧を前記複数のストレージキャパシターの他端に供給する段階；

を含む液晶表示装置の駆動方法。

#### 【請求項 9】

前記相殺電圧は、同じ画素領域に含まれる液晶キャパシターとストレージキャパシターとの間の容量比によって決定されることを特徴とする、請求項 8に記載の液晶表示装置の駆動方法。

#### 【発明の詳細な説明】

##### 【0001】

#### 【発明の属する技術分野】

本発明は、液晶表示装置とその駆動装置及び駆動方法に関し、より詳しくは、共通電極電圧の歪曲によって発生するクロストークを防止するための液晶表示装置とその駆動装置及び駆動方法に関する。

##### 【0002】

#### 【従来の技術】

一般に、液晶表示装置の画質中のクロストーク (CROSSTALK) は、液晶パネルの構造上必然的に発生するものであって、十分に調整されないと画質に悪影響を及ぼす。

##### 【0003】

#### 【発明が解決しようとする課題】

これは、共通電極電圧の歪曲により、データラインを通じて入力される階調電圧と共通電極電圧との差に比例するピクセル充電状態が所望の階調電圧にならないために発生する。また、共通電極電圧の歪曲現象は、LCD内[水平解像度\*3]のデータラインと上板共通電極との間の寄生容量によって発生するもので、データラインの階調電圧がライジング (rising) またはフォーリング (falling) に転移する時、共通電極電圧がライジング電圧やフォーリング電圧にカップリング (coupling) されて発生する。

##### 【0004】

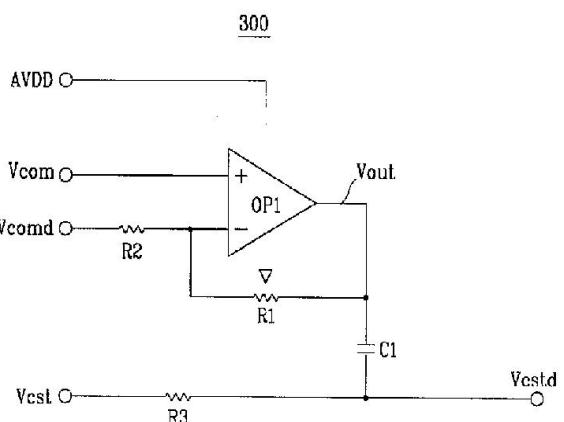

図1はクロストークを説明するための波形図である。

図1を参照すると、階調電圧レベルと共通電極電圧レベルとの間の差による面積に比例してピクセル充電量が決定されるが、データラインに印加される階調電圧波形の振幅が大き

10

20

30

40

50

い場合と小さい場合とでは、図示したように面積 A と面積 B とが異なる。

【 0 0 0 5 】

このような面積差によって中間階調電圧などの充電率が異なるため、クロストーク現象が発生する問題点がある。

本発明の技術と課題は、このような従来の問題点を解決するためのものであって、本発明の目的は、共通電極電圧が歪曲してピクセル電圧の充電率が異なっても、これを補償してピクセル電圧の充電率を同一にし、クロストークの発生防止機能を有する液晶表示装置を提供することにある。

【 0 0 0 6 】

また、本発明の他の目的は、前記クロストークの発生防止機能を有する液晶表示装置の駆動装置を提供することにある。 10

また、本発明の他の目的は、前記クロストークの発生防止機能を有する液晶表示装置の駆動方法を提供することにある。

【 0 0 0 7 】

【課題を解決するための手段】

前記本発明の目的を実現するための一つの特徴による液晶表示装置は、

画像信号を出力するデータドライバーと；

走査信号を順次出力するゲートドライバーと；

前記走査信号の印加に応答して前記画像信号を伝達するスイッチング素子と、一端を通じて印加される画像信号と他端を通じて印加される共通電極電圧との差電圧によって駆動される液晶キャパシターと、前記スイッチング素子のターンオン時に一端を通じて印加される前記画像信号を蓄積し、前記スイッチング素子のターンオフ時に蓄積された画像信号を一端を通じて前記液晶キャパシターに印加するストレージキャパシターとを備えた液晶パネルと； 20

前記液晶キャパシターの他端に印加される共通電極電圧の歪曲分を感知して共通電極歪曲電圧を出力する歪曲感知部と；

前記共通電極歪曲電圧に基づいて前記ストレージキャパシターの充電率を上昇させて過剰充電のための相殺電圧を前記ストレージキャパシターの他端に出力する相殺電圧発生部とを含んでなる。

【 0 0 0 8 】

ここで、歪曲感知部は、前記共通電極電圧が前記液晶パネルに印加される前に所定の経路に設置された感知抵抗を備え、前記感知抵抗の両端間の電位差を感知して共通電極歪曲電圧を出力することを一つの特徴とし、前記共通電極電圧が印加される前記液晶パネルの内部抵抗の両端間の電位差を感知して共通電極歪曲電圧を出力することをまた一つの特徴とする。 30

【 0 0 0 9 】

また、前記相殺電圧発生部は、非反転端を通じて共通電極電圧の提供を受け、反転端を通じて共通電極歪曲電圧の提供を受けて、出力端を通じて相殺電圧を出力する O P アンプを含むことを一つの特徴とし、非反転端を通じて共通電極電圧の提供を受け、反転端を通じて共通電極歪曲電圧の提供を受けて、出力端を通じて出力電圧を出力する O P アンプ、及び前記出力電圧に含まれる直流成分を除去して交流成分の相殺電圧を出力する直流成分除去部からなることをまた一つの特徴とする。 40

【 0 0 1 0 】

この時、前記相殺電圧は、前記共通電極歪曲電圧の位相と反転する位相を有すること一つのを特徴とし、前記液晶キャパシターと前記ストレージキャパシターとの容量比によって生成されることをまた一つの特徴とする。

また、前記本発明の他の目的を実現するための一つの特徴による液晶表示装置の駆動装置は、ゲートラインとデータラインとによって囲まれた領域に形成され、前記それぞれのゲートライン及びデータラインに連結されたスイッチング素子と、前記スイッチング素子のターンオン動作によって共通電極電圧と前記データ電圧とに比例するピクセル電圧によっ 50

て光を透過する液晶キャパシターと、前記スイッチング素子のターンオン時に前記データ電圧を蓄積し、前記スイッチング素子のターンオフ時に蓄積されたデータ電圧を前記液晶キャパシターに印加するストレージキャパシターとを備えたLCDパネルを含む液晶表示装置の駆動装置において、

画像信号を前記データラインに出力するデータドライバーと；

走査信号を前記ゲートラインに順次出力するゲートドライバーと；

前記液晶キャパシターの他端に印加される共通電極電圧の歪曲分を感知して共通電極歪曲電圧を出力する歪曲感知部と；

前記共通電極歪曲電圧に基づいて前記ストレージキャパシターの充電率を上昇させて過剰充電のための相殺電圧を前記ストレージキャパシターの他端に出力する相殺電圧発生部とを含んでなる。

#### 【0011】

また、前記本発明の他の目的を実現するための一つの特徴による液晶表示装置の駆動方法は、データライン及びゲートラインに連結されたスイッチング素子と、前記スイッチング素子のターンオン動作によって共通電極電圧とデータ電圧とに比例するピクセル電圧によって光を透過する液晶キャパシターと、一端を通じて前記液晶キャパシターの一端に連結され、前記スイッチング素子のターンオン時に前記データ電圧を蓄積し、前記スイッチング素子のターンオフ時に蓄積されたデータ電圧を前記液晶キャパシターに印加するストレージキャパシターとを備えた液晶表示装置の駆動方法において、

(a) 前記データ電圧を前記データラインに供給する段階と；

(b) 前記データラインに印加されたデータ電圧を液晶キャパシターとストレージキャパシターとのそれぞれの一端を通じて蓄積するように走査信号をゲートラインに供給する段階と；

(c) 共通電極電圧を液晶キャパシターの他端に供給する段階と；

(d) 前記共通電極電圧の歪曲分を感知して共通電極歪曲電圧を出力する段階と；

(e) 前記共通電極歪曲電圧の歪曲分を相殺するための相殺電圧を生成する段階と；

(f) 前記相殺電圧をストレージキャパシターの一端に供給する段階とを含んでなる。

#### 【0012】

このような液晶表示装置とその駆動装置及び駆動方法によると、液晶キャパシターに印加される共通電極電圧の歪曲によって不足する充電率を補償するためにストレージキャパシターを過剰充電させることによって、クロストークが最少化した良質の画質を得ることができる。

#### 【0013】

##### 【発明の実施の形態】

以下、通常の知識を持っている者が本発明を容易に実施することができるよう実施例について説明する。

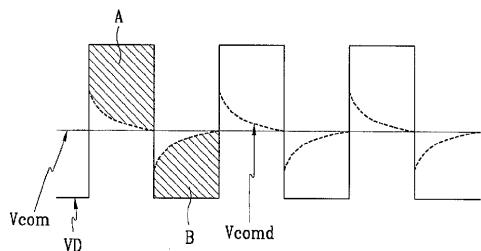

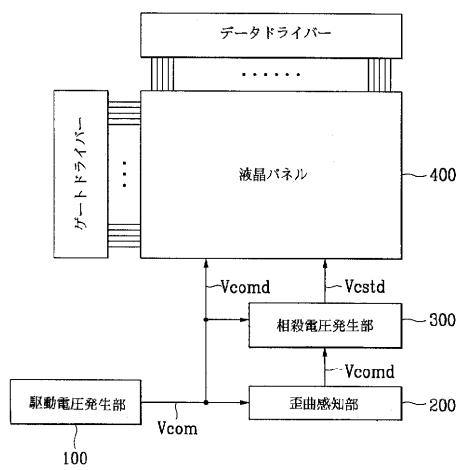

図2は、本発明の実施例による液晶表示装置を説明するための図面であり、図3は、一般に印加される共通電極電圧と本発明によって印加される相殺電圧とを各々説明するための波形図である。特に、図3の(a)は共通電極電圧の波形図であり、(b)は本発明によって印加される相殺電圧の波形図である。

#### 【0014】

図2を参照すると、本発明の実施例による液晶表示装置は、駆動電圧発生部100、歪曲感知部200、相殺電圧発生部300、液晶パネル400、データドライバー及びゲートドライバーを含む。

駆動電圧発生部100は、液晶パネル400内のデータ電圧差の基準となる共通電極電圧(Vcom)を歪曲感知部200、相殺電圧発生部300及び液晶パネル400に各々出力する。

#### 【0015】

歪曲感知部200は、駆動電圧発生部100から共通電極電圧(Vcom)の提供を受けて前記共通電極電圧の歪曲程度を感知して共通電極歪曲電圧(Vcomd)を相殺電圧発生部300

10

20

30

40

50

0に提供する。

相殺電圧発生部300は、駆動電圧発生部100から共通電極電圧(Vcom)の提供を受け、歪曲感知部200から共通電極歪曲電圧(Vcomd)の提供を受けて、相殺電圧(Vcstd)を液晶パネル400に提供する。

【0016】

液晶パネル400は、マトリックスタイルに具現された多数の画素を含み、駆動電圧発生部100から共通電極電圧(Vcom)の提供を受け、相殺電圧発生部300から相殺電圧(Vcstd)の提供を受けて、クロストークが減少した良質の画像をディスプレイする。

より詳しくは、液晶パネルに具現される共通電極ラインには、図3の(a)に図示したように、共通電極歪曲電圧が印加されて液晶キャパシターの充電率不足を招いても、図3の(b)に図示したように、充電率不足を補償することができる相殺電圧を出力することによってクロストークの発生を低減させる。

10

【0017】

以下、前記液晶パネルに一般に印加される共通電極電圧と本発明によって前記共通電極電圧の歪曲を補償するために印加される相殺電圧とについてより詳細に説明する。

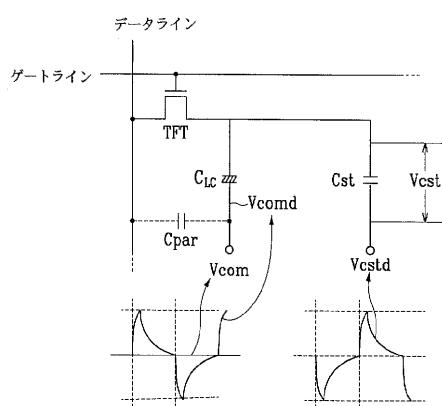

図4は、本発明によって液晶パネルに印加される共通電極電圧と相殺電圧とを説明するための図面であって、液晶パネルに内蔵される画素の等価回路を示す。

【0018】

図4を参照すると、一般に液晶パネルに内蔵される一つの画素領域は、ゲートライン(GATE LINE)とデータライン(DATE LINE)とによって囲まれた領域に形成されたスイッチング素子(TFT)と、液晶キャパシター(C<sub>LC</sub>)と、ストレージキャパシター(C<sub>st</sub>)とを含む。

20

スイッチング素子(TFT)はゲートライン及びデータラインに連結され、液晶キャパシター(C<sub>LC</sub>)はスイッチング素子のターンオン動作によって共通電極電圧(Vcom)とデータ電圧とに比例するピクセル電圧によって所定の光を透過し、ストレージキャパシター(C<sub>st</sub>)はスイッチング素子のターンオン時にデータ電圧を蓄積し、スイッチング素子(TFT)のターンオフ時に蓄積されたデータ電圧を液晶キャパシター(C<sub>LC</sub>)に印加する方式を通じて画像を具現する。

【0019】

しかし、液晶キャパシター(C<sub>LC</sub>)には理想的には正極性のデータ電圧と負極性のデータ電圧との基準となる共通電極電圧(Vcom)が印加されなければならないが、実際にはデータラインと液晶キャパシター(C<sub>LC</sub>)との間の寄生キャパシター(Cpar)によって理想的な共通電極電圧(Vcom)が歪曲されて共通電極歪曲電圧(Vcomd)が印加される。

30

【0020】

このような共通電極歪曲電圧の供給は、データラインを通じて入力される階調電圧と共通電極電圧との差に比例してピクセル充電率が低減されてクロストークが発生する原因となる。このため、本発明では、歪曲される共通電極歪曲電圧を補償するためにストレージキャパシター(Cst)に所定の相殺電圧(Vcstd)を印加する。

【0021】

より詳しくは、既存の共通電極の歪曲によって発生する液晶キャパシター(C<sub>LC</sub>)の充電率不足分をストレージキャパシター(Cst)に過剰充電させる。

40

その結果、一つの画素立場で二つのキャパシター(C<sub>LC</sub>、Cst)による充電率の差によって液晶キャパシター(C<sub>LC</sub>)の充電率不足分を相殺することができる。つまり、階調を表現するためにデータラインに印加される電圧と、これによって発生する共通電極電圧の歪曲程度とを逆位相としてストレージキャパシター(Cst)に印加する。この時、ストレージキャパシター(Cst)に印加される逆位相の歪曲電圧は、液晶キャパシター(C<sub>LC</sub>)とストレージキャパシター(Cst)との容量比によって決定される。

【0022】

例えば、液晶キャパシター(C<sub>LC</sub>)とストレージキャパシター(Cst)との容量比が1:1である場合には、共通電極歪曲電圧に対して同一の大きさと逆位相を有する相殺電圧をス

50

トレージキャパシター (Cst) に印加し、液晶キャパシター ( $C_{LC}$ ) とストレージキャパシター (Cst) との容量比が 2 : 1 である場合には、共通電極歪曲電圧に対して 0.5 倍の大きさと逆位相とを有する相殺電圧をストレージキャパシター (Cst) に印加する。

【0023】

このようにすることによって得られる本発明の効果をより詳細に説明する。

まず、共通電極電圧に歪曲が発生しない理想的な状態であると仮定すれば、一つのピクセルに充電される電荷 ( $Q_0$ ) は下記の数式 1 の通りである。

$$Q_0 = C_{LC} \cdot (Vs - Vcom) + Cst \cdot (Vs - Vcst) \quad \dots \text{(数式 1)}$$

ここで、 $C_{LC}$  は液晶キャパシターのキャパシタンス、Vs は 1 H (または 1 水平時間) の間にデータラインに印加されるデータ電圧、Vcom は歪曲のない共通電極電圧、Cst はストレージキャパシターのキャパシタンス、Vcst は従来のストレージキャパシター (Cst) に印加される電圧である。

【0024】

一方、共通電極電圧に歪曲が発生して一つのピクセルに充電される電荷 ( $Q_1$ ) は下記の数式 2 の通りである。

$$Q_1 = C_{LC} \cdot (Vs - Vcomd) + Cst \cdot (Vs - Vcstd) \quad \dots \text{(数式 2)}$$

ここで、Vcomd は 1 H (または 1 水平時間) の間に発生する共通電極歪曲電圧、Vcstd は相殺電圧である。

【0025】

したがって、歪曲が発生しないピクセルの充電電荷 ( $Q_0$ ) と歪曲が発生したピクセルの充電電荷 ( $Q_1$ ) との間の充電量の差 ( $Q_0 - Q_1$ ) を前記数式 1 と数式 2 に基づいて計算すると下記の数式 3 の通りである。

$$Q_0 - Q_1 = C_{LC} \cdot (Vcomd - Vcom) \quad \dots \text{(数式 3)}$$

このように、充電率の差によって、これに比例する大きさでクロストークが発生する。

【0026】

しかし、本発明によって共通電極歪曲電圧 ( $Vcst$ ) の代わりに相殺電圧 ( $Vcstd$ ) をストレージキャパシター (Cst) に印加すれば、ピクセルに充電される電荷 ( $Q_2$ ) は下記の数式 4 の通りである。

$$Q_2 = C_{LC} \cdot (Vs - Vcomd) + Cst \cdot (Vs - Vcstd) \quad \dots \text{(数式 4)}$$

ここで、 $Vcstd = (C_{LC}/Cst) \cdot (Vcomd - Vcom) + Vcst$  であるので、共通電極電圧の歪曲がない時にピクセルに充電される電荷 ( $Q_0$ ) と比較してみると、下記の数式 5 の通りである。

$$Q_0 - Q_2 = C_{LC} \cdot (Vcomd - Vcom) + Cst \cdot (Vcstd - Vcst) = 0 \quad \dots \text{(数式 5)}$$

前記数式 5 で言及したように、液晶キャパシター (Cst) に印加される共通電極電圧に歪曲が発生しても充電量の差がゼロ (zero) であるのでクロストークの発生を低減させることができる。

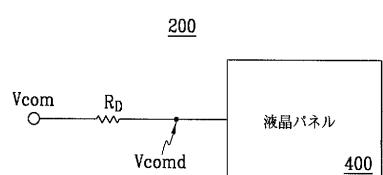

【0027】

図 5 a は前記図 2 の共通電極電圧感知部の一例を説明するための図面である。図 2 と図 5 a とを参照すると、駆動電圧発生部 100 で発生する共通電極電圧 ( $Vcom$ ) が液晶パネル 400 に印加される前に所定の感知抵抗 ( $RD$ ) を設置し、設置された感知抵抗 ( $R_D$ ) の両端間の電位差で共通電極電圧の歪曲量を感知して共通電極歪曲電圧 ( $Vcomd$ ) を相殺電圧発生部 300 に出力する。

【0028】

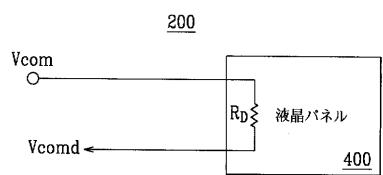

図 5 b は前記図 2 の共通電極電圧感知部の他の一例を説明するための図面である。

図 2 と図 5 b とを参照すると、駆動電圧発生部 100 で発生する共通電極電圧 ( $Vcom$ ) を液晶パネル 400 に印加した後、液晶パネル 400 の内部抵抗を感知抵抗 ( $R_D$ ) として両端間の電位差で共通電極電圧の歪曲量を感知して共通電極歪曲電圧 ( $Vcomd$ ) を相殺電圧発生部 300 に出力する。

【0029】

以下、前記図 5 a、b で感知された共通電極歪曲電圧 ( $Vcomd$ ) に基づいて相殺電圧を発

10

20

30

40

50

生する相殺電圧発生部の一例を説明する。

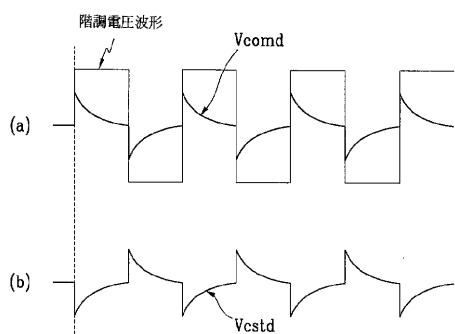

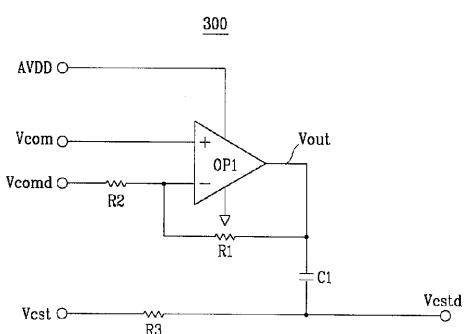

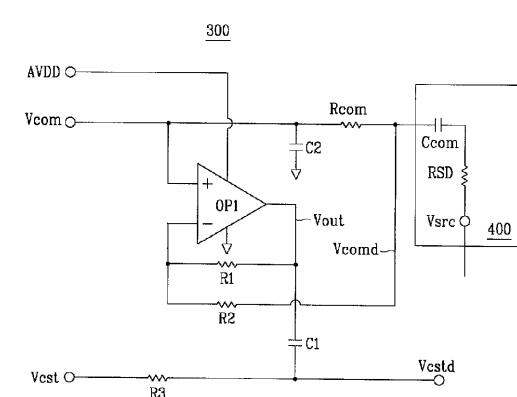

図6 aは前記図2の相殺電圧発生部の一例を説明するための図面である。

図6 aを参照すると、本発明の一例による相殺電圧発生部は、電源電圧(AVDD)の提供を受けて駆動される第1OPアンプ(OP1)と、第1乃至第3抵抗(R1、R2、R3)と、第1キャパシター(C1)とを含む。

#### 【0030】

より詳しくは、第1OPアンプ(OP1)の非反転入力端は共通電極電圧(Vcom)に連結され、反転入力端は並列連結された第1抵抗(R1)と第2抵抗(R2)とに連結されるが、この時、第1抵抗(R1)はフィードバック抵抗として第1OPアンプ(OP1)の出力端に連結され、第2抵抗(R2)は感知された共通電極歪曲電圧(Vcomd)に連結される。

10

#### 【0031】

動作時、第1OPアンプ(OP1)の反転入力端は第2抵抗(R2)を通じて感知された共通電極歪曲電圧(Vcomd)の入力を受けて出力端を通じて出力電圧(Vout)を出力し、前記出力電圧(Vout)は第1キャパシター(C1)を通じてDC成分が除去され、AC成分だけが伝達されて相殺電圧(Vcstd)をストレージキャパシター(Cst)の他端に出力する。

#### 【0032】

前記図6 aによる相殺電圧発生部の具体的な動作を数式によって説明する。

まず、図6 aに示したOPアンプの特性は下記の式6のように整理できる。 $Vout = - (R1/R2) \cdot Vcomd + (1 + (R1/R2)) \cdot Vcom$  ... (式6)

また、共通電極歪曲電圧(Vcomd)はAC成分とDC成分とが含まれるので、下記の式7のように整理できる。

20

$$Vcomd = Vcomd (AC) + Vcomd (DC)$$

$$= Vcomd (AC) + Vcom ... (式7)$$

したがって、前記式7を前記式6に代入して整理すると、出力電圧(Vout)は下記の式8のようになる。

$$Vout = - (R1/R2) [Vcomd (AC) + Vcom] + (1 + (R1/R2)) Vcom = - (R1/R2) \cdot Vcomd (AC) + R1/R2 \cdot Vcom ... (式8)$$

ここで、 $<- R1/R2 \cdot Vcomd (AC) >$ 項はAC成分であり、 $<R1/R2 \cdot Vcom>$ 項はDC成分であるが、前記出力電圧(Vout)は第1キャパシター(C1)を経由するため、第1キャパシター(C1)と第3抵抗(R3)によるストレージキャパシターの充電電圧(Vcst)へのレベルシフト回路にはAC成分である $<- R1/R2 \cdot Vcomd (AC) >$ 成分だけが伝達される。

30

#### 【0033】

もちろん、共通電極電圧(Vcom)と同一な大きさのストレージキャパシターの充電電圧(Vcst)をストレージキャパシター(Cst)に印加しようとする場合には、前記DC成分のフィルタリング過程なしで出力電圧(Vout)をストレージキャパシター(Cst)の他端に直接印加することもできる。

前記図6 aによる回路を液晶パネルに適用した等価回路を図6 bに図示する。

#### 【0034】

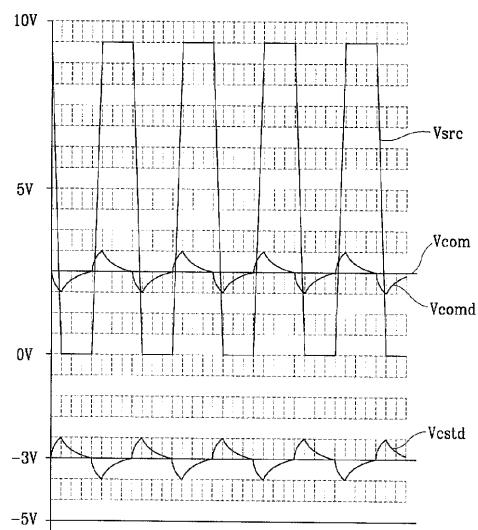

図6 bは本発明の実施例による液晶表示装置の等価回路図である。

図6 bを参照すると、本発明による液晶パネルの等価回路で、Vsrcはデータドライバーの出力電圧がデータラインに印加される波形であり、これは寄生キャパシターであるCcom(またはCpar)によって共通電極とカップリングされる。これは、DC成分である共通電極電圧を共通電極歪曲電圧のように歪曲させ、共通電極歪曲電圧は所定の比率(R1/R2)で反転増幅されてストレージキャパシター充電電圧(Vcst)に第1キャパシター(C1)を通じてACの歪曲成分だけが伝達され、これによって相殺電圧(Vcstd)にはストレージキャパシター充電電圧(Vcst)基準に共通電極歪曲電圧が加えられてクロストーク補償用電圧が作られる。

40

#### 【0035】

図7は、前記図6 bのシミュレーション結果を説明するための波形図であって、特に、第1抵抗(R1)と第2抵抗(R2)とを同一にした場合、つまり、液晶キャパシター(CLC)

50

の容量とストレージキャパシター ( $C_{st}$ ) の容量とを同一と仮定した場合の補償波形図である。

図 6 b と図 7 とを参照すると、データラインに印加されるデータ電圧 ( $V_{src}$ ) の波形とカップリングされて共通電極電圧 ( $V_{com}$ ) が歪曲される現象を確認することができ、共通電極歪曲電圧 ( $V_{comd}$ ) のAC成分とは逆位相でストレージキャパシター ( $C_{st}$ ) に印加される相殺電圧 ( $V_{cstd}$ ) 波形が発生することが確認できる。

#### 【0036】

もし、液晶キャパシター ( $C_{LC}$ ) の容量とストレージキャパシター ( $C_{st}$ ) の容量とを相異するように設計する場合、第 1 抵抗と第 2 抵抗との比率を液晶キャパシター ( $C_{LC}$ ) とストレージキャパシター ( $C_{st}$ ) との容量比に設定すれば最適の補償波形が発生し得る。

10

以上で説明したように、本発明は、液晶キャパシターに印加される共通電極電圧の歪曲程度が異なっても同一なピクセル電圧充電率を有するようにするものであって、特に、従来の共通電極の歪曲によって発生する液晶キャパシターの充電率不足をストレージキャパシターに過剰充電されるようにし、ピクセル側では液晶キャパシターとストレージキャパシターとによる充電率の差によって液晶キャパシターの充電率不足分を相殺するため、共通電極電圧の歪曲程度が異なっても同一なピクセル電圧充電率を維持してクロストークを防止することができる。

#### 【0037】

前記では本発明の好ましい実施例を参照して説明したが、該当技術分野の熟練した当業者であれば、特許請求の範囲に記載された本発明の思想及び領域から逸脱しない範囲内で本発明を多様に修正及び変更させることができる。

20

#### 【0038】

##### 【発明の効果】

以上で説明したように、本発明によれば、液晶キャパシターに印加される共通電極電圧の歪曲によって不足する充電率を補償するためにストレージキャパシターを過剰充電させることによって、クロストークが最少化された良質の画質を得ることができる。

##### 【図面の簡単な説明】

【図 1】 クロストークを説明するための波形図である。

【図 2】 本発明の実施例による液晶表示装置を説明するための図面である。

【図 3】 一般に印加される共通電極電圧と本発明によって印加される相殺電圧とを各々説明するための波形図である。

30

【図 4】 本発明によって液晶パネルに印加される共通電極電圧と相殺電圧とを説明するための図面である。

【図 5 a】 前記図 2 の共通電極電圧感知部の一例を説明するための図面である。

【図 5 b】 前記図 2 の共通電極電圧感知部の他の一例を説明するための図面である。

【図 6 a】 前記図 2 の相殺電圧発生部の一例を説明するための図面である。

【図 6 b】 本発明の実施例による液晶表示装置の等価回路図である。

【図 7】 前記図 6 b のシミュレーション結果を説明するための図面である。

##### 【符号の説明】

100 駆動電圧発生部

40

200 歪曲感知部

300 相殺電圧発生部

400 液晶パネル

【図1】

【図2】

【図3】

【図4】

【図5 a】

【図5 b】

【図6 a】

【図6 b】

【図7】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 9 G 3/20 6 4 2 P

(72)発明者 文 勝 煥

大韓民国ソウル市瑞草区蠶院洞70番地新盤浦4次アパート210棟404号

審査官 一宮 誠

(56)参考文献 特開平06-027899 (JP, A)

特開2000-330518 (JP, A)

特許第3196998 (JP, B2)

特開平02-000089 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00 - 3/38

G02F 1/133

|                |                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置，驱动装置及其驱动方法                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP4157727B2</a>                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2008-10-01 |

| 申请号            | JP2002159667                                                                                                                                                                                                                                                                                                          | 申请日     | 2002-05-31 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                              |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 文勝煥                                                                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 文勝煥                                                                                                                                                                                                                                                                                                                   |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                           |         |            |

| CPC分类号         | G09G3/3655 G09G2300/0876 G09G2310/06 G09G2320/0204 G09G2320/0209                                                                                                                                                                                                                                                      |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.611.D G09G3/20.611.J G09G3/20.624.D G09G3/20.642.P                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NC18 2H093/NC34 2H093/NC35 2H093/NC58 2H093/NC65 2H093/ND15 2H193 /ZA04 2H193/ZF59 2H193/ZH21 2H193/ZH40 5C006/AC25 5C006/AC27 5C006/AF50 5C006/AF54 5C006/AF64 5C006/BB16 5C006/BF25 5C006/BF38 5C006/FA25 5C080/AA10 5C080/BB05 5C080 /DD10 5C080/FF01 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 |         |            |

| 审查员(译)         | 一宮诚                                                                                                                                                                                                                                                                                                                   |         |            |

| 优先权            | 1020010059319 2001-09-25 KR                                                                                                                                                                                                                                                                                           |         |            |

| 其他公开文献         | JP2003108100A                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                             |         |            |

## 摘要(译)

要解决的问题：通过补偿像素电压的充电率的变化来提供具有串扰防止功能的液晶显示装置，即使在由于像素电压的充电率变化的情况下也具有相同的像素电压充电率公共电极电压的失真。解决方案：液晶显示装置具有液晶电容器，该液晶电容器由通过一端施加的图像信号和通过另一端施加的公共电极电压之间的差电压驱动，并且存储电容器施加存储的图像信号。开关元件通过一端离开液晶电容器。在液晶显示装置中，失真感测部分施加到液晶电容器另一端的公共电极电压的失真分量并输出公共电极失真电压，并且偏移电压产生部分提高充电率。存储电容器基于公共电极失真电压并输出电压以抵消过量充电到存储电容器的另一端。

## 【図 6 a】