(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-128907

(P2009-128907A)

(43) 公開日 平成21年6月11日(2009.6.11)

(51) Int.Cl.

G02F 1/1343 (2006.01)

G02F 1/1368 (2006.01)

F 1

G02F 1/1343

G02F 1/1368

テーマコード(参考)

2 H 0 9 2

審査請求 有 請求項の数 9 O L (全 11 頁)

(21) 出願番号 特願2008-265126 (P2008-265126)

(22) 出願日 平成20年10月14日 (2008.10.14)

(31) 優先権主張番号 10-2007-0120233

(32) 優先日 平成19年11月23日 (2007.11.23)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 501426046

エルジー ディスプレイカンパニー リ

ミテッド

大韓民国 ソウル, ヨンドゥンパーク, ヨ

イドードン 20

(74) 代理人 100110423

弁理士 曾我 道治

(74) 代理人 100084010

弁理士 古川 秀利

(74) 代理人 100094695

弁理士 鈴木 憲七

(74) 代理人 100111648

弁理士 梶並 順

(74) 代理人 100147566

弁理士 上田 俊一

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】本発明は、データ配線の数を減少させて製造費用を減らすことができるとともに、画質を維持することができる液晶表示装置を提供する。

【解決手段】本発明の液晶表示装置は、多数のピクセルが定義された基板と、基板上に第1方向に配列されて、多数のピクセルを2列ごとに分割する多数のデータ配線と、基板上に第1方向と交差する第2方向に配列される複数のゲート配線と、各ピクセル上に配置されて、ゲート配線及びデータ配線と電気的に繋がった薄膜トランジスタと、各ピクセル上に配置されて、薄膜トランジスタと電気的に繋がったピクセル電極と、絶縁膜を間にしてゲート配線と隣接するピクセル電極と重なり、ピクセル電極とゲート配線間の寄生キャパシタンスを減らすための補償電極とを含む。

【選択図】図2 a

**【特許請求の範囲】****【請求項 1】**

多数のピクセルが定義された基板と、

前記基板上に第1方向に配列されて、前記多数のピクセルを2列ごとに分割する多数のデータ配線と、

前記基板上に前記第1方向と交差する第2方向に配列される複数のゲート配線と、

前記各ピクセル上に配置されて、前記ゲート配線及び前記データ配線と電気的に繋がった薄膜トランジスタと、

前記各ピクセル上に配置されて、前記薄膜トランジスタと電気的に繋がったピクセル電極と、

絶縁膜を間にして前記ゲート配線と隣接する前記ピクセル電極と重なり、前記ピクセル電極と前記ゲート配線間の寄生キャパシタンスを減らすための補償電極と

を含む液晶表示装置。

**【請求項 2】**

前記補償電極は、前記ゲート配線及び前記データ配線のうちのいずれかと同一層に配置されることを特徴とする請求項1に記載の液晶表示装置。

**【請求項 3】**

前記データ配線によって分割され、かつ前記第2方向に隣接する2つのピクセル間のそれにおいて、前記データ配線と平行し、絶縁膜を間にして前記ピクセル電極と重なることでストレージキャパシターを形成するストレージ電極部を具備する共通配線を更に含むことを特徴とする請求項1に記載の液晶表示装置。

**【請求項 4】**

前記補償電極と前記共通配線は、一体で構成されたことを特徴とする請求項3に記載の液晶表示装置。

**【請求項 5】**

前記ゲート配線と平行して、絶縁膜を間にて前記ピクセル電極と重なることでストレージキャパシターを形成するストレージ電極部を具備する共通配線を更に含むことを特徴とする請求項1に記載の液晶表示装置。

**【請求項 6】**

前記補償電極と前記共通配線は、一体で構成されたことを特徴とする請求項5に記載の液晶表示装置。

**【請求項 7】**

前記共通配線は、メッシュ形態を持つことを特徴とする請求項5に記載の液晶表示装置。

**【請求項 8】**

前記ゲート配線を間にて隣接する2つのピクセルにそれぞれ配置された共通配線を相互電気的に連結する連結パターンを含むことを特徴とする請求項5に記載の液晶表示装置。

**【請求項 9】**

前記連結パターンは、前記ピクセル電極と同一層上に配置されることを特徴とする請求項8に記載の液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、液晶表示装置に関するもので、より具体的には、画質を維持して製造費用を節減することができる液晶表示装置に関するものである。

**【背景技術】****【0002】**

今日、液晶表示装置は、消費電力が低く、携帯性に優れており、技術集約的で、付加価値が高い次世代先端ディスプレー素子として脚光を浴びている。

**【0003】**

液晶表示装置は、液晶の光学的異方性を利用した表示装置として、液晶に電界を印加して液晶の光透過率を調節することで、多様な映像を表示する。

**【0004】**

図1は、従来液晶表示装置の概略的な平面図である。

**【0005】**

図1を参照すれば、液晶表示装置は、映像を表示する液晶パネル10、液晶パネル10に走査信号を印加するゲート駆動部20、及び液晶パネル10に画素電圧を印加するデータ駆動部30を含む。

**【0006】**

液晶パネル10は、相互に対向する第1基板及び第2基板と、両基板間に介在する液晶層を含む。

10

**【0007】**

第1基板上に、多数のゲート配線21と多数のデータ配線31が相互に交差して定義された多数のピクセルを含む。ゲート配線21は、ゲート駆動部20と電気的に繋がっている。データ配線31は、データ駆動部30と電気的に繋がっている。

**【0008】**

ゲート駆動部20は、ゲート配線21に順次、走査信号を出力し、データ駆動部30は、ゲート配線21に走査信号が印加される区間に応じて選択されたゲート配線21に電気的に接続されたピクセルに、画素電圧を供給する。

20

**【0009】**

ゲート配線21とデータ配線31の数は、液晶表示装置の解像度によって変わる。例えば、液晶表示装置の解像度が $1024 \times 768$ である場合、データ配線31は、 $1024 \times 3$ 個が第1基板上に配置される。また、ゲート配線21は、768個が第1基板上に配置される。

**【0010】**

最近、液晶表示装置の解像度は、増加する傾向にあり、液晶表示装置に具備されたデータ配線もますます増加する。これに連れて、ゲート配線21とデータ配線31の数と同じ数のチャンネルを持つように、データIC及びゲートICの数も増加する。従って、液晶表示装置の解像度が増加するに伴って、製作費用が増加するという問題点がある。

30

**【0011】**

また、液晶表示装置で、垂直方向に形成されるデータ配線31は、ゲート配線21に比べて本数が多く、ぎっしりと配列されるので、データ配線31間の間隔確保が困難であり、液晶表示装置の誤動作を起こすことがある。

**【発明の開示】****【発明が解決しようとする課題】****【0012】**

本発明の1つの課題は、データ配線の数を減少させて製造費用を減らすことができる液晶表示装置を提供することにある。

**【0013】**

本発明のもう1つの課題は、液晶表示装置の画質を維持することができる液晶表示装置を提供することにある。

40

**【課題を解決するための手段】****【0014】**

前記技術的課題を解決するために、本発明の液晶表示装置は、多数のピクセルが定義された基板と、前記基板上に第1方向に配列されて、前記多数のピクセルを2列ごとに分割する多数のデータ配線と、前記基板上に前記第1方向と交差する第2方向に配列される複数のゲート配線と、前記各ピクセル上に配置されて、前記ゲート配線及び前記データ配線と電気的に繋がった薄膜トランジスタと、前記各ピクセル上に配置されて、前記薄膜トランジスタと電気的に繋がったピクセル電極と、絶縁膜を間にして前記ゲート配線と隣接す

50

る前記ピクセル電極と重なり、前記ピクセル電極と前記ゲート配線間の寄生キャパシタンスを減らすための補償電極とを含む。

## 【0015】

前記液晶表示装置は、共通配線を更に含むことができる。

## 【0016】

前記共通配線は、前記データ配線によって分割され、かつ前記第2方向に隣接する2つのピクセル間のそれぞれにおいて、前記データ配線と平行し、絶縁膜を間にして前記ピクセル電極と重なることでストレージキャパシターを形成するストレージ電極部を具備することができる。

## 【0017】

または、前記共通配線は、前記ゲート配線と平行して、絶縁膜を間にして前記ピクセル電極と重なることでストレージキャパシターを形成するストレージ電極部を具備することができる。

## 【0018】

前記共通配線と前記補償電極は、一体で構成されることができる。

## 【0019】

前記共通配線は、メッシュ形態を持つことができる。

## 【発明の効果】

## 【0020】

本発明によれば、液晶表示装置のデータ配線数を減少させて製造費用を減らすとともに、画質特性の低下を防止することができる。

## 【発明を実施するための最良の形態】

## 【0021】

以下、本発明の実施例を液晶表示装置の図面を参照して詳細に説明する。以下に紹介される実施例は、本発明の思想が充分に伝達されるようにするために、一例として開示されるものである。よって、本発明は、以下で説明される実施例に限定されるのではなく、他の形態で具体化されることもできる。また、図面において、装置の大きさ及び厚さなどは、説明の便宜を図り、誇張されて表現されることもある。明細書全体にかけて、同一参照番号は、同一構成要素を現わす。

## 【0022】

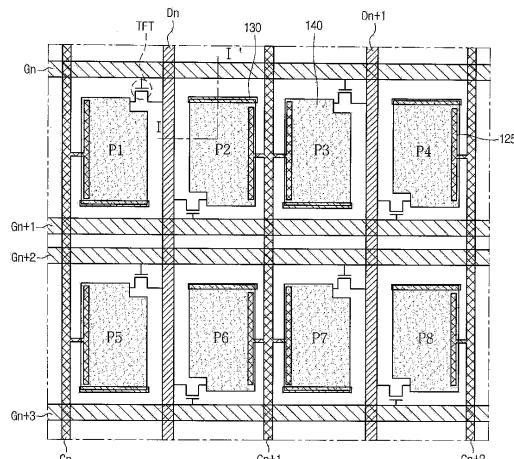

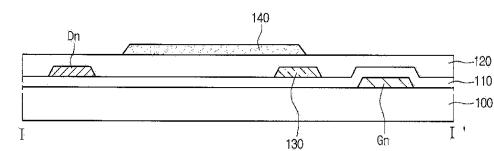

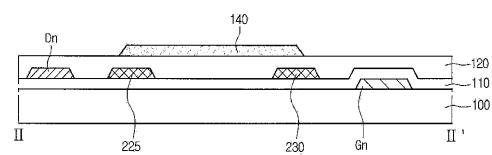

図2a及び図2bは、本発明の第1実施例による液晶表示装置の説明をするために図示した図面である。図2aは、本発明の第1実施例による液晶表示装置の一部のピクセルを図示した平面図である。図2bは、図2aに図示されたI-I'ラインに沿って切断した断面図である。

## 【0023】

図2a及び図2bを参照すれば、液晶表示装置は、液晶パネル(図示していない)と、液晶パネルに外部から電気的信号を供給するデータドライバー(図示していない)及びゲートドライバーを含む。

## 【0024】

液晶パネルは、映像を表示するための多数のピクセルP1～P8を含む。また、液晶パネルは、第1基板100、第2基板(図示していない)及び第1基板及び第2基板間に介在する液晶を含む。

## 【0025】

第1基板100上に、第1方向に配列された多数のデータ配線Dn、Dn+1が配置されている。データ配線Dn、Dn+1は、多数のピクセルP1～P8を少なくとも第1方向に沿って2列ごとに分割する。例えば、第1データ配線Dnは、左右に接続された2つのピクセルである第1ピクセルP1及び第2ピクセルP2に、画素電圧(またはデータ電圧信号)を印加できる。よって、データ配線Dn、Dn+1は、同一解像度の液晶表示装置に具備されたデータ配線の数に比べて、半分に減らすことができる。

## 【0026】

10

20

30

40

50

第1基板100上に、第1方向と交差する第2方向に配列された多数のゲート配線G<sub>n</sub>、G<sub>n+1</sub>、G<sub>n+2</sub>、G<sub>n+3</sub>が配置されている。すなわち、データ配線D<sub>n</sub>、D<sub>n+1</sub>と多数のゲート配線G<sub>n</sub>、G<sub>n+1</sub>、G<sub>n+2</sub>、G<sub>n+3</sub>は、相互に交差して、多数のピクセルP<sub>1</sub>～P<sub>8</sub>を定義することができる。例えば、第1データ配線D<sub>n</sub>及び第2データ配線D<sub>n+1</sub>と、第1ゲート配線G<sub>n</sub>及び第2ゲート配線G<sub>n+1</sub>とによって区画された領域には、二つのピクセルである第2ピクセルP<sub>2</sub>及び第3ピクセルP<sub>3</sub>が配置される。すなわち、第1ゲート配線G<sub>n</sub>及び第2ゲート配線G<sub>n+1</sub>の間に、第2ピクセルP<sub>2</sub>及び第3ピクセルP<sub>3</sub>が配置される。

## 【0027】

各ピクセルP<sub>1</sub>～P<sub>8</sub>には、薄膜トランジスタ及び薄膜トランジスタと電気的に繋がったピクセル電極140が配置されている。10

## 【0028】

薄膜トランジスタは、ゲート配線G<sub>n</sub>、G<sub>n+1</sub>、G<sub>n+2</sub>、G<sub>n+3</sub>から分岐したゲート電極、ゲート絶縁膜を間にしてゲート電極と重なった半導体パターン、半導体パターン上に配置されてデータ配線D<sub>n</sub>、D<sub>n+1</sub>と電気的に繋がったソース電極、及び半導体パターン上に配置されてソース電極と離隔されたドレーン電極を含む。

## 【0029】

ここで、同一ラインに属した、例えば、第1ピクセルP<sub>1</sub>、第2ピクセルP<sub>2</sub>、第3ピクセルP<sub>3</sub>及び第4ピクセルP<sub>4</sub>は、薄膜トランジスタを通じて隣接した第1ゲート配線G<sub>n</sub>及び第2ゲート配線G<sub>n+1</sub>に交互に繋がるようになる。20

## 【0030】

この時、同一ラインに属した、例えば、第1ピクセルP<sub>1</sub>、第2ピクセルP<sub>2</sub>、第3ピクセルP<sub>3</sub>及び第4ピクセルP<sub>4</sub>は、電気的に接続された第1ゲート配線G<sub>n</sub>及び第2ゲート配線G<sub>n+1</sub>を通じて、順次、印加される走査信号によって選択されて、第1データ配線D<sub>n</sub>及び第2データ配線D<sub>n+1</sub>は、走査信号によって選択されたピクセルで画素電圧を繰り返し供給する。よって、第1ピクセル～第4ピクセルP<sub>4</sub>を含む同一ライン上のピクセルに、半分ずつ、順次、データラインD<sub>n</sub>、D<sub>n+1</sub>からの画素電圧を入力する。

## 【0031】

しかし、同一ラインに属した、例えば、第1ピクセルP<sub>1</sub>～第4ピクセルP<sub>4</sub>は、異なるキックバック電圧( V<sub>p</sub> )を持つことができる。ここで、キックバック電圧とは、ピクセルに供給された画素電圧とピクセルに実質的に充電された電圧との差を言う。30

## 【0032】

このように、異なるキックバック電圧は、同一ラインに属したピクセル中、半分が自体の一側と隣接したゲートラインに接続されたピクセル電極を含み、残りのピクセルが自他の他側と隣接したゲートラインに接続されたピクセル電極を含むことによって印加される。例えば、第1ピクセル～第4ピクセルP<sub>4</sub>の中で、第1ゲート配線G<sub>n</sub>と隣接するピクセル電極140を持つ第2ピクセルP<sub>2</sub>及び第4ピクセルP<sub>4</sub>と、第2ゲート配線G<sub>n+1</sub>と隣接するピクセル電極140を持つ第1ピクセルP<sub>1</sub>及び第3ピクセルP<sub>3</sub>とは、異なるキックバック電圧を持つ。

## 【0033】

すなわち、第1ゲート配線G<sub>n</sub>と第1ピクセルP<sub>1</sub>及び第3ピクセルP<sub>3</sub>のピクセル電極140との間に形成される寄生キャパシタンスと、第2ゲート配線G<sub>n+1</sub>と第2ピクセルP<sub>2</sub>及び第4ピクセルP<sub>4</sub>のピクセル電極140との間に形成される寄生キャパシタンスとの差が発生することで、同一ラインに属したピクセルに発生するキックバック電圧の差が発生する。これにより、液晶表示装置は、フリッカー現象及び色感の差のような画質が低下することがある。40

## 【0034】

各ピクセルP<sub>1</sub>～P<sub>8</sub>のキックバック電圧の差を減らすためには、ゲート配線G<sub>n</sub>、G<sub>n+1</sub>、G<sub>n+2</sub>、G<sub>n+3</sub>と隣接するピクセル電極140の間に発生する寄生キャパシタンスを減らさなければならない。50

## 【0035】

このためには、ゲート配線  $G_n$ 、 $G_{n+1}$ 、 $G_{n+2}$ 、 $G_{n+3}$  と各ピクセル  $P_1 \sim P_8$  に配置されたピクセル電極 140 との間隔を増加させることが考えられるが、これにより開口率が低下することがある。

## 【0036】

従って、開口率の減少を防止した上で、ゲート配線  $G_n$ 、 $G_{n+1}$ 、 $G_{n+2}$ 、 $G_{n+3}$  と隣接するピクセル電極 140 の間に発生する寄生キャパシタンスを減らすために、ゲート配線  $G_n$ 、 $G_{n+1}$ 、 $G_{n+2}$ 、 $G_{n+3}$  と隣接するピクセル電極 140 上に補償電極 130 を形成する。補償電極 130 は、ピクセル電極 140 と絶縁膜を間に重なる。この時、補償電極 130 は、ピクセル電極 140 のエッジ部を覆うようにする。補償電極 130 は、フローティングされていることがある。よって、補償電極 130 は、ゲート配線  $G_n$ 、 $G_{n+1}$ 、 $G_{n+2}$ 、 $G_{n+3}$  と隣接するピクセル電極 140 の間に配置され、その間で発生する電界を遮蔽することによって、ゲート配線  $G_n$ 、 $G_{n+1}$ 、 $G_{n+2}$ 、 $G_{n+3}$  と隣接するピクセル電極 140 の間に発生する寄生キャパシタンスの形成を減少或いは防止する役割をする。

10

## 【0037】

また、補償電極 130 は、ゲート配線  $G_n$ 、 $G_{n+1}$ 、 $G_{n+2}$ 、 $G_{n+3}$  を間に重ね、相互に隣り合うピクセル電極 140 の間の寄生キャパシターの形成を防止することができる。

20

## 【0038】

補償電極 130 は、ゲート配線  $G_n$ 、 $G_{n+1}$ 、 $G_{n+2}$ 、 $G_{n+3}$  及びデータ配線  $D_n$ 、 $D_{n+1}$  のうち、どれか 1 つと同一層に配置されることがある。

20

## 【0039】

補償電極 130 がゲート配線  $G_n$ 、 $G_{n+1}$ 、 $G_{n+2}$ 、 $G_{n+3}$  と同一層に配置される場合、絶縁膜は、ゲート絶縁膜 110 と保護膜 120 で構成されることがある。これにより、補償電極 130 を、第 1 基板 100 上に配置させることができる。補償電極 130 は、ゲート配線  $G_n$ 、 $G_{n+1}$ 、 $G_{n+2}$ 、 $G_{n+3}$  と同一材質で構成することができる。

## 【0040】

一方、補償電極 130 がデータ配線  $D_n$ 、 $D_{n+1}$  と同一層に配置される場合、図 2 b に図示しているように、絶縁膜は、保護膜 120 で構成されることがある。これにより、補償電極 130 を、ゲート絶縁膜 110 上に配置させることができる。補償電極 130 は、データ配線  $D_n$ 、 $D_{n+1}$  と同一材質で構成することができる。

30

## 【0041】

よって、補償電極 130 は、ゲート配線  $G_n$ 、 $G_{n+1}$ 、 $G_{n+2}$ 、 $G_{n+3}$  及びデータ配線  $D_n$ 、 $D_{n+1}$  のうち、どれか 1 つを形成する工程と一緒に形成されるように設計することによって、補償電極 130 を形成するための別途の工程を追加しなくても良い。

## 【0042】

更に、データ配線  $D_n$ 、 $D_{n+1}$  によって 2 列ごとに分割されたピクセルの間に、データ配線  $D_n$ 、 $D_{n+1}$  と平行する共通配線  $C_n$ 、 $C_{n+1}$ 、 $C_{n+2}$  を配置させることができる。共通配線  $C_n$ 、 $C_{n+1}$ 、 $C_{n+2}$  は、データ配線  $D_n$ 、 $D_{n+1}$  と同一層、例えば、ゲート絶縁膜 110 上に配置させることができる。

40

## 【0043】

共通配線  $C_n$ 、 $C_{n+1}$ 、 $C_{n+2}$  は、保護膜 120 を間に重ねてピクセル電極 140 と重なることでストレージキャパシターを形成するストレージ電極部 125 を具備することができる。

## 【0044】

図面には示されてないが、第 2 基板の内側面に、特定の波長をフィルタリングするカラーフィルタパターンと、ピクセル電極 140 と液晶を駆動するための電界を形成する共通電極とを配置させることができる。

50

## 【0045】

よって、本発明の実施例による液晶表示装置は、データ配線を従来に比べて半分に減少させることができ、製造費用を減らすことができる。

## 【0046】

また、本発明の実施例による液晶表示装置は、補償電極を具備することで、ゲート配線とピクセル電極との間に形成される寄生キャパシタンスを減らすことができる。よって、液晶表示装置の全てのピクセルに、一定のキックバック電圧を持たせることができ、液晶表示装置の画質不良を防止することができる。

## 【0047】

本発明の実施例で、各ピクセルに配置された薄膜トランジスタは、ジグザグの形態で配列させた例で説明したが、これに限定されるのではなく、多様な形態で配列させることができる。

## 【0048】

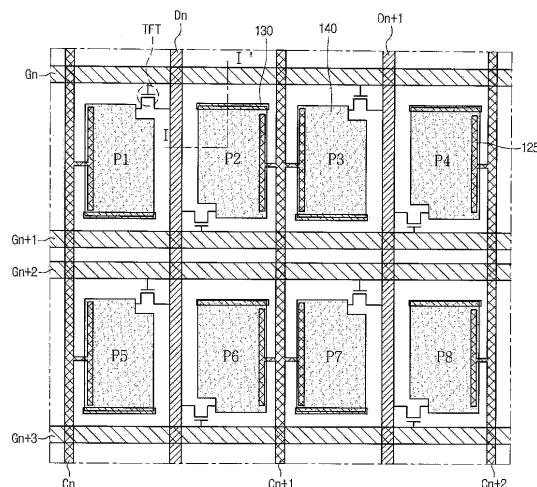

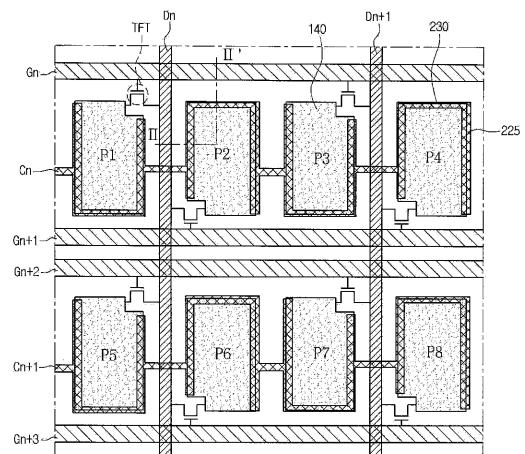

図3a及び図3bは、本発明の第2実施例による液晶表示装置を説明するために図示した図面である。図3aは、本発明の第2実施例による液晶表示装置の一部のピクセルを図示した平面図である。図3bは、図3aに図示されたII-II'ラインに沿って切断した断面図である。本発明の第2実施例は、補償電極及び共通配線を除いて、前で説明した本発明の第1実施例による液晶表示装置と同一構成を持つ。よって、本発明の第2実施例では、本発明の第1実施例と重なる説明は、省略することにして、同一構成に対しては、同一参照符号を付与する。

10

20

## 【0049】

図3a及び図3bを参照すれば、液晶表示装置は、多数のピクセルが定義された第1基板100を含む。第1基板100上に、多数のピクセルを2列ごとに分割する多数のデータ配線を具備することで、本発明の第2実施例の液晶表示装置は、同じ解像度を持つ従来の液晶表示装置に比べて、データ配線の数を半分に減らすことができる。

## 【0050】

液晶表示装置は、ピクセル電極140とゲート配線Gn、Gn+1、Gn+2、Gn+3との間の寄生キャパシタンスを減らすための補償電極230を含む。よって、液晶表示装置の全てのピクセルに、一定のキックバック電圧を持たせることができ、液晶表示装置の画質不良を防止することができる。

30

## 【0051】

液晶表示装置は、ゲート配線Gn、Gn+1、Gn+2、Gn+3と平行する共通配線Cn、Cn+1を含む。共通配線Cn、Cn+1は、ゲート配線Gn、Gn+1、Gn+2、Gn+3と同一層に同一材質で構成することができる。

## 【0052】

共通配線Cn、Cn+1は、絶縁膜、例えば、ゲート絶縁膜110及び保護膜120の二重膜を間にし、ピクセル電極140と重なることでストレージキャパシターを形成するストレージ電極部225を具備する。ストレージ電極部225は、ピクセル電極140のエッジ部に配置させることができる。

## 【0053】

ストレージ電極部225は、補償電極230と一体で構成することができる。すなわち、補償電極230は、共通配線Cn、Cn+1と一体で構成することができる。よって、補償電極230は、ピクセル電極140とゲート配線Gn、Gn+1、Gn+2、Gn+3との間に形成された寄生キャパシタンスを減少させ、各ピクセルP1～P8にストレージキャパシターを形成することができる。

40

## 【0054】

よって、本発明の第2実施例による補償電極230は、共通配線Cn、Cn+1と一緒に形成でき、ピクセル電極140とゲート配線Gn、Gn+1、Gn+2、Gn+3との間に形成された寄生キャパシタンスを減少させると同時に、各ピクセルP1～P8に画素電圧を充電する役割を同時に行うことができる。

50

## 【0055】

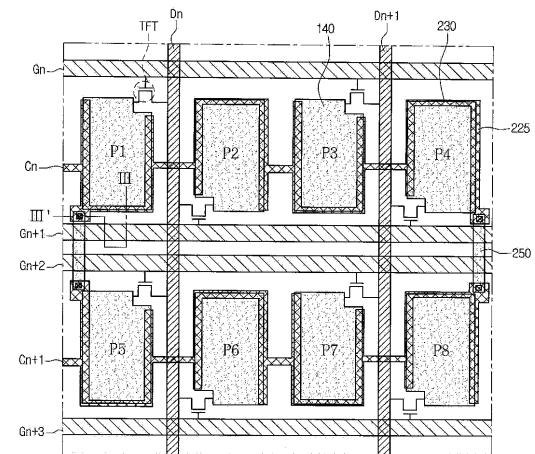

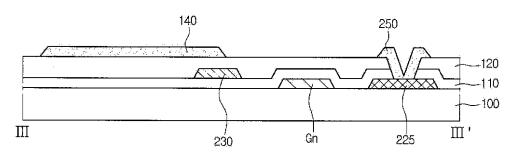

図4a及び図4bは、本発明の第3実施例による液晶表示装置を説明するために図示した図面である。図4aは、本発明の第3実施例による液晶表示装置の一部のピクセルを図示した平面図である。図4bは、図4aに図示されたI I I - I I I' ラインに沿って切断した断面図である。本発明の第3実施例は、連結パターンを除いて、前で説明した本発明の第2実施例による液晶表示装置と同一構成を持つ。よって、本発明の第3実施例は、本発明の第2実施例と重なる説明は、省略することにして、同一構成に対しては、同一参考符号を付与する。

## 【0056】

図4a及び図4bを参照すれば、液晶表示装置は、ピクセル電極140とゲート配線Gn、Gn+1、Gn+2、Gn+3との間の寄生キャパシタンスを減らすための補償電極230を含む。補償電極230は、ゲート配線Gn、Gn+1、Gn+2、Gn+3と平行する共通配線Cn、Cn+1と一緒に構成することができる。10

## 【0057】

共通配線Cn、Cn+1は、各ピクセルを横断しつつ配置させることができる。すなわち、共通配線Cn、Cn+1は、データ配線Dn、Dn+1を間に隙り合う2つのピクセルの間に配置される。

## 【0058】

連結パターン250は、ゲート配線Gn、Gn+1、Gn+2、Gn+3を間に隙りして相互に隣接して配置されたストレージ電極部225を相互に電気的に連結させる。ゲート配線Gn、Gn+1、Gn+2、Gn+3を間に隙りして相互に隣接した共通配線Cn、Cn+1は、連結パターン250によって相互に電気的に連結させることができる。共通配線Cn、Cn+1は、メッシュ形態を持つことができる。よって、共通配線Cn、Cn+1の抵抗値を下げることができ、共通配線Cn、Cn+1のストレージ電極部225とピクセル電極140との間に形成されるストレージキャパシターのキャパシタンスを向上させることができる。20

## 【0059】

連結パターン250は、ピクセル電極140と同一層上に配置させることができる。また、ピクセル電極140と同一材質で構成することができる。よって、連結パターン250は、ピクセル電極140と同一工程で形成されるように設計することによって、別途の工程の追加なしにストレージキャパシターのキャパシタンスを向上させることができる。30

## 【0060】

本発明の第3実施例で、共通配線Cn、Cn+1のメッシュ単位は、8個のピクセル、例えば、第1ピクセルP1～第8ピクセルP8を含むもので説明したが、これに限定されるのではない。例えば、共通配線Cn、Cn+1のメッシュ単位は、2つのピクセルまたは、4つのピクセルを含むこともできる。

## 【0061】

上述したように、本発明の液晶表示装置は、1つのデータ配線に2列分のピクセルが接続されることによって、従来に比べてデータ配線数を半分に減らすことができると共に、データICの数も減るようになり、液晶表示装置の製造費用を減らすことができる。40

## 【0062】

また、本発明の液晶表示装置は、絶縁膜を間に隙りゲート配線と隣接したピクセル電極の一部と重なる補償電極を具備することによって、ゲート配線とピクセル電極との間に形成される寄生キャパシタンスを減らすことができる。よって、液晶表示装置の全てのピクセルに、一定のキックバック電圧を持たせることができ、液晶表示装置の画質不良を防止することができる。

## 【0063】

また、本発明の液晶表示装置の補償電極は、ゲート配線、データ配線、共通配線のうちのどれか1つと同一層に形成することによって、補償電極を形成するための別途の工程を追加しなくても良い。50

## 【0064】

また、本発明の液晶表示装置の補償電極は、共通配線と一体で形成し、共通配線は、メッシュタイプに形成することによって、共通配線の抵抗値を下げることができる。

## 【図面の簡単な説明】

## 【0065】

【図1】従来液晶表示装置の概略的な平面図である。

【図2a】本発明の第1実施例による液晶表示装置の一部のピクセルを図示した平面図である。

10

【図2b】図2aに図示されたI-I'に沿って切断した断面図である。

【図3a】本発明の第2実施例による液晶表示装置の一部のピクセルを図示した平面図である。

15

【図3b】図3aに図示されたII-II'線に沿って切断した断面図である。

【図4a】本発明の第3実施例による液晶表示装置の一部のピクセルを図示した平面図である。

20

【図4b】図4aに図示されたIII-III'線に沿って切断した断面図である。

## 【符号の説明】

## 【0066】

100 第1基板、110 ゲート絶縁膜、120 保護膜、130、230 補償電極、140 ピクセル電極、125、225 ストレージ電極部、Dn、Dn+1 データ配線、Gn、Gn+1、Gn+2、Gn+3 ゲート配線。

20

【図1】

【図2a】

【図2b】

【図3a】

【図3b】

【図4a】

【図4b】

---

フロントページの続き

(72)発明者 ジュンホ・パク

大韓民国、キョンサンブク - ド、クミ - シ、クピョン - ドン、プヨン・アパートメント 306 -

104

F ターム(参考) 2H092 GA23 GA64 JA24 JB02 JB22 JB24 JB31 JB66 JB69 NA23

NA27

|                |                                                                                                                                                                                                                   |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP2009128907A</a>                                                                                                                                                                                     | 公开(公告)日 | 2009-06-11 |

| 申请号            | JP2008265126                                                                                                                                                                                                      | 申请日     | 2008-10-14 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                          |         |            |

| 申请(专利权)人(译)    | Eruji显示有限公司                                                                                                                                                                                                       |         |            |

| [标]发明人         | ジュンホ・パク                                                                                                                                                                                                           |         |            |

| 发明人            | ジュンホ・パク                                                                                                                                                                                                           |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368                                                                                                                                                                                             |         |            |

| CPC分类号         | G02F1/136286 G02F2001/13606 G02F2001/136218 G09G3/3648 G09G2300/0426 G09G2300/043 G09G2320/0219                                                                                                                   |         |            |

| FI分类号          | G02F1/1343 G02F1/1368                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 2H092/GA23 2H092/GA64 2H092/JA24 2H092/JB02 2H092/JB22 2H092/JB24 2H092/JB31 2H092 /JB66 2H092/JB69 2H092/NA23 2H092/NA27 2H092/JB41 2H192/AA24 2H192/CC24 2H192/CC62 2H192/DA15 2H192/DA73 2H192/GA02 2H192/GA03 |         |            |

| 代理人(译)         | 英年古河<br>Kajinami秩序<br>上田俊一                                                                                                                                                                                        |         |            |

| 优先权            | 1020070120233 2007-11-23 KR                                                                                                                                                                                       |         |            |

| 其他公开文献         | <a href="#">JP5269540B2</a>                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                         |         |            |

### 摘要(译)

本发明的目的是提供一种液晶显示装置，其能够减少数据线的数量以降低制造成本并保持图像质量。根据本发明的液晶显示装置包括：基板，其上限定有多个像素；沿第一方向布置在基板上并且将多个像素划分为两列的多条数据线；以及基板。在与上述第一方向相交的第二方向上布置的多个栅极布线，布置在每个像素上，电连接到栅极布线和数据布线并布置在每个像素上的薄膜晶体管。电连接到薄膜晶体管的像素电极和与相邻于栅极线的像素电极交叠的补偿电极，其间插入有绝缘膜，以减小像素电极和栅极线之间的寄生电容。[选择图]图2a