(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-106745

(P2006-106745A)

(43) 公開日 平成18年4月20日(2006.4.20)

|                                        |                                                                                                      |             |

|----------------------------------------|------------------------------------------------------------------------------------------------------|-------------|

| (51) Int.CI.                           | F 1                                                                                                  | テーマコード (参考) |

| <b>G09G 3/36 (2006.01)</b>             | G09G 3/36                                                                                            | 2 H 093     |

| <b>G02F 1/133 (2006.01)</b>            | G02F 1/133 550                                                                                       | 5 C 006     |

| <b>G09G 3/20 (2006.01)</b>             | G02F 1/133 510                                                                                       | 5 C 080     |

|                                        | G02F 1/133 525                                                                                       |             |

|                                        | G09G 3/20 624B                                                                                       |             |

| 審査請求 未請求 請求項の数 21 O L (全 21 頁) 最終頁に続く  |                                                                                                      |             |

| (21) 出願番号 特願2005-290598 (P2005-290598) | (71) 出願人 390019839                                                                                   |             |

| (22) 出願日 平成17年10月3日 (2005.10.3)        | 三星電子株式会社                                                                                             |             |

| (31) 優先権主張番号 10-2004-0078279           | Samsung Electronics                                                                                  |             |

| (32) 優先日 平成16年10月1日 (2004.10.1)        | C o., L t d.                                                                                         |             |

| (33) 優先権主張国 韓国 (KR)                    | 大韓民国京畿道水原市靈通区梅灘洞416<br>416, Maetan-dong, Yeongtong-gu, Suwon-si<br>Gyeonggi-do, Republic<br>of Korea |             |

|                                        | (74) 代理人 110000051                                                                                   |             |

|                                        | 特許業務法人共生国際特許事務所                                                                                      |             |

|                                        | (72) 発明者 季龍淳                                                                                         |             |

|                                        | 大韓民国忠清南道天安市木川面應院里セグアンエンリッヂビル107棟<br>404号                                                             |             |

|                                        | 最終頁に続く                                                                                               |             |

(54) 【発明の名称】 液晶表示装置及びその駆動方法

## (57) 【要約】

【課題】 駆動回路のチップ数を減らし、液晶表示装置の製造コストを削減する。さらに、液晶表示装置の画質を向上させる。

【解決手段】 本発明に係る液晶表示素子は、一行の画素に対し二つのゲート線、二列の画素に対し一つのデータ線が割り当てられる。偶数番目ゲート線に接続された第1ゲート駆動部と、奇数番目ゲート線に接続された第2ゲート駆動部とを備え、第1ゲート駆動部が所定時間約1/2H先に駆動されて、ゲートオン電圧を当該ゲート線に印加する。これによって、偶数番目ゲート線と奇数番目ゲート線に1/2Hの間隔で交互にゲートオン電圧が印加され、各ゲートオン電圧は1Hの間隔印加される。この結果、1Hのうち前半1/2Hの間は、直前の当該ゲート線にゲートオン電圧が印加されるデータ電圧によって予備充電され、後半1/2Hの間に自身の当該データ電圧によって本充電される。

【選択図】図8

**【特許請求の範囲】****【請求項 1】**

行方向に交互に配置され、第1スイッチング素子を有する複数の第1画素と、第2スイッチング素子を有する複数の第2画素とを各々含む複数の画素行と、

前記画素行の上側に行方向に配置され、前記第1スイッチング素子または前記第2スイッチング素子に第1ゲートオン電圧を印加する複数の第1ゲート線と、

前記画素行の下側に行方向に配置され、前記第2スイッチング素子または前記第1スイッチング素子に第2ゲートオン電圧を印加する複数の第2ゲート線と、

前記第1ゲート線及び前記第2ゲート線に交差し、隣接した一対の第1及び第2画素の間に各々配置され、前記第1及び第2画素にデータ電圧を印加する複数のデータ線と、

前記複数の第1ゲート線に前記第1ゲートオン電圧を印加する第1ゲート駆動部と、

前記複数の第2ゲート線に前記第2ゲートオン電圧を印加する第2ゲート駆動部と、

前記データ電圧を前記データ線に印加するデータ駆動部とを備え、

前記第2ゲートオン電圧が前記第1ゲートオン電圧よりも所定時間先に印加されることを特徴とする液晶表示装置。

**【請求項 2】**

前記所定時間が1/2Hであることを特徴とする請求項1に記載の液晶表示装置。

**【請求項 3】**

複数の制御信号を出力して前記第1及び第2ゲート駆動部及び前記データ駆動部を制御する信号制御部をさらに備え、

前記複数の制御信号は、前記第1ゲート駆動部に印加される第1垂直同期開始信号及び第1ゲートクロック信号と前記第2ゲート駆動部に印加される第2垂直同期開始信号及び第2ゲートクロック信号を有することを特徴とする請求項2に記載の液晶表示装置。

**【請求項 4】**

前記信号制御部は、前記第1垂直同期開始信号にパルスを生成してから1/2Hが経過した後、前記第2垂直同期開始信号にパルスを生成することを特徴とする請求項3に記載の液晶表示装置。

**【請求項 5】**

前記第1ゲートオン電圧及び前記第2ゲートオン電圧は各々1Hの間印加されることを特徴とする請求項4に記載の液晶表示装置。

**【請求項 6】**

前記第1ゲートオン電圧は、前記第2ゲートオン電圧と1/2Hの間重畳することを特徴とする請求項5に記載の液晶表示装置。

**【請求項 7】**

隣接した二つのデータ線の間行方向に配列されている第1及び第2画素(単位画素群)は、同一なデータ線に接続されていることを特徴とする請求項1に記載の液晶表示装置。

**【請求項 8】**

列方向に隣接した画素は互いに異なるデータ線に接続されていることを特徴とする請求項7に記載の液晶表示装置。

**【請求項 9】**

前記単位画素群において前記第1及び第2スイッチング素子の形成位置は異なり、前記第1スイッチング素子と前記第2スイッチング素子は互いに異なるゲート線に接続されていることを特徴とする請求項8に記載の液晶表示装置。

**【請求項 10】**

同一な画素行において、隣接した単位画素群の第1及び第2スイッチング素子の形成位置が同一であることを特徴とする請求項9に記載の液晶表示装置。

**【請求項 11】**

隣接した画素列において、隣接した単位画素群の第1及び第2スイッチング素子の形成位置が異なることを特徴とする請求項10に記載の液晶表示装置。

**【請求項 12】**

10

20

30

40

50

前記液晶表示装置は、前記各画素に対応する領域に赤色、緑色、または青色のカラーフィルタをさらに有し、

前記カラーフィルタはストライプ状に配置されていることを特徴とする請求項1に記載の液晶表示装置。

【請求項13】

交互に配列されている複数の第1及び第2画素を各々含む複数の画素行、前記複数の第1画素及び第2画素の上側に配置され、前記第1画素または第2画素に第1ゲートオン電圧を印加する複数の第1ゲート線、前記複数の第1画素及び第2画素の下側に配置され、前記第2画素または前記第1画素に第2ゲートオン電圧を印加する複数の第2ゲート線、前記第1ゲート線及び前記第2ゲート線に交差し、隣接した一対の第1及び第2画素の間に各々配置され、前記第1及び第2画素にデータ電圧を印加する複数のデータ線、前記複数の第1ゲート線に前記第1ゲートオン電圧を印加する第1ゲート駆動部、前記複数の第2ゲート線に前記第2ゲートオン電圧を印加する第2ゲート駆動部、並びに前記データ電圧を前記データ線に印加するデータ駆動部を備える液晶表示装置の駆動方法であって、

前記第2ゲート駆動部で前記第2ゲートオン電圧を前記第2ゲート線に印加する段階と、

該当するデータ電圧を当該画素に印加する段階と、

前記第2ゲートオン電圧が印加された後、所定時間が経過したとき、前記第1ゲート駆動部で前記第1ゲートオン電圧を前記第1ゲート線に印加する段階と、並びに

該当するデータ電圧を当該画素に印加する段階と、を含むことを特徴とする液晶表示装置の駆動方法。

【請求項14】

前記所定時間は1/2Hであることを特徴とする請求項13に記載の液晶表示装置の駆動方法。

【請求項15】

前記第1ゲートオン電圧及び前記第2ゲートオン電圧は各々1Hの間印加されることを特徴とする請求項14に記載の液晶表示装置の駆動方法。

【請求項16】

前記第1ゲートオン電圧は、前記第2ゲートオン電圧と1/2Hの間重畳することを特徴とする請求項15に記載の液晶表示装置の駆動方法。

【請求項17】

スイッチング素子を備え、一つの色相を表す複数の画素からなる少なくとも一つの画素行と、

前記スイッチング素子に接続され、前記画素行の下上に配置され、前記スイッチング素子をターンオンするゲートオン電圧を伝達する複数対のゲート線と、

前記スイッチング素子に接続され、二つの画素列の間に配置され、データ電圧を伝達する複数のデータ線とを有し、

1 一つの画素行において、同一な色相を表す隣接した画素は、同じ画素列または前記同じ画素列と同一な色相の画素列に印加されるデータ電圧で予備充電されることを特徴とする液晶表示装置。

【請求項18】

一つの画素行において隣接した二つのデータ線の間に形成されている二つの画素は、同一なデータ線に接続されていることを特徴とする請求項17に記載の液晶表示装置。

【請求項19】

下上に隣接した二つの画素は、互いに異なるデータ線に接続されていることを特徴とする請求項18に記載の液晶表示装置。

【請求項20】

前記液晶表示装置は、前記各画素に対応する領域に赤色、緑色、または青色のカラーフィルタをさらに有し、前記カラーフィルタはストライプ状に配置されていることを特徴とする請求項19に記載の液晶表示装置。

10

20

30

40

50

**【請求項 21】**

各データ線に沿って流れるデータ電圧の極性が同一であることを特徴とする請求項 20 に記載の液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は液晶表示装置及びその駆動方法に関する。

**【背景技術】****【0002】**

一般的な液晶表示装置は、画素電極及び共通電極が備えられた二つの表示板と、その間に挟持される誘電率異方性を有する液晶層を含む。画素電極は、行列状に配列されて薄膜トランジスタ（TFT）などのスイッチング素子に接続され、一行ずつ順次データ電圧を印加される。共通電極は、表示板の全面に亘って形成されており、共通電圧を印加される。画素電極と共に共通電極及びその間の液晶層は、回路的には液晶キャパシタをなし、液晶キャパシタは、これに接続されたスイッチング素子と共に画素を構成する基本単位になる。

**【0003】**

このような液晶表示装置は、二つの電極に電圧を印加して液晶層に電界を生成し、この電界の強さを調節して、液晶層を通過する光の透過率を調節することによって所望の画像を得る。この時、液晶層に一方向の電界が長く印加されることによって発生する劣化現象を防止するため、フレーム毎に、行毎に、または画素毎に共通電圧に対するデータ電圧の極性を反転させる。

**【0004】**

なお、液晶表示装置は、スイッチング素子を制御するためのゲート信号を伝達するゲート線と電界生成電極に印加するためのデータ電圧を伝達するデータ線、並びにゲート信号とデータ電圧を生成するゲート駆動部とデータ駆動部を備える。ゲート駆動部とデータ駆動部は、複数の駆動集積回路チップからなるのが一般的であり、該チップ数を減らすことが生産コストを削減するために必要な重要な要素である。特に、データ駆動集積回路チップは、ゲート駆動回路チップに比べて値段が高いため、その数を減らすことが要求されている。

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

本発明の目的は、駆動回路のチップ数を減らし、液晶表示装置の製造コストを削減することである。本発明の他の目的は、液晶表示装置の画質向上させることである。

**【課題を解決するための手段】****【0006】**

本発明の特徴による液晶表示装置は、行方向に交互に配置されており、第1スイッチング素子を備えた複数の第1画素と、第2スイッチング素子を備えた複数の第2画素とを各々含む複数の画素行、前記画素行の上側に行方向に配置され、前記第1スイッチング素子または前記第2スイッチング素子に第1ゲートオン電圧を印加する複数の第1ゲート線、前記画素行の下側に行方向に配置され、前記第2スイッチング素子または前記第1スイッチング素子に第2ゲートオン電圧を印加する複数の第2ゲート線、前記第1ゲート線及び前記第2ゲート線に交差し、隣接した一対の第1及び第2画素の間に各々配置され、前記第1及び第2画素にデータ電圧を印加する複数のデータ線、前記複数の第1ゲート線に前記第1ゲートオン電圧を印加する第1ゲート駆動部、前記複数の第2ゲート線に前記第2ゲートオン電圧を印加する第2ゲート駆動部、並びに前記データ電圧を前記データ線に印加するデータ駆動部を有し、前記第2ゲートオン電圧が前記第1ゲートオン電圧より所定時間先に印加される。この時、所定時間は1/2Hであるのが良い。

**【0007】**

前記液晶表示装置は、複数の制御信号を出力して前記第1及び第2ゲート駆動部及び前記データ駆動部を駆動する。

10

20

30

40

50

記データ駆動部を制御する信号制御部をさらに有し、前記複数の制御信号は、前記第1ゲート駆動部に印加される第1垂直同期開始信号及び第1ゲートクロック信号と前記第2ゲート駆動部に印加される第2垂直同期開始信号及び第2ゲートクロック信号を含むことができる。

この場合、前記信号制御部は、前記第1垂直同期開始信号にパルスを生成してから1/2Hが経過した後に、前記第2垂直同期開始信号にパルスを生成することが好ましい。

#### 【0008】

前記第1ゲートオン電圧及び前記第2ゲートオン電圧は各々1Hの間印加され、前記第1ゲートオン電圧は、前記第2ゲートオン電圧と1/2Hの間重畠することができる。

隣接した二つのデータ線間に行方向に配列されている第1及び第2画素（単位画素群）10は、同一なデータ線に接続されているのが良く、列方向に隣接した画素は、互いに異なるデータ線に接続されているのが良い。

前記単位画素群において、前記第1及び第2スイッチング素子の形成位置は異なり、前記第1スイッチング素子と前記第2スイッチング素子は互いに異なるゲート線に接続されていることが好ましい。また、同一な画素行において、隣接した単位画素群の第1及び第2スイッチング素子の位置は同一であるのが良い。

隣接した画素列において、隣接した単位画素群の第1及び第2スイッチング素子の位置は異なることが好ましい。

前記特徴による液晶表示装置は、前記各画素に対応する領域に赤色、緑色、または青色のカラーフィルタをさらに有し、前記カラーフィルタは、ストライプ状に配置されるのが良い。20

#### 【0009】

本発明の他の特徴による液晶表示装置の駆動方法は、交互に配列されている複数の第1及び第2画素を各々含む複数の画素行、前記複数の第1画素及び第2画素の上側に配置されて前記第1画素または第2画素に第1ゲートオン電圧を印加する複数の第1ゲート線、前記複数の第1画素及び第2画素の下側に配置されて前記第2画素または前記第1画素に第2ゲートオン電圧を印加する複数の第2ゲート線、前記第1ゲート線及び前記第2ゲート線に交差し、隣接した一対の第1及び第2画素の間に各々配置されて前記第1及び第2画素にデータ電圧を印加する複数のデータ線、前記複数の第1ゲート線に前記第1ゲートオン電圧を印加する第1ゲート駆動部、前記複数の第2ゲート線に前記第2ゲートオン電圧を印加する第2ゲート駆動部、並びに前記データ電圧を前記データ線に印加するデータ駆動部を有する液晶表示装置の駆動方法であって、前記第2ゲート駆動部から前記第2ゲートオン電圧を前記第2ゲート線に印加する段階、該当するデータ電圧を当該画素に印加する段階、前記第2ゲートオン電圧が印加されてから所定の時間が経過した時、前記第1ゲート駆動部から前記第1ゲートオン電圧を前記第1ゲート線に印加する段階、並びに該当するデータ電圧を当該画素に印加する段階を有する。30

#### 【0010】

この時、前記所定時間は1/2Hであるのが良い。

また、前記第1ゲートオン電圧及び前記第2ゲートオン電圧は、各々1Hの間印加されるのが良く、前記第1ゲートオン電圧は、前記第2ゲートオン電圧と1/2Hの間重畠することが好ましい。40

#### 【0011】

本発明の他の特徴による液晶表示装置は、スイッチング素子を備え、一つの色相を表す複数の画素からなる少なくとも一つの画素行、前記スイッチング素子に接続されており、前記画素行の下上に配置され、前記スイッチング素子をターンオンさせるゲートオン電圧を伝達する複数対のゲート線、並びに前記スイッチング素子に接続されており、二つの画素列の間に配置され、データ電圧を伝達する複数のデータ線を有し、一つの画素行で同一な色相を表す隣接した画素は、同じ画素列または前記同じ画素列と同一な色相の画素列に印加されるデータ電圧によって予備充電される。

#### 【0012】

10

20

30

40

50

前記特徴において、一つの画素行で隣接した二つのデータ線の間に形成されている二つの画素は、同一なデータ線に接続されているのが良く、下上に隣接した二つの画素は、互いに異なるデータ線に接続されているのが良い。

前記特徴による液晶表示装置は、前記各画素に対応する領域に赤色、緑色、または青色のカラーフィルタをさらに有し、前記カラーフィルタは、ストライプ状に配置されているのが良い。この時、各データ線に沿って流れるデータ電圧の極性が同一であるのが良い。

#### 【発明の効果】

#### 【0013】

二つの画素が一つのデータ線を共有するようにし、データ線の個数を減少させることで、それに接続された高価のデータ駆動回路チップ数も減らし、表示装置の製造コストを大きく削減できる。10

また、隣接した画素行間にスイッチング素子が接続されたデータ線の位置を変更し、たとえば駆動部反転が列反転方式であっても見掛け反転が $1 \times 2$ ドット反転になることができるようにして、データ駆動部から列反転方式でデータ電圧の極性が決定されて印加されるので、データ線の材料を選択できる幅が大きくなり、製造工程を単純化し易く、見掛け反転がドット反転であるので画質が向上する。

#### 【0014】

各画素行の上側に形成された奇数番目ゲート線よりも各画素行の下側に形成された偶数番目ゲート線に先にゲートオン電圧を印加する方法で全ゲート線を走査する。これによって、一つの画素行において同じ色相の画素が同一な色相のデータ電圧で予備充電され、予備充電量が互いに異なるために生じる縦筋模様が減少し、その結果表示装置の画質が向上する。20

#### 【発明を実施するための最良の形態】

#### 【0015】

添付した図面を参照して、本発明の実施形態を、本発明が属する技術分野における通常の知識を有する者が容易に実施することができるよう詳細に説明する。しかし、本発明は、多様な形態で実現することができ、ここで説明する実施形態に限定されない。

#### 【0016】

本発明の実施形態に係る液晶表示装置及びその駆動方法について図面を参照して詳細に説明する。30

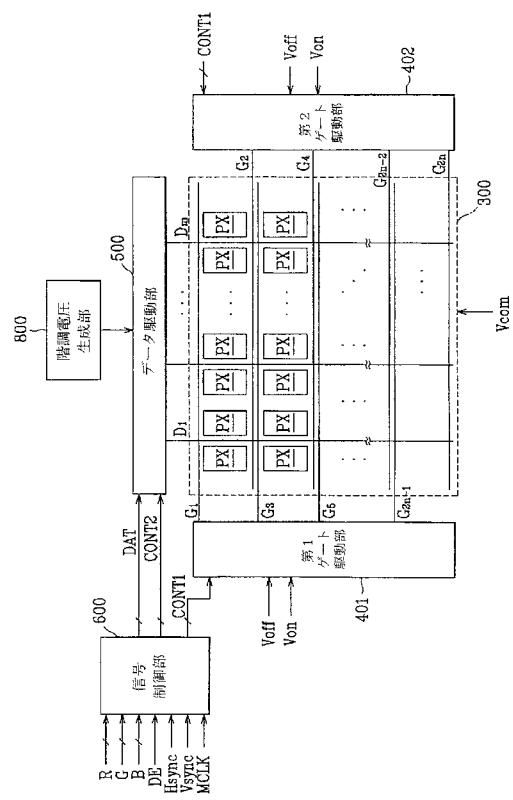

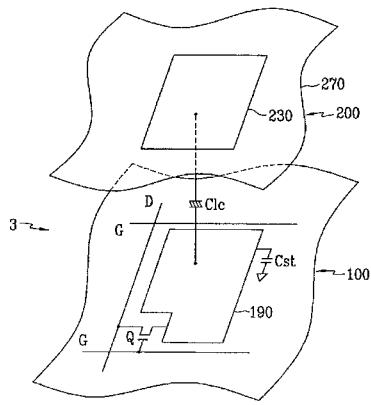

図1は、本発明の一実施形態に係る液晶表示装置のブロック図であり、図2は、本発明の一実施形態に係る液晶表示装置の一画素に対する等価回路図である。図3は、本発明の一実施形態に係る液晶表示装置の構造図である。

図1に示すように、本発明の一実施形態に係る液晶表示装置は、液晶表示板組立体300及びこれに接続された第1ゲート駆動部401、第2ゲート駆動部402とデータ駆動部500、データ駆動部500に接続された階調電圧生成部800、並びにこれらを制御する信号制御部600を有する。

#### 【0017】

液晶表示板組立体300は、等価回路によれば、複数の表示信号線 $G_1 - G_{2n}$ 、 $D_1 - D_m$ 、 $L_1$ 、 $L_2$ （ここで、 $n = 1, 2, 3, \dots$ 、 $m = 1, 2, 3, \dots$ ）と、これに接続されてほぼ行列状に配列された複数の画素（PX）を有する。40

表示信号線 $G_1 - G_{2n}$ 、 $D_1 - D_m$ 、 $L_1$ 、 $L_2$ は、ゲート信号（走査信号ともいう）を伝達する複数のゲート線 $G_1 - G_{2n}$ と、データ信号を伝達するデータ線 $D_1 - D_m$ 及びダミー線 $L_1$ 、 $L_2$ を有する。ゲート線 $G_1 - G_{2n}$ はほぼ行方向に延びて、互いにほぼ平行であり、データ線 $D_1 - D_m$ とダミー線 $L_1$ 、 $L_2$ はほぼ列方向に延びて、互いにほぼ平行である。

#### 【0018】

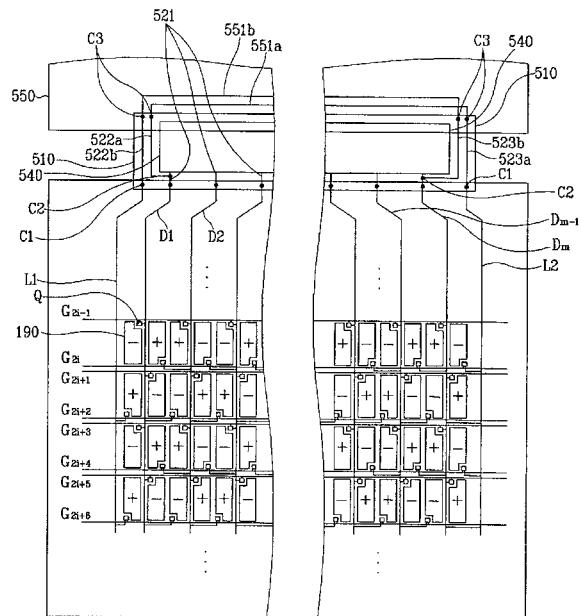

図3に示すように、ゲート線 $G_1 - G_{2n}$ 、データ線 $D_1 - D_m$ 及びダミー線 $L_1$ 、 $L_2$ が備えられた液晶表示板組立体300の上側には、液晶表示装置を駆動するための信号制御部600、駆動電圧生成部700（図示しない）及び階調電圧生成部800などの回50

路要素が備えられている印刷回路基板（PCB）550が位置している。ダミー線L1は液晶表示板組立体300の最左側周縁付近に、また、ダミー線L2は液晶表示板組立体300の最右側周縁付近にほぼ行方向に延びてデータ線D<sub>1</sub> - D<sub>m</sub>とほぼ平行である。

#### 【0019】

液晶表示板組立体300とPCB550は、可撓性回路（FPC）基板510を介して互いに電気的、物理的に接続されている。

この可撓性回路基板510には、データ駆動部500を構成するデータ駆動集積回路チップ540が装着されており、複数のデータ伝達線521が形成されている。このデータ伝達線521は、接触部C1を介して液晶表示板組立体300上に形成された複数のデータ線D<sub>1</sub> - D<sub>m</sub>に各々接続され、該当するデータ電圧を伝達する。

10

#### 【0020】

最左側と最右側に位置したFPC基板510には、信号伝達線522a、522b、523a、523bが形成されている。信号伝達線522a、522b、523a、523bは、接触部C3を介してPCB550に形成された信号伝達線551a、551bに接続される。

最左側のFPC基板510に形成された信号伝達線522aは、接触部C2を介して最も左側に位置したデータ線D1に接続されており、また、接触部C3を介して信号伝達線551a、523aに接続されて、接触部C1を介してダミー線L2に接続されている。

20

また、最右側のFPC基板510に形成された信号伝達線523bは、最右側に位置したデータ線Dmに接触部C2を介して接続されており、また、接触部C3を介して信号伝達線551b、523bに接続されて、接触部C1を介してダミー線L1に接続されている。

#### 【0021】

各画素は、表示信号線G<sub>1</sub> - G<sub>2n</sub>、D<sub>1</sub> - D<sub>m</sub>及びダミー線L1、L2に接続されたスイッチング素子Qと、これに接続された液晶キャパシタ（C<sub>Lc</sub>）及び維持キャパシタ（C<sub>ST</sub>）を有する。維持キャパシタ（C<sub>ST</sub>）は必要に応じて省略することができる。

薄膜トランジスタなどのスイッチング素子（Q）は、薄膜トランジスタ表示板である下部表示板100に備えられ、三端子素子としてその制御端子及び入力端子は、各々ゲート線G<sub>1</sub> - G<sub>2n</sub>、データ線D<sub>1</sub> - D<sub>m</sub>及びダミー線L1、L2に接続されており、出力端子は、液晶キャパシタ（C<sub>Lc</sub>）及び維持キャパシタ（C<sub>ST</sub>）に接続されている。

30

#### 【0022】

液晶キャパシタ（C<sub>Lc</sub>）は、下部表示板100の画素電極190と共に電極表示板である上部表示板200の共通電極270を二つの端子とし、二つの電極190、270の間の液晶層3は誘電体として機能する。画素電極190は、スイッチング素子（Q）に接続され、共通電極270は、上部表示板200の全面に形成され、共通電圧（V<sub>c0m</sub>）を印加される。図2とは異なって、共通電極270が下部表示板100に備えられることもあり、その場合、二つの電極190、270の少なくとも一つが線形または棒形に作られる。

#### 【0023】

液晶キャパシタ（C<sub>Lc</sub>）の補助的な役割を果たす維持キャパシタ（C<sub>ST</sub>）は、下部表示板100に備えられた別個の信号線（図示せず）と、画素電極190が絶縁体を介在して重畠してなり、この別個の信号線には、共通電圧（V<sub>c0m</sub>）などの所定の電圧が印加される。しかし、維持キャパシタ（C<sub>ST</sub>）は、画素電極190が絶縁体を介してすぐ上の前段ゲート線と重畠してなることができる。

40

#### 【0024】

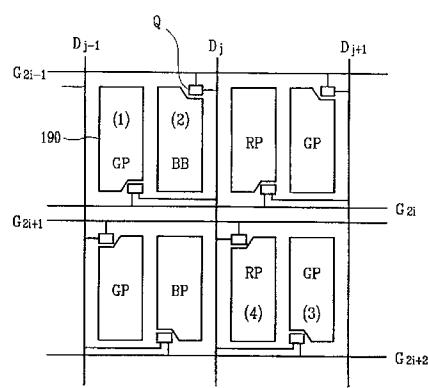

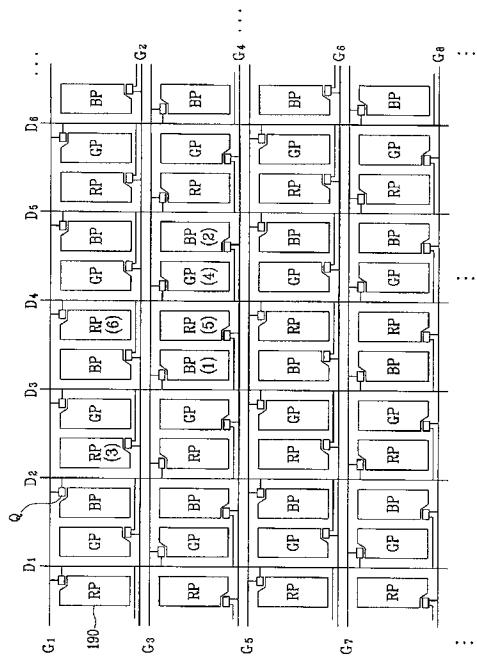

図3に示すように、一対のゲート線G1及びG2、G3及びG4は、一つの行の画素電極190上下に配置されている。また、データ線D<sub>1</sub> - D<sub>m</sub>は、二列の画素電極190の間に一つずつ配置されている。即ち、一対の画素列の間に一つのデータ線が配置されている。これらゲート線G<sub>1</sub> - G<sub>2n</sub>及びデータ線D<sub>1</sub> - D<sub>m</sub>と画素電極190間の接続をより詳しく説明する。

50

## 【0025】

画素電極 190 の上側と下側に配置された複数対のゲート線  $G_1 - G_{2n}$  は、各画素電極 190 の上側または下側に配置されたスイッチング素子 (Q) を介して当該画素電極 190 に接続される。

即ち、奇数番目の画素行において、データ線  $D_1 - D_m$  を中心に左側に位置した第 1 スイッチング素子 (Q) は、上側に位置した第 1 ゲート線  $G_1, G_5, G_9, \dots$  に接続されており、データ線  $D_1 - D_m$  を中心に右側に位置した第 2 スイッチング素子 (Q) は、下側に位置した第 2 ゲート線  $G_2, G_6, G_{10}, \dots$  に接続されている。これに対し、偶数番目の画素行の上側に位置した第 1 ゲート線  $G_3, G_7, G_{11}, \dots$  及び下側の第 2 ゲート線  $G_4, G_8, G_{12}, \dots$  とスイッチング素子 (Q) との接続は奇数番目の画素行と逆である。つまり、データ線  $D_1 - D_m$  を中心に右側に位置した第 1 スイッチング素子 (Q) は、上側に位置した第 1 ゲート線  $G_3, G_7, G_{11}, \dots$  に接続されており、データ線  $D_1 - D_m$  を中心に左側に位置した第 2 スイッチング素子 (Q) は、下側に位置した第 2 ゲート線  $G_4, G_8, G_{12}, \dots$  に接続されている。

## 【0026】

奇数番目行の画素電極 190 のうち、データ線  $D_1 - D_m$  を中心に左側に位置した第 1 画素の画素電極 190 は、第 1 スイッチング素子 (Q) を介して隣接したデータ線  $D_1 - D_m$  に接続されており、データ線  $D_1 - D_m$  を中心に右側に位置した第 2 画素の画素電極 190 は、第 2 スイッチング素子 (Q) を介して次に隣接したデータ線に接続されている。偶数番目行の画素電極 190 のうちデータ線  $D_1 - D_m$  を中心に左側に位置した第 2 画素の画素電極 190 は、第 2 スイッチング素子 (Q) を介して直前のデータ線に接続されており、データ線  $D_1 - D_m$  を中心に右側に位置した第 1 画素の画素電極 190 は、第 1 スイッチング素子 (Q) を介して隣接したデータ線に接続されている。また、第 1 列偶数番目行の画素電極 190 は、最後のデータ線  $D_m$  に連結されたダミー線 L1 に接続されており、最後列奇数番目行の画素電極 190 は、第 1 データ線  $D_1$  に連結された連結線 L2 に接続されている。

## 【0027】

既に説明したように、各画素に形成されたスイッチング素子 (Q) は、接続されたデータ線  $D_1 - D_m$  やダミー線 L1, L2 とより簡単に接続されるように、接続長さをできるだけ短くできる位置に形成される。よって、図 3 に示した配置からスイッチング素子 (Q) の位置が毎画素行毎に変わる。即ち、奇数番目行に位置した画素対のうちデータ線  $D_1 - D_m$  の左側に位置した第 1 画素には、右側上段部に第 1 スイッチング素子 (Q) が形成されており、データ線  $D_1 - D_m$  の右側に位置した第 2 画素には、右側下段部に第 2 スイッチング素子 (Q) が形成されている。

これに対し、偶数番目行に位置した画素のスイッチング素子 (Q) の形成位置は、隣接した画素行の形成位置と正反対である。即ち、偶数番目行に位置した画素対のうちデータ線  $D_1 - D_m$  の左側に位置した第 2 画素には、左側下段部に第 2 スイッチング素子 (Q) が形成されており、データ線  $D_1 - D_m$  の右側に位置した第 1 画素には、左側上段部に第 1 スイッチング素子 (Q) が形成されている。

## 【0028】

図 3 に示した画素電極 190 とデータ線  $D_1 - D_m$  の接続を整理すれば、各画素行において、隣接した二つのデータ線間に位置した二つの画素のスイッチング素子 (Q) は同一なデータ線に接続されている。即ち、奇数番目の画素行において二つのデータ線間に形成された二つの画素のスイッチング素子 (Q) は、右側に位置したデータ線に接続されており、偶数番目の画素行において二つのデータ線間に形成された二つの画素のスイッチング素子 (Q) は、左側に位置したデータ線に接続されている。

図 3 に示した配置は一例であり、奇数番目行と偶数番目行の画素電極 190 とデータ線  $D_1 - D_m$  及びゲート線  $G_1 - G_{2n}$  の接続は互いに入れ替わることができ、さらに他の接続関係を有することができる。

## 【0029】

10

20

30

40

50

一方、色表示を実現するため、各画素が三原色の一つを固有に表示したり（空間分割）、各画素が時間によって交互に三原色を表示するように（時間分割）して、これら三原色の空間的、時間的作用によって色相が認識されるようとする。図2は、空間分割の一例として各画素が画素電極190に対応する領域に赤色、緑色、または青色のカラーフィルタ230を備える状態を示す。図2とは異なって、カラーフィルタ230は、下部表示板100の画素電極190の上または下に形成することもできる。

#### 【0030】

図3は、カラーフィルタ230が行方向には赤色、緑色、青色の順序で配列されており、各画素列は一つの色相のカラーフィルタ230のみを有するストライプ状に配列されている。

液晶表示板組立体300の二つの表示板100、200の少なくとも一つの外側面には、光を偏光させる偏光子（図示せず）が付着されている。

以下、このような液晶表示板組立体300の薄膜トランジスタ表示板100の構造について図4乃至図7を参照して詳細に説明する。

#### 【0031】

図4は、本発明の一実施形態に係る薄膜トランジスタ表示板の配置図であり、図5乃至図7は、各々図4の薄膜トランジスタ表示板をV-V'線、VI-VI'線及びVII-VII'線に沿って切断した断面図である。

既に説明したように、本発明の一実施形態に係る液晶表示装置は、薄膜トランジスタ表示板100とこれと対向する共通電極表示板200、及び薄膜トランジスタ表示板100と共に共通電極表示板200の間に挟持された液晶層3を有する。

#### 【0032】

まず、薄膜トランジスタ表示板100について詳細に説明する。

透明なガラスなどの絶縁基板110上に複数のゲート線121a、121bと複数の維持電極線131が形成されている。

ゲート線121a、121bは主に横方向に延びており、ゲート線121aの一部は下または上に突出してゲート電極124a、124bをなす。また、ゲート線121a、121bの一端部129は、他の層または外部装置との接続のために幅が拡張されている。二つのゲート線121a、121bは互いに隣接して対をなしている。最上部のゲート線121bと最下部のゲート線121aは対をなさない。

#### 【0033】

各維持電極線131は、ゲート線121a、121bと分離されており、互いに接続されて一対の長方形をなす複数の維持電極133a-133d集合と、一対の維持電極連結部135a、135bとを有する。

一つの維持電極133a～133d集合は、主に横方向に延びた第1維持電極133a及び第2維持電極133bを一対ずつ有し、主に縦方向に延びた一対の第3維持電極133cと、その間に位置し縦方向に延びた第4維持電極133dとを有する。第4維持電極133dを中心に左右両側に第1乃至第3維持電極133a-133cが一つずつ配置されて第4維持電極133dを共有する長方形をなし、この二つの長方形は、第4維持電極133dの中央を中心に180°回転対称関係を有する。

維持電極連結部135は、隣接した二つの維持電極133a-133d集合の隣接した維持電極133cを接続し、維持電極133aはゲート電極124付近で曲がっている。

維持電極線131には液晶表示装置の共通電極表示板200の共通電極270に印加される共通電圧など所定の電圧が印加される。

#### 【0034】

ゲート線121a、121bと維持電極線131は、アルミニウム（Al）やアルミニウム合金などのアルミニウム系金属、銀（Ag）や銀合金などの銀系金属、銅（Cu）や銅合金などの銅系金属、モリブデン（Mo）やモリブデン合金などのモリブデン系金属、クロム（Cr）、タンタル（Ta）及びチタニウム（Ti）などからなる。しかし、ゲート線121a、121bと維持電極線131は物理的な性質が異なる二つの膜、つまり下

部膜(図示せず)とその上の上部膜(図示せず)を有することもできる。上部膜は、ゲート線121a、121bと維持電極線131の信号遅延や電圧降下を減らすことができるよう、低い比抵抗の金属、例えばアルミニウム(A1)やアルミニウム合金などのアルミニウム系金属、銀(Ag)や銀合金などの銀系金属、銅(Cu)や銅合金などの銅系金属からなることができる。これとは異なって、下部膜は、他の物質特にITO(indium tin oxide)及びIZO(indium zinc oxide)との接触特性が優れた物質、例えばクロム、モリブデン(Mo)、モリブデン合金、タンタル(Ta)、またはチタニウム(Ti)などからなることができる。下部膜と上部膜の組み合わせの良い例としては、クロム/アルミニウム-ネオジム(Nd)合金を挙げられる。

## 【0035】

ゲート線121a、121bと維持電極線131の側面は、基板110の表面に対して傾斜しており、その傾斜角は約30~80°であることが好ましい。

ゲート線121a、121b及び維持電極線131上には、窒化ケイ素(SiNx)などからなるゲート絶縁膜140が形成されている。

ゲート絶縁膜140上には、水素化非晶質シリコン(非晶質シリコンはa-Siと略称する。)、または多結晶シリコンなどからなる複数の島状半導体152、154a、154bが形成されている。半導体154a、154bは、各々ゲート電極124a、124b上に位置し、これらを覆っており、半導体154aは延びて隣接するゲート線121a及び維持電極連結部135aを覆う。また、半導体152は維持電極連結部135bを覆っている。

## 【0036】

半導体152、154a、154bの上部には、シリサイドまたはn型不純物が高濃度にドーピングされているn+水素化非晶質シリコンなどの物質で作られた複数の島状オーム接触部材(ohmic contact)162、163a、163b、165a、165bが形成されている。接触部材163a/163bと接触部材165a/165bは対をなして島状半導体154a/154b上に位置している。

半導体152、154a、154bとオーム接触部材162、163a、163b、165a、165bの側面も基板110表面に対して傾斜されており、その傾斜角は30~80°である。

オーム接触部材162、163a、163b、165a、165b及びゲート絶縁膜140上には、各々複数のデータ線171と複数のドレイン電極175a、175bが形成されている。

## 【0037】

データ線171は、主に縦方向に延びてゲート線121a、121b及び維持電極連結部135a、135bと交差し、データ電圧を伝達する。各データ線171の端部179は、他の層または外部装置との接続のために幅が拡張されている。各データ線171からドレイン電極175a、175bに向けて右側方向または左側方向にそれぞれ延びた複数の枝がソース電極173a、173bをなし、ドレイン電極175a、175bの一端部は線形であるが、他端部は他の層との接続のために幅が拡張され、維持電極133a上に位置している。ソース電極173bはドレイン電極175aの線状端部を一部囲むように曲がっており、ソース電極173aは隣接した二つのゲート線121a、121bの間を横切って次隣接ドレイン電極175aに接近してドレイン電極175aの線状端部を一部囲むように曲がっている。

## 【0038】

ゲート電極124a/124b、ソース電極173a/173b及びドレイン電極175a/175bは、島状半導体154a/154bと共に薄膜トランジスタ(TFT)をなし、薄膜トランジスタのチャンネルは、ソース電極173a/173bとドレイン電極175a/175bの間の島状半導体154a/154bに形成される。

データ線171とドレイン電極175a、175bは、モリブデン系金属、クロム、タンタル、チタニウムなどの耐火性金属からなることが好ましく、低い抵抗の上部膜と接触

10

20

30

40

50

特性が良い下部膜を含む多層膜構造を有することができる。

データ線 171 とドレイン電極 175a、175b もゲート線 121 と同様に、その側面が約 30~80° でそれぞれ傾斜している。

オーミック接触部材 162、163a、163b、165a、165b は、その下部の半導体 152、154a、154b とその上部のデータ線 171 及びドレイン電極 175a、175b の間にのみ存在し、接触抵抗を低くする役割を果たす。

#### 【0039】

既に説明したように、島状半導体 152、154a、154b は、データ線 171 またはドレイン電極 175a、175b がゲート線 121 及び維持電極線 133a-133d、135 と出会う部分でゲート線 121 及び維持電極線 133a-133d、135 の境界を覆い、データ線 171 の断線を防止する。

データ線 171 及びドレイン電極 175a、175b と露出された半導体 152、154a、154b 部分の上には、保護膜 180 が形成されている。保護膜 180 は、平坦化特性が優れてかつ感光性を有する有機物質、またはプラズマ化学気相蒸着 (PECVD) で形成される a-Si : C : O、a-Si : O : F などの誘電率 4.0 以下の低誘電率絶縁物質、または無機物質である窒化ケイ素などからなる。これとは異なって、保護膜 180 は有機物と窒化ケイ素の二重層からなることができる。

#### 【0040】

保護膜 180 には、ドレイン電極 175a、175b 及びデータ線 171 の端部 179 をそれぞれ露出する複数のコンタクトホール (接触孔) 185、182 が形成されており、ゲート絶縁膜 140 と共にゲート線 121 の端部 129 を露出する複数のコンタクトホール 181 が形成されている。

保護膜 180 上には、ITO またはIZO からなる複数の画素電極 190 と複数の接触補助部材 81、82 が形成されている。

#### 【0041】

画素電極 190 は、コンタクトホール 185 を介してドレイン電極 175a、175b と物理的・電気的に接続され、ドレイン電極 175a、175b からデータ電圧の印加を受ける。データ電圧が印加された画素電極 190 は、共通電圧 ( $V_{c.m}$ ) の印加を受ける他の表示板 200 の共通電極 270 と共に電場を生成することによって、二つの電極 190、270 の間の液晶層 3 の液晶分子を再配列する。

また、画素電極 190 と共に共通電極 270 は、液晶キャパシタ ( $C_{Lc}$ ) を構成し、薄膜トランジスタがターンオフされた後にも印加された電圧を維持しており、電圧維持能力を強化するために液晶キャパシタ ( $C_{Lc}$ ) と並列に接続された維持キャパシタ ( $C_{st}$ ) は、画素電極 190 及びこれと隣接する維持電極線 131 の重畳などで作られる。

#### 【0042】

画素電極 190 は、ドレイン電極 175a、175b の拡張された端部と維持電極 133a を覆い、維持電極 133b、133c、133d とは一部重畳して画素電極 190 の境界線が維持電極 133b、133c、133d 上に位置する。このように、ゲート線 121a、121b と画素電極 190 の境界線の間に維持電極 133b が露出しており、画素電極 190 とゲート線 121a の間の寄生容量による画素電極 190 の電圧変動が減少する。

#### 【0043】

接触補助部材 81、82 は、コンタクトホール 181、182 を介してゲート線 121a、121b の端部 129 及びデータ線 171 の端部 179 とそれぞれ接続される。接触補助部材 81、82 は、ゲート線 121a、121b 及びデータ線 171 の各端部 129、179 と外部装置との接着性を補完し、これらを保護する役割を果たす。ゲート線 121a、121b に走査信号を印加するゲート駆動部 (図示せず) が表示板上に集積された場合、接触部材 81 は、ゲート線 121a、121b の端部 129 とゲート駆動部を接続する連結部材の役割を果たすことができ、場合によって省略することもできる。

#### 【0044】

10

20

30

40

50

本発明の他の実施形態によれば、画素電極 190 の材料として透明な導電性ポリマーなどを使用し、反射型 (reflective) 液晶表示装置の場合、不透明な反射性金属を使用してもよい。この時、接触補助部材 81、82 は、画素電極 190 と他の物質、特にITOまたはIZOで作ることができる。

画素電極 190 上には、液晶層 3 を配向できる配向膜 (図示せず) が塗布されている。

#### 【0045】

次に、共通電極表示板 200 について詳細に説明する。

透明なガラスなどの絶縁基板 210 上にブラックマトリックスという遮光部材 220 が形成されている。遮光部材 220 は、画素電極 190 間の光漏れを防止する役割を果たすものであって、画素電極 190 と対向する開口領域を定義する。

基板 210 と遮光部材 220 の上には、複数のカラーフィルタ 230 が形成されている。カラーフィルタ 230 は、遮光部材 220 が定義する開口領域内にほとんど入るように配置されている。隣接する二つのデータ線 171 の間に位置し、縦方向に配列されたカラーフィルタ 230 は互いに連結されて一つの帯をなすことができる。各カラーフィルタ 230 は、赤色、緑色及び青色などの三原色のうち一つを表すことができる。

カラーフィルタ 230 及び遮光部材 220 上には、有機物質などからなるカバー膜 (overcoat) 250 が形成され、カラーフィルタ 230 を保護し、表面を平坦化する。

カバー膜 250 の上には、ITOまたはIZOなどの透明な導電物質などからなる共通電極 270 が形成されている。

#### 【0046】

再び図 1 を参照すれば、階調電圧生成部 800 は、画素の透過率に関わる二組の複数階調電圧を生成する。そのうちの一組は共通電圧 ( $V_{c.m}$ ) に対してプラスの値を有し、もう一組はマイナスの値を有する。

第 1、第 2 ゲート駆動部 401、402 は、各々液晶表示板組立体 300 のゲート線  $G_1 - G_{2n}$  の奇数番目ゲート線  $G_1, G_3, \dots, G_{2n-1}$  と偶数番目ゲート線  $G_2, G_4, \dots, G_{2n}$  に接続され、外部からのゲートオン電圧 ( $V_{on}$ ) とゲートオフ電圧 ( $V_{off}$ ) の組み合わせからなるゲート信号をゲート線  $G_1 - G_{2n}$  に印加し、複数の集積回路からなる。

データ駆動部 500 は、液晶表示板組立体 300 のデータ線  $D_1 - D_m$  に接続され、階調電圧生成部 800 からの階調電圧を選択してデータ信号として画素に印加する。

複数のゲート駆動集積回路またはデータ駆動集積回路は、チップの形態に FPC 基板に実装して FPC 基板を液晶表示板組立体 300 に付着することもでき、FPC 基板を使用せずガラス基板上にこれら集積回路を直接付着することもできる (COG 実装方式: chip on glass)。さらに、これら集積回路のような機能を遂行する回路を画素の薄膜トランジスタと共に液晶表示板組立体 300 に直接形成することもできる。

#### 【0047】

信号制御部 600 は、第 1、第 2 ゲート駆動部 401、402 及びデータ駆動部 500 などの動作を制御する。

次に、このような液晶表示装置の表示動作について詳細に説明する。

信号制御部 600 は、外部のグラフィック制御部 (図示せず) から入力映像信号 R、G、B 及びその表示を制御する入力制御信号、例えば垂直同期信号 Vsync と水平同期信号 Hsync、メインクロック MCLK、データイネーブル信号 DE などの提供を受ける。信号制御部 600 の入力映像信号 R、G、B と入力制御信号に基づいて映像信号 R、G、B を液晶表示板組立体 300 の動作条件に合うように適切に処理し、ゲート制御信号 CONT1 及びデータ制御信号 CONT2などを生成した後、ゲート制御信号 CONT1 を第 1、第 2 ゲート駆動部 401、402 に送出し、データ制御信号 CONT2 と処理した映像信号 DATA をデータ駆動部 500 に送出する。ここで、映像信号 R、G、B の処理は、図 3 に示した液晶表示板組立体 300 の画素配列によって映像データ R、G、B を再配列する動作を含む。

## 【0048】

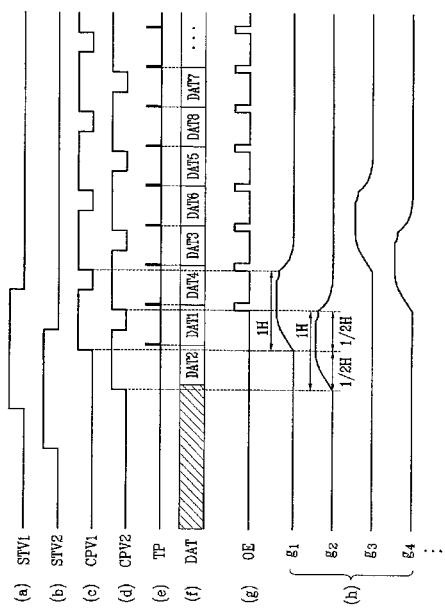

ゲート制御信号 C O N T 1 は、ゲートオン電圧 ( $V_{o_n}$ ) の出力開始を指示する垂直同期開始信号 S T V 1、S T V 2、及びゲートオン電圧 ( $V_{o_n}$ ) の出力時期を制御するゲートクロック信号 C P V 1、C P V 2、及びゲートオン電圧 ( $V_{o_n}$ ) の持続時間を限定する出力イネーブル信号 O E などを有する。この時、垂直同期開始信号 S T V 1 とゲートクロック信号 C P V 1 は、第 1 ゲート駆動部 401 のためのものであり、垂直同期開始信号 S T V 2 とゲートクロック信号 C P V 2 は、第 2 ゲート駆動部 402 のためのものであるが、これに限定されない。

## 【0049】

データ制御信号 C O N T 2 は、映像データ D A T の伝送開始を知らせる水平同期開始信号 S T H、データ線  $D_1 - D_m$  に当該データ電圧の印加を指示するロード信号 T P、共通電圧 ( $V_{c_m}$ ) に対するデータ電圧の極性（以下、共通電圧に対するデータ電圧の極性を略してデータ電圧の極性という。）を反転させる反転信号 R V S 及びデータクロック信号 H C L K などを有する。

データ駆動部 500 は、信号制御部 600 からのデータ制御信号 C O N T 2 によって一行の画素の半分に対する映像データ D A T 集合を順次に受信し、階調電圧生成部 800 からの階調電圧のうち各映像データ D A T に対応する階調電圧を選択することによって、映像データ D A T を当該データ電圧に変換した後、これを当該データ線  $D_1 - D_m$  に印加する。

## 【0050】

第 1、第 2 ゲート駆動部 401、402 は、各々信号制御部 600 からのゲート制御信号 C O N T 1 によってゲートオン電圧 ( $V_{o_n}$ ) を偶数番目ゲート線  $G_2$ 、 $G_4$ 、…、 $G_{2n}$  と奇数番目ゲート線  $G_1$ 、 $G_3$ 、…、 $G_{2n-1}$  に順次に印加して、これらゲート線  $G_2$ 、 $G_4$ 、…、 $G_{2n}$  及び  $G_1$ 、 $G_3$ 、…、 $G_{2n-1}$  に接続されたスイッチング素子 (Q) をターンオンし、これによってデータ線  $D_1 - D_m$  に印加されたデータ電圧がターンオンされたスイッチング素子 (Q) を介して当該画素に印加される。この時、第 2 ゲート駆動部 402 が第 1 ゲート駆動部 401 より先に駆動されてゲートオン電圧 ( $V_{o_n}$ ) が当該ゲート線に印加されるので、 $G_2 - G_1 - G_4 - G_3 - G_6 - G_5$ 、…の順に当該ゲート線にゲートオン電圧 ( $V_{o_n}$ ) が順次に印加される。

## 【0051】

画素に印加されたデータ電圧と共通電圧 ( $V_{c_m}$ ) の差は、液晶キャパシタ C L C の充電電圧、つまり画素電圧として現れる。液晶分子は、画素電圧の大きさによってその配列が異なり、これによって液晶層 3 を通過する光の偏光が変化する。このような偏光の変化は、表示板 100、200 に付着された偏光子（図示せず）によって光透過率の変化として現れる。

## 【0052】

1 / 2 水平周期（または 1 / 2 H）（水平同期信号 H s y n c の一周期）を単位としてデータ駆動部 500 と第 1、第 2 ゲート駆動部 401、402 は同一な動作を繰り返す。このような方法で、1 フレーム期間中に全てのゲート線  $G_1 - G_{2n}$  に対し順次にゲートオン電圧 ( $V_{o_n}$ ) を印加して、全ての画素にデータ電圧を印加する。1 フレームが終了すれば次のフレームが開始され、各画素に印加されるデータ電圧の極性が直前フレームでの極性と逆になるように、データ駆動部 500 に印加される反転信号 R V S の状態が制御される（フレーム反転）。

## 【0053】

このようなフレーム反転の他に、データ駆動部 500 は、1 フレーム内で隣接するデータ線  $D_1 - D_m$  に沿って下降するデータ電圧の極性を反転し、これによってデータ電圧の印加を受けた画素電圧の極性も変化する。ところが、図 3 に示すように、画素とデータ線  $D_1 - D_m$  との接続は様々であって、データ駆動部 500 での極性反転パターンと液晶表示板組立体 300 の画面に表示される画素電圧の極性反転パターンが異なる。以下、データ駆動部 500 での反転を駆動部反転といい、画面に表示される反転を見掛け反転（a p

10

20

30

40

50

parent inversion) という。

#### 【0054】

再び図3を参照して、本発明の一つの実施形態に係る反転形態について詳細に説明する。

図3において、駆動部反転は列反転であって、一つのデータ線に流れるデータ電圧は常に同一極性であり、隣接した二つのデータ線に流れるデータ電圧は逆極性であり、見掛け反転は $1 \times 2$ ドット反転である。

このように、見掛け反転がドット反転になれば、画素電圧が正極性であるときと負極性であるときのキックバック電圧によって発生する輝度差が分散し、縦筋による不良が減少する。

#### 【0055】

次に、図3に示すように、駆動部反転が一列反転である場合、各画素に電圧を印加する方法について、図1と共に図8及び図9を参照して詳細に説明する。

図8は、本発明の一実施形態に係る液晶表示装置の信号波形を時間によって示す図であり、図9は、本発明の一実施形態に係る液晶表示装置における画素の充電順序を示す図である。

図8で $g_1$ 、 $g_2$ 、 $g_3$ 、 $g_4$ は、第1番目のゲート線 $G_1$ 、第2番目のゲート線 $G_2$ 、第3番目のゲート線 $G_3$ 、第4番目のゲート線 $G_4$ に印加されるゲート信号を示す。

図8に示す実施形態において、各ゲート線 $G_1$  -  $G_{2n}$ にゲートオン電圧( $V_{on}$ )を印加する時間は1Hであり、隣接した二つのゲート線 $G_1$  -  $G_{2n}$ にゲートオン電圧( $V_{on}$ )を印加する時間は $1/2$ Hの間重複する。この時、各ゲート線 $G_1$  -  $G_{2n}$ に接続された画素に印加する目標データ電圧は、後半 $1/2$ Hの間印加される。

#### 【0056】

既に説明したように、信号制御部600は、第1ゲート駆動部401に垂直同期開始信号STV1、ゲートクロック信号CPV1などを提供し、第2ゲート駆動部402に垂直同期開始信号STV2、ゲートクロック信号CPV2などを提供する。

図8に示すように、信号制御部600が第2ゲート駆動部402に印加される垂直同期開始信号STV2にパルスを発生させた後、さらに所定時間後、ゲートクロック信号CPV2にパルスを発生させる(図8b及び図8d)。

従って、第2ゲート駆動部402は、垂直同期開始信号STV2にパルスが発生し、さらにゲートクロック信号CPV2にパルスが発生すれば、この垂直同期開始信号STV2のパルスに同期して、ゲートクロック信号CPV2にパルスが発生した時から次のパルスが発生する時までゲートオン電圧( $V_{on}$ )を発生する。これにより、第2番目のゲート線 $G_2$ 、第4番目のゲート線 $G_4$ 、第6番目のゲート線 $G_6$ 、…の順に接続された偶数番目ゲート線 $G_2$ 、 $G_4$ 、 $G_6$ 、…に順次にゲートオン電圧( $V_{on}$ )が含まれたゲート信号 $g_2$ 、 $g_4$ 、…を印加する(図8h)。

#### 【0057】

これにより、偶数番目ゲート線 $G_2$ 、 $G_4$ 、 $G_6$ 、…に接続された画素は、信号制御部600がロード信号TPにパルスを生成する度に(図8e)、該当するデータDATA1、DATA3、DATA5、…に対するデータ電圧を順次にデータ駆動部500から印加を受けて充電する。このために、信号制御部600は、一つの画素行に該当するデータをラインメモリ(図示せず)に記憶させた後、奇数番目ゲート線 $G_1$ 、 $G_3$ 、…に接続された画素の映像データと、偶数番目ゲート線 $G_2$ 、 $G_4$ 、…に接続された画素の映像データに分けてデータ駆動部500に供給する。従って、データ駆動部500は、ゲート線 $G_1$  -  $G_{2n}$ に1Hの間ゲートオン電圧( $V_{on}$ )が印加されれば、ターンオンされたスイッチング素子を介して該当する画素に $1/2$ Hの間、偶数番目ゲート線 $G_2$ 、 $G_4$ 、 $G_6$ 、…に接続された画素に当該データ電圧を印加する。

#### 【0058】

第2ゲート駆動部402のための垂直同期開始信号STV2にパルスを生成した後、 $1/2$ Hが経過すれば、信号制御部600は、第1ゲート駆動部401に印加される垂直同

期開始信号 S T V 1 にパルスを発生させた後、さらに所定時間後、ゲートクロック信号 C P V 1 にパルスを発生させる（図 8 a と図 8 c）。

従って、第 1 ゲート駆動部 401 は、垂直同期開始信号 S T V 1 にパルスが発生し、さらにゲートクロック信号 C P V 1 にパルスが発生すれば、この垂直同期開始信号 S T V 1 とゲートクロック信号 C P V 1 に基づいて、第 1 番目のゲート線 G<sub>1</sub>、第 3 番目のゲート線 G<sub>3</sub>、第 5 番目のゲート線 G<sub>5</sub>、…の順に接続された奇数番目ゲート線 G<sub>1</sub>、G<sub>3</sub>、G<sub>5</sub>、…に順次にゲートオン電圧（V<sub>o</sub><sub>n</sub>）が含まれたゲート信号 g<sub>1</sub>、g<sub>3</sub>、…を印加する（図 8 H）。

これにより、奇数番目ゲート線 G<sub>1</sub>、G<sub>3</sub>、G<sub>5</sub>、…に接続された画素は、信号制御部 600 がロード信号（TP）にパルスを生成する度に（図 8 e）、奇数番目ゲート線 G<sub>1</sub>、G<sub>3</sub>、G<sub>5</sub>、…に接続された画素に該当するデータ DATA 1、DATA 3、DATA 5 のデータ電圧を順次にデータ駆動部 500 から印加を受けて 1 / 2 H の間充電する。

10

#### 【0059】

このように、第 2 ゲート駆動部 402 がゲートオン電圧（V<sub>o</sub><sub>n</sub>）を印加する時期と、第 1 ゲート駆動部 401 がゲートオン電圧（V<sub>o</sub><sub>n</sub>）を印加する時期に 1 / 2 H だけ差が生じるので、既に説明したように、隣接した二つのゲート線 G<sub>1</sub> - G<sub>2</sub><sub>n</sub> にゲートオン電圧（V<sub>o</sub><sub>n</sub>）を印加する時間が 1 / 2 H の間重畠する。即ち、直前ゲート線に接続された画素に自身の充電時間である 1 H の後半 1 / 2 H の間目標データ電圧が本充電される時、次のゲート線に接続された画素には、自身の充電時間の前半 1 / 2 H の間予備充電される。

20

このような第 1、第 2 ゲート駆動部 402、401 の動作によって、図 9 に示すように、ゲートオン電圧（V<sub>o</sub><sub>n</sub>）が G<sub>2</sub> - G<sub>1</sub> - G<sub>4</sub> - G<sub>3</sub>、…順に印加され、データ線 D<sub>j</sub><sub>+1</sub> に接続された画素は、画素 1 - 画素 2 - 画素 3 - 画素 4、…順にデータ電圧の充電動作が行われる。

30

これにより、一行で同一な色相のデータ電圧が充電される画素において、予備充電されるデータ電圧が互いに異なるために発生する画素間の明るさの差がなくなる。次に、図 10 を参照して、これについて詳細に説明する。

#### 【0060】

図 10 は、シアン（青）を表示するために赤色の画素にブラック用データ電圧を印加した場合の画素パターンを示している。

30

図 10 の液晶表示装置において、カラーフィルタが行方向に赤色、緑色及び青色の順序に配列されており、各画素列は同一な色相のカラーフィルタが配列されているストライプ状の配列を有している。また、シアンを表示するために、赤色の画素（R）には全てブラック用データ電圧が印加され、ブラックを表示しているものと仮定する。

奇数番目ゲート線用第 1 ゲート駆動部 401 を偶数番目ゲート線用第 2 ゲート駆動部 402 より先に駆動させれば、ゲート線にゲートオン電圧（V<sub>o</sub><sub>n</sub>）が印加される順序は G<sub>1</sub> - G<sub>2</sub> - G<sub>3</sub> - G<sub>4</sub>、…になる。これによって、第 1 番目のゲート線 G<sub>1</sub> に接続された画素の 1 H 充電時間のうち本充電が行われる後半 1 / 2 H の間、第 2 番目のゲート線 G<sub>2</sub> に接続された画素の充電時間のうち前半 1 / 2 H の間予備充電が行われる。同様に、第 2 番目のゲート線 G<sub>2</sub> に接続された画素の全充電時間のうち後半 1 / 2 H の間本充電が行われる時、第 3 番目のゲート線 G<sub>3</sub> に接続された画素の充電時間のうち前半 1 / 2 H の間予備充電が行われる。このような過程を経て全てのゲート線 G<sub>1</sub> - G<sub>2</sub><sub>n</sub> に予備充電と本充電が順次に行われる。

40

#### 【0061】

この場合、第 3 番目のゲート線 G<sub>3</sub> とデータ線 D<sub>3</sub> に接続された青色の画素（1）に接続されたデータ線 D<sub>3</sub> が、第 2 番目のゲート線 G<sub>2</sub> に接続されたブラックを示す赤色の画素（R）にも接続されているので、この画素（1）に予備充電されるデータ電圧はブラック用データ電圧になる。ところが、第 4 番目のゲート線 G<sub>4</sub> とデータ線 D<sub>4</sub> に接続された青色（B）の画素（2）に接続されたデータ線 D<sub>4</sub> が第 2 番目のゲート線 G<sub>2</sub> に接続された緑色の画素（4）に接続されているので、この画素（2）に予備充電されるデータ電圧

50

は緑色用データ電圧になる。このように同一な画素行において、青色用データ電圧が充電される画素(1)(2)に予備充電されるデータ電圧は、各々ブラック用データ電圧と緑色用データ電圧として異なるので、同一な青色用データ電圧が本充電されても、最終画素に充電される画素電圧が互いに異なる。このような現象は隣接した画素行においても同様に発生し、その結果、これら二つの画素(1)(2)の間に明るさの差が生じ、縦筋模様が発生する。

#### 【0062】

しかし、 $G_2 - G_1 - G_4 - G_3, \dots$ の順にゲートオン電圧( $V_{on}$ )を印加して画素を予備充電し、本充電を行う場合、画素(1)に予備充電されるデータ電圧は隣接している赤色の画素(R)に印加されるブラック用データ電圧になる。また、画素(2)に予備充電されるデータ電圧は、すぐ上に隣接する画素行から左に2番目に位置した赤色の画素(R)に印加されるブラック用データ電圧になる。このように、これら二つの画素(1)(2)全部に同一なデータ電圧で予備充電されているので、青色用データ電圧で本充電された後の画素電圧も同一であって、二つの画素(1)(2)の明るさの差は生じない。

即ち、データ線が画素電極190の下側に位置したスイッチング素子(第2スイッチング素子)(Q)に接続されている画素の場合、すぐ上に隣接した画素から左側または右側に2番目に位置した画素に印加されるデータ電圧が予備充電され、データ線が画素電極190の上側に位置したスイッチング素子(第1スイッチング素子)(Q)に接続されている画素の場合、同じデータ線に接続された隣接画素に印加されるデータ電圧が予備充電される。

#### 【0063】

その結果、同一な画素行において、同一な色相の画素は同じ画素列やこのような画素列と同一な色相の画素列(同色画素列)にある画素のデータ電圧で予備充電される。即ち、同じ色の画素は、同一な色相のデータ電圧が予備充電される。従って、同一な行において、同一な色相の画素には同じ色相のデータ電圧が予備充電され、縦筋模様の発生が減少する。

本実施形態において、第2番目のゲート線 $G_2$ に接続される画素を予備充電するため、信号制御部600には、内部メモリ(図示せず)などに記憶された別途のデータ電圧が印加されることができる。

#### 【0064】

以上のように、二つの画素が一つのデータ線を共有するようにし、データ線の本数を減少させることで、それに接続された高価なデータ駆動回路チップ数も減らし、表示装置の製造コストを大きく削減できる。

#### 【0065】

また、隣接した画素行間にスイッチング素子が接続されたデータ線の位置を変更し、たとえば駆動部反転が列反転方式であっても見掛け反転が $1 \times 2$ ドット反転になることができるようにして、データ駆動部から列反転方式でデータ電圧の極性が決定されて印加されるので、データ線の材料を選択できる幅が大きくなり、製造工程を単純化し易く、見掛け反転がドット反転であるので画質が向上する。

各画素行の上側に形成された奇数番目ゲート線よりも各画素行の下側に形成された偶数番目ゲート線に先にゲートオン電圧を印加する方法で全ゲート線を走査する。これによって、一つの画素行において同じ色相の画素が同一な色相のデータ電圧で予備充電され、予備充電量が互いに異なるために生じる縦筋模様が減少し、その結果表示装置の画質が向上する。

#### 【0066】

以上、本発明の好適な実施形態について詳細に説明したが、本発明の権利範囲はこれに限定されるものではなく、特許請求の範囲で定義している本発明の基本概念を利用した当業者の様々な変形及び改良形態も本発明の権利範囲に属する。

#### 【図面の簡単な説明】

#### 【0067】

10

20

30

40

50

【図1】本発明の一実施形態に係る液晶表示装置のブロック図である。

【図2】本発明の一実施形態に係る液晶表示装置の一つの画素に対する等価回路図である。

【図3】本発明の一実施形態に係る液晶表示装置の構造図である。

【図4】本発明の一実施形態に係る薄膜トランジスタ表示板の配置図である。

【図5】図4の薄膜トランジスタ表示板をV-V'線に沿って切断した断面図である。

【図6】図4の薄膜トランジスタ表示板をVI-VI'線に沿って切断した断面図である。

【図7】図4の薄膜トランジスタ表示板をVII-VII'線に沿って切断した断面図である。

10

【図8】本発明の一実施形態に係る液晶表示装置の信号波形を時間によって示す図である。

【図9】本発明の一実施形態に係る液晶表示装置で画素の充電順序を示す図である。

【図10】赤色の画素にブラック用データ電圧を印加した場合の画素パターンを示す。

【符号の説明】

【0068】

3 液晶層

100、200 表示板

190 画素電極

230 カーフィルタ

270 共通電極

300 液晶表示板組立体

401、402 ゲート駆動部

500 データ駆動部

600 信号制御部

800 階調電圧生成部

121a、121b ゲート線

124a、124b ゲート電極

131 維持電極線

133a～133d 維持電極

135 維持電極連結部

140 ゲート絶縁膜

152、154a、154b 半導体

162、163a、163b、165a、165b オーム接觸部材

171 データ線

175a、175b ドレイン電極

180 保護膜

181、182、185 コンタクトホール

81、82 接触補助部材

220 遮光部材

230 カーフィルタ

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 6 】

【図7】

【 図 8 】

【図9】

【図10】

## フロントページの続き

| (51)Int.Cl. | F I     | テーマコード(参考)   |

|-------------|---------|--------------|

|             | G 0 9 G | 3/20 6 8 0 H |

|             | G 0 9 G | 3/20 6 2 1 M |

|             | G 0 9 G | 3/20 6 8 0 G |

|             | G 0 9 G | 3/20 6 2 2 K |

|             | G 0 9 G | 3/20 6 2 2 D |

|             | G 0 9 G | 3/20 6 4 2 K |

|             | G 0 9 G | 3/20 6 2 3 Y |

|             | G 0 9 G | 3/20 6 2 1 B |

(72)発明者 朴 普 允

大韓民国 京畿道 龍仁市 器興邑 農書里 山24 月桂樹棟 1017号

(72)発明者 姜 南 洙

大韓民国 京畿道 安山市 四1洞 プレンマウル住公5団地アパート 517棟 704号

(72)発明者 朴 倖 源

大韓民国 京畿道 城南市 中院区 銀杏2洞 住公アパート 117棟 602号

(72)発明者 文 勝 煥

大韓民国 京畿道 龍仁市 上ヒョン洞 マンヒョンマウル現代アイパーク6次アパート 205

棟 1504号

F ターム(参考) 2H093 NA16 NA31 NA32 NA43 NA47 NA53 NC10 NC12 NC32 NC34

NC53 NC58

5C006 AA16 AA22 AC11 AC21 AC22 AC28 AF42 AF43 AF72 BB16

BB21 BB27 BC02 BC03 BC06 BC22 BC23 BF05 BF43 EB04

FA22 FA26 FA37 FA42 FA43 FA51

5C080 AA10 BB06 CC03 DD05 DD23 DD28 EE29 EE30 FF11 FF13

JJ02 JJ04 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP2006106745A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2006-04-20 |

| 申请号            | JP2005290598                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2005-10-03 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 李龍淳<br>朴普允<br>姜南洙<br>朴倖源<br>文勝煥                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 李 龍 淳<br>朴 普 允<br>姜 南 浚<br>朴 倖 源<br>文 勝 煥                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| CPC分类号         | G09G3/3648 G02F1/136286 G09G3/3614 G09G3/3677 G09G2300/0408 G09G2300/0426 G09G2310 /0251 G09G2320/0219 G09G2320/0233 H01L27/124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G02F1/133.510 G02F1/133.525 G09G3/20.624.B G09G3/20.680.H G09G3 /20.621.M G09G3/20.680.G G09G3/20.622.K G09G3/20.622.D G09G3/20.642.K G09G3/20.623.Y G09G3/20.621.B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA31 2H093/NA32 2H093/NA43 2H093/NA47 2H093/NA53 2H093/NC10 2H093 /NC12 2H093/NC32 2H093/NC34 2H093/NC53 2H093/NC58 5C006/AA16 5C006/AA22 5C006/AC11 5C006/AC21 5C006/AC22 5C006/AC28 5C006/AF42 5C006/AF43 5C006/AF72 5C006/BB16 5C006 /BB21 5C006/BB27 5C006/BC02 5C006/BC03 5C006/BC06 5C006/BC22 5C006/BC23 5C006/BF05 5C006/BF43 5C006/EB04 5C006/FA22 5C006/FA26 5C006/FA37 5C006/FA42 5C006/FA43 5C006 /FA51 5C080/AA10 5C080/BB06 5C080/CC03 5C080/DD05 5C080/DD23 5C080/DD28 5C080/EE29 5C080/EE30 5C080/FF11 5C080/FF13 5C080/JJ02 5C080/JJ04 5C080/JJ06 2H193/ZA02 2H193 /ZA04 2H193/ZA08 2H193/ZC02 2H193/ZC13 2H193/ZD23 2H193/ZF22 2H193/ZF24 2H193/ZF36 2H193/ZH21 |         |            |

| 优先权            | 1020040078279 2004-10-01 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

**摘要(译)**

要解决的问题：通过减少驱动电路的芯片数量来降低液晶显示装置的制造成本，并进一步提高液晶显示装置的图像质量。解决方案：本发明的液晶显示元件具有分配给一行像素的两条栅极线和分配给两列像素的一条数据线。显示元件配备有连接到偶数栅极线的第一栅极驱动部分和连接到奇数栅极线的第二栅极驱动部分，并且第一栅极驱动部分在约1/2H的指定时间之前被驱动到向栅极线施加栅极导通电压。因此，栅极导通电压交替地以1/2H的间隔施加到偶数栅极线和奇数栅极线，并且每个栅极导通电压施加1H的时段。因此，在1H的前半部分1/2H中，在栅极线中施加栅极导通电压的数据电压预先对像素充电，并且在后半部分1/2H中主要充电其数据电压。ž