(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4478077号

(P4478077)

(45) 発行日 平成22年6月9日(2010.6.9)

(24) 登録日 平成22年3月19日(2010.3.19)

(51) Int.CI.

F 1

G02F 1/1368 (2006.01)

G02F 1/1335 (2006.01)G02F 1/1368

G02F 1/1335 505

請求項の数 15 (全 27 頁)

(21) 出願番号 特願2005-192296 (P2005-192296)

(22) 出願日 平成17年6月30日 (2005.6.30)

(65) 公開番号 特開2006-18295 (P2006-18295A)

(43) 公開日 平成18年1月19日 (2006.1.19)

審査請求日 平成17年6月30日 (2005.6.30)

(31) 優先権主張番号 10-2004-0050171

(32) 優先日 平成16年6月30日 (2004.6.30)

(33) 優先権主張国 韓国 (KR)

(31) 優先権主張番号 10-2005-0010589

(32) 優先日 平成17年2月4日 (2005.2.4)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 501426046

エルジー ディスプレイ カンパニー リ

ミテッド

大韓民国 ソウル, ヨンドゥンポーク, ヨ

イドードン 20

(74) 代理人 100110423

弁理士 曽我 道治

(74) 代理人 100084010

弁理士 古川 秀利

(74) 代理人 100094695

弁理士 鈴木 憲七

(74) 代理人 100111648

弁理士 梶並 順

最終頁に続く

(54) 【発明の名称】 液晶表示装置の製造方法及び液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に第1マスク工程でゲート配線とゲート電極を形成する段階と、

前記ゲート配線とゲート電極を含む基板の全面にゲート絶縁膜を形成する段階と、

前記ゲート絶縁膜上部に単一マスクを利用した第2マスク工程で、アクティブ層とオーミックコンタクト層、ソース電極、ドレイン電極、及び前記ゲート配線と交差して画素領域を定義するデータ配線を形成する段階と、

前記ソース及びドレイン電極とデータ配線を含む基板全面に第1保護膜を形成する段階と、

前記アクティブ層上部の第1保護膜上に第3マスク工程で、ブラックマトリックスを形成する段階と、 10

前記画素領域の前記第1保護膜上部に第4マスク工程で、カラーフィルター層を形成する段階と、

前記カラーフィルター及びブラックマトリックスが形成された基板の全面に第2保護膜を形成する段階と、

第5マスク工程で、前記画素領域及び前記ドレイン電極の一部に対応する第2保護膜を露出する感光パターンを形成する段階と、

前記感光パターンをマスクとして前記露出した第2保護膜を除去して、前記第2保護膜に接触する第1保護膜部分を除去して前記ドレイン電極の一部を露出する段階と、

前記ドレイン電極の露出した部分を含み、前記感光パターンが形成された基板全面に透 20

明導電層を形成する段階と、

前記感光パターンと前記感光パターン上部の透明導電層を除去して、前記画素領域内に前記ドレン電極の露出した部分と接触する画素電極を形成する段階と

を含む液晶表示装置の製造方法。

【請求項 2】

前記第2マスク工程は前記ゲート配線の上部に前記画素電極と接触する金属パターンを形成する段階を含むことを特徴とする請求項1に記載の液晶表示装置の製造方法。

【請求項 3】

前記第1マスク工程は前記ゲート配線の一端にゲートパッドを形成する段階を含んで、前記第2マスク工程は前記データ配線の一端にデータパッドを形成する段階を含むことを特徴とする請求項1に記載の液晶表示装置の製造方法。 10

【請求項 4】

前記画素電極を形成する段階は前記ゲートパッドと接触するゲートパッド端子及び前記データパッドと接触するデータパッド端子を形成する段階を含むことを特徴とする請求項3に記載の液晶表示装置の製造方法。

【請求項 5】

前記画素電極と、ゲートパッド端子及びデータパッド端子は透明導電物質で形成されることを特徴とする請求項4に記載の液晶表示装置の製造方法。

【請求項 6】

前記画素電極を含む基板上に、前記ゲート及びデータ配線に対応する柱状のスペーサーを形成する段階をさらに含むことを特徴とする請求項4に記載の液晶表示装置の製造方法。 20

【請求項 7】

前記柱状のスペーサーを形成する段階は、前記ゲートパッド端子を覆う第1遮断層を形成する段階と、前記データパッド端子を覆う第2遮断層を形成する段階を含むことを特徴とする請求項6に記載の液晶表示装置の製造方法。

【請求項 8】

前記第2マスク工程は、

前記ゲート絶縁膜上に純粋非晶質シリコーン層と不純物非晶質シリコーン層と金属層と感光層を積層する段階と、 30

前記金属層上部に感光層を形成する段階と、

前記感光層上部に、透過部と半透過部及び遮断部を含む前記単一マスクを位置させる段階と、

前記単一マスクを介して前記感光層を露光して現像して、互いに異なる厚さを有する感光パターンを形成する段階と、

前記感光パターンにより露出した前記金属層と不純物非晶質シリコーン層及び純粋非晶質シリコーン層の一部を除去する段階と、

さらに薄い厚さを有する前記感光パターンの部分を除去して前記単一マスクの半透過部に対応する金属層を露出する段階と、

前記露出した金属層を除去して不純物非晶質シリコーンを露出する段階と、 40

前記露出した不純物非晶質シリコーン層を除去する段階と、

前記残っている感光パターンを除去する段階を含むことを特徴とする請求項1に記載の液晶表示装置の製造方法。

【請求項 9】

前記単一マスクを利用して前記データ配線下部に、純粋非晶質シリコーン層と不純物非晶質シリコーン層を含む半導体パターンを形成する段階をさらに含むことを特徴とする請求項1に記載の液晶表示装置の製造方法。

【請求項 10】

前記第2保護膜は前記画素領域で選択的にパターニングされて前記カラーフィルター層を選択的に露出することを特徴とする請求項1に記載の液晶表示装置の製造方法。 50

## 【請求項 1 1】

前記画素電極と離隔されて同じ層上に位置する共通電極を形成する段階をさらに含むことを特徴とする請求項 1 0 に記載の液晶表示装置の製造方法。

## 【請求項 1 2】

基板と、

前記基板上に形成されたゲート配線とゲート電極と、

前記ゲート配線とゲート電極上部のゲート絶縁膜と、

前記ゲート電極上部のゲート絶縁膜上に形成されたアクティブ層と、

前記アクティブ層上部のオーミックコンタクト層と、

前記オーミックコンタクト層上部に形成されたソース電極とドレイン電極、及び前記ゲート配線と交差して画素領域を定義するデータ配線と、

前記ソース及びドレイン電極とデータ配線上部の第 1 保護膜と、

前記アクティブ層上部の前記第 1 保護膜上に形成されたブラックマトリックスと、

前記画素領域の第 1 保護膜上に形成されたカラーフィルター層と、

前記ブラックマトリックス及びカラーフィルター層上部に形成されて、前記画素領域のカラーフィルター層を露出する第 2 保護膜と、

前記第 2 保護膜と水平に重畠することなく前記第 2 保護膜と同じ層上に位置し、前記画素領域の露出したカラーフィルター層上部に形成されて、前記ドレイン電極と連結された画素電極と

を含む液晶表示装置。

20

## 【請求項 1 3】

前記ゲート配線及びデータ配線上部に柱状のスペーサーをさらに含むことを特徴とする請求項 1 2 に記載の液晶表示装置。

## 【請求項 1 4】

前記第 2 保護膜は前記画素領域で選択的にパターニングされて前記カラーフィルター層を選択的に露出することを特徴とする請求項 1 2 に記載の液晶表示装置。

## 【請求項 1 5】

前記画素領域で選択的に露出したカラーフィルター層上に、前記画素電極と離隔して設けられ同じ層上に位置する共通電極をさらに含むことを特徴とする請求項 1 4 に記載の液晶表示装置。

30

## 【発明の詳細な説明】

## 【技術分野】

## 【0 0 0 1】

本発明は、液晶表示装置に係り、特に、カラーフィルターオン薄膜トランジスタ (COT : color filter on TFT) 構造の液晶表示装置用アレイ基板の製造方法に関する。

## 【背景技術】

## 【0 0 0 2】

一般的に、液晶表示装置は、液晶分子の光学的異方性と複屈折特性を利用して画像を表現するものであって、電界が印加されると液晶の配列が変わり、変わった液晶の配列方向によって光が透過する特性も変わる。

40

## 【0 0 0 3】

液晶表示装置は、電界生成電極がそれぞれ形成されている両基板を両電極が形成されている面が向かい合うように配置し、両基板間に液晶物質を注入した後に、両電極に電圧を印加して生成される電界により前記液晶分子を動かすようにすることによって、これにより変わる光の透過率により画像を表現する装置である。

## 【0 0 0 4】

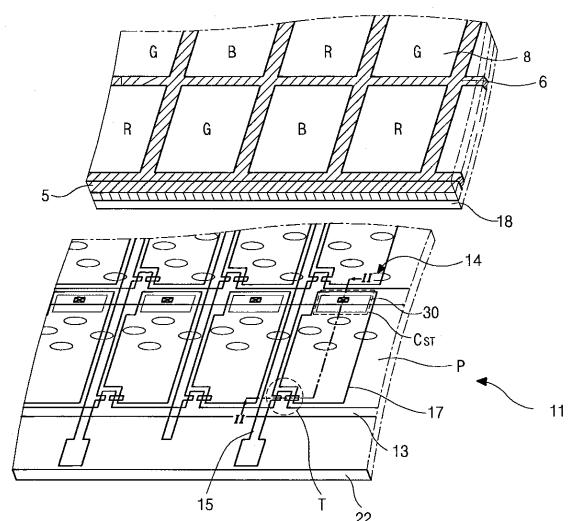

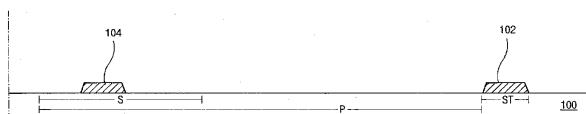

図 1 は、従来による液晶表示装置を概略的に示した図面である。

## 【0 0 0 5】

図示したように、一般的なカラー液晶表示装置 1 1 は、赤、緑、青のカラーフィルターを含むカラーフィルター層 8 と、カラーフィルター層 8 のカラーフィルター間に形成され

50

たブラックマトリックス 6 と、前記カラーフィルター層 8 とブラックマトリックス 6 を覆う共通電極 18 が形成された上部基板 5 と、画素領域 P が定義されて画素領域には画素電極 17 とスイッチング素子 T が形成され、画素領域 P の周辺でアレイ配線が形成された下部基板 22 とを含み、上部基板 5 と下部基板 22 との間には液晶 14 が充填されている。

【0006】

前記下部基板 22 は、アレイ基板ともいい、スイッチング素子である薄膜トランジスタ T がマトリックス状に位置して、このような複数の薄膜トランジスタ T を交差してゲート配線 13 とデータ配線 15 が形成される。

【0007】

ここで、前記画素領域 P は、前記ゲート配線 13 とデータ配線 15 とが交差して定義される領域であり、前記画素領域 P 上には前述したように透明な画素電極 17 が形成される。

【0008】

前記画素電極 17 は、インジウム - スズ - オキサイド (indium tin oxide : ITO) のように光の透過率が比較的優れた透明導電性金属を用いる。

【0009】

前記画素電極 17 と並列に連結されたストレージキャパシター C<sub>ST</sub> がゲート配線 13 の上部に構成され、ストレージキャパシター C<sub>ST</sub> の第 1 電極でゲート配線 13 の一部を使用し、第 2 電極でソース及びドレイン電極と同一層同一物質で形成されたアイランド状の金属パターン 30 を使用する。

【0010】

ここで、前記金属パターン 30 は、画素電極 17 と接触して画素電極の信号を受けるように形成される。

【0011】

ところが、前述したように、上部カラーフィルター基板 5 と下部アレイ基板 22 とを合着して液晶パネルを製作する場合には、カラーフィルター基板 5 とアレイ基板 22 との合着誤差による光漏れ不良などが発生する確率が非常に高い。

【0012】

これに対して、以下、図 2 を参照しながら説明する。

【0013】

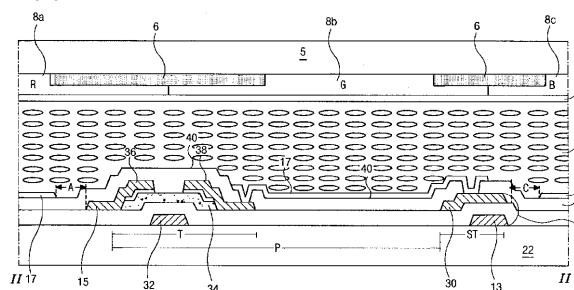

図 2 は図 1 の II - II を切断して図示した液晶表示装置の断面図である。

【0014】

図示したように、第 1 基板 22 は、スイッチング領域 S を含む画素領域 P とストレージ領域 ST で定義される。

【0015】

前記スイッチング領域 S には、ゲート電極 32 とアクティブ層 34 とソース電極 36 とドレイン電極 38 で構成された薄膜トランジスタ T が形成されて、前記画素領域 P には透明な画素電極 17 が形成される。

【0016】

前記ストレージ領域 ST には、ゲート配線 13 を第 1 電極にし、前記ゲート配線 13 の上部にアイランド状に形成されて前記画素電極 17 と接触する金属パターン 30 を第 2 電極にするストレージキャパシター C<sub>ST</sub> が構成される。

【0017】

ここで、前記ストレージキャパシター C<sub>ST</sub> は、多様な構造及び形態で構成することができる。

【0018】

前記第 1 基板 22 と液晶層 14 を間に置いて離隔された第 2 基板 5 の対向面には、前記薄膜トランジスタ T とゲート配線及びデータ配線 13、15 に対応してブラックマトリックス 6 が形成されて、前記画素領域 P に対応する面にはカラーフィルター 8a、8b、8c が形成される。

10

20

30

40

50

## 【0019】

前記カラーフィルター 8 a、8 b、8 c とブラックマトリックス 6 が形成された基板 5 の全面には透明な共通電極 18 が形成される。

## 【0020】

一般的に、前述した第1基板 22 と第2基板 5 は別途に製作されてそれぞれの製作が完了すると合着する工程が進められる。

## 【0021】

ここで、合着誤差が発生するようになれば、前記ブラックマトリックス 6 の位置が最初に設計された位置から外れるようになり、これにより、前記薄膜トランジスタ T には光が入り漏れ電流が発生するようになり、前記ゲート及びデータ配線 13、15 に対応する領域、すなわち、データ配線 15 と画素電極 17 の離隔された領域 A と前記ゲート配線 13 と前記画素電極 17 間の離隔された領域 C で光漏れ現象が発生する問題がある。10

## 【0022】

したがって、従来は、このような問題を解決するために、合着工程時の誤差を勘案して設計時合着マージン (align margin) をさらに設けて設計するようになる。

## 【0023】

すなわち、前記ブラックマトリックス 6 のサイズをさらに大きく設計することである。

## 【0024】

このようにすれば、合着誤差が発生しても上述した不良が発生しない。

## 【0025】

しかし、輝度及び開口率が減少される問題がある。20

## 【0026】

したがって、これを解決するための方法で前記カラーフィルターを薄膜トランジスタアレイ配線の上部に形成する COT 構造の液晶表示装置が提案された。

## 【0027】

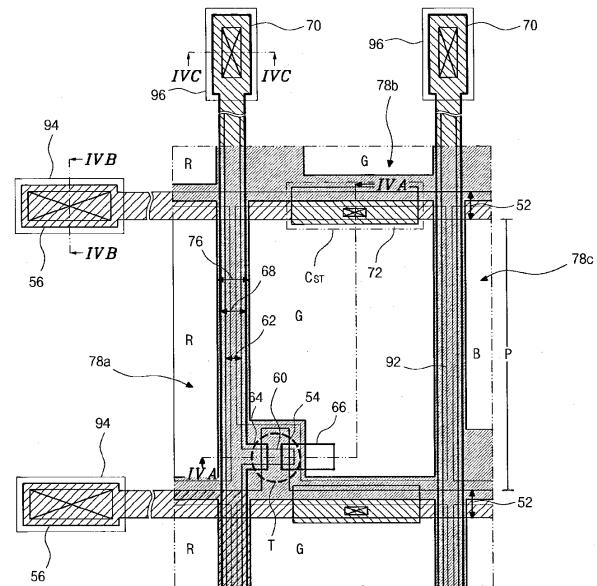

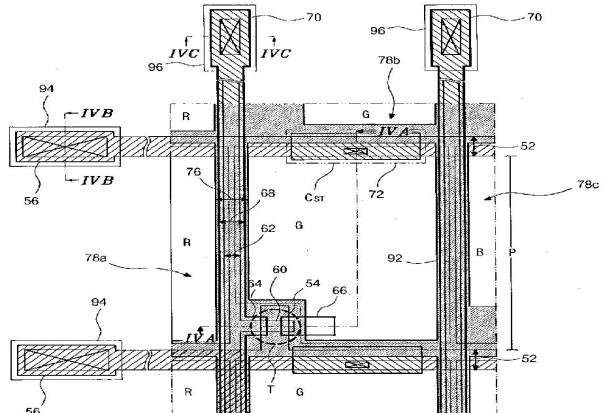

図3は、従来による COT 構造の液晶表示装置用アレイ基板の一部を示した拡大平面図である。

## 【0028】

図示したように、基板 50 上に一方向に延長されて相互に平行するように離隔された複数のゲート配線 52 と、前記ゲート配線 52 と垂直に交差して画素領域 P を定義して相互に平行するように離隔された複数のデータ配線 68 を形成する。30

## 【0029】

前記ゲート配線 52 の一端にはゲートパッド 56 及びここに接触する透明なゲートパッド端子 94 が形成されて、前記データ配線 68 の一端にはデータパッド及びここに接触する透明なデータパッド端子 70、96 が形成される。

## 【0030】

前記ゲート配線 52 とデータ配線 68 の交差地点毎にゲート電極 54 と半導体層 60 とソース電極 64 とドレイン電極 66 を含む薄膜トランジスタ T が形成される。

## 【0031】

ここで、前記半導体層 60 から前記データ配線 68 の下部に半導体層 60 の延長部 62 を形成することができ、これは前記データ配線 68 の付着特性を改善するための用途である。40

## 【0032】

前記ゲート配線 52 とデータ配線 68 が交差して定義される画素領域 P 毎にカラーフィルター 78 a、78 b、78 c が形成されて、前記薄膜トランジスタ T に対応してブラックマトリックス 76 が形成される。

## 【0033】

場合によっては、図示したように、前記ブラックマトリックス 76 は前記ゲート配線 52 とデータ配線 68 に対応しても形成される。

## 【0034】

10

20

30

40

50

前記画素領域 P に対応するカラーフィルター 78a、78b、78c の上部には前記ドレイン電極 66 と接触する画素電極 92 が形成される。

【0035】

前述した構成は、前記カラーフィルター 78a、78b、78c とブラックマトリックス 76 を上部基板（図示せず）ではない下部アレイ基板に形成することによって、前述した合着マージンなどを考慮しなくても良いので、合着マージンだけの領域を開口領域に拡大して用いることができる長所がある。

【0036】

前記ゲート配線 52 の一部上部にはストレージキャパシター  $C_{ST}$  が構成されるが、前記ストレージキャパシター  $C_{ST}$  は第1電極をゲート配線 52 にし、前記ゲート配線 52 の一部上部にアイランド状で形成されて前記画素電極 92 と接触した金属パターン 72 を第2電極にする。

10

【0037】

ここで、前記ストレージキャパシター  $C_{ST}$  の構成及び位置は多様に変形することができる。

【0038】

以下、工程断面図を参照して前述した従来による COT 構造液晶表示装置用アレイ基板を形成する方法を説明する。

【0039】

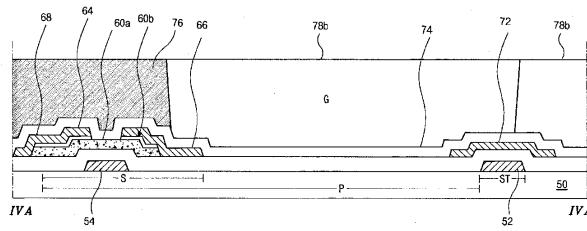

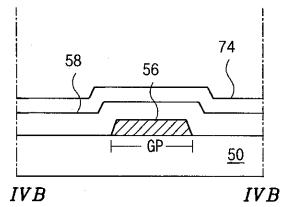

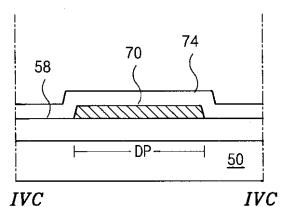

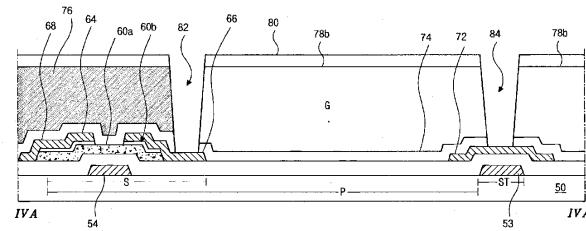

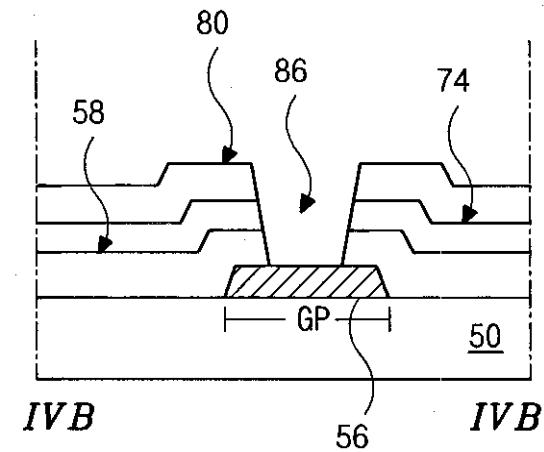

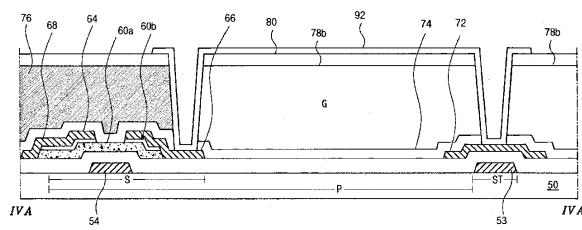

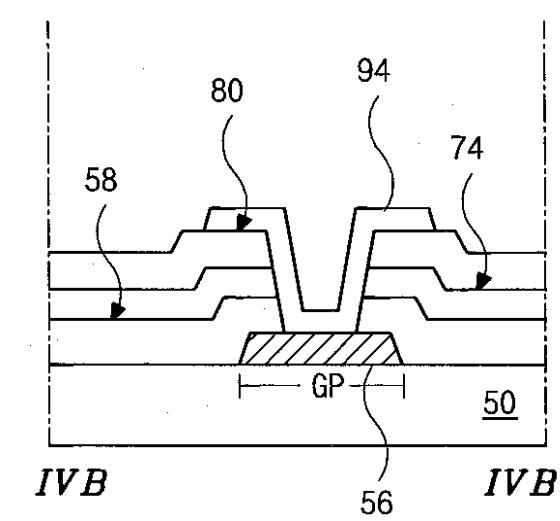

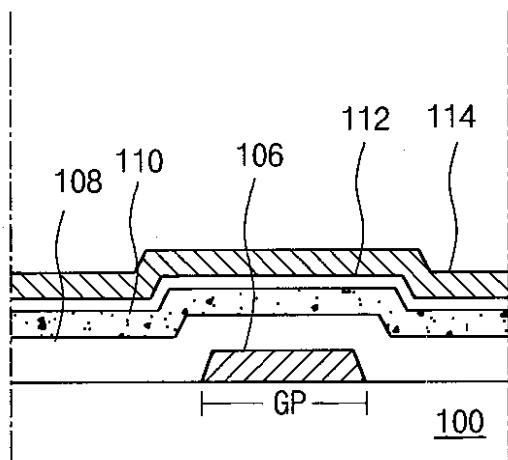

図 4A と図 4B 及び図 4C は、従来の第1マスク工程と第2マスク工程を示した図面であって、それぞれ図 3 の IVA - IVA 線、IVB - IVB 線、IVC - IVC 線に沿って切断した面に対応する断面図である。

20

【0040】

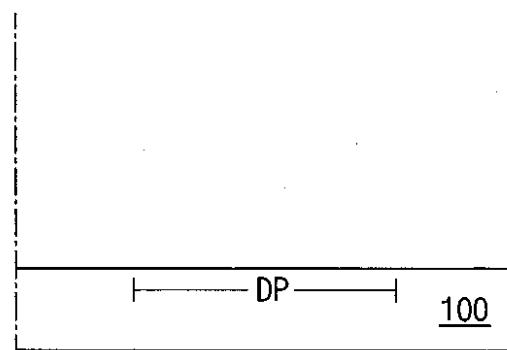

基板 50 上にスイッチング領域 S を含む画素領域 P と、画素領域 P の一側にストレージ領域 ST と、ゲートパッド領域 GP と、データパッド領域 DP を定義する。

【0041】

前記複数の領域 S、P、ST、GP、DP が定義された基板 50 上にアルミニウム (A1)、アルミニウム合金 (AlNd) 等を含む金属物質を蒸着してパターニングして、ゲート電極 54 とゲート配線 52 を形成する。ゲート電極 54 は前記スイッチング領域 S に対応して、ゲート配線 52 の一部は前記ストレージ領域 ST に対応する。ゲート配線 52 は一端にゲートパッド 56 を含むが、ゲートパッド 56 はゲートパッド領域 GP に対応する。

30

【0042】

前記ゲート電極 54 とゲート配線 52 が形成された基板 50 の全面に窒化シリコーン (SiNx) と酸化シリコーン (SiO<sub>2</sub>) を含む無機絶縁物質グループのうちから選択された一つまたはそれ以上の物質を蒸着してゲート絶縁膜 58 を形成する。

【0043】

前記ゲート絶縁膜 58 の上部に純粋な非晶質シリコーン層と不純物が含まれた非晶質シリコーン層を積層して第2マスク工程でパターニングして、前記ゲート電極 54 に対応するゲート絶縁膜 58 の上部にアクティブ層 60a とオーミックコンタクト層 60b で構成された半導体層 60 と前記半導体層 60 で垂直するように延長された延長部 62 を形成する。

40

【0044】

ここで、前記延長部 62 は形成しないこともある。

【0045】

図 5A と図 5B 及び図 5C は、第3マスク工程を示した図面であって、それぞれ図 3 の IVA - IVA 線、IVB - IVB 線、IVC - IVC 線に沿って切断した面に対応する断面図である。

【0046】

前記アクティブ層 60a とオーミックコンタクト層 60b が形成された基板 50 の全面

50

に前述した導電性金属グループのうちから選択された一つまたはそれ以上を蒸着して第3マスク工程でパターニングして、前記オーミックコンタクト層60bの上部で相互に離隔されたソース電極64とドレイン電極66を形成して、前記ソース電極64から前記データパッド領域DPに延長形成されて一端にデータパッド70を含むデータ配線68が形成される。

【0047】

同時に、前記ストレージ領域STに対応するゲート配線52の上部にアイランド状の金属パターン72を形成する。

【0048】

続いて、前記ソース及びドレイン電極64、66をエッチングマスクにして露出したオーミックコンタクト層60bを除去して下部のアクティブ層60aを露出する工程を行う。

【0049】

図6Aと図6B及び図6Cは、第4マスク工程と第5マスク工程を示した図面であって、それぞれ図3のIVA-IVA線、IVB-IVB線、IVC-IVC線に沿って切断した面に対応する断面図である。

【0050】

前記ソース及びドレイン電極64、66とデータ配線68が形成された基板50の全面に窒化シリコーン(SiNx)と酸化シリコーン(SiO<sub>2</sub>)を含む無機絶縁物質グループのうちから選択された一つを蒸着して保護膜74を形成する。

【0051】

前記保護膜74が形成された基板50の全面にブラック樹脂を塗布した後第4マスク工程でパターニングして、前記ソース及びドレイン電極64、66と露出したアクティブ層60aに対応してブラックマトリックス76を形成する。

【0052】

場合によって、前記ブラックマトリックス76は前記ゲート配線52とデータ配線68に対応してさらに形成することができる。

【0053】

次に、カラー樹脂を塗布して第5マスク工程を介してパターニングして、カラーフィルター層、例えば、緑色カラーフィルター78bを画素領域Pの保護膜74上部に形成する

【0054】

図7Aと図7B及び図7Cは、第6マスク工程を示した図面であって、それぞれ図3のIVA-IVA線、IVB-IVB線、IVC-IVC線に沿って切断した面に対応する断面図である。

【0055】

次に、前記カラーフィルター78bが形成された基板50の全面にベンゾシクロブテン(BCB)とアクリル系樹脂を含む平坦化膜80を形成して第6マスク工程でパターニングして、前記ドレイン電極66を露出するドレインコンタクトホール82と、前記金属パターン72を露出するストレージコンタクトホール84と、前記ゲートパッド56を露出するゲートパッドコンタクトホール86と、前記データパッド70を露出するデータパッドコンタクトホール88を形成する。

【0056】

図8Aと図8B及び図8Cは、第7マスク工程を示した図面であって、それぞれ図3のIVA-IVA線、IVB-IVB線、IVC-IVC線に沿って切断した面に対応する断面図である。

【0057】

図示したように、前記平坦化膜80が形成された基板50の全面にインジウム-スズ-オキサイド(ITO)とインジウム-ジンク-オキサイド(IZO)を含む透明な導電性金属グループのうちから選択された一つを蒸着してパターニングして、前記ドレイン電極66と前記金属パターン72に同時に接触しながら前記画素領域Pに位置した画素電極9

10

20

30

40

50

2と、前記ゲートパッド56と接触するゲートパッド端子94と前記データパッド70と接触するデータパッド端子96が形成される。

【0058】

前述したような7マスク工程を介して従来によるCOT構造の液晶表示装置用アレイ基板を製作することができる。

【0059】

前述した工程は、前記ブラックマトリックスと前記カラーフィルターを形成するための2マスク工程を除外すれば、画素電極を含むアレイ配線及び電極を形成するために5マスク工程を行っている。

【0060】

一般的に、液晶パネルを製作するにおいて工程数が多ければ工程時間が遅れ工程費用の高くなる問題がある同時に不良確率が大きくなり、製品の収率が低下する問題が発生する。

【発明の開示】

【発明が解決しようとする課題】

【0061】

本発明は前述した問題を解決するための目的で提案されたもので、カラーフィルターをアレイ基板に形成したCOT構造の液晶表示装置を製作する際、工程を単純化する方法を提案する。

【課題を解決するための手段】

【0062】

前述した目的を達成するための本発明による液晶表示装置の製造方法は、基板上に第1マスク工程でゲート配線とゲート電極を形成する段階と、前記ゲート配線とゲート電極を含む基板の全面にゲート絶縁膜を形成する段階と、前記ゲート絶縁膜上部に単一マスクを利用した第2マスク工程で、アクティブ層とオーミックコンタクト層、ソース電極、ドレイン電極、そして前記ゲート配線と交差して画素領域を定義するデータ配線を形成する段階と、前記ソース及びドレイン電極とデータ配線を含む基板全面に第1保護膜を形成する段階と、前記アクティブ層上部の第1保護膜上に第3マスク工程で、ブラックマトリックスを形成する段階と、前記画素領域の前記第1保護膜上部に第4マスク工程で、カラーフィルター層を形成する段階と、前記カラーフィルター及びブラックマトリックスが形成された基板の全面に第2保護膜を形成する段階と、第5マスク工程で、前記画素領域及び前記ドレイン電極の一部に対応する第2保護膜を露出する感光パターンを形成する段階と、前記感光パターンをマスクとして前記露出した第2保護膜を除去して、前記第2保護膜に接触する第1保護膜部分を除去して前記ドレイン電極の一部を露出する段階と、前記ドレイン電極の露出した部分を含み、前記感光パターンが形成された基板全面に透明導電層を形成する段階と、前記感光パターンと前記感光パターン上部の透明導電層を除去して、前記画素領域内に前記ドレイン電極の露出した部分と接触する画素電極を形成する段階を含む。

【0063】

また、本発明による液晶表示装置は、基板と、前記基板上に形成されたゲート配線とゲート電極と、前記ゲート配線とゲート電極上部のゲート絶縁膜と、前記ゲート電極上部のゲート絶縁膜上に形成されたアクティブ層と、前記アクティブ層上部のオーミックコンタクト層と、前記オーミックコンタクト層上部に形成されたソース電極とドレイン電極、そして前記ゲート配線と交差して画素領域を定義するデータ配線と、前記ソース及びドレイン電極とデータ配線の上部の第1保護膜と、前記アクティブ層上部の前記第1保護膜上に形成されたブラックマトリックスと、前記画素領域の第1保護膜上に形成されたカラーフィルター層と、前記ブラックマトリックス及びカラーフィルター層上部に形成されて、前記画素領域のカラーフィルター層を露出する第2保護膜と、前記第2保護膜と水平に重畳することなく前記第2保護膜と同じ層上に位置し、前記画素領域の露出したカラーフィルター層上部に形成されて、前記ドレイン電極と連結された画素電極を含む。

10

20

30

40

50

## 【発明の効果】

## 【0064】

したがって、本発明によるCOT構造液晶表示装置用アレイ基板は、第一に、COT構造であるのでブラックマトリックスを上部基板に構成する時の合着マージンを開口領域で用いることができるので開口率改善及びこれによる輝度が改善される効果がある。

## 【0065】

第二に、薄膜トランジスタアレイ部を減少させた工程を介して製作することによって、工程単純化を介した工程時間の短縮及び固定費用を低めることができると同時に工程中発生する不良確率を低めることができ、製品の収率を改善することができる効果がある。

## 【発明を実施するための最良の形態】

10

## 【0066】

以下、添付した図面を参照して、本発明による望ましい実施の形態を説明する。

- - 第1の実施の形態 - -

## 【0067】

本発明の特徴は、カラーフィルター及びブラックマトリックスを含むアレイ基板の構成で、前記ブラックマトリックス及びカラーフィルターを除外したアレイ基板の構成を3マスク工程で製作することを特徴とする。

## 【0068】

以下、工程断面図を参照して本発明によるCOT構造の液晶表示装置用アレイ基板の製造工程を説明する。

20

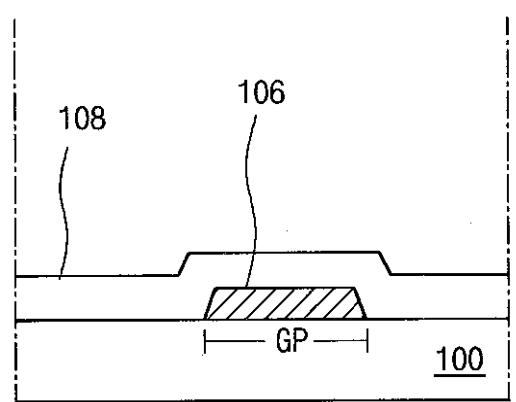

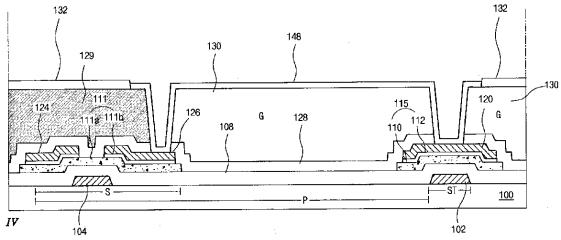

## 【0069】

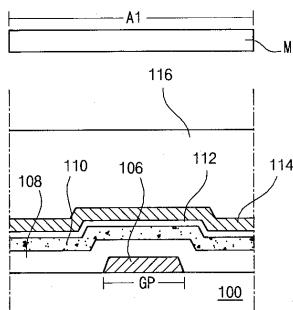

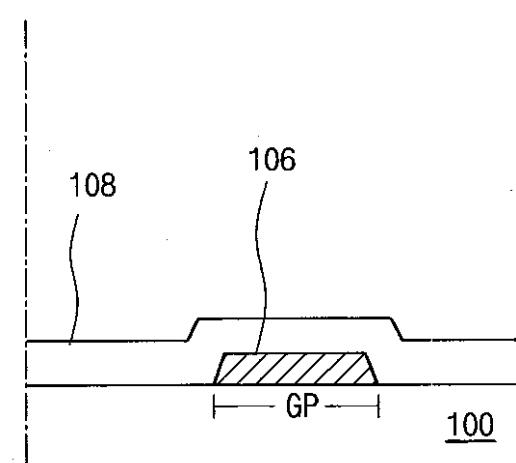

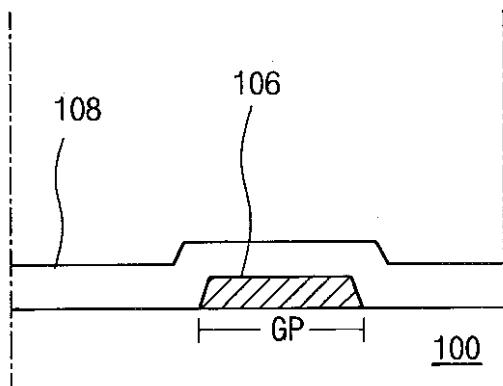

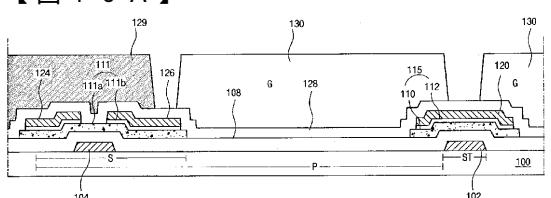

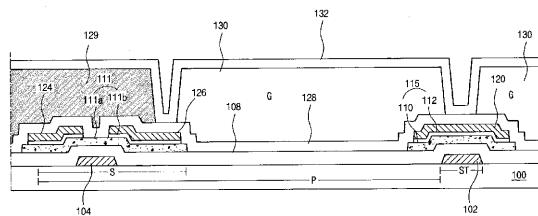

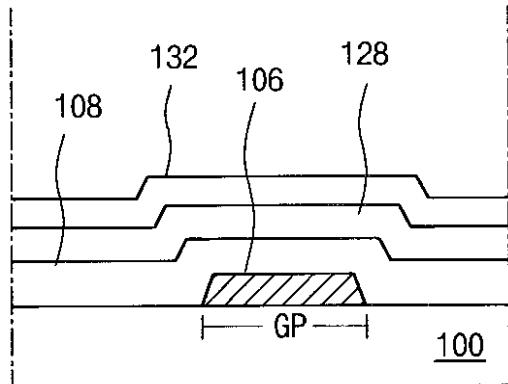

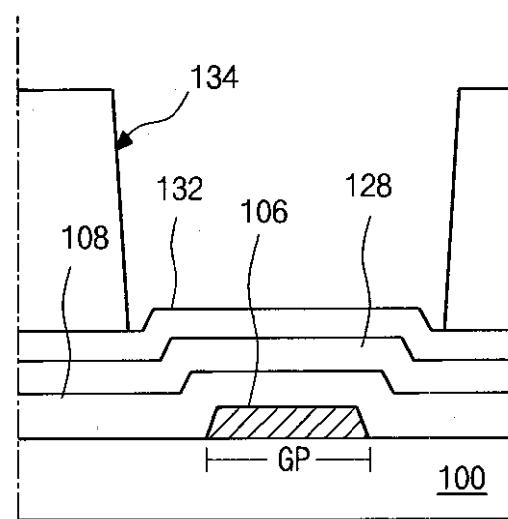

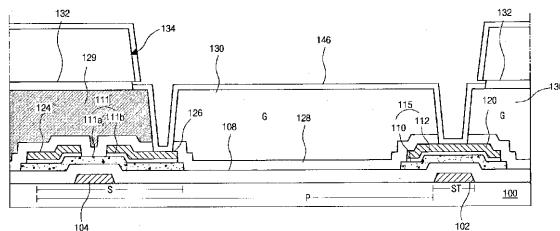

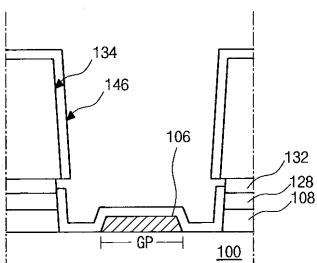

図9A、図9B及び図9Cは、本発明の第1マスク工程を示した図面であって、それぞれ画素領域と、ゲートパッド領域及びデータパッド領域に対応する断面図である。

## 【0070】

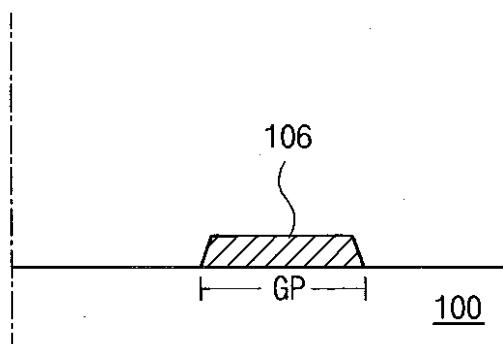

図示したように、基板100上にスイッチング領域Sを含む画素領域Pを定義して、ゲートパッド領域GPとデータパッド領域DPと、前記画素領域Pの一部に対応するストレージ領域STを定義する。

## 【0071】

前記複数の領域S、ST、P、GP、DPが定義された基板100上に、アルミニウム(A1)、アルミニウム合金(A1Nd)、銅(Cu)、タンゲステン(W)、クロム(Cr)、モリブデン(Mo)等を含む導電性金属グループのうちから選択された一つまたはそれ以上の物質を蒸着して第1マスク工程によりパターニングして、ゲート電極104とゲート配線102を形成する。ゲート電極104は、前記画素領域Pのスイッチング領域Sに位置して、ゲート配線102の一部は、前記ストレージ領域STに対応する。ゲート配線102は、前記ゲート電極104と連結されて、一端にゲートパッド106を含むが、ゲートパッド106はゲートパッド領域GPに位置する。

30

## 【0072】

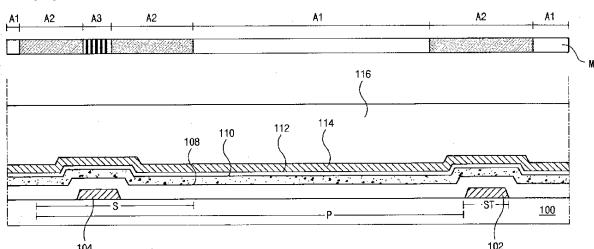

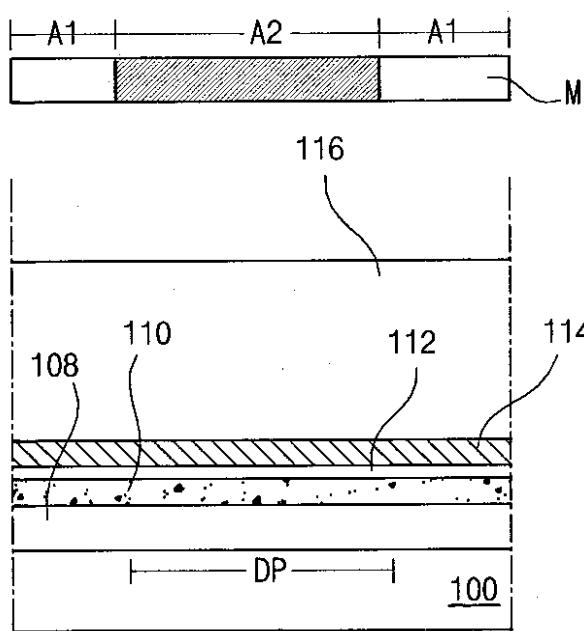

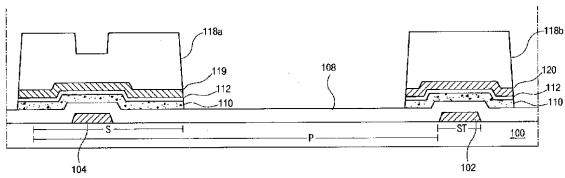

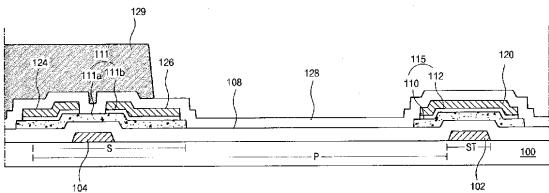

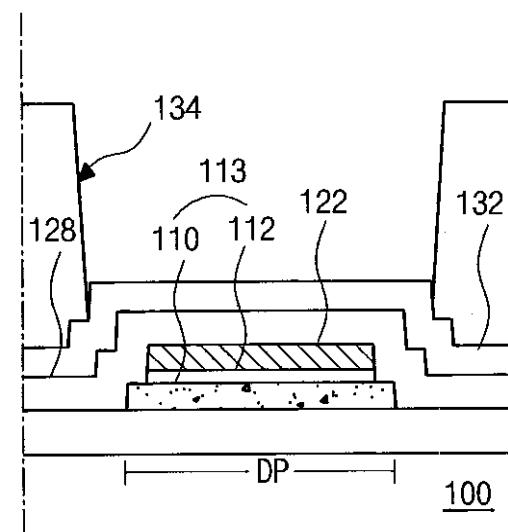

図10A、図10B、図10Cないし図14A、図14B、図14Cは、第2マスク工程を工程順序に従って示した図面であって、それぞれ画素領域と、ゲートパッド領域及びデータパッド領域に対応する断面図である。

40

## 【0073】

まず、図10A、図10B及び図10Cに示したように、前記ゲートパッド及びゲート配線106、102とゲート電極104が形成された基板100の全面に、窒化シリコーン(SiNx)と酸化シリコーン(SiO<sub>2</sub>)を含む無機絶縁物質グループのうちから選択された一つまたはそれ以上の物質を蒸着してゲート絶縁膜108を形成する。

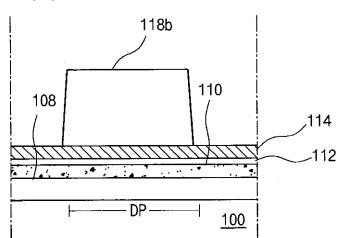

## 【0074】

続いて、前記ゲート絶縁膜108が形成された基板100の全面に、純粋非晶質シリコーン(a-Si:H)と不純物非晶質シリコーン(n+またはp+またはa-Si:H)を順次蒸着して、純粋非晶質シリコーン層110と不純物非晶質シリコーン層112を形成して、前記不純物非晶質シリコーン層112の上部に前述した導電性金属を蒸着して導

50

電性金属層 114 を形成する。

【0075】

次に、前記導電性金属層 114 が形成された基板 100 の全面に、フォトレジストを塗布して感光層 116 を形成する。

【0076】

前記感光層 116 の離隔された上部に遮断部 A2 と透過部 A1 と半透過部 A3 で構成されたマスク M を位置させる。

【0077】

ここで、前記マスク M の遮断部 A2 は、スイッチング領域 S とストレージ領域 ST とデータパッド領域 DP に対応するようにし、前記半透過部 A3 は、前記スイッチング領域 S のうち前記ゲート電極 104 の中心一部領域に位置するように構成する。それ以外の領域には、前記透過部 A1 が対応するようにする。

【0078】

前記感光層 116 がポジティブ特性を有したと仮定した場合、前記マスク M の透過部 A1 に対応する感光層 116 は完全に露光されて、前記マスク M の半透過部 A3 に対応する感光層 116 は一部だけが露光される特性を有する。

【0079】

前記マスク M の上部に光を照射して下部の感光層 116 を露光して現像する工程を行う。

【0080】

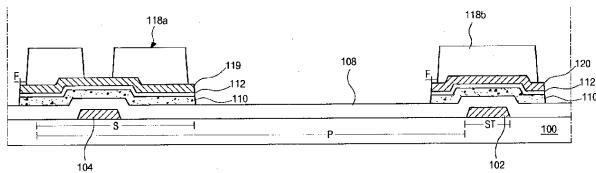

このようにすれば、図 11A、図 11B 及び図 11C に示したように、前記スイッチング領域 S に対応して互いに異なる第 1 及び第 2 厚さを有する第 1 感光パターン 118a と、前記ストレージ領域 ST と、データパッド領域 DP に対応して第 1 感光パターン 118a の第 1 厚さと同様な厚さの第 2 感光パターン 118b を形成する。第 1 感光パターン 118a の第 1 厚さは、図 10A のマスク M の遮断部 A2 に対応し、第 2 厚さは第 1 厚さより薄いし図 10A のマスク M の透過部 A3 に対応する。

【0081】

ここで、前記データパッド領域 DP に形成された第 2 感光パターン 118b は、前記第 1 感光パターン 118a と延長されて前記ゲート配線 102 とは垂直方向で延長されて形成された形状である。

【0082】

次に、図 12A、図 12B 及び図 12C に示したように、前記第 1 及び第 2 感光パターン 118a、118b の周辺で露出した金属層 114 とその下部の不純物非晶質シリコーン層 112 と純粋非晶質シリコーン層 110 を除去する工程を行う。

【0083】

このようにすれば、前記スイッチング領域 S に対応する第 1 感光パターン 118a の下部にはパターニングされたソースドレインパターン 119 が形成され、前記ストレージ領域 ST に対応する第 2 感光パターン 118b の下部にはアイランド状の金属パターン 120 が形成され、前記データパッド領域 DP に対応する第 2 感光パターン 118b の下部には前記ソースドレインパターン 119 と連結されて一方向に延長されて一端にデータパッド 122 を含むデータ配線（図示せず）が形成される。

【0084】

そして、ソースドレインパターン 119 と金属パターン 120 及びデータパッド 122 下部にはパターニングされた不純物非晶質シリコーン層 112 と純粋非晶質シリコーン層 110 が残るようになる。

【0085】

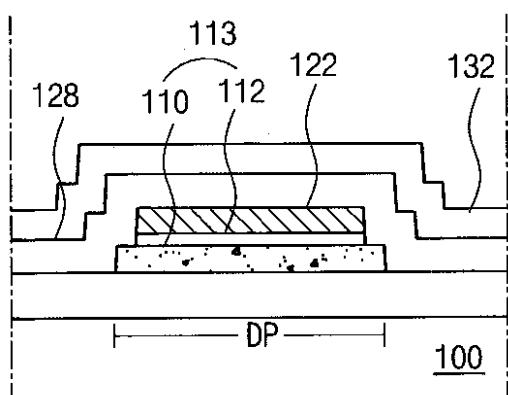

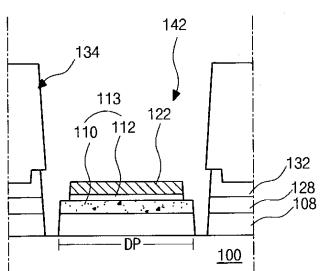

図 13A、図 13B 及び図 13C は、前記第 1 及び第 2 感光パターン 118a、118b を灰化（ashing）する工程を示した図面である。

【0086】

図示したように、前記第 1 感光パターン 118a の第 2 厚さを完全に除去することによ

10

20

30

40

50

つて、下部のソースドレインパターン 119 を露出する工程を行う。ここで、第 1 感光パターン 118a の第 1 厚さ及び第 2 感光パターン 118b も一部除去されて厚さが薄くなり、第 1 及び第 2 感光パターン 118a、118b の縁も除去される。

【0087】

したがって、前記ソースドレインパターン 119 はその周辺 F も一定領域露出して、前記金属パターン 120 とデータパッド 122 及びデータ配線（図示せず）の周辺 F も一定領域露出する形状になる。

【0088】

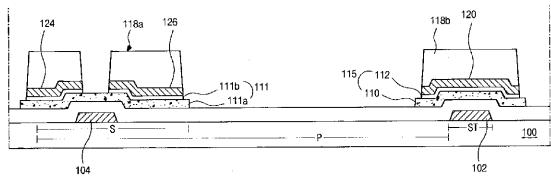

図 14A、図 14B 及び図 14C に示したように、露出したソースドレインパターンを除去して、その下部の不純物非晶質シリコーン層 112 を除去する工程を行う。

10

【0089】

このようにすれば、前記ゲート電極 104 に対応して離隔されたソース電極（124）とドレイン電極 126 が形成される。

【0090】

一方、ソース及びドレイン電極 124、126 とデータパッド 122 及び金属パターン 120 下部に第 1 半導体パターン 111 と第 2 半導体パターン 113 及び第 3 半導体パターン 115 がそれぞれ形成される。半導体パターン 111、113、115 のそれぞれは不純物非晶質シリコーン層 112 と純粋非晶質シリコーン層 110 を含む。

【0091】

ここで、前記ソース及びドレイン電極 124、126 の下部に形成された第 1 半導体パターン 111 の純粋非晶質シリコーン層をアクティブ層 111a といい、不純物非晶質シリコーン層をオーミックコンタクト層 111b という。不純物非晶質シリコーン層と純粋非晶質シリコーン層を含んで、第 1 及び第 2 半導体パターン 111、113 と連結されるまた他の半導体パターンがデータ配線下部にさらに形成されることもできる。

20

【0092】

次に、前記ソース及びドレイン電極 124、126 と、金属パターン 120 と、データパッド 122 及びデータ配線（図示せず）の上部に位置した第 1 及び第 2 感光パターン 118a、118b を除去する工程を行う。

【0093】

前述したような工程を介して本発明による第 2 マスク工程を完了する。

30

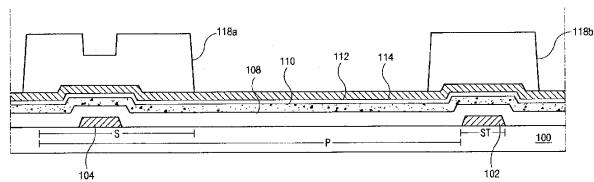

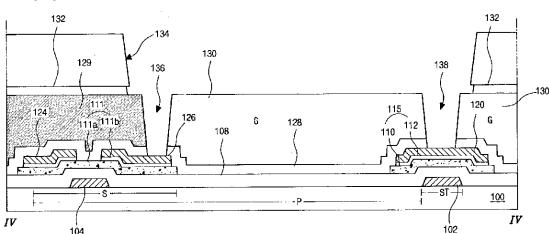

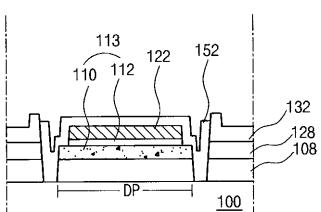

【0094】

図 15A、図 15B 及び図 15C は、本発明の第 3 マスク工程を示した図面であって、それぞれ画素領域と、ゲートパッド領域及びデータパッド領域に対応する断面図である。

【0095】

図 15A、図 15B 及び図 15C に示したように、前記ソース及びドレイン電極 124、126 とデータパッド 122 及びデータ配線（図示せず）が形成された基板 100 の全面に、窒化シリコーン（ $\text{SiN}_x$ ）と酸化シリコーン（ $\text{SiO}_2$ ）を含む無機絶縁物質グループのうちから選択された一つを蒸着して第 1 保護膜 128 を形成する。前記第 1 保護膜 128 が形成された基板 100 の全面に、ブラック樹脂を塗布した後、第 3 マスク工程でパターニングして前記スイッチング領域 S に対応してブラックマトリックス 129 を形成する。

40

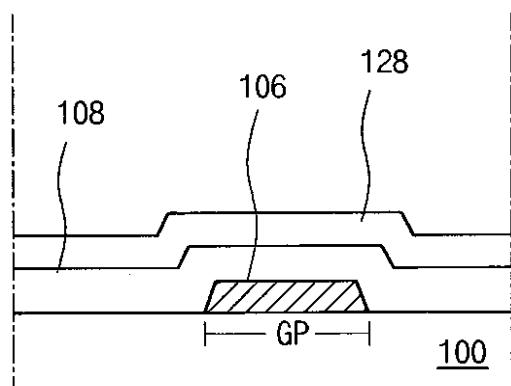

【0096】

次に、図 16A、図 16B 及び図 16C は、本発明の第 4 マスク工程を示した図面であって、それぞれ画素領域と、ゲートパッド領域及びデータパッド領域に対応する断面図である。

【0097】

図 16A、図 16B 及び図 16C に示したように、第 1 保護膜 128 上部にカラー樹脂を塗布して第 4 マスク工程でパターニングして前記画素領域 P に対応するカラーフィルター層、例えば緑色カラーフィルター 130 を形成する。

【0098】

50

前記カラーフィルター層は、赤、緑、青色カラーフィルターを含み、複数の画素領域に対応して赤色（RED）と緑色（GREEN）及び青色（BLUE）のカラーフィルターを順次形成するのが一般的である。ここで、赤色及び青色カラーフィルターは、緑色カラーフィルター130と同一な方法で形成される。

【0099】

前記ブラックマトリックス129とカラーフィルター130を形成する時は、前記ドレイン電極126の一部と前記金属パターン120の一部に対応する部分の第1保護膜128が露出するようにする。ゲートパッド106及びデータパッド122上部にはカラーフィルターを形成しない。

【0100】

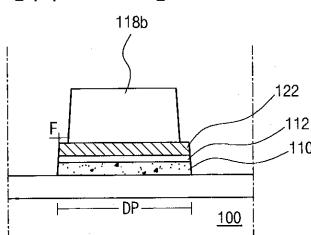

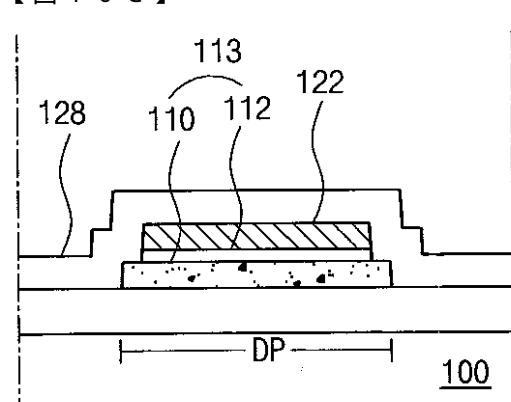

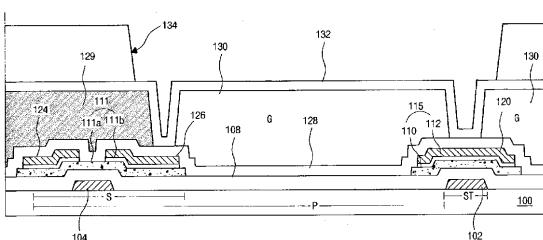

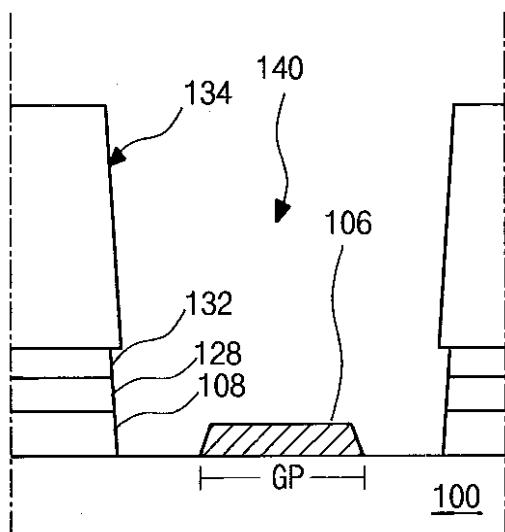

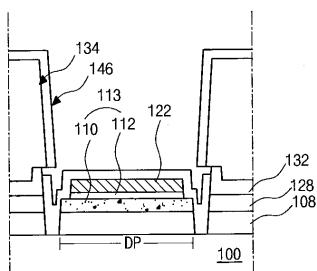

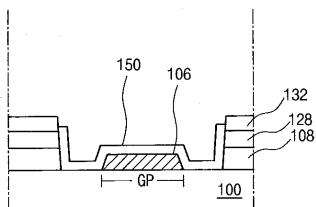

次に、図17A、図17B、図17Cないし図21A、図21B、図21Cは、本発明の第5マスク工程を示した図面であって、それぞれ画素領域と、ゲートパッド領域及びデータパッド領域に対応する断面図である。

【0101】

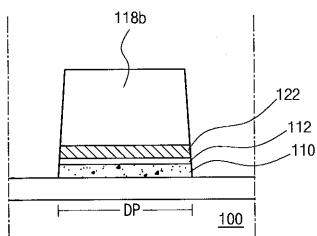

図17A、図17B及び図17Cに示したように、前記ブラックマトリックス129とカラーフィルター130が形成された基板100の全面に、前述した絶縁物質を蒸着して第2保護膜132を形成する。

【0102】

図18A、図18B及び図18Cに示したように、前記第2保護膜132が形成された基板100の全面に、フォトレジストを塗布した後、第5マスク工程でパターニングして、画素領域Pと前記ドレイン電極126の一部、前記金属パターン120の一部、前記データパッド122及びゲートパッド106に対応する第2保護膜132が露出されるように感光パターン134を形成する。

【0103】

次に、図19A、図19B及び図19Cに示したように、前記スイッチング領域Sとストレージ領域STに対応して、前記感光パターン134の間で露出した第2保護膜132とその下部の第1保護膜128を除去してドレインコンタクトホール136とストレージコンタクトホール138を形成し、前記ゲートパッド領域GPに対応して第2保護膜132とその下部の第1保護膜128とゲート絶縁膜108を除去してゲートパッドコンタクトホール140を形成し、前記データパッド領域DPに対応して第2保護膜132とその下部の第1保護膜128を除去してデータパッドコンタクトホール142を形成する。

【0104】

図20A、図20B及び図20Cに示したように、前記感光パターン134が形成された基板100の全面に、インジウム-スズ-オキサイド(ITO)とインジウム-ジンク-オキサイドIZOを含む透明な導電性金属グループのうちから選択された一つを蒸着して透明な金属層146を形成する。

【0105】

次に、図21A、図21B及び図21Cに示したように、前記感光パターン(図20A、図20B、図20Cの134)を除去する工程を行い、前記ドレイン電極126と金属パターン120に同時に接触しながら前記画素領域Pに位置する画素電極148を形成する。

【0106】

同時に、前記ゲートパッド106と接触するアイランド状のゲートパッド端子150、そして前記データパッド122と接触するアイランド状のデータパッド端子152を形成する。

【0107】

前述したような工程を介して本発明によるCOT構造の液晶表示装置用アレイ基板を製作することができ、前述したアレイ基板に透明な共通電極を形成した第2基板を合着する工程を介してCOT構造の液晶表示装置を製作することができる。

【0108】

前述した本発明によるC O T構造の液晶表示装置用アレイ基板は、総5マスク工程で製作され、従来に比べて製造工程が減少し費用及び時間を減らすことができる。

【0109】

一方、柱状のスペーサーを本発明のアレイ基板上部にさらに形成することができる。

【0110】

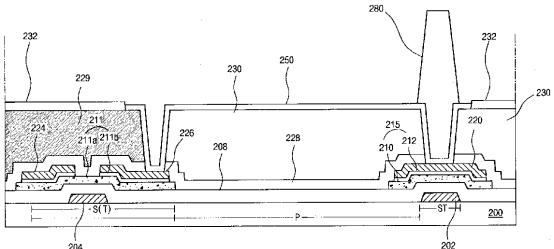

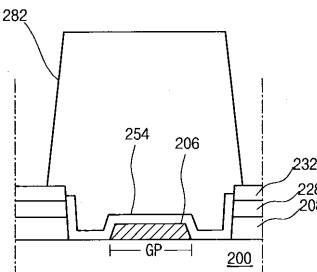

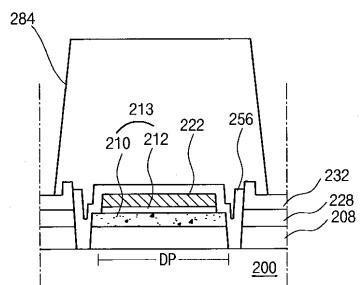

図22A、図22B及び図22Cは、本発明による柱状のスペーサーを含むアレイ基板を示したものであって、それぞれ画素領域と、ゲートパッド領域及びデータパッド領域に対応する断面図である。

【0111】

図示したように、絶縁基板200上にスイッチング領域Sを含む画素領域Pと、ストレージ領域S T、ゲートパッド領域G P及びデータパッド領域D Pが定義される。 10

【0112】

ゲート配線202とゲート電極204及びゲートパッド206が基板200上に形成される。ゲート電極204はスイッチング領域Sに位置し、ゲート配線202の一部はストレージ領域S Tに位置し、ゲートパッド206はゲートパッド領域G Pに位置する。図示しなかったが、ゲート電極204はゲート配線202に連結し、ゲートパッド206はゲート配線202の一端に位置する。

【0113】

ゲート絶縁膜208はゲート配線202とゲート電極204及びゲートパッド206上部に形成される。 20

【0114】

第1、第2、第3半導体パターン211、213、215はゲート絶縁膜208上部のスイッチング領域S、データパッド領域D P及びストレージ領域S Tにそれぞれ形成される。半導体パターン211、213、215のそれぞれは純粋非晶質シリコーン層210と不純物非晶質シリコーン層212を含む。第1半導体パターン211の純粋非晶質シリコーン層はアクティブ層211aになって、第1半導体パターン211の不純物非晶質シリコーン層はオーミックコンタクト層211bになる。

【0115】

ソース電極224とドレイン電極226は第1半導体パターン211上部に形成され、データパッド222は第2半導体パターン213上部に形成され、金属パターン220は第3半導体パターン215上部に形成される。図示しなかったが、データ配線はソース及びドレイン電極224、226とデータパッド222及び金属パターン220と同じ層上に形成される。データ配線はゲート配線202と交差してソース電極224に連結し、データパッド222はデータ配線の一端に位置する。金属パターン220はゲート配線202と重なって、金属パターン220とゲート配線202を第1及び第2キャパシター電極にするストレージキャパシターが形成される。 30

【0116】

ゲート電極204と第1半導体パターン211、ソース電極224及びドレイン電極226は薄膜トランジスタTを形成する。

【0117】

第1保護膜228はソース及びドレイン電極224、226、データパッド222及び金属パターン220上部に形成される。続いて、ブラックマトリックス229はスイッチング領域Sにある薄膜トランジスタT上部の第1保護膜228上に形成される。カラーフィルター層230はスイッチング領域Sを除外した画素領域Pの第1保護膜228上に形成される。カラーフィルター層230は赤、緑、青色カラーフィルターを含み、各カラーフィルターは画素領域Pに対応する。カラーフィルターはそれぞれの画素領域に順次形成される。 40

【0118】

第2保護膜232はブラックマトリックス229とカラーフィルター層230上部に形成される。第2保護層232はスイッチング領域Sを除外した画素領域Pとストレージ領 50

域 S T、ゲートパッド領域 G P 及びデータパッド領域 D P を露出する。

【 0 1 1 9 】

画素電極 250 とゲートパッド端子 254 及びデータパッド端子 256 は第 2 保護膜 232 で露出した領域のブラックマトリックス 229 及びカラーフィルター層 230 上部に形成される。画素電極 250 とゲートパッド端子 254 及びデータパッド端子 256 は透明導電物質で形成される。画素電極 250 はドレイン電極 226 及び金属パターン 220 と接触し、ゲートパッド端子 254 はゲートパッド 206 と接触して、データパッド端子 256 はデータパッド 222 と接触する。

【 0 1 2 0 】

柱状のスペーサー 280 は画素電極 250 を含む基板 200 上に形成される。スペーサー 280 はゲート配線 202 とデータ配線 (図示せず) に対応する。スペーサー 280 は感光性や非感光性樹脂を基板 200 全面に塗布してマスクを利用したフォトエッチング工程を介してパターニングして形成される。

【 0 1 2 1 】

第 1 遮断層 282 と第 2 遮断層 284 はゲートパッド 206 とデータパッド 222 上部にスペーサー 280 と同じ層でそれぞれ形成される。ゲートパッド 206 とデータパッド 222 がアルミニウム (A1) を含む金属物質で形成される時、スペーサー 280 をパターニングするためのエッチング液により、ゲートパッド 206 とゲートパッド端子 254 間またはデータパッド 222 とデータパッド端子 256 間にガルバニック現象が発生して、ゲートパッド 206 またはデータパッド 222 が除去することができる。したがって、このような問題を防止するために、第 1 遮断層 282 はゲートパッド 206 を覆っており、第 2 遮断層 284 はデータパッド 222 を覆う。

【 0 1 2 2 】

ゲートパッド端子 254 とデータパッド端子 256 に信号を印加するために、第 1 及び第 2 遮断層 282、284 は次の段階で除去される。

【 0 1 2 3 】

スペーサー 280 と第 1 及び第 2 遮断層 282、284 を除外した図 22A と図 22B 及び図 22C のアレイ基板は前述したのと同一な工程を介して製造されることができる。

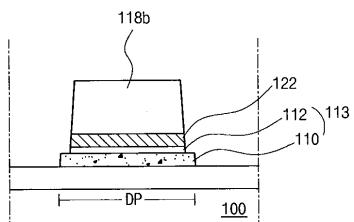

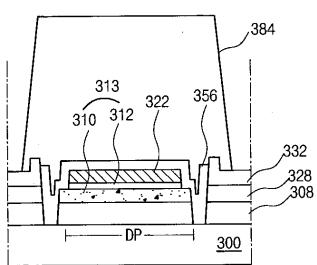

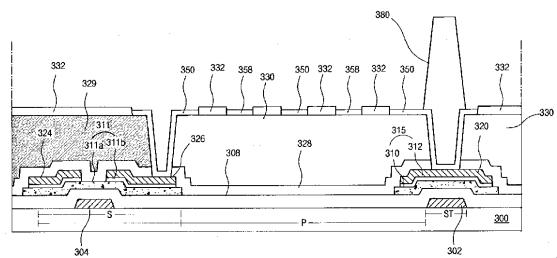

【 0 1 2 4 】

図 23A、図 23B 及び図 23C は、本発明の他の実施の形態によるアレイ基板を示したものであって、それぞれ画素領域と、ゲートパッド領域及びデータパッド領域に対応する断面図である。前記アレイ基板は画素電極と共に電極を含み、また柱状のスペーサーを含む。

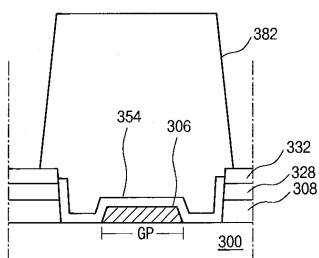

【 0 1 2 5 】

図示したように、絶縁基板 300 上にスイッチング領域 S を含む画素領域 P と、ストレージ領域 S T、ゲートパッド領域 G P 及びデータパッド領域 D P が定義される。

【 0 1 2 6 】

ゲート配線 302 とゲート電極 304 及びゲートパッド 306 が基板 300 上に形成される。ゲート電極 304 はスイッチング領域 S に位置して、ゲート配線 302 の一部はストレージ領域 S T に位置し、ゲートパッド 306 はゲートパッド領域 G P に位置する。図示しなかったが、ゲート電極 304 はゲート配線 302 に連結して、ゲートパッド 306 はゲート配線 302 の一端に位置する。

【 0 1 2 7 】

ゲート絶縁膜 308 がゲート配線 302 とゲート電極 304 及びゲートパッド 306 上部に形成される。

【 0 1 2 8 】

第 1、第 2、第 3 半導体パターン 311、313、315 はゲート絶縁膜 308 上部のスイッチング領域 S、データパッド領域 D P 及びストレージ領域 S T にそれぞれ形成される。半導体パターン 311、313、315 のそれぞれは純粋非晶質シリコーン層 310 と不純物非晶質シリコーン層 312 を含む。第 1 半導体パターン 311 の純粋非晶質シリ

10

20

30

40

50

コーン層はアクティブ層 311a になって、第 1 半導体パターン 311 の不純物非晶質シリコーン層はオーミックコンタクト層 311b になる。

【0129】

ソース電極 324 とドレイン電極 326 は第 1 半導体パターン 311 上部に形成され、データパッド 322 は第 2 半導体パターン 313 上部に形成され、金属パターン 320 は第 3 半導体パターン 315 上部に形成される。図示しなかったが、データ配線はソース及びドレイン電極 324、326 とデータパッド 322 そして金属パターン 320 と同じ層上に形成される。データ配線はゲート配線 302 と交差してソース電極 324 に連結し、データパッド 322 はデータ配線の一端に位置する。金属パターン 320 はゲート配線 302 と重なって、金属パターン 320 とゲート配線 302 を第 1 及び第 2 キャパシター電極にするストレージキャパシターが形成される。

10

【0130】

ゲート電極 304 と第 1 半導体パターン 311、ソース電極 324 及びドレイン電極 326 は薄膜トランジスタを形成する。

【0131】

第 1 保護膜 328 はソース及びドレイン電極 324、326、データパッド 322 及び金属パターン 320 上部に形成される。続いて、ブラックマトリックス 329 はスイッチング領域 S にある薄膜トランジスタ上部の第 1 保護膜 328 上に形成される。カラーフィルター層 330 はスイッチング領域 S を除外した画素領域 P の第 1 保護膜 328 上に形成される。カラーフィルター層 330 は、赤、緑、青色カラーフィルターを含み、各カラーフィルターは画素領域 P に対応する。カラーフィルターはそれぞれの画素領域に順次形成される。

20

【0132】

第 2 保護膜 332 はブラックマトリックス 329 とカラーフィルター層 330 上部に形成される。第 2 保護層 332 はスイッチング領域 S を除外した画素領域 P とストレージ領域 S T、ゲートパッド領域 G P そしてデータパッド領域 D P を露出する。第 2 保護膜 332 は画素領域 P でパターニングされてカラーフィルター層 330 を選択的に露出する。

【0133】

画素電極 350 と共通電極 358、ゲートパッド端子 354 及びデータパッド端子 356 は、第 2 保護膜 332 で露出した領域のブラックマトリックス 329 及びカラーフィルター層 330 上部に形成される。画素電極 350 と共通電極 358 は画素領域 P に位置し、相互に平行するように離隔されている。画素電極 350 は共通電極 358 と互い違うように配置される。画素電極 350 と共通電極 358 のそれぞれは複数の部分を含む。画素電極 350 はドレイン電極 326 及び金属パターン 320 と接触し、ゲートパッド端子 354 はゲートパッド 306 と接触して、データパッド端子 356 はデータパッド 322 と接触する。画素電極 350 と共通電極 358、ゲートパッド端子 354 及びデータパッド端子 256 は透明導電物質で形成される。

30

【0134】

共通配線（図示せず）がゲート配線 302 に平行するように形成されて共通電極 358 と連結されることができる。

40

【0135】

一方、柱状のスペーサー 380 は画素電極 350 を含む基板 300 上に形成される。スペーサー 380 はゲート配線 302 とデータ配線（図示せず）に対応する。スペーサー 380 は感光性や非感光性樹脂を基板 300 全面に塗布してマスクを利用したフォトエッチング工程を介してパターニングして形成される。

【0136】

ゲートパッド 306 とデータパッド 322 上部に、第 1 遮断層 382 と第 2 遮断層 384 がスペーサー 380 と同じ層でそれぞれ形成される。ゲートパッド 306 とデータパッド 322 がアルミニウム（A1）を含む金属物質で形成される時、スペーサー 380 をパターニングするためのエッチング液により、ゲートパッド 306 とゲートパッド端子 35

50

4間またはデータパッド322とデータパッド端子356間にガルバニック現象が発生して、ゲートパッド306またはデータパッド322が除去することができる。したがって、このような問題を防止するために、第1遮断層382はゲートパッド306を覆っており、第2遮断層384はデータパッド322を覆う。一方、前記遮断層382、384は前記共通配線の終端リンク部に対応して形成することができる。

## 【0137】

ゲートパッド端子354とデータパッド端子356に信号を印加するために、第1及び第2遮断層382、384は次の段階で除去される。

## 【図面の簡単な説明】

## 【0138】

10

【図1】一般的な液晶表示装置を概略的に示した分解斜視図である。

【図2】一般的な液晶表示装置を概略的に示した断面図である。

【図3】一般的なCOT構造の液晶表示装置用アレイ基板の一部を拡大した拡大平面図である。

【図4A】従来の第1及び第2マスク工程を示した図面であって、図3のIVA-IVA線に沿って切断した面に対応する工程断面図である。

【図4B】従来の第1及び第2マスク工程を示した図面であって、図3のIVB-IVB線に沿って切断した面に対応する工程断面図である。

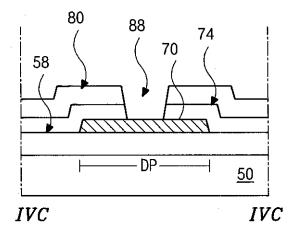

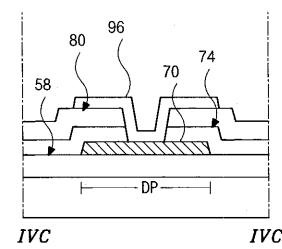

【図4C】従来の第1及び第2マスク工程を示した図面であって、図3のIVC-IVC線に沿って切断した面に対応する工程断面図である。

20

【図5A】従来の第3マスク工程を示した図面であって、図3のIVA-IVA線に沿って切断した面に対応する工程断面図である。

【図5B】従来の第3マスク工程を示した図面であって、図3のIVB-IVB線に沿って切断した面に対応する工程断面図である。

【図5C】従来の第3マスク工程を示した図面であって、図3のIVC-IVC線に沿って切断した面に対応する工程断面図である。

【図6A】従来の第4及び第5マスク工程を示した図面であって、図3のIVA-IVA線に沿って切断した面に対応する工程断面図である。

【図6B】従来の第4及び第5マスク工程を示した図面であって、図3のIVB-IVB線に沿って切断した面に対応する工程断面図である。

30

【図6C】従来の第4及び第5マスク工程を示した図面であって、図3のIVC-IVC線に沿って切断した面に対応する工程断面図である。

【図7A】従来の第6マスク工程を示した図面であって、図3のIVA-IVA線に沿って切断した面に対応する工程断面図である。

【図7B】従来の第6マスク工程を示した図面であって、図3のIVB-IVB線に沿って切断した面に対応する工程断面図である。

【図7C】従来の第6マスク工程を示した図面であって、図3のIVC-IVC線に沿って切断した面に対応する工程断面図である。

【図8A】従来の第7マスク工程を示した図面であって、図3のIVA-IVA線に沿って切断した面に対応する工程断面図である。

40

【図8B】従来の第7マスク工程を示した図面であって、図3のIVB-IVB線に沿って切断した面に対応する工程断面図である。

【図8C】従来の第7マスク工程を示した図面であって、図3のIVC-IVC線に沿って切断した面に対応する工程断面図である。

【図9A】本発明の第1マスク工程を示した図面であって、画素領域に対応する工程断面図である。

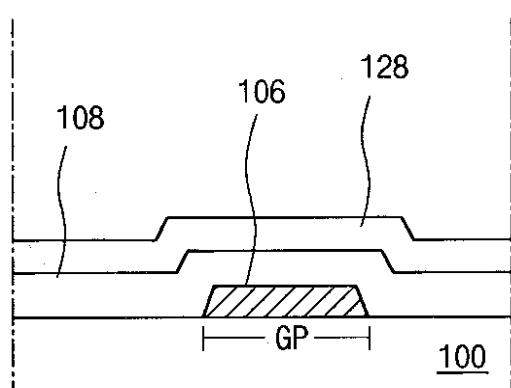

【図9B】本発明の第1マスク工程を示した図面であって、ゲートパッド領域に対応する工程断面図である。

【図9C】本発明の第1マスク工程を示した図面であって、データパッド領域に対応する工程断面図である。

50

【図10A】本発明の第2マスク工程を工程順序によって示す図面であって、画素領域に対応する工程断面図である。

【図10B】本発明の第2マスク工程を工程順序によって示す図面であって、ゲートパッド領域に対応する工程断面図である。

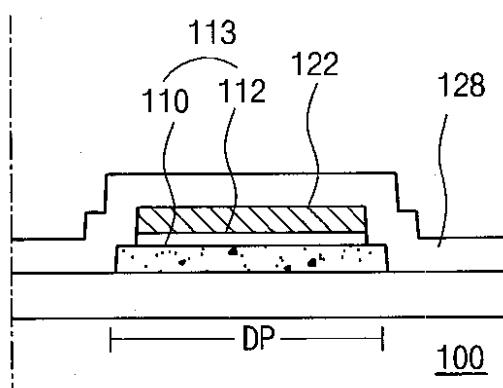

【図10C】本発明の第2マスク工程を工程順序によって示す図面であって、データパッド領域に対応する工程断面図である。

【図11A】図10Aに続く工程断面図である。

【図11B】図10Bに続く工程断面図である。

【図11C】図10Cに続く工程断面図である。

【図12A】図11Aに続く工程断面図である。

【図12B】図11Bに続く工程断面図である。

【図12C】図11Cに続く工程断面図である。

【図13A】図12Aに続く工程断面図である。

【図13B】図12Bに続く工程断面図である。

【図13C】図12Cに続く工程断面図である。

【図14A】図13Aに続く工程断面図である。

【図14B】図13Bに続く工程断面図である。

【図14C】図13Cに続く工程断面図である。

【図15A】本発明の第3マスク工程を示した図面であって、画素領域に対応する工程断面図である。

【図15B】本発明の第3マスク工程を示した図面であって、ゲートパッド領域に対応する工程断面図である。

【図15C】本発明の第3マスク工程を示した図面であって、データパッド領域に対応する工程断面図である。

【図16A】本発明の第4マスク工程を示した図面であって、画素領域に対応する工程断面図である。

【図16B】本発明の第4マスク工程を示した図面であって、ゲートパッド領域に対応する工程断面図である。

【図16C】本発明の第4マスク工程を示した図面であって、データパッド領域に対応する工程断面図である。

【図17A】本発明の第5マスク工程を示した図面であって、画素領域に対応する断面図である。

【図17B】本発明の第5マスク工程を示した図面であって、ゲートパッド領域に対応する断面図である。

【図17C】本発明の第5マスク工程を示した図面であって、データパッド領域に対応する断面図である。

【図18A】図17Aに続く工程断面図である。

【図18B】図17Bに続く工程断面図である。

【図18C】図17Cに続く工程断面図である。

【図19A】図18Aに続く工程断面図である。

【図19B】図18Bに続く工程断面図である。

【図19C】図18Cに続く工程断面図である。

【図20A】図19Aに続く工程断面図である。

【図20B】図19Bに続く工程断面図である。

【図20C】図19Cに続く工程断面図である。

【図21A】図20Aに続く工程断面図である。

【図21B】図20Bに続く工程断面図である。

【図21C】図20Cに続く工程断面図である。

【図22A】本発明による柱状のスペーサーを含む液晶表示装置用アレイ基板の断面図であって、画素領域に対応する断面図である。

10

20

30

40

50

【図22B】本発明による柱状のスペーサーを含む液晶表示装置用アレイ基板の断面図であって、ゲートパッド領域に対応する断面図である。

【図22C】本発明による柱状のスペーサーを含む液晶表示装置用アレイ基板の断面図であって、データパッド領域に対応する断面図である。

【図23A】本発明の他の実施の形態による液晶表示装置用アレイ基板の断面図であって、画素領域に対応する断面図である。

【図23B】本発明の他の実施の形態による液晶表示装置用アレイ基板の断面図であって、ゲートパッド領域に対応する断面図である。

【図23C】本発明の他の実施の形態による液晶表示装置用アレイ基板の断面図であって、データパッド領域に対応する断面図である。

10

【符号の説明】

【0139】

100：基板

102：ゲート配線

104：ゲート電極

108：ゲート絶縁膜

110：純粋非晶質シリコーン層

112：不純物非晶質シリコーン層

120：金属パターン

124：ソース電極

20

126：ドレイン電極

128：第1保護膜

130：カラーフィルター層

132：第2保護膜

134：感光パターン

136：ドレインコンタクトホール

138：ストレージコンタクトホール

【図1】

【図3】

【図2】

【図 6 A】

【図 6 B】

【図 6 C】

【図 7 A】

【図 7 B】

【図 7 C】

【図 8 A】

【図 8 B】

【図 8 C】

【図 9 A】

【図 9 B】

【図 9 C】

【図 10 A】

【図 10 B】

【図 10 C】

【図 11 A】

【図 1 1 B】

【図 1 1 C】

【図 1 2 A】

【図 1 2 B】

【図 1 2 C】

【図 1 3 A】

【図 1 3 B】

【図 1 3 C】

【図 1 4 A】

【図 1 4 B】

【図 1 5 A】

【図 1 5 B】

【図 1 4 C】

【図 1 5 C】

【図 1 6 B】

【図 1 6 A】

【図 1 6 C】

【図 17 A】

【図 17 B】

【図 17 C】

【図 18 A】

【図 18 B】

【図 18 C】

【図 19 A】

【図 19 B】

【図 20 A】

【図 20 B】

【図 19 C】

【図 20 C】

【図 21 A】

【図 22 A】

【図 21 B】

【図 22 B】

【図 21 C】

【図 2 2 C】

【図 2 3 C】

【図 2 3 A】

【図 2 3 B】

---

フロントページの続き

(72)発明者 ジヨン - チン・パク

大韓民国、431-070 キヨンギ - ド、アニヤン - シ、ドンアン - グ、ピヨンチヨン - ドン

897-5、チョウォン・アパートメント 604-602

審査官 吉田 英一

(56)参考文献 特開2002-055363 (JP, A)

特開2001-100652 (JP, A)

特開2003-029297 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1368

G02F 1/1335

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置的制造方法和液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP4478077B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2010-06-09 |

| 申请号            | JP2005192296                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2005-06-30 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | Eruji飞利浦杜迪股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | Eruji显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| [标]发明人         | ジョン・チン・パク                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | ジョン・チン・パク                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G02F1/1368 G02F1/1335                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| CPC分类号         | H01L27/1288 G02F1/13458 G02F1/136209 G02F1/136227 G02F2001/136222 H01L27/1214 H01L27/124                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| FI分类号          | G02F1/1368 G02F1/1335.505                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 2H091/FA02Y 2H091/FA34Y 2H091/FA35Y 2H091/GA13 2H091/GA16 2H091/LA12 2H092/JA26 2H092/JA28 2H092/JA34 2H092/JA37 2H092/JA41 2H092/JA46 2H092/JB57 2H092/JB58 2H092/KB26 2H092/MA13 2H092/MA17 2H092/MA37 2H092/NA27 2H092/PA08 2H191/FA02Y 2H191/FA13Y 2H191/FA14Y 2H191/GA19 2H191/GA22 2H191/LA13 2H192/AA24 2H192/BC31 2H192/CB05 2H192/DA02 2H192/EA13 2H192/EA42 2H192/HA44 2H192/HA47 2H291/FA02Y 2H291/FA13Y 2H291/FA14Y 2H291/GA19 2H291/GA22 2H291/LA13 |         |            |

| 代理人(译)         | 英年古河<br>Kajinami秩序                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 审查员(译)         | 吉田栄一                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 优先权            | 1020040050171 2004-06-30 KR<br>1020050010589 2005-02-04 KR                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 其他公开文献         | JP2006018295A                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

## 摘要(译)

要解决的问题：为了简化制造COT结构的液晶显示装置的过程，其中在阵列基板上形成滤色器。在栅电极上方的栅极绝缘膜上形成的有源层；有源层上的欧姆接触层；以及欧姆接触层形成在有源层的上部的源电极和漏电极，与栅极布线交叉以限定像素区域的数据布线，源电极和漏电极上的第一保护膜以及数据布线和第一保护膜在像素区域中的第一保护膜上形成滤色器层，在黑矩阵和滤色器层上形成第二保护以暴露像素区域中的滤色器层，膜和像素电极形成在像素区域的暴露的滤色器层上并连接到漏电极号（图19A）

【図3】

【図4A】