(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-195703

(P2005-195703A)

(43) 公開日 平成17年7月21日(2005.7.21)

(51) Int.CI.<sup>7</sup>

**G09G** 3/36

**G02F** 1/133

**G09G** 3/20

**H04N** 5/66

F 1

G09G 3/36

G02F 1/133 550

G02F 1/133 570

G09G 3/20 611A

G09G 3/20 621B

テーマコード(参考)

2 H093

5 C006

5 C058

5 C080

審査請求 未請求 請求項の数 25 O L (全 32 頁) 最終頁に続く

(21) 出願番号

(22) 出願日特願2003-435928 (P2003-435928)

平成15年12月26日 (2003.12.26)

(71) 出願人 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(74) 代理人 100096699

弁理士 鹿嶋 英實

(72) 発明者 平山 隆一

東京都八王子市石川町2951番地の5

カシオ計算機株式会社八王子技術センター内

(72) 発明者 横山 俊二

東京都八王子市石川町2951番地の5

カシオ計算機株式会社八王子技術センター内

最終頁に続く

(54) 【発明の名称】表示駆動装置及びその駆動制御方法並びに該表示駆動装置を備えた表示装置

## (57) 【要約】

【課題】 ドライバのチップサイズを縮小し、消費電力を低減させるとともに、実装面積の縮小及び製造コストを低減させることができ、また、表示パネルと周辺回路との接続工程における工数の抑制や必要な接続精度を緩和することができる表示駆動装置及びその駆動制御方法、並びに、該表示駆動装置を備えた表示装置を提供する。

【解決手段】 液晶表示装置100Aは、複数の表示画素P<sub>x</sub>が2次元配列された液晶表示パネル110と、各走査ラインS<sub>L</sub>に所定のタイミングで走査信号を順次印加するゲートドライバ120と、表示データに基づくシリアルデータからなる表示信号電圧を、所定のタイミングで、各データラインD<sub>L</sub>に分配して印加するソースドライバ130と、垂直制御信号、水平制御信号及びデータ変換制御信号を生成して出力するLCDコントローラ150と、を備えている。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

複数の表示画素が2次元配列された表示パネルに対して、表示データに基づく表示信号電圧を、前記表示画素の各々が接続された信号ラインを介して印加する表示駆動装置において、

少なくとも、

外部から供給される前記表示データを取り込み、並列的に保持するデータ保持部と、

該記データ保持部に並列的に保持された前記表示データを、所定の数の前記表示データごとに時分割的に配列された画素データに変換する第1のデータ変換部と、

前記所定の数の信号ラインごとに共通に設けられ、前記画素データに基づく前記表示信号電圧を、前記所定の数の信号ラインに接続された前記表示画素の選択期間中に、前記所定の数の信号ラインの各々に対して順次印加するように分配するとともに、前記表示信号電圧の印加順序を所定の周期で切り換える第2のデータ変換部と、10

を有することを特徴とする表示駆動装置。

**【請求項 2】**

前記第2のデータ変換部は、前記表示パネルの1画面分の表示動作を行う1フィールド期間ごとに、前記所定の数の信号ラインへの前記表示信号電圧の印加順序を反転させることを特徴とする請求項1記載の表示駆動装置。20

**【請求項 3】**

前記第2のデータ変換部は、前記表示パネルの1行分の表示動作を行う1水平期間ごとに、前記所定の数の信号ラインへの前記表示信号電圧の印加順序を反転させることを特徴とする請求項1又は2記載の表示駆動装置。20

**【請求項 4】**

前記第2のデータ変換部は、前記所定の数の信号ラインを介して印加される前記表示信号電圧に基づいて、前記表示画素に保持される画素電位が複数のフィールド期間を1周期として平均化されるように前記所定の数の信号ラインへの前記表示信号電圧の印加順序を反転させることを特徴とする請求項1乃至3のいずれかに記載の表示駆動装置。30

**【請求項 5】**

前記第2のデータ変換部は、前記所定の数の信号ラインへの前記表示信号電圧の印加順序を、4つのフィールド期間を1周期として、第1及び第4のフィールド期間で正順序に設定し、第2及び第3のフィールド期間で逆順序に設定することを特徴とする請求項4記載の表示駆動装置。30

**【請求項 6】**

複数の表示画素が2次元配列された表示パネルに対して、表示データに基づく表示信号電圧を、前記表示画素の各々が接続された信号ラインを介して印加する表示駆動装置において、40

少なくとも、

外部から供給される前記表示データを取り込み、並列的に保持するデータ保持部と、

該記データ保持部に並列的に保持された前記表示データを、所定の数の前記表示データごとに時分割的に配列された画素データに変換する第1のデータ変換部と、

前記所定の数の信号ラインごとに共通に設けられ、前記画素データに基づく前記表示信号電圧を、前記所定の数の信号ラインの各々に対して、前記表示画素における前記表示信号電圧の書き速度に応じて書き時間を個別に設定して印加するように分配する第2のデータ変換部と、40

を有することを特徴とする表示駆動装置。

**【請求項 7】**

前記第2のデータ変換部は、前記所定の数の信号ラインに接続された前記表示画素の選択期間に設定される前記所定の数の書き時間のうち、少なくとも、最後の書き時間を、前記表示画素における前記表示信号電圧の書きが終了する時間に設定することを特徴とする請求項6記載の表示駆動装置。50

**【請求項 8】**

前記第2のデータ変換部は、前記所定の数の信号ラインに接続された前記表示画素の選択期間中に、前記所定の数の信号ラインの各々に対して前記表示信号電圧を順次印加とともに、前記表示信号電圧の印加順序を所定の周期で切り換えることを特徴とする請求項6又は7記載の表示駆動装置。

**【請求項 9】**

前記表示駆動装置は、所定のタイミング信号に基づいて、前記第2のデータ変換部における前記表示信号電圧の印加順序の切り換えを制御するための切換信号を生成するスイッチ駆動制御部を、さらに具備することを特徴とする請求項1乃至8のいずれかに記載の表示駆動装置。

10

**【請求項 10】**

前記表示駆動装置は、前記所定の数の信号ラインに接続された前記表示画素を選択状態に設定する走査信号を順次出力する走査駆動部を、さらに具備し、

前記スイッチ駆動制御部は、前記走査駆動部と一体的に構成されていることを特徴とする請求項9記載の表示駆動装置。

**【請求項 11】**

少なくとも、前記第2のデータ変換部は、表示パネルが形成された単一の絶縁性基板上に一体的に構成されていることを特徴とする請求項1乃至10のいずれかに記載の表示駆動装置。

**【請求項 12】**

複数の表示画素が2次元配列された表示パネルに対して、表示データに基づく表示信号電圧を、前記表示画素の各々が接続された信号ラインを介して印加する表示駆動装置の駆動制御方法において、

少なくとも、

前記表示データを取り込み、並列的に保持するステップと、

該並列的に保持された前記表示データを、所定の数の前記表示データごとに時分割的に配列された画素データに変換するステップと、

前記画素データに基づく前記表示信号電圧を、前記所定の数の信号ラインに接続された前記表示画素の選択期間中に、前記所定の数の信号ラインの各々に対して順次印加するよう分配するステップと、

少なくとも前記表示パネルの1画面分の表示動作を行う1フィールド期間ごとに、前記所定の数の信号ラインへの前記表示信号電圧の印加順序を切り換えるステップと、を含むことを特徴とする表示駆動装置の駆動制御方法。

30

**【請求項 13】**

前記所定の数の信号ラインへの前記表示信号電圧の印加順序を切り換えるステップは、前記1フィールド期間ごとに加え、前記表示パネルの1行分の表示動作を行う1水平期間ごとに切り換えることを特徴とする請求項12記載の表示駆動装置の駆動制御方法。

**【請求項 14】**

前記所定の数の信号ラインへの前記表示信号電圧の印加順序を切り換えるステップは、前記所定の数の信号ラインを介して印加される前記表示信号電圧に基づいて、前記表示画素に保持される画素電位が複数のフィールド期間を1周期として平均化されるように切り換えることを特徴とする請求項12又は13記載の表示駆動装置の駆動制御方法。

40

**【請求項 15】**

複数の表示画素が2次元配列された表示パネルに対して、表示データに基づく表示信号電圧を、前記表示画素の各々が接続された信号ラインを介して印加する表示駆動装置の駆動制御方法において、

少なくとも、

前記表示データを取り込み、並列的に保持するステップと、

該並列的に保持された前記表示データを、所定の数の前記表示データごとに時分割的に配列された画素データに変換するステップと、

50

前記画素データに基づく前記表示信号電圧を、前記所定の数の信号ラインの各々に対して、前記表示画素における前記表示信号電圧の書込速度に応じて書込時間を個別に設定して印加するように分配するステップと、

を含むことを特徴とする表示駆動装置の駆動制御方法。

**【請求項 16】**

前記所定の数の信号ラインに接続された前記表示画素の選択期間中に、前記所定の数の信号ラインの各々に対して前記表示信号電圧を順次印加するステップと、

前記表示信号電圧の印加順序を所定の周期で切り換えるステップと、

をさらに含むことを特徴とする請求項 15 記載の表示駆動装置の駆動制御方法。

**【請求項 17】**

複数の信号ライン及び複数の走査ラインが相互に直交するように配設され、該信号ライン及び走査ラインの交点近傍に複数の表示画素が 2 次元配列された表示パネルに、表示データに基づく所望の画像情報を表示する表示装置において、

少なくとも、

各行の前記走査ラインに所定のタイミングで走査信号を順次印加して、該行の前記表示画素を選択状態に設定する走査駆動手段と、

外部から供給される前記表示データを取り込み、並列的に保持するデータ保持部と、該記データ保持部に並列的に保持された前記表示データを、所定の数の前記表示データごとに時分割的に配列された画素データに変換する第 1 のデータ変換部と、前記所定の数の信号ラインごとに共通に設けられ、前記画素データに基づく前記表示信号電圧を、前記所定の数の信号ラインに接続された前記表示画素の選択期間中に、前記所定の数の信号ラインの各々に対して順次印加するように分配するとともに、前記表示信号電圧の印加順序を所定の周期で切り換える第 2 のデータ変換部と、を有する信号駆動手段と、

を具備することを特徴とする表示装置。

**【請求項 18】**

前記第 2 のデータ変換部は、少なくとも、前記表示パネルの 1 画面分の表示動作を行う 1 フィールド期間ごとに、前記所定の数の信号ラインへの前記表示信号電圧の印加順序を反転させることを特徴とする請求項 17 記載の表示装置。

**【請求項 19】**

前記第 2 のデータ変換部は、前記所定の数の信号ラインを介して印加される前記表示信号電圧に基づいて、前記表示画素に保持される画素電位が複数のフィールド期間を 1 周期として平均化されるように前記所定の数の信号ラインへの前記表示信号電圧の印加順序を反転させることを特徴とする請求項 17 又は 18 記載の表示装置。

**【請求項 20】**

複数の信号ライン及び複数の走査ラインが相互に直交するように配設され、該信号ライン及び走査ラインの交点近傍に複数の表示画素が 2 次元配列された表示パネルに、表示データに基づく所望の画像情報を表示する表示装置において、

少なくとも、

各行の前記走査ラインに所定のタイミングで走査信号を順次印加して、該行の前記表示画素を選択状態に設定する走査駆動手段と、

外部から供給される前記表示データを取り込み、並列的に保持するデータ保持部と、該記データ保持部に並列的に保持された前記表示データを、所定の数の前記表示データごとに時分割的に配列された画素データに変換する第 1 のデータ変換部と、前記所定の数の信号ラインごとに共通に設けられ、前記画素データに基づく前記表示信号電圧を、前記所定の数の信号ラインの各々に対して、前記表示画素における前記表示信号電圧の書込速度に応じて書込時間を個別に設定して印加するように分配する第 2 のデータ変換部と、を有する信号駆動手段と、

を具備することを特徴とする表示装置。

**【請求項 21】**

前記第 2 のデータ変換部は、前記所定の数の信号ラインに接続された前記表示画素の選択

10

20

30

40

50

期間中に、前記所定の数の信号ラインの各々に対して前記表示信号電圧を順次印加とともに、前記表示信号電圧の印加順序を所定の周期で切り換えることを特徴とする請求項 20 記載の表示装置。

【請求項 22】

前記第2のデータ変換部は、表示パネルが形成された単一の絶縁性基板上に一体的に構成されていることを特徴とする請求項 17 乃至 21 のいずれかに記載の表示装置。

【請求項 23】

前記表示装置は、所定のタイミング信号に基づいて、前記第2のデータ変換部における前記表示信号電圧の印加順序の切り換えを制御するための切換信号を生成するスイッチ駆動制御部を、さらに具備することを特徴とする請求項 17 乃至 22 のいずれかに記載の表示装置。10

【請求項 24】

前記スイッチ駆動制御部は、前記走査駆動手段と一体的に構成されていることを特徴とする請求項 23 記載の表示駆動装置。

【請求項 25】

前記複数の表示画素は、各々、前記走査ラインにゲート電極が接続され、前記信号ラインにドレイン電極が接続され、ソース電極が画素電極に接続された画素トランジスタと、前記画素電極及び該画素電極に対向して共通に設けられた共通電極間に液晶分子を充填してなる画素容量と、前記画素容量に並列に接続された補助容量と、を備えて構成され、20

前記表示データに応じた前記表示信号電圧を印加することにより、前記表示画素に充填された前記液晶分子の配向状態が制御されることを特徴とする請求項 17 乃至 24 のいずれかに記載の表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示駆動装置及びその駆動制御方法並びに該表示駆動装置を備えた表示装置に関し、特に、アクティブマトリクス型の駆動方式に対応した表示パネルに適用して良好な表示駆動装置及びその駆動制御方法、並びに、該表示駆動装置を備えた表示装置に関する。30

【背景技術】

【0002】

近年、普及が著しいデジタルビデオカメラやデジタルスチルカメラ等の撮像機器や、携帯電話や携帯情報端末（PDA）等の携帯機器において、画像や文字情報等を表示するための表示装置（ディスプレイ）として、また、コンピュータ等の情報端末やテレビジョン等の映像機器のモニタやディスプレイとしても、薄型軽量で、低消費電力化が可能であり、表示画質にも優れた液晶表示装置（Liquid Crystal Display；LCD）が多用されている。

【0003】

以下、従来技術における液晶表示装置について、簡単に説明する。

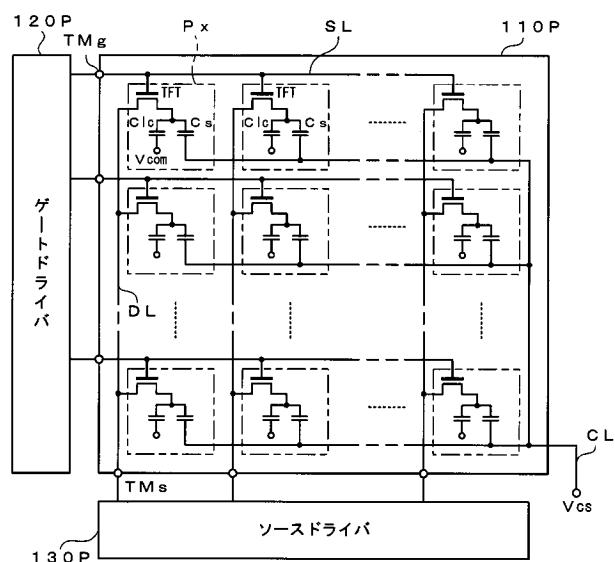

図 20 は、従来技術における薄膜トランジスタ（TFT）型の表示画素を備えた液晶表示装置の概略構成を示すブロック図であり、図 21 は、従来技術における液晶表示パネルの要部構成の一例を示す等価回路図である。40

図 20、図 21 に示すように、従来技術における液晶表示装置 100P は、概略、表示画素 Px が、2 次元配列された液晶表示パネル（表示パネル）110P と、該液晶表示パネル 110P の各行の表示画素 Px 群を順次走査して選択状態に設定するゲートドライバ（走査ドライバ）120P と、選択状態に設定された行の表示画素 Px 群に、映像信号に基づく表示信号電圧を一括して出力するソースドライバ（データドライバ）130P と、ゲートドライバ 120P 及びソースドライバ 130P における動作タイミングを制御するための制御信号（水平制御信号、垂直制御信号等）を生成、出力する LCD コントローラ 150P と、映像信号から各種タイミング信号（水平同期信号、垂直同期信号、コンポジ

ット同期信号等)を抽出してLCDコントローラ150Pに出力するとともに、輝度信号からなる表示データを生成してソースドライバ130Pに出力する表示信号生成回路160Pと、LCDコントローラ150Pにより生成される極性反転信号FRPに基づいて、液晶表示パネル110Pの各表示画素Pxに共通に設けられた共通電極(対向電極)に対して、所定の電圧極性を有するコモン信号電圧Vcomを印加するコモン信号駆動アンプ(駆動アンプ)170Pと、を備えた構成を有している。

#### 【0004】

ここで、液晶表示パネル110Pは、対向する透明基板間に、例えば、図21に示すように、行列方向に互いに直交するように配設された複数の走査ラインSL及び複数のデータラインDLと、該走査ラインSL及びデータラインDLの各交点近傍に配置された複数の表示画素(液晶表示画素)Pxと、を備えて構成されている。また、各表示画素Pxは、画素電極とデータラインDL間にソース-ドレイン(電流路)が接続され、走査ラインSLにゲート(制御端子)が接続された薄膜トランジスタからなる画素トランジスタTFTと、画素電極に対向し、全表示画素Pxに共通に設けられた共通電極と上記画素電極との間に充填、保持された液晶分子からなる画素容量(液晶容量)Clcと、画素容量Clcに並列に構成され、該画素容量Clcに印加された信号電圧を保持するための補助容量(蓄積容量)Csと、を備えた構成を有している。

#### 【0005】

なお、液晶表示パネル110Pに配設された走査ラインSL及びデータラインDLは、各々、接続端子TMg、TMgを介して、液晶表示パネル110Pとは別個に設けられたゲートドライバ120P及びソースドライバ130Pに接続されるように構成されている。また、補助容量Csの他端側の電極(補助電極)は、共通の接続ラインCLを介して所定の電圧Vcs(例えば、コモン信号電圧Vcom)が印加されるように構成されている。

#### 【0006】

このような構成を有する液晶表示装置100Pにおいて、表示信号生成回路160Pから供給される、液晶表示パネル110Pの1行分の表示画素に対応した表示データが、LCDコントローラ150Pから供給される水平制御信号に基づいて、ソースドライバ130Pにより順次取り込み保持される。一方、LCDコントローラ150Pから供給される垂直制御信号に基づいて、ゲートドライバ120Pにより液晶表示パネル110Pに配設された各走査ラインSLに走査信号が順次印加され、各行の表示画素Px群の画素トランジスタTFTがオン動作して、表示信号電圧を取り込み可能な選択状態に設定される。そして、この各行の表示画素Px群の選択タイミングに同期して、ソースドライバ130Pにより、上記取り込み保持した表示データに基づく表示信号電圧を、各データラインDLを介して各表示画素Pxに一斉に供給する。

#### 【0007】

これにより、選択状態に設定された各表示画素Pxの画素トランジスタTFTを介して、画素容量Clcに充填された液晶分子が、該表示信号電圧に応じて配向状態を変化させて所定の階調表示動作が行われるとともに、該画素容量Clcに並列に接続された補助容量Csに、該画素容量Clcに印加された電圧が充電される。このような一連の動作を、1画面分の各行に対して繰り返し実行することにより、映像信号に基づく所望の画像情報が液晶表示パネル110Pに表示される。

#### 【0008】

なお、液晶表示装置の実装構造としては、図20、図21に示したように、液晶表示パネル110Pを構成する(画素アレイが形成される)ガラス基板等の絶縁性基板とは別個に、周辺回路であるゲートドライバ120P及びソースドライバ130Pを設け、接続端子TMg、TMgを介して、液晶表示パネル110Pと周辺回路とを電気的に接続する構成のほか、上記絶縁性基板上に、例えば、ゲートドライバ120Pやソースドライバ130Pを、ポリシリコントランジスタを適用して、画素アレイ(表示画素Px)と一体的に形成した構成も知られている。このような液晶表示装置の概略構成や実装構造等については、例えば、特許文献1等に記載されている。

【 0 0 0 9 】

【特許文献1】特開2000-267590号公報（第3頁、図1）

【発明の開示】

【発明が解決しようとする課題】

【 0 0 1 0 】

しかしながら、上述したような液晶表示装置においては、以下に示すような問題を有していた。

すなわち、図20、図21に示したように、液晶表示パネル110Pに対して、ゲートドライバ120P及びソースドライバ130Pを周辺回路として別個に設けた構成においては、表示画質の向上のために液晶表示パネル110Pを高精細化した場合、データライン数の増加を招き、これにより、ゲートドライバ120Pやソースドライバ130Pの出力端子数が増加し、このため各ドライバ（ゲートドライバ120Pやソースドライバ130P）の回路規模が増大して、各ドライバを構成するチップサイズが大きくなり、各ドライバの実装面積が増大するとともに、各ドライバ回路のコストの上昇を招くという問題を有していた。また、回路規模の増大に伴い、各ドライバ回路の消費電力が増加するという問題を有していた。

【 0 0 1 1 】

更に、ゲートドライバ120Pやソースドライバ130Pの出力端子数が増加して、液晶表示パネル110Pと各ドライバとを接続するための接続端子数が増加するとともに、当該接続端子間のピッチが狭くなるため、接続工程における工数が増加するとともに、高い接続精度を必要とすることになり、製造コストの上昇を招くという問題を有していた。

【 0 0 1 2 】

このような液晶表示パネルと周辺回路との接続に係る工数や接続精度の問題を解決する技術としては、上述した特許文献1等にも示されているように、単一の絶縁性基板上に液晶表示パネルと、ゲートドライバやソースドライバを、ポリシリコントランジスタを適用して一体的に形成した構成が知られているが、ポリシリコントランジスタは、アモルファスシリコントランジスタのように、既に製造技術が確立され、良好な素子特性（動作特性）が得られているトランジスタ素子とは異なり、製造プロセスが煩雑で製造コストも高価であり、また、動作特性も不十分であるため、液晶表示装置の製品コストの上昇を招くとともに、安定した表示特性を得ることが難しいという問題を有していた。

【 0 0 1 3 】

そこで、本発明は、上述した課題に鑑み、ドライバのチップサイズを縮小し、消費電力を低減させるとともに、実装面積の縮小及び製造コストを低減させることができ、また、表示パネルと周辺回路との接続工程における工数の抑制や必要な接続精度を緩和することができる表示駆動装置及びその駆動制御方法、並びに、該表示駆動装置を備えた表示装置を提供することを目的とする。

【課題を解決するための手段】

【 0 0 1 4 】

請求項1記載の発明は、複数の表示画素が2次元配列された表示パネルに対して、表示データに基づく表示信号電圧を、前記表示画素の各々が接続された信号ラインを介して印加する表示駆動装置において、少なくとも、外部から供給される前記表示データを取り込み、並列的に保持するデータ保持部と、該記データ保持部に並列的に保持された前記表示データを、所定の数の前記表示データごとに時分割的に配列された画素データに変換する第1のデータ変換部と、前記所定の数の信号ラインごとに共通に設けられ、前記画素データに基づく前記表示信号電圧を、前記所定の数の信号ラインに接続された前記表示画素の選択期間中に、前記所定の数の信号ラインの各々に対して順次印加するよう分配するとともに、前記表示信号電圧の印加順序を所定の周期で切り換える第2のデータ変換部と、を有することを特徴とする。

【 0 0 1 5 】

請求項2記載の発明は、請求項1記載の表示駆動装置において、前記第2のデータ変換

10

20

30

40

50

部は、前記表示パネルの1画面分の表示動作を行う1フィールド期間ごとに、前記所定の数の信号ラインへの前記表示信号電圧の印加順序を反転させることを特徴とする。

請求項3記載の発明は、請求項1又は2記載の表示駆動装置において、前記第2のデータ変換部は、前記表示パネルの1行分の表示動作を行う1水平期間ごとに、前記所定の数の信号ラインへの前記表示信号電圧の印加順序を反転させることを特徴とする。

#### 【0016】

請求項4記載の発明は、請求項1乃至3のいずれかに記載の表示駆動装置において、前記第2のデータ変換部は、前記所定の数の信号ラインを介して印加される前記表示信号電圧に基づいて、前記表示画素に保持される画素電位が複数のフィールド期間を1周期として平均化されるように前記所定の数の信号ラインへの前記表示信号電圧の印加順序を反転させることを特徴とする。

請求項5記載の発明は、請求項4記載の表示駆動装置において、前記第2のデータ変換部は、前記所定の数の信号ラインへの前記表示信号電圧の印加順序を、4つのフィールド期間を1周期として、第1及び第4のフィールド期間で正順序に設定し、第2及び第3のフィールド期間で逆順序に設定することを特徴とする。

#### 【0017】

請求項6記載の発明は、複数の表示画素が2次元配列された表示パネルに対して、表示データに基づく表示信号電圧を、前記表示画素の各々が接続された信号ラインを介して印加する表示駆動装置において、少なくとも、外部から供給される前記表示データを取り込み、並列的に保持するデータ保持部と、該記データ保持部に並列的に保持された前記表示データを、所定の数の前記表示データごとに時分割的に配列された画素データに変換する第1のデータ変換部と、前記所定の数の信号ラインごとに共通に設けられ、前記画素データに基づく前記表示信号電圧を、前記所定の数の信号ラインの各々に対して、前記表示画素における前記表示信号電圧の書き速度に応じて書き時間を個別に設定して印加するよう分配する第2のデータ変換部と、を有することを特徴とする。

#### 【0018】

請求項7記載の発明は、請求項6記載の表示駆動装置において、前記第2のデータ変換部は、前記所定の数の信号ラインに接続された前記表示画素の選択期間に設定される前記所定の数の書き時間のうち、少なくとも、最後の書き時間を、前記表示画素における前記表示信号電圧の書きが終了する時間に設定することを特徴とする。

請求項8記載の発明は、請求項6又は7記載の表示駆動装置において、前記第2のデータ変換部は、前記所定の数の信号ラインに接続された前記表示画素の選択期間中に、前記所定の数の信号ラインの各々に対して前記表示信号電圧を順次印加するとともに、前記表示信号電圧の印加順序を所定の周期で切り換えることを特徴とする。

#### 【0019】

請求項9記載の発明は、請求項1乃至8のいずれかに記載の表示駆動装置において、前記表示駆動装置は、所定のタイミング信号に基づいて、前記第2のデータ変換部における前記表示信号電圧の印加順序の切り換えを制御するための切換信号を生成するスイッチ駆動制御部を、さらに具備することを特徴とする。

請求項10記載の発明は、請求項9記載の表示駆動装置において、前記表示駆動装置は、前記所定の数の信号ラインに接続された前記表示画素を選択状態に設定する走査信号を順次出力する走査駆動部を、さらに具備し、前記スイッチ駆動制御部は、前記走査駆動部と一体的に構成されていることを特徴とする。

請求項11記載の発明は、請求項1乃至10のいずれかに記載の表示駆動装置において、少なくとも、前記第2のデータ変換部は、表示パネルが形成された単一の絶縁性基板上に一体的に構成されていることを特徴とする。

#### 【0020】

請求項12記載の発明は、複数の表示画素が2次元配列された表示パネルに対して、表示データに基づく表示信号電圧を、前記表示画素の各々が接続された信号ラインを介して印加する表示駆動装置の駆動制御方法において、少なくとも、前記表示データを取り込み

10

20

30

40

50

、並列的に保持するステップと、該並列的に保持された前記表示データを、所定の数の前記表示データごとに時分割的に配列された画素データに変換するステップと、前記画素データに基づく前記表示信号電圧を、前記所定の数の信号ラインに接続された前記表示画素の選択期間中に、前記所定の数の信号ラインの各々に対して順次印加するように分配するステップと、少なくとも前記表示パネルの1画面分の表示動作を行う1フィールド期間ごとに、前記所定の数の信号ラインへの前記表示信号電圧の印加順序を切り換えるステップと、を含むことを特徴とする。

#### 【0021】

請求項13記載の発明は、請求項12記載の表示駆動装置の駆動制御方法において、前記所定の数の信号ラインへの前記表示信号電圧の印加順序を切り換えるステップは、前記1フィールド期間ごとに加え、前記表示パネルの1行分の表示動作を行う1水平期間ごとに切り換えることを特徴とする。10

請求項14記載の発明は、請求項12又は13記載の表示駆動装置の駆動制御方法において、前記所定の数の信号ラインへの前記表示信号電圧の印加順序を切り換えるステップは、前記所定の数の信号ラインを介して印加される前記表示信号電圧に基づいて、前記表示画素に保持される画素電位が複数のフィールド期間を1周期として平均化されるように切り換えることを特徴とする。

#### 【0022】

請求項15記載の発明は、複数の表示画素が2次元配列された表示パネルに対して、表示データに基づく表示信号電圧を、前記表示画素の各々が接続された信号ラインを介して印加する表示駆動装置の駆動制御方法において、少なくとも、前記表示データを取り込み、並列的に保持するステップと、該並列的に保持された前記表示データを、所定の数の前記表示データごとに時分割的に配列された画素データに変換するステップと、前記画素データに基づく前記表示信号電圧を、前記所定の数の信号ラインの各々に対して、前記表示画素における前記表示信号電圧の書き速度に応じて書き時間を個別に設定して印加するように分配するステップと、を含むことを特徴とする。20

請求項16記載の発明は、請求項15記載の表示駆動装置の駆動制御方法において、前記所定の数の信号ラインに接続された前記表示画素の選択期間中に、前記所定の数の信号ラインの各々に対して前記表示信号電圧を順次印加するステップと、前記表示信号電圧の印加順序を所定の周期で切り換えるステップと、をさらに含むことを特徴とする。30

#### 【0023】

請求項17記載の発明は、複数の信号ライン及び複数の走査ラインが相互に直交するように配設され、該信号ライン及び走査ラインの交点近傍に複数の表示画素が2次元配列された表示パネルに、表示データに基づく所望の画像情報を表示する表示装置において、少なくとも、各行の前記走査ラインに所定のタイミングで走査信号を順次印加して、該行の前記表示画素を選択状態に設定する走査駆動手段と、外部から供給される前記表示データを取り込み、並列的に保持するデータ保持部と、該記データ保持部に並列的に保持された前記表示データを、所定の数の前記表示データごとに時分割的に配列された画素データに変換する第1のデータ変換部と、前記所定の数の信号ラインごとに共通に設けられ、前記画素データに基づく前記表示信号電圧を、前記所定の数の信号ラインに接続された前記表示画素の選択期間中に、前記所定の数の信号ラインの各々に対して順次印加するように分配するとともに、前記表示信号電圧の印加順序を所定の周期で切り換える第2のデータ変換部と、を有する信号駆動手段と、を具備することを特徴とする。40

#### 【0024】

請求項18記載の発明は、請求項17記載の表示装置において、前記第2のデータ変換部は、少なくとも、前記表示パネルの1画面分の表示動作を行う1フィールド期間ごとに、前記所定の数の信号ラインへの前記表示信号電圧の印加順序を反転させることを特徴とする。

請求項19記載の発明は、請求項17又は18記載の表示装置において、前記第2のデータ変換部は、前記所定の数の信号ラインを介して印加される前記表示信号電圧に基づい50

て、前記表示画素に保持される画素電位が複数のフィールド期間を1周期として平均化されるように前記所定の数の信号ラインへの前記表示信号電圧の印加順序を反転させることを特徴とする。

#### 【0025】

請求項20記載の発明は、複数の信号ライン及び複数の走査ラインが相互に直交するように配設され、該信号ライン及び走査ラインの交点近傍に複数の表示画素が2次元配列された表示パネルに、表示データに基づく所望の画像情報を表示する表示装置において、少なくとも、各行の前記走査ラインに所定のタイミングで走査信号を順次印加して、該行の前記表示画素を選択状態に設定する走査駆動手段と、外部から供給される前記表示データを取り込み、並列的に保持するデータ保持部と、該記データ保持部に並列的に保持された前記表示データを、所定の数の前記表示データごとに時分割的に配列された画素データに変換する第1のデータ変換部と、前記所定の数の信号ラインごとに共通に設けられ、前記画素データに基づく前記表示信号電圧を、前記所定の数の信号ラインの各々に対して、前記表示画素における前記表示信号電圧の書き速度に応じて書き時間を個別に設定して印加するように分配する第2のデータ変換部と、を有する信号駆動手段と、を具備することを特徴とする。10

#### 【0026】

請求項21記載の発明は、請求項20記載の表示装置において、前記第2のデータ変換部は、前記所定の数の信号ラインに接続された前記表示画素の選択期間中に、前記所定の数の信号ラインの各々に対して前記表示信号電圧を順次印加するとともに、前記表示信号電圧の印加順序を所定の周期で切り換えることを特徴とする。20

請求項22記載の発明は、請求項17乃至21のいずれかに記載の表示装置において、前記第2のデータ変換部は、表示パネルが形成された単一の絶縁性基板上に一体的に構成されていることを特徴とする。

請求項23記載の発明は、請求項17乃至22のいずれかに記載の表示装置において、前記表示装置は、所定のタイミング信号に基づいて、前記第2のデータ変換部における前記表示信号電圧の印加順序の切り換えを制御するための切換信号を生成するスイッチ駆動制御部を、さらに具備することを特徴とする。

#### 【0027】

請求項24記載の発明は、請求項23記載の表示駆動装置において、前記スイッチ駆動制御部は、前記走査駆動手段と一体的に構成されていることを特徴とする。30

請求項25記載の発明は、請求項17乃至24のいずれかに記載の表示装置において、前記複数の表示画素は、各々、前記走査ラインにゲート電極が接続され、前記信号ラインにドレイン電極が接続され、ソース電極が画素電極に接続された画素トランジスタと、前記画素電極及び該画素電極に対向して共通に設けられた共通電極間に液晶分子を充填してなる画素容量と、前記画素容量に並列に接続された補助容量と、を備えて構成され、前記表示データに応じた前記表示信号電圧を印加することにより、前記表示画素に充填された前記液晶分子の配向状態が制御されることを特徴とする。

#### 【発明の効果】

#### 【0028】

すなわち、本発明に係る表示駆動装置及びその駆動制御方法、並びに、該表示駆動装置を備えた表示装置は、表示パネルに2次元配列された複数の表示画素（液晶画素等）に対して、表示データに基づく表示信号電圧を信号ラインを介して所定のタイミングで印加する表示駆動装置（信号駆動手段；データドライバ）を備えた表示装置において、第1のデータ変換部（マルチプレクサ）により、表示データを所定の数の表示データごとに時分割的に配列された画素データに変換し、次いで、当該表示データに対応する表示画素が選択状態に設定される期間中に、第2のデータ変換部（トランスファスイッチ部、分配マルチプレクサ）により、第1のデータ変換部から送出される画素データに基づく表示信号電圧を、上記所定の数の信号ラインに対して所定の印加順序で順次印加するよう分配するとともに、スイッチ駆動制御部により生成、出力される切換信号に基づいて、分配された表4050

示信号電圧の印加順序を所定の周期（1フィールド期間ごと、さらには、1水平期間ごと）で正順序又は逆順序に切り換えるように構成されている。

#### 【0029】

これにより、分配された表示信号電圧の各データライン（表示画素）への印加順序が、奇数フィールド期間と偶数フィールド期間で、さらには、1水平期間ごとに反転するよう10に制御されるので、各表示画素の選択期間中にリークする電荷量が、画面単位、もしくは、走査ライン単位で略均一化されて、各表示画素に保持される書き電荷量が、時間平均的に均一化される。したがって、隣り合う信号ライン（データライン）ごとのリーク電流量の差が抑制されて、フリッカの発生を防止することができ、表示画質の改善を図ることができる。

#### 【0030】

また、本発明に係る表示駆動装置によれば、各表示画素に供給する表示信号電圧を、複数本（例えば、3本）の信号ラインを一組として、該一組の信号ラインに対応する表示データを時分割シリアルデータに変換して、該シリアルデータごとに単一の配線を介して送出することができる所以、表示駆動装置（ソースドライバ）内に設けられるD/Aコンバータや出力アンプ、また、これらの構成と第2のデータ変換部とを接続する配線の数を、数分の1（各組に含まれる信号ラインの本数分の1）に削減することができて、表示駆動装置（ソースドライバ）を構成する回路規模を削減してチップサイズを縮小することができ、製造コストの削減及び実装面積の縮小を図ることができるとともに、消費電力を削減することができる。

20

#### 【0031】

また、本発明に係る表示駆動装置においては、上記表示パネルが、液晶表示パネルである場合には、第2のデータ変換部により制御される表示信号電圧の印加順序を、各表示画素に保持される画素電位（画素電極電圧）とコモン電圧との関係に基づいて、コモン電圧の中心電圧からの偏りを解消するように、例えば、4つのフィールド期間を1周期として、第1及び第4のフィールド期間で正順序に設定し、第2及び第3のフィールド期間で逆順序に設定することができ、これにより、液晶に印加される直流成分が相殺され、液晶の焼き付きやフリッカの発生を防止することができる。

20

#### 【0032】

また、本発明に係る表示駆動装置においては、第2のデータ変換部により表示信号電圧の印加順序を制御する手法に代えて、表示画素における表示信号電圧の書き速度（画素トランジスタの駆動能力）に応じて、選択期間中に設定される書き時間と個別に設定する手法を適用することもできる。この場合、選択期間中に設定される所定の数の書き時間のうち、少なくとも、最後（末期）の書き時間を、表示画素における表示信号電圧の書き動作が完了する時間に設定し、他の書き時間をこの最後の書き時間よりも短く設定する。

30

#### 【0033】

これにより、書き時間後も選択期間が継続している表示画素においては、当該選択期間が終了するまでに表示信号電圧の書き動作を良好に完了させることができ、また、書き時間の終了と略同時に選択期間が終了する表示画素においては、表示信号電圧の書き動作が完了するまでの時間に書き時間が設定されているので、いずれの表示信号電圧も表示画素に良好に書き込むことができ（書き量を均一化することができ）、表示信号電圧に基づく正常な画像表示を行うことができる。

40

#### 【0034】

なお、上述したような第2のデータ変換部の動作状態を設定する切換信号を生成するスイッチ駆動制御部は、表示駆動装置（信号駆動手段）内に設けられるものであってもよいし、表示駆動装置の外部に独立して、あるいは、走査駆動手段（ゲートドライバ）内に設けられるものであってもよい。さらに、第2のデータ変換部についても、表示駆動装置（信号駆動手段）内に一体的に設けられるものであってもよいし、例えば、表示パネルが形成される絶縁性基板上に一体的に形成されているものであってもよい。

#### 【0035】

ここで、第2のデータ変換部が絶縁性基板上に形成された構成にあっては、絶縁性基板とは別個に設けられた表示駆動装置と第2のデータ変換部との間を、上記所定の数ごとに一組にされた信号ラインごとに单一の接続端子により接続することができるので、表示パネルと表示駆動装置の接続端子の数を、上記各組に含まれる信号ラインの本数分の1に削減して、当該接続工程における工数を削減することができるとともに、比較的低い接続精度であっても良好に接続することができ、製造コストの削減及び表示駆動装置の実装面積の縮小を図ることができる。

#### 【0036】

加えて、表示パネル（複数の表示画素）と第2のデータ変換部が、同一の絶縁性基板上に一体的に形成された構成を有していることにより、表示画素を構成する画素トランジスタや、第2のデータ変換部を構成する各機能素子を、例えば、アモルファスシリコンを適用して同一の製造プロセスで形成することができるので、すでに技術的に確立されたアモルファスシリコン製造プロセスを適用して、安価に表示駆動装置及び表示装置を製造することができるとともに、動作特性の安定した機能素子を実現することができるので、表示装置の表示特性を向上させることができ。

10

#### 【発明を実施するための最良の形態】

#### 【0037】

以下、本発明に係る表示駆動装置及びその駆動制御方法並びに該表示駆動装置を備えた表示装置について、実施形態の形態を示して詳しく説明する。ここでは、まず、本発明に係る表示駆動装置を備えた表示装置の全体構成を示し、次いで、表示駆動装置及びその駆動制御方法について具体的に説明する。なお、以下に示す実施形態においては、本発明に係る表示駆動装置及び表示装置を、アクティブマトリクス型の駆動方式を採用した液晶表示装置に適用した場合について説明する。

20

#### 【0038】

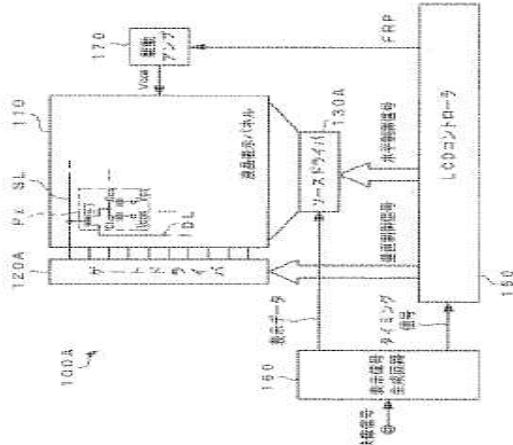

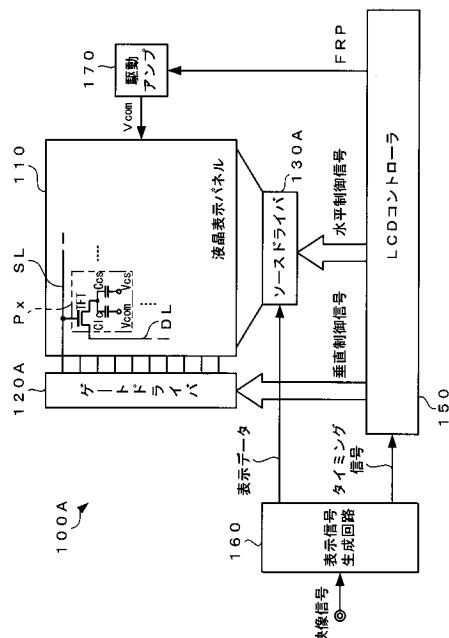

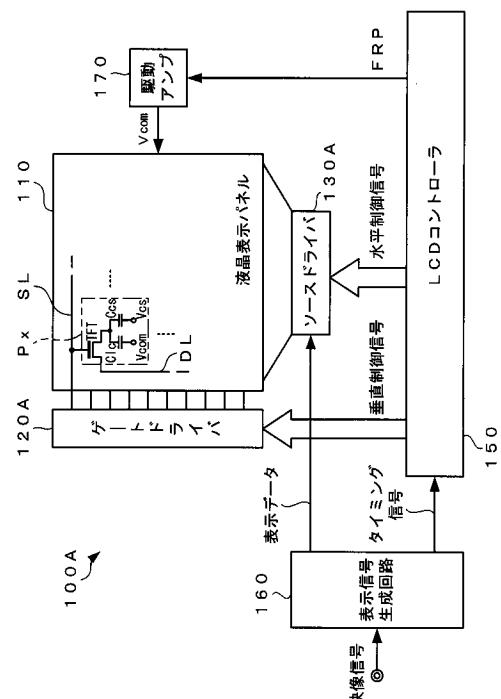

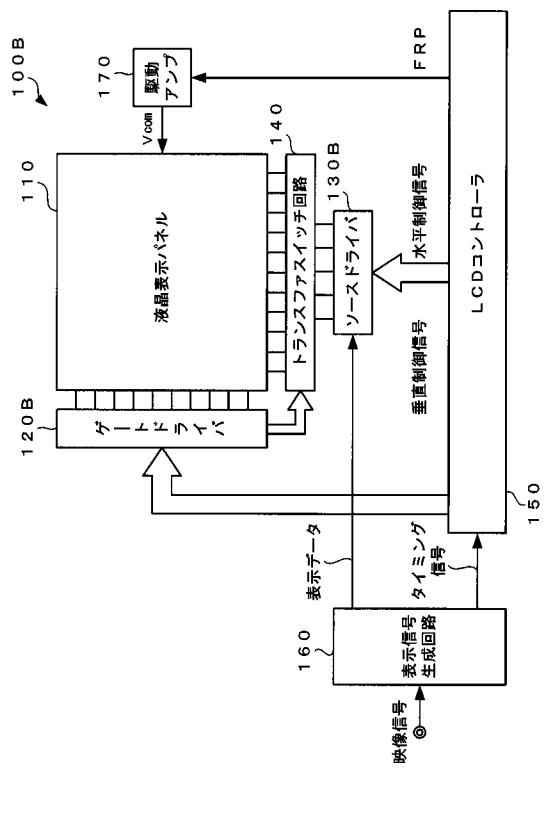

##### <表示装置の第1の実施形態>

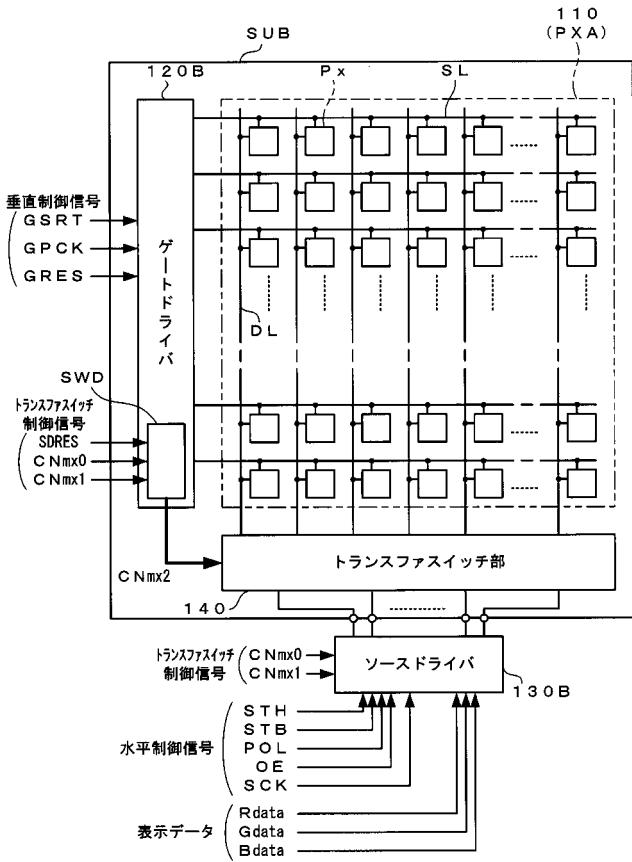

図1は、本発明に係る表示装置を適用した液晶表示装置の第1の実施形態の全体構成を示す概略ブロック図である。ここで、上述した従来技術（図20及び図21）と同等の構成については、同等又は同一の符号を付して説明を簡略化する。

#### 【0039】

図1に示すように、本構成例に係る液晶表示装置100Aは、概略、上述した従来技術（図20、図21参照）と同様に、複数の走査ラインSL及び複数のデータラインDLの交点近傍に複数の表示画素Pxが2次元配列された液晶表示パネル110（表示パネル：又は、図示を省略した絶縁性基板上に設けられた画素アレイ）と、各走査ラインSLに所定のタイミングで走査信号を順次印加するゲートドライバ（走査駆動手段）120Aと、表示データに基づくシリアルデータからなる表示信号電圧を、所定のタイミングで、各データラインDLに分配して印加するソースドライバ（信号駆動手段）130Aと、少なくとも、ゲートドライバ120A及びソースドライバ130A、後述するトランスマスイッチ部140の動作状態を制御するための各種制御信号（後述する垂直制御信号、水平制御信号、データ変換制御信号）を生成して出力するLCDコントローラ150と、映像信号に基づいてソースドライバ130Aに供給する表示データを生成するとともに、LCDコントローラ150に供給するタイミング信号を生成する表示信号生成回路160と、全表示画素Pxに共通に設けられた共通電極に対して、所定の電圧極性を有するコモン信号電圧を印加するコモン電圧駆動アンプ（駆動アンプ）170と、を備えた構成を有している。

30

ここで、本実施形態においては、例えば、液晶表示パネル110を構成する複数の表示画素Pxが2次元配列される画素アレイが形成されたガラス基板等の絶縁性基板とは別個のドライバチップとして、ソースドライバ130Aやゲートドライバ120Aを構成することができる。

40

#### 【0040】

次いで、上述した液晶表示装置の各構成について具体的に説明する。なお、液晶表示パ

50

ネル 110 (画素アレイ) は、従来技術に示した構成 (図 21 に示した液晶表示パネル 110P) と同等の構成を有しているので、その詳細な説明を省略する。

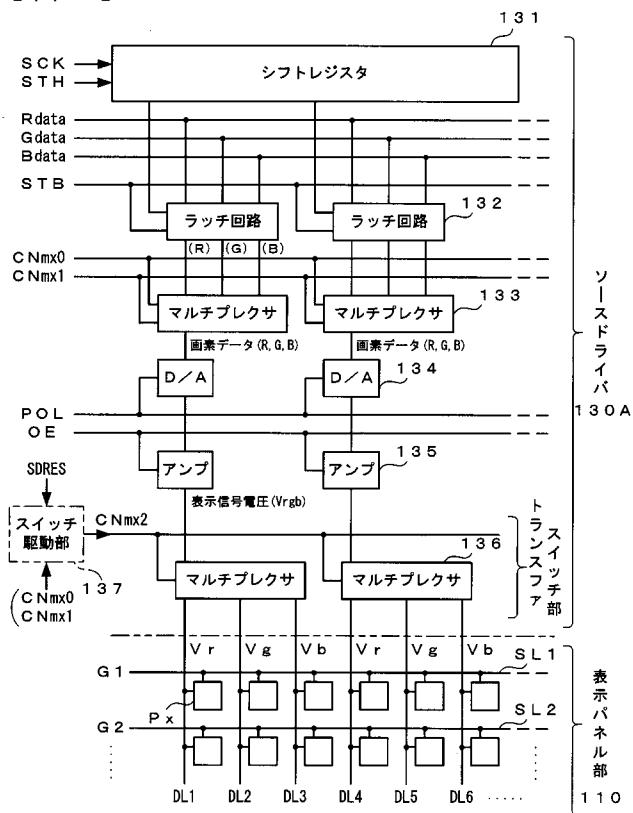

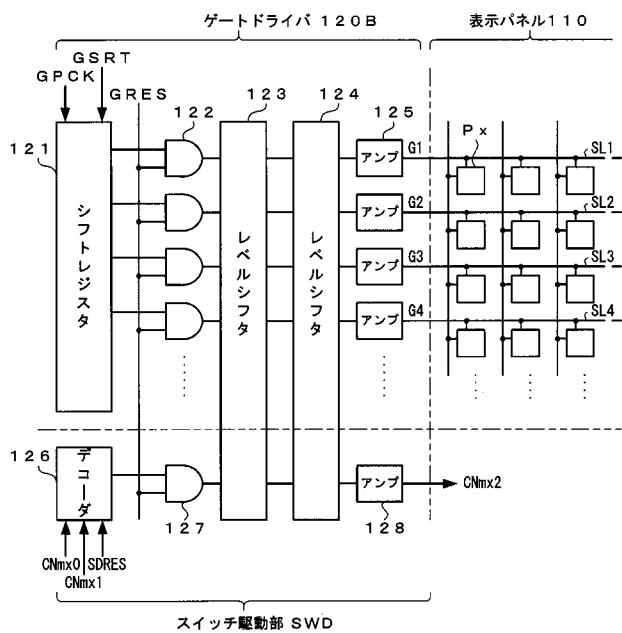

図 2 は、本実施形態に係る液晶表示装置に適用されるゲートドライバの一具体例を示す概略構成図であり、図 3 は、本実施形態に係る液晶表示装置に適用されるソースドライバの一具体例を示す概略構成図である。ここでは、上述した図 1 に示した構成を適宜参照しながら説明する。

#### 【0041】

ゲートドライバ 120A は、図 2 に示すように、LCD コントローラ 150 から垂直制御信号として供給されるゲートスタート信号 GSR ト 及びゲートクロック信号 GPC ト に基づいて、所定のタイミングでシフト信号を順次出力するシフトレジスタ 121 と、該シフトレジスタ 121 から出力されるシフト信号を一方の入力とし、LCD コントローラ 150 から垂直制御信号として供給されるゲートリセット信号 GRES を他方の入力とする 2 入力論理積演算回路 (以下、「AND 回路」と略記する) 122 と、該 AND 回路 122 からの出力信号を所定の信号レベルに設定 (昇圧) する複数段 (2 段) のレベルシフタ 123、124 及び出力アンプ (図中、「アンプ」と表記) 125 と、を備えた構成を有している。ここで、レベルシフタ 123、124 及び出力アンプ 125 は、主にシフトレジスタ 121 を低電圧で駆動させるためのものであり、走査ライン SL (表示画素 Px) に印加する走査信号の信号レベルに応じて、ゲートドライバ 120A の出力段に適宜設けられる。

#### 【0042】

このような構成を有するゲートドライバ 120Aにおいては、LCD コントローラ 150 から垂直制御信号としてゲートスタート信号 GSR ト、ゲートクロック信号 GPC ト が供給されると、シフトレジスタ 121 により、ゲートクロック信号 GPC ト に基づいてゲートスタート信号 GSR ト を順次シフトしつつ、各走査ラインに対応して設けられた複数の AND 回路 122 の一方の入力接点に該シフト信号が入力される。

#### 【0043】

ここで、ゲートリセット信号 GRES をハイレベル (“1”) に設定した状態 (ゲートドライバの駆動状態) では、AND 回路 122 の他方の入力接点に常時 “1” レベルが入力されるので、上記ゲートスタート信号 GSR ト、ゲートクロック信号 GPC ト に基づいて、シフトレジスタ 121 からシフト信号が出力されるタイミングで、AND 回路 122 からハイレベル (“1”) の信号が出力され、レベルシフタ 123、124 及び出力アンプ 125 を介して、所定のハイレベルを有する走査信号 G1、G2、G3、… が生成され、各走査ライン SL1、SL2、SL3、… に順次印加される。これにより、走査信号 G1、G2、G3、… が印加された走査ライン SL1、SL2、SL3、… の各行ごとに接続された表示画素 Px 群が一括して選択状態に設定される。

#### 【0044】

一方、ゲートリセット信号 GRES をローレベル (“0”) に設定した状態 (ゲートドライバ 120A のリセット状態) では、AND 回路 122 の他方の入力接点に常時 “0” レベルが入力されるので、シフトレジスタ 121 からのシフト信号の出力の有無にかかわらず、AND 122 からローレベル (“0”) の信号が常時出力されることにより、所定のローレベルを有する走査信号 G1、G2、G3、… が生成され、走査ライン SL1、SL2、SL3、… の各行ごとに接続された表示画素 Px 群が非選択状態に設定される。

#### 【0045】

ソースドライバ 130A は、例えば、図 3 に示すように、水平シフトクロック信号 SCK、水平期間スタート信号 STH に基づいて、所定のタイミングでシフト信号を順次出力するシフトレジスタ 131 と、該シフトレジスタ 131 から出力されるシフト信号に応じて、表示信号生成回路 160 から並列的に供給される複数系統の表示データ、例えば、画像情報を構成する赤色成分 (R)、緑色成分 (G)、青色成分 (B) からなる 3 系統の表示データ R data、G data、B data を順次取り込むとともに、前の水平期間に取り込まれた

10

20

30

40

50

表示データを制御信号 S T B に応じて一斉に出力するラッチ回路（データ保持部）132と、マルチプレクサ制御信号 C N mx0、C N mx1に基づいて、ラッチ回路132から一斉に出力された各表示データ R data、G data、B data（すなわち、パラレルデータ）を、時分割的に配列された1系統の画素データ（R、G、B）（すなわち、シリアルデータ）に変換する3入力マルチプレクサ（第1のデータ変換部）133と、該3入力マルチプレクサ133から出力される画素データ（R、G、B）をデジタル-アナログ変換し、極性制御信号 P O L に基づいて所定の信号極性を有するアナログ信号を生成するデジタル-アナログ変換器（以下、「D/Aコンバータ」と略記する。図中、「D/A」と表記））134と、出力イネーブル信号 O E に基づいて、アナログ変換された画素データ（R、G、B）を所定の信号レベルに増幅して、分配マルチプレクサ136に表示信号電圧 V rgb として出力する出力アンプ（図中、「アンプ」と表記）135と、マルチプレクサ制御信号 C N mx2に基づいて、出力アンプ135から出力されたシリアルデータからなる1系統の画素データ（R、G、B）を、各表示データ R data、G data、B data に対応した表示信号電圧 V r、V g、V b（すなわち、パラレルデータ）に時分割的に変換（分配）して、各データライン D L 1 ~ D L 3、D L 4 ~ D L 6、・・・ごとに、任意のタイミング（所定の順序）で印加する分配マルチプレクサ（第2のデータ変換部）136と、を備えた構成を有している。なお、図3においては、複数の分配マルチプレクサ136からなる構成をトランスマスファスイッチ部と表記する。

## 【0046】

ここで、上述した各構成に供給される水平シフトクロック信号 S C K、水平期間スタート信号 S T H、制御信号 S T B、マルチプレクサ制御信号 C N mx0、C N mx1、極性制御信号 P O L、出力イネーブル信号 O E は、いずれも L C D コントローラ 150 から供給される水平制御信号である。また、マルチプレクサ制御信号（切換信号）C N mx2は、上述した各制御信号と同様に、L C D コントローラ 150 から供給される水平制御信号の一つであってもよいし、図3に示すように、L C D コントローラ 150 から水平制御信号（データ変換制御信号）として供給される、マルチプレクサ制御信号 C N mx0、C N mx1及びスイッチャリセット信号 S D R E S に基づいて、スイッチ駆動部（スイッチ駆動制御部）137により生成、出力するものであってもよい。

## 【0047】

なお、スイッチ駆動部137は、ソースドライバ130Aの内部に設けられるものであってもよいし、ソースドライバ130Aの外部に設けられるものであってもよい。また、スイッチ駆動部137の具体的な回路構成例については、特に限定するものではないが、後述するように、フィールド期間の切り替わりタイミングや走査ライン S L の選択期間ごとに、上記分配マルチプレクサ136の動作状態を切り換え制御する信号を生成、出力するものであればよく、例えば、後述する表示装置の第2の実施形態（図18参照）に示すような構成を良好に適用することができる。

## 【0048】

すなわち、このような構成を有するソースドライバ130Aにおいては、表示信号生成回路160から1行分のR G Bの各色の表示画素 P x に対応した表示データ R data、G data、B dataが並列的かつ順次供給され、ラッチ回路132により1組のR G B各色の表示画素に対応した表示データ R data、G data、B dataが順次取り込み保持された後、3入力マルチプレクサ133により時分割シリアルデータ（表示信号電圧 V rgb）に変換されて、D/Aコンバータ134、出力アンプ135を介して分配マルチプレクサ136に出力される。

## 【0049】

このとき、ソースドライバ130A内に設けられたスイッチ駆動部137から、上記3入力マルチプレクサ133におけるシリアル変換処理を制御するマルチプレクサ制御信号 C N mx0、C N mx1に基づいて生成されるマルチプレクサ制御信号 C N mx2を分配マルチプレクサ136に供給することにより、上記時分割シリアルデータからなる表示信号電圧 V rgbの時分割タイミングに同期して、各データライン D L 1 ~ D L 3、D L 4 ~ D L 6、

10

20

30

40

50

・・・ごとに設けられた分配マルチプレクサ 136 を所定の分配順序（具体的には、例えば、正順序又は逆順序）で動作させる。

#### 【0050】

これにより、時分割シリアルデータのうち、表示データの赤色成分 R dataに基づく表示信号電圧 V r がデータライン D L 1、D L 4、D L 7、・・・D L (k+1)に供給され、緑色成分 G dataに基づく表示信号電圧 V g がデータライン D L 2、D L 5、D L 8、・・・D L (k+2)に供給され、青色成分 B dataに基づく表示信号電圧 V b がデータライン D L 3、D L 6、D L 9、・・・D L (k+3)に供給されるとともに、各データライン D L 1～D L 3、D L 4～D L 6、・・・への、これらの表示信号電圧 V r、V g、V b の印加順序（すなわち、表示信号電圧 V r、V g、V b の印加順序を、V r V g V b の正順序とするか、V b V g V r の逆順序とするか）が適宜設定される。ここで、データライン D L の列番号を表す k は、k = 0、1、2、3、・・・である。10

#### 【0051】

表示信号生成回路 160 は、例えば、液晶表示装置 100 A の外部から供給される映像信号（コンポジットビデオ信号等）から水平同期信号、垂直同期信号及びコンポジット同期信号を抽出し、タイミング信号として LCD コントローラ 150 に供給するとともに、所定の表示信号生成処理（ペデスタルクランプ、クロマ処理等）を実行して、映像信号に含まれる R、G、B 各色の輝度信号（表示データ）を抽出し、アナログ信号又はデジタル信号としてソースドライバ 130 A に出力する。20

#### 【0052】

LCD コントローラ 150 は、上記表示信号生成回路 160 から供給される水平同期信号、垂直同期信号及びシステムクロック等の各種タイミング信号に基づいて、水平制御信号及び垂直制御信号を生成して、各自、ゲートドライバ 120 A 及びソースドライバ 130 A に供給するとともに、本発明特有の機能として、上記 3 入力マルチプレクサ 133 A や分配マルチプレクサ 136 の動作状態を制御するデータ変換制御信号（マルチプレクサ制御信号 C N mx0、C N mx1 及びスイッチリセット信号 S D R E S）を生成して、ソースドライバ 130 A（スイッチ駆動部 137 を含む）に供給し、概略、上述したように、表示信号生成回路 160 から供給される表示データ R data、G data、B data を、3 入力マルチプレクサ 133 により時分割シリアルデータからなる表示信号電圧 V rgb に変換し、その後、該表示信号電圧 V rgb の供給タイミングに同期して、分配マルチプレクサ 136 を所定の分配順序で動作させることにより、上記表示信号電圧 V rgb を各データライン（表示画素）に分配するように制御する。30

なお、本実施形態において、上述したソースドライバ 130 A に設けられたスイッチ駆動部 137 やトランスファスイッチ部は、本発明に係る表示装置に適用可能な回路構成のごく一例を示したものにすぎず、本発明はこの構成に限定されるものではない。

#### 【0053】

（液晶表示装置の駆動制御方法）

次いで、本実施形態に係る液晶表示装置における駆動制御動作について、図面を参照して説明する。

（第 1 の駆動制御方法）

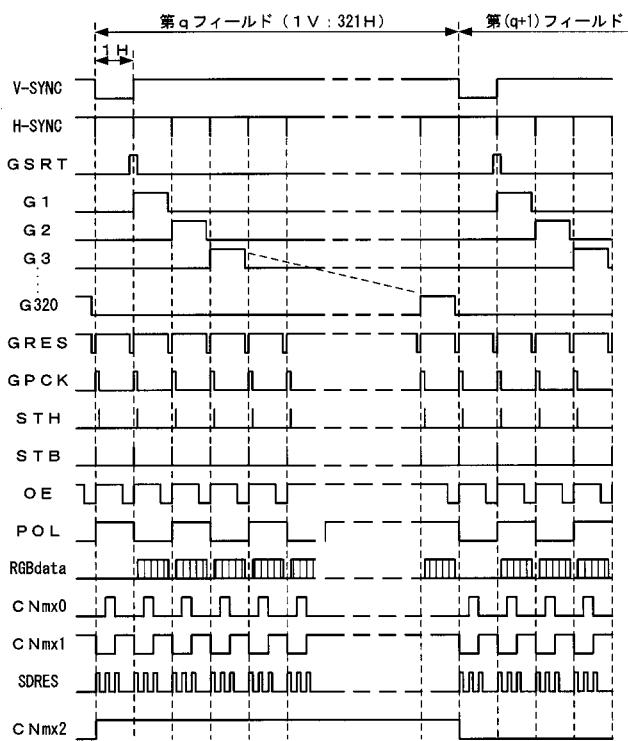

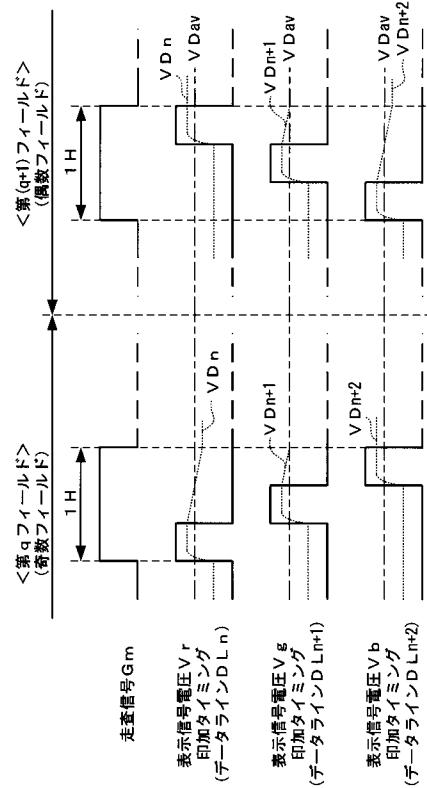

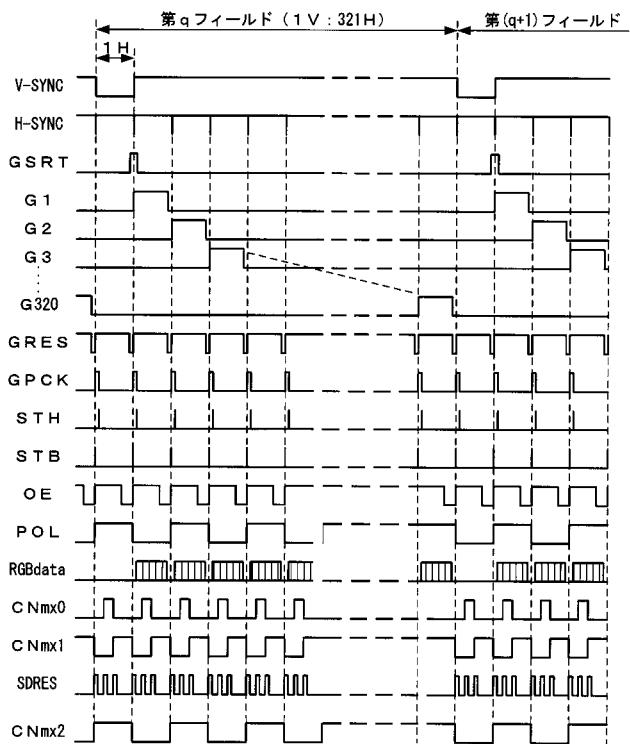

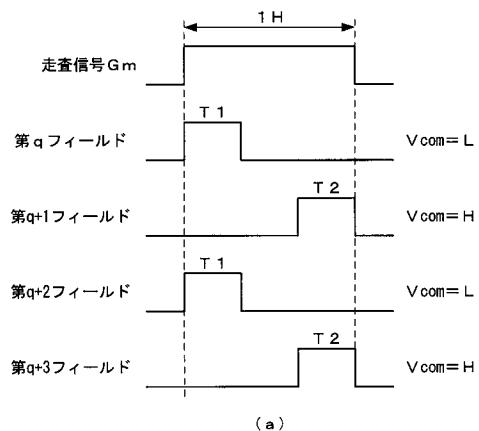

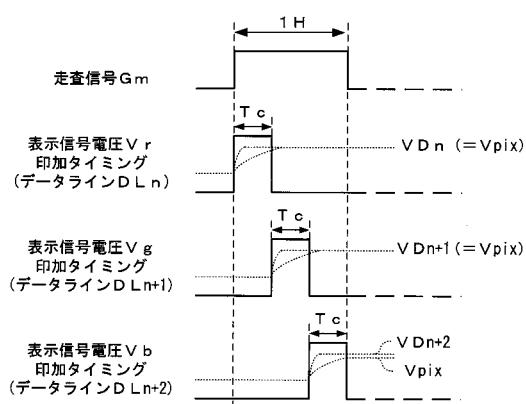

図 4 は、本実施形態に係る液晶表示装置の駆動制御動作の一例を示すタイミングチャートであり、図 5 は、本実施形態に係る液晶表示装置の第 1 の駆動制御方法の制御概念を示す要部タイミングチャートである。40

#### 【0054】

上述したような構成を有する液晶表示装置における駆動制御動作は、図 4 のタイミングチャートに示すように、1 水平期間（1 H）を 1 サイクルとして、まず、ゲートドライバ 120 A から n 行目の走査ライン S L n に走査信号 G i を印加して、当該行の表示画素 P × 群を選択状態に設定する。この選択期間に、マルチプレクサ制御信号 C N mx0～C N mx2 及びスイッチリセット信号 S D R E S に基づく所定のタイミングで、ソースドライバ 130 A を介して、各自 3 本のデータライン D L 1～D L 3、D L 4～D L 6、・・・を 1 組

として、3入力マルチプレクサ133及び分配マルチプレクサ136における動作を同期して実行させ、各データラインDL1～DL3、DL4～DL6、・・・に接続された表示画素Pxに対応した表示データを、時分割されたシリアルデータからなる表示信号電圧Vrgbに変換してトランスファスイッチ部(分配マルチプレクサ136)に送出した後、図5のタイミングチャートに示すように、分配マルチプレクサ136により上記表示信号電圧Vrgbを、各組のデータラインDL1～DL3、DL4～DL6、・・・の各々に対応する個別の表示信号電圧Vr、Vg、Vbに分配して異なるタイミングで順次印加し、当該行の各表示画素Pxに表示データを書き込む動作を実行する。

#### 【0055】

そして、このような書き込み動作を、1フィールド期間(1垂直期間；1V)に、液晶表示パネル110を構成する各走査ラインSL1、SL2、・・・(本構成例では、液晶表示パネル110が320本の走査ラインSLを備えるものとする。)に対して、順次走査信号G1、G2、G3、・・・を印加することにより、液晶表示パネル1画面分の表示データを各表示画素Pxに書き込む。

#### 【0056】

特に、第1の駆動制御方法においては、図5のタイミングチャートに示すように、マルチプレクサ制御信号CNmx2がフィールド期間ごとに切り換え制御されることにより、例えば、奇数フィールド期間となる第qフィールド期間においては、ハイレベルのマルチプレクサ制御信号CNmx2を印加することにより、各行の走査ラインに走査信号Gmが印加されて当該行の表示画素Px群が選択状態に設定された状態で、各組のデータラインDL1～DL3、DL4～DL6、・・・の各々(すなわち、各表示画素Px)に対応して分配された表示信号電圧Vr、Vg、Vbが、相互に時間的に重ならないタイミングで、Vr Vg Vbの順序(正順序)で順次印加される。

#### 【0057】

一方、偶数フィールド期間となる第q+1フィールド期間においては、ローレベルのマルチプレクサ制御信号CNmx2を印加することにより、各行の表示画素Px群が選択状態に設定された状態で、各組のデータラインDL1～DL3、DL4～DL6、・・・の各々に対応して分配された表示信号電圧Vr、Vg、Vbが、相互に時間的に重ならないタイミングで、Vb Vg Vrの順序(逆順序)で順次印加される。

これにより、各表示画素Pxが表示データに応じた階調状態に設定されるので、液晶表示パネル110に所望の画像情報が表示される。

#### 【0058】

ここで、第1の駆動制御方法における特徴的な作用効果について、比較例を示して具体的に説明する。

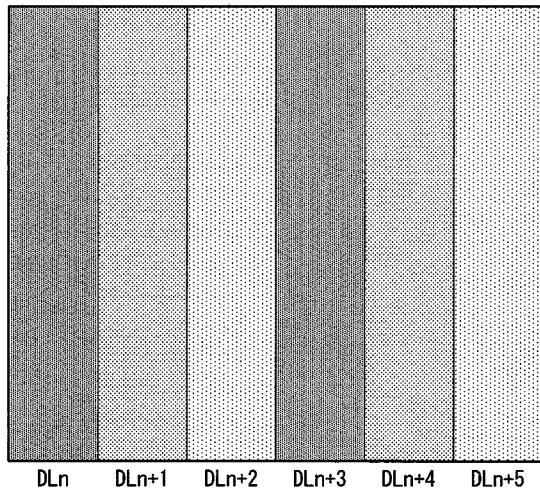

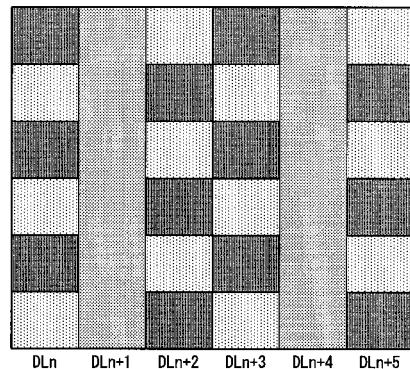

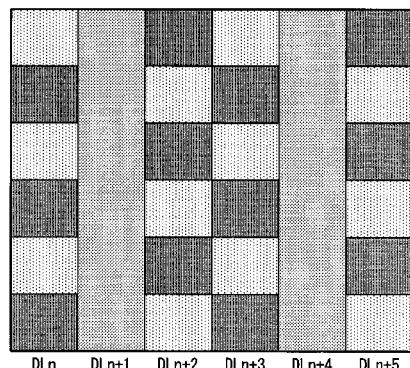

図6は、第1の駆動制御方法における作用効果を説明するための、比較対象となる他の駆動制御方法の例を示すタイミングチャートであり、図7は、当該比較対象となる他の駆動制御方法における表示画質の概念図である。なお、図6に示すタイミングチャートにおいては、略連続して印加される走査信号Gm、Gm+1により設定される各選択期間(1H)について示すが、説明の都合上、双方の選択期間を便宜的に離間させて表示する。

#### 【0059】

上述したように、本駆動制御方法においては、分配された表示信号電圧Vr、Vg、Vbの各データライン(表示画素Px)への印加(供給)順序を、奇数フィールド期間と偶数フィールド期間で反転するように制御したことを特徴としている。これに対して、図6に示す駆動制御方法(以下、便宜的に「比較対象例」とも記す)においては、分配された表示信号電圧Vr、Vg、Vbの各データライン(表示画素Px)への印加(供給)順序が、奇数フィールド期間であるか、偶数フィールド期間であるかに関わらず、常に固定されている。

#### 【0060】

図4に示したように、本駆動制御方法及び比較対象例に係る駆動制御方法においては、各データライン(表示画素Px)への表示信号電圧の書き動作は、ゲートラインに走査信

10

20

30

40

50

号 G m が印加される選択期間中に実行されるので、該選択期間は各表示信号電圧の書込動作に要する期間（各書込期間）に比較して長くなるように設定されている（本実施形態においては、選択期間（1 H） 各書込期間の総和）。

#### 【 0 0 6 1 】

そのため、分配された表示信号電圧 V r、V g、V b の各データライン（表示画素 P x ）への印加順序が固定されている比較対象例に係る駆動制御方法においては、図 6 に示すように、例えば、表示信号電圧 V r の書込動作後、選択期間が終了するまでの間、当該行の表示画素 P x には依然として走査信号 G m が印加されているので、各表示画素 P x の画素トランジスタ TFT（図 1 参照）がオン状態を継続する。これにより、表示信号電圧 V r、V g、V b に基づいて各表示画素 P x に保持された電荷の一部がデータライン DL に設けられた静電気保護用の保護素子（例えば、ダイオード）を介してリーケして、保持電荷量が減少する問題が生じる。10

#### 【 0 0 6 2 】

ここで、各表示画素 P x からの電荷のリーケ量は、表示画素 P x （データライン DL ）への表示信号電圧 V r、V g、V b の印加順序（又は、書込動作後の選択期間の残り時間）に依存し、例えば、図 6 に示したように、表示信号電圧 V r が印加されるデータライン DL n では書込動作後の選択期間の残り時間が長いため、電荷のリーケ量が大きく（図中、点線で示したデータライン電圧 V D n の変化参照）、表示信号電圧 V b が印加されるデータライン DL n+2 では書込動作後の選択期間の残り時間が殆ど無いため、電荷のリーケは殆ど無く（図中、点線で示したデータライン電圧 V D n+2 の変化参照）、表示信号電圧 V g が印加されるデータライン DL n+1 の電荷のリーケ量はこれらの中間程度になり（図中、点線で示したデータライン電圧 V D n+1 の変化参照）、これにより各表示画素 P x に保持される書込電荷量にバラツキが生じる。なお、図 5、図 6 において、V D av は、データライン電圧 V D n ~ V D n+5 の平均電圧である。20

#### 【 0 0 6 3 】

したがって、分配された表示信号電圧 V r、V g、V b の各データライン（表示画素 P x ）への印加順序が固定された駆動制御方法においては、隣り合うデータライン DL ごと（列方向に配列された表示画素 P x 群ごと）に常に同等のリーケ電流量の差が生じてしまい、一様な輝度の表示画像（ラスター表示）を表示するように表示信号電圧を設定した場合であっても、図 7 に示すように、表示画像に縦スジ状の輝度の変化（明暗）が生じて、画質の劣化を招くという問題を有している。なお、図 7 においては、図示の都合上、ハッティングの濃さ（ドット密度）により表示輝度の明暗を示す。30

#### 【 0 0 6 4 】

そこで、本駆動制御方法においては、図 5 に示したように、分配された表示信号電圧 V r、V g、V b の各データライン（表示画素 P x ）への印加順序を、奇数フィールド期間と偶数フィールド期間で反転するように制御することにより、各表示画素 P x からの電荷のリーケ量は、一組の奇数フィールド期間（第 q フィールド期間）と偶数フィールド期間（第 q + 1 フィールド期間）に着目すると、表示信号電圧 V r、V g、V b が印加される各データライン DL 間で略均一化されて、第 q フィールド期間と第 q + 1 フィールド期間における、データライン電圧 V D n の総和と、データライン電圧 V D n+1 の総和と、データライン電圧 V D n+2 の総和が略均一化されることになる。すなわち、各表示画素 P x に保持される書込電荷量が、時間平均的に均一化される。したがって、隣り合うデータライン DL ごと（列方向に配列された表示画素 P x 群ごと）のリーケ電流量の差が抑制され、スジ状の輝度の明暗の発生を防止することができ、表示画質の改善を図ることができる。40

#### 【 0 0 6 5 】

また、上述した構成を有する液晶表示装置によれば、液晶表示パネル 110 を構成する各データライン DL に接続された表示画素 P x に供給する表示信号電圧を、ソースドライバ 130 A 内部で複数本のデータライン DL を一組として時分割シリアルデータに変換して、当該複数本のデータライン DL に対応した表示信号電圧を单一の信号配線を介して送50

出することができるので、ソースドライバ 130A 内に設けられる D/A コンバータ 134 や出力アンプ 135、また、これらの構成とトランスファスイッチ部（分配マルチブレクサ 136）とを接続する信号配線の数を、数分の 1（各組に含まれるデータラインの本数分の 1）に削減することができる。これによりソースドライバを構成する回路規模を削減することができて、ソースドライバのチップサイズを縮小することができ、製造コストの削減及びソースドライバの実装面積の縮小を図ることができるとともに、上記 D/A コンバータや出力アンプで消費される電力を削減して、ソースドライバの消費電力を低減させることができる。

#### 【0066】

なお、本実施形態においては、 $i$  系統（ $j$  は任意の正の整数；上述したように RGB の各色成分に対応させた場合には、3 系統（ $j = 3$ ））のパラレルデータとして供給された表示データを、マルチブレクサ（3 入力マルチブレクサ 133）によりシリアルデータに変換して、トランスファスイッチ部に送出し、分配マルチブレクサ 136 により、複数（ $j$  本）のデータライン DL に分配する構成を有しているので、単に、表示データを取り込み保持して、表示信号電圧に変換して出力する従来（周知）のソースドライバに比較して、ソースドライバ 130A は、 $j$  倍の動作速度（ $j$  倍のクロック周波数）で信号処理を行うように設定される。ここで、ソースドライバ 130A（マルチブレクサ 133 及び分配マルチブレクサ 136）により処理される表示データは、上述した表示データの各色成分 RGB に対応した 3 系統に限定されるものではなく、2 系統や 3 系統以上のパラレルデータであってもよく、この場合には、該表示データの系統数に応じた入出力接点を備えたマルチブレクサが適用される。

#### 【0067】

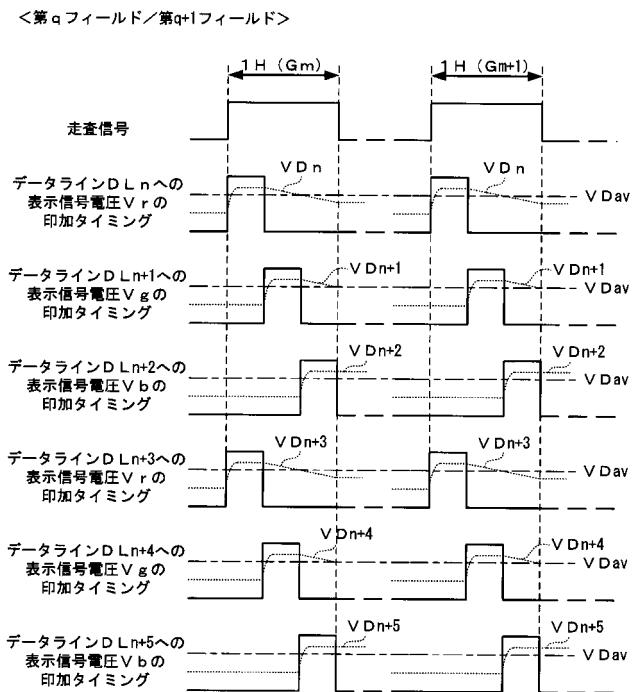

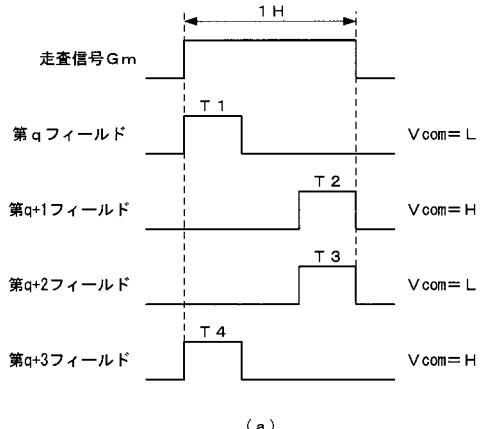

##### （第 2 の駆動制御方法）

図 8 は、本実施形態に係る液晶表示装置の駆動制御動作の他の例を示すタイミングチャートであり、図 9 は、本実施形態に係る液晶表示装置の第 2 の駆動制御方法の制御概念を示す要部タイミングチャートである。また、図 10 は、第 2 の駆動制御方法における表示画質の概念図である。ここでは、上述した液晶表示装置（図 1～図 3 参照）の構成を適宜参照しながら説明する。また、第 1 の駆動制御方法と同等の動作については、その説明を簡略化又は省略する。

#### 【0068】

上述した第 1 の駆動制御方法においては、ソースドライバ 130A に設けられた分配マルチブレクサ 136 の動作状態（表示信号電圧 Vr、Vg、Vb の印加順序）を設定するマルチブレクサ制御信号 CNmx2 をフィールド期間ごとに切り換える場合について説明したが、第 2 の駆動制御方法においては、マルチブレクサ制御信号 CNmx2 をフィールド期間ごとに切り換えるとともに、さらに、1 水平期間（選択期間）ごとに切り換えるように制御する。

#### 【0069】

すなわち、第 1 の駆動制御方法においては、図 5 に示したように、フィールド期間ごとに表示信号電圧 Vr、Vg、Vb の印加順序が Vr Vg Vb の正順序、又は、Vb Vg Vr の逆順序に切り替わるため、表示信号電圧 Vr、Vb が印加されるデータライン DLn、DLn+2 については、選択期間中のデータライン電圧 VDn、VDn+2 が大きく変化（低下）するフィールド期間と、ほとんど変化しないフィールド期間がフィールド期間ごとに繰り返されることになるが、表示信号電圧 Vg が印加されるデータライン DLn+1 については、そのデータライン電圧 VDn+1 の変化がフィールド期間に関わらず実質的に同一となる。これにより、データライン DLn、DLn+2 に対応する表示画像の輝度が、フィールド期間ごとに変化することになるため、ラスター表示等の特定の画像を表示する場合にフリッカが発生する可能性がある。

#### 【0070】

そこで、第 2 の駆動制御方法においては、上述した液晶表示装置と同等の構成において、図 8 に示すように、マルチブレクサ制御信号 CNmx2 を 1 水平期間（選択期間）ごとに

10

20

30

40

50

切り換えるとともに、さらに、フィールド期間ごとに切り換えるように設定することにより、ソースドライバ 130A に設けられた分配マルチブレクサ 136 により各データライン DL に印加される表示信号電圧 Vr、Vg、Vb の順序を、上述した第 1 の駆動制御方法と同様に（図 5 参照）フィールド期間ごとに正順序又は逆順序に切り換え、かつ、図 9 に示すように、選択期間ごと（走査ライン SL ごと）にも正順序又は逆順序に切り換える。

#### 【0071】

これにより、分配された表示信号電圧 Vr、Vg、Vb の各データライン（表示画素 Px）への印加順序が、少なくとも選択期間ごと（1 水平期間ごと）に切り替わるので、上述した第 1 の駆動制御方法に比較して、データライン DL ごと（列方向に配列された表示画素 Px 群ごと）のリーク電流量の差に起因する表示画像の輝度の変化がより短い周期で生じて、図 10 に示すように、ラスター表示等の特定の画像を表示する場合であってもフリッカが比較的視認されにくくなり、表示画質の改善を図ることができる。なお、図 10 においても、図 7 と同様に、図示の都合上、ハッティングの濃さ（ドット密度）により表示輝度の明暗を示す。

#### 【0072】

##### （第 3 の駆動制御方法）

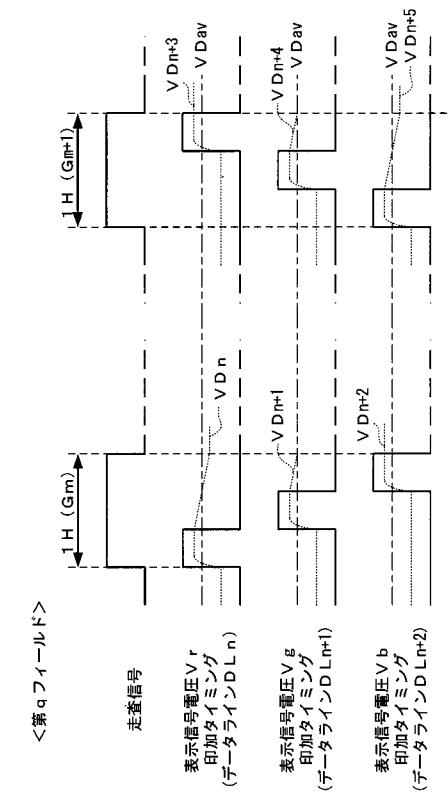

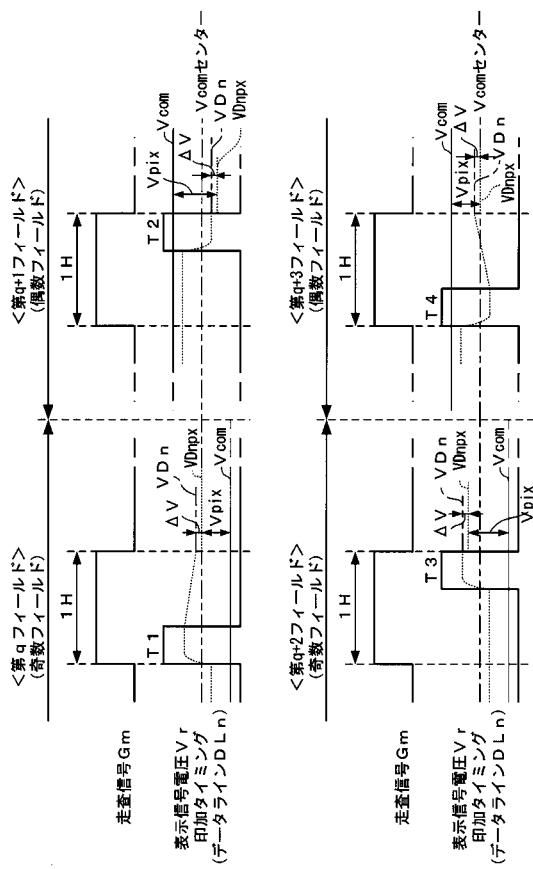

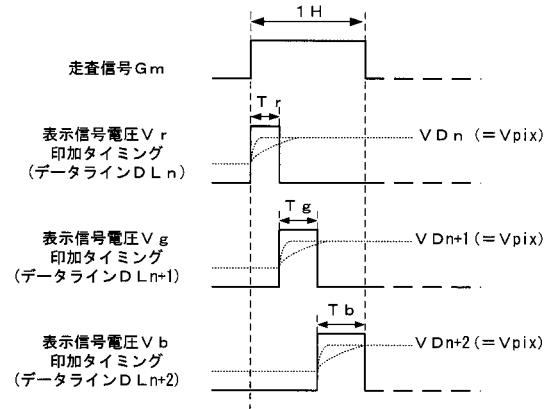

図 11 は、第 1 の駆動制御方法におけるフィールドスルーレ電圧の影響を説明するためのタイミングチャートであり、図 12 は、第 1 の駆動制御方法における表示信号電圧の印加タイミングと画素電極電圧との関係を示す図である。また、図 13 は、本実施形態に係る液晶表示装置の第 3 の駆動制御方法の制御概念を示す要部タイミングチャートであり、図 14 は、第 3 の駆動制御方法における表示信号電圧の印加タイミングと画素電極電圧との関係を示す図である。ここでは、上述した液晶表示装置（図 1～図 3 参照）の構成を適宜参照しながら説明する。また、第 1 及び第 2 の駆動制御方法と同等の動作については、その説明を簡略化又は省略する。

#### 【0073】

上述した第 1 及び第 2 の駆動制御方法においては、選択期間（1 水平期間）内に各表示画素に書き込み、保持された電荷のリークに伴う画素電位の低下に起因する、輝度のバラツキ（画質の劣化）を抑制する手法について説明したが、第 3 の駆動制御方法においては、液晶表示パネルに特有のフィールドスルーレ電圧 V に起因する画素電位の低下の影響をさらに加味して、液晶の焼き付きや表示画質の劣化を抑制する手法を有している。

#### 【0074】

すなわち、第 1 及び第 2 の駆動制御方法においては、図 5 に示したように、少なくともフィールド期間ごとに表示信号電圧 Vr、Vg、Vb の印加順序を Vr Vg Vb の正順序、又は、Vb Vg Vr の逆順序に切り換えるように分配マルチブレクサを切り換え制御しているため、特定の走査ライン SLm 及びデータライン DLn に着目した場合、図 11、図 12(a) に示すように、奇数フィールド期間となる第 q フィールド期間、第 q + 2 フィールド期間、・・・においては、走査信号 Gm により設定される選択期間（1H）中の初期のタイミング T1 で、ソースドライバ 130A（分配マルチブレクサ 136）からデータライン DLn に対して表示信号電圧 Vr が印加され、偶数フィールド期間となる第 q + 1 フィールド期間、第 q + 3 フィールド期間、・・・においては、選択期間（1H）中の末期のタイミング T2 で、データライン DLn に対して表示信号電圧 Vr が印加される。

#### 【0075】

ここで、液晶表示パネルにおいては、液晶への直流電圧の印加による焼き付きを防止するため、周知のように、フィールド反転駆動、さらには、ライン反転駆動方法が適用される。これにより、図 11 に示すように、例えば、奇数フィールド期間においては、コモン電圧の中心電圧（Vcom センター）よりも低電位側にコモン電圧 Vcom (= L) が設定されて、ソースドライバ 130A からデータライン DLn に印加される表示信号電圧 Vr（データライン電圧 VDn）は、当該コモン電圧 Vcom に対して高電位となるように設定され

10

20

30

40

50

、一方、偶数フィールド期間においては、 $V_{com}$ センターよりも高電位側にコモン電圧 $V_c$ <sub>om</sub>( = H )が設定されて、ソースドライバ130Aからデータライン $D_L n$ に印加される表示信号電圧 $V_r$  (データライン電圧 $V_D n$ )は、当該コモン電圧 $V_{com}$ に対して低電位となるように設定される。

## 【0076】

この場合、第1の駆動制御方法においても説明したように、書込動作終了後の選択期間中に、データライン $D_L n$ に設けられた保護素子を介して、表示画素 $P_x$ に保持された電荷がリークするとともに、当該選択期間の終了(走査信号 $G_m$ の供給遮断；ローレベルの走査信号 $G_m$ の印加)に伴って、周知のフィールドスルーレ電圧 V 分の電圧降下が生じる。これにより、表示画素 $P_x$ に保持される実質的な画素電位 $V_{pix}$ は、選択期間終了直前のデータライン電圧 $V_D n$ からフィールドスルーレ電圧 V 分降下した電圧(画素電極電圧) $V_D npx$ と、コモン電圧 $V_{com}$ との差分となる。

## 【0077】

この画素電極電圧 $V_D npx$ は、図11に示すように、コモン電圧 $V_{com}$ に対して高電位となる表示信号電圧 $V_r$  (データライン電圧 $V_D n$ )が印加される奇数フィールド期間においては、タイミングT1における書込動作後の電荷のリークにより低下したデータライン電圧 $V_D n$ から、さらにフィールドスルーレ電圧 V 分低下することにより、 $V_{com}$ センター(もしくは、コモン電圧 $V_{com}$ )に近づく方向に変化するのに対して、コモン電圧 $V_{com}$ に対して低電位となる表示信号電圧 $V_r$  (データライン電圧 $V_D n$ )が印加される偶数フィールド期間においては、タイミングT2における書込動作後の電荷のリークがほとんど生じないデータライン電圧 $V_D n$ から、フィールドスルーレ電圧 V 分低下することにより、 $V_{com}$ センター(もしくは、コモン電圧 $V_{com}$ )から遠ざかる方向に変化するので、図12(b)に示すように、例えば、奇数フィールド期間における画素電極電圧 $V_D npx$ の $V_{com}$ センターからのずれを“±0”(基準)とした場合には、偶数フィールド期間における画素電極電圧 $V_D npx$ の $V_{com}$ センターからのずれは常に“-”(負)の状態となり、画素電位 $V_{pix}$ が負側に偏って液晶に直流成分が印加される頻度が高くなり、液晶の焼き付きや表示画像にフリッカが生じる可能性がある。

## 【0078】

そこで、第3の駆動制御方法においては、上述した液晶表示装置と同等の構成において、特定の走査ライン $S_L m$ 及びデータライン $D_L n$ に着目した場合、図13、14(a)に示すように、連続する4つのフィールド期間を1周期として、奇数フィールド期間となる第qフィールド期間においては、走査信号 $G_m$ により設定される選択期間(1H)中の初期のタイミングT1で、ソースドライバ130A(分配マルチプレクサ136)からデータライン $D_L n$ に対して表示信号電圧 $V_r$ が印加され、偶数フィールド期間となる第q+1フィールド期間においては、選択期間(1H)中の末期のタイミングT2で、データライン $D_L n$ に対して表示信号電圧 $V_r$ が印加され、奇数フィールド期間となる第q+2フィールド期間においては、選択期間(1H)中の末期のタイミングT3で、データライン $D_L n$ に対して表示信号電圧 $V_r$ が印加され、偶数フィールド期間となる第q+3フィールド期間においては、選択期間(1H)中の初期のタイミングT4で、データライン $D_L n$ に対して表示信号電圧 $V_r$ が印加される。

## 【0079】

ここで、上述した場合と同様に、図13に示すように、奇数フィールド期間においては、 $V_{com}$ センターよりも低電位側にコモン電圧 $V_{com}$ ( = L )が設定されて、当該コモン電圧 $V_{com}$ に対して高電位となる表示信号電圧 $V_r$  (データライン電圧 $V_D n$ )がデータライン $D_L n$ に印加され、一方、偶数フィールド期間においては、 $V_{com}$ センターよりも高電位側にコモン電圧 $V_{com}$ ( = H )が設定されて、当該コモン電圧 $V_{com}$ に対して低電位となる表示信号電圧 $V_r$  (データライン電圧 $V_D n$ )がデータライン $D_L n$ に印加される。

## 【0080】

これにより、本駆動制御方法においては、書込動作終了後の選択期間中における電荷のリークと、当該選択期間の終了時のフィールドスルーレによる電圧降下に基づいて規定され

10

20

30

40

50

る表示画素  $P \times$  の画素電極電圧  $V_{D npx}$  は、図 13 に示すように、コモン電圧  $V_{com}$  に対して高電位となる表示信号電圧  $V_r$  (データライン電圧  $V_{D n}$ ) が印加される第  $q$  フィールド期間 (奇数フィールド期間)、及び、コモン電圧  $V_{com}$  に対して低電位となる表示信号電圧  $V_r$  (データライン電圧  $V_{D n}$ ) が印加される第  $q + 3$  フィールド期間 (偶数フィールド期間) においては、タイミング  $T_1$  又は  $T_4$  における書込動作後の電荷のリークにより低下したデータライン電圧  $V_{D n}$  から、さらにフィールドスルーレ電圧  $V$  分低下することにより、 $V_{com}$  センター (もしくは、コモン電圧  $V_{com}$ ) に近づく方向に変化する。

#### 【0081】

また、コモン電圧  $V_{com}$  に対して低電位となる表示信号電圧  $V_r$  (データライン電圧  $V_{D n}$ ) が印加される第  $q + 1$  フィールド期間 (偶数フィールド期間)、及び、コモン電圧  $V_{com}$  に対して高電位となる表示信号電圧  $V_r$  (データライン電圧  $V_{D n}$ ) が印加される第  $q + 2$  フィールド期間 (奇数フィールド期間) においては、表示画素  $P \times$  の画素電極電圧  $V_{D npx}$  は、タイミング  $T_2$  又は  $T_3$  における書込動作後の電荷のリークがほとんど生じないデータライン電圧  $V_{D n}$  から、フィールドスルーレ電圧  $V$  分低下することにより、 $V_{com}$  センター (もしくは、コモン電圧  $V_{com}$ ) から遠ざかる方向、もしくは、依然として  $V_{com}$  センターに対して充分な電圧差を有する電圧に変化する。

#### 【0082】

すなわち、図 14 (b) に示すように、例えば、タイミング  $T_1$ 、 $T_4$  における画素電極電圧  $V_{D npx}$  の  $V_{com}$  センターからのずれを “±0” (基準) とした場合、タイミング  $T_2$  における画素電極電圧  $V_{D npx}$  の  $V_{com}$  センターからのずれは “-” (負) の状態となり、タイミング  $T_3$  における画素電極電圧  $V_{D npx}$  の  $V_{com}$  センターからのずれは “+” (正) の状態となるので、4つのフィールド期間分を1周期とした場合にあっては、画素電位  $V_{pix}$  の偏りが解消されて液晶に印加される直流成分が相殺され、液晶の焼き付きやフリッカの発生を防止することができる。

#### 【0083】

##### (第4の駆動制御方法)

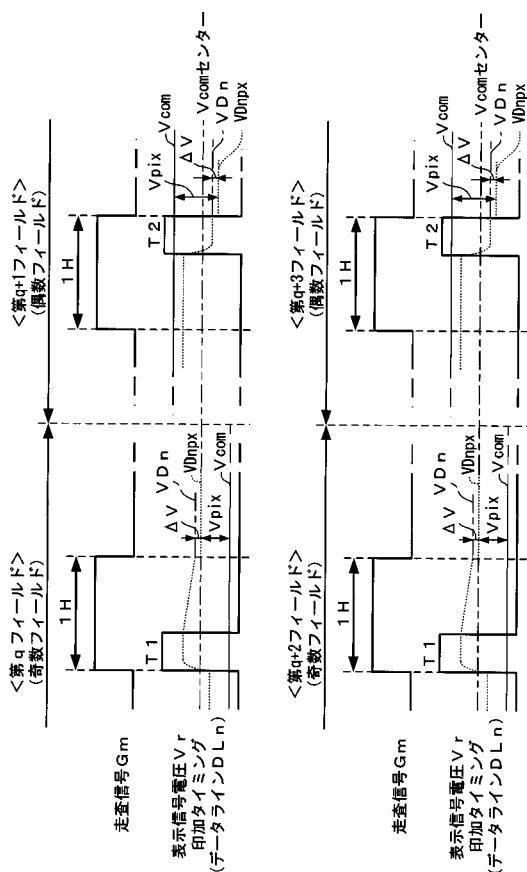

図 15 は、第 1 乃至第 3 の駆動制御方法における表示画素への書き込み速度の影響を説明するためのタイミングチャートであり、図 16 は、本実施形態に係る液晶表示装置の第 4 の駆動制御方法の制御概念を示す要部タイミングチャートである。ここでは、上述した液晶表示装置 (図 1 ~ 図 3 参照) の構成を適宜参照しながら説明する。また、第 1 及び第 2 の駆動制御方法と同等の動作については、その説明を簡略化又は省略する。

#### 【0084】

上述した第 1 乃至第 3 の駆動制御方法においては、ソースドライバ (分配マルチプレクサ) からゲートライン  $D_L$  に印加される表示信号電圧の表示画素への書き込み動作が、一定の書き込み期間内に完了する場合 (すなわち、表示画素に設けられた画素トランジスタのトランジスタサイズが、比較的大きい場合) について説明したが、第 4 の駆動制御方法においては、表示画素に設けられた画素トランジスタのトランジスタサイズ等により規定される、表示信号電圧の書き込み動作の所要時間に対応させて、各書き込み期間を異ならせるように設定する。

#### 【0085】

すなわち、例えば、高精細な液晶表示パネルや小型の液晶表示パネルにおいては、各表示画素の面積が小さくなるため、開口率を向上させるために画素トランジスタを小さく形成する場合がある。この場合、画素トランジスタの駆動能力が小さくなるので、ソースドライバからデータラインを介して印加される表示信号電圧を、画素容量に書き込むために要する時間が相対的に長くなる。

#### 【0086】

ここで、上述した第 1 乃至第 3 の駆動制御方法に示したように、選択期間内に設定された各書き込み期間  $T_c$  を同一の時間に設定し、かつ、各表示画素への表示信号電圧の書き込み動作に要する時間が、当該書き込み期間  $T_c$  よりも長い場合には、図 15 に示すように、書き込み期間後も選択期間が継続して、画素トランジスタがオン動作している表示画素  $P \times$  においては

10

20

30

40

50

、当該選択期間が終了するまでに表示信号電圧の書き込み動作が完了して、表示信号電圧  $V_r$  、  $V_g$  に基づく各データライン電圧  $V_{Dn}$  、  $V_{Dn+1}$  と画素電位  $V_{pix}$  とが同等になる ( $V_{Dn} = V_{pix}$  、  $V_{Dn+1} = V_{pix}$ ) が、書き込み期間の終了と略同時に選択期間が終了する表示画素  $P_x$  においては、表示信号電圧を充分に書き込むことができず、表示信号電圧  $V_b$  に基づく各データライン電圧  $V_{Dn+2}$  と画素電位  $V_{pix}$  とが異なり ( $V_{Dn+2} \neq V_{pix}$ ) 、正常な画像表示を行うことができなくなる可能性がある。

#### 【0087】

そこで、第4の駆動制御方法においては、上述した液晶表示装置と同等の構成において、図16に示すように、少なくとも選択期間 (1H) 中の末期に設定される表示信号電圧  $V_b$  の印加タイミングにおける書き込み期間  $T_b$  が、表示画素  $P_x$  に設けられた画素トランジスタ TFT のトランジスタサイズ等により規定される書き速度で、当該表示信号電圧  $V_b$  の書き込み動作が完了するまでの時間に設定され、選択期間中の初期及び中期に設定される他の書き込み期間  $T_r$  、  $T_g$  が、上記書き込み期間  $T_b$  よりも短い時間に設定されるように、ソースドライバ (分配マルチプレクサ) における出力タイミングが制御される。

#### 【0088】

これによれば、書き込み期間  $T_r$  、  $T_g$  後も選択期間が継続して、画素トランジスタがオン動作している表示画素  $P_x$  においては、当該選択期間が終了するまでに表示信号電圧  $V_r$  、  $V_g$  の書き込み動作が完了し、また、書き込み期間  $T_b$  の終了と略同時に選択期間が終了する表示画素  $P_x$  においては、表示信号電圧  $V_b$  の書き込み動作が完了するまでの時間に書き込み期間  $T_b$  が設定されているので、いずれの表示信号電圧も良好に書き込むことができ（書き量を均一化することができ）、表示信号電圧  $V_r$  、  $V_g$  、  $V_b$  に基づく各データライン電圧  $V_{Dn}$  、  $V_{Dn+1}$  、  $V_{Dn+2}$  と画素電位  $V_{pix}$  を一致させて正常な画像表示を行うことができる。

#### 【0089】

なお、図16に示した本駆動制御方法においては、表示画素に保持された電荷のリークの影響については言及しなかったが、本実施形態についても書き込み期間  $T_r$  、  $T_g$  後の選択期間に、電荷のリークによりデータライン電圧が顕著に低下する場合には、上述した第1乃至第3の駆動制御方法に示したように、表示信号電圧の各データライン DL への印加タイミングを、フィールド期間ごと、さらには、走査ラインごとに正順序又は逆順序に切り換えることにより、表示画質の改善や液晶の焼き付きを防止することができる。

#### 【0090】

##### <表示装置の第2の実施形態>

次いで、上述したような各駆動制御方法を適用可能な、本発明に係る表示装置の第2の実施形態について、図面を参照して簡単に説明する。

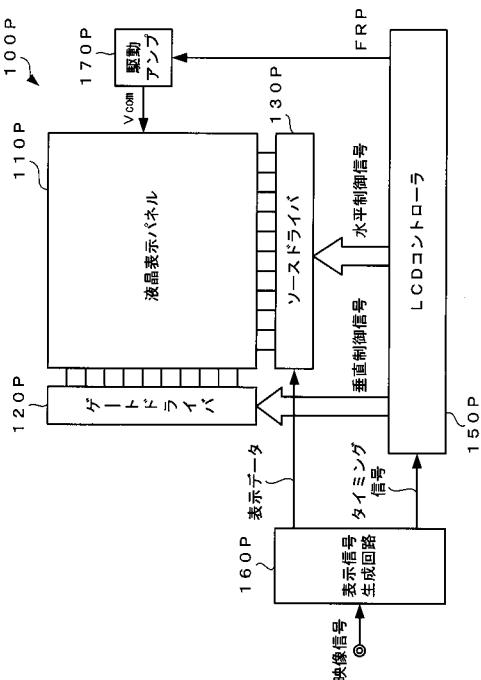

図17は、本発明に係る表示装置を適用した液晶表示装置の第2の実施形態の全体構成を示す概略ブロック図であり、図18は、本発明に係る表示装置を適用した液晶表示装置の要部構成例を示す概略構成図である。ここで、上述した第1の実施形態と同等の構成については、同等又は同一の符号を付してその説明を簡略化又は省略する。

#### 【0091】

図17、図18に示すように、本構成例に係る液晶表示装置 100B は、概略、上述した第1の実施形態（図1参照）と同様に、液晶表示パネル 110 と、ゲートドライバ 120B と、ソースドライバ 130B と、LCDコントローラ 150 と、表示信号生成回路 160 と、コモン電圧駆動アンプ 170 と、を備え、さらに、本実施形態特有の構成として、液晶表示パネル 110 とソースドライバ 130B との間に、ソースドライバ 130B から出力されるシリアルデータからなる表示信号電圧を、液晶表示パネル 110 に配設された各データライン DL に分配して印加するトランスマスイッチ部（データ分配手段） 140 と、ゲートドライバ 120B 内に一体的に形成され、トランスマスイッチ部 140 を駆動制御するためのマルチプレクサ制御信号を生成、出力するスイッチ駆動部（スイッチ駆動制御手段） SWD と、を設けた構成を有している。

#### 【0092】

10

20

30

40

50

ここで、本実施形態においては、図18に示すように、少なくとも、液晶表示パネル110を構成する複数の表示画素Pxが2次元配列される画素アレイPxAと、ゲートドライバ120B及びトランスファスイッチ部140が、ガラス基板等の絶縁性基板SUB上に一体的に形成された構成を適用することができる。また、ソースドライバ130Bは、該絶縁性基板SUBとは別個のドライバチップとして形成され、絶縁性基板SUB上に形成された配線電極(接続接点)を介して電気的に接続されるとともに、絶縁性基板SUB上に外付け(後付け)部品として搭載される構成を有している。

#### 【0093】

なお、この場合、表示画素Pxを構成する画素トランジスタ(図21に示した画素トランジスタTFTに相当する)、及び、後述するゲートドライバ120B及びトランスファスイッチ部140(薄膜トランジスタ等)を、例えば、アモルファスシリコンを適用して同一の製造プロセスで形成することができる。これにより、すでに技術的に確立されたアモルファスシリコン製造プロセスを適用して、安価に液晶表示装置を製造することができるとともに、動作特性の安定した機能素子を実現することができるので、液晶表示装置の表示特性を向上させることができる。

#### 【0094】

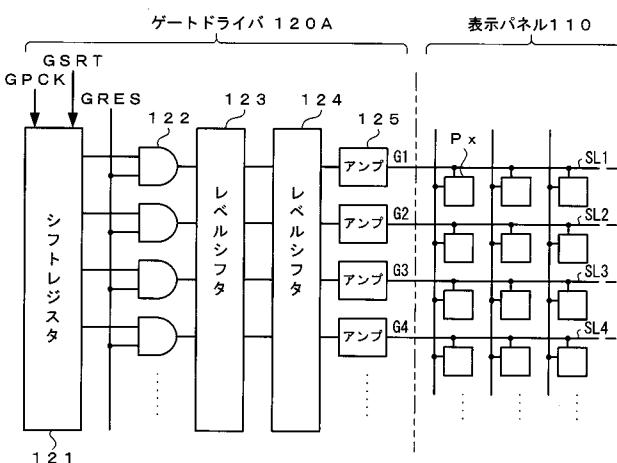

図19は、本実施形態に係る液晶表示装置に適用されるゲートドライバ及びスイッチ駆動部の一具体例を示す概略構成図である。ここでは、上述した図17、図18に示した構成を適宜参照しながら説明する。

ゲートドライバ120Bは、図19に示すように、図2に示したゲートドライバ120Aの構成に加え、トランスファスイッチ部140を駆動制御するためのスイッチ駆動部(スイッチ駆動制御手段)SWDが一体的に形成された構成を有している。ここで、スイッチ駆動部SWDは、図19に示すように、LCDコントローラ150から供給されるトランスファスイッチ制御信号(マルチプレクサ制御信号CNmx0、CNmx1及びスイッチリセット信号SDRES)に基づいて、所定のタイミングでデコード信号を順次出力するデコーダ126と、ゲートドライバ120Bを構成するAND回路122と同様に、デコーダ126から出力されるデコード信号を一方の入力とし、LCDコントローラ150から供給されるゲートリセット信号GRESを他方の入力とするAND回路127と、該AND回路127からの出力信号を所定の信号レベルに設定する複数段のレベルシフタ(上述したゲートドライバ120Bに示したレベルシフタ123、124と同一の構成)及び出力アンプ128と、を備えた構成を有している。

#### 【0095】

このような構成を有するスイッチ駆動部SWDにおいては、LCDコントローラ150からトランスファスイッチ制御信号として供給されるマルチプレクサ制御信号CNmx0、CNmx1及びスイッチリセット信号SDRESに基づいて、デコーダ126により生成されるデコード信号が、AND回路127の一方の入力接点に入力される。

#### 【0096】

ここで、スイッチ駆動部SWDにおいては、上述したゲートリセット信号GRESをハイレベルに設定した状態(ゲートドライバの駆動状態)において、LCDコントローラ150から供給されるマルチプレクサ制御信号CNmx0、CNmx1及びスイッチリセット信号SDRESの各信号レベルに基づいて、トランスファスイッチ部140の分配マルチプレクサの動作状態をフィールド期間ごと、さらには、走査ラインごとに切り換え制御するマルチプレクサ制御信号CNmx2が生成、出力される。

#### 【0097】

ソースドライバ130Bは、図3に示したソースドライバ130Aにおいて、トランスファスイッチ部を除いた構成を有し、表示信号生成回路160から並列的に供給される複数系統の表示データを順次取り込み、3入力マルチプレクサ(データ変換部)133により時分割的に配列された1系統の画素データ(R、G、B)に変換し、D/Aコンバータ134によりアナログ変換して、配線電極(接続接点)を介してトランスファスイッチ部140に表示信号電圧Vrgbとして出力する。

10

20

30

40

50

## 【0098】

また、トランスファスイッチ部140は、概略、図3に示したトランスファスイッチ部と同等であって、上述したソースドライバ130Bから、時分割シリアルデータとして供給された表示信号電圧V<sub>rgb</sub>を、各データラインに対応した個別の表示信号電圧に分配して、スイッチ駆動部SWDから出力されるマルチブレクサ制御信号C<sub>Nmx2</sub>に基づく所定の順序で、各データラインに順次印加する。

## 【0099】

したがって、本実施形態に係る表示装置においても、上述した各駆動制御方法を適用することにより、表示画素に保持された電荷のリークに起因するフリッカの発生や画素電位の偏りに起因する液晶の焼き付き、表示画素（画素トランジスタ）の書込速度に起因する書込不良等を、良好に抑制して表示画質や製品寿命の改善を図ることができる。10

## 【0100】

また、本実施形態に係る表示装置においては、液晶表示パネル110（画素エリアP<sub>X</sub>A）に配設された各データラインDLに接続された表示画素Pxに供給する表示信号電圧を、ソースドライバ130B内部で複数本のデータラインDLを一組として時分割シリアルデータに変換して、絶縁性基板SUB上に画素エリアP<sub>X</sub>Aとともに一体的に形成されたトランスファスイッチ部140に出力し、該トランスファスイッチ部140により各組の時分割シリアルデータを時分割タイミングに応じて分配して、所定の順序で各組のデータラインDLに順次印加することができる、絶縁性基板SUBに設けられたトランスファスイッチ部140と、該絶縁性基板SUBとは別個に設けられたソースドライバ130Bとの間を、上記データラインDLの組数分の接続端子により接続することができる。20

## 【0101】

これにより、液晶表示パネル110とソースドライバ130B間の接続端子の数を数分の1（各組に含まれるデータラインの本数分の1）に削減して、当該接続端子間のピッチを比較的広く設計することができるので、当該接続工程における工数を削減することができるとともに、比較的低い接続精度であっても良好に接続することができ、製造コストの削減を図ることができる。

## 【0102】

なお、上述した各実施形態においては、本発明に係る表示装置を液晶表示装置に適用した場合について説明したが、本発明はこれに限定されるものではなく、例えば、液晶表示パネルに限らず、有機ELパネル等の他の表示パネルに適用することができることはいうまでもない。さらに、アクティブマトリクス型の駆動方式に対応した表示パネルに適用する場合にあっては、ゲートドライバとスイッチ駆動部とを一体的に構成することができるので、回路構成及び駆動制御方法（制御信号の処理等）の両面において共通化を図ることができることできる。30

## 【図面の簡単な説明】

## 【0103】

【図1】本発明に係る表示装置を適用した液晶表示装置の第1の実施形態の全体構成を示す概略プロック図である。

【図2】本実施形態に係る液晶表示装置に適用されるゲートドライバの一具体例を示す概略構成図である。40

【図3】本実施形態に係る液晶表示装置に適用されるソースドライバの一具体例を示す概略構成図である。

【図4】本実施形態に係る液晶表示装置の駆動制御動作の一例を示すタイミングチャートである。

【図5】本実施形態に係る液晶表示装置の第1の駆動制御方法の制御概念を示す要部タイミングチャートである。

【図6】第1の駆動制御方法における作用効果を説明するための、比較対象となる他の駆動制御方法の例を示すタイミングチャートである。

【図7】当該比較対象となる他の駆動制御方法における表示画質の概念図である。50

【図 8】本実施形態に係る液晶表示装置の駆動制御動作の他の例を示すタイミングチャートである。

【図 9】本実施形態に係る液晶表示装置の第 2 の駆動制御方法の制御概念を示す要部タイミングチャートである。

【図 10】第 2 の駆動制御方法における表示画質の概念図である。

【図 11】第 1 の駆動制御方法におけるフィールドスルーレ電圧の影響を説明するためのタイミングチャートである。

【図 12】第 1 の駆動制御方法における表示信号電圧の印加タイミングと画素電極電圧との関係を示す図である。

【図 13】本実施形態に係る液晶表示装置の第 3 の駆動制御方法の制御概念を示す要部タイミングチャートである。 10

【図 14】第 3 の駆動制御方法における表示信号電圧の印加タイミングと画素電極電圧との関係を示す図である。

【図 15】第 1 乃至第 3 の駆動制御方法における表示画素への書き込み速度の影響を説明するためのタイミングチャートである。

【図 16】本実施形態に係る液晶表示装置の第 4 の駆動制御方法の制御概念を示す要部タイミングチャートである。

【図 17】本発明に係る表示装置を適用した液晶表示装置の第 2 の実施形態の全体構成を示す概略構成図である。

【図 18】本発明に係る表示装置を適用した液晶表示装置の要部構成例を示す概略構成図である。 20

【図 19】本実施形態に係る液晶表示装置に適用されるゲートドライバ及びスイッチ駆動部の一具体例を示す概略構成図である。

【図 20】従来技術における薄膜トランジスタ(TFT)型の表示画素を備えた液晶表示装置の概略構成を示す構成図である。

【図 21】従来技術における液晶表示パネルの要部構成の一例を示す等価回路図である。

【符号の説明】

【0104】

100A、100B 液晶表示装置

110 液晶表示パネル

30

120A、120B ゲートドライバ

130A、130B ソースドライバ

140 トランスファスイッチ部

150 LCDコントローラ

SWD スイッチ駆動部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【 四 9 】

【 図 1 1 】

【 四 1 0 】

〈第9フィールド〉

(奇数フィールド)

〈第q+1フィールド〉

(偶数フィールド)

【図 1-2】

|          | 印加タイミング       | T 1 | T 2   | T 1 | T 2   |

|----------|---------------|-----|-------|-----|-------|

| Gm/VDnpx | Vcomセンターからのずれ | ±0  | - (負) | ±0  | - (負) |

|          | Vcom極性        | L   | H     | L   | H     |

( b )

【図13】

【 図 1 5 】

【 図 1 4 】

ずれ =

| Gm/VDnpix | 印加タイミング       | T1 | T2    | T3    | T4 |

|-----------|---------------|----|-------|-------|----|

|           | Vcomセンターからのずれ | ±0 | - (負) | + (正) | ±0 |

|           | Vcom極性        | L  | H     | L     | H  |

【 図 1 6 】

【図17】

【図18】

【図19】

【図20】

【図21】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

| F I     | テーマコード(参考)   |

|---------|--------------|

| G 0 9 G | 3/20 6 2 1 M |

| G 0 9 G | 3/20 6 2 3 D |

| G 0 9 G | 3/20 6 2 3 F |

| G 0 9 G | 3/20 6 2 3 G |

| G 0 9 G | 3/20 6 2 3 H |

| G 0 9 G | 3/20 6 2 3 L |

| G 0 9 G | 3/20 6 2 3 R |

| G 0 9 G | 3/20 6 4 1 A |

| G 0 9 G | 3/20 6 4 1 C |

| G 0 9 G | 3/20 6 4 2 L |

| G 0 9 G | 3/20 6 8 0 G |

| H 0 4 N | 5/66 1 0 2 B |

(72)発明者 稲垣 直樹

東京都八王子市石川町2951番地の5

センター内

カシオ計算機株式会社八王子技術

F ターム(参考) 2H093 NA32 NC16 NC22 NC24 NC34 ND34 ND49 NH15

5C006 AA01 AA15 AA16 AA22 AC11 AC21 AC28 AF22 AF44 AF45

AF46 AF51 AF52 AF53 AF61 AF69 AF71 AF83 BB16 BC03

BC11 BC20 BF03 BF04 BF05 BF14 BF24 BF25 FA41 FA47

5C058 AA06 BA01 BA26

5C080 AA10 BB05 CC03 DD03 DD22 DD26 DD28 EE28 FF11 JJ02

JJ03 JJ05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示驱动装置及其驱动控制方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP2005195703A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 公开(公告)日 | 2005-07-21 |

| 申请号            | JP2003435928                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2003-12-26 |

| [标]申请(专利权)人(译) | 卡西欧计算机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 卡西欧计算机有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 平山 隆一<br>樺山 俊二<br>稻垣 直樹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 发明人            | 平山 隆一<br>樺山 俊二<br>稻垣 直樹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G02F1/133 G02F1/136 G09G3/20 G09G3/36 H04N5/66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| CPC分类号         | G09G3/3677 G09G3/3688 G09G2310/027 G09G2310/0297 G09G2320/0233                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G02F1/133.570 G09G3/20.611.A G09G3/20.621.B G09G3/20.621.M G09G3/20.623.D G09G3/20.623.F G09G3/20.623.G G09G3/20.623.H G09G3/20.623.L G09G3/20.623.R G09G3/20.641.A G09G3/20.641.C G09G3/20.642.L G09G3/20.680.G H04N5/66.102.B                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 2H093/NA32 2H093/NC16 2H093/NC22 2H093/NC24 2H093/NC34 2H093/ND34 2H093/ND49 2H093/NH15 5C006/AA01 5C006/AA15 5C006/AA16 5C006/AA22 5C006/AC11 5C006/AC21 5C006/AC28 5C006/AF22 5C006/AF44 5C006/AF45 5C006/AF46 5C006/AF51 5C006/AF52 5C006/AF53 5C006/AF61 5C006/AF69 5C006/AF71 5C006/AF83 5C006/BB16 5C006/BC03 5C006/BC11 5C006/BC20 5C006/BF03 5C006/BF04 5C006/BF05 5C006/BF14 5C006/BF24 5C006/BF25 5C006/FA41 5C006/FA47 5C058/AA06 5C058/BA01 5C058/BA26 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD03 5C080/DD22 5C080/DD26 5C080/DD28 5C080/EE28 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ05 2H193/ZA04 2H193/ZC02 |         |            |

| 其他公开文献         | <a href="#">JP4168339B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

### 摘要(译)

可以减小驱动器的芯片尺寸，可以减小功耗，可以减小安装面积，并且可以降低制造成本，并且可以抑制和必要在显示面板和外围电路的连接过程中的步骤数。提供一种能够降低连接精度的显示驱动装置，其驱动控制方法以及具有该显示驱动装置的显示装置。液晶显示装置(100A)包括以二维方式排列有多个显示像素(Px)的液晶显示面板(110)，以预定的时序向各扫描线(SL)依次施加扫描信号的栅极驱动器(120)和显示数据。源极驱动器130在预定的定时将由串行数据组成的显示信号电压分配并施加到每条数据线DL，LCD控制器产生并输出垂直控制信号，水平控制信号和数据转换控制信号。还有150 [选型图]图1