(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-49840

(P2005-49840A)

(43) 公開日 平成17年2月24日(2005.2.24)

(51) Int.Cl.<sup>7</sup>

**G09G 3/36**

**G02F 1/133**

**G09G 3/20**

**H04N 5/66**

F 1

GO9G 3/36

GO2F 1/133 550

GO2F 1/133 570

GO2F 1/133 575

GO9G 3/20 612U

テーマコード(参考)

2H093

5C006

5C058

5C080

審査請求 未請求 請求項の数 12 O L (全 17 頁) 最終頁に続く

(21) 出願番号

特願2004-194344 (P2004-194344)

(22) 出願日

平成16年6月30日 (2004.6.30)

(31) 優先権主張番号

2003-045449

(32) 優先日

平成15年7月4日 (2003.7.4)

(33) 優先権主張国

韓国(KR)

(71) 出願人

390019839

三星電子株式会社

大韓民国京畿道水原市靈通区梅灘洞416

(74) 代理人

100094145

弁理士 小野 由己男

(74) 代理人

100106367

弁理士 稲積 朋子

(72) 発明者

李 昇祐

大韓民国ソウル特別市衿川区始興2洞26

6番地冠岳ビヨクサンタウン519棟16

O1号

F ターム(参考) 2H093 NA16 NA53 NC10 NC12 NC21

NC29 NC34 NC35 NC49 NC65

ND06 ND33 ND58 NF04 NH15

最終頁に続く

(54) 【発明の名称】 液晶表示装置と、これの駆動方法及びその装置 {LIQUID CRYSTAL DISPLAY, AND METHOD AND APPARATUS FOR DRIVING THEREOF}

(57) 【要約】 (修正有)

【課題】 液晶の応答速度を高速化するための液晶表示装置と、これの駆動方法及び駆動装置を提供する。

【解決手段】 タイミング制御部は現在データと以前データを考慮した原始補償データと、現在データと原始補償データとの間の差動データを考慮して最終補償データを出力する。スキャンドライバ部はスキャン信号を順次に出力し、データドライバ部は最終補償データを基にしてデータ信号を出力する。垂直配向モードの液晶を具備する液晶パネルはスキャン信号を伝達するスキャンラインと、データ信号を伝達するデータラインと、スキャンラインとデータラインとの間に形成されたスイッチング素子とを具備し、スキャン信号に応答してデータ信号を基にして液晶を配列させて画像を表示する。これによって、垂直配向モードの液晶を採用する液晶表示装置のライジングタイムを改善することで液晶の応答速度を高速化することができる。

【選択図】 図5

**【特許請求の範囲】****【請求項 1】**

現在フレームのデータと以前フレームのデータを考慮して第1補正データを生成し、前記第1補正データと前記現在フレームのデータとの間の差動データを出力し、前記第1補正データ及び保存されている以前フレームの差動データに対応した第2補正データを出力するタイミング制御部と、

スキャン信号を順次に出力するスキャンドライバ部と、

前記第2補正データに対応したデータ電圧を出力するデータドライバ部と、

前記スキャン信号を伝達するスキャンラインと、前記データ信号を伝達するデータラインと、前記スキャンラインとデータラインとの間に形成されたスイッチング素子を具備した液晶パネルと、を含む液晶表示装置。 10

**【請求項 2】**

前記スキャンドライバ部は、前記液晶パネルに形成されることを特徴とする請求項1記載の液晶表示装置。

**【請求項 3】**

前記液晶パネルは、PVA (Patterned Vertical Alignment) モードを採用することを特徴とする請求項1記載の液晶表示装置。

**【請求項 4】**

前記タイミング制御部は、

以前フレームのデータ及び差動データを保存するメモリーと、

前記以前フレームのデータ及び現在フレームのデータを考慮して第1補正データを生成する補正データ反映部と、

前記第1補正データと前記現在フレームのデータを比較した差動データを生成し前記差動データを前記メモリーに保存する差動演算部と、

前記第1補正データと前記メモリーに既に保存されている差動データを考慮して前記第2補正データを生成する階調変更部と、を含むことを特徴とする請求項1記載の液晶表示装置。

**【請求項 5】**

前記タイミング制御部は、

以前フレームのデータを保存する第1メモリーと、

前記第1メモリーに保存された以前フレームのデータと前記現在フレームのデータを考慮して第1補正データを生成する補正データ反映部と、

前記第1補正データと前記現在データを比較して差動データを生成する差動演算部と、前記差動データを保存する第2メモリーと、

前記第1補正データと前記第2メモリーに既に保存されている以前フレームの差動データを考慮して前記第2補正データを生成する階調変更部と、を含むことを特徴とする請求項1記載の液晶表示装置。

**【請求項 6】**

前記タイミング制御部は、

一つのフレームに対応するxビットのデータを保存するメモリーと、

前記現在フレームのxビットのデータと前記メモリーに既に保存されている以前フレームのxビットのデータを考慮して第1補正データを生成する補正データ反映部と、

前記第1補正データと前記現在フレームのデータを比較してyビットの差動データを生成し、前記生成されたyビットの差動データを前記メモリーに保存する差動演算部と、

前記xビットの第1補正データと前記メモリーに既に保存されている以前フレームのyビットの差動データを考慮してxビットの第2補正データを生成する階調変更部と、を含むことを特徴とする請求項1記載の液晶表示装置。

**【請求項 7】**

前記xはyより大きいか同じであることを特徴とする請求項6記載の液晶表示装置。

**【請求項 8】**

10

20

30

40

50

複数のゲートラインと、前記ゲートラインと絶縁されて交差する複数のデータラインと、前記ゲートライン及び前記データラインに連結されているスイッチング素子を有し行列形態に配列された複数の画素と、を含む液晶表示装置の駆動方法において、

- (a) 前記ゲートラインにスキャン信号を順次に供給する段階と、

- (b) 現在フレームのデータと以前フレームのデータを考慮して第1補正データを生成する段階と、

- (c) 前記第1補正データと前記現在フレームのデータを考慮して差動データを生成する段階と、

- (d) 前記差動データを保存する段階と、

- (e) 既に保存されている以前フレームの差動データと前記現在フレームのデータを考慮して第2補正データを生成する段階と、

- (f) 前記第2補正データに対応したデータ電圧を前記ゲートラインに供給する段階と、を含む液晶表示装置の駆動方法。

#### 【請求項9】

前記段階(d)は前記差動データのうち、一部を保存する段階を含むことを特徴とする請求項8記載の液晶表示装置の駆動方法。

#### 【請求項10】

外部から入力される画像を表示する表示装置の駆動装置において、

現在フレームのデータと以前フレームのデータを考慮して第1補正データを生成し、前記現在フレームのデータと前記第1補正データとの間の差動データを生成し、前記第1補正データと前記差動データを考慮して第2補正データを出力することを特徴とする表示装置の駆動装置。

#### 【請求項11】

前記以前フレームのデータを保存する第1メモリーを含むことを特徴とする請求項10記載の表示装置の駆動装置。

#### 【請求項12】

前記差動データを保存する第2メモリーを含むことを特徴とする請求項10記載の表示装置の駆動装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、液晶表示装置と、この駆動方法及びその装置に関するもので、より詳細には液晶の応答速度を高速化するための液晶表示装置と、この駆動方法及びその装置に関する。

##### 【背景技術】

##### 【0002】

一般的に液晶表示装置(Liquid Crystal Display)は、スリムなデザイン、低消費電力、高解像度などの長所を基にしてノートブックコンピュータ用、モニタ用などの各種応用製品が出始めている。特に、液晶パネルの大型化が可能になってからTV用に急速に浮彫されている。しかし、動映像を主に表示するTVに採用されるためには液晶の応答速度が市場で平価される一番重要な平価基準のうちの一つである。

##### 【0003】

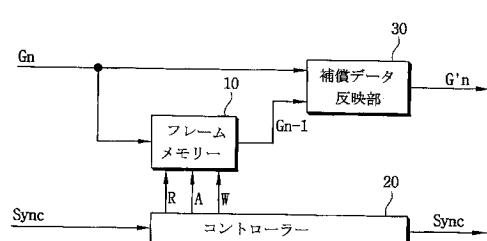

図1は、一般的な液晶の応答速度高速化方式を示すための図面である。ここで、前記液晶の応答速度高速化方式をDCC(Dynamic Capacitance Compensation)と命名して説明する。

##### 【0004】

図1に示すように、一般的に液晶の応答速度を高速化するために、フレームメモリー10はコントローラー20のアドレス、リード、ライト制御(A, R, W)によって一つのフレームだけの階調データを保存する。そして、補償データ反映部30は、現在フレームの階調データ(Gn)と以前フレームの階調データ(Gn-1)が印加されると、補正階

10

20

30

40

50

調データ（または補正データ電圧値）（G'n）を抽出して出力する。

【0005】

即ち、現在フレームの目標画素電圧と以前フレームの画素電圧を考慮して補正データ電圧を印加することで、画素電圧がすぐ目標画素電圧に到達して液晶の応答速度を高速化する。

【0006】

具体的に、現在フレームの目標画素電圧と以前フレームの画素電圧が異なる場合は、現在フレームの目標電圧より更に高い電圧を補正データ電圧として印加する。一番目のフレームからすぐ目標電圧レベルに到達するようにした後、以後のフレームでは目標電圧をデータ電圧に印加する方式を通じて液晶の応答速度を改善することができる。この時、前記補正データ電圧（即ち、電荷量）は、以前フレームの画素電圧によって決定される液晶キャパシタンスを考慮して決定する。即ち、以前フレームの画素電圧レベルを考慮して電荷量を供給することで、一番目のフレームからすぐ目標画素電圧レベルに到達するようとする。

【0007】

一方、広視野角のためにPVA（P a t t e r n e d V e r t i c a l A l i g n m e n t，以下PVAと称する）モードを採用する液晶表示装置が利用されている。

【0008】

前記PVAモードの液晶表示装置においては、前記画素電極（または透明電極）や共通電極（図示せず）に開口パターンを形成し、フリンジフィールド（F r i n g e f i e l d）を形成させて液晶の傾く方向を色々な方向に均一に分散させることで、広視野角を確保することができる。

【0009】

しかし、前記PVAモードを採用する液晶表示装置に応答速度の高速化方式（DCC）を適用しても画面の残像が目撃される。特に、液晶表示装置が大型化されるほどその程度は激しい。

【0010】

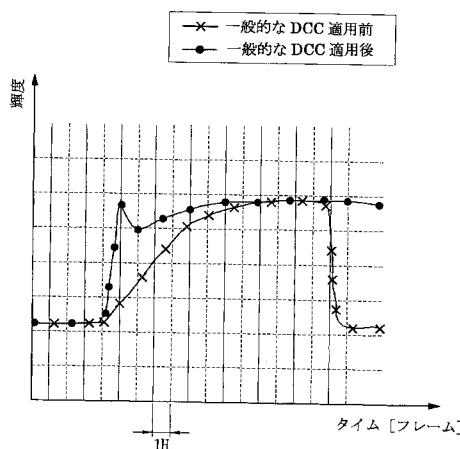

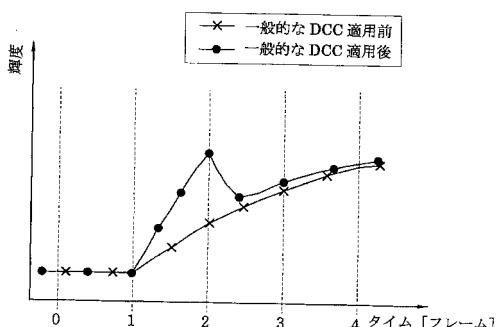

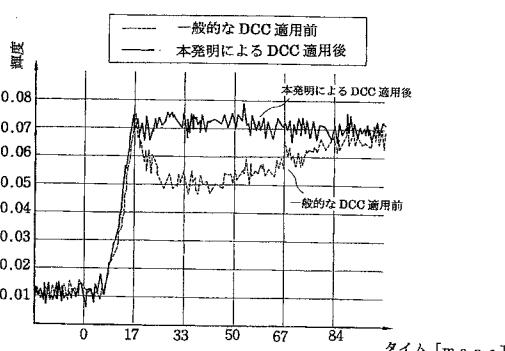

図2は、PVAモードの液晶表示装置に応答速度の高速化するためのDCC適用前後の応答特性を示したグラフである。

【0011】

図2に表示したように、一般にPVAモードにおいては中間階調でライジングタイム（r i s i n g t i m e）が非常に遅い。それにもまして前記したライジングタイムは7ないし8フレームに対応する時間まで遅延される。

【0012】

前記DCC方式を適用した場合、測定上には非常に早い応答特性を有することが測定されるが、実質的には輝度が再び落ちて画面の残像が残る問題点がある。特に、PVAモードの液晶表示装置に前記DCC方式を適用してもTVのように動映像表示をする時、画面の残像がよく目撃される問題点がある。

【0013】

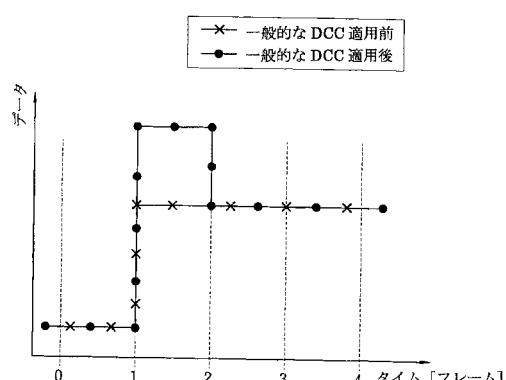

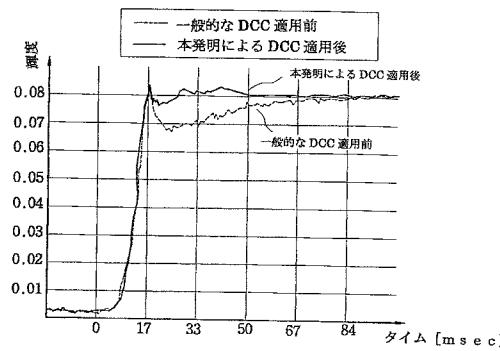

図3及び図4は一般的なDCC方式適用前と適用後によるデータ及び液晶の応答特性を示すための図面である。

【0014】

図3及び図4に図示したように、一般的に液晶の応答特性高速化方式（DCC方式）を適用する以前には、低階調から高階調に変化すると、液晶の応答特性がついていくことができない。そのため、2ないし3フレーム以後になってから目標画素電圧に該当する前記高階調に至る問題点がある。しかし、DCC方式を適用すると、低階調から高階調に変化する時、該当高階調に対応してオーバーシュート発生のためのデータ電圧を印加することで、液晶の応答特性を高速化することができる。

【0015】

しかし、液晶の実際の応答波形は上昇した後、再び落ちる現象を見せる。このような現

10

20

30

40

50

象は、利用者には画面に残像が残るように観察されて、画面の品質を悪化させる要因として作用する問題点がある。

【発明の開示】

【発明が解決しようとする課題】

【0016】

本発明の技術と課題は、このような従来の問題点を解決するためであり、本発明の目的は、液晶表示装置のライジングタイムを改善して液晶の応答速度を高速化するための液晶表示装置を提供することにある。

【0017】

また、本発明の他の目的は、前記液晶表示装置の駆動方法を提供することにある。 10

【0018】

また、本発明の他の目的は、表示装置の駆動装置を提供することにある。

【課題を解決するための手段】

【0019】

前記本発明の目的を実現するために、タイミング制御部は、現在フレームのデータと以前フレームのデータを考慮して第1補正データを生成し、前記第1補正データと前記現在フレームのデータとの間の差動データを出力し、前記第1補正データ及び保存されている以前フレームの差動データに対応した第2補正データを出力する。スキャンドライバ部はスキャン信号を順次に出力し、データドライバ部は前記第2補正データに対応したデータ電圧を出力する。 20

【0020】

液晶パネルは、前記スキャン信号を伝達するスキャンラインと、前記データ信号を伝達するデータラインと、前記スキャンラインとデータラインとの間に形成されたスイッチング素子を具備する。

【0021】

また、前記本発明の他の目的を実現するために、複数のゲートラインと、前記ゲートラインと絶縁されて交差する複数のデータラインと、前記ゲートライン及び前記データラインに連結されているスイッチング素子を有して行列形態に配列された複数の画素と、を含む液晶表示装置において、前記ゲートラインにスキャン信号を順次に供給し、現在フレームのデータと以前フレームのデータを考慮して第1補正データを生成し、前記第1補正データと前記現在フレームのデータを考慮して差動データを生成する。続いて、前記差動データを保存し、既に保存されている以前フレームの差動データと前記現在フレームのデータを考慮して第2補正データを生成した後、前記第2補正データに対応したデータ電圧を前記データラインに供給する。 30

【0022】

前記本発明の他の目的を実現するために、外部から入力される画像を表示する表示装置の駆動装置は、現在フレームのデータと以前フレームのデータを考慮して第1補正データを生成し、前記現在フレームのデータと前記第1補正データとの間の差動データを生成し、前記第1補正データと前記差動データを考慮して第2補正データを出力する。

【発明の効果】

【0023】

このような液晶表示装置と、この駆動方法及びその装置によると、液晶表示装置のライジングタイムを改善することで、液晶の応答速度を高速化することができ、表示品質を確保することができる。

【発明を実施するための最良の形態】

【0024】

以下、添付した図面を参照して本発明をより詳細に説明する。

【0025】

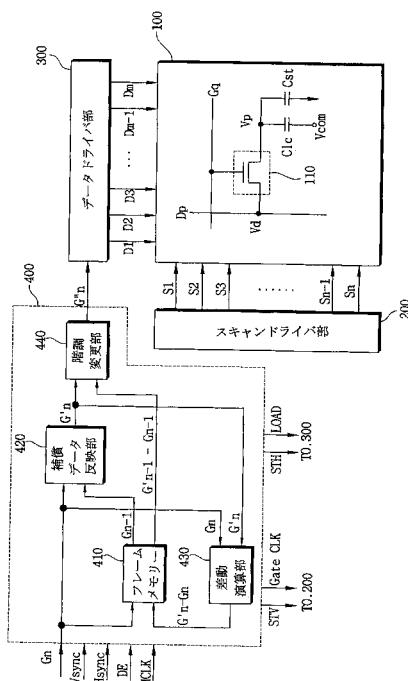

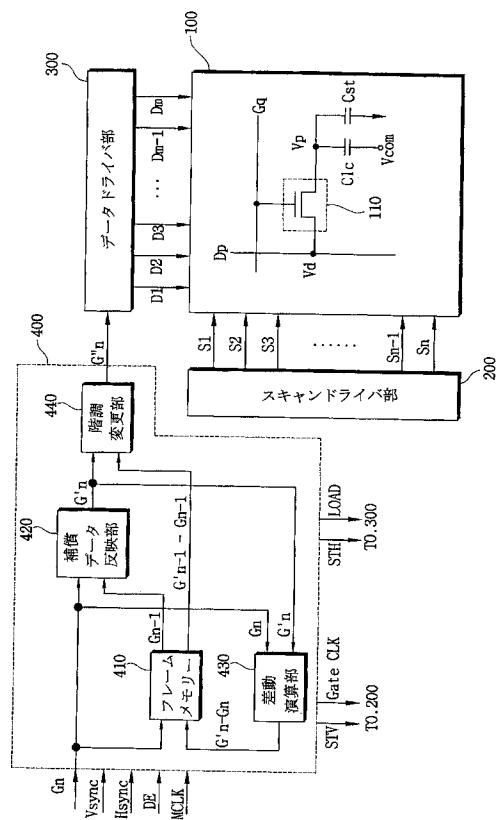

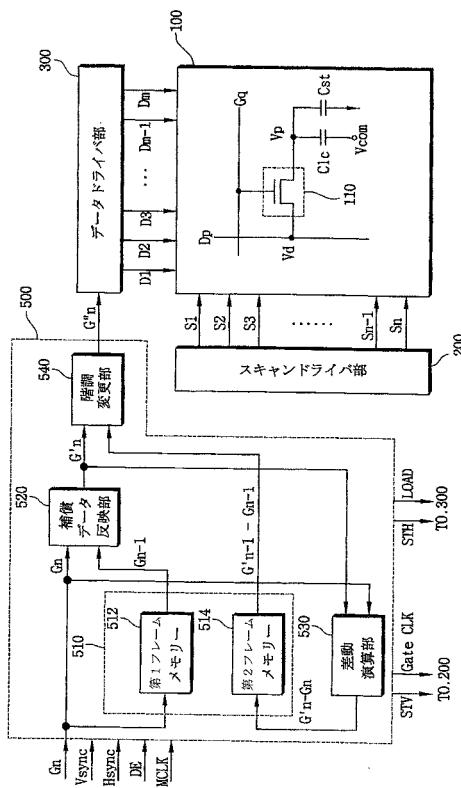

図5は、本発明の一実施例による液晶表示装置を示すための図面である。

【0026】

10

20

30

40

50

図5に示すように、本発明の一実施例による液晶表示装置は液晶パネル100、スキャンドライバ部200、データドライバ部300及びタイミング制御部400を含む。ここで、スキャンドライバ部200、データドライバ部300及びタイミング制御部400は、グラフィックコントローラーのような外部のホストから提供される階調データを液晶パネル100に適応するように変換して出力する液晶表示装置の駆動装置として動作を遂行する。

#### 【0027】

液晶パネル100にはゲートオン信号を伝達するための複数のゲートライン（走査ラインまたはスキャンライン）が形成されていて、また、補正されたデータ電圧を伝達するためのデータライン（またはソースライン）が形成されている。前記ゲートラインと前記データラインによって囲まれた領域はそれぞれ画素を構成し、各画素は前記ゲートラインと前記データラインにそれぞれゲート電極及びソース電極が連結される薄膜トランジスタ110と、前記薄膜トランジスタ110のドレイン電極に連結される液晶キャパシター（C1）と、ストレージキャパシター（Cst）を含む。液晶パネル100に採用される液晶はTN（Twisted Nematic）モードを採用するか、PVAモードを採用することもできる。

#### 【0028】

スキャンドライバ部200は、前記ゲートラインに順次にゲートオン電圧（S1, S2, S3, . . . , Sn）を印加して、前記ゲートオン電圧が印加されたゲートラインにゲート電極が連結される薄膜トランジスタ110をターンオンさせる。

#### 【0029】

前記スキャンドライバ部200は、別の印刷回路基板やFPC（Flexible Printed Circuit）を通じて具現可能であり、液晶パネル100に薄膜トランジスタ110を形成する時、前記薄膜トランジスタ110が形成される基板と同じ基板上に形成されることもできる。特に、同じ基板上に形成されるスキャンドライバ部200は複数のステージが連結され、各ステージの出力端が液晶パネルのゲートラインにそれぞれ連結されたシフトレジスタに具現される。

#### 【0030】

データドライバ部300は、前記データタイミング制御部400から受信された補正階調データ（Gn”）を該当階調電圧（またはデータ電圧）に変更したデータ信号（D1, D2, . . . , Dm）をそれぞれデータラインに印加する。

#### 【0031】

タイミング制御部400は、外部から第1タイミング信号（Vsync, Hsync, DE, MCLK）が印加されることで、第2タイミング信号（Gate Clk, STV）をスキャンドライバ部200に出力し、第3タイミング信号（LOAD, TH）をデータドライバ部300に出力する。

#### 【0032】

タイミング制御部400はフレームメモリー410、補償データ反映部420、差動演算部430及び階調変更部440を含み、現在フレームの階調データ（Gn）が印加されることで、現在フレームの階調データ（Gn）と以前フレームの階調データ（Gn-1）に対応する原始補償データ（G'n）を生成する。前記補償データ反映部420はルックアップテーブル（LUT）の形態に定義され、階調が変化する時に目標画素電圧よりは高いか低いデータ電圧が出力されるように制御する補正データを保存する。

#### 【0033】

タイミング制御部400は、現在フレームの階調データ（Gn）と原始補償データ（G'n）に対応する差動データ（G'n-Gn）を生成する。また、タイミング制御部400は、原始補償データ（G'n）と、以前フレームの階調データ（Gn-1）及び以前フレームの原始補償データ（Gn'-1）間の差動データ（G'n-1-Gn-1）とを考慮して生成した最終補償データ（G"n）をデータドライバ部300に出力する。前記最終補償データ（G"n）は液晶のライジングタイムを最適化することができるデータであ

る。

【0034】

即ち、以前フレームの階調データ( $G_{n-1}$ )と現在フレームの階調データ( $G_n$ )が同じ場合には補正しないが、以前フレームの階調データ( $G_{n-1}$ )がブラック階調に対応し、現在フレームの階調データ( $G_n$ )が明るい階調またはホワイト階調に対応する階調である場合、前記ブラック階調よりは高い階調が形成されるように最終補償データ( $G''_n$ )を出力する。即ち、現在フレームの階調データと以前フレームの階調データとの比較を通じてオーバーシュート波形形成のための最終補償データ( $G''_n$ )を出力する。

【0035】

具体的に、フレームメモリー410は、外部から提供される一つのフレームに対応する<sup>10</sup> $\times$ ビットの階調データ( $G_n$ )と差動演算部430から提供される $y$ ビットの差動データ( $G'_n - G_n$ )を保存する。そして、フレームメモリー410は、コントローラー(図示せず)の制御に応答して保存された以前フレームの階調データ( $G_{n-1}$ )を補償データ反映部420に提供する。さらに、フレームメモリー410は、保存された差動データ( $G'_n - G_{n-1}$ )を階調変更部440に提供する。このようにフレームメモリー410は一例に前記現在データが入力されることで、既に保存された以前データを出力し、前記現在データを保存するSDRAMである。

【0036】

補償データ反映部420は、現在フレームの階調データとフレームメモリー410に保存された以前フレームの階調データを考慮して現在フレームの原始補償データ( $G'_n$ )<sup>20</sup>を抽出する。そして、補償データ反映部420は、抽出された原始補償データ( $G'_n$ )を前記差動演算部430及び階調変更部440に出力する。

【0037】

差動演算部430は、現在フレームの原始補償データ( $G'_n$ )と現在フレームの階調データ( $G_n$ )との比較を通じて現在フレームの差動データ( $G'_n - G_n$ )を生成し、生成された差動データ( $G'_n - G_n$ )を前記フレームメモリー410に保存する。

【0038】

階調変更部440は、原始補償データ( $G'_n$ )と、以前フレームの階調データ( $G_{n-1}$ )及び以前フレームの原始補償データ( $G_{n'-1}$ )間の差動データ( $G'_n - 1 - G_{n-1}$ )とを考慮して最終補償データ( $G''_n$ )を生成し、生成された最終補償データ( $G''_n$ )をデータドライバ部300に出力する。例えば、RGBそれぞれの階調データが8ビットとして総24ビットであり、フレームメモリー410が32ビットのデータバスを有する場合、フレームメモリー410は8ビットのデータバスは使用しない。このような点を勘案してRGBそれぞれの差動データ( $G'_n - G_n$ )である8ビット、総24ビット全部を保存せず、RGBそれぞれの差動データの一部だけを保存することで液晶の応答速度を高速化する。<sup>30</sup>

【0039】

即ち、入力されるRGBそれぞれの階調データを $x$ ビットにする時、差動データ( $G'_n - G_n$ )としては、 $y$ ビット(ここで、 $y$ は $x$ より小さい整数)だけを保存するため、フレームメモリー410の数を一つだけ使用して保存することができる。RGB階調データに対応するそれぞれの差動データは、3、3、2ビット、3、2、3ビットまたは2、3、3ビットなどの多様な組合に保存されることができる。前記RGBそれぞれに対応する保存される差動データのビットはMSBに対応している。それゆえに、タイミング制御部400は、1つのフレームメモリー410を用いて最終補償データ( $G''_n$ )を生成することができる。<sup>40</sup>

【0040】

このようにすると、最小化されたフレームメモリーの数を利用して液晶の応答速度を高速化させながら液晶のライジング特性を改善させることができる。

【0041】

図面上においては、タイミング制御部500が階調データの入力を受けて最終補正階調<sup>50</sup>

データを出力する機能を有することを図示したが、前記機能を別のスタンドアローン（*s t a n d - a l o n e*）ユニットに分離するか、外部のグラフィックカードやデータドライバ部などに前記機能が統合されるように具現することもできる。

#### 【0042】

以上、説明したように、本発明の一実施例によると、一つのフレームメモリーを使用して一部の領域には映像データを保存し、残りの領域には現在フレームの階調データと現在データの補償データとの差動データを保存することで、最終補償データを現在フレームの原始補償データと差動データとを基にして算出することで、液晶の応答速度を高速化することができる。

#### 【0043】

従って、階調データに対応するデータ電圧を補正して、補正されたデータの電圧を画素に印加することで、画素電圧がすぐ目標画素の電圧レベルに到達することができるようになる。従って、液晶表示パネルの構造を変更するか、液晶の物性を変更しなくても液晶の応答速度を改善させることができて動画像などを有用に表示することができる。

#### 【0044】

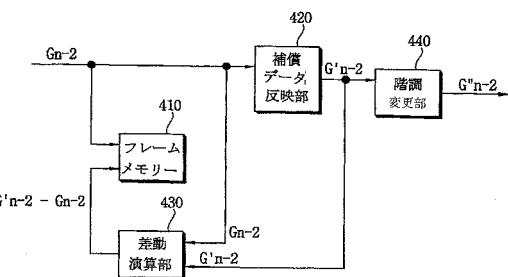

図6ないし図8は前記図5のタイミング制御部の動作を示すための図面である。説明の便宜のため、n-2番目のフレームを最初の階調データフレームと定義して説明する。

#### 【0045】

まず、図6に示すように、n-2番目のフレームの階調データ（G<sub>n-2</sub>）がフレームメモリー410及び補償データ反映部420に提供されることで、補償データ反映部420はn-2番目フレームの原始補償データ（G' n-2）を差動演算部430及び階調変更部440に提供する。

#### 【0046】

差動演算部430は、前記n-2番目フレームの原始補償データ（G' n-2）と前記n-2番目フレームの階調データ（G<sub>n-2</sub>）との間の差であるn-2番目フレームの差動データ（G' n-2 - G<sub>n-2</sub>）をフレームメモリー410に保存する。そして、階調変更部440は、前記n-2番目フレームの最終補償データ（G" n-2）をデータドライバ部300に提供する。前記n-2番目フレームの最終補償データ（G" n-2）は、補償されていない未補償データであり、前記n-2番目のフレームの階調データ（G<sub>n-2</sub>）と同じである。

#### 【0047】

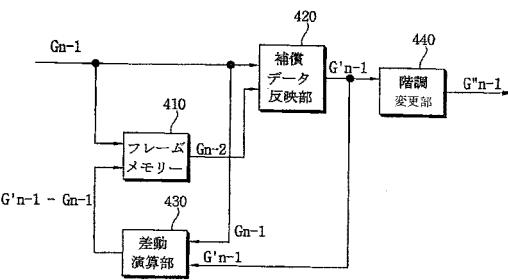

続いて、図7に示すように、n-1番目フレームの階調データ（G<sub>n-1</sub>）がフレームメモリー410及び補償データ反映部420に提供されることで、フレームメモリー410は保存された前記n-2番目フレームの階調データ（G<sub>n-2</sub>）を補償データ反映部420に提供する。そして、補償データ反映部420は、前記n-2番目フレームの階調データ（G<sub>n-2</sub>）と前記n-1番目フレームの階調データ（G<sub>n-1</sub>）を考慮してn-1番目フレームの原始補償データ（G' n-1）を生成した後、差動演算部430及び階調変更部440に提供する。

#### 【0048】

差動演算部430は、前記n-1番目フレームの原始補償データ（G' n-1）と前記n-1番目フレームの階調データ（G<sub>n-1</sub>）との間の差であるn-1番目フレームの差動データ（G' n-1 - G<sub>n-1</sub>）をフレームメモリー410に保存する。そして、階調変更部440はn-1番目フレームの最終補償データ（G" n-1）をデータドライバ部300に提供する。前記n-1番目フレームの最終補償データ（G" n-1）は、一般的なDCC方式によって補償された階調データであり、前記n-1番目フレームの原始補償データ（G' n-1）と同じである。

#### 【0049】

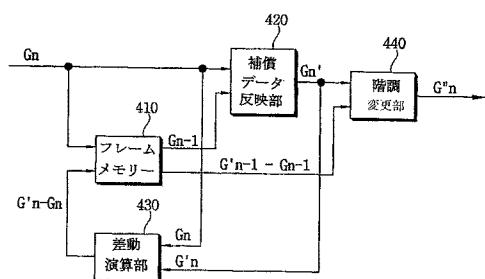

続いて図8に示すように、n番目フレームの階調データ（G<sub>n</sub>）がフレームメモリー410及び補償データ反映部420に提供されることで、フレームメモリー410は保存されたn-1番目フレームの階調データ（G<sub>n-1</sub>）を補償データ反映部420に提供する

10

20

30

40

50

。そして、補償データ反映部 420 は、前記 n - 1 番目フレームの階調データ (G<sub>n-1</sub>) と前記 n 番目フレームの階調データ (G<sub>n</sub>) を考慮して n 番目フレームの原始補償データ (G'<sub>n</sub>) を生成した後、差動演算部 430 及び階調変更部 440 に提供する。

#### 【0050】

差動演算部 430 は、前記 n 番目フレームの原始補償データ (G'<sub>n</sub>) と前記 n 番目フレームの階調データ (G<sub>n</sub>) との間の差である n 番目フレームの差動データ (G'<sub>n</sub> - G<sub>n</sub>) をフレームメモリー 410 に保存する。そして、フレームメモリー 410 は、階調変更部 440 に n - 1 番目フレームの差動データ (G'<sub>n-1</sub> - G<sub>n-1</sub>) を提供する。階調変更部 440 は、前記 n 番目フレームの原始補償データ (G'<sub>n</sub>) と n - 1 番目フレームの差動データ (G'<sub>n-1</sub> - G<sub>n-1</sub>) とを受信する。そして、階調変更部 440 は、前記 n 番目フレームの原始補償データ (G'<sub>n</sub>) と n - 1 番目フレームの差動データ (G'<sub>n-1</sub> - G<sub>n-1</sub>) とに基づいて n 番目フレームの最終補償データ (G"<sub>n</sub>) を発生する。階調変更部 440 は、n 番目フレームの最終補償データ (G"<sub>n</sub>) をデータドライバ部 300 に提供する。前記 n 番目フレームの最終補償データ (G"<sub>n</sub>) は、本発明による DCC 方式によって補償されたデータとして、一種の液晶のライジング特性を改善した階調データである。10

#### 【0051】

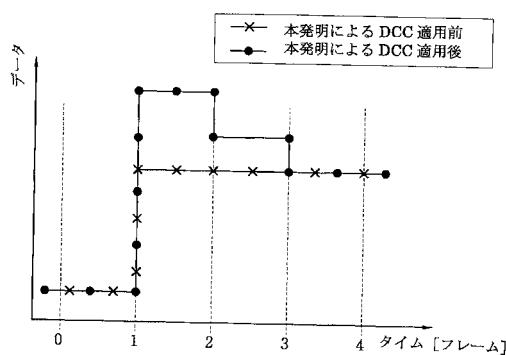

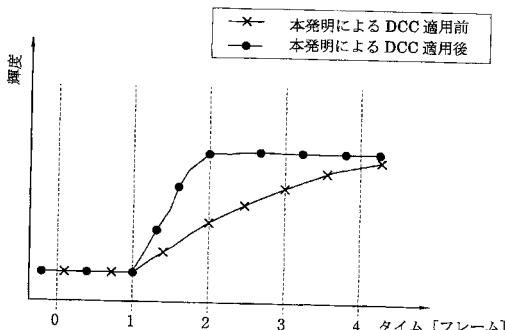

図 9 及び図 10 は、本発明による DCC 方式の適用前と適用後に対した応答特性を示すための図面である。特に、図 9 は本発明による DCC 方式の適用前のフレーム別データの特性を示すための図面であり、図 10 は本発明による DCC 方式の適用後のフレーム別輝度の応答特性を示すための図面である。20

#### 【0052】

図 9 に図示したように、第 1 フレームにおいて低階調のためのデータから高階調のためのデータに変化する時、液晶の応答速度を高速化するために、目標画素電圧値より高い電圧の画素電圧を提供して第 1 オーバーシュート波形を発生させる。次に、第 2 フレームにおいてもやはり液晶の応答速度を高速化するために、目標画素電圧より高い電圧の階調電圧を提供することで、前記第 1 オーバーシュート波形よりはレベルが低い第 2 オーバーシュート波形を発生させる。

#### 【0053】

このように、少なくとも 2 回以上にかけてデータ電圧の目標値より高い電圧を提供することで、実際の液晶の応答波形は図 10 に図示したように一つのフレームの中に完璧に反応する特性を示すようになる。これによって利用者の側から観察される画面の残像が発生されないので、表示品質の信頼性を確保することができる。30

#### 【0054】

本発明を適用した結果を図示すると、下記の図 11 及び図 12 のようである。

#### 【0055】

図 11 は、64 - 階調の中間階調において一般的な DCC 方式と本発明による DCC 方式による輝度の変化を示すためのグラフである。大略 16.5 ms を一つのフレームの時間に定型化させて図示する。

#### 【0056】

図 11 に図示したように、総 64 階調を表示する時、10 階調のような低階調から 60 階調のような高階調に変化する時、一般的な DCC 方式によると、目標画素電圧値まで液晶の応答特性が改善された後、すぐ応答特性曲線が下降することを確認することができる。40

#### 【0057】

しかし、本発明による DCC 方式によると、64 階調を表示する液晶表示装置においても目標画素電圧値まで液晶の応答特性が改善された後、改善された応答特性が保持されることを確認することができる。このような応答特性の保持は 2 回以上にかけてデータ電圧の目標値より高い電圧が印加されるためである。これによって低階調から高階調に画面変化後、利用者の側から観察される画面の残像を防止して表示品質に信頼性を付与すること50

ができる。

**【0058】**

図12は、128-階調の中間階調において一般的なDCC方式と本発明によるDCC方式による輝度変化を示すためのグラフである。大略16.5msを一つのフレームの時間に定型化させて図示する。

**【0059】**

図12に図示したように、総128階調を表示する時、10階調のような低階調から20階調のような高階調に変化する時、一般的なDCC方式によると、目標電圧値まで液晶の応答特性が改善された後、すぐ応答特性曲線が下降することを確認することができる。

10

**【0060】**

しかし、本発明によるDCC方式によると、128階調を表示する液晶表示装置においても目標画素電圧まで液晶の応答特性が改善された後、改善された応答特性が保持されることを確認することができる。このような応答特性の保持は2回以上にかけてデータ電圧の目標値より高い電圧が印加されるためである。これによって低階調から高階調に画面の変化後、利用者の側から観察される画面の残像を防止して表示品質に信頼性を付与することができる。

**【0061】**

以上では、一つのフレームメモリーに現在の階調データ( $G_n$ )と、現在の原始補償データ( $G_{n'}$ )と現在の階調データ( $G_n$ )との間の差動データ( $G_{n'} - G_n$ )の一部のビットを保存して液晶の応答速度を高速化することを説明した。より完璧な応答特性を得るために、図13のように前記差動データの全てを保存する。

20

**【0062】**

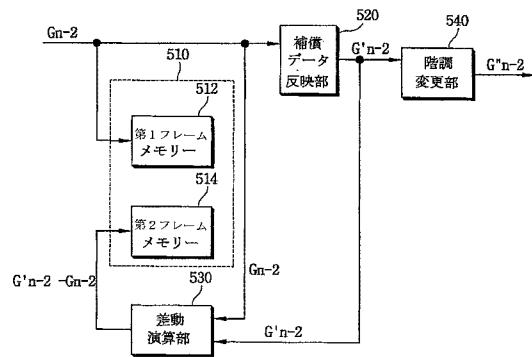

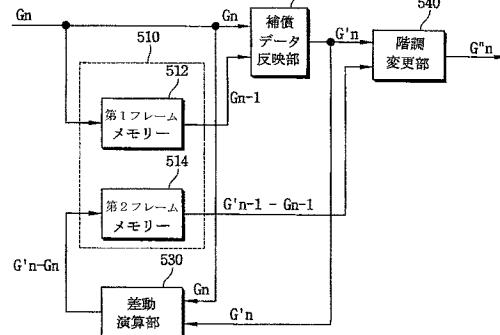

図13は、本発明の他の実施例による液晶表示装置を示すための図面である。

**【0063】**

図13に示すように、本発明の他の実施例による液晶表示装置は液晶パネル100、スキャンドライバ部200、データドライバ部300及びタイミング制御部500を含む。前記図5と比較する時、同じ図面符号を付与し、その説明は省略する。

**【0064】**

タイミング制御部500は図示しなかったが、外部から第1タイミング信号( $V_{sync}$ ,  $H_{sync}$ ,  $MCLK$ )が印加することで、第2タイミング信号( $Gate_Clk$ ,  $STV$ )をスキャンドライバ部200に出力して、第3タイミング信号( $LOAD$ ,  $STH$ )を前記データドライバ部300に出力する。

30

**【0065】**

タイミング制御部500は、第1フレームメモリー512、第2フレームメモリー514、補償データ反映部520、差動演算部530及び階調変更部540を含めて、現在階調データ( $G_n$ )が印加することで、現在階調データ( $G_n$ )と以前階調データ( $G_{n-1}$ )に対応する原始補償データ( $G'n$ )を生成する。

**【0066】**

タイミング制御部500は、現在階調データ( $G_n$ )と原始補償データ( $G'n$ )に対応する差動データ( $G'n - G_n$ )を生成する。そして、タイミング制御部500は、原始補償データ( $G'n$ )と、現在階調データ( $G_n$ )との差から差動データ( $G'n - G_n$ )を生成する。さらに、タイミング制御部500は、原始補償データ( $G'n$ )と、以前フレームの階調データ( $G_{n-1}$ )及び以前フレームの原始補償データ( $G_{n'-1}$ )間の差動データ( $G'n - G_{n-1}$ )とを考慮して生成した最終補償データ( $G''n$ )を前記データドライバ部300に出力する。即ち、以前フレームの階調データ( $G_{n-1}$ )と現在フレームの階調データ( $G_n$ )が同じ場合には補正しないが、以前フレームの階調データ( $G_{n-1}$ )が例えばブラック階調等の低階調に対応し、現在フレームの階調データ( $G_n$ )が以前フレームよりも明るい階調またはホワイト階調に対応する階調である場合、前記ブラック階調よりは高い階調が形成されるように最終補償データ( $G''n$ )

40

50

を出力する。即ち、現在フレームの階調データと以前フレームの階調データとの比較を通じて、オーバーシュート波形の形成のための最終補償データ( $G''_n$ )を出力する。

#### 【0067】

具体的に、第1フレームメモリー512は、外部から提供される一つのフレームに対応する階調データ( $G_n$ )を保存し、コントローラー(図示せず)の制御に応答して保存された以前フレームの階調データ( $G_{n-1}$ )を前記補償データ反映部520に提供する。前記第1フレームメモリー512は、一例として前記現在フレームの階調データ( $G_n$ )が入力されることで、既に保存された以前フレームの階調データ( $G_{n-1}$ )を出力し、前記現在フレームの階調データ( $G_n$ )を保存するSDRAMである。

#### 【0068】

第2フレームメモリー514は前記差動演算部530から提供される差動データ( $G'_n - G_n$ )を保存し、前記コントローラーの制御に応答して保存された差動データ( $G'_n - 1 - G_{n-1}$ )を前記階調変更部540に提供する。ここで、差動データ( $G'_n - G_n$ )は、現在フレームの階調データ $G_n$ 及び現在フレームの原始補償データ $G_n'$ 間の差動データであり、動データ( $G'_n - 1 - G_{n-1}$ )は、以前フレームの階調データ( $G_{n-1}$ )及び以前フレームの原始補償データ( $G_{n-1}'$ )間の差動データである。

#### 【0069】

前記第2フレームメモリー514は、現在フレームの差動データ( $G'_n - G_n$ )が入力されることで、既に保存された以前フレームの差動データ( $G'_n - 1 - G_{n-1}$ )を出力し、前記現在フレームの差動データ( $G'_n - G_n$ )を保存するSDRAMである。

#### 【0070】

補償データ反映部520は現在フレームの階調データ $G_n$ と前記第1フレームメモリー512に保存された以前フレームの階調データ $G_{n-1}$ とを考慮して現在フレームの原始補償データ( $G'_n$ )を抽出し、抽出された原始補償データ( $G'_n$ )を前記差動演算部530及び階調変更部540に出力する。

#### 【0071】

差動演算部530は、現在フレームの原始補償データ( $G'_n$ )と現在フレームの階調データ( $G_n$ )との比較を通じて現在フレームの差動データ( $G'_n - G_n$ )を生成し、生成された差動データ( $G'_n - G_n$ )を第2フレームメモリー514に保存する。

#### 【0072】

階調変更部540は、前記原始補償データ( $G'_n$ )と、以前フレームの階調データ( $G_{n-1}$ )及び以前フレームの原始補償データ( $G_{n-1}'$ )間の前記差動データ( $G'_n - 1 - G_{n-1}$ )とを考慮して最終補償データ( $G''_n$ )を生成し、生成された最終補償データ( $G''_n$ )を前記データドライバ部300に出力する。

#### 【0073】

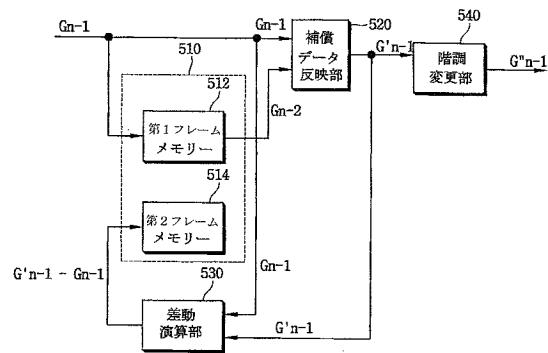

図14ないし図16は前記図13のタイミング制御部の動作を示すための図面である。説明の便宜のために、 $n-2$ 番目フレームを最初の階調データフレームに定義して説明する。

#### 【0074】

まず、図14に示すように、 $n-2$ 番目フレームの階調データ( $G_{n-2}$ )が第1フレームメモリー512及び補償データ反映部520に提供されることで、補償データ反映部520は前記 $n-2$ 番目フレームの原始補償データ( $G'_{n-2}$ )を差動演算部530及び階調変更部540に提供する。

#### 【0075】

差動演算部530は、前記 $n-2$ 番目フレームの原始補償データ( $G'_{n-2}$ )と前記 $n-2$ 番目フレームの階調データ( $G_{n-2}$ )との間の差である $n-2$ 番目フレームの差動データ( $G'_{n-2} - G_{n-2}$ )を第2フレームメモリー514に保存する。そして、階調変更部540は、 $n-2$ 番目フレームの最終補償データ( $G''_{n-2}$ )をデータドライバ部300に提供する。前記 $n-2$ 番目フレームの最終補償データ( $G''_{n-2}$ )は、補償されていない未補償データであり、前記 $n-2$ 番目フレームの階調データ( $G_{n-2}$ )

10

20

30

40

50

)と同じである。

**【0076】**

続いて、図15に示すように、n-1番目フレームの階調データ( $G_{n-1}$ )が第1フレームメモリー512及び補償データ反映部520に提供されることで、第1フレームメモリー512は保存されたn-2番目フレームの階調データ( $G_{n-2}$ )を補償データ反映部520に提供する。そして、補償データ反映部520は、前記n-2番目フレームの階調データ( $G_{n-2}$ )と前記n-1番目フレームの階調データ( $G_{n-1}$ )とを考慮して前記n-1番目フレームの原始補償データ( $G'_{n-1}$ )を生成した後、差動演算部530及び階調変更部540に提供する。

**【0077】**

差動演算部530は前記n-1番目フレームの原始補償データ( $G'_{n-1}$ )と前記n-1番目フレームの階調データ( $G_{n-1}$ )との間の差であるn-1番目フレームの差動データ( $G'_{n-1} - G_{n-1}$ )を第2フレームメモリー514に保存する。そして、階調変更部540は、n-1番目フレームの最終補償データ( $G''_{n-1}$ )をデータドライバ部300に提供する。前記n-1番目フレームの最終補償データ( $G''_{n-1}$ )は一般的なDDC方式によって補償された階調データであり、前記n-1番目フレームの原始補償データ( $G'_{n-1}$ )と同じである。

**【0078】**

続いて、図16に示すように、n番目フレームの階調データ( $G_n$ )が第1フレームメモリー512及び補償データ反映部520に提供されることで、第1フレームメモリー512は保存された前記n-1番目フレームの階調データ( $G_{n-1}$ )を補償データ反映部520に提供する。そして、補償データ反映部520は、前記n-1番目フレームの階調データ( $G_{n-1}$ )と前記n番目フレームの階調データ( $G_n$ )とを考慮して、n番目フレームの原始補償データ( $G'_{n}$ )を生成した後、差動演算部530及び階調変更部540に提供する。

**【0079】**

差動演算部530は、前記n番目フレームの原始補償データ( $G'_{n}$ )と前記n番目フレームの階調データ( $G_n$ )との間の差であるn番目フレームの差動データ( $G'_{n} - G_n$ )を第2フレームメモリー514に保存する。そして、第2フレームメモリー514は、階調変更部540にn-1番目フレームの差動データ( $G'_{n-1} - G_{n-1}$ )を提供する。階調変更部540は、前記n番目フレームの原始補償データ( $G'_{n}$ )とn-1番目フレームの差動データ( $G'_{n-1} - G_{n-1}$ )とを受信する。そして、階調変更部540は、前記n番目フレームの原始補償データ( $G'_{n}$ )とn-1番目フレームの差動データ( $G'_{n-1} - G_{n-1}$ )とに基づいてn番目フレームの最終補償データ( $G''_{n}$ )を発生する。階調変更部540はn番目フレームの最終補償データ( $G''_{n}$ )をデータドライバ部300に提供する。前記n番目フレームの最終補償データ( $G''_{n}$ )は本発明によるDCC方式によって補償されたデータとして、一種の液晶のライジング特性を改善した階調データである。

**【0080】**

以上、説明した本発明の他の実施例によると、フレームメモリーに保存しなければならないデータは増加する。即ち、現在の階調データ( $G_n$ )と、現在の原始補償データ( $G'_{n}$ )と現在の階調データ( $G_n$ )との間の差動データ( $G'_{n} - G_n$ )を二つのメモリーに保存する方法である。このようにすると、メモリー増加による材料費の増加が発生するが、完璧な応答特性を得ることができる。つまり、2つのフレームメモリーに保存された、現在の階調データ( $G_n$ )及び差動データ( $G'_{n} - G_n$ )に関するより多いデータを用いて、さらに微細に階調データを補償することができる。

**【0081】**

以上、本発明の実施例によって詳細に説明したが、本発明はこれに限定されず、本発明が属する技術分野において通常の知識を有するものであれば本発明の思想と精神を離れることなく、本発明を修正または変更できる。

10

20

30

40

50

## 【産業上の利用可能性】

## 【0082】

以上、説明したように、本発明によると、一つのフレームメモリーを使用して一部の領域には映像データを保存し、余りの領域には現在フレームの階調データと現在フレームの補償データとの差動データを保存することで、最終補償データを現在フレームの原始補償データと差動データとを基にして算出することで、液晶の応答速度を高速化することができ、表示品質を向上することができる。

## 【0083】

また、二つのフレームメモリーを使用して一つのフレームには以前フレームの階調データを保存し、他のフレームメモリーには現在フレームの階調データと現在フレームの補償データとの差動データを保存し、最終補償データを現在フレームの原始補償データと差動データとを基にして算出することで、液晶の応答速度を高速化することができ、表示品質を向上することができる。10

## 【0084】

また、PVAモードのように垂直配向モードを採用する液晶表示装置の応答特性を高速化するために、以前フレームの階調データと現在フレームの階調データとの差動データを算出し、以前フレームの階調データと以前フレームの補償データとの差を基にして現在フレームの最終補償データを発生させることで、液晶の応答速度を高速化させることができる。特に、低階調から高階調に変化する時、液晶のライジング速度を高速化することができ、表示品質を向上させることができる。20

## 【図面の簡単な説明】

## 【0085】

【図1】一般的な液晶の応答速度の高速化方式を示すための図面である。

【図2】PVAモードの液晶表示装置に応答速度の高速化するためのDCC適用前と適用後の応答特性を示したグラフである。

【図3】一般的なDCC方式の適用前と適用後によるデータ及び液晶の応答特性を示すための図面である。

【図4】一般的なDCC方式の適用前と適用後によるデータ及び液晶の応答特性を示すための図面である。

【図5】本発明の一実施例による液晶表示装置を示すための図面である。30

【図6】前記図5のタイミング制御部の動作を示すための図面である。

【図7】前記図5のタイミング制御部の動作を示すための図面である。

【図8】前記図5のタイミング制御部の動作を示すための図面である。

【図9】本発明によるDCC方式の適用前と適用後に対する応答特性を示すための図面である。

【図10】本発明によるDCC方式の適用前と適用後に対する応答特性を示すための図面である。

【図11】64-階調の中間階調において一般的なDCC方式と本発明によるDCC方式による輝度変化を示すためのグラフである。

【図12】128-階調の中間階調において一般的なDCC方式と本発明によるDCC方式による輝度変化を示すためのグラフである。40

【図13】本発明の他の実施例による液晶表示装置を示すための図面である。

【図14】前記図13のタイミング制御部の動作を示すための図面である。

【図15】前記図13のタイミング制御部の動作を示すための図面である。

【図16】前記図13のタイミング制御部の動作を示すための図面である。

## 【符号の説明】

## 【0086】

10、410 フレームメモリー

20 コントローラー

30 補償データ反映部

10

20

30

40

50

1 0 0 液晶パネル

1 1 0 薄膜トランジスタ

2 0 0 スキャンドライバ部

3 0 0 データドライバ部

4 0 0 タイミング制御部

4 2 0 、 5 2 0 補償データ反映部

4 3 0 、 5 3 0 差動演算部

4 4 0 、 5 4 0 階調変更部

5 1 2 第1フレームメモリー

5 1 4 第2フレームメモリー

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図15】

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 1 F |

| G 0 9 G | 3/20 | 6 2 1 M |

| G 0 9 G | 3/20 | 6 3 1 B |

| G 0 9 G | 3/20 | 6 3 1 V |

| G 0 9 G | 3/20 | 6 4 1 P |

| H 0 4 N | 5/66 | 1 0 2 B |

F ターム(参考) 5C006 AA01 AA16 AC11 AC21 AF03 AF04 AF44 AF45 AF46 AF50

AF52 AF71 BA19 BB16 BC02 BC12 BC16 BC20 BF02 FA14

5C058 AA06 BA01 BA23 BA31 BA35 BB13

5C080 AA10 BB05 DD08 EE29 FF11 GG08 GG15 GG17 JJ02 JJ05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其驱动方法及其装置{LIQUID CRYSTALDISPLAY , ANDMETHODANDAPPARATUSFORDRIVINGTHEROF}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP2005049840A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2005-02-24 |

| 申请号            | JP2004194344                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2004-06-30 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| [标]发明人         | 李昇祐                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 李昇祐                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36 H04N5/66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| CPC分类号         | G09G3/3648 G09G3/2092 G09G2320/0252 G09G2320/0285 G09G2340/16 G09G2360/18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G02F1/133.570 G02F1/133.575 G09G3/20.612.U G09G3/20.621.F G09G3 /20.621.M G09G3/20.631.B G09G3/20.631.V G09G3/20.641.P H04N5/66.102.B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA53 2H093/NC10 2H093/NC12 2H093/NC21 2H093/NC29 2H093/NC34 2H093 /NC35 2H093/NC49 2H093/NC65 2H093/ND06 2H093/ND33 2H093/ND58 2H093/NF04 2H093/NH15 5C006/AA01 5C006/AA16 5C006/AC11 5C006/AC21 5C006/AF03 5C006/AF04 5C006/AF44 5C006 /AF45 5C006/AF46 5C006/AF50 5C006/AF52 5C006/AF71 5C006/BA19 5C006/BB16 5C006/BC02 5C006/BC12 5C006/BC16 5C006/BC20 5C006/BF02 5C006/FA14 5C058/AA06 5C058/BA01 5C058 /BA23 5C058/BA31 5C058/BA35 5C058/BB13 5C080/AA10 5C080/BB05 5C080/DD08 5C080/EE29 5C080/FF11 5C080/GG08 5C080/GG15 5C080/GG17 5C080/JJ02 5C080/JJ05 2H193/ZA04 2H193 /ZD23 2H193/ZE01 2H193/ZF22 2H193/ZF36 2H193/ZH40 |         |            |

| 优先权            | 1020030045449 2003-07-04 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 其他公开文献         | <a href="#">JP4638182B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

### 摘要(译)

解决的问题：提供一种用于提高液晶的响应速度的液晶显示装置，其驱动方法和驱动装置。时序控制单元在考虑了当前数据和先前数据的原始补偿数据以及当前数据和原始补偿数据之间的差分数据的情况下输出最终补偿数据。扫描驱动器单元顺序输出扫描信号，并且数据驱动器单元基于最终补偿数据输出数据信号。包括垂直取向模式液晶面板的液晶面板包括：传输扫描信号的扫描线，传输数据信号的数据线以及在扫描线和数据线之间形成的开关元件。响应于此，基于数据信号布置液晶以显示图像。结果，可以通过改善使用垂直取向模式的液晶的液晶显示装置的上升时间来增加液晶的响应时间。[选择图]图5