(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-296741

(P2004-296741A)

(43) 公開日 平成16年10月21日(2004.10.21)

|                           |                                |                 |

|---------------------------|--------------------------------|-----------------|

| (51) Int.Cl. <sup>7</sup> | F 1                            | テーマコード (参考)     |

| H 01 L 27/08              | H 01 L 27/08                   | 3 3 1 E 2 H 092 |

| G 02 F 1/1368             | G 02 F 1/1368                  | 5 C 006         |

| H 01 L 29/786             | H 01 L 29/78                   | 5 C 080         |

| // G 09 G 3/20            | G 09 G 3/20                    | 5 F 048         |

| G 09 G 3/36               | G 09 G 3/20                    | 5 F 11 O        |

|                           | 審査請求 未請求 請求項の数 14 O L (全 12 頁) | 最終頁に続く          |

|           |                            |            |                                                                                                                                                                                                                                               |

|-----------|----------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2003-86371 (P2003-86371) | (71) 出願人   | 000153878                                                                                                                                                                                                                                     |

| (22) 出願日  | 平成15年3月26日 (2003. 3. 26)   |            | 株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地                                                                                                                                                                                                             |

|           |                            | (72) 発明者   | 小山 潤<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                                                                                                                                                                                   |

|           |                            | F ターム (参考) | 2H092 GA59 JA24 NA01 NA05 PA06<br>5C006 BB16 BC02 BC03 BC06 BC08<br>BC11 BC20 BF03 BF11 BF34<br>FA46 FA47<br>5C080 AA10 BB05 DD22 DD26 EE29<br>FF01 FF11 JJ02 JJ03 JJ04<br>KK01 KK07 KK43 KK47<br>5F048 AB03 AB07 AC02 AC04 BA16<br>BB14 BC16 |

|           |                            |            | 最終頁に続く                                                                                                                                                                                                                                        |

(54) 【発明の名称】ソースフォロワ回路又はブートストラップ回路、当該回路を有する駆動回路、及び当該駆動回路を有する液晶表示装置

## (57) 【要約】

【課題】アナログバッファ回路では、入力電圧に多結晶シリコンTFTのゲート・ソース間電圧分を上乗せする問題があった。その結果、電源電圧が大きくなり、発熱するとともに、消費電力が高くなってしまった。

【解決手段】上記課題を鑑み本発明は、ソースフォロワ回路等のアナログバッファ回路に用いられる多結晶シリコンTFTを、デプレッション型とする特徴とする。デプレッション型の多結晶シリコンTFTは、しきい値電圧が負電圧側にあるため、上述したような入力電圧を増大させずにすむ。その結果、電源電圧を上げる必要がなくなり、特に液晶表示装置の低消費電力を達成することができる。

【選択図】 図1

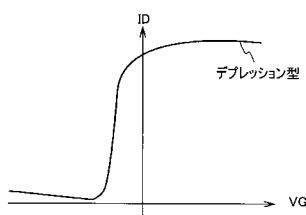

(B) 本発明のNチャネル型TFTのVG-ID特性

**【特許請求の範囲】****【請求項 1】**

チャネル形成領域に多結晶半導体膜を有する薄膜トランジスタを備え、前記薄膜トランジスタはデプレッション型の特性を有することを特徴とするソースフォロワ回路。

**【請求項 2】**

チャネル形成領域に非晶質シリコン膜を結晶化した多結晶半導体膜を有する薄膜トランジスタを備え、

前記薄膜トランジスタはデプレッション型の特性を有することを特徴とするソースフォロワ回路。 10

**【請求項 3】**

請求項 1 又は 2 において、前記薄膜トランジスタは出力端子に直接接続されていることを特徴とするソースフォロワ回路。

**【請求項 4】**

請求項 1 乃至 3 のいずれか一において、前記多結晶半導体膜は石英基板又はガラス基板上に設けられることを特徴とするソースフォロワ回路。

**【請求項 5】**

チャネル形成領域に多結晶半導体膜を有する薄膜トランジスタを備え、前記薄膜トランジスタはデプレッション型の特性を有することを特徴とするブートストラップ回路。 20

**【請求項 6】**

チャネル形成領域に非晶質シリコン膜を結晶化した多結晶半導体膜を有する薄膜トランジスタを備え、

前記薄膜トランジスタはデプレッション型の特性を有することを特徴とするブートストラップ回路。 20

**【請求項 7】**

請求項 5 又は 6 において、前記薄膜トランジスタは出力端子に直接接続されていることを特徴とするブートストラップ回路。

**【請求項 8】**

請求項 5 乃至 7 のいずれか一において、前記多結晶半導体膜は石英基板又はガラス基板上に設けられることを特徴とするブートストラップ回路。 30

**【請求項 9】**

チャネル形成領域に多結晶半導体膜を有する薄膜トランジスタを備えたソースフォロワ回路と、シフトレジスタと、バッファ回路と、アナログメモリと、を有する駆動回路において、

前記薄膜トランジスタはデプレッション型の特性を有することを特徴とする駆動回路。

**【請求項 10】**

チャネル形成領域に非晶質シリコン膜を結晶化した多結晶半導体膜を有する薄膜トランジスタを備えたソースフォロワ回路と、シフトレジスタと、バッファ回路と、アナログメモリと、を有する駆動回路において、

前記薄膜トランジスタはデプレッション型の特性を有することを特徴とする駆動回路。 40

**【請求項 11】**

チャネル形成領域に多結晶半導体膜を有する薄膜トランジスタを備えたブートストラップ回路と、シフトレジスタと、バッファと、を有する駆動回路において、前記薄膜トランジスタはデプレッション型の特性を有することを特徴とする駆動回路。

**【請求項 12】**

チャネル形成領域に非晶質シリコン膜を結晶化した多結晶半導体膜を有する薄膜トランジスタを備えたブートストラップ回路と、シフトレジスタと、バッファと、を有する駆動回路において、

前記薄膜トランジスタはデプレッション型の特性を有することを特徴とする駆動回路。 50

**【請求項 1 3】**

絶縁表面上に設けられた信号線と、走査線と、前記信号線と走査線との交差部に設けられた画素と、前記信号線を駆動する信号線駆動回路と、を有する液晶表示装置において、前記信号線駆動回路は、シフトレジスタと、バッファ回路と、アナログメモリと、ソースフォロワ回路を有し、

前記ソースフォロワ回路は、チャネル形成領域に多結晶半導体膜を有するデプレッション型の薄膜トランジスタを備えたことを特徴とする液晶表示装置。

**【請求項 1 4】**

絶縁表面上に設けられた信号線と、走査線と、前記信号線と走査線との交差部に設けられた画素と、前記走査線を駆動する走査線駆動回路と、を有する液晶表示装置において、前記走査線駆動回路は、シフトレジスタと、バッファと、ブートストラップ回路を有し、前記ブートストラップ回路は、チャネル形成領域に多結晶半導体膜を有するデプレッション型の薄膜トランジスタを備えたことを特徴とする液晶表示装置。 10

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、多結晶薄膜トランジスタを用いたソースフォロワ回路等のアナログバッファ回路に関する。また本発明のソースフォロワ回路を有する信号線駆動回路、更にアクティブマトリクス型の液晶表示装置に関する。

**【0002】****【従来の技術】**

近年、絶縁基板上に形成される薄膜トランジスタ（以下、TFTと表記する）を用いた半導体装置に関する技術が急速に発達してきている。さらに加熱やレーザ照射により、非晶質半導体膜を多結晶半導体膜とする多結晶半導体膜を有する半導体装置においては、画素部と、駆動回路部とを一体形成することができ、半導体装置の小型化、狭額縫化（表示部における画素部の割合を高めること）が目標とされている。 20

**【0003】**

一方、15インチから30インチといった大型の半導体装置、特に液晶表示装置への要求や期待が高まっている。このような大型の液晶表示装置は、CRT表示装置と比べて、非常に薄く、軽量であり、デザイン性に富んでいる。 30

**【0004】**

このような大型の液晶表示装置は、信号線や走査線が長くなるにつれ、配線抵抗が増大し、負荷が大きくなってしまい、信号遅延を引き起こす問題があった。そのため大型の液晶表示装置では、信号線駆動回路内のメモリで一旦信号を保持したのち、信号線に書き込みを行う線順次駆動が行われている。この場合、メモリの後にアナログバッファ回路を配置する必要がある。

**【0005】**

このアナログバッファ回路に薄膜トランジスタを用いることができるが、薄膜トランジスタは特性がばらついてしまった。そこで、薄膜トランジスタのばらつきを補正する方法が考えられている。例えば、コンデンサに、入力電圧とトランジスタのしきい値電圧の差の電圧と電源の電圧との差を記憶させ、出力時に当該トランジスタを利用して、しきい値をキャンセルする入力電圧をホールドする方法がある（特許文献1参照）。 40

**【0006】**

またポリシリコンTFTで構成されたソースフォロワ回路において、ソースフォロワトランジスタのゲートにキャパシタの一端を接続し、ソースフォロワトランジスタのゲートとプリチャージ電源の間に第1のアナログスイッチを、キャパシタの他端とソースフォロワトランジスタのソースの間に第2のアナログスイッチを、キャパシタの他端と信号源の間に第3のアナログスイッチを接続し、プリチャージ動作を行わせ、オフセットキャンセルを高精度に行う方法がある。このときソースフォロワトランジスタにNMOStランジスタをカスコード接続し、ソースフォロワトランジスタのゲート-ドレイン電圧V<sub>gd</sub>を、 50

プリチャージ期間及び出力期間において、ほぼ一定に保つようにし、このカスコード接続するN M O Sトランジスタをデプレッション型のトランジスタとすることが記載されている（特許文献2参照）。

#### 【0007】

##### 【特許文献1】

特開2000-194323号公報

##### 【特許文献2】

特開平11-73165号公報

#### 【0008】

##### 【発明が解決しようとする課題】

しかしアナログバッファ回路では、T F Tのしきい値電圧のバラツキとは別に、新たな問題があった。それはアナログバッファ回路の入力電圧に多結晶シリコンT F Tのゲート・ソース間電圧分を上乗せする必要が生ずる点である。具体的には、Nチャネル型の多結晶シリコンT F Tを使用した場合、入力電位に対して、出力電位がT F Tのゲート・ソース間電圧( $V_{G_S}$ )分、低下するため、入力電圧をその電圧分大きくする必要があった。その結果、電源電圧が大きくなり、発熱するとともに、消費電力が高くなってしまった。

#### 【0009】

上記現象が生じる理由を説明する。ゲート・ソース間電圧( $V_{G_S}$ )とは、ドレイン電流(I D)が流れ始めるときのゲート電圧であるしきい値電圧( $V_{t_h}$ )と、ドレイン電流が飽和に達する電圧との合計である。そのため、しきい値電圧の値によりゲート・ソース間電圧( $V_{G_S}$ )が決まる。

#### 【0010】

そして一般的に、M O Sトランジスタのしきい値電圧の絶対値は約0.3~0.7Vであり、エンハンスマント型（ノーマリーオフ）のNチャネル型M O Sトランジスタのゲート・ソース間電圧( $V_{G_S}$ )は約0.5~1である。それに対して、多結晶シリコンT F Tのしきい値電圧は、約1.5~2V程度であり、エンハンスマント型のNチャネル型T F Tのゲート・ソース間電圧( $V_{G_S}$ )は3V以上となってしまった。

#### 【0011】

これは、チャネル形成領域が多結晶シリコン膜から形成される多結晶シリコンT F Tは、結晶化や不純物添加等のプロセス、ゲート絶縁膜と半導体膜との界面汚染等により、しきい値電圧は大きく、さらにはらついてしまうためである。

#### 【0012】

すなわち、M O Sトランジスタと異なり、多結晶シリコンT F Tを用いてアナログバッファ回路を形成する場合、多結晶シリコンT F Tのゲート・ソース間電圧( $V_{G_S}$ )が大きくなり、電源電圧の増加は大きな問題となった。

#### 【0013】

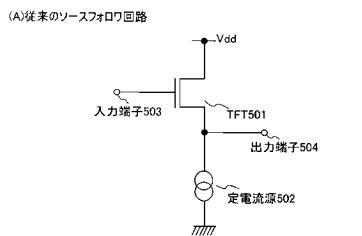

アナログバッファ回路の一例として、定電流源とT F Tとを有するソースフォロワ回路について具体的に説明する。

#### 【0014】

図5(A)には、ソースフォロワ回路の構成を示す。ソースフォロワ回路は、多結晶シリコンT F T501と定電流源502によって構成される。なおT F T501は、Nチャネル型であっても、Pチャネル型であっても構わない。そして、入力端子503からの電位(以下、入力電位： $V_{in}$ と表記する)により、T F T501がオン又はオフし、出力端子504から電圧(以下、出力電圧： $V_{out}$ と表記する)が出力される。

#### 【0015】

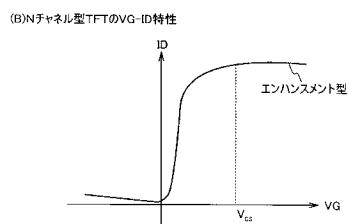

図5(B)には、Nチャネル型の多結晶シリコンT F Tの $V_G - I D$ 特性を示す。T F Tの $V_G - I D$ 特性は、 $V_G = 0$ のとき、 $I D = 0$ となるように設定されている。このようにゲートに大きな電圧を印加した場合に大きなドレイン電流(I D)が流れ、ゲート電圧が0Vではドレイン電流が流れなうような多結晶シリコンT F Tをエンハンスマント型T F Tという。エンハンスマント型T F Tは、ゲート電圧を印加してT F Tの導通を制御し

10

20

30

40

50

ている。

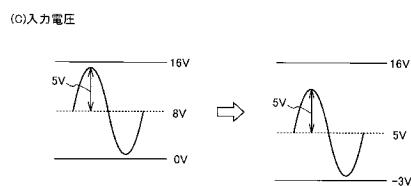

【0016】

図5(A)に示すソースフォロワ回路のTFT501にはエンハンスマント型TFTを用いており、例えば図5(C)左図に示すような振幅5Vの入力電圧を入力する。すると、TFTのゲート・ソース間電圧( $V_{GS}$ )が所定の値、例えば3V(しきい値+数V)となるため、入力電圧より3V下がった出力電圧となってしまう。そのため、定電流源502の電位を-3Vとし、(C)右図に示すように3V分増加させた合計19Vの電源とする必要があった。その結果、表示装置等の電源電圧が増加し、消費電力が高くなってしまった。

【0017】

以上は、Nチャネル型の多結晶シリコンTFTの説明であるが、Pチャネル型の多結晶シリコンTFTについては極性を変えることによって同様に説明できる。

【0018】

そして上述したように、大型の液晶表示装置では線順次駆動を行う必要があるため、アナログバッファ回路を形成する必要があった。特に、多結晶シリコンTFTを用いることにより、画素部と、駆動回路部、すなわちアナログバッファ回路を一体形成された液晶表示装置では、低消費電力が利点であるため、上述のような電源電圧の増大は顕著な問題となっていた。

【0019】

そこで本発明は、多結晶シリコンTFTを用いたソースフォロワ回路等のアナログバッファ回路において、入力電圧を増大することなく動作させることを課題とする。また、本発明のアナログバッファ回路を有する信号線駆動回路、更には液晶表示装置を提供することを課題とする。

【0020】

【課題を解決するための手段】

上記課題を鑑み本発明は、ソースフォロワ回路等のアナログバッファ回路に用いられる多結晶シリコンTFTを、デプレッション型(ノーマリーオン)とすることを特徴とする。

【0021】

デプレッション型の多結晶シリコンTFT(以下、デプレッション型TFTと表記する)は、しきい値電圧が負電圧側にある。そのためデプレッション型TFTのゲート・ソース間電圧( $V_{GS}$ )は、0~1V程度となり、上述したような入力電圧を増大させずにすむ。その結果、電源電圧を上げる必要がなくなり、特に液晶表示装置の低消費電力を達成することができる。

【0022】

また多結晶シリコンTFTを用いることにより、アナログバッファ回路、すなわち信号線駆動回路等の駆動回路と、画素部とを一体形成したモノリシック型の液晶表示装置を提供することができる。もちろん本発明のアナログバッファ回路を有する駆動回路と、画素部とを別途形成しても構わない。

【0023】

またさらに多結晶シリコンTFTは、チャネル形成領域として、CVD法等により絶縁表面(例えば、石英基板等)上に形成された多結晶シリコン膜や、絶縁表面(例えば、ガラス基板等)上に形成された非晶質シリコン膜を形成した後加熱やレーザにより結晶化した多結晶シリコン膜を有すればよい。

【0024】

加熱により結晶化を行う場合、ニッケル等の半導体膜の結晶化を促進させる金属元素を添加した後、450~580度4~12時間程度加熱すればよい。またレーザにより結晶化を行う場合、連続発振又はパルス発振のレーザを照射すればよく、エキシマレーザやYAGレーザを用いることができる。

【0025】

なおシリコン膜とは、シリコン(珪素)を主成分とする半導体膜であり、ゲルマニウム等

を有していてもよい。すなわちチャネル形成領域が多結晶半導体膜により形成される TFT をデプレッション型 TFT とする。

【0026】

また、デプレッション型 TFT を形成する場合、TFT の活性層、少なくともチャネル形成領域へ不純物を  $5 \times 10^{12} \sim 5 \times 10^{14}$  atoms/cm<sup>2</sup> で添加すればよい。なお不純物として、N チャネル型のデプレッション型 TFT ではリン (P)、P チャネル型のデプレッション型 TFT ではボロン (B) を用いればよい。

【0027】

以上のような本発明により、多結晶シリコン TFT を用いた駆動回路（電気回路）において、電源電圧を所望の値より上昇させずに動作させることができる。その結果、当該駆動回路を有する液晶表示装置、発光装置等の表示装置、CPU やメモリ等の半導体集積回路において、電源電圧を低く保持することができ、低消費電力を達成することができる。10

【0028】

【発明の実施の形態】

以下に、本発明の実施の形態を図面に基づいて説明する。

【0029】

(実施の形態 1)

本実施の形態では、デプレッション型 TFT を用いたソースフォロワ回路について説明する。20

【0030】

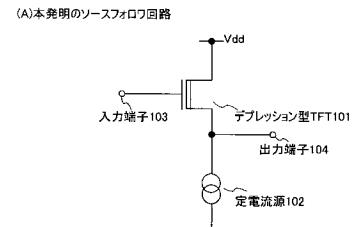

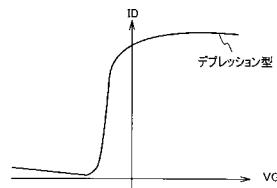

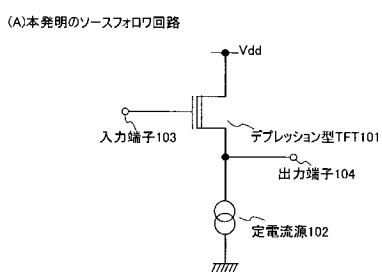

図 1 (A) には、本発明のデプレッション型 TFT 101 と、定電流源 102、入力端子 103、出力端子 104 を有するソースフォロワ回路を示す。またデプレッション型 TFT は電源線 Vdd に接続されている。なお本発明の図面において、デプレッション型 TFT は 101 に示すような記号を用いて記載する。20

【0031】

また、図 1 (B) にはデプレッション型 TFT の VG - ID 特性を示す。図 5 (B) と比べると、デプレッション型 TFT のゲート・ソース間電圧 ( $V_{GS}$ ) が非常に小さい。つまりデプレッション型 TFT のゲート・ソース間電圧 ( $V_{GS}$ ) ほぼ 0 ~ 1 V 程度となり、上述したような入力電圧を増分する必要がないことがわかる。30

【0032】

さらに定電流源 102 は公知のものを使用すればよく、特に多結晶シリコン TFT を用いる場合、デプレッション型にするといい。

【0033】

また本発明のソースフォロワ回路は、基本回路構成であり、その他の回路が接続されても構わない。

【0034】

このように本発明は、デプレッション型 TFT を用いることで、入力電圧を追加する必要がなく、低消費電力を達成することができる。

【0035】

以上のような、ソースフォロワ回路は、オペアンプ回路等の他のアナログバッファ回路と比べて構成や作製工程が複雑でないため、駆動回路等の集積回路に適する。特に、多結晶シリコン TFT を有する駆動回路部及び画素部を一体形成した液晶表示装置の信号線駆動回路に適する。40

【0036】

なお、カスコード接続される NMOS トランジスタにデプレッション型トランジスタを用いている特許文献 2 に記載の発明と、本発明は構成、課題及び効果が異なっている。すなわち、本発明は、ソースフォロワの入力電圧に多結晶シリコン TFT のゲート・ソース間電圧を追加する必要性を鑑み、ソースフォロワの出力端子に直接接続されるトランジスタ（特許文献 2 のソースフォロワトランジスタに相当）をデプレッション型の多結晶シリコン TFT で形成することを特徴としている。その結果、ソースフォロワの入力電圧に多結50

晶シリコンTFTのゲート・ソース間電圧を追加せずにすむという効果を奏する。

【0037】

(実施の形態2)

本実施の形態では、デプレッション型TFTを用いたブートストラップ回路について説明する。

【0038】

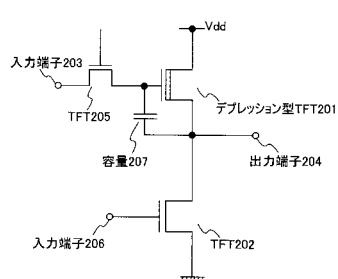

図2に示すブートストラップ回路は、Nチャネル型のデプレッション型TFT201、TFT205、Nチャネル型のエンハンスマント型TFT202、入力端子203、出力端子204、入力端子206、容量207を有し、デプレッション型TFTは電源線Vddに接続されている。

【0039】

ブートストラップ回路では、電源線に接続されるTFTのゲート電圧を電源Vdd以上に上げて動作しているが、実際には寄生容量等により、十分電源を上げることが難しかった。しかし本発明のデプレッション型TFT201では、電源Vddを越えるゲート電圧がエンハンスマント型TFTより少なくてすむ。

これは上述したように、多結晶シリコンTFTのゲート・ソース間電圧( $V_{GS}$ )が数V程度であるが、デプレッション型TFTの特性では、しきい値電圧が負であり、ゲート・ソース間電圧( $V_{GS}$ )がほぼ0Vとなるためである。その結果、所定の電源Vddの範囲で十分にデプレッション型TFTをオンさせ、当該回路を動作させることができる。

【0040】

このような本発明のブートストラップ回路は、シフトレジスタやレベルシフタのようなダイナミック回路に用いることができる。

【0041】

(実施の形態3)

本実施の形態では、本発明のソースフォロワ回路を用いた信号線駆動回路について説明する。

【0042】

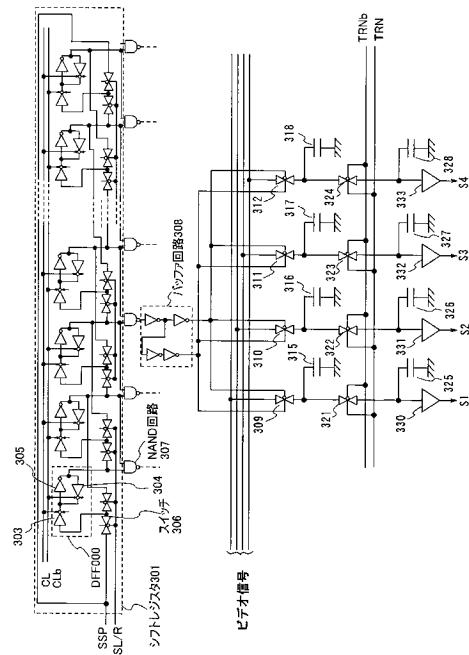

図3にはシフトレジスタ301、NAND回路307、バッファ回路308、を有する信号線駆動回路を示す。

【0043】

まず、シフトレジスタの初段にスイッチ306を介してソーススタートパルスSSPが入力される。スイッチ306はシフトレジスタの走査方向を規定する機能を有しており、走査方向切り替え信号SL/RがLoのとき図3では左から右に、Hiのときに右から左に走査が行なわれる。シフトレジスタの各段は、DFF(ディレイフィリップフロップ)302はクロックドインバータ303、304、インバータ305を有するDFF302によって構成され、クロックパルスCLおよびCLbが入力されるごとにパルスをシフトしていく。

【0044】

シフトレジスタの出力はNAND回路307を介して、バッファ回路308に入力される。バッファ回路の出力によってアナログスイッチ309～312はオンになり、ビデオ信号をアナログメモリとしての容量(以下、アナログメモリと表記する)315～318にサンプリングしていく。1ライン分のデータが順次アナログメモリに蓄えられると、次の帰線期間中にTRN、TRNbの信号がアクティブになり、アナログスイッチ321～324がオンになる。これによって、アナログメモリ315～318のデータはアナログメモリとしての容量325～328へ一斉に転送される。このように信号を保持し、一斉に転送する回路をラッチ回路ともいう。

【0045】

なおシフトレジスタには、実施の形態2に示したデプレッション型TFTを有するブートストラップ回路を用いて、電源を増分させることなく、入力される電圧の振幅を増大することができる。

10

20

30

40

50

**【 0 0 4 6 】**

そして、次のサンプリングのため、アナログスイッチ 309～312 がオンする前に、アナログスイッチ 321～324 はオフとなる。アナログメモリ 325～328 のデータはソースフォロワ回路 330～333 を介して、信号線 S1～S4 に出力される。アナログメモリ 325～328 のデータは 1 ライン期間の間保持されるため、ソースフォロワ回路 330～333 は 1 ライン期間の時間をかけて信号線を充電できる。さらにデプレッショント F T T を有するソースフォロワ回路により、電源電圧を増分する必要がなく、低消費電力な信号線駆動回路を提供することができる。

**【 0 0 4 7 】**

このようにして、アナログメモリ、アナログバッファ回路を有することにより、線順次駆動が可能となる。以上のような信号線駆動回路は、15 インチ以上の大型の液晶表示装置や発光装置等の表示装置に適する。10

**【 0 0 4 8 】****( 実施の形態 4 )**

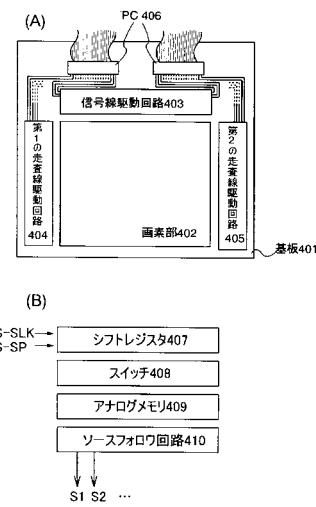

本実施の形態では、本発明のソースフォロワ回路を有する信号線駆動回路を備えた液晶表示装置について、図 4 を用いて説明する。

**【 0 0 4 9 】**

本発明の液晶表示装置は、基板 401 上に、複数の画素がマトリクス状に配置された画素部 402 を有し、画素部 402 の周辺には、本発明の信号線駆動回路 403、第 1 の走査線駆動回路 404 及び第 2 の走査線駆動回路 405 を有する。信号線駆動回路 403 と、第 1 の走査線駆動回路 404 及び第 2 の走査線駆動回路 405 には、FPC 406 を介して外部より信号が供給される。図 4 (A) において、信号線駆動回路 403 と、2 組の走査線駆動回路 404、405 を有し、画素部と一体形成しているが、本発明はこれに限定されず、画素の構成に応じて任意に設計することができる。20

**【 0 0 5 0 】**

信号線駆動回路の構成について図 4 (B) を用いて説明する。信号線駆動回路は、シフトレジスタ 407、スイッチ 408、アナログメモリ 409、ソースフォロワ回路 410 を有している。シフトレジスタ 407 は、フリップフロップ回路 (FF) 等を複数列用いて構成され、クロック信号 (S-CLK)、スタートパルス (S-SP) 等が入力される。これらの信号のタイミングに従って、サンプリングパルスが出力される。実施の形態 3 で示したように順次アナログメモリ 409 へ入力され、ソースフォロワ回路 330～333 を介して、信号線 S1、S2・・・に出力される。30

**【 0 0 5 1 】**

また第 1 の走査線駆動回路 404 及び第 2 の走査線駆動回路 405 は、シフトレジスタ、バッファ回路を有する。動作を簡単に説明すると、シフトレジスタは、クロック信号 (G-CLK)、スタートパルス (S-SP) 及びクロック反転信号 (G-CLKb) に従って、順次サンプリングパルスを出力する。その後バッファ回路で増幅されたサンプリングパルスは、走査線に入力されて 1 行ずつ選択状態にしていく。そして走査線の選択されるタイミングに合わせて、順に信号線から信号電流が書き込まれる。

**【 0 0 5 2 】**

なおシフトレジスタと、バッファの間にはレベルシフタ回路を配置した構成にしてもよい。レベルシフタ回路を配置することによって、電圧振幅を大きくすることができる。このレベルシフタ回路に、本発明のブートストラップ回路を用いることができる。40

**【 0 0 5 3 】****( 実施の形態 5 )**

本発明のソースフォロワ回路等のアナログバッファ回路を用いた電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ (ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置 (カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末 (モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等)、記録媒体を備えた画像再生装置 (具体的には D i

10

20

30

40

50

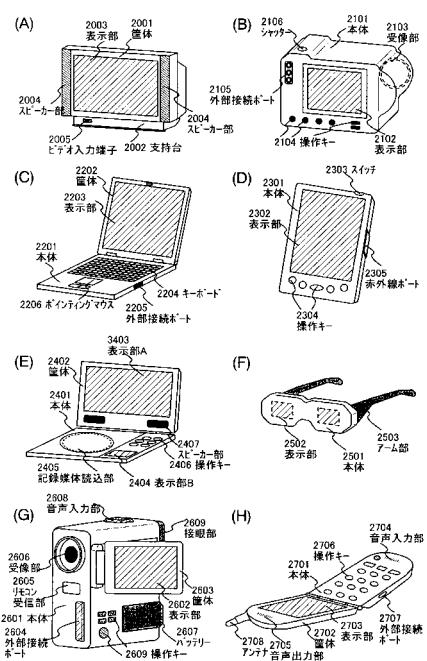

g i t a l V e r s a t i l e D i s c ( D V D ) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。 それら電子機器の具体例を図6に示す。

【 0 0 5 4 】

図6(A)は液晶表示装置であり、筐体2001、支持台2002、表示部2003、スピーカー部2004、ビデオ入力端子2005等を含む。本発明のソースフォロワ回路を有する液晶表示装置は表示部2003に用いることができる。本発明により薄くて、かつ軽量であって、低消費電力な液晶表示装置を提供することができる。なお液晶表示装置は、パソコン用、T V放送受信用、広告表示用などの全ての情報表示用発光装置が含まれる。

10

【 0 0 5 5 】

図6(B)はデジタルスチルカメラであり、本体2101、表示部2102、受像部2103、操作キー2104、外部接続ポート2105、シャッター2106等を含む。本発明のソースフォロワ回路を有する液晶表示装置は表示部2102に用いることができる。

【 0 0 5 6 】

図6(C)はノート型パーソナルコンピュータであり、本体2201、筐体2202、表示部2203、キーボード2204、外部接続ポート2205、ポインティングマウス2206等を含む。本発明のソースフォロワ回路を有する液晶表示装置は表示部2203に用いることができる。

【 0 0 5 7 】

図6(D)はモバイルコンピュータであり、本体2301、表示部2302、スイッチ2303、操作キー2304、赤外線ポート2305等を含む。本発明のソースフォロワ回路を有する液晶表示装置は表示部2302に用いることができる。

20

【 0 0 5 8 】

図6(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはD V D再生装置)であり、本体2401、筐体2402、表示部A2403、表示部B2404、記録媒体(D V D等)読み込み部2405、操作キー2406、スピーカー部2407等を含む。表示部A2403は主として画像情報を表示し、表示部B2404は主として文字情報を表示する。本発明のソースフォロワ回路を有する液晶表示装置はこれら表示部A、B2403、2404に用いることができる。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。

30

【 0 0 5 9 】

図6(F)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)であり、本体2501、表示部2502、アーム部2503を含む。本発明のソースフォロワ回路を有する液晶表示装置は表示部2502に用いることができる。

【 0 0 6 0 】

図6(G)はビデオカメラであり、本体2601、表示部2602、筐体2603、外部接続ポート2604、リモコン受信部2605、受像部2606、バッテリー2607、音声入力部2608、操作キー2609等を含む。本発明のソースフォロワ回路を有する液晶表示装置は表示部2602に用いることができる。

40

【 0 0 6 1 】

ここで図6(H)は携帯電話であり、本体2701、筐体2702、表示部2703、音声入力部2704、音声出力部2705、操作キー2706、外部接続ポート2707、アンテナ2708等を含む。本発明のソースフォロワ回路を有する液晶表示装置は表示部2703に用いることができる。なお、表示部2703は黒色の背景に白色の文字を表示することで携帯電話の消費電流を抑えることができる。

【 0 0 6 2 】

以上のように、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。また本実施の携帯の電子機器は、実施の形態1から5に示したいずれの構成のソースフォロワ回路やポートストラップ回路、信号線駆動回路を用いることができる。

50

## 【0063】

## 【発明の効果】

本発明により、多結晶シリコンTFTを用いた駆動回路（電気回路）において、電源電圧を所望の値より上昇させずに動作させることができる。その結果、当該駆動回路を有する液晶表示装置、発光装置等の表示装置、CPUやメモリ等の半導体集積回路において、電源電圧を低く保持することができ、低消費電力を達成することができる。

## 【0064】

またさらに多結晶シリコンTFTを用いることにより、画素部と駆動回路部とを一体形成した表示装置を提供することができる。

## 【図面の簡単な説明】

10

【図1】本発明のソースフォロワ回路を示す図。

【図2】本発明のブートストラップ回路を示す図。

【図3】本発明の信号線駆動回路を示す図。

【図4】本発明の表示装置を示す図。

【図5】従来のソースフォロワ回路を示す図。

【図6】本発明を搭載した電子機器を示す図。

【図1】

(B)本発明のNチャネル型TFTのVG-ID特性

【図2】

【 図 3 】

【 四 4 】

【図5】

〔 四 6 〕

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

G 09 G 3/20 6 2 3 B

G 09 G 3/36

F ターム(参考) 5F110 AA09 BB02 CC10 DD02 DD03 GG01 GG02 GG13 GG32 GG44

PP01 PP03 PP10 PP34

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 源极跟随器电路或自举电路，具有该电路的驱动电路，以及具有该驱动电路的液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2004296741A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2004-10-21 |

| 申请号            | JP2003086371                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 申请日     | 2003-03-26 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 申请(专利权)人(译)    | 半导体能源研究所有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| [标]发明人         | 小山潤                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 小山 潤                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G02F1/1368 G09G3/20 G09G3/36 H01L27/08 H01L27/12 H01L29/786 H03F1/02 H03F1/22 H03F3/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| CPC分类号         | G09G3/3688 G09G3/2074 G09G2330/021 H01L29/78672 H03F1/02 H03F1/223 H03F3/505 H03F2200/51 H03F2200/513                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| FI分类号          | H01L27/08.331.E G02F1/1368 H01L29/78.612.B G09G3/20.611.A G09G3/20.622.B G09G3/20.623.B G09G3/36 H01L27/06.102.F H01L27/06.102.Z H01L27/088.331.E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 2H092/GA59 2H092/JA24 2H092/NA01 2H092/PA06 5C006/BB16 5C006/BC02 5C006/BC03 5C006/BC06 5C006/BC08 5C006/BC11 5C006/BC20 5C006/BF03 5C006/BF11 5C006/BF34 5C006/FA46 5C006/FA47 5C080/AA10 5C080/BB05 5C080/DD22 5C080/DD26 5C080/EE29 5C080/FF01 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/KK01 5C080/KK07 5C080/KK43 5C080/KK47 5F048/AB03 5F048/AB07 5F048/AC02 5F048/AC04 5F048/BA16 5F048/BB14 5F048/BC16 5F110/AA09 5F110/BB02 5F110/CC10 5F110/DD02 5F110/DD03 5F110/GG01 5F110/GG02 5F110/GG13 5F110/GG32 5F110/GG44 5F110/PP01 5F110/PP03 5F110/PP10 5F110/PP34 2H192/AA24 2H192/FA44 2H192/FA73 2H192/FB02 2H192/FB05 |         |            |

| 其他公开文献         | JP2004296741A5<br>JP4531343B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

### 摘要(译)

模拟缓冲电路具有将多晶硅TFT的栅极-源极电压添加到输入电压的问题。结果，电源电压增加，产生热量，并且功耗增加。鉴于上述问题，本发明的特征在于，在诸如源极跟随器电路之类的模拟缓冲电路中使用的多晶硅TFT是耗尽型的。由于耗尽型多晶硅TFT的阈值电压在负电压侧，因此如上所述不必增加输入电压。结果，不需要增加电源电压，并且可以实现液晶显示装置的特别低的功耗。[选型图]图1