(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4881368号

(P4881368)

(45) 発行日 平成24年2月22日(2012.2.22)

(24) 登録日 平成23年12月9日(2011.12.9)

(51) Int.CI.

F 1

G02F 1/1343 (2006.01)

G02F 1/1368 (2006.01)G02F 1/1343

G02F 1/1368

請求項の数 2 (全 16 頁)

(21) 出願番号 特願2008-321419 (P2008-321419)

(22) 出願日 平成20年12月17日 (2008.12.17)

(65) 公開番号 特開2010-20277 (P2010-20277A)

(43) 公開日 平成22年1月28日 (2010.1.28)

審査請求日 平成20年12月17日 (2008.12.17)

(31) 優先権主張番号 10-2008-0067524

(32) 優先日 平成20年7月11日 (2008.7.11)

(33) 優先権主張国 韓国(KR)

(73) 特許権者 501426046

エルジー ディスプレイカンパニー リ

ミテッド

大韓民国 ソウル, ヨンドゥンパーク, ヨ

イドードン 20

(74) 代理人 100110423

弁理士 曾我 道治

(74) 代理人 100084010

弁理士 古川 秀利

(74) 代理人 100094695

弁理士 鈴木 憲七

(74) 代理人 100111648

弁理士 梶並 順

(74) 代理人 100147566

弁理士 上田 俊一

最終頁に続く

(54) 【発明の名称】 液晶表示装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上にゲートライン及び前記ゲートラインと交差して画素領域を定義するデータラインを形成する段階と、

前記ゲートライン及び前記データラインの交差部に薄膜トランジスタを形成する段階と、

前記薄膜トランジスタを含む基板上に、前記薄膜トランジスタを保護する保護膜を形成する段階と、

前記薄膜トランジスタと接続された画素電極を形成する段階と、

前記画素電極と共にフリンジ電界を形成する共通電極を形成する段階と、

前記画素電極及び共通電極のうち少なくともいずれか1つをマスクとして用い前記保護膜を乾式エッチングすることにより前記保護膜に溝を形成する段階と

を備え、

前記溝は、前記画素電極または共通電極を湿式エッチングした後、連続した乾式エッチングを通じて形成され、

前記画素電極及び前記共通電極のうち少なくともいずれか1つは、前記画素領域で互いに離間して形成され、

前記溝は、前記離間して形成された電極間の保護膜に形成される

ことを特徴とする液晶表示装置の製造方法。

## 【請求項 2】

10

20

前記共通電極及び前記画素電極のうちいずれか1つの電極間の、前記溝が形成された部分の保護膜の高さが、前記溝が形成されていない部分の保護膜の高さと0.1~0.7μmの差を有することを特徴とする請求項1に記載の液晶表示装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶表示装置の製造方法に係り、特に、低電圧駆動させることができるとともに、透過率を向上させることができる液晶表示装置の製造方法に関する。

【背景技術】

【0002】

情報化社会の発展に伴い、表示装置に対する要求も様々な形態で徐々に増加しつつある。これに応えて、最近では、LCD (Liquid Crystal Display)、PDP (Plasma Display Panel)、ELD (Electro Luminescent Display)、VFD (Vacuum Fluorescent Display)など様々な平板表示装置が研究されてきており、一部は、既に様々な装備で表示装置として用いられている。

10

【0003】

その中でも、現在、高画質、軽量、薄型、低消費電力といった長所から、移動型の画像表示装置として、CRT (Cathode Ray Tube) を取って代わりつつあるLCDが最も多用されている。これは、ノートブックコンピュータのモニターのような移動型表示装置の他にも、放送信号を受信してディスプレイするテレビ、及びコンピュータのモニターなどとしても、多様に開発されている。

20

【0004】

一般に、液晶表示装置は、大きく、薄膜トランジスタアレイ基板と、カラーフィルタアレイ基板と、これら両基板間に形成された液晶層と、で構成される。

【0005】

薄膜トランジスタ基板は、基板上に縦横に配列されて複数の画素領域を定義する複数のゲートラインとデータライン、ゲートラインとデータラインとの交差領域に形成されたスイッチング素子である薄膜トランジスタ、及び画素領域上に形成された画素電極で構成される。

30

【0006】

カラーフィルタ基板は、色相を具現するカラーフィルタと、これらカラーフィルタ間の区分及び外部光反射防止のためのブラックマトリクスと、で構成される。

【発明の開示】

【発明が解決しようとする課題】

【0007】

ここで、薄膜トランジスタを保護するための保護膜は、開口領域で光を透過させることとなるが、光を吸収または反射する特性によって光透過率が低下してしまう他、共通電極及び画素電極の電界形成時に保護膜によって電界が弱くなり、高い駆動電圧が要求されるという問題点があった。

40

【0008】

なお、電極上では液晶駆動が円滑でないため、電極上における透過率が大幅に低下するという問題点があった。

【0009】

本発明は上記の問題点を解決するためのもので、その目的は、液晶表示装置において特に低電圧駆動及び透過率の向上を実現する液晶表示装置の製造方法を提供することにある。

【課題を解決するための手段】

【0010】

上記目的を達成するために、本発明による液晶表示装置の製造方法は、基板上にゲート

50

ライン及び前記ゲートラインと交差して画素領域を定義するデータラインを形成する段階と、前記ゲートライン及び前記データラインの交差部に薄膜トランジスタを形成する段階と、前記薄膜トランジスタを含む基板上に、前記薄膜トランジスタを保護する保護膜を形成する段階と、前記薄膜トランジスタと接続された画素電極を形成する段階と、前記画素電極と共にフリンジ電界を形成する共通電極を形成する段階と、前記画素電極及び共通電極のうち少なくともいずれか1つをマスクとして用い前記保護膜を乾式エッチングすることにより前記保護膜に溝を形成する段階とを備え、前記溝は、前記画素電極または共通電極を湿式エッチングした後、連続した乾式エッチングを通じて形成され、前記画素電極及び前記共通電極のうち少なくともいずれか1つは、前記画素領域で互いに離間して形成され、前記溝は、前記離間して形成された電極間の保護膜に形成されることを特徴とする。

10

#### 【発明の効果】

##### 【0012】

本発明による液晶表示装置の製造方法は、下記の効果を奏する。

##### 【0013】

電圧上昇や構造変更なしで、保護膜上に形成された電極間の保護膜を一定高さにエッチングし、溝を形成することによって、透過効率を増加させ、且つ同一透過効率を低電圧駆動で得られ、消費電力を減少させることが可能になる。

#### 【発明を実施するための最良の形態】

##### 【0014】

以下、添付の図面を参照しつつ、本発明の実施例による液晶表示装置について詳細に説明する。

20

##### 【0015】

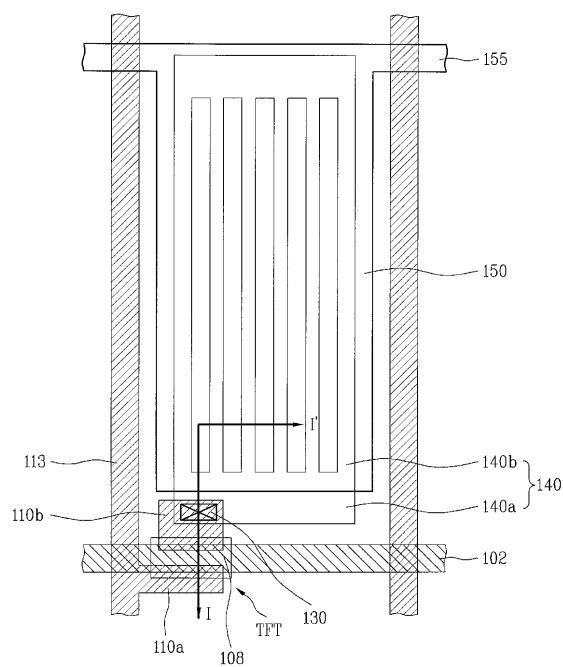

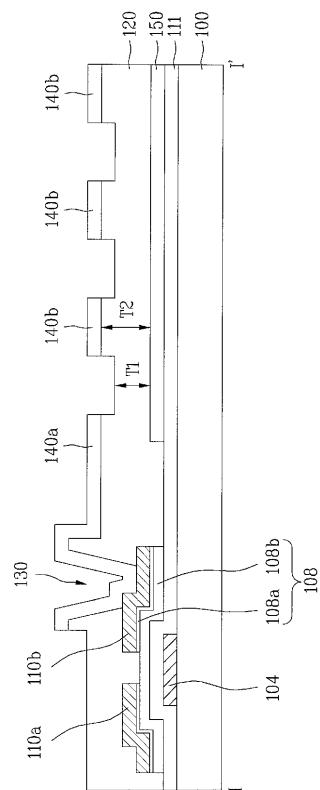

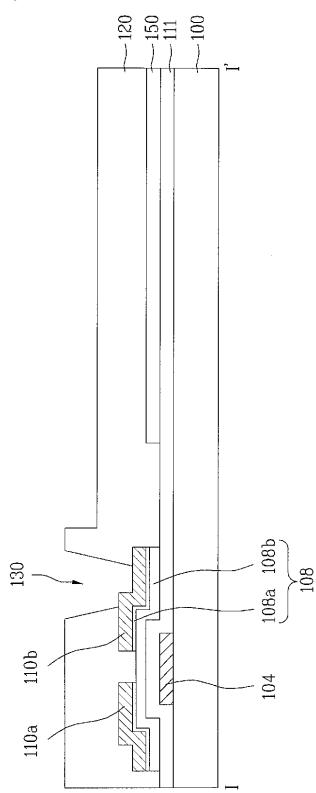

図1は、本発明の第1実施例によるフリンジフィールドスイッチングモード(Fringe Field Switching:FFS)の液晶表示装置の薄膜トランジスタ基板を示す平面図であり、図2は、図1に示すI-I'線に沿った薄膜トランジスタ基板を示す断面図である。

##### 【0016】

図1及び図2に示すフリンジフィールドスイッチングモードの液晶表示装置は、基板上に、複数のゲートライン102と、ゲート絶縁膜111を介在してゲートライン102と交差するように形成され、画素領域を定義する複数のデータライン112と、ゲートライン102及びデータライン112が交差する部分に形成された薄膜トランジスタTFTと、薄膜トランジスタTFTと接続される画素電極140と、画素電極140と保護膜120を介在して重なり、板形状に形成される共通電極150と、共通電極150と接続され、共通電極150に液晶を駆動するための共通電圧を供給する共通ライン155と、を備える。

30

##### 【0017】

薄膜トランジスタTFTは、ゲートライン102に含まれているゲート電極104と、ゲートライン102が形成された薄膜トランジスタ基板100の全面にゲート電極104と重なるように形成されたゲート絶縁膜111と、ゲート絶縁膜111上にゲート電極104と重なるように形成されたオーミックコンタクト層108a及び活性層108bからなる半導体層108と、データライン112から分岐し、半導体層108上に形成されるソース電極110a及び半導体層108上にソース電極110aと対向して形成されたドレイン電極110bと、で構成される。

40

##### 【0018】

画素電極140と共に電極150との間隔は、液晶パネルの上下基板のセルギャップよりも小さく形成することによって、フリンジ電界を形成する。フリンジ電界によって上下基板間に埋め込まれた液晶分子が動作するようにすることによって、開口率及び透過率を向上させることとなる。

##### 【0019】

画素電極140は、スリットを有する板形状で、保護膜120を貫通するコンタクトホ

50

ール 130 を通じて露出されたドレン電極 110b と電気的に接続され、ゲートラインと並んで形成された画素電極水平部 140a と、画素電極水平部 140a と接続され、共通電極 150 とフリンジ電界を形成する画素電極垂直部 140b と、を含む。画素電極垂直部 140b は、互いに離間して形成される。

#### 【0020】

共通電極 150 は、ゲート絶縁膜 111 上に板形状に形成され、保護膜 120 を介在して画素電極 140 と重なっており、画素電極 140 とフリンジ電界を形成する。共通電極 150 及び画素電極 140 の形成位置は、互いに変えても良い。すなわち、画素電極 140 が保護膜 120 の下部に板形状に形成され、保護膜 120 を介在して画素電極 140 と重なるように共通電極 150 が形成されても良い。

10

#### 【0021】

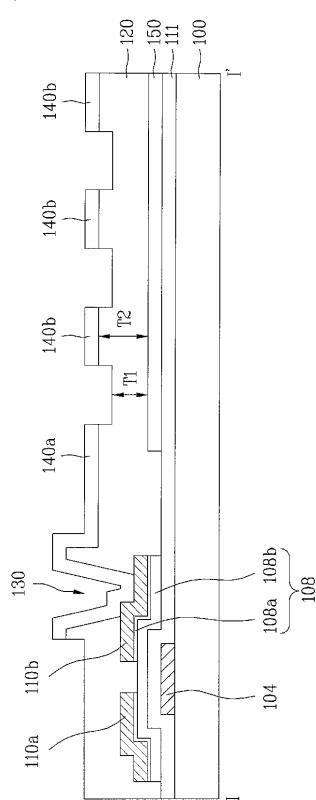

ここで、画素電極 140 または共通電極 150 との間に形成された保護膜 120 によって光の透過率が落ち、画素電極 140 及び共通電極 150 間の電界が弱くなるので、高い駆動電圧が要求される。このような問題点を解決すべく、保護膜 120 上に共通電極 150 または画素電極 140 をマスクとして乾式エッチング工程を行い、共通電極 150 または画素電極 140 間の保護膜 120 に一定高さの溝を形成する。溝を有する共通電極 150 または画素電極 140 間の保護膜 120 の高さ T1 は、共通電極 150 または画素電極 140 下部の保護膜 120 の高さ T2 よりも小さく形成され、これらの差 (T2 - T1) は、水平配向する構造において物理的ラビング時にダメージが生じないような値、すなわち、0.1 ~ 0.7 μm にする。

20

#### 【0022】

保護膜 120 は、ゲート絶縁膜 111 と同一の無機絶縁物質が、PECVD などの蒸着方法で蒸着されてなるか、誘電定数の小さいアクリル系有機化合物、BCB (Benzocyclobutene) またはPFCB (Perfluorocyclobutane) などの有機絶縁物質がスピンまたはスピンレスなどのコーティング方法でコーティングされてなる。

#### 【0023】

画素電極 140、共通電極 150 及び共通ライン 155 は、透明導電物質からなり、インジウムスズ酸化物 (Indium Tin Oxide: ITO)、スズ酸化物 (Tin Oxide: TO)、インジウム亜鉛酸化物 (Indium Zinc Oxide: IZO) またはインジウムスズ亜鉛酸化物 (Indium Tin Zinc Oxide: ITZO) などで形成される。

30

#### 【0024】

ここで、共通電極 150 及び共通ライン 155 が同一物質から形成される場合には、一体化して形成されるが、相互に異なる層で異なる物質で形成される場合には、別のコンタクトホールを通じて共通電極 150 及び共通ライン 155 を電気的に連結させ、この時、共通電極 150 は、モリブデン (Mo)、アルミニウム (Al)、アルミニウム・ネオジミウム (Al-Nd)、銅 (Cu)、クロム (Cr)、チタン (Ti) などの金属と、これらの合金が単一層または複数層構造で形成される。

#### 【0025】

40

このように、電圧上昇や構造変更なしで、保護膜 120 上に形成された電極間の保護膜 120 を一定高さにエッチングして溝を形成することによって、透過効率を増加させ、且つ同一透過効率を低電圧駆動で得られ、消費電力を減少させることが可能になる。

#### 【0026】

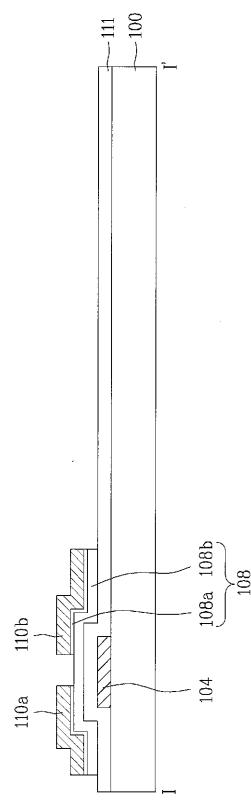

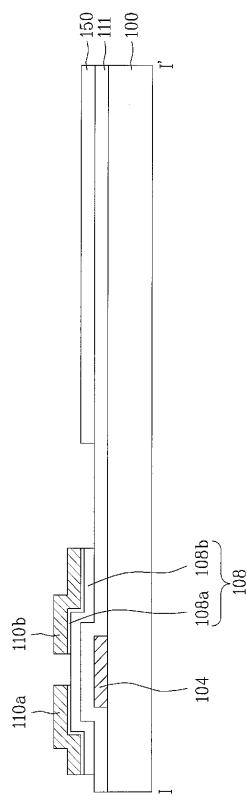

図3A乃至図3Eは、図2に示す薄膜トランジスタ基板の製造方法を説明するための断面図である。

#### 【0027】

図3Aを参照すると、基板 100 上に形成されたゲート電極 104 と、ゲート電極 104 が形成された基板の全面に形成されたゲート絶縁膜 111 と、ゲート絶縁膜 111 上にゲート電極 104 と重なるように形成されたオーミックコンタクト層 108a 及び活性層

50

108bからなる半導体層108と、データライン112から分岐し、半導体層108上に形成されたソース電極110a及び半導体層108上にソース電極110aと対向して形成されたドレイン電極110bと、を含む薄膜トランジスタが形成される。

#### 【0028】

具体的に、基板100上にゲート金属層をスパッタリングなどの蒸着方法で形成した後、マスクを用いたフォトリソグラフィ工程及びエッチング工程でゲート金属層をパターニングし、ゲートライン102(図1)及びゲート電極104を形成する。

#### 【0029】

ゲート金属層は、モリブデン(Mo)、アルミニウム(Al)、アルミニウム-ネオジミウム(Al-Nd)、銅(Cu)、クロム(Cr)、チタン(Ti)などの金属と、これらの合金が単一層または複数層構造で形成されてなる。10

#### 【0030】

続いて、ゲート電極104を含む基板100全面にPECVD(Plasma Enhanced Chemical Vapor Deposition)等の蒸着方法で、ゲート絶縁膜111、非晶質シリコン(a-Si)層及び不純物(n+)がドープされた非晶質シリコン層が順次に形成される。次いで、ソース/ドレイン金属層をスパッタリングなどの蒸着方法で形成した後、マスクを用いたフォトリソグラフィ工程及びエッチング工程によってパターニングし、活性層108b及びオームиконтакト層108aからなる半導体層108と、データライン112(図1)、ソース電極110a及びドレイン電極110bを形成する。この時、ソース電極110a及びドレイン電極110bとオームиконтакト層108aとの電気的な分離のために、回折露光またはハーフトーンマスク(half-tone mask)が用いられる。20

#### 【0031】

ゲート絶縁膜111には、酸化シリコン(SiO<sub>x</sub>)または窒化シリコン(SiNx)などの無機絶縁物質が用いられる。ソース電極及びドレイン電極は、モリブデン(Mo)、アルミニウム(Al)、アルミニウム-ネオジミウム(Al-Nd)、銅(Cu)、クロム(Cr)、チタン(Ti)、モリブデン-チタン合金(MoTi)、モリブデン-ニオビウム合金(MoNb)、チタン-ニオビウム合金(TiNb)などの金属と、これらの合金が単一層または複数層構造で形成されてなる。

#### 【0032】

続いて、図3Bに示すように、ソース電極110a及びドレイン電極110bを含む基板の全面に第1透明導電層を蒸着した後、マスクを用いたフォトリソグラフィ工程及びエッチング工程によってパターニングし、画素領域上に板形状の共通電極150と、共通電極150と一体化して形成され、共通電極150に共通電圧を印加する共通ライン155(図1)と、を形成する。30

#### 【0033】

第1透明導電層は、インジウムスズ酸化物(Indium Tin Oxide:ITO)、スズ酸化物(Tin Oxide:TO)、インジウム亜鉛酸化物(Indium Zinc Oxide:IZO)またはインジウムスズ亜鉛酸化物(Indium Tin Zinc Oxide:ITZO)などで形成される。40

#### 【0034】

共通電極150及び共通ライン155(図1)が相互に異なる層で異なる物質で形成される場合、別のコンタクトホールを通じて共通電極150及び共通ライン155を電気的に連結させ、この時、共通電極150は、モリブデン(Mo)、アルミニウム(Al)、アルミニウム-ネオジミウム(Al-Nd)、銅(Cu)、クロム(Cr)、チタン(Ti)などの金属と、これらの合金が単一層または複数層構造で形成されてなる。

#### 【0035】

図3Cを参照すると、共通電極150を含む基板の全面に、ドレイン電極110bを露出させるコンタクトホール130を有する保護膜120を形成する。

#### 【0036】

10

20

30

40

50

具体的に、共通電極 150 を含む基板の全面に保護膜 120 を形成した後、マスクを用いたフォトリソグラフィ工程及びエッチング工程によって保護膜 120 をパターニングすることで、ドレイン電極 110b を露出させるコンタクトホール 130 を形成する。

#### 【0037】

保護膜 120 は、ゲート絶縁膜 111 と同一の無機絶縁物質が P E C V D などの蒸着方法で蒸着されてなるか、誘電定数の小さいアクリル系有機化合物、 B C B ( B e n z o c y c l o b u t e n ) または P F C B ( P e r f l u o r o c y c l o b u t a n e ) などのような有機絶縁物質がスピンまたはスピレスなどのコーティング方法でコーティングされてなる。

#### 【0038】

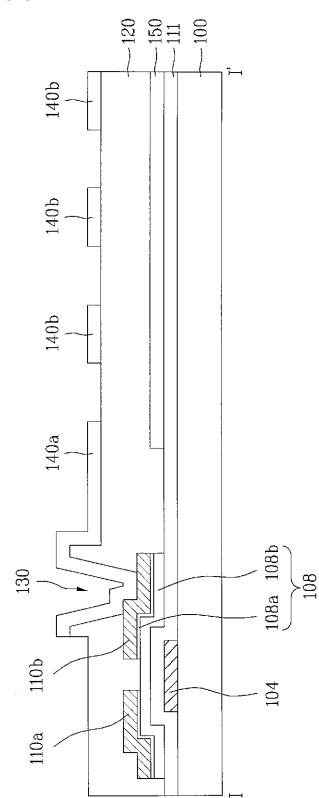

図 3D を参照すると、保護膜 120 上に画素電極 140 が形成される。 10

#### 【0039】

具体的に、保護膜 120 上に第 2 透明導電層を蒸着した後、マスクを用いたフォトリソグラフィ工程及び湿式エッチング工程によってパターニングし、コンタクトホールを通じてドレイン電極 110b と電気的に連結される画素電極水平部 140a、及びデータライン 112 ( 図 1 ) と並んで形成された複数の画素電極垂直部 140b を形成する。画素電極 140 は、保護膜 120 を介在して共通電極 150 と重なり、フリンジ電界を形成する。

#### 【0040】

ここで、共通電極 150 及び画素電極 140 の形成位置は、互いに変わっても良い。すなわち、画素電極 140 が保護膜 120 の下部に板形状に形成され、保護膜 120 を介在して画素電極 140 と重なるように共通電極 150 が形成されても良い。 20

#### 【0041】

第 2 透明導電層は、インジウムスズ酸化物 ( I n d i u m T i n O x i d e : I T O ) 、スズ酸化物 ( T i n O x i d e : T O ) 、インジウム亜鉛酸化物 ( I n d i u m Z i n c O x i d e : I Z O ) またはインジウムスズ亜鉛酸化物 ( I n d i u m T i n Z i n c O x i d e : I T Z O ) などで形成される。

#### 【0042】

続いて、図 3E に示すように、保護膜 120 上に共通電極 150 または画素電極 140 をマスクとした乾式エッチング工程を行い、共通電極 150 または画素電極 140 間の保護膜 120 に一定高さの溝を形成する。 30

#### 【0043】

すなわち、画素電極 140 または共通電極 150 を形成するための湿式エッチング後に、連続した乾式エッチングを通じて共通電極 150 または画素電極 140 のパターンと正確にオーバーレイ整列に合うように保護膜 120 をパターニングし、溝を形成する。保護膜 120 は、電極パターンに自己整列 ( s e l f a l i g n m e n t ) してパターニングされる。

#### 【0044】

溝を有する共通電極 150 または画素電極 140 間の保護膜 120 の高さ T1 は、共通電極 150 または画素電極 140 下部の保護膜 120 の高さ T2 よりも小さく形成され、これらの差 ( T2 - T1 ) は、水平配向する構造において物理的ラビング時にダメージが生じないような値、すなわち、 0.1 ~ 0.7 μm にする。 40

#### 【0045】

下式 ( 1 ) は、しきい値電圧 ( V<sub>t h</sub> ) を示し、ここで、 K<sub>I P S</sub> は回転弾性係数、  $\epsilon_0$  は真空誘電率、  $\epsilon_r$  は液晶固有定数、 d はセルギャップ、 l は電極間距離を表す。

#### 【0046】

【数1】

$$V_{th} = \frac{\pi l}{d} \sqrt{\frac{K_{IPS}}{\epsilon_0 \epsilon_r}} \quad (1)$$

【0047】

このように、保護膜120上の共通電極150または画素電極140間の保護膜120を一定高さにエッティングし、溝を形成することによって、上下基板のセルギャップが大きくなり、フリンジ電界を形成する共通電極150または画素電極140間の距離が小さくなる。これにより、しきい値電圧が小さくなり、低電圧駆動が可能になることが、上式(1)からわかる。10

【0048】

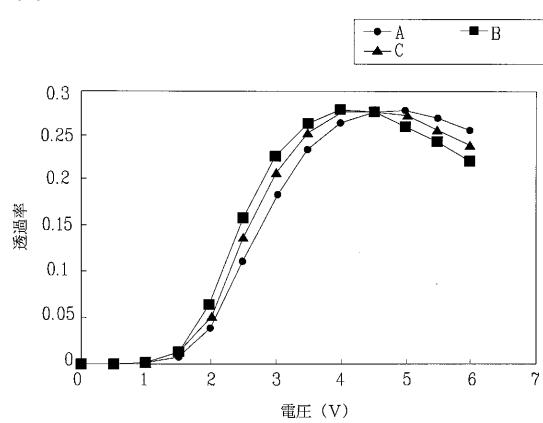

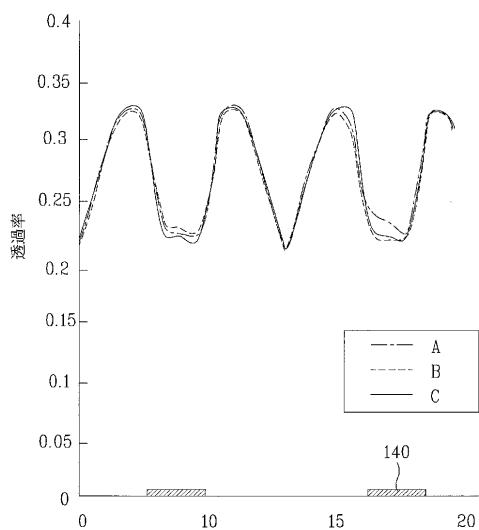

図4は、第1実施例による、電圧による透過率を示すグラフである。

【0049】

図4を参照すると、Aは、従来の画素領域で共通電極150または画素電極140下部の保護膜120に溝がない平坦な構造を表し、Bは、画素領域で共通電極150または画素電極140間の保護膜120に0.3μmの溝が形成された構造を表し、Cは、画素領域で共通電極150または画素電極140間の保護膜120に0.2μmの溝が形成された構造を表す。20

【0050】

例えば、電極間の保護膜120に溝が形成されていないA構造で、3Vの電圧を印加すると、約0.17の透過率を示すが、0.3μmの溝が形成されたB構造では、3Vの電圧印加時に約0.23の透過率を示し、0.2μmの溝が形成されたC構造では、3Vの電圧印加時に約0.21の透過率を示したことがわかる。これにより、従来のA構造と比較し、保護膜120に溝が形成されたB及びC構造が同一透過率において低電圧駆動が可能であるということがわかり、よって、消費電力を減少できるという効果を奏する。20

【0051】

したがって、電極間の保護膜120をエッティングし、一定の溝を形成することによって、同一電圧印加時に透過率を向上させることができる。

【0052】

図5は、第1実施例のフリンジ電界を形成する画素電極140の断面における透過率を示すグラフである。30

【0053】

各画素電極140の上部において、従来の画素領域で画素電極140下部の保護膜120に溝がない平坦なA構造に比べて、保護膜120に溝が形成されたB及びC構造の透過率がより上昇したことがわかる。ここで、画素電極140と共に電極150は、互いに位置を変えて形成しても良く、その場合、図5は、共通電極150の断面における透過率となる。

【0054】

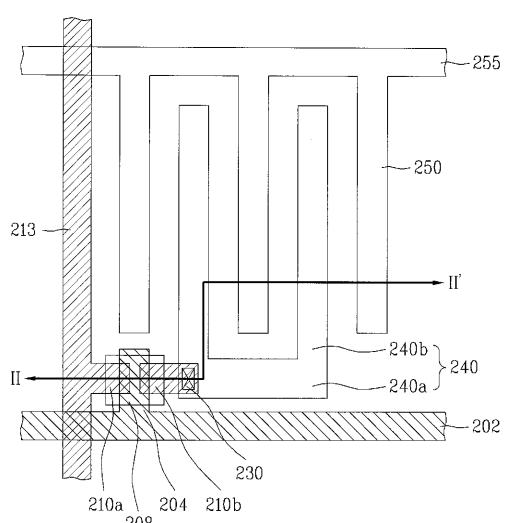

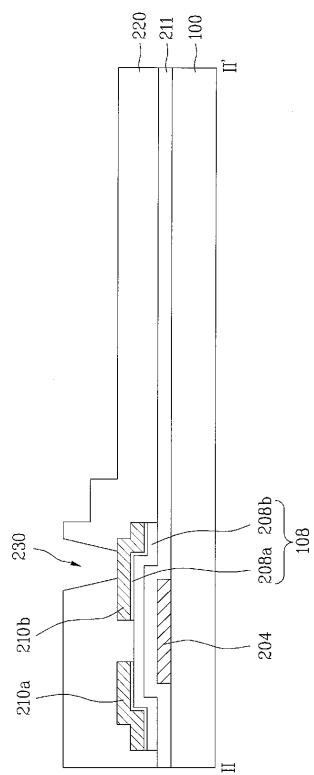

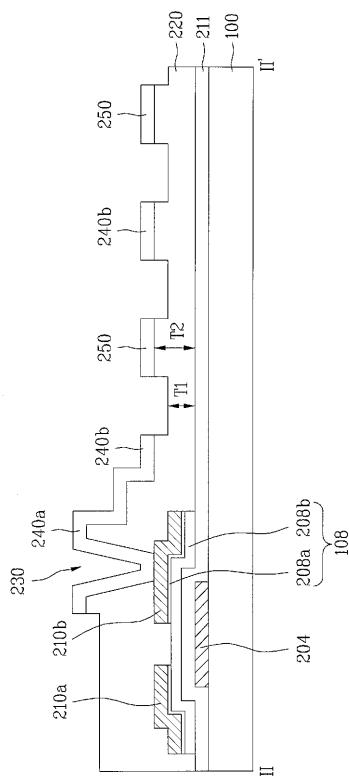

図6は、本発明の第2実施例によるインプレーンスイッチングモード(Plane Switching Mode: IPS)の液晶表示装置の薄膜トランジスタ基板を示す平面図であり、図7は、図6に示すII-II'線に沿った薄膜トランジスタ基板を示す断面図である。40

【0055】

図6及び図7に示すインプレーンスイッチングモードの液晶表示装置は、基板100上に複数のゲートライン202と、ゲート絶縁膜211を介在してゲートライン202と交差するように形成され、画素領域を定義する複数のデータライン213と、ゲートライン202及びデータライン213が交差する部分に形成された薄膜トランジスタTFTと、薄膜トランジスタTFTと接続される画素電極240と、各画素領域で画素電極240と水平電界を形成する共通電極250と、共通電極250と接続され、共通電極250に液

晶を駆動するための共通電圧を供給する共通ライン255と、を備える。

**【0056】**

薄膜トランジスタTFTは、ゲートライン202から分岐したゲート電極204と、ゲートライン202が形成された薄膜トランジスタ基板100の全面に、ゲート電極204と重なるように形成されたゲート絶縁膜211と、ゲート絶縁膜211上にゲート電極204と重なるように形成されたオーミックコンタクト層208a及び活性層208bからなる半導体層208と、データライン213から分岐し、半導体層208上に形成されるソース電極210a及び半導体層208上にソース電極210aと対向して形成されたドレイン電極210bと、で構成される。

**【0057】**

画素電極240は、保護膜220を貫通するコンタクトホール230を通じて露出されたドレイン電極210bと電気的に接続され、ゲートライン202と並んで形成された画素電極水平部240aと、画素電極水平部240aと接続され、共通電極250と水平電界を形成する画素電極フィンガー部240bと、を含む。

**【0058】**

共通ライン255は、ゲートライン202と並んで形成され、共通電極250は、共通ライン255から分岐し、各画素領域に形成される。共通電極250は、画素電極フィンガー部240bと交互に配列され、水平電界を形成する。

**【0059】**

ここで、画素電極240及び共通電極250の下部に薄膜トランジスタTFTを保護する保護膜220が形成されるが、画素電極240及び共通電極250の間、すなわち、開口部領域では保護膜220によって光の透過率が落ちることとなる。このような問題点を解決すべく、保護膜220上の共通電極250及び画素電極240をマスクとした乾式エッチング工程を行い、共通電極250及び画素電極240間の保護膜220に一定高さの溝を形成する。溝を有する共通電極250及び画素電極240間の保護膜220の高さT1は、共通電極250または画素電極240下部の保護膜220の高さT2よりも小さく形成され、これらの差(T2-T1)は、水平配向する構造において物理的ラビング時にダメージが生じないような値、すなわち、0.1~0.7μmにする。

**【0060】**

保護膜220は、ゲート絶縁膜211と同一の無機絶縁物質がPECVDなどの蒸着方法で蒸着されてなるか、誘電定数の小さいアクリル系有機化合物、BCB(Benzocyclobutene)またはPFCB(Perfluorocyclobutane)などの有機絶縁物質がスピンまたはスピンレスなどのコーティング方法でコーティングされてなる。

**【0061】**

画素電極240、共通電極250及び共通ライン255は、透明導電物質からなり、インジウムスズ酸化物(Indium Tin Oxide:ITO)、スズ酸化物(Tin Oxide:TO)、インジウム亜鉛酸化物(Indium Zinc Oxide:IZO)またはインジウムスズ亜鉛酸化物(Indium Tin Zinc Oxide:ITZO)などで形成される。

**【0062】**

ここで、共通電極250及び共通ライン255が同一物質から形成される場合には、一体化して形成されるが、相互に異なる層で異なる物質から形成される場合には、別のコンタクトホールを通じて共通電極250及び共通ライン255を電気的に連結させ、この時、共通電極250は、モリブデン(Mo)、アルミニウム(Al)、アルミニウム-ネオジミウム(Al-Nd)、銅(Cu)、クロム(Cr)、チタン(Ti)などの金属と、これらの合金が単一層または複数層構造で形成されてなる。

**【0063】**

このように、共通電極250及び画素電極240間の保護膜220を一定高さにエッチングし、溝を形成することによって、上下基板のセルギャップが大きくなる。これにより

10

20

30

40

50

、しきい電圧が小さくなり、低電圧駆動が可能になるということは、上式(1)からわかる。

#### 【0064】

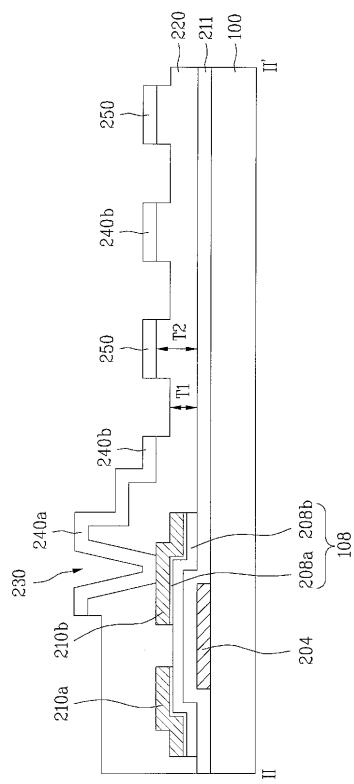

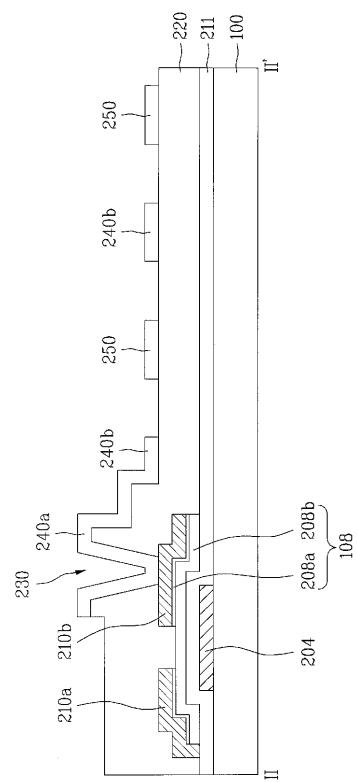

図8A乃至図8Dは、図7に示す薄膜トランジスタ基板の製造方法を説明するための断面図である。

#### 【0065】

図8Aを参照すると、基板100上に形成されたゲート電極204と、ゲート電極204が形成された基板の全面に形成されたゲート絶縁膜211と、ゲート絶縁膜211上にゲート電極204と重なるように形成されたオーミックコンタクト層208a及び活性層208bからなる半導体層208と、データライン213(図6)から分岐し、半導体層208上に形成されたソース電極210a及び半導体層208上にソース電極210aと対向して形成されたドレイン電極210bと、を含む薄膜トランジスタTFTが形成される。

10

#### 【0066】

具体的に、基板100上にゲート金属層をスパッタリングなどの蒸着方法で形成した後、マスクを用いたフォトリソグラフィ工程及びエッチング工程でゲート金属層をパターニングし、データライン202(図6)及びゲート電極204を形成する。

#### 【0067】

ゲート金属層は、モリブデン(Mo)、アルミニウム(Al)、アルミニウム-ネオジミウム(Al-Nd)、銅(Cu)、クロム(Cr)、チタン(Ti)などの金属と、これらの合金が単一層または複数層構造で形成されてなる。

20

#### 【0068】

続いて、ゲート電極204を含む基板100の全面にPECVD(Plasma Enhanced Chemical Vapor Deposition)等の蒸着方法でゲート絶縁膜211、非晶質シリコン(a-Si)層及び不純物(n+)がドープされた非晶質シリコン層が、順次、形成される。次いで、ソース/ドレイン金属層をスパッタリングなどの蒸着方法で形成した後、マスクを用いたフォトリソグラフィ工程及びエッチング工程によってパターニングし、活性層208b及びオーミックコンタクト層208aからなる半導体層208と、データライン213(図6)、ソース電極210a及びドレイン電極210bを形成する。この時、ソース電極210a及びドレイン電極210bとオーミックコンタクト層208aの電気的な分離のために、回折露光またはハーフトーンマスクが用いられる。

30

#### 【0069】

ゲート絶縁膜211には、酸化シリコン(SiO<sub>x</sub>)または窒化シリコン(SiNx)などの無機絶縁物質が用いられる。ソース電極210a及びドレイン電極210bは、モリブデン(Mo)、アルミニウム(Al)、アルミニウム-ネオジミウム(Al-Nd)、銅(Cu)、クロム(Cr)、チタン(Ti)、モリブデン-チタン合金(MoTi)、モリブデン-ニオビウム合金(MoNb)、チタン-ニオビウム合金(TiNb)などの金属と、これらの合金が単一層または複数層構造で形成されてなる。

#### 【0070】

続いて、ソース電極210a及びドレイン電極210bを含む基板の全面に保護膜220を形成した後、図8Bに示すように、マスクを用いたフォトリソグラフィ工程及びエッチング工程によって保護膜220をパターニングし、ドレイン電極210bを露出させるコンタクトホール230を形成する。

40

#### 【0071】

保護膜220は、ゲート絶縁膜211と同一の無機絶縁物質がPECVDなどの蒸着方法で蒸着されてなるか、誘電定数の小さいアクリル系有機化合物、BCB(Benzocyclobutene)またはPFCB(Perfluorocyclobutane)などのような有機絶縁物質が、スピノンまたはスピノレスなどのコーティング方法でコーティングされてなる。

50

## 【0072】

図8Cを参照すると、コンタクトホール230を有する保護膜220上に共通電極250及び画素電極240が形成される。

## 【0073】

具体的に、保護膜220上に透明導電層を蒸着した後、マスクを用いたフォトリソグラフィ工程及びエッチング工程によってパターニングし、コンタクトホール230を通じてドレイン電極210bと電気的に連結される画素電極水平部240aと、画素電極水平部240aと連結されて形成される画素電極フィンガー部240bと、画素電極フィンガー部240bと水平電界を形成する共通電極250、及び共通電極250に連結され、共通電極250に液晶を駆動するための共通電圧を供給する共通ライン255と、を形成する。

10

## 【0074】

透明導電層は、インジウムスズ酸化物(Indium Tin Oxide:ITO)、スズ酸化物(Tin Oxide:TO)、インジウム亜鉛酸化物(Indium Zinc Oxide:IZO)またはインジウムスズ亜鉛酸化物(Indium Tin Zinc Oxide:ITZO)などで形成される。

## 【0075】

続いて、図8Dに示すように、保護膜220上に共通電極250及び画素電極240をマスクとした乾式エッチング工程を行い、共通電極250及び画素電極240間の保護膜220に一定高さの溝を形成する。すなわち、画素電極240または共通電極250を形成するための湿式エッチング後に、連続して乾式エッチングを行い、共通電極250及び画素電極240のパターンと正確にオーバーレイ整列に合うように保護膜220をパターニングし、溝を形成する。保護膜220は、電極パターンに自己整列(self alignment)してパターニングされる。

20

## 【0076】

溝を有する共通電極250及び画素電極240間の保護膜220の高さT1は、共通電極250または画素電極240下部の保護膜220の高さT2よりも小さく形成され、これらの差(T2-T1)は、水平配向する構造において物理的ラビング時にダメージが生じないような値、すなわち、0.1~0.7μmにする。

## 【0077】

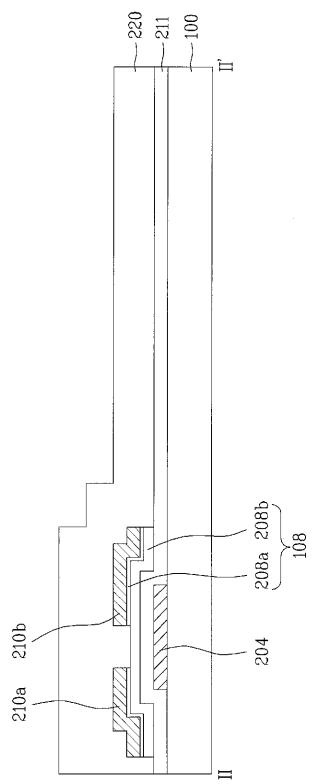

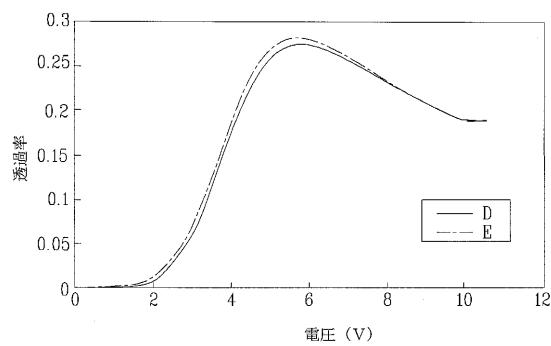

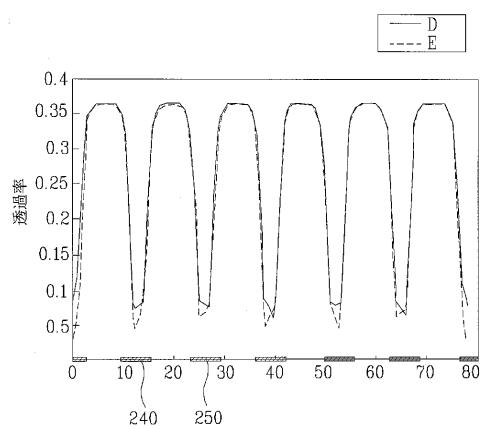

図9は、第2実施例による、電圧による透過率を示すグラフである。

30

## 【0078】

図9を参照すると、Dは、従来の画素領域で共通電極250及び画素電極240下部の保護膜220に溝がない平坦な構造を表し、Eは、画素領域で共通電極250及び画素電極240間の保護膜220に溝が形成された構造を表す。

## 【0079】

同一電圧で、保護膜220に溝がないD構造に比べて、保護膜220に溝が形成されたE構造が、より高い透過率を有することがわかる。すなわち、従来のD構造と比較し、保護膜220に溝が形成されたE構造が同一透過率において低電圧駆動が可能であるということがわかり、よって、消費電力を減少させるという効果を奏する。

40

## 【0080】

図10は、第2実施例による、水平電界を形成する画素電極240及び共通電極250の断面における透過率を示すグラフである。

## 【0081】

ここで、各電極の上部において、画素領域で交互に形成される共通電極250及び画素電極240下部の保護膜220に溝がない平坦なD構造に比べて、保護膜220に溝が形成されたE構造の透過率がより上昇したことがわかる。

## 【0082】

このような薄膜トランジスタ基板の構造及び製造方法は、水平電界を形成するいずれの構造にも適用可能である。

50

**【0083】**

このように、電圧上昇や構造変更なしで保護膜220上に形成された電極間の保護膜220を一定高さにエッチングし、溝を形成することによって、透過効率を増加させ、且つ、同一透過効率を低電圧駆動で得られ、消費電力を減少させることができるという効果を奏する。

**【図面の簡単な説明】****【0084】**

【図1】本発明の第1実施例によるフリンジフィールドスイッチングモードの液晶表示装置の薄膜トランジスタ基板を示す平面図である。

【図2】図1に示すI-I'線に沿った薄膜トランジスタ基板を示す断面図である。

10

【図3A】図2に示す薄膜トランジスタ基板の製造方法を説明するための断面図である。

【図3B】図2に示す薄膜トランジスタ基板の製造方法を説明するための断面図である。

【図3C】図2に示す薄膜トランジスタ基板の製造方法を説明するための断面図である。

【図3D】図2に示す薄膜トランジスタ基板の製造方法を説明するための断面図である。

【図3E】図2に示す薄膜トランジスタ基板の製造方法を説明するための断面図である。

【図4】第1実施例による、電圧による透過率を示すグラフである。

【図5】第1実施例のフリンジ電界を形成する画素電極及び共通電極の断面における透過率を示すグラフである。

【図6】本発明の第2実施例によるインプレーンスイッチングモードの液晶表示装置の薄膜トランジスタ基板を示す平面図である。

20

【図7】図6に示すII-II'線に沿った薄膜トランジスタ基板を示す断面図である。

【図8A】図7に示す薄膜トランジスタ基板の製造方法を説明するための断面図である。

【図8B】図7に示す薄膜トランジスタ基板の製造方法を説明するための断面図である。

【図8C】図7に示す薄膜トランジスタ基板の製造方法を説明するための断面図である。

【図8D】図7に示す薄膜トランジスタ基板の製造方法を説明するための断面図である。

【図9】第2実施例による、電圧による透過率を示すグラフである。

【図10】第2実施例による水平電界を形成する画素電極及び共通電極の断面における透過率を示すグラフである。

**【符号の説明】****【0085】**

30

100 基板、102、202 ゲートライン、104、204 ゲート電極、108

、208 半導体層、120、220 保護膜、140、240 画素電極、150、2

50 共通電極、155、255 共通ライン。

【図1】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図4】

【図5】

【図6】

【図7】

【図8A】

【図 8 B】

【図 8 C】

【図 8 D】

【図 9】

【図 10】

---

フロントページの続き

(72)発明者 李 相 ヨブ

大韓民國京畿道儀旺市五全洞、エルジー・チンドルレ・アパートメント 104-109

審査官 藤田 都志行

(56)参考文献 特開2007-212706 (JP, A)

特開平11-064886 (JP, A)

特開2000-347171 (JP, A)

特開2003-131248 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1343

G02F 1/1368

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置的制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">JP4881368B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2012-02-22 |

| 申请号            | JP2008321419                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2008-12-17 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | Eruji显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 当前申请(专利权)人(译)  | Eruji显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 李相ヨブ°                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 李 相▲ヨブ▼                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | G02F1/133345 G02F1/133371 G02F1/134363 G02F2001/133357 G02F2001/134372                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| FI分类号          | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 2H092/GA13 2H092/GA14 2H092/GA17 2H092/GA29 2H092/JA26 2H092/JA40 2H092/JA44 2H092/JA46 2H092/JB05 2H092/JB24 2H092/JB56 2H092/JB58 2H092/KA05 2H092/KA12 2H092/KA18 2H092/KB04 2H092/KB22 2H092/KB25 2H092/MA04 2H092/MA05 2H092/MA08 2H092/MA10 2H092/MA13 2H092/MA18 2H092/MA19 2H092/MA27 2H092/MA41 2H092/NA01 2H092/NA07 2H092/NA26 2H192/AA24 2H192/BB03 2H192/BB12 2H192/BB13 2H192/BB73 2H192/BC31 2H192/CB05 2H192/CC04 2H192/EA62 2H192/EA66 2H192/HA36 2H192/HA44 2H192/JA32 |         |            |

| 代理人(译)         | 英年古河<br>Kajinami秩序<br>上田俊一                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 优先权            | 1020080067524 2008-07-11 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | JP2010020277A                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

## 摘要(译)

提供一种液晶显示装置。与栅极线交叉以限定像素区域的数据线;在栅极线和数据线的交叉处形成的薄膜晶体管;保护薄膜晶体管的保护膜;，连接到薄膜晶体管的像素电极，用于与像素电极形成电场的公共电极，以及形成在保护膜中的凹槽，其中像素电极和公共电极中的至少一个包括像素区域从而在形成的电极之间的保护膜中形成凹槽，同时彼此分离。

The

## 数 1】

$$V_{th} = \frac{\pi l}{d} \sqrt{\frac{K_{IPS}}{\epsilon_0 \epsilon_r}}$$

## 0 0 4 7】

このように、保護膜1一定高さにエッ칭