(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4567634号

(P4567634)

(45) 発行日 平成22年10月20日(2010.10.20)

(24) 登録日 平成22年8月13日(2010.8.13)

(51) Int.Cl.

F 1

**G02F 1/136 (2006.01)**

**H01L 29/786 (2006.01)**

**H01L 21/336 (2006.01)**

GO2F 1/136

HO1L 29/78 612B

HO1L 29/78 612D

HO1L 29/78 613A

請求項の数 10 (全 32 頁)

(21) 出願番号 特願2006-176575 (P2006-176575)

(22) 出願日 平成18年6月27日 (2006.6.27)

(65) 公開番号 特開2007-133364 (P2007-133364A)

(43) 公開日 平成19年5月31日 (2007.5.31)

審査請求日 平成18年7月14日 (2006.7.14)

(31) 優先権主張番号 10-2005-0106840

(32) 優先日 平成17年11月9日 (2005.11.9)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 501426046

エルジー ディスプレイ カンパニー リ

ミテッド

大韓民国 ソウル, ヨンドゥンパーク, ヨ

イドードン 20

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100096943

弁理士 白井 伸一

(74) 代理人 100101498

弁理士 越智 隆夫

最終頁に続く

(54) 【発明の名称】 液晶表示装置用アレイ基板とその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

表示領域と、第1マスク工程により、前記表示領域の周辺の非表示領域とを有する基板において、前記非表示領域に、第1領域及び前記第1領域の側面の第2領域を有する第1半導体層、及び第3領域と前記第3領域の両側面の第4領域と前記第4領域の両外側面の第5領域とを有する第2半導体層を形成し、前記表示領域に、第6領域と前記第6領域の両側面の第7領域と前記第7領域の両外側面の第8領域とを有する第3半導体層、第4半導体層、及び前記第4半導体層の上部の補助電極で構成される第1ストレージ電極を形成する段階と；

第2マスク工程により、前記第1半導体層の上部に、前記第2領域を露出させる第1ゲート電極と、前記第2半導体層を覆う第1金属パターンと、前記第3半導体層及び補助電極を覆う第2金属パターンと、ゲート配線とを形成し、該第2領域をp+イオンでドーピングする段階と；

第3マスク工程により、前記第1金属パターンをエッチングして前記第2半導体層の第3領域に対応する第2ゲート電極を形成し、前記第2金属パターンをエッチングして前記第3半導体層の第6領域に対応する第3ゲート電極を形成し、そして前記第1ストレージ電極の上部に第2ストレージ電極を形成し、該第5領域及び第8領域をn+イオンで、前記第4領域及び第7領域をn-イオンでドーピングする段階と；

第4マスク工程により、前記第1乃至第3ゲート電極及び前記第2ストレージ電極の上部に、前記第2領域を露出させる第1コンタクトホール及び第2コンタクトホールと、前

10

20

記第5領域を露出させる第3コンタクトホール及び第4コンタクトホールと、前記8領域を露出させる第5コンタクトホール及び第6コンタクトホールとを含む層間絶縁膜を形成する段階と；

第5マスク工程により、前記第1コンタクトホール及び第2コンタクトホールを通じて前記第2領域と各々接触する第1ソース電極及び第1ドレイン電極と、前記第3コンタクトホール及び第4コンタクトホールを通じて前記第5領域と各々接触する第2ソース電極及び第2ドレイン電極と、前記第5コンタクトホール及び第6コンタクトホールを通じて前記第8領域と各々接触する第3ソース電極及び第3ドレイン電極と、前記第3ドレイン電極から延長した、前記第2ストレージ電極の上部に位置する第3ストレージ電極と、前記ゲート配線と交差して前記表示領域に画素領域を定義するデータ配線と、前記第3ストレージ電極から延長した、前記画素領域に位置する画素電極とを形成する段階とを含むことを特徴とする液晶表示装置用アレイ基板の製造方法。10

#### 【請求項2】

前記第1乃至第3ソース電極と前記第1乃至第3ドレイン電極と前記第3ストレージ電極とは透明電極と不透明電極を含み、前記画素電極は前記第3ドレイン電極の透明電極から延長されることを特徴とする請求項1に記載の液晶表示装置用アレイ基板の製造方法。

#### 【請求項3】

前記層間絶縁膜を形成する段階は、

酸化シリコンで構成される第1層間絶縁膜を形成する段階と；

前記第1層間絶縁膜上に、窒化シリコンで構成される第2層間絶縁膜を形成する段階とを含むことを特徴とする請求項1に記載の液晶表示装置用アレイ基板の製造方法。20

#### 【請求項4】

前記第1層間絶縁膜が形成された基板を加熱する段階をさらに含むことを特徴とする請求項3に記載の液晶表示装置用アレイ基板の製造方法。

#### 【請求項5】

前記第1乃至第4半導体層と前記第1ストレージ電極を形成する段階は、

多結晶シリコン層と、第1伝導性金属層と、第1フォトレジスト層とを形成する段階と；

第1部分と、前記第1部分の透過率より小さい透過率を有する第2部分と、前記第2部分の透過率より小さい透過率を有する第3部分とで構成される第1マスクを前記第1フォトレジスト層の上部に配置する段階と；30

前記第1フォトレジスト層を露光及び現像することによって、第1フォトレジストパターンと第2フォトレジストパターン間と前記第2フォトレジストパターンと第3フォトレジストパターン間とで前記第1伝導性金属層が露出するように、前記非表示領域に、相互に離隔する前記第1フォトレジストパターン及び第2フォトレジストパターンを、前記表示領域に、前記第3フォトレジストパターンと前記第3フォトレジストパターンとから延長した、前記第1乃至第3フォトレジストパターンより高い高さを有する第4フォトレジストパターンを形成する段階と；

前記第1フォトレジストパターン及び第2フォトレジストパターンの間と前記第2フォトレジストパターン及び第3フォトレジストパターンの間との第1伝導性金属層及び前記多結晶シリコン層を除去することによって、前記第1フォトレジスト層の下部の第1金属パターン及び第1半導体層と、前記第2フォトレジストパターンの下部の第2金属パターン及び第2半導体層と、前記第3フォトレジストパターンの下部の第3金属パターン及び第3半導体層と、前記第4フォトレジストパターンの下部の補助電極及び第4半導体層とを形成する段階と；40

前記第1乃至第3フォトレジストパターンをアッシングして、前記第1乃至第3金属パターンを露出させる段階と；

前記第1乃至第3金属パターン及び前記第4フォトレジストパターンを除去する段階とを含むことを特徴とする請求項1に記載の液晶表示装置用アレイ基板の製造方法。

#### 【請求項6】

前記基板と前記多結晶シリコン層との間にバッファ層を形成する段階をさらに含むことを特徴とする請求項5に記載の液晶表示装置用アレイ基板の製造方法。

**【請求項 7】**

前記第1ゲート電極、前記第1金属パターン及び第2金属パターンを形成する段階は、前記第1乃至第3半導体層と前記補助電極上に、ゲート絶縁膜と第2伝導性金属層と第2フォトレジスト層とを形成する段階；

第4部分と前記第4部分より大きい透過率を有する第5部分とで構成された第2マスクを利用して前記第2フォトレジスト層を露光及び現像することによって、前記第1半導体層より小さい大きさの第5フォトレジストパターンと、前記第2半導体層に対応する第6フォトレジストパターンと、前記第3半導体層及び第4半導体層に対応する第7フォトレジストパターンとを形成する段階；

10

前記第5フォトレジストパターン及び第6フォトレジストパターン間と前記第6フォトレジストパターン及び第7フォトレジストパターン間との第2伝導性金属層を除去することによって、前記第1ゲート電極と、前記第1金属パターン及び第2金属パターンとを形成する段階を含むことを特徴とする請求項1に記載の液晶表示装置用アレイ基板の製造方法。

**【請求項 8】**

前記第2ゲート電極及び第3ゲート電極と前記第2ストレージ電極とを形成する段階と、前記第5領域及び第8領域と前記第4領域及び第7領域とをドーピングする段階とは、前記第1ゲート電極と前記第1金属パターン及び第2金属パターンの上に第3フォトレジスト層を形成する段階；

20

第3マスクを利用して前記第3フォトレジスト層を露光及び現像することによって、前記第1半導体層を覆う第8フォトレジストパターンと、前記第2半導体層の第3領域及び第4領域に対応する第9フォトレジストパターンと、前記第3半導体層の第6領域及び第7領域に対応する第10フォトレジストパターンと、前記第4半導体層を覆う第11フォトレジストパターンとを形成する段階；

前記第8乃至第11フォトレジストパターン間の前記第1金属パターン及び第2金属パターンを除去する段階と；

前記第2半導体層の第5領域及び前記第3半導体層の第8領域にn+イオンをドーピングする段階と；

30

前記第8乃至第11フォトレジストパターンをアッシングすることによって、前記第2半導体層の第4領域に対応する前記第2金属パターンと、前記第3半導体層の第7領域に対応する前記第2金属パターンと、前記補助電極に対応するように前記第2金属パターンの両一端を露出させる段階と；

前記第8乃至第11フォトレジストパターンをアッシングする段階によって露出された第1金属パターン及び第2金属パターンを除去することにより、前記第2半導体層の第3領域に対応する第2ゲート電極と、前記第3半導体層の第6領域に対応する第3ゲート電極と、前記補助電極に対応する第2ストレージ電極とを形成する段階と；

前記第2半導体層の第4領域と前記第3半導体層の第7領域にn-イオンをドーピングする段階と；

40

前記第8乃至第11フォトレジストパターンを除去する段階とを含むことを特徴とする請求項1に記載の液晶表示装置用アレイ基板の製造方法。

**【請求項 9】**

前記第1乃至第3ソース電極と前記第1乃至第3ドレイン電極と前記第3ストレージ電極と前記画素電極とを形成する段階は、

前記層間絶縁膜上に、透明電極層と、第3伝導性金属層と、第4フォトレジスト層を形成する段階と；

前記第4フォトレジスト層上に、第6部分と、前記第6部分より小さい透過率を有する第7部分と、前記第7部分より小さい透過率を有する第8部分とで構成された第4マスクを配置する段階と；

50

前記第4マスクを利用して前記第4フォトレジスト層を露光及び現像することによって、前記層間絶縁膜の第1コンタクトホール及び第2コンタクトホールの上部に第12フォトレジストパターンを、前記層間絶縁膜の第3コンタクトホールと第4コンタクトホールの上部に第13フォトレジストパターンを、前記層間絶縁膜の第5コンタクトホールと第6コンタクトホールの上部に第14フォトレジストパターンを、前記第2ストレージ電極の上部に第15フォトレジストパターンを、そして前記画素領域に第12乃至第15フォトレジストパターンより低い高さを有する、前記第15フォトレジストパターンから延長される第16フォトレジストパターンを形成する段階と；

前記第12乃至第15フォトレジストパターン間の第3伝導性金属層と透明電極層を除去することによって、前記第1コンタクトホール及び第2コンタクトホールを通じて第1半導体層の第2領域と各々接触する前記第1ソース電極及び第1ドレイン電極と、前記第3コンタクトホール及び第4コンタクトホールを通じて第2半導体層の第5領域と各々接触する前記第2ソース電極及び第2ドレイン電極と、前記第5コンタクトホール及び第6コンタクトホールを通じて第3半導体層の第8領域と各々接触する前記第3ソース電極及び第3ドレイン電極とを形成する段階と；

前記画素領域の第3伝導性金属層が露出するように前記第12乃至第16フォトレジストパターンをアッシングする段階と；

前記画素領域の第3伝導性金属層を除去することによって、前記第2ストレージ電極の上部の第3ストレージ電極と前記画素領域に前記画素電極を形成する段階とを含むことを特徴とする請求項1に記載の液晶表示装置用アレイ基板の製造方法。

#### 【請求項10】

前記第3ドレイン電極と第3ストレージ電極は透明電極と不透明電極を含み、前記画素電極は前記透明電極から延長されることを特徴とする請求項9に記載の液晶表示装置用アレイ基板の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、液晶表示装置に係り、特に、駆動回路一体型の液晶表示装置用アレイ基板とその製造方法に関する。

##### 【背景技術】

##### 【0002】

一般的な液晶表示装置は、薄膜トランジスタTFTを含むアレイ基板とカラーフィルター基板間に液晶を注入して、この液晶の異方性による光の屈折率の差を利用してイメージを得る表示装置である。

このような表示装置のスイッチング素子として使用される薄膜トランジスタは、アレイ部の設計によって多様な形態で構成できて、特に、アクティブ層として使用される半導体層には、非晶質シリコンまたは、多結晶シリコン（ポリシリコン）を使用する。

この時、一般的なスイッチング素子としては、水素化された非晶質シリコン（a-Si:H）が主に利用されるが、これは、低温工程が可能であって、低価の絶縁基板が使用できるからである。

ところが、水素化された非晶質シリコンは、原子配列が無秩序であるために、弱い結合（weak Si-Si bond）及びダングリングボンド（dangling bond）が存在して、光の照射や電場の印加時、準安定状態に変化され、薄膜トランジスタ素子として活用時、安定性が問題になっており、電気的特性（低い電界効果の移動度：0.1～1.0 cm<sup>2</sup>/V・s）が良くなないので、駆動回路としては、使用し難い。

一方、ポリシリコンは、非晶質シリコンに比べて、電界効果と移動度が大きいので、基板上に、駆動回路が形成できて、ポリシリコンを利用して、基板に直接駆動回路を形成すると、実装が大変簡単になり、液晶パネルがさらにコンパクトに製作できる長所がある。

##### 【0003】

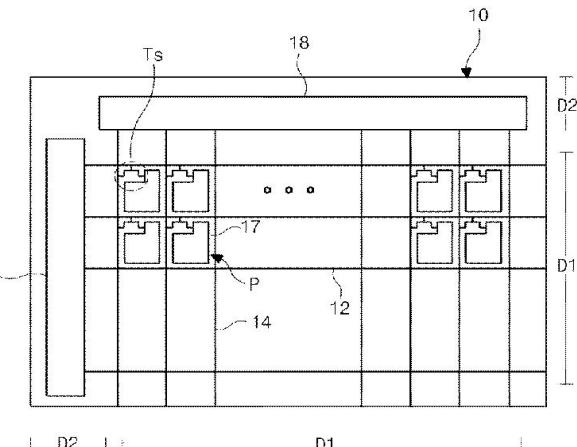

図1は、従来技術による液晶表示装置用アレイ基板を概略的に示した平面図である。

10

20

30

40

50

図1に示したように、第1基板10は、表示領域D1と非表示領域D2で定義されて、表示領域D1には、多数の画素領域Pがマトリックス状に位置して、各画素ごとにスイッチング素子T及びこれに連結された画素電極17が構成される。

また、画素領域Pの一側に沿って延長されたゲート配線12と、これとは垂直に交差するデータ配線14が構成される。

#### 【0004】

非表示領域D2には、駆動回路部16、18が構成されるが、駆動回路部16、18は、第1基板10の一側に位置して、ゲート配線12に信号を印加するゲート駆動回路部16と、これとは平行ではない第1基板10の他側に位置して、データ配線14に信号を印加するデータ駆動回路部18を含む。10

ゲート駆動回路部16及びデータ駆動回路部18は、外部から入力された信号を調節し、各々ゲート配線12及びデータ配線14を通じて画素部Pに、ディスプレーコントロール信号及びデータ信号を供給するための装置である。

従って、ゲート駆動回路部16及びデータ駆動回路部18は、入力される信号を適切に出力させるために、一般的には、インバーターであるCMOS(Complementary Metal-Oxide Semiconductor)構造の薄膜トランジスタで構成される。

#### 【0005】

CMOSは、高速信号処理が要求される駆動回路部薄膜トランジスタに使用される半導体技術の一種であって、陰電気で充電された余分の電子等(n型の半導体)と陽電気で充電された正孔等(p型の半導体)を利用して1つの伝導体を形成し、相互補完的な方法として、2種類の半導体の効果的な電気制御に使用される。20

このように、非表示領域の駆動回路部を構成するCMOS素子は、n型及びp型の多結晶薄膜トランジスタの組合で構成されて、表示領域のスイッチング素子は、n型及びp型の多結晶薄膜トランジスタで構成される。

#### 【0006】

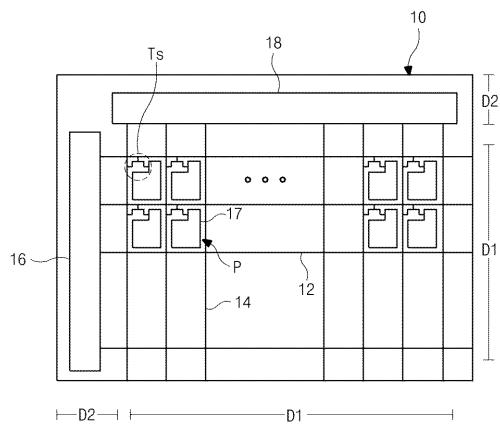

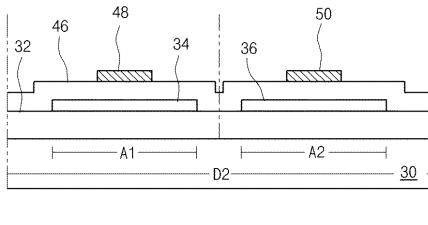

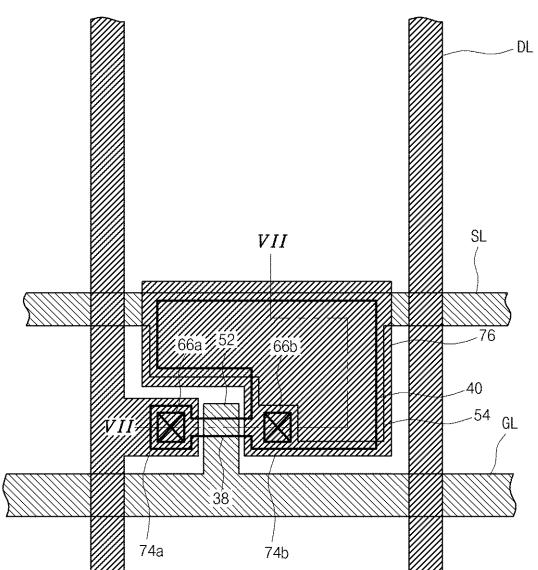

図2は、従来技術による液晶表示装置用アレイ基板の一部を拡大した平面図である。

図2に示したように、基板30の一面に、第1方向に、ゲート配線GLが構成されて、ゲート配線GLと交差して、画素領域Pを定義するデータ配線DLが構成される。

ゲート配線GL及びデータ配線DLの交差部には、ゲート電極52とアクティブ層(38、多結晶シリコン層)と、ソース電極74aとドレイン電極74bとで構成された多結晶の薄膜トランジスタTが構成されて、画素領域Pには、ドレイン電極74bと接触する画素電極82が構成される。30

また、画素領域Pには、第1ストレージ電極40、第2ストレージ電極54、第3ストレージ電極76で形成されたストレージキャパシターCstが構成される。

前述のような構成は、液晶パネルの表示領域の一部を示しており、このような形状が連続され表示領域を構成する。

#### 【0007】

前述した表示装置の周辺に、駆動回路部(図1の16、18)を形成して、駆動回路部(図1の16、18)には、ゲート配線GL及びデータ配線DLに信号を伝達するための駆動回路(図示せず)が形成される。40

駆動回路(図示せず)は、多結晶薄膜トランジスタTの組合によって構成されて、駆動の特性が速くて、漏洩電流を有しないようにするために、n型の多結晶薄膜トランジスタTも、前述したように、CMOSトランジスタの組合によって形成することができる。

#### 【0008】

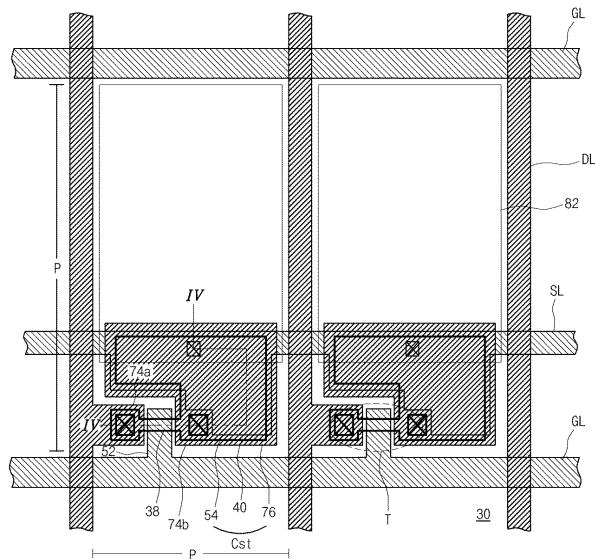

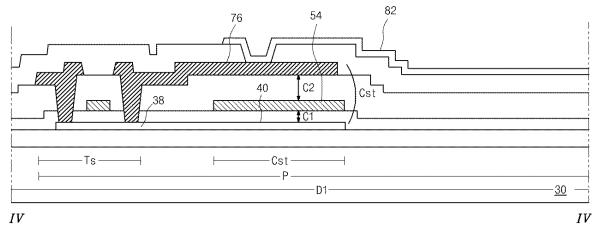

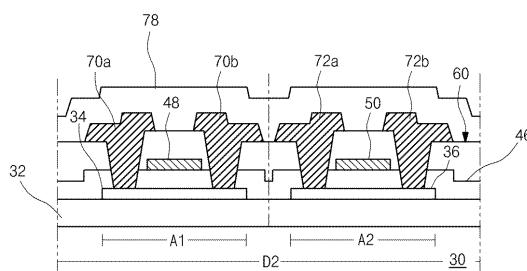

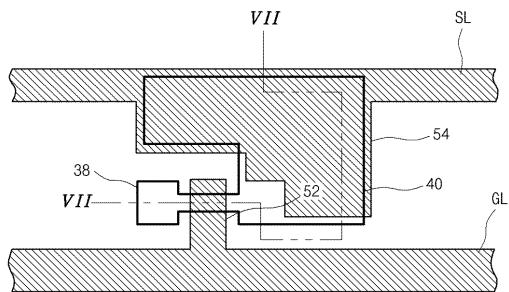

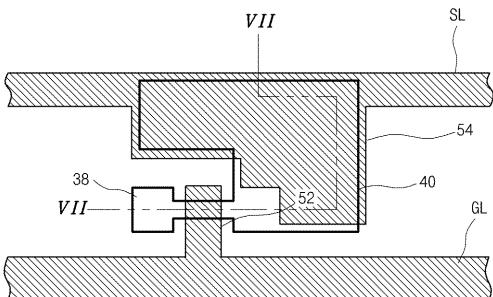

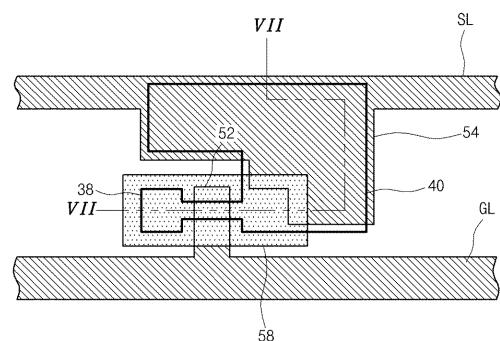

図3は、従来技術による駆動回路部の断面図であって、図4は、図2のI-I'I線に沿って切断したアレイ基板の表示領域の断面図である。

図3と図4に示したように、非表示領域D2に構成した駆動回路DCは、CMOS薄膜トランジスタTの組合によって構成されて、CMOS薄膜トランジスタTは、n型の薄膜トランジスタTnとp型の薄膜トランジスタTpの組合によって構成される。

表示領域D1に構成された単一画素領域Pは、スイッチング素子Tsと、これと接触し50

ながら画素領域 P 全面に形成された画素電極 8 2 と、補助容量部であるストレージキャパシター Cst が形成される。

この時、表示領域 P に使用するスイッチング素子 T s は、n 型または、p 型の多結晶薄膜トランジスタを使用するが、一般的には、n 型の多結晶薄膜トランジスタを使用する。

#### 【 0 0 0 9 】

ストレージキャパシター Cst は、第 1 ストレージ電極 4 0 、第 2 ストレージ電極 5 4 、第 3 ストレージ電極 7 6 で形成されて、等価回路的には、2 つのキャパシター C 1 、C 2 が直列連結された状態である。

このような構成は、領域を拡大しなくても、補助容量がさらに確保できる長所がある。

#### 【 0 0 1 0 】

前述したような構成の駆動回路一体型の液晶表示装置用アレイ基板は、一般的に、ストレージキャパシター Cst を形成するためのドーピング工程と、n 型の多結晶薄膜トランジスタ T n を形成するための n + イオンドーピング工程と、p 型の多結晶薄膜トランジスタ T p を形成するための p + イオンドーピング工程を含む 9 マスク工程を必要とする。

以下、工程図面を参照して、従来による駆動回路一体型の液晶表示装置用アレイ基板の製造方法を説明する。

#### 【 0 0 1 1 】

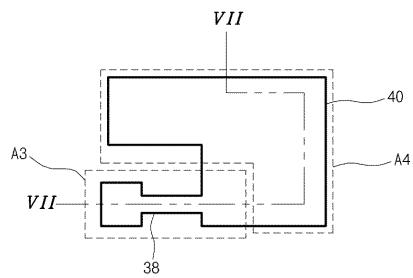

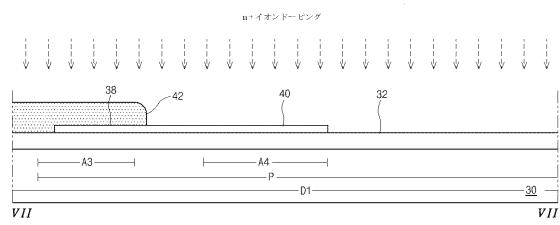

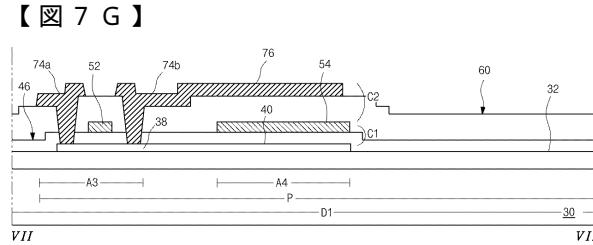

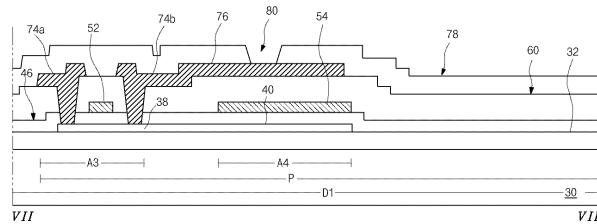

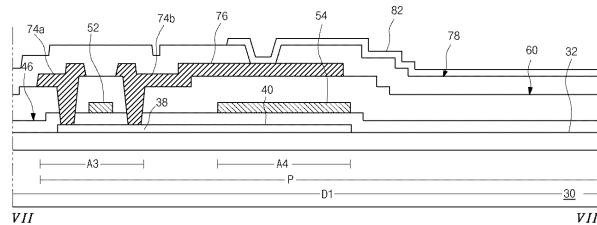

図 5 A ないし図 5 I は、従来技術によって駆動回路部を製造する工程を示した工程断面図であって、図 6 A ないし図 6 I は、従来技術によってアレイ基板の表示領域を製造する工程を示した断面図であり、図 7 A ないし図 7 I は、各々図 5 A ないし図 5 I の V I - V I 線に沿って切断した部分の製造工程を示した断面図である。

#### 【 0 0 1 2 】

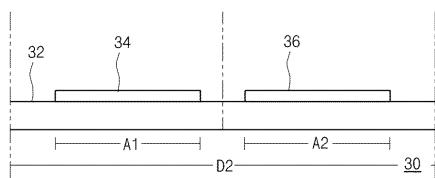

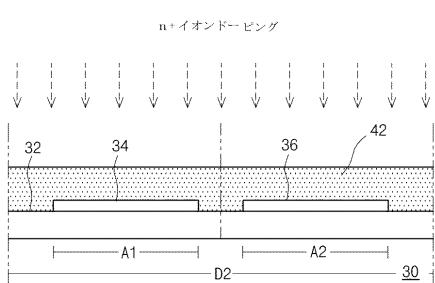

図 5 A と図 6 A と図 7 A は、第 1 マスク工程を示した図である。

図 5 A と図 6 A と図 7 A に示したように、第 1 基板 3 0 に表示領域 D 1 と非表示領域 D 2 が定義されて、表示領域 D 1 には、多数の画素領域 P が定義される。

この時、非表示領域 D 2 に、便宜上、第 1 領域 A 1 と第 2 領域 A 2 を定義して、画素領域 P に、第 3 領域 A 3 と第 4 領域 A 4 を定義する。

前述したように、第 1 ないし第 4 領域 A 1 、A 2 、A 3 、A 4 が定義された第 1 基板 3 0 の一面に、絶縁物質を蒸着してバッファ層 3 2 を形成し、バッファ層 3 2 の上部に非晶質シリコン ( a - S i : H ) を蒸着した後、結晶化する工程を行う。一般的には、レーザーを利用して結晶化を行う。

結晶化工程によって結晶化された層をパターンし、第 1 領域 A 1 と第 2 領域 A 2 と第 3 領域 A 3 に、アクティブ層として機能する第 1 ないし第 3 多結晶半導体層 3 4 、3 6 、3 8 を形成して、第 4 領域 A 4 に、第 1 ストレージ電極として機能する第 4 多結晶半導体層 4 0 を形成する。

この時、第 3 多結晶半導体層 3 8 と第 4 多結晶半導体層 4 0 は、一体に形成することができる。

#### 【 0 0 1 3 】

図 5 B と図 6 B と図 7 B は、第 2 マスク工程を示しており、第 4 領域 A 4 の第 4 多結晶半導体層 4 0 にイオンをドーピングする工程を示した図である。

図 5 B と図 6 B と図 7 B に示したように、第 1 ないし第 4 多結晶半導体層 3 4 、3 6 、3 8 、4 0 が形成された基板 3 0 全面に、フォトレジストを塗布した後、第 2 マスク工程によってパターンし、第 1 領域 A 1 と第 2 領域 A 2 及び第 3 領域 A 3 を遮蔽する第 1 フォトレジストパターン 4 2 を形成する。

第 1 フォトレジストパターン 4 2 によって遮蔽されない第 4 領域 A 4 の第 4 多結晶半導体層 4 0 の表面に、n + イオンをドーピングする工程を行う。

第 4 多結晶半導体層 4 0 は、電極の役割をして、低い抵抗を有するために、イオン ( n または、p 型のイオン ) をドーピングする工程を行う。イオンドーピング工程が完了されると、第 1 フォトレジストパターン 4 2 を除去する工程を行う。

#### 【 0 0 1 4 】

図5Cと図6Cと図7Cは、第3マスク工程を示した断面図である。

図5Cと図6Cと図7Cに示したように、第4A4の第4多結晶半導体層40にイオンをドーピングする工程後、第1ないし第4多結晶半導体層34、36、38、40が形成された基板30にゲート絶縁膜46を形成する。

ゲート絶縁膜46は、窒化シリコンSiNxと酸化シリコンSiO<sub>2</sub>を含む無機絶縁物質グループのうちから選択された1つ以上の物質を蒸着して形成する。

ゲート絶縁膜46が形成された基板30全面に、導電性金属を蒸着して第3マスク工程によってパターンし、第1ないし第3多結晶半導体層34、36、38の中心に対応する上部に第1ないし第3ゲート電極48、50、52を形成して、第4領域A4の第4多結晶半導体層40に対応する上部に第2ストレージ電極54を形成すると同時に、第3領域A3に構成した第3ゲート電極52から延長され、画素領域Pの一側に位置するようにゲート配線GLを形成して、第2ストレージ電極54から延長され画素領域Pを横切るストレージ配線SLを形成する。

10

#### 【0015】

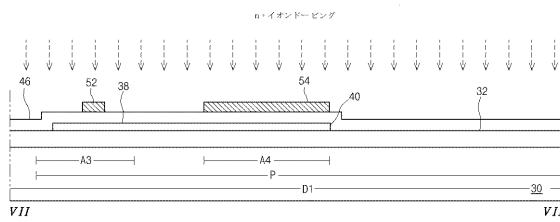

図5Dと図6Dと図7Dは、第4マスク工程を示しており、第2領域A2と第3領域A3の第2多結晶半導体層36及び第3多結晶半導体層38に、n+イオンをドーピングするための工程断面図である。

図5Dと図6Dと図7Dに示したように、第1ないし第3電極48、50、52と第2ストレージ電極54とゲート配線(図示せず)が形成された第1基板30全面にフォトレジストを塗布した後、第4マスク工程によってパターンし、第1領域A1を覆う第2フォトレジストパターン56を形成する。

20

第2フォトレジストパターン56間に露出された第2領域A2と第3領域A3にn+イオンをドーピングする工程を行う。

第2領域A2と第3領域A3の第2半導体層36と第3半導体層38領域の第2ゲート電極50と第3ゲート電極52の周辺に露出された表面にn+イオンがドーピングされて、イオンがドーピングされた領域は、抵抗性接触(ohmic contact)の特性を有する。

前述したような第4マスク工程が完了すると、第2フォトレジストパターン56を除去する工程を行う。

#### 【0016】

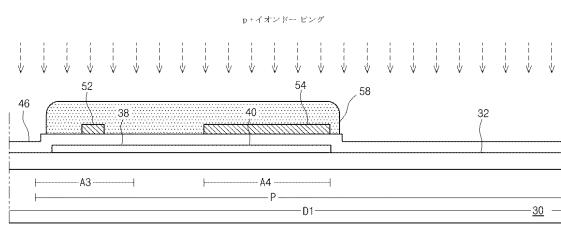

図5Eと図6Eと図7Eは、第5マスク工程を示しており、第1領域A1の半導体層にp+イオンをドーピングするための工程断面図である。

30

図5Eと図6Eと図7Eに示したように、第1ないし第3ゲート電極48、50、52と第2ストレージ電極54が形成された第1基板30にフォトレジストを塗布した後、第5マスク工程によってパターンし、第2領域A2と第3領域A3及び第4領域A4を覆う第3フォトレジストパターン58を形成する。

ここで、第4領域A4は、もう第2ストレージ電極54が形成された状態であるので、フォトレジストパターンを形成しなくても良い。

第1領域A1の露出された第1半導体層34のゲート電極48の周辺に露出された表面にp+イオンをドーピングする工程を行う。この時、イオンがドーピングされた領域は、前述したように、抵抗性接触(ohmic contact)の特性を有する。

40

#### 【0017】

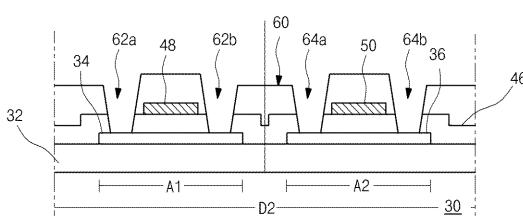

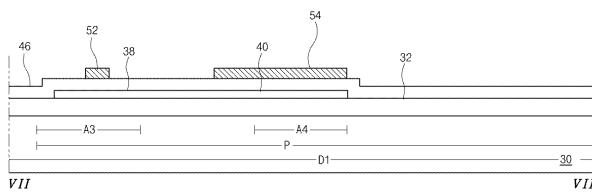

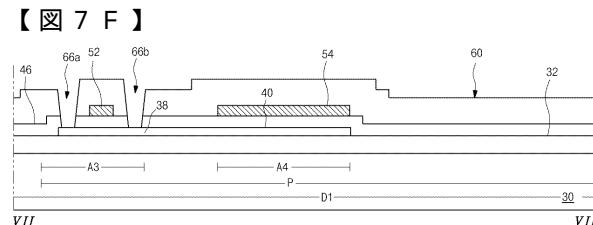

図5Fと図6Fと図7Fは、第6マスク工程を示した工程断面図である。

前述したように、第1ないし第3半導体層34、36、38にイオンをドーピングして抵抗性接触領域(以下、オーミックコンタクト領域と称する。)の形成工程が行われれた第1基板30に、窒化シリコンSiNxと酸化シリコンSiO<sub>2</sub>を含む無機絶縁物質グループのうちから選択された1つを蒸着して層間絶縁膜60を形成する。

層間絶縁膜60とその下部のゲート絶縁膜46を第6マスク工程によってパターンし、第1ないし第3半導体層34、36、38のオーミックコンタクト領域を各々露出する多数のコンタクトホール62a、62b、64a、64b、66a、66bを形成する。

#### 【0018】

10

20

30

40

50

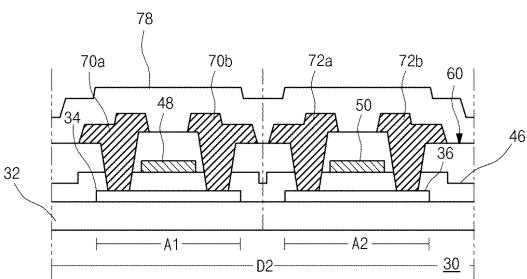

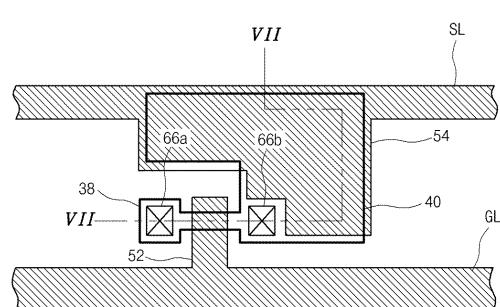

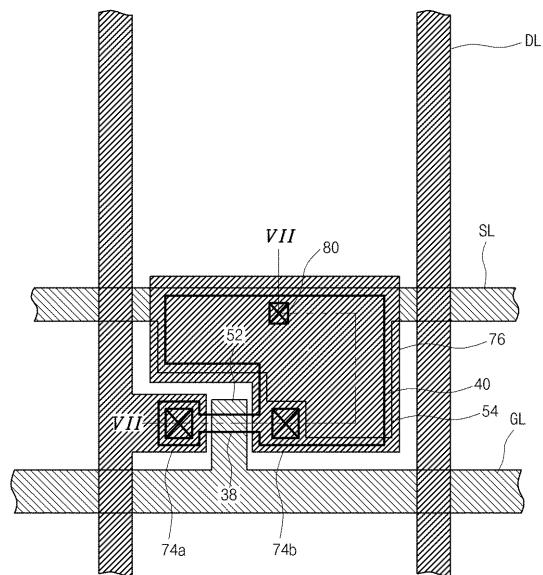

図5Gと図6Gと図7Gは、第7マスク工程を示した工程断面図である。

第1ないし第3半導体層34、36、38のオーミックコンタクト領域の一部を露出する層間絶縁膜60が形成された基板30全面に、クロムCr、モリブデンMo、タンゲステンW、銅Cu、アルミニウム合金AlNd等を含む伝導性金属グループのうちから選択された1つを蒸着してパターンし、露出されたオーミックコンタクト領域と各々接触する多数のソース電極70a、72a、74aと多数のドレイン電極70b、72b、74bを形成する。

この時、第3領域A3に構成したドレイン電極74bから第4領域A4に延長された延長部をさらに形成して、これは、第3ストレージ電極76としての役割をする。また、表示領域D1の第3領域A3に形成したソース電極74aから延長され、ゲート配線GLと交差して画素領域Pの一側に延長されたデータ配線DLを形成する。

10

前述した第1ないし第7マスク工程によって、非表示領域D2には、p型の多結晶薄膜トランジスタとn型の多結晶薄膜トランジスタの組合であるCMOS素子が形成され、表示領域D1の第3領域A3には、n型の多結晶薄膜トランジスタが形成され、第4領域A4には、第1ないし第3ストレージ電極40、54、76で構成された第1ストレージキャパシターC1及び第2ストレージキャパシターC2が形成される。

#### 【0019】

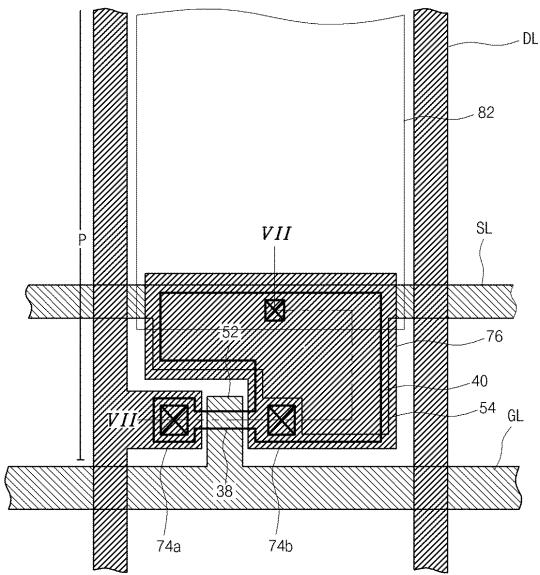

図5Hと図6Hと図7Hは、第8マスク工程を示した工程断面図である。

図5Hと図6Hと図7Hに示したように、各領域A1、A2、A3ごとに多数のソース電極70a、72a、74aと多数のドレイン電極70b、72b、74bが形成された第1基板30全面に、前述した絶縁物質グループのうちから選択された1つ以上の物質を蒸着して保護層78を形成する。

20

保護層78を第8マスク工程によってパターンし、第3領域A3のドレイン電極74bまたは、第3ストレージ電極76を露出するドレインコンタクトホール80を形成する。

#### 【0020】

図5Iと図6Iと図7Iは、第9マスク工程を示した工程断面図である。

図5Iと図6Iと図7Iに示したように、保護層78が形成された第1基板30全面に、インジウムースズーオキサイドITOとインジウムージンクーオキサイドIZOを含む透明な伝導性金属グループのうちから選択された1つを蒸着して、第9マスク工程によってパターンし、ドレイン電極74bまたは、これに延長された第3ストレージ電極76と接触しながら画素領域Pに位置する画素電極82を形成する。

30

以上、前述したような第1ないし第9マスク工程によって、従来による駆動回路一体型の液晶パネルの薄膜トランジスタアレイ基板を製作することができる。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0021】

従って、従来には、多数の工程によって駆動回路一体型のアレイ基板を製作するために、工程時間の遅延と生産費用の増加により工程収率が低下される問題がある。また、多数の工程による不良発生率を高める短所がある。

#### 【課題を解決するための手段】

#### 【0022】

本発明は、前述した問題を解決するために提案されており、工程数を減少させて工程時間を短縮し、工程費用を低下させると同時に、不良発生確率を低めて生産収率を高めることを目的とする。

40

#### 【0023】

前述のような目的を達成するために、本発明は、表示領域と、表示領域の周辺の非表示領域を含む基板と；非表示領域に形成された駆動回路と；表示領域に形成された第1薄膜トランジスタと；第1半導体層と第1半導体層の上部の補助電極で構成された第1ストレージ電極と、第1ストレージ電極の上部の第2ストレージ電極と、透明電極パターンと透明電極パターンの上部の第1金属パターンで構成されて、第2ストレージ電極の上部に形

50

成される第3ストレージ電極を含み、表示領域に形成されたストレージキャパシターと；相互に交差して表示領域に画素領域を定義するゲート配線及びデータ配線と；第1薄膜トランジスタに連結されて、画素領域に形成される画素電極とを含む液晶表示装置用アレイ基板を提供する。

**【0024】**

第1薄膜トランジスタは、第1領域、第1領域の両側面の第2領域及び第2領域の両側面の第3領域を有する第2半導体層と、ゲート配線から延長された第1ゲート電極と、データ配線から延長された第1ソース電極と、第1ソース電極と離隔された第1ドレン電極を含み、第2領域には、n-イオンがドーピングされ、第3領域には、n+イオンがドーピングされて、第1ソース電極及び第1ドレン電極各々は、第3領域に接触されて、第1ソース電極及び第1ドレン電極各々は、透明電極と透明電極の上部の不透明電極を含む。また、第1半導体層は、第2半導体層と同一層に形成されて、第2半導体層から延長され、第1ソース電極及び第1ドレン電極は、第3ストレージ電極と同一層に形成される。10

**【0025】**

さらに、駆動回路は、第2薄膜トランジスタと第3薄膜トランジスタを含み、第2薄膜トランジスタは、第4領域、第4領域の両側面の第5領域を有する第2半導体層と、第2ゲート電極と、第2ソース電極及び第2ドレン電極を含んで、第4領域には、p+イオンがドーピングされ、第2ソース電極及び第2ドレン電極各々は、第5領域に接触される。20

**【0026】**

第2ソース電極及び第2ドレン電極各々は、透明電極と透明電極の上部の不透明電極を含み、第1半導体層は、第3半導体層と同一層に形成される。また、第2ソース電極及び第2ドレン電極は、第3ストレージ電極と同一層に形成される。

**【0027】**

第3薄膜トランジスタは、第6領域、第6領域の両側面の第7領域、第7領域の両外側面の第8領域を有する第4半導体層と、第3ゲート電極と、第3ソース電極及び第3ドレン電極を含み、第7領域には、n-イオンがドーピングされ、第8領域には、n+イオンがドーピングされる。

**【0028】**

第3ソース電極及び第3ドレン電極各々は、第8領域に接触されて、第3ソース電極及び第2ドレン電極各々は、透明電極と透明電極の上部の不透明電極を含み、第1半導体層は、第4半導体層と同一層に形成されて、第3ソース電極及び第3ドレン電極は、第3ストレージ電極と同一層に形成される。30

**【0029】**

また、本発明は、表示領域と、表示領域の周辺の非表示領域を有する基板において、非表示領域に、第1領域及び第1領域の側面の第2領域を有する第1半導体層と、第3領域、第3領域の両側面の第4領域及び第4領域両外側面の第5領域を有する第2半導体層を形成して、表示領域に、第6領域、第6領域の両側面の第7領域及び第7領域の両外側面の第8領域を有する第3半導体層と、第4半導体層と、第4半導体層の上部の補助電極で構成される第1ストレージ電極を形成する段階と；第1半導体層の上部に、第2領域を露出させる第1ゲート電極と、第2半導体層を覆う第1金属パターンと、第3半導体層及び補助電極を覆う第2金属パターンと、ゲート配線を形成する段階と；第2領域に、p+イオンをドーピングする段階と；第1金属パターンをエッチングして、第2半導体層の第3領域に対応する第2ゲート電極と、第2金属パターンをエッチングして、第3半導体層の第6領域に対応する第3ゲート電極と、第1ストレージ電極の上部に、第2ストレージ電極を形成する段階と；第5領域及び第8領域に、n+イオンを、第4領域及び第7領域に、n-イオンをドーピングする段階と；第1ないし第3ゲート電極及び第2ストレージ電極の上部に、第2領域を露出させる第1コンタクトホール及び第2コンタクトホールと、第5領域を露出させる第3コンタクトホール及び第4コンタクトホールと、8領域を露出4050

させる第5コンタクトホール及び第6コンタクトホールを含む層間絶縁膜を形成する段階と；第1コンタクトホール及び第2コンタクトホールを通じて第2領域と各々接触する第1ソース電極及び第1ドレイン電極と、第3コンタクトホール及び第4コンタクトホールを通じて第5領域と各々接触する第2ソース電極及び第2ドレイン電極と、第5コンタクトホール及び第6コンタクトホールを通じて第8領域と各々接触する第3ソース電極及び第3ドレイン電極と、第3ドレイン電極から延長されて、第2ストレージ電極の上部に位置する第3ストレージ電極と、ゲート配線と交差して表示領域に画素領域を定義するデータ配線と、第3ストレージ電極から延長されて、画素領域に位置する画素電極を形成する段階とを含む液晶表示装置用アレイ基板の製造方法を提供する。

## 【0030】

10

第1ないし第3ソース電極と第1ないし第3ドレイン電極と第3ストレージ電極は、透明電極と不透明電極を含み、画素電極は、第3ドレイン電極の透明電極から延長される。

また、層間絶縁膜の形成段階は、酸化シリコンで構成される第1層間絶縁膜を形成する段階と；第1層間絶縁膜上に、窒化シリコンで構成される第2層間絶縁膜を形成する段階を含み、第1層間絶縁膜が形成された基板を加熱する段階をさらに含む。

## 【0031】

20

第1ないし第4半導体層と第1ストレージ電極を形成する段階は、多結晶シリコン層と、第1伝導性金属層と、第1フォトレジスト層を形成する段階と；第1部分と、第1部分の透過率より小さい透過率を有する第2部分と、第2部分の透過率より小さい透過率を有する第3部分で構成される第1マスクを第1フォトレジスト層の上部に配置する段階と；第1フォトレジスト層を露光、現像することによって、第1フォトレジストパターンと第2フォトレジストパターン間と、第2フォトレジストパターンと第3フォトレジストパターン間で、第1伝導性金属層が露出されるように、非表示領域に、相互に離隔する第1フォトレジストパターン及び第2フォトレジストパターンと、表示領域に、第3フォトレジストパターンと第3フォトレジストパターンから延長されて、第1ないし第3フォトレジストパターンより高い高さを有する第4フォトレジストパターンを形成する段階と；第1フォトレジストパターンと第2フォトレジストパターン間と、第2フォトレジストパターンと第3フォトレジストパターン間の第1伝導性金属層及び多結晶シリコン層を除去することによって、第1フォトレジスト層の下部の第1金属パターン及び第1半導体層と、第2フォトレジストパターンの下部の第2金属パターン及び第2半導体層と、第3フォトレジストパターンの下部の第3金属パターン及び第3半導体層と、第4フォトレジストパターンの下部の補助電極及び第4半導体層を形成する段階と；第1ないし第3フォトレジストパターンをアッシングして、第1ないし第3金属パターンを露出させる段階と；第1ないし第3金属パターン及び第4フォトレジストパターンを除去する段階とを含むことを特徴として、基板と多結晶シリコン層間に、バッファ層を形成する段階をさらに含む。

30

## 【0032】

40

第1ゲート電極、第1金属パターン及び第2金属パターンを形成する段階は、第1ないし第3半導体層と補助電極上に、ゲート絶縁膜と、第2伝導性金属層と第2フォトレジスト層を形成する段階と；第4部分と、第4部分より大きい透過率を有する第5部分で構成されたた第2マスクを利用して第2フォトレジスト層を露光、現像することによって、第1半導体層より小さい大きさの第5フォトレジストパターンと、第2半導体層に対応する第6フォトレジストパターンと、第3半導体層及び第4半導体層に対応する第7フォトレジストパターンを形成する段階と；第5フォトレジストパターン及び第6フォトレジストパターンと第6フォトレジストパターン及び第7フォトレジストパターン間の第2伝導性金属層を除去することによって、第1ゲート電極と、第1金属パターン及び第2金属パターンを形成する段階を含む。

## 【0033】

50

第2ゲート電極及び第3ゲート電極と第2ストレージ電極を形成する段階と、第5領域及び第8領域と第4領域及び第7領域をドーピングする段階は、第1ゲート電極と第1金属パターン及び第2金属パターンの上に、第3フォトレジスト層を形成する段階と；第3

マスクを利用して第3フォトレジスト層を露光、現像することによって、第1半導体層を覆う第8フォトレジストパターンと、第2半導体層の第3領域及び第4領域に対応する第9フォトレジストパターンと、第3半導体層の第6領域及び第7領域に対応する第10フォトレジストパターンと、第4半導体層を覆う第11フォトレジストパターンを形成する段階と；第8ないし第11フォトレジストパターン間の第1金属パターン及び第2金属パターンを除去する段階と；第2半導体層の第5領域及び第3半導体層の第8領域に、 $n^+$ イオンをドーピングする段階と；第8ないし第11フォトレジストパターンをアッシングすることによって、第2半導体層の第4領域に対応する第2金属パターンと、第3半導体層の第7領域に対応する第2金属パターンと、補助電極に対応するように第2金属パターンの両一端を露出させる段階と；第8ないし第11フォトレジストパターンをアッシングする段階によって露出された第1金属パターン及び第2金属パターンを除去することにより、第2半導体層の第3領域に対応する第2ゲート電極と、第3半導体層の第6領域に対応する第3ゲート電極と、補助電極に対応する第2ストレージ電極を形成する段階と；第2半導体層の第4領域と、第3半導体層の第7領域に、 $n^-$ イオンをドーピングする段階と；第8ないし第11フォトレジストパターンを除去する段階とを含む。10

#### 【0034】

第1ないし第3ソース電極と第1ないし第3ドレイン電極と、第3ストレージ電極と画素電極を形成する段階は、層間絶縁膜上に、透明電極層と、第3伝導性金属層と、第4フォトレジスト層を形成する段階と；第4フォトレジスト層上に、第6部分と、第6部分より小さい透過率を有する第7部分と、第7部分より小さい透過率を有する第8部分で構成された第4マスクを配置する段階と；第4マスクを利用して第4フォトレジスト層を露光、現像することによって、層間絶縁膜の第1コンタクトホール及び第2コンタクトホールの上部に、第12フォトレジストパターンと、層間絶縁膜の第3コンタクトホールと第4コンタクトホールの上部に、第13フォトレジストパターンと、層間絶縁膜の第5コンタクトホールと第6コンタクトホールの上部に、第14フォトレジストパターンと、第2ストレージ電極の上部に、第15フォトレジストパターンと、画素領域に第12ないし第15フォトレジストパターンより低い高さを有して、第15フォトレジストパターンから延長される第16フォトレジストパターンを形成する段階と；第12ないし第15フォトレジストパターン間の第3伝導性金属層と透明電極層を除去することによって、第1コンタクトホール及び第2コンタクトホールを通じて第1半導体層の第2領域と各々接触する第1ソース電極及び第1ドレイン電極と、第3コンタクトホール及び第4コンタクトホールを通じて第2半導体層の第5領域と各々接触する第2ソース電極及び第2ドレイン電極と、第5コンタクトホール及び第6コンタクトホールを通じて第3半導体層の第8領域と各々接触する第3ソース電極及び第3ドレイン電極を形成する段階と；画素領域の第3伝導性金属層が露出されるように第12ないし第16フォトレジストパターンをアッシングする段階と；画素領域の第3伝導性金属層を除去することによって、第2ストレージ電極の上部の第3ストレージ電極と画素領域に、画素電極を形成する段階とを含み、第3ドレイン電極と第3ストレージ電極は、透明電極と不透明電極を含んで、画素電極は、透明電極から延長される。30

#### 【発明の効果】

#### 【0035】

本発明による液晶表示装置用アレイ基板の製造方法は、従来に比べて、工程が単純化され工程費用を節減して、工程時間が短縮される。

また、工程が単純化されることによって、不良発生確率を低め、生産収率が改善される。

#### 【実施例】

#### 【0036】

以下、本発明の実施例による駆動回路一体型の液晶表示装置用アレイ基板の製造方法を説明する。

#### 【0037】

50

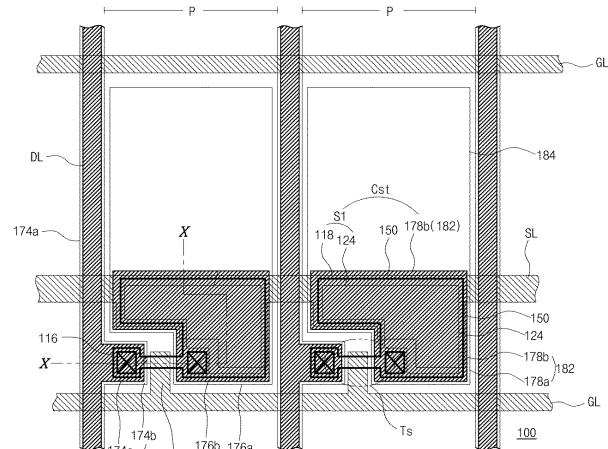

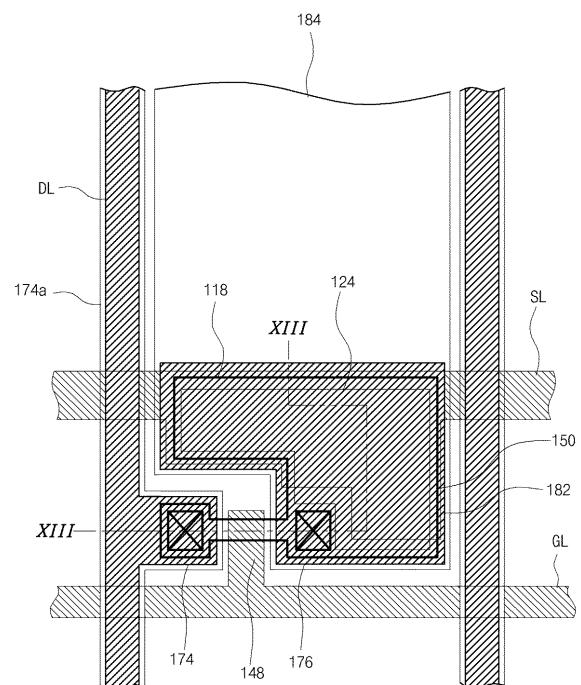

図8は、本発明の実施例による一体型駆動回路を含むアレイ基板の表示領域を概略的に示した平面図である。

図8に示したように、第1基板100上に、一方向に延長されたゲート配線GLと、ゲート配線GLと垂直に交差して画素領域Pを定義するデータ配線DLを構成する。

ゲート配線GLとデータ配線DLの交差地点には、スイッチング素子である多結晶薄膜トランジスタTsを構成して、画素領域Pには、画素電極184を構成する。

多結晶薄膜トランジスタTsは、多結晶シリコン層である半導体層116と、ゲート電極148とソース電極174とドレイン電極176を含み、画素電極184は、ドレイン電極176と接触するように構成する。

#### 【0038】

10

画素領域Pの一部には、補助容量部であるストレージキャパシターCstを構成するが、ストレージキャパシターCstは、半導体層120と補助電極124が積層された第1ストレージ電極S1と、ストレージ配線SLから第1ストレージ電極S1の上部に延長された第2ストレージ電極150と、ドレイン電極176から第2ストレージ電極150の上部に延長された第3ストレージ電極182で構成される。この時、補助電極124とその下部の半導体層118は、オーミックコンタクトの特性を有するために、同一信号が流れるようにすることを特徴とする。

また、ソース電極174及びドレイン電極176は、透明電極層174a、176aと伝導性金属層174b、176bが積層された形状であるとともに、第3ストレージ電極182も透明電極層178aと伝導性金属層178bが積層された形状であって、この時、第3ストレージ電極の透明電極層178aは、画素電極184と一緒に構成される。

20

以下、断面構成を参照して、前述した構成を含む駆動回路一体型の液晶表示装置用アレイ基板の構成を察する。

#### 【0039】

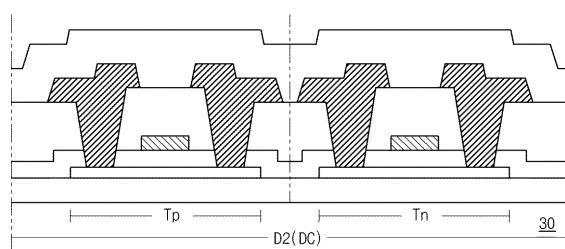

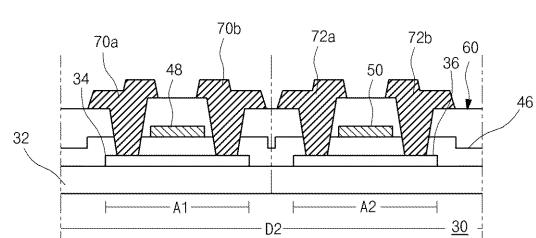

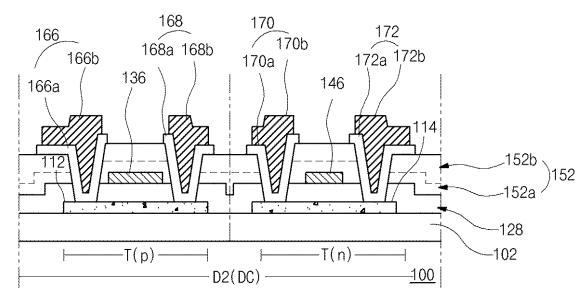

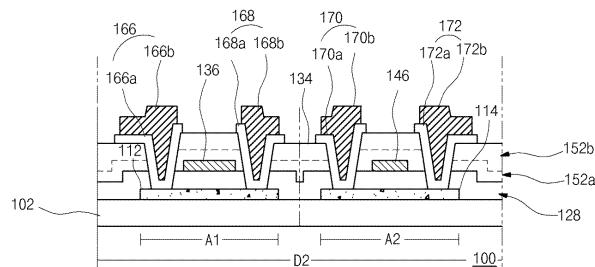

図9は、本発明の実施例による駆動回路部の断面図であって、図10は、図8のX-X線に沿って切断した表示領域の断面図である。

図9と図10に示したように、駆動回路一体型の液晶表示装置用アレイ基板の第1基板100は、表示領域D1と非表示領域D2に区分される。

非表示領域D2には、n型の多結晶薄膜トランジスタである第1薄膜トランジスタT(n)とp型の多結晶薄膜トランジスタである第2薄膜トランジスタT(p)の組合であるCMOSで構成された駆動回路を形成する。

30

表示領域D1には、スイッチング素子である第3薄膜トランジスタTsと、多結晶半導体層118と補助電極124が積層された第1ストレージ電極S1と、第2ストレージ電極150と、透明電極層178aと伝導性金属層178bが積層された第3ストレージ電極182を含むストレージキャパシターCstが形成される。また、画素領域Pごとにスイッチング素子Tsと接触する画素電極184が形成される。

#### 【0040】

第3薄膜トランジスタTsは、通常、n型の多結晶薄膜トランジスタで構成されて、ストレージキャパシターCstは、第1ストレージ電極S1及び第2ストレージ電極150で構成された第1ストレージキャパシターC1と、第2ストレージ電極150及び第3ストレージ電極182で構成された第2ストレージキャパシターC2を等価回路的に直列連結した構成である。

40

#### 【0041】

前述した構成は、駆動回路部DCの第1薄膜トランジスタT(p)及び第2薄膜トランジスタT(n)及び第3薄膜トランジスタTsに使用されるn型及びp型の多結晶薄膜トランジスタの多結晶半導体層112、114、116と、ストレージキャパシターCstの多結晶半導体層118と、その上部の補助電極124を單一マスク工程によって構成することを第1特徴とする。

#### 【0042】

また、第1ないし第3薄膜トランジスタT(p)、T(n)、Tsのゲート電極136

50

、146、148と、第2薄膜トランジスタT(n)及び第3薄膜トランジスタTsの半導体層114、116の表面に、部分的にn+イオンドーピングと、n-イオンドーピング工程と、第1薄膜トランジスタT(p)の半導体層112に、p+イオンドーピング工程及びストレージキャパシターCstの第2ストレージ電極150を形成する工程を、2度のマスク工程によって行うことを第2特徴とする。

#### 【0043】

さらに、第3薄膜トランジスタTsのソース電極174及びドレイン電極176と第3ストレージ電極182と、画素電極184を單一マスク工程によって形成することを第3特徴とする。

#### 【0044】

この時、画素電極184と接触する層間絶縁膜152a、152bは、酸化シリコン膜(152a、SiO<sub>2</sub>)と窒化シリコン膜(152b、SiNx)を積層して形成し、特に、画素電極184との界面特性の良い窒化シリコン膜152bが画素電極と直接接触するように構成する。

#### 【0045】

本発明による液晶表示装置用アレイ基板は、前述したマスク工程を含み、5マスク工程によって製作することができる。

以下、工程図面を参照して、本発明による駆動回路一体型の液晶表示装置用アレイ基板の製造工程を説明する。

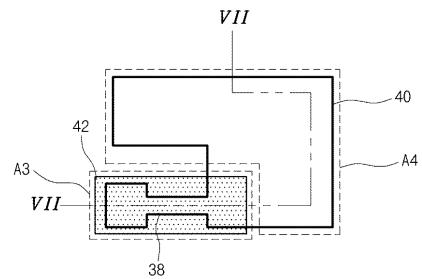

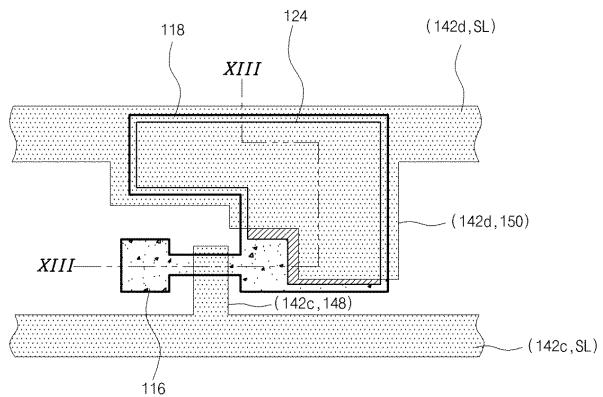

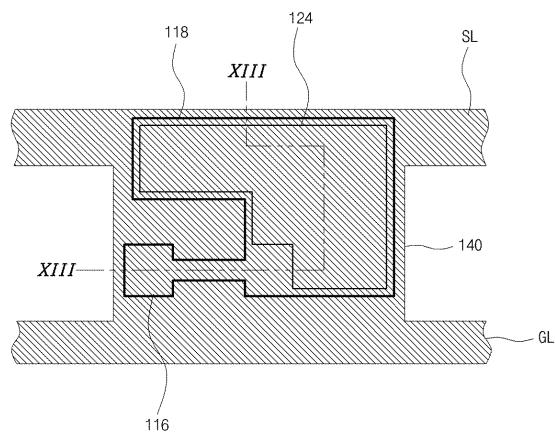

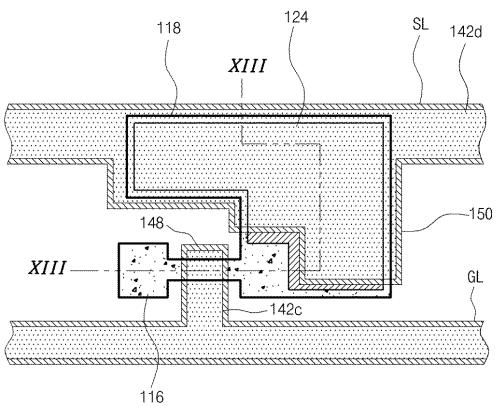

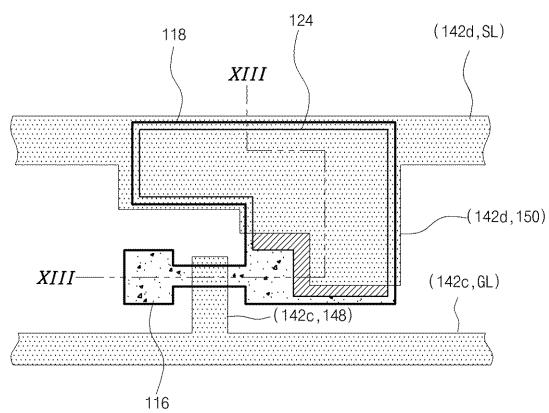

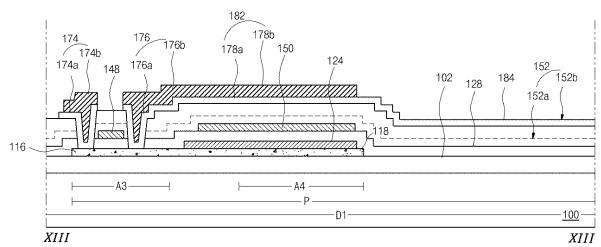

#### 【0046】

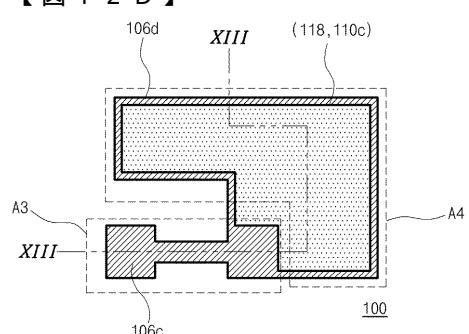

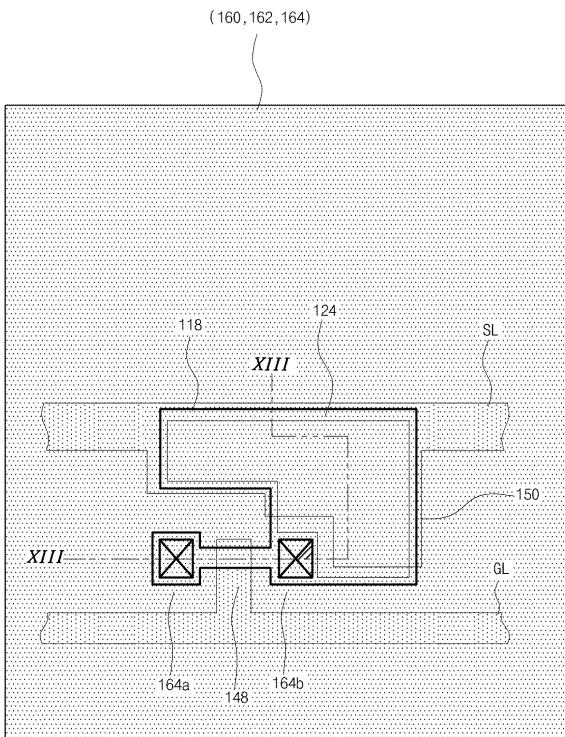

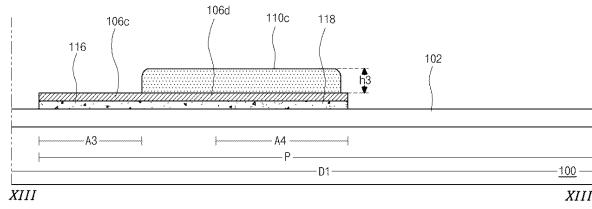

図11Aないし図11Pは、本発明の実施例によって駆動回路を製造する工程を示した断面図であって、図12Aないし図12Pは、本発明の実施例によってアレイ基板の表示領域を製造する工程を示した断面図であり、図13Aないし図13Pは、各々図12Aないし図12PのXIIIXII線に沿って切断した部分の製造工程を示した断面図である。

#### 【0047】

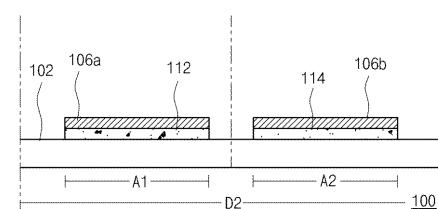

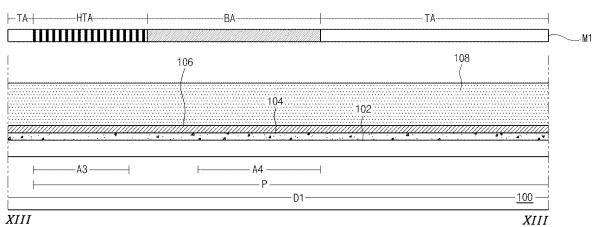

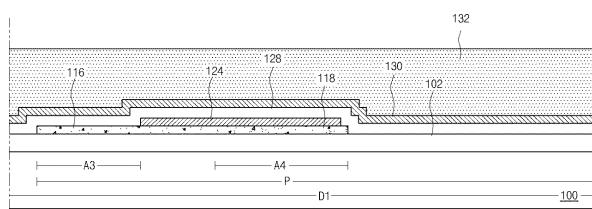

以下、図11Aないし図11Eと図12Aないし図12Eと図13Aないし図13Eは、第1マスク工程を示した図である。

図11Aと図12A図13Aに示したように、第1基板100に、表示領域D1と非表示領域D2が定義されて、表示領域D1には、多数の画素領域Pが定義される。また、非表示領域D2には、第1領域A1と第2領域A2を定義して、画素領域Pに、第3領域A3と第4領域A4を定義する。

この時、第1領域A1は、第1薄膜トランジスタT(p)が形成される領域であって、第2領域A2は、第2薄膜トランジスタT(n)が形成される領域である。さらに、第3領域A3は、スイッチング素子である第3薄膜トランジスタTsが形成される領域であって、第4領域A4は、ストレージキャパシターCstが形成される領域である。

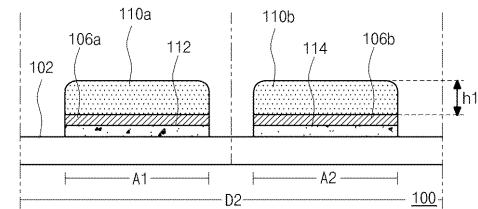

#### 【0048】

前述したように、多数の領域A1、A2、A3、A4が定義された第1基板100全面に、バッファ層102と多結晶シリコン層104と第1伝導性金属層106を積層形成する。

バッファ層102は、窒化シリコンSiNxと酸化シリコンSiO<sub>x</sub>を含む無機絶縁物質グループのうちから選択された1つ又は、それ以上の物質を蒸着して形成する。

多結晶シリコン層104は、不純物を含まない純粋非晶質シリコン(a-Si:H)を蒸着した後、脱水素工程及び結晶化工程を行って形成する。

#### 【0049】

第1伝導性金属層106は、タングステンW、モリブデンMo、クロムCr、モリブデンタングステンMoW等を含む伝導性金属グループのうちから選択された1つを蒸着して形成する。

第1伝導性金属層106が形成された基板100全面に、フォトレジストを塗布して第1フォトレジスト層108を形成する。

10

20

30

40

50

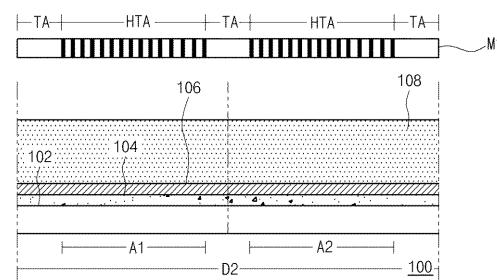

第1フォトレジスト層108と離隔された上部に、透過部TAと遮断部BAと半透過部HTAで構成されたマスクM1を位置させる。遮断部BAは、第4領域A4に対応するようにして、半透過部HTAは、第1領域A1と第2領域A2と第3領域A3に対応するようにして、透過部TAは、その他の領域に対応するようとする。

この時、マスクM1は、第1フォトレジスト層108の位置によって強度の異なる光を照射して、部分的にフォトレジスト層を露光し、特に、半透過部HTAは、光の回折による光強度の減少を利用して下部の感光層が表面から一部だけ露光されるようにすることを特徴とする。

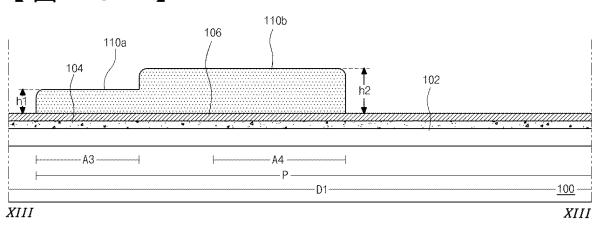

#### 【0050】

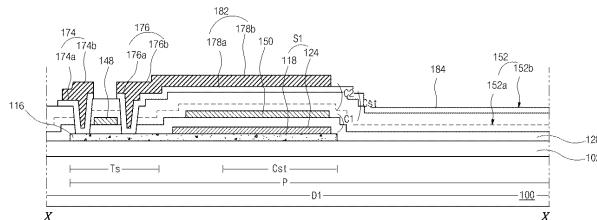

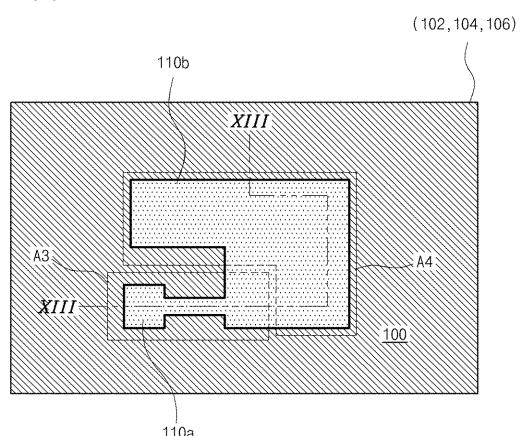

従って、図11Bと図12Bと図13Bに示したように、マスクの上部に光を照射した後、現像すると、第1ないし第3領域A1、A2、A3には、最初より低い高さの第1フォトレジストパターン110aが形成されて、第4領域A4には、第1フォトレジストパターン110aより高い高さの第2フォトレジストパターン110bが形成される。第3フォトレジストパターン110cは、第3領域A3の第1フォトレジストパターン110aから延長され形成するが、マスクの半透過部HTAに対応する第3領域A3には、低い高さのフォトレジストパターンが形成される。10

#### 【0051】

第1フォトレジストパターン110a及び第2フォトレジストパターン110bの周辺に露出された第1伝導性金属層106及びその下部の多結晶シリコン層104を除去する工程を行う。このことによって、第1ないし第4半導体層112、114、116、118と第1ないし第4金属パターン106a、106b、106c、106dが形成される。第1半導体層112と第1金属パターン106aは、第1領域A1に形成されて、第2半導体層114と第2金属パターン106bは、第2領域A2に形成される。また、第3半導体層116と第3金属パターン106cは、第3領域A3に形成されて、第4半導体層118と第4金属パターン106dは、第4領域A4に形成される。20

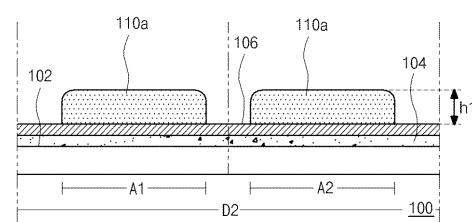

#### 【0052】

図11Cと図12Cと図13Cに示したように、第1フォトレジストパターン110aの下部には、第1ないし第3金属パターン106a、106b、106cと第1ないし第3半導体層112、114、116が残り、第2フォトレジストパターン110bの下部には、第4金属パターン106dと第4半導体層118が残る。この時、第3多結晶半導体層116及び第4多結晶半導体層118は、一体にパターンされる。30

第1フォトレジストパターン110a及び第2フォトレジストパターン110bをアッシングする工程を行う。

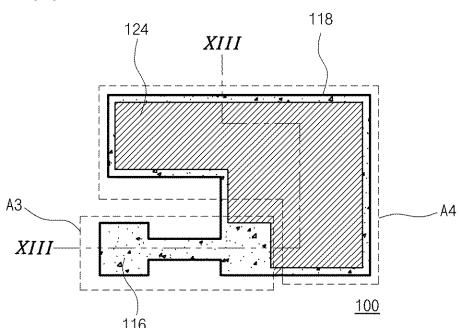

#### 【0053】

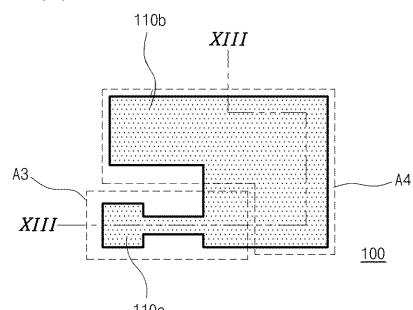

図11Dと図12Dと図13Dに示したように、第1領域A1と第2領域A2と第3領域A3に対応する第1フォトレジストパターン（図11C及び図13Cの110a）が除去され、第4領域A4には、高さが減少された第3フォトレジストパターン110cだけが残る。

第1領域A1と第2領域A2と第3領域A3に対応して露出された第1ないし第3金属パターン106a、106b、106cを除去する工程を行う。40

#### 【0054】

図11Eと図12Eと図13Eに示したように、第1ないし第3領域A1、A2、A3には、第1ないし第3金属パターン106a、106b、106cが除去され、第1ないし第3多結晶半導体層112、114、116が露出されて、第4領域の第4半導体層118の上部には、第3金属パターン（図13Dの106d）が残って補助電極124が形成される。

以上、前述した第1マスク工程によって、第1領域A1と第2領域A2と第3領域A3に、第1ないし第3多結晶半導体層112、114、116が形成できて、第4領域A4に、第3多結晶半導体層116と一緒に構成された第4多結晶半導体層118と、補助電極124を積層して形成することができる。この時、第4多結晶半導体層118と第4多50

結晶半導体層 118 上に形成された補助電極 124 は、第 1 ストレージ電極としての役割をする。

#### 【0055】

前述した工程で、第 4 多結晶半導体層 118 に補助電極 124 を形成することによって、第 4 多結晶半導体層 118 を電極として使用するための別途の不純物イオンドーピング工程が省略できる。

#### 【0056】

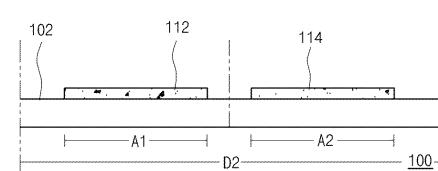

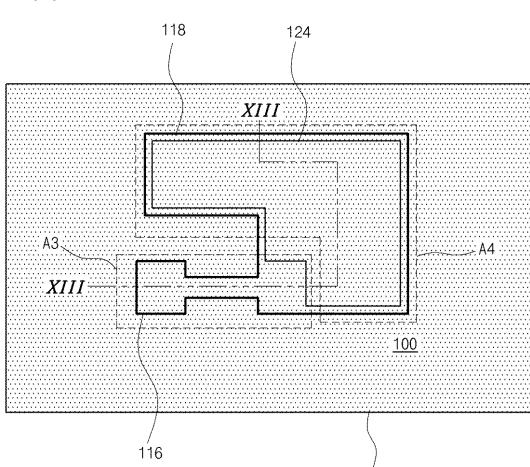

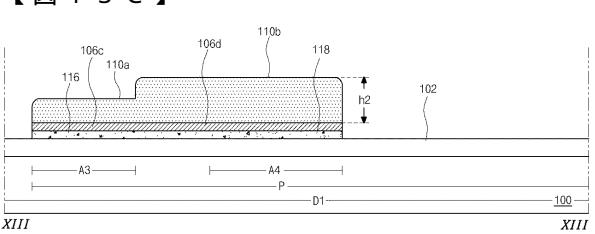

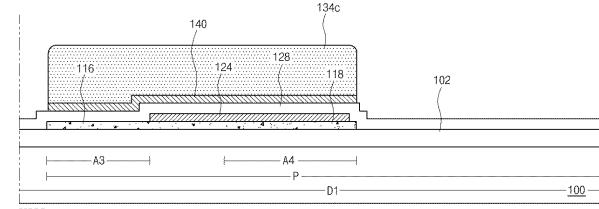

以下、図 11F ないし図 11G と図 12F ないし図 12G と図 13F ないし図 13G は、第 2 マスク工程を示した図である。

図 11F と図 12F と図 13F に示したように、第 4 領域 A4 に、補助電極 124 が形成された第 1 基板 100 全面に、ゲート絶縁膜 128 と第 2 伝導性金属層 130 を積層して、第 2 伝導性金属層 130 上に、フォトレジストを塗布して第 2 フォトレジスト層 132 を形成する。

10

第 2 マスクで第 2 フォトレジスト層 132 を露光して現像する工程を行う。

#### 【0057】

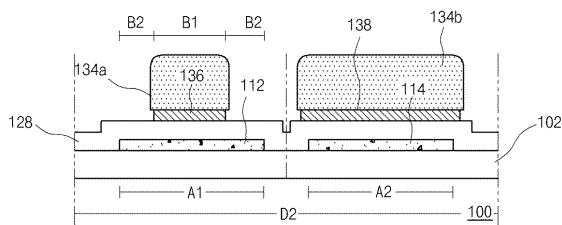

図 11G と図 12G 図 13G に示したように、第 1 領域 A1 と第 2 領域 A2 に残された第 4 フォトレジストパターン 134a 及び第 5 フォトレジストパターン 134b と、第 3 領域 A3 と第 4 領域 A4 に残された第 6 フォトレジストパターン 134c の周辺に露出された第 2 伝導性金属層（図 9F と図 11F の 130）を除去する工程を行う。

第 1 領域 A1 の第 1 半導体層 112 の上部には、第 1 ゲート電極 136 が形成されて、

20 第 2 領域 A2 の第 2 半導体層 114 の上部には、第 4 金属パターン 138 が残される。また、第 3 領域 A3 及び第 4 領域 A4 には、第 5 金属パターン 140 が残る。

この時、第 1 領域 A1 の第 1 半導体層 112 を第 1 アクティブ領域 B1 と、第 1 アクティブ領域 B1 の両側の第 2 アクティブ領域 B2 とで定義すると、第 1 ゲート電極 136 は、第 1 アクティブ領域 B1 に対応するように形成する。

前述した工程で、第 5 金属パターン 140 の一側と他側に連結されたゲート配線 GL とストレージ配線 SL を形成する。

第 4 ないし第 6 フォトレジストパターン 134a、134b、134c を除去する工程を行う。

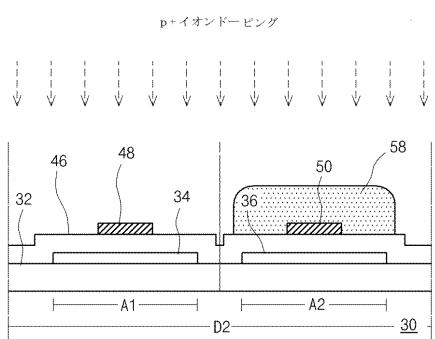

#### 【0058】

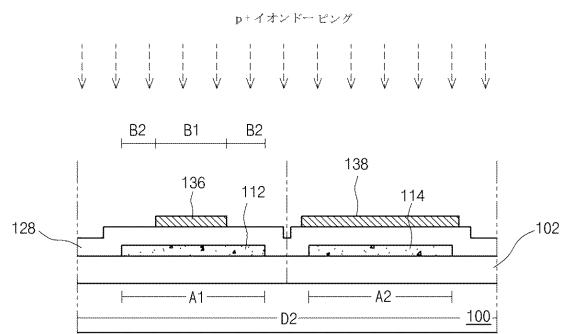

図 11H と図 12H と図 13H は、第 1 領域の第 1 半導体層に、p+イオンをドーピングする工程を示した図である。

図 11H と図 12H と図 13H に示したように、第 1 領域 A1 に、第 1 ゲート電極 136 と、第 2 領域 A2 に、第 4 金属パターン 138 と、第 3 領域 A3 及び第 4 領域 A4 に、第 5 金属パターン 140 が形成された第 1 基板 100 全面に、p+イオンドーピング工程を行う。

第 1 領域 A1 に構成した第 1 半導体層 112 の第 2 アクティブ領域 B2 に、p+イオンドーピングされオームックコンタクト領域が形成される。

#### 【0059】

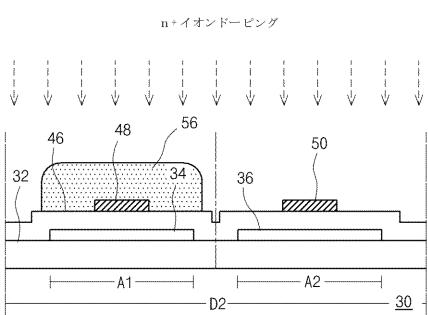

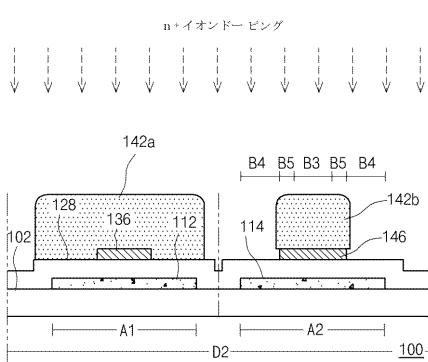

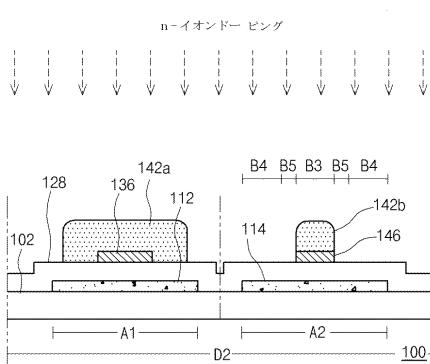

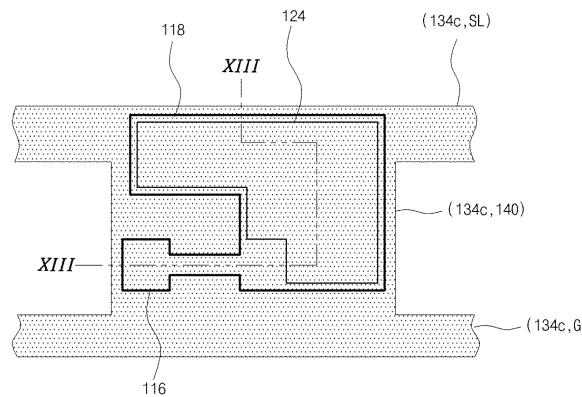

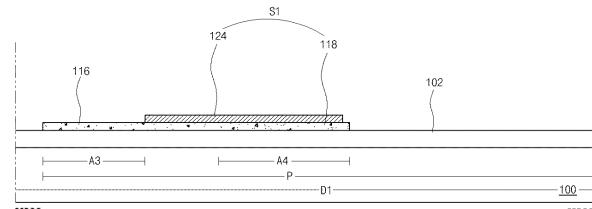

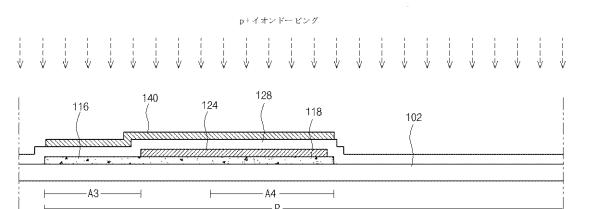

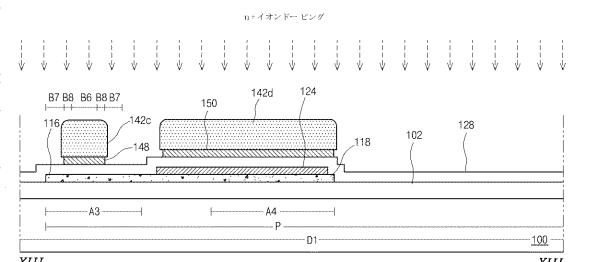

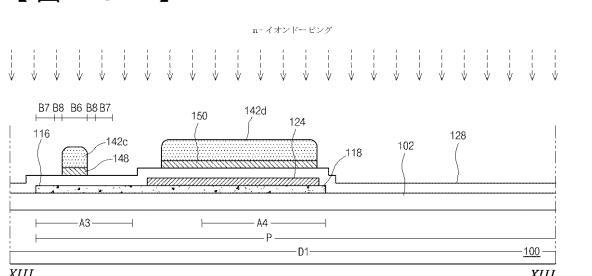

図 11I ないし図 11K と図 12I ないし図 12K と図 13I ないし図 13K は、第 3

40 マスク工程を示した図である。

図 11I と図 12I と図 13I に示したように、第 1 ゲート電極 136 と第 4 金属パターン及び第 5 金属パターン（図 11H の 136、138）及び第 6 金属パターン（図 13H の 140）が形成された第 1 基板 100 全面に、第 3 フォトレジスト層（図示せず）を形成し第 3 マスク工程によってパターンし、第 1 領域 A1 を覆う第 7 フォトレジストパターン 142a を形成して、第 2 領域 A2 に、第 8 フォトレジストパターン 142b とその下部の第 2 ゲート電極 146 を形成する。また、第 3 領域 A3 に、第 9 フォトレジストパターン 142c とその下部の第 3 ゲート電極 148 を形成して、第 4 領域 A4 に、第 10 フォトレジストパターン 142d とその下部の第 2 ストレージ電極 150 を形成する。

#### 【0060】

10

20

30

40

50

第3領域A3の第3ゲート電極148は、ゲート配線GLから突出された形状であって、第2ストレージ電極150は、ストレージ配線SLから突出延長された形状である。

この時、第2領域A2の第2半導体層114に、第3アクティブ領域B3と、第3アクティブ領域B3の両側の第4アクティブ領域B4と、第4アクティブ領域B4と第3アクティブ領域B3間に、第5アクティブ領域B5を定義して、また、第3領域A3の第3半導体層116に、第3アクティブ領域B3と、第3アクティブ領域B3の両側の第4アクティブ領域B4と、第4アクティブ領域B4と第3アクティブ領域B3間に、第5アクティブ領域B5を定義する。そうすると、第2ゲート電極146は、第3アクティブ領域B3及び第5アクティブ領域B5に対応して、第3ゲート電極148は、第6アクティブ領域B6及び第8アクティブ領域B8に対応する。10

第7ないし第10フォトレジストパターン142a、142b、142c、142dをそのまま置いた状態で、第1基板100全面に、n+イオンドーピング工程を行う。

第8フォトレジストパターン142bと第9フォトレジストパターン142cによって遮れない第2多結晶半導体層114及び第3多結晶半導体層116の第4アクティブ領域B4及び第7アクティブ領域B7に、n+イオンドーピングされて、この部分は、オームックコンタクト領域になる。

この時、補助電極124の周辺に露出された第4多結晶半導体層の表面にも、n+イオンドーピングされる。

#### 【0061】

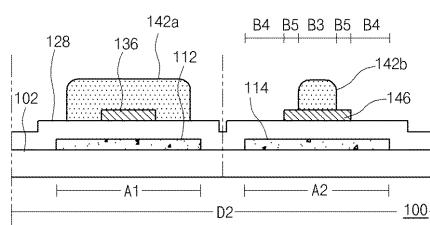

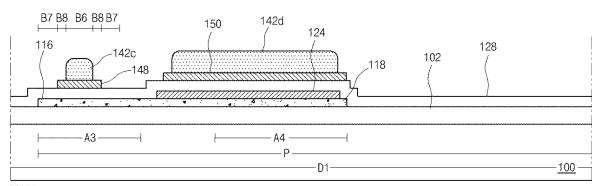

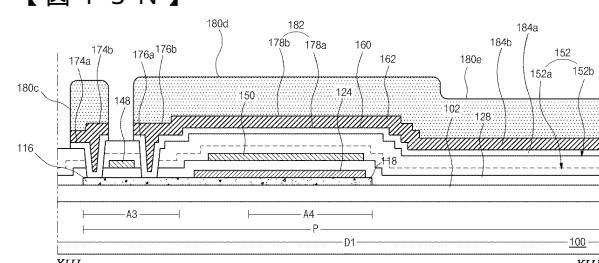

図11Jないし図11Kと図12Jないし図12Kと図13Jないし図13Kは、第2領域と第3領域の半導体層に低ドーピング領域（lightly doped drain、LDD）を形成するための工程である。20

図11Jと図12Jと図13Jに示したように、第1ないし第4領域（A1、A2、A3、A4）に残された第7ないし第10フォトレジストパターン142a、142b、142c、142dをアッシング（ashing）する工程を行う。

アッシング工程は、乾式エッチング工程と類似であって、第7ないし第10フォトレジストパターン142a、142b、142c、142dを完全に除去する目的よりは、周辺の一部だけを除去して下部金属層の一部を露出するためである。

従って、本工程では、フォトレジストパターンのアッシングによって、第2半導体層114の第4アクティブ領域B4に対応する上部の第2ゲート電極146と、第3半導体層の第8アクティブ領域B8に対応する上部の第3ゲート電極148を露出する。この時、第2ストレージ電極150及びゲート配線GLとストレージ配線SLの周辺も一部露出される。30

以後、工程によって露出された第2ゲート電極146及び第3ゲート電極148の一部を除去する工程を行う。

#### 【0062】

図11Kと図12Kと図13Kは、低ドーピング領域を形成するためにn-イオンをドーピングする工程を示した図である。

図11Kと図12Kと図13Kに示したように、前述した工程で、第2領域A2と第3領域A3に位置した第2ゲート電極146及び第3ゲート電極148の周辺一部が除去された部分に対応する第2多結晶半導体層114及び第3多結晶半導体層116の第3アクティブ領域B3にn-イオンをドーピングする工程を行い、低ドーピング領域を形成する。低ドーピング領域を形成する理由は、チャンネル（第3アクティブ領域及び第6アクティブ領域）に近接した領域で、熱電子効果によって発生する漏洩電流特性を最小化するためである。40

第2多結晶半導体層114及び第3多結晶半導体層116に低ドーピング領域を形成した後、第1ないし第4領域A1、A2、A3、A4の第7ないし第10フォトレジストパターン142a、142b、142c、142dを除去する工程を行う。

#### 【0063】

以上、前述した第2ないし第3マスク工程によって、第1領域A1の第1半導体層1150

2の上部に第1ゲート電極118を形成して、ゲート電極118が位置しない第1半導体層112の表面に、p+イオンをドーピングしてオーミックコンタクト領域を形成し、第2領域A2と第3領域A3の第2半導体層114及び第3半導体層116には、n+イオンとn-イオンを各々ドーピングして、オーミックコンタクト領域と低ドーピング領域を形成すると同時に、各々第2ゲート電極146及び第3ゲート電極148を形成した。また、第4領域A4には、第2ストレージ電極150を形成する工程を行う。

#### 【0064】

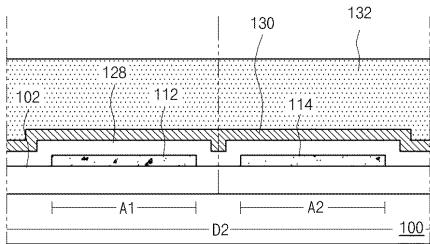

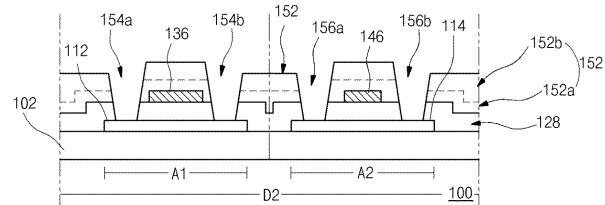

図11Lと図12Lと図13Lは、第4マスク工程を示した図である。

図11Lと図12Lと図13Lに示したように、第1ないし第3領域A1、A2、A3に、各々第1ないし第3ゲート電極136、146、148が形成されて、第4領域A4に、第2ストレージ電極150が形成された第1基板100全面に、酸化シリコンSiO<sub>2</sub>を蒸着した第1層間絶縁膜152aと、第1層間絶縁膜152aの上部に、窒化シリコンSiNxを蒸着して形成した第2層間絶縁膜152aで構成された層間絶縁膜152を形成する。

層間絶縁膜152が形成された第1基板100全面に、フォトレジストを塗布した後、第4マスク工程によってパターンし、第1ないし第3半導体層112、114、116のオーミックコンタクト領域を各々露出する第7ないし第12コンタクトホール154a、154b、156a、156b、158a、158bを形成する。

すなわち、第7コンタクトホール154a及び第8コンタクトホール154bは、第1半導体層112の第2アクティブ領域(図11GのB2)を露出し、第9コンタクトホール156a及び第10コンタクトホール156bは、第2半導体層114の第4アクティブ領域(図11KB4)を露出して、第11コンタクトホール158a及び第12コンタクトホール158bは、第3半導体層114の第7アクティブ領域(図13KのB7)を露出する。

前述した工程で、第1層間絶縁膜152aを形成した後、第1基板100を熱処理する工程を行うことができる。

#### 【0065】

補助電極124の周辺に露出された第4半導体層118の表面にドーピングされたイオン(n+イオン)が、補助電極124の下部に拡散される現象が起きる。このことによつて、補助電極124とその下部の第4半導体層118は、オーミックコンタクトを構成して相互に信号が流れようになる。また、第2層間絶縁膜152bを形成した後、水素化熱処理を行うことができる。

さらに、第7ないし第12コンタクトホール154a、154b、156a、156b、158a、158bを形成しながら第3半導体層118の第12コンタクトホール158bの代りに、補助電極124の周辺に露出された第4半導体層118または、補助電極124を露出してコンタクトホールを形成することもできる。これが可能な理由は、第3半導体層116と第4半導体層118が一体に形成され同一な信号が流れる構造で形成されたためである。

#### 【0066】

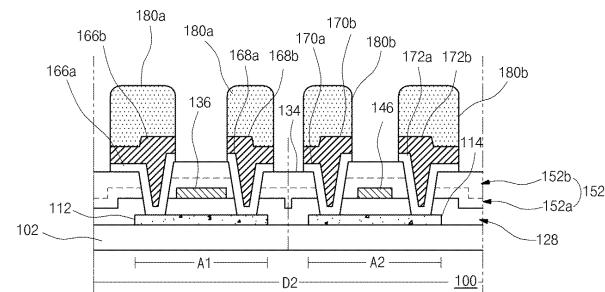

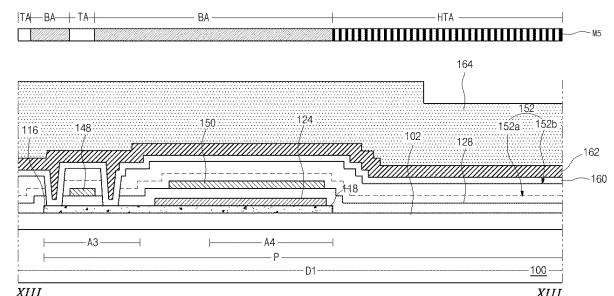

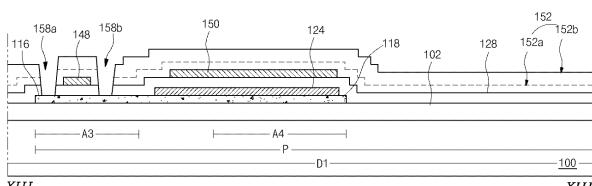

以下、図11Mないし図11Pと図12Mないし図12Pと図13Mないし図13Pは、第5マスク工程を示した図である。

図11Mと図12Mと図13Mに示したように、層間絶縁膜152が形成された第1基板100全面に、透明電極層160と第3伝導性金属層162と第4フォトレジスト層164を積層して形成する。

透明電極層160は、インジウムースズーオキサイドITOとインジウムージンクーオキサイドIZOを含む透明な物質グループのうちから選択された1つまたは、それ以上を蒸着して形成し、第3伝導性金属層162は、前述した伝導性金属物質グループのうちから選択された1つまたは、それ以上の物質を蒸着して形成する。

第4フォトレジスト層164は、フォトレジスト(ポジティブ型、positive type)を塗布して形成する。

10

20

30

40

50

第4フォトレジスト層164が形成された第1基板100と離隔された上部に、透過部TAと半透過部HTAと遮断部BAで構成された第5マスクM5を位置させる。

この時、透過部TAは、第1ないし第3領域A1、A2、A3に構成された第1ないし第3ゲート電極136、146、148に対応して、半透過部HTAは、第3領域A3及び第4領域A4を除いた画素領域Pに対応して位置する。また、遮断部BAは、第1ないし第3領域A1、A2、A3のうち、第1ないし第3ゲート電極136、146、148で覆われてない領域と、第4領域A4に対応して位置するようとする。

第5マスクM5の上部に光(紫外線)を照射して、下部の第4フォトレジスト層164を部分的に露光する工程を行う。

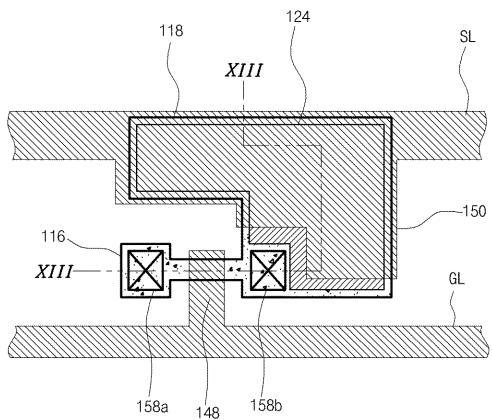

#### 【0067】

前述したように、透過部TAに対応する部分は完全に露光され、半透過部HTAに対応する部分は表面から一部だけが露光されて、遮断部(BA)に対応する部分は露光されないで残る。

露光された部分を現像して第3伝導性金属層162上に、第11ないし第15フォトレジストパターン180a、180b、180c、180d、180eを形成する。第11フォトレジストパターン180aは、第7コンタクトホール及び第8コンタクトホール(図11Lの154a、154b)に対応されて形成され、第12フォトレジストパターン180bは、第9コンタクトホール及び第10コンタクトホール(図11Lの156a、156b)に対応されて形成される。第13フォトレジストパターン180cは、第11コンタクトホール(図13Lの158a)に対応されて、第14フォトレジストパターン180dは、第12コンタクトホール(図13Lの158b)に対応される。また、第15フォトレジストパターン180eは、第14フォトレジストパターン180dから延長され、画素領域Pに形成されて、第11ないし第14フォトレジストパターン180a、180b、180c、180dに比べて低い高さを有する。

第11ないし第14フォトレジストパターン180a、180b、180c、180d間の第3伝導性金属層162と透明電極層160を除去する。

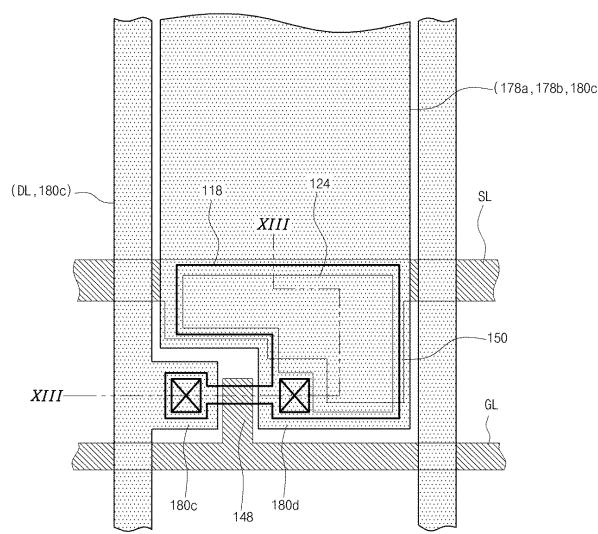

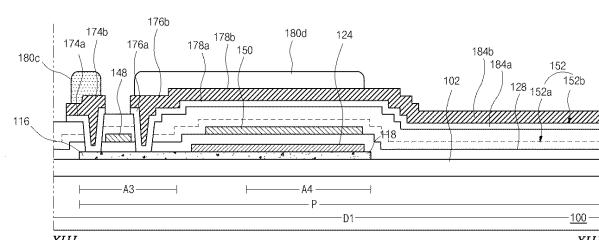

#### 【0068】

図11Nと図12Nと図13Nに示したように、第1ないし第3領域A1、A2、A3に、多数の透明電極166a、168a、170a、172a、174a、176aと多数の不透明電極166b、168b、170b、172b、173b、176bが積層されて形成され、第4領域A4に、透明電極パターン178aと不透明電極パターン178bが残されて第3ストレージ電極182を形成成して、また、画素領域Pに、透明電極パターン184aと不透明電極パターン184bが残る。

前述した工程で、第3領域A1の透明電極パターン174aと不透明電極パターン174bで画素領域Pの一側に沿って延長されたデータ配線DLを形成する。

#### 【0069】

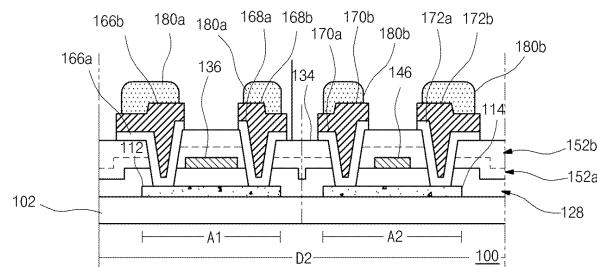

図11Oと図12Oと図13Oは、第11ないし第15フォトレジストパターンをアッシングしてエッチングした後を示した図である。

図11Oと図12Oと図13Oに示したように、アッシング工程後、第11ないし第14フォトレジストパターン180a、180b、180c、180dは、表面から一部だけが除去された状態になって、周辺が除去され下部の不透明電極パターン166b、168b、170b、172b、174b、176bが一部露出されて、第15フォトレジストパターン180eは、完全に除去され下部の不透明電極パターン184bが露出される。

露出された不透明電極パターン166b、168b、170b、172b、174b、176b、178bを除去する工程を行い、第11ないし第15フォトレジストパターン180a、180b、180c、180d、180eを除去する。

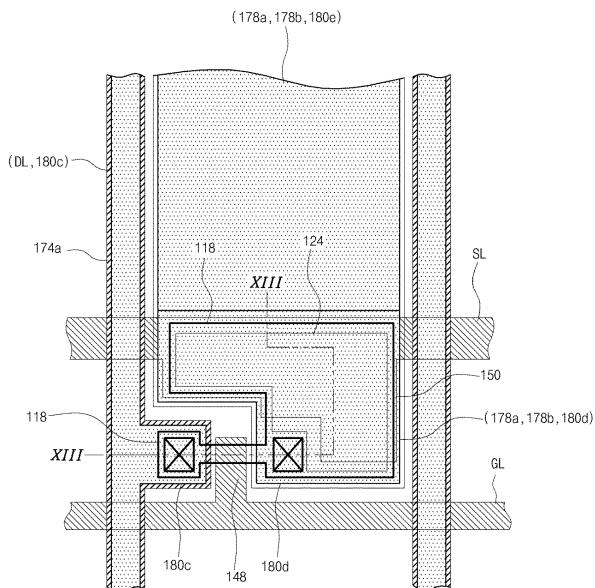

#### 【0070】

図11Pと図12Pと図13Pに示したように、第1ないし第3領域A1、A2、A3の不透明電極パターン166b、168b、170b、172b、174bが一部除去さ

10

20

30

40

50

れ周辺に、下部の透明電極パターン 166a、168b、170c、172d、174e が露出されることによって、第 1 ないし第 3 ソース電極 166、170、174 と第 1 ないし第 3 ドレイン電極 168、172、176 が形成される。また、第 4 領域 A4 には、透明電極パターン 178a と不透明電極パターン 178b が積層された第 3 ストレージ電極 182 が形成されて、画素領域 P の一部に透明な画素電極 184 が形成される。

#### 【0071】

以上、単一マスク工程によって、第 1 ないし第 3 領域 A1、A2、A3 に、ソース電極 166、170、174 及びドレイン電極 168、172、176 を形成し、第 4 領域 A4 に、第 3 ストレージ電極 182 を形成して、また、画素領域 P の一部に、画素電極 184 を形成することができる。

前述したように、5 マスク工程によって本発明による駆動回路一体型の液晶表示装置用アレイ基板が製作できる。

#### 【図面の簡単な説明】

#### 【0072】

【図 1】従来技術による液晶表示装置用アレイ基板を概略的に示した平面図である。

【図 2】従来技術による液晶表示装置用アレイ基板の一部を拡大した平面図である。

【図 3】従来技術による駆動回路部の断面図である。

【図 4】図 2 の I-I - I-I 線に沿って切断したアレイ基板の表示領域の断面図である。

【図 5 A】従来技術によって駆動回路部を製造する工程を示した工程断面図である。

【図 5 B】図 5 A に続く製造工程を示す断面図である。

【図 5 C】図 5 B に続く製造工程を示す断面図である。

【図 5 D】図 5 C に続く製造工程を示す断面図である。

【図 5 E】図 5 D に続く製造工程を示す断面図である。

【図 5 F】図 5 E に続く製造工程を示す断面図である。

【図 5 G】図 5 F に続く製造工程を示す断面図である。

【図 5 H】図 5 G に続く製造工程を示す断面図である。

【図 5 I】図 5 H に続く製造工程を示す断面図である。

【図 6 A】従来技術によってアレイ基板の表示領域を製造する工程を示した断面図である。

。

【図 6 B】図 6 A に続く製造工程を示す断面図である。

30

【図 6 C】図 6 B に続く製造工程を示す断面図である。

【図 6 D】図 6 C に続く製造工程を示す断面図である。

【図 6 E】図 6 D に続く製造工程を示す断面図である。

【図 6 F】図 6 E に続く製造工程を示す断面図である。

【図 6 G】図 6 F に続く製造工程を示す断面図である。

【図 6 H】図 6 G に続く製造工程を示す断面図である。

【図 6 I】図 6 H に続く製造工程を示す断面図である。

【図 7 A】各々図 5 A ないし図 5 I の V-I - V-I 線に沿って切断した部分の製造工程を示した断面図である。

【図 7 B】図 7 A に続く製造工程を示す断面図である。

40

【図 7 C】図 7 B に続く製造工程を示す断面図である。

【図 7 D】図 7 C に続く製造工程を示す断面図である。

【図 7 E】図 7 D に続く製造工程を示す断面図である。

【図 7 F】図 7 E に続く製造工程を示す断面図である。

【図 7 G】図 7 F に続く製造工程を示す断面図である。

【図 7 H】図 7 G に続く製造工程を示す断面図である。

【図 7 I】図 7 H に続く製造工程を示す断面図である。

【図 8】本発明の実施例による一体型駆動回路を含むアレイ基板の表示領域を概略的に示した平面図である。

【図 9】本発明の実施例による駆動回路部の断面図である。

50

【図13P】図13Oに続く製造工程を示す断面図である。

【符号の説明】

【0073】

- 100：第1基板

- 112：第1半導体層

- 114：第2半導体層

- 116：第3半導体層

- 118：第4半導体層

- 124：補助電極

- 136：第1ゲート電極

- 146：第2ゲート電極

- 148：第3ゲート電極

- S1：第1ストレージ電極

- 150：第2ストレージ電極

- 182：第3ストレージ電極

- 184：画素電極

10

【図1】

【図2】

【図3】

【図4】

【図5 C】

【図5 A】

【図5 D】

【図5 B】

【図5 E】

【図5 H】

【図5 F】

【図5 I】

【図5 G】

【図 6 A】

【図 6 B】

【図 6 C】

【図 6 D】

【図 6 E】

【図 6 F】

【図 6 G】

【図6H】

【図6I】

【図7B】

【図7E】

【図7C】

【図7F】

【図7D】

【図7G】

【図7H】

【図7I】

【図8】

【図9】

【図10】

【図11C】

【図11A】

【図11D】

【図11B】

【図11E】

【図 11 F】

【図 11 H】

【図 11 G】

【図 11 I】

【図 11 J】

【図 11 L】

【図 11 K】

【図 11 M】

【図 11 N】

【図 1 1 O】

【図 1 2 A】

【図 1 1 P】

【図 1 2 B】

【図 1 2 C】

【図 1 2 D】

【図 1 2 E】

【図 1 2 F】

【図 1 2 G】

【図 1 2 I】

【図 1 2 H】

【図 1 2 J】

【図 1 2 K】

【図 1 2 M】

【図 1 2 L】

【図12N】

【図12O】

【図12P】

【図13A】

【図13B】

【図13C】

【図13D】

【図13G】

【図13E】

【図13H】

【図13F】

【図13I】

【図13J】

【図13M】

【図13K】

【図13N】

【図13L】

【図13O】

## 【図13P】

---

フロントページの続き

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100128657

弁理士 三山 勝巳

(72)発明者 イ ソクウ

大韓民国 431-050 キョンギド アニヤンシ ドンアング ビサンドン 1102ボンジ

グアナク アパート 127-1207

(72)発明者 パク ヨンイン

大韓民国 431-080 キョンギド アニヤンシ ドンアング ホギエドン 811ボンジ

ホギエ2チャ ヒュンデ ホームタウン 202-201

審査官 金高 敏康

(56)参考文献 特開平10-177163 (JP, A)

特開2003-197612 (JP, A)

特開2004-271824 (JP, A)

特開平10-096956 (JP, A)

特開2005-072292 (JP, A)

特開平05-034679 (JP, A)

特開2003-195350 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/136

H01L 21/336

H01L 29/786

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于液晶显示装置的阵列基板及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP4567634B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2010-10-20 |

| 申请号            | JP2006176575                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2006-06-27 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | Eruji. 菲利普斯杜天公司，有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 当前申请(专利权)人(译)  | Eruji显示有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| [标]发明人         | イソクウ<br>パクヨンイン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 发明人            | イソクウ<br>パクヨンイン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | G02F1/136 H01L29/786 H01L21/336                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| CPC分类号         | G02F1/136213 G02F1/13454 G02F2001/136231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| FI分类号          | G02F1/136 H01L29/78.612.B H01L29/78.612.D H01L29/78.613.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 2H092/GA12 2H092/GA59 2H092/GA60 2H092/JA24 2H092/JA28 2H092/JA37 2H092/JA41 2H092/JB21 2H092/JB68 2H092/JB69 2H092/KA04 2H092/KA12 2H092/KA18 2H092/KA22 2H092/KB04 2H092/MA14 2H092/MA27 2H092/NA27 2H192/AA24 2H192/CB02 2H192/CB53 2H192/CC72 2H192/CC75 2H192/DA12 2H192/DA42 2H192/DA67 2H192/FB02 2H192/HA44 2H192/HA47 2H192/HA48 5F110/AA16 5F110/BB02 5F110/BB04 5F110/CC02 5F110/DD13 5F110/DD14 5F110/DD17 5F110/EE02 5F110/GG02 5F110/GG13 5F110/GG35 5F110/GG42 5F110/HJ12 5F110/HL02 5F110/HL07 5F110/HL11 5F110/HL22 5F110/HM15 5F110/NN03 5F110/NN23 5F110/NN24 5F110/NN73 5F110/PP35 5F110/QQ11 5F110/QQ21 |         |            |

| 代理人(译)         | 臼井伸一<br>朝日伸光                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 优先权            | 1020050106840 2005-11-09 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 其他公开文献         | JP2007133364A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

## 摘要(译)

液晶显示装置及其制造方法技术领域本发明涉及液晶显示装置，更具体地涉及用于集成驱动电路的液晶显示装置的阵列基板及其制造方法。根据本发明，通过第一掩模工艺形成在驱动电路部分和像素区域中形成的p型和n型第一薄膜晶体管和第二薄膜晶体管的半导体层。形成电极以形成第一存储电极。此外，通过第二掩模工艺和第三掩模工艺形成p型和n型薄膜晶体管的栅电极，并且在每个薄膜晶体管的多晶半导体层中形成p+离子和n+离子掺杂工艺以及n-离子。并且形成第二存储电极。此外，每个多晶薄膜晶体管的源电极和漏电极以及像素电极通过单个掩模工艺形成。[选定图]图7I。

【 图 1 】