(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-188079

(P2007-188079A)

(43) 公開日 平成19年7月26日(2007.7.26)

| (51) Int.CI.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>G09G 3/36</b> (2006.01)   | G09G 3/36  | 2 H 093     |

| <b>H01L 29/786</b> (2006.01) | H01L 29/78 | 5 C 006     |

| <b>H01L 23/522</b> (2006.01) | H01L 29/78 | 5 C 080     |

| <b>H01L 21/768</b> (2006.01) | H01L 21/90 | 5 F 033     |

| <b>G09G 3/20</b> (2006.01)   | G09G 3/20  | 5 F 110     |

審査請求 未請求 請求項の数 29 O L (全 16 頁) 最終頁に続く

|              |                         |          |                                                                                        |

|--------------|-------------------------|----------|----------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2007-2111(P2007-2111) | (71) 出願人 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市八達区梅灘洞416<br>番地 |

| (22) 出願日     | 平成19年1月10日(2007.1.10)   | (74) 代理人 | 100094145<br>弁理士 小野 由己男                                                                |

| (31) 優先権主張番号 | 10-2006-0002843         | (74) 代理人 | 100106367<br>弁理士 稲積 朋子                                                                 |

| (32) 優先日     | 平成18年1月10日(2006.1.10)   | (72) 発明者 | 金 汎 俊<br>大韓民国137-890ソウル市瑞草区良<br>才洞82-13                                                |

| (33) 優先権主張国  | 韓国(KR)                  |          |                                                                                        |

最終頁に続く

(54) 【発明の名称】ゲートドライバー、これを備えた薄膜トランジスター基板及び液晶表示装置

## (57) 【要約】

【課題】コンタクト不良が防止可能な非晶質シリコンTFTを用いたゲートドライバーを提供する。

【解決手段】液晶パネルの上に形成された複数のゲート線を駆動するために、ゲートドライバーは、ゲート駆動信号を出力する複数のステージより構成されるシフトレジスターを備え、複数のステージのそれぞれは、第1のクロック信号及び第2のクロック信号に基づいて、ゲート駆動信号を出力端子に与えるためのプルアップ回路と、ゲートオフ信号を出力端子に与えるためのプルダウン回路と、第1の制御信号に基づいて、プルアップ回路を駆動するプルアップ駆動回路と、第2の制御信号に基づいて、プルダウン回路を駆動するプルダウン駆動回路とを備え、ステージは複数のスイッチング素子を備え、第1のクロック信号、第2のクロック信号、第1の制御信号または第2の制御信号が印加される信号線とスイッチング素子が電気的に接続されるノードのうち所定のノードは複数のコンタクトを備える。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

複数のゲート線を駆動するためのゲートドライバーであって、

前記ゲートドライバーは、ゲート駆動信号を出力する複数のステージより構成されるシフトレジスターを備え、

前記ステージは、第1のクロック信号及び第2のクロック信号に基づいて、ゲート駆動信号を出力端子に与えるためのプルアップ回路と、ゲートオフ信号を前記出力端子に与えるためのプルダウン回路と、第1の制御信号に基づいて前記プルアップ回路を駆動するプルアップ駆動回路と、第2の制御信号に基づいて前記プルダウン回路を駆動するプルダウン駆動回路と、複数のスイッチング素子とを備え、

前記第1のクロック信号、第2のクロック信号、第1の制御信号または第2の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードのうち少なくとも1つのノードは、少なくとも2つのコンタクトを備えることを特徴とするゲートドライバー。

**【請求項 2】**

前記スイッチング素子は、非晶質シリコン活性層を備える薄膜トランジスターであることを特徴とする請求項1に記載のゲートドライバー。

**【請求項 3】**

前記少なくとも1つのノードは、前記第1の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードであることを特徴とする請求項1に記載のゲートドライバー。

**【請求項 4】**

前記第1の制御信号は、直前のステージのゲート駆動信号であることを特徴とする請求項3に記載のゲートドライバー。

**【請求項 5】**

前記少なくとも2つのコンタクトは、透明導電体を備えることを特徴とする請求項1に記載のゲートドライバー。

**【請求項 6】**

前記透明導電体は、インジウム錫酸化物(ITO)を含むことを特徴とする請求項5に記載のゲートドライバー。

**【請求項 7】**

前記少なくとも2つのコンタクトは、異なる個所に形成されることを特徴とする請求項1に記載のゲートドライバー。

**【請求項 8】**

前記ノードのうち前記少なくとも2つのコンタクトを備えるノードの電流値が最も高いことを特徴とする請求項1に記載のゲートドライバー。

**【請求項 9】**

前記少なくとも2つのコンタクトを備えるノードの電流値は、約75μAであることを特徴とする請求項1に記載のゲートドライバー。

**【請求項 10】**

複数のゲート線を駆動するためのゲートドライバーであって、

前記ゲートドライバーは、ゲート駆動信号を出力する複数のステージより構成されるシフトレジスターを備え、

前記ステージは、第1のクロック信号及び第2のクロック信号に基づいてゲート駆動信号を出力端子に与えるためのプルアップ回路と、ゲートオフ信号を前記出力端子に与えるためのプルダウン回路と、第1の制御信号に基づいて前記プルアップ回路を駆動するプルアップ駆動回路と、第2の制御信号に基づいて前記プルダウン回路を駆動するプルダウン駆動回路とを備え、複数のスイッチング素子及び前記複数のスイッチング素子のうち第1のスイッチング素子に接続されている冗長スイッチング素子を備えることを特徴とするゲートドライバー。

**【請求項 1 1】**

前記冗長スイッチング素子は、前記プルダウン駆動回路に作り込まれる少なくとも1つのスイッチング素子に接続されていることを特徴とする請求項10に記載のゲートドライバー。

**【請求項 1 2】**

前記第1のクロック信号、第2のクロック信号、第1の制御信号または第2の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードのうち第1のノードは、少なくとも2つのコンタクトを備えることを特徴とする請求項10に記載のゲートドライバー。

**【請求項 1 3】**

前記スイッチング素子は、非晶質シリコン活性層を備える薄膜トランジスターであることを特徴とする請求項10に記載のゲートドライバー。

**【請求項 1 4】**

前記第1のノードは、前記第1の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードであることを特徴とする請求項12に記載のゲートドライバー。

**【請求項 1 5】**

前記第1の制御信号は、直前のステージのゲート駆動信号であることを特徴とする請求項14に記載のゲートドライバー。

**【請求項 1 6】**

前記少なくとも2つのコンタクトは、透明導電体を備えることを特徴とする請求項12に記載のゲートドライバー。

**【請求項 1 7】**

前記透明導電体は、インジウム錫酸化物(ITO)を含むことを特徴とする請求項16に記載のゲートドライバー。

**【請求項 1 8】**

スイッチング薄膜トランジスターと、前記スイッチング薄膜トランジスターに印加された信号電圧を液晶に加えるための画素電極及び前記画素電極に印加された信号電圧を一定時間以上に維持するストレージキャパシターを備える画素がマトリックス状に配列された基板と、

前記基板の上に形成された複数のゲート線を駆動するために前記基板の上に形成されたゲートドライバーと、

を備え、

前記ゲートドライバーは、ゲート駆動信号を出力する複数のステージより構成されるソフトレジスターを備え、

前記ステージは、第1のクロック信号及び第2のクロック信号に基づいてゲート駆動信号を出力端子に与えるためのプルアップ回路と、ゲートオフ信号を前記出力端子に与えるためのプルダウン回路と、第1の制御信号に基づいて前記プルアップ回路を駆動するプルアップ駆動回路と、第2の制御信号に基づいて前記プルダウン回路を駆動するプルダウン駆動回路と、複数のスイッチング素子とを備え、

前記第1のクロック信号、第2のクロック信号、第1の制御信号または第2の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードのうち少なくとも1つのノードは、少なくとも2つのコンタクトを備えることを特徴とする薄膜トランジスター基板。

**【請求項 1 9】**

前記少なくとも1つのノードは、前記第1の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードであることを特徴とする請求項18に記載の薄膜トランジスター基板。

**【請求項 2 0】**

前記第1の制御信号は、以前のステージのゲート駆動信号であることを特徴とする請求

10

20

30

40

50

項 1 9 に記載の薄膜トランジスター基板。

【請求項 2 1】

前記画素のスイッチング薄膜トランジスターは、非晶質シリコン薄膜トランジスターであることを特徴とする請求項 1 8 に記載の薄膜トランジスター基板。

【請求項 2 2】

スイッチング薄膜トランジスターと、前記スイッチング薄膜トランジスターに印加された信号電圧を液晶に加えるための画素電極及び前記画素電極に印加された信号電圧を一定時間以上に維持するストレージキャパシターを備える画素がマトリックス状に配列された基板と、

前記基板の上に形成された複数のゲート線を駆動するために前記基板の上に形成されたゲートドライバーを備え、10

前記ゲートドライバーは、ゲート駆動信号を出力する複数のステージより構成されるシフトレジスターを備え、

前記ステージは、

第 1 のクロック信号及び第 2 のクロック信号に基づいて、ゲート駆動信号を出力端子に与えるためのプルアップ回路と、ゲートオフ信号を前記出力端子に与えるためのプルダウン回路と、第 1 の制御信号に基づいて、前記プルアップ回路を駆動するプルアップ駆動回路と、第 2 の制御信号に基づいて、前記プルダウン回路を駆動するプルダウン駆動回路とを備えるとともに、複数のスイッチング素子及び前記複数のスイッチング素子のうち第 1 のスイッチング素子に接続されている冗長スイッチング素子を備えることを特徴とする薄膜トランジスター基板。20

【請求項 2 3】

前記冗長スイッチング素子は、前記プルダウン駆動回路に作り込まれる少なくとも 1 つのスイッチング素子に接続されていることを特徴とする請求項 2 2 に記載の薄膜トランジスター基板。

【請求項 2 4】

前記第 1 のクロック信号、第 2 のクロック信号、第 1 の制御信号または第 2 の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードのうち第 1 のノードは、少なくとも 2 つのコンタクトを備えることを特徴とする請求項 2 2 に記載の薄膜トランジスター基板。30

【請求項 2 5】

前記第 1 のノードは、前記第 1 の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードであることを特徴とする請求項 2 4 に記載の薄膜トランジスター基板。

【請求項 2 6】

前記第 1 の制御信号は、直前のステージのゲート駆動信号であることを特徴とする請求項 2 5 に記載の薄膜トランジスター基板。

【請求項 2 7】

前記スイッチング薄膜トランジスターは、非晶質シリコン薄膜トランジスターであることを特徴とする請求項 2 2 に記載の薄膜トランジスター基板。40

【請求項 2 8】

ゲートドライバー及び複数の画素を備え、各画素は、スイッチング薄膜トランジスターと、前記スイッチング薄膜トランジスターに印加された信号電圧を液晶に加えるための画素電極及び前記画素電極に印加された信号電圧を一定時間以上に維持するストレージキャパシターを備える薄膜トランジスター基板と、

カラーフィルター及び前記液晶に電圧を印加するための共通電極を有するカラーフィルター基板と、を備え、

前記ゲートドライバーは、ゲート駆動信号を出力する複数のステージより構成されるシフトレジスターを備え、

前記ステージは、50

第1のクロック信号及び第2のクロック信号に基づいて、ゲート駆動信号を出力端子に与えるためのプルアップ回路と、ゲートオフ信号を前記出力端子に与えるためのプルダウン回路と、第1の制御信号に基づいて前記プルアップ回路を駆動するプルアップ駆動回路と、第2の制御信号に基づいて前記プルダウン回路を駆動するプルダウン駆動回路と、複数のスイッチング素子とを備え、

前記第1のクロック信号、第2のクロック信号、第1の制御信号または第2の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードのうち少なくとも1つのノードは、少なくとも2つのコンタクトを備えることを特徴とする液晶表示装置。

#### 【請求項29】

ゲートドライバー及び複数の画素を備え、各画素は、スイッチング薄膜トランジスターと、前記スイッチング薄膜トランジスターに印加された信号電圧を液晶に加えるための画素電極及び前記画素電極に印加された信号電圧を一定時間以上に維持するストレージキャパシターを備える薄膜トランジスター基板と、

カラーフィルター及び前記液晶に電圧を印加するための共通電極を有するカラーフィルター基板とを備え、

前記ゲートドライバーは、ゲート駆動信号を出力する複数のステージより構成されるソフトレジスターを備え、

前記ステージは、

第1のクロック信号及び第2のクロック信号に基づいて、ゲート駆動信号を出力端子に与えるためのプルアップ回路と、ゲートオフ信号を前記出力端子に与えるためのプルダウン回路と、第1の制御信号に基づいて、前記プルアップ回路を駆動するプルアップ駆動回路と、第2の制御信号に基づいて、前記プルダウン回路を駆動するプルダウン駆動回路とを備えるとともに、複数のスイッチング素子及び前記複数のスイッチング素子のうち所定のスイッチング素子に接続されている冗長スイッチング素子を備えることを特徴とする液晶表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、ゲートドライバー、これを備えた薄膜トランジスター基板及び液晶表示装置に係り、さらに詳しくは、非晶質シリコン薄膜トランジスターを用いてゲートドライバーのコンタクト不良を防止することのできるゲートドライバー、これを備えた薄膜トランジスター基板及び液晶表示装置に関する。

##### 【背景技術】

##### 【0002】

液晶表示装置は、従来のC.R.T (Cathode Ray Tube)と比較して、小型・軽量化及び大画面化が可能であるという長所を有することから、その開発が活発に行われている。また、液晶表示素子は、ノート型パソコンだけではなく、デスクトップ型パソコンのモニター、大型表示装置にも用いられており、その使用範囲が急速に広がってきてている。この種の液晶表示装置は、マトリックス状に配列された多数の制御用のスイッチに印加される映像信号に基づいて、光の透過量が調節され、液晶表示装置のパネルに所望の画像を表示する。

##### 【0003】

一方、液晶表示装置は、非晶質シリコン薄膜トランジスター（以下、TFTとも称する）液晶表示装置と、ポリシリコン薄膜トランジスター液晶表示装置とに大別できる。非晶質シリコンTFTは、TFTの主な特性である移動度がポリシリコンTFTよりも約100~200ほど低いものの、大面積での素子の製作が簡単であり、均一の特性を示すという特徴を備える。しかも、非晶質シリコンTFT程度の特性があれば、画素のスイッチング素子としては十分であるため、液晶表示装置は、主として非晶質シリコンTFTを用い

10

20

30

40

50

て製作されるのが現状である。これに対し、ポリシリコンTFTは、非晶質シリコンTFTに比して高い移動度と素子特性を有する。非晶質シリコンTFT液晶表示装置の場合、液晶パネルには画素部のみを製作し、後で駆動回路をTAB (Tape Automated Bonding) やCOG (Chip On Glass) により取り付けるのに対し、ポリシリコンTFT液晶表示装置においては、画素部を製作するときにデータ駆動回路とゲートドライバーを同時に集積することから、別途の駆動回路が不要になる。なお、最近では、非晶質シリコン技術の発達に伴い、非晶質シリコンTFTを用いたゲートドライバーを液晶パネルに作り込む技術が開発されている。

#### 【0004】

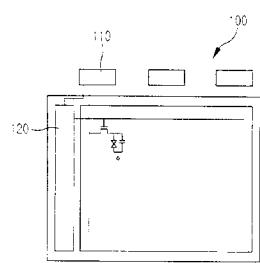

図1は、通常のゲートドライバーが作り込まれた液晶パネルの概略構成図である。図1に示すように、液晶パネル100は、データ線を駆動するためのソースドライバー110と、ゲート線を駆動するためのゲートドライバー120とを備える。ゲートドライバー120は、外部クロック信号とゲート線を接続するスイッチング素子であるTFTと、これを制御する回路とにより構成されているが、TFTとしての非晶質シリコンTFTを基板の上に組み付けることにより外部部品を低減している。

#### 【0005】

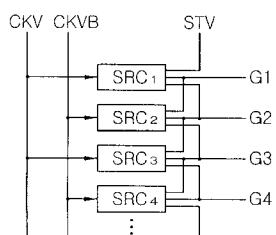

図2は、ゲートドライバーの構造を説明するための概略構成図である。図2に示すように、ゲートドライバーは、クロック信号CKV及び反転クロック信号CKVBに応答して、ゲート線G1、G2、G3、G4を順にターンオンさせるための複数個の縦続接続されたステージSRC<sub>1</sub>、SRC<sub>2</sub>、SRC<sub>3</sub>、SRC<sub>4</sub>より構成されるシフトレジスターを備える。開始信号STVが第1のステージSRC<sub>1</sub>を駆動すると、第1のステージは、クロック信号CKVに応答して第1のゲート線G1をターンオンさせる。ターンオンした第1のゲート線G1は第2のステージSRC<sub>2</sub>を駆動し、第2のステージは、反転クロック信号CKVBに応答して第2のゲート線G2をターンオンさせる。ターンオンした第2のゲート線G2は第3のステージSRC<sub>3</sub>を駆動すると共に、第1のステージSRC<sub>1</sub>をターンオフさせる。このような方式により、ゲート線は順にターンオンされる。

#### 【0006】

かかるゲートドライバーが作り込まれた基板を高温多湿な条件、例えば、温度60℃、湿度95%の条件下で、500～1000時間をかけて信頼性の評価を行ったところ、ゲートドライバーを構成する回路配線ノードを電気的に接続しているコンタクトのうち一部のコンタクトは水分の浸透により腐食されて変色及び剥離が起こり、結果として、ノード同士の電気的な接続が正常になされなくなってしまった。その結果、液晶パネルのゲート線にゲート駆動信号が正常に印加できず、ディスプレイ不良を招く原因となっていた。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0007】

本発明は上述の如き従来の問題点を克服するためのものであり、その目的は、ゲートドライバーが作り込まれた基板を高温多湿な条件下で用いる場合であっても、水分の浸透によるコンタクトの変色及び剥離が原因となって起こるコンタクト不良を防止することのできるゲートドライバー、これを備えた薄膜トランジスター基板及び液晶表示装置を提供することである。

#### 【課題を解決するための手段】

#### 【0008】

前記本発明の目的を達成するために、本発明の一側面によれば、複数のゲート線を駆動するためのゲートドライバーであって、前記ゲートドライバーは、ゲート駆動信号を出力する複数のステージより構成されるシフトレジスターを備え、前記ステージは、第1のクロック信号及び第2のクロック信号に基づいて、ゲート駆動信号を出力端子に与えるためのプルアップ回路と、ゲートオフ信号を前記出力端子に与えるためのプルダウン回路と、第1の制御信号に基づいて前記プルアップ回路を駆動するプルアップ駆動回路と、第2の制御信号に基づいて、前記プルダウン回路を駆動するプルダウン駆動回路とを備え、前記

10

20

30

40

50

ステージは複数のスイッチング素子を備え、前記第1のクロック信号、第2のクロック信号、第1の制御信号または第2の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードのうち少なくとも1つのノードは、少なくとも2つのコンタクトを備えることを特徴とするゲートドライバーを提供する。

#### 【0009】

前記スイッチング素子は、非晶質シリコン活性層を備える薄膜トランジスターであることが好ましい。

前記少なくとも1つのノードは、前記第1の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードであることが好ましい。

前記第1の制御信号は、以前のステージのゲート駆動信号であることが好ましい。 10

#### 【0010】

前記少なくとも2つのコンタクトは、透明導電体を備えることが好ましい。

前記透明導電体は、インジウム錫酸化物（ITO）を含むことが好ましい。

前記少なくとも2つのコンタクトは、異なる個所に形成されることが好ましい。

前記ノードのうち前記少なくとも2つのコンタクトを備えるノードの電流値が最も高いことが好ましい。

#### 【0011】

前記少なくとも2つのコンタクトを備えるノードの電流値は、約75μAであることが好ましい。

前記本発明の目的を達成するために、本発明の他の側面によれば、複数のゲート線を駆動するためのゲートドライバーであって、前記ゲートドライバーは、ゲート駆動信号を出力する複数のステージより構成されるシフトレジスターを備え、前記ステージは、第1のクロック信号及び第2のクロック信号に基づいて、ゲート駆動信号を出力端子に与えるためのプルアップ回路と、ゲートオフ信号を前記出力端子に与えるためのプルダウン回路と、第1の制御信号に基づいて前記プルアップ回路を駆動するプルアップ駆動回路と、第2の制御信号に基づいて前記プルダウン回路を駆動するプルダウン駆動回路とを備え、前記ステージは、複数のスイッチング素子及び前記複数のスイッチング素子のうち第1のスイッチング素子に接続されている冗長スイッチング素子を備えることを特徴とするゲートドライバーを提供する。 20

#### 【0012】

前記冗長スイッチング素子は、前記プルダウン駆動回路に作り込まれる少なくとも1つのスイッチング素子に接続されている。

前記第1のクロック信号、第2のクロック信号、第1の制御信号または第2の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードのうち第1のノードは、少なくとも2つのコンタクトを備えることが好ましい。

#### 【0013】

前記スイッチング素子は、非晶質シリコン活性層を備える薄膜トランジスターであることが好ましい。

前記第1のノードは、前記第1の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードであることが好ましい。 40

前記第1の制御信号は、直前のステージのゲート駆動信号であることが好ましい。

#### 【0014】

前記少なくとも2つのコンタクトは、透明導電体を備えることが好ましい。

前記透明導電体は、インジウム錫酸化物（ITO）を含むことが好ましい。

前記本発明の目的を達成するために、本発明のさらに他の側面によれば、スイッチング薄膜トランジスターと、前記スイッチング薄膜トランジスターに印加された信号電圧を液晶に加えるための画素電極、及び前記画素電極に印加された信号電圧を一定時間以上に維持するストレージキャパシターを備える画素がマトリックス状に配列された基板と、前記基板の上に形成された複数のゲート線を駆動するために前記基板の上に形成されたゲートドライバーとを備え、前記ゲートドライバーは、ゲート駆動信号を出力する複数のステー 50

ジより構成されるシフトレジスターを備え、前記ステージは、第1のクロック信号及び第2のクロック信号に基づいて、ゲート駆動信号を出力端子に与えるためのプルアップ回路と、ゲートオフ信号を前記出力端子に与えるためのプルダウン回路と、第1の制御信号に基づいて、前記プルアップ回路を駆動するプルアップ駆動回路と、第2の制御信号に基づいて前記プルダウン回路を駆動するプルダウン駆動回路とを備え、前記ステージは複数のスイッチング素子を備え、前記第1のクロック信号、第2のクロック信号、第1の制御信号または第2の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードのうち少なくとも1つのノードは、少なくとも2つのコンタクトを備えることを特徴とする薄膜トランジスター基板を提供する。

【0015】

前記少なくとも1つのノードは、前記第1の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードであることが好ましい。

前記第1の制御信号は、直前のステージのゲート駆動信号である。

前記画素のスイッチング薄膜トランジスターは、非晶質シリコン薄膜トランジスターであることが好ましい。

【0016】

前記本発明の目的を達成するために、本発明のさらに他の側面によれば、スイッチング薄膜トランジスターと、前記スイッチング薄膜トランジスターに印加された信号電圧を液晶に加えるための画素電極、及び前記画素電極に印加された信号電圧を一定時間以上に維持するストレージキャパシターを備える画素がマトリックス状に配列された基板と、前記基板の上に形成された複数のゲート線を駆動するために前記基板の上に形成されたゲートドライバーを備え、前記ゲートドライバーは、ゲート駆動信号を出力する複数のステージより構成されるシフトレジスターを備え、前記ステージは、第1のクロック信号及び第2のクロック信号に基づいて、ゲート駆動信号を出力端子に与えるためのプルアップ回路と、ゲートオフ信号を前記出力端子に与えるためのプルダウン回路と、第1の制御信号に基づいて前記プルアップ回路を駆動するプルアップ駆動回路と、第2の制御信号に基づいて前記プルダウン回路を駆動するプルダウン駆動回路とを備え、前記ステージは、複数のスイッチング素子及び前記複数のスイッチング素子のうち第1のスイッチング素子に接続されている冗長スイッチング素子を備えることを特徴とする薄膜トランジスター基板を提供する。

【0017】

前記冗長スイッチング素子は、前記プルダウン駆動回路に作り込まれる少なくとも1つのスイッチング素子に接続されていることが好ましい。

前記第1のクロック信号、第2のクロック信号、第1の制御信号または第2の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードのうち第1のノードは、少なくとも2つのコンタクトを備えることが好ましい。

【0018】

前記第1のノードは、前記第1の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードであることが好ましい。

前記第1の制御信号は、以前のステージのゲート駆動信号であることが好ましい。

前記スイッチング薄膜トランジスターは、非晶質シリコン薄膜トランジスターであることが好ましい。

【0019】

前記本発明の目的を達成するために、本発明のさらに他の側面によれば、ゲートドライバー及び複数の画素を備え、各画素は、スイッチング薄膜トランジスターと、前記スイッチング薄膜トランジスターに印加された信号電圧を液晶に加えるための画素電極、及び前記画素電極に印加された信号電圧を一定時間以上に維持するストレージキャパシターを備える薄膜トランジスター基板と、カラーフィルター及び前記液晶に電圧を印加するための共通電極を有するカラーフィルター基板とを備え、前記ゲートドライバーは、ゲート駆動信号を出力する複数のステージより構成されるシフトレジスターを備え、前記ステージは

10

20

30

40

50

、第1のクロック信号及び第2のクロック信号に基づいてゲート駆動信号を出力端子に与えるためのプルアップ回路と、ゲートオフ信号を前記出力端子に与えるためのプルダウン回路と、第1の制御信号に基づいて前記プルアップ回路を駆動するプルアップ駆動回路と、第2の制御信号に基づいて前記プルダウン回路を駆動するプルダウン駆動回路とを備え、前記ステージは複数のスイッチング素子を備え、前記第1のクロック信号、第2のクロック信号、第1の制御信号または第2の制御信号が印加される信号線と前記スイッチング素子が電気的に接続されるノードのうち少なくとも1つのノードは、少なくとも2つのコンタクトを備えることを特徴とする液晶表示装置を提供し。

#### 【0020】

前記本発明の目的を達成するために、本発明のさらに他の側面によれば、ゲートドライバー及び複数の画素を備え、各画素は、スイッチング薄膜トランジスターと、前記スイッチング薄膜トランジスターに印加された信号電圧を液晶に加えるための画素電極、及び前記画素電極に印加された信号電圧を一定時間以上に維持するストレージキャパシターを備える薄膜トランジスター基板と、カラーフィルター及び前記液晶に電圧を印加するための共通電極を有するカラーフィルター基板とを備え、前記ゲートドライバーは、ゲート駆動信号を出力する複数のステージより構成されるシフトレジスターを備え、前記ステージは、第1のクロック信号及び第2のクロック信号に基づいて、ゲート駆動信号を出力端子に与えるためのプルアップ回路と、ゲートオフ信号を前記出力端子に与えるためのプルダウン回路と、第1の制御信号に基づいて前記プルアップ回路を駆動するプルアップ駆動回路と、第2の制御信号に基づいて前記プルダウン回路を駆動するプルダウン駆動回路とを備え、前記ステージは、複数のスイッチング素子及び前記複数のスイッチング素子のうち所定のスイッチング素子に接続されている冗長スイッチング素子を備えることを特徴とする液晶表示装置を提供する。

#### 【発明の効果】

#### 【0021】

本発明によれば、所定のノードに接続されるコンタクトを少なくとも2以上のコンタクトにより構成することにより、これらのうち1つのコンタクトが腐食されて変色及び剥離が起きた場合であっても、もう1つのコンタクトにノードを接続すればよいので、コンタクト不良を防止することが可能になる。

#### 【発明を実施するための最良の形態】

#### 【0022】

以下、添付図面に基づき、本発明の好適な実施の形態について詳細に説明する。

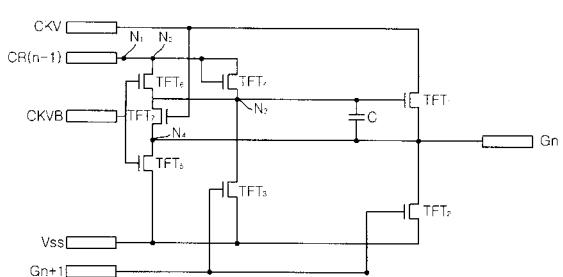

図3Aは、従来の技術によるゲートドライバーの概略回路図であり、図3Bは、ゲートドライバーノードの電流測定値を示すグラフである。

この図3Aは、シフトレジスターを構成する複数個の縦続接続されたステージのうち個別ステージの概略回路図であり、このステージは、複数個の非晶質シリコン薄膜トランジスタTFT<sub>1</sub>～TFT<sub>7</sub>と、キャパシターCとにより構成されている。このとき、信号入力端子、例えば、クロック信号CKV、反転クロック信号CKVB、前段のキャリー信号CR<sub>(n-1)</sub>などを印加するための信号線は、非晶質シリコンTFTのゲート電極と同じ平面上に形成されるため、これらの信号線を非晶質シリコンTFTのソース／ドレイン電極と電気的に接続するために多数のコンタクトが形成される。

#### 【0023】

一方、図3Aに示すステージが縦続接続されてなるシフトレジストを有するゲートドライバーを作り込んでいる基板の信頼性を評価するとき、一部のコンタクトにおいてのみコンタクト不良が現れる理由を極めるために、ゲートドライバーの各ノードに流れる電流を測定した。図3Aには、信号線と非晶質シリコンTFTが接続されるノード及びTFT同士が接続されるノードが示してあり、これらのノードではコンタクトにより互いに電気的に接続される。

#### 【0024】

図3Bは、各ノードに流れる電流を測定した結果を示すグラフである。第1のノードN

10

20

30

40

50

<sub>1</sub> 及び第2のノードN<sub>2</sub>に流れる電流は約75μA程度であり、他のノード、例えば、第3のノードN<sub>3</sub>及び第4のノードN<sub>4</sub>に比べて約2倍以上高い電流が流れている。このとき、第2のノードN<sub>2</sub>は、前段のキャリー信号C R ( n - 1 )の入力端子と非晶質シリコンTFT<sub>6</sub>が電気的に接続されるノードである。

#### 【0025】

一方、非晶質シリコンTFTを用いたゲートドライバーが作り込まれた基板に対して、高温多湿な条件下で信頼性の評価を行うと、上述の通り、高い電流が流れるノード、すなわち、第1のノードN<sub>1</sub>及び第2のノードN<sub>2</sub>に接続されているコンタクトだけが腐食されて変色及び剥離が起こる。これは、コンタクトに水分が浸透して変色が起こるとき、第1のノードN<sub>1</sub>及び第2のノードN<sub>2</sub>には他のノードに比べて相対的に高い電流が流れるため、その分だけ高熱が発生し、その熱により腐食されたコンタクトが剥離されるためである。

#### 【0026】

このため、このように高い電流が流れるノードに接続されているコンタクトが腐食により変色及び剥離された場合であっても、ノード同士が電気的に切断されることを防ぐことが重要であるが、このために、本発明においては、ノードに接続されるコンタクトを単一ではなく、少なくとも2以上にすることにより、これらのうち1つのコンタクトが腐食により変色及び剥離されても、もう1つのコンタクトによりノード同士の電気的な切断を防いでいる。このようなコンタクト不良が防止可能なゲートドライバーを以下の実施形態を参照して一層詳細に説明する。

#### 【0027】

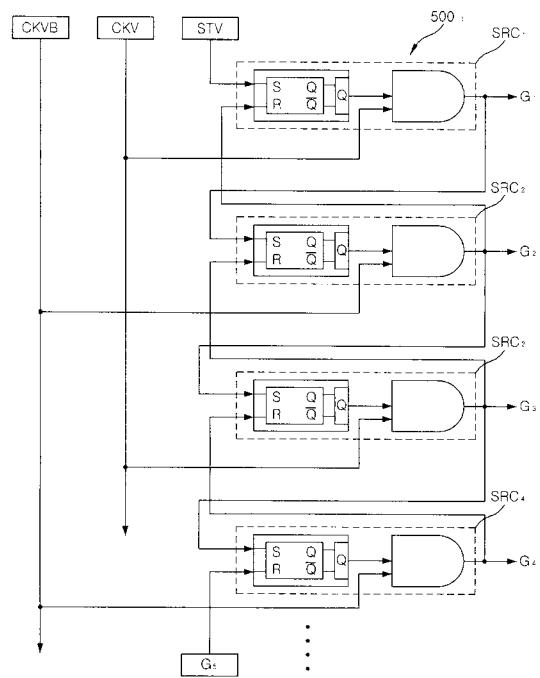

図4は、本発明によるゲートドライバーのシフトレジスターの機能ブロック図である。

図4に示すように、ゲート駆動信号G<sub>1</sub>、G<sub>2</sub>、...、G<sub>n</sub>を出力するゲートドライバー500はシフトレジスターを備え、シフトレジスターは、複数のステージSRC<sub>1</sub>、SRC<sub>2</sub>、...、SRC<sub>n</sub>を備える。ステージSRC<sub>1</sub>、SRC<sub>2</sub>、...、SRC<sub>n</sub>のそれぞれは、S-R( Set - Reset )ラッチとANDゲートとにより構成される。S-Rラッチは、前段のキャリー信号、すなわち、ゲート出力信号によりセットされ、次段のキャリー信号、すなわち、ゲート出力信号によりリセットされる。ラッチがセットされた状態で、クロック信号が「ハイ」の信号であるとき、ゲート駆動信号が出力される。

#### 【0028】

奇数番目のステージSRC<sub>1</sub>、SRC<sub>3</sub>、...には第1のクロック信号CKVが供給され、偶数番目のステージSRC<sub>2</sub>、SRC<sub>4</sub>、...には第2のクロック信号CKVBが供給されている。第1のクロック信号CKVと第2のクロック信号CKVBは互いに逆位相を有する。第1のステージ及び最後のステージSRC<sub>1</sub>、SRC<sub>n</sub>を除いて、各ステージの出力端子が次のステージの入力端子と直前のステージの入力端子にそれぞれ接続される。

#### 【0029】

第1のステージSRC<sub>1</sub>は、開始信号STVを供給されて第1のゲート線を選択する第1のゲート駆動信号G<sub>1</sub>を出力する。また、第1のゲート駆動信号G<sub>1</sub>は、第2のステージSRC<sub>2</sub>の入力端子に印加され、第2のステージSRC<sub>2</sub>は、前述の信号と共に直前のステージからの第1のゲート駆動信号G<sub>1</sub>と第3のゲート駆動信号G<sub>3</sub>を供給されて第2のゲート線を選択する第2のゲート信号G<sub>2</sub>を出力する。このような方式により、n番目のステージSRC<sub>n</sub>は、出力端子を介して第nのゲート駆動信号G<sub>n</sub>を出力する。一方、前述のように縦続接続された複数のステージからなるシフトレジスターを有するゲートドライバーは、非晶質シリコンTFTを用い、液晶表示装置の下部基板、すなわち、薄膜トランジスター基板の一側の上に組み付けられる。

#### 【0030】

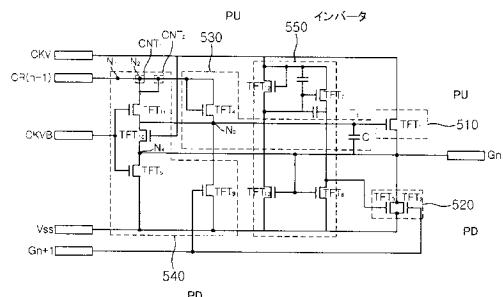

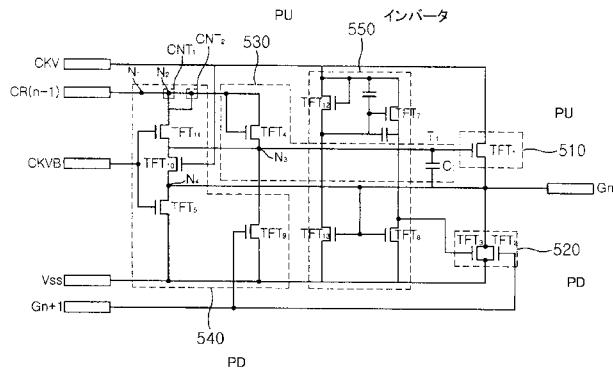

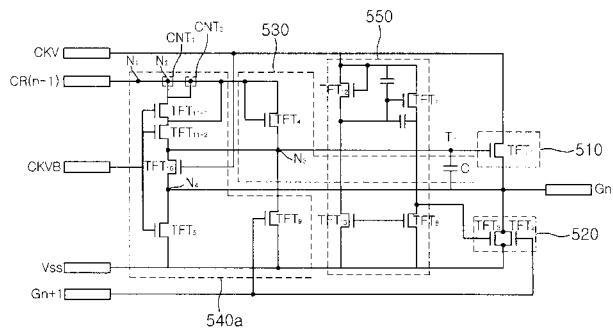

図5は、本発明の一実施形態によるゲートドライバーの概略回路図である。

図5に示すように、シフトレジスターの各ステージは、プルアップ回路510、プルダ

10

20

30

40

50

ウン回路 520、プルアップ駆動回路 530、プルダウン駆動回路 540 及びインバータ 550 を備える。

プルアップ回路 510 は、クロック信号 CKV またはこれとは逆位相を有するクロック反転信号 CKVB を出力端子に供給する。この実施形態において、プルアップ回路 510 は TFT<sub>1</sub> を備え、TFT<sub>1</sub> は、クロック信号 CKV の入力端子と接続されてゲート駆動信号を出力する。

#### 【0031】

プルアップ回路 510 はプルアップ駆動回路 530 により駆動されるが、プルアップ駆動回路 530 は、TFT<sub>4</sub> とキャパシター C により構成される。キャパシター C は、T<sub>1</sub> ノードと出力端子との間に接続され、TFT<sub>4</sub> は、前段のキャリー信号、すなわち、前段のゲート駆動信号が入力される制御信号の入力端子 CR<sub>(n-1)</sub> と接続される。制御信号の入力端子 CR<sub>(n-1)</sub> に「ハイ」の信号が入力されると、キャパシター C に電荷が充電されて TFT<sub>1</sub> がターンオンし、クロック信号 CKV が出力端子に出力され、結果として、ゲート線の上に接続されている全ての非晶質 TFT をターンオンさせる。

#### 【0032】

プルダウン回路 520 は、出力端子にゲートオフ信号を出力すると共に、プルダウン駆動回路 540 により駆動される。

プルダウン回路 520 は TFT<sub>2</sub> 及び TFT<sub>3</sub> を備え、TFT<sub>2</sub> は、ゲートオフ信号が入力されるゲートオフ信号入力端子 Vss と接続され、次段のゲート駆動信号 G<sub>n+1</sub> が入力されると、ゲート駆動信号をゲートオフ信号として放電し、TFT<sub>3</sub> は、クロック信号 CKV により同期されてゲートオフ信号レベルを維持する。

#### 【0033】

プルダウン駆動回路 540 は、プルダウン回路 520 を駆動すると共に、4 個の薄膜トランジスタ TFT<sub>5</sub>、TFT<sub>9</sub>、TFT<sub>10</sub>、TFT<sub>11</sub> により構成される。TFT<sub>5</sub> は、クロック反転信号 CKVB により同期されてゲートオフ信号レベルを維持し、TFT<sub>9</sub> は、ゲート駆動信号をゲートオフ信号として放電し、TFT<sub>10</sub> 及び TFT<sub>11</sub> はそれぞれ、クロック信号 CKV とクロック反転信号 CKVB により T<sub>1</sub> ノードをオフレベルに維持する。インバータ 550 は、TFT<sub>3</sub> を駆動するためのものであり、4 個の薄膜トランジスタ TFT<sub>7</sub>、TFT<sub>8</sub>、TFT<sub>12</sub>、TFT<sub>13</sub> を備える。

#### 【0034】

一方、上述のように、他のノードに流れる電流に比べて高い電流が流れる第 1 のノード N<sub>1</sub> 及び第 2 のノード N<sub>2</sub> のうち、この実施形態においては、第 2 のノード N<sub>2</sub> を 2 つのコンタクト CNT<sub>1</sub>、CNT<sub>2</sub> により接続している。しかし、コンタクトの個数はこれに限定されるものではなく、2 以上のコンタクトに接続してもよい。

また、この実施形態においては、第 2 のノード N<sub>2</sub>、すなわち、前段のゲート駆動信号が入力される制御信号の入力端子 CR<sub>(n-1)</sub> と TFT<sub>11</sub> との間のノードを 2 つのコンタクトに接続することを想定しているが、他のノードに 2 以上のコンタクトを形成することも可能である。このとき、コンタクトとしては、ITO などの透明導電体を用いることが好みしい。

#### 【0035】

上述のように、高い電流が流れるノードにコンタクトを少なくとも 2 以上形成することにより、これらのうち 1 つのコンタクトが水分の浸透により変色及び剥離されてコンタクト不良が発生した場合であっても、もう 1 つの冗長コンタクトにノードが接続されるので、正常にゲート駆動信号を出力することが可能になる。

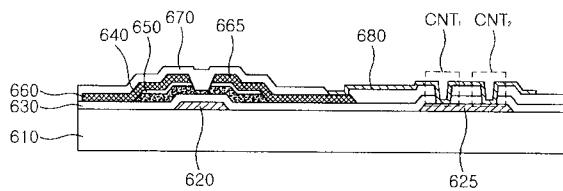

図 6 は、図 5 に示すコンタクトの概略断面図である。図 6 には、制御信号の入力端子 CR<sub>(n-1)</sub> と TFT<sub>11</sub> との間のノードに形成された 2 つのコンタクト CNT<sub>1</sub>、CNT<sub>2</sub> の概略断面図が示してある。

#### 【0036】

基板 610 の上に第 1 の導電性膜を形成した後、感光膜マスクを用いてパターニング工程を行うことにより、ゲート電極 620 及び制御信号の入力端子 CR<sub>(n-1)</sub> と接続さ

10

20

30

40

50

れる信号線 625 を形成する。

その上部にゲート絶縁膜 630、活性層 640 及びオーミック接触層 650 を順に形成した後、感光膜マスクパターンを用いてエッチング工程を行うことにより、薄膜トランジスターの活性領域を限定する。このとき、活性層 640 としては、液晶パネル上の TFT の活性層と同じ材料である非晶質シリコン層を用い、オーミック接触層 650 としては、シリサイド、N型不純物またはP型不純物が高濃度にてドープされた非晶質シリコン層を用いる。

#### 【0037】

次に、全面に第2の導電性膜を形成した後、感光膜マスクパターンを用いてエッチングすることにより、ソース及びドレイン電極 660、665 及びソース線を形成する。

その上部に絶縁膜 670 を形成し、ドレイン電極 665 の上部の絶縁膜の一部を除去してコンタクトホールを形成した後、制御信号の入力端子 CR<sub>(n-1)</sub> と接続される信号線 625 の上のゲート絶縁膜 630 と絶縁膜 670 の一部を除去して2つのコンタクトホールを形成する。次いで、その上部に導電性層 680 を形成し、2重コンタクト CNT<sub>1</sub>、CNT<sub>2</sub> を形成する。このとき、導電性層 680 は、透明導電体、例えば、ITO (Indium Tin Oxide)などを用いて形成する。

#### 【0038】

図7は、本発明の他の実施形態によるゲートドライバーの概略回路図である。

図7には、本発明の他の実施形態によるシフトレジスターの各ステージに対する概略回路図が示してあるが、図5の実施形態のものと比較して、所定の TFT に冗長 TFT をさらに接続しているという点で異なり、任意のノードに複数のコンタクトを形成することによりコンタクト不良を防ぐような構造はほとんど同様であるため、以下では異なる部分についてのみ説明する。

#### 【0039】

図7に示すように、シフトレジスターの各ステージは、プルアップ回路 510、プルダウン回路 520、プルアップ駆動回路 530、プルダウン駆動回路 540 及びインバータ 550 を備える。

プルダウン駆動回路 540 は、プルダウン回路 520 を駆動すると共に、4個の TFT TFT<sub>5</sub>、TFT<sub>9</sub>、TFT<sub>10</sub>、TFT<sub>11-1</sub> と単一の冗長薄膜トランジスタ TFT<sub>11-2</sub> により構成される。TFT<sub>5</sub> は、クロック反転信号 CKVB により同期されてゲートオフ信号レベルを維持し、TFT<sub>9</sub> は、ゲート駆動信号をゲートオフ信号として放電し、TFT<sub>10</sub> 及び TFT<sub>11-1</sub> はそれぞれクロック信号 CKV とクロック反転信号 CKVB により T<sub>1</sub> ノードをオフレベルに維持する。また、冗長薄膜トランジスタ TFT<sub>11-2</sub> は、TFT<sub>11-1</sub> が不良である場合に備えて、TFT<sub>11-1</sub> に接続される。その結果、TFT のうちいずれか1つの TFT がコンタクト不良により駆動されなくなった場合であっても、残りの TFT が動作可能である。

#### 【0040】

一方、上述のように、他のノードに流れる電流に比べて高い電流が流れる第1のノード N<sub>1</sub> 及び第2のノード N<sub>2</sub> のうち、この実施形態においては、第2のノード N<sub>2</sub> を2つのコンタクト CNT<sub>1</sub>、CNT<sub>2</sub> に接続している。しかし、コンタクトの個数はこれに限定されるものではなく、2以上のコンタクトに接続してもよい。

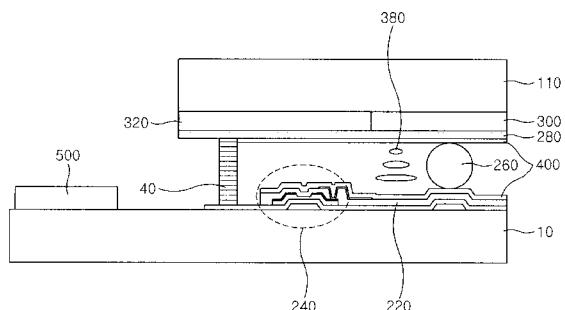

図8は、本発明によるゲートドライバーを備えた液晶表示装置の概略断面図である。

#### 【0041】

図8に示すように、液晶表示装置のカラーフィルター基板 110 には、ブラックマトリックス 320 と、カラーフィルター 300 及び共通電極 280 が順に形成される。

ブラックマトリックス 320 は、カラーフィルターと画素との間に形成されて光漏れを抑え、カラーフィルター 300 は、3種の基本色（赤色、緑色、青色）の染料や顔料を含む樹脂フィルムから形成される。また、共通電極 280 は、透明な導電体である ITO などから形成され、液晶セルに電圧を印加する。

#### 【0042】

10

20

30

40

50

薄膜トランジスター基板 10 には、液晶に信号電圧を印加 / 遮断するスイッチング素子としての薄膜トランジスター 240、透明で且つ導電性を有するITOから形成されると共に、薄膜トランジスターに印加された信号電圧を液晶セルに加える画素電極 220 と、画素電極に印加された信号電圧を一定時間以上に維持するストレージキャパシター（図示せず）とが形成される。カラーフィルター基板 110 と薄膜トランジスター基板 10 の最上層には、ポリイミドからなる薄い有機膜であって、液晶を配向するための配向膜 400 が形成され、カラーフィルター基板 110 と薄膜トランジスター基板 10 との間に隙間を取るためのスペーサー 260 がカラーフィルター基板と薄膜トランジスター基板との間に配置され、スペーサーによりできた空間に液晶層 260 が注入される。シールパターン 40 は基板の周辺部に形成され、カラーフィルター基板と薄膜トランジスター基板を貼り合わせる。なお、シールパターン 40 は、周辺回路寄りに形成することもできる。10

#### 【0043】

薄膜トランジスター基板の一側の上部には、薄膜トランジスター 240 をターンオンまたはターンオフさせるためのゲート駆動信号を出力するゲートドライバー 500 が組み付けられる。ゲートドライバー 500 内に作り込まれたスイッチング素子である薄膜トランジスターもまた、画素内に含まれた薄膜トランジスターと同じ非晶質シリコン TFT から形成されるため、同じ製造工程により製造可能である。その結果、ポリシリコン TFT を用いる場合よりも製造工程が格段に単純化される。また、上述のように、ゲートドライバーのノードのうち高い電流が流れるノードに接続されるコンタクトは、單一コンタクトではなく、2重コンタクトにすることで、2つのコンタクトのうちどちらか一方のコンタクトが剥離された場合であっても、ゲート駆動信号を出力する上で差し支えのないようにする。20

#### 【0044】

このような液晶表示装置の駆動原理を説明すると、ゲートドライバー 500 から 1 フレームに対する各ゲート線が選択され、選択されたゲート線にゲート駆動信号が印加されると、薄膜トランジスター 240 に位置するゲート電極にゲート駆動信号が印加され、選択されたゲート線に位置する薄膜トランジスターのチャンネルは開かれる。このとき、ソースドライバー（図示せず）は、映像情報に基づく画像信号電圧をデータ線に伝え、データ線に伝わった信号電圧は、開かれた薄膜トランジスターを介して液晶キャパシターとストレージキャパシターに充電される。薄膜トランジスター・チャンネルが閉じられると、液晶キャパシターとストレージキャパシターに充電された電圧は維持され、電圧の充電のためのストレージキャパシターにより、画素には充電された電圧が次のフレームまで維持される。30

#### 【0045】

以上、本発明によるゲートドライバー、これを備えた薄膜トランジスター基板及び液晶表示装置について説明したが、これは单なる例示的なものに過ぎず、本発明はこれらに限定されるものではない。なお、特許請求の範囲において請求するように、本発明の要旨を逸脱することなく、この技術分野における通常の知識を持った者であれば誰でも種々の変更実施が行える範囲まで本発明の技術的な精神があると言えるであろう。

#### 【図面の簡単な説明】

#### 【0046】

【図 1】通常のゲートドライバーが作り込まれた液晶パネルの概略構成図である。

【図 2】ゲートドライバーの構造を説明するための概略構成図である。

【図 3A】従来の技術によるゲートドライバーの概略回路図である。

【図 3B】従来の技術によるゲートドライバーノードの電流測定値を示すグラフである。

【図 4】本発明によるゲートドライバーのシフトレジスターの機能ブロック図である。

【図 5】本発明の一実施形態によるゲートドライバーの概略回路図である。

【図 6】図 5 に示すコンタクトの概略断面図である。

【図 7】本発明の他の実施形態によるゲートドライバーの概略回路図である。

【図 8】本発明によるゲートドライバーを備えた液晶表示装置の概略断面図である。50

## 【符号の説明】

【0 0 4 7】

5 0 0 : ゲートドライバー

【図 1】

【図 2】

【図 3 A】

【図 3 B】

【図4】

【図5】

【図6】

【図7】

【図8】

## フロントページの続き

| (51) Int.Cl.                  | F I          | テーマコード(参考) |

|-------------------------------|--------------|------------|

| <b>G 02 F 1/133 (2006.01)</b> | G 09 G 3/20  | 6 1 2 L    |

|                               | G 09 G 3/20  | 6 2 1 M    |

|                               | G 09 G 3/20  | 6 8 0 G    |

|                               | G 09 G 3/20  | 6 7 0 A    |

|                               | G 02 F 1/133 | 5 5 0      |

(72)発明者 姜 信 宅

大韓民国448 - 519 京畿道龍仁市水枝区上 ヒョン 洞ソンウォンサンテビル230 - 180

1号

(72)発明者 安 炳 宰

大韓民国443 - 725 京畿道水原市靈通区靈通洞ビヨクジェクゴルウソンアパート826 - 12

03

(72)発明者 李 鍾 赫

大韓民国150 - 752 ソウル市永登浦区堂山洞2街現代アパート102 - 1802

(72)発明者 金 有 珍

大韓民国336 - 841 忠清南道牙山市湯井面鳴岩里クリスタルタウンビチドン610

F ターム(参考) 2H093 NA16 NC10 NC22 NC34 ND46 ND47 ND48 ND60 NE03

5C006 AF51 BB16 BC06 BC20 EB04

5C080 AA10 BB05 DD30 FF11 JJ02 JJ03 JJ05 JJ06 KK02

5F033 HH38 JJ38 NN34 VV15

5F110 AA03 AA26 BB02 CC07 GG02 GG15 HK05 HK09 HK16 HK21

HL07 HM19 NN72

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 栅极驱动器，具有该栅极驱动器的薄膜晶体管基板，以及液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2007188079A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2007-07-26 |

| 申请号            | JP2007002111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 申请日     | 2007-01-10 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | 金汎俊<br>姜信宅<br>安炳宰<br>李鍾赫<br>金有珍                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 发明人            | 金汎俊<br>姜信宅<br>安炳宰<br>李鍾赫<br>金有珍                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G09G3/36 H01L29/786 H01L23/522 H01L21/768 G09G3/20 G02F1/133                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| CPC分类号         | G09G3/3677                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G09G3/36 H01L29/78.612.C H01L29/78.612.B H01L21/90.B G09G3/20.622.B G09G3/20.612.L G09G3 /20.621.M G09G3/20.680.G G09G3/20.670.A G02F1/133.550 G11C19/00 G11C19/00.J G11C19/28.D G11C19/28.230                                                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NC10 2H093/NC22 2H093/NC34 2H093/ND46 2H093/ND47 2H093/ND48 2H093 /ND60 2H093/NE03 5C006/AF51 5C006/BB16 5C006/BC06 5C006/BC20 5C006/EB04 5C080/AA10 5C080/BB05 5C080/DD30 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ05 5C080/JJ06 5C080 /KK02 5F033/HH38 5F033/JJ38 5F033/NN34 5F033/VV15 5F110/AA03 5F110/AA26 5F110/BB02 5F110/CC07 5F110/GG02 5F110/GG15 5F110/HK05 5F110/HK09 5F110/HK16 5F110/HK21 5F110 /HL07 5F110/HM19 5F110/NN72 2H193/ZA04 2H193/ZF22 2H193/ZK21 2H193/ZP03 5B074/AA03 5B074/CA01 5B074/DB01 |         |            |

| 优先权            | 1020060002843 2006-01-10 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 其他公开文献         | <a href="#">JP5630937B2</a><br><a href="#">JP2007188079A5</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

**摘要(译)**

使用能够防止接触故障的非晶硅TFT提供栅极驱动器。A至驱动多个形成于液晶面板上的栅线，栅极驱动器包括多个级组成的移位寄存器，用于输出的栅极驱动信号，每个所述多个级中的基于所述第一时钟信号和第二时钟信号，用于向输出端提供的栅极驱动信号的上拉电路，用于向输出端提供栅极截止信号的下拉电路，所述第一控制信号基于该上拉驱动电路，用于驱动所述上拉电路，基于所述第二控制信号，和一个下拉驱动电路，用于驱动所述下拉电路，所述级包括多个开关元件，第一时钟信号，施加第二时钟信号，第一控制信号或第二控制信号的信号线和开关元件电连接的节点中预定节点包括多个触头。点域5