(19)日本国特許庁( J P )

(12) 公開特許公報 (A) (11)特許出願公開番号

特開2002 - 55362

(P2002 - 55362A)

(43)公開日 平成14年2月20日(2002.2.20)

|                          |      |                |              |

|--------------------------|------|----------------|--------------|

| (51) Int.Cl <sup>7</sup> | 識別記号 | F I            | マーク-コード (参考) |

| G 0 2 F 1/1368           |      | G 0 2 F 1/1368 | 2 H 0 9 2    |

| H 0 1 L 21/3213          |      | H 0 1 L 21/88  | C 5 F 0 3 3  |

| 21/3205                  |      |                | R 5 F 1 1 0  |

| 21/768                   |      | 21/90          | A            |

| 29/786                   |      | 29/78          | 612 D        |

審査請求 未請求 請求項の数 140 件 (全 166 件) 最終頁に続く

(21)出願番号 特願2001 - 46234(P2001 - 46234)

(71)出願人 390019839

三星電子株式会社

大韓民国京畿道水原市八達区梅灘洞416

(22)出願日 平成13年2月22日(2001.2.22) 大韓民国京畿道水原市八達区梅灘洞416

(22)出願日 平成13年2月22日(2001.2.22)

(72) 発明者 金湘甲

大韓民国ソウル市

三益アパート205棟913号

(31)優先権主張番号 2000 - 43505 大韓民国ソウル市江東区明逸洞309 - 1番地

(32) 優先日 平成12年7月27日(2000.7.27) 三益アパート205棟913号

(33) 優先権主張國 韓国(KR)

(72) 発明者 洪 むん

大韓民国京畿道城

ンマウル雙龍アパート401棟2202号

(74)代理人 100094145

弁理士 小野 由己男（外1名）

最終頁に続く

(54) 【発明の名称】 液晶表示装置用薄膜トランジスタ基板の製造方法

(57) 【要約】 (修正有)

【課題】 優れた接触特性を有し、低抵抗配線を有する薄膜トランジスタ基板の製造方法を提供する。

【解決手段】 アルミニウム系列の導電物質を積層し基板の上にゲート線22、ゲート電極及びゲートパッド24を含むゲート配線を形成し、ゲート絶縁膜30、半導体層及び抵抗性接触層を順次に形成し、クロムの下部膜とアルミニウム系列の上部膜とからなる導電物質を積層して、ゲート線と交差するデータ線、ソース電極、ドレーン電極及びデータパッドを含むデータ配線を形成する。この時、クロムの下部膜をC<sub>1</sub>またはH<sub>C</sub>1を含むエッチング用気体を用いてパターニングする。その後、保護膜を積層しドレーン電極、ゲートパッド及びデータパッドを露出する接触孔を形成し、IZOを積層しパターニングして、ドレーン電極66、ゲートパッド及びデータパッドと各々連結される画素電極、補助ゲートパッド及び補助データパッドを形成する。

## 【特許請求の範囲】

【請求項1】絶縁基板の上にアルミニウム系列の導電物質を積層しパターニングして、ゲート線、前記ゲート線と連結されているゲート電極を含むゲート配線を形成する段階、

ゲート絶縁膜を積層する段階、

半導体層を形成する段階、

下部膜と上部膜からなる導電層を積層しパターニングして、前記ゲート線と交差するデータ線、前記データ線と連結されており前記ゲート電極に隣接するソース電極及び前記ゲート電極に対して前記ソース電極の対向側に位置するドレーン電極を含むデータ配線を形成する段階、保護膜を積層しパターニングして、前記ドレーン電極の上部に第1接触孔を形成する段階、

前記保護膜の上部に前記第1接触孔を通じて前記ドレーン電極と連結される画素電極を形成する段階を含む液晶表示装置用薄膜トランジスタ基板の製造方法において、前記下部膜は前記半導体層と同時にパターニングする液晶表示装置用薄膜トランジスタ基板の製造方法。

【請求項2】前記画素電極はIZOで形成する請求項1に記載の液晶表示装置用薄膜トランジスタ基板の製造方法。

【請求項3】前記ゲート配線は、外部から走査信号の伝達を受けて前記ゲート線に伝達するゲートパッドをさらに含み、

前記データ配線は、外部から映像信号の伝達を受ける前記データ線に伝達するデータパッドをさらに含み、

前記保護膜は、前記データパッド及び前記ゲート絶縁膜とともに前記ゲートパッドを露出する第2及び第3接触孔を有し、

前記画素電極と同一の層に、前記第2及び第3接触孔を通じて前記ゲートパッド及び前記データパッドと電気的に連結される補助ゲートパッドと補助データパッドをさらに形成する請求項1に記載の液晶表示装置用薄膜トランジスタ基板の製造方法。

【請求項4】前記データ配線及び前記半導体層は、部分的に厚さの異なる感光膜パターンを利用した写真エッチング工程で同時に形成する請求項1に記載の液晶表示装置用薄膜トランジスタ基板の製造方法。

【請求項5】前記感光膜パターンは、第1厚さを有する第1部分、前記第1厚さより厚い第2部分、前記第1及び第2部分を除いた厚さのない第3部分を含む請求項1に記載の液晶表示装置用薄膜トランジスタ基板の製造方法。

【請求項6】前記写真エッチング工程において、前記感光膜パターンは第1領域、前記第1領域より低い透過率を有する第2領域及び前記第1領域より高い透過率を有する第3領域を含む請求項5に記載の液晶表示装置用薄膜トランジスタ基板の製造方法。

【請求項7】前記写真エッチング工程において、前記第1部分は前記ソース電極と前記ドレーン電極との間、前記第2部分は前記データ配線の上部に位置するように形成する請求項6に記載の液晶表示装置用薄膜トランジスタ基板の製造方法。

【請求項8】前記第1乃至第3領域の透過率を異なるように調節するために、光マスクには半透明膜または露光器の分解能より小さいスリットパターンが形成されている請求項7に記載の液晶表示装置用薄膜トランジスタ基板の製造方法。

【請求項9】前記半導体層と前記データ配線との間に抵抗性接触層を形成する段階をさらに含む請求項8に記載の液晶表示装置用薄膜トランジスタ基板の製造方法。

【請求項10】前記データ配線と前記抵抗性接触層及び前記半導体層を一つのマスクを使用して形成する請求項9に記載の液晶表示装置用薄膜トランジスタ基板の製造方法。

【請求項11】前記下部膜と前記抵抗性接触層及び前記半導体層は連続的に乾式エッチング方法でパターニングする請求項10に記載の液晶表示装置用薄膜トランジスタ基板の製造方法。

【請求項12】前記下部膜をパターニングするための乾式エッチング用気体はC<sub>2</sub>またはHClを含む請求項11に記載の液晶表示装置用薄膜トランジスタ基板の製造方法。

【請求項13】前記下部膜を300以下に形成する請求項1に記載の液晶表示装置用薄膜トランジスタ基板の製造方法。

【請求項14】前記下部膜及び上部膜はクロム及びアルミニウム系列で形成する請求項1に記載の液晶表示装置用薄膜トランジスタ基板の製造方法。

## 【発明の詳細な説明】

## 【0001】

【発明の属する技術分野】本発明は薄膜トランジスタ基板及びその製造方法に関するものである。

## 【0002】

【従来の技術】液晶表示装置は現在最も広く用いられている平板表示装置のうちの一つであって、電極が形成されている二つの基板とその間に挿入されている液晶層からなり、電極に電圧を印加して液晶層の液晶分子を再配列させることによって透過する光の量を調節する表示装置である。

【0003】液晶表示装置の中でも現在主に用いられているものは、二つの基板に電極が各々形成されていて電極に印加される電圧をスイッチングする薄膜トランジスタを有している液晶表示装置であり、薄膜トランジスタは二つの基板のうちの一つに形成されるのが一般的である。

【0004】このような液晶表示装置で信号遅延を防止するために、配線は低抵抗を有するアルミニウム(AI)またはアルミニウム合金(AI Alloy)などの低抵抗

抗物質を使用するのが一般的である。しかしながら、液晶表示装置でのように透明な導電物質のITO(indium tin oxide)を使用して画素電極を形成したりパッド部の信頼性を確保する場合、アルミニウム系列の金属とITOの接触特性がよくないため接触特性に優れた他の金属を介在させるようにするが、接触部ではアルミニウムまたはアルミニウム合金は除去しなければならぬため、製造工程が複雑になるという問題点を有している。また、アルミニウム系列の金属がケイ素の半導体層と接する場合にはアルミニウム系列の金属が半導体層に拡散するのを防止するために他の金属を介在しなければならないが、多層構造の配線を形成するためには互いに異なるエッティング条件が必要になる。

【0005】一方、液晶表示装置を製造する方法のうち、薄膜トランジスタが形成されている基板はマスクを用いた写真エッティング工程を通じて製造するのが一般的である。この時、生産費用を減らすためにはマスクの数を減少させることが好ましい。

#### 【0006】

【発明が解決しようとする課題】本発明が目的とする技術的課題は、優れた接触特性を有すると同時に低抵抗配線を有する薄膜トランジスタ基板の製造方法を提供することにある。

【0007】また、本発明の他の課題は薄膜トランジスタ基板の製造方法を単純化することである。

#### 【0008】

【課題を解決するための手段】このような問題点を解決するために、本発明ではアルミニウム系列の金属からなる配線と連結される導電膜をIZO(indium zinc oxide)で形成し、アルミニウム系列の配線と半導体層との間に介在しているクロムの導電膜を乾式エッティングでパターニングする。

【0009】本発明による薄膜トランジスタ基板の製造方法では、まず、絶縁基板の上にアルミニウム系列の導電物質を積層しパターニングしてゲート線、ゲート線と連結されているゲート電極を含むゲート配線を形成し、ゲート絶縁膜を積層する。続いてゲート絶縁膜の上部に半導体層を形成し、その上部にクロムの下部膜とアルミニウム系列の上部膜とからなる導電膜を積層しパターニングして、ゲート線と交差するデータ線、データ線と連結されておりゲート電極に隣接するソース電極及びゲート電極に対してソース電極の対向側に位置するドレーン電極を含むデータ配線を形成する。その後、保護膜を積層しパターニングしてドレーン電極の上部に第1接触孔を形成し、保護膜の上部にドレーン電極と電気的に連結される画素電極を形成する。この時、データ配線の下部膜は乾式エッティングでパターニングする。

【0010】ここで、画素電極は透明な導電物質であるIZOで形成することが好ましく、下部膜は300以下の厚さで形成することが良い。また、下部膜をエッチ

ングするための乾式エッティング用気体としてはCl<sub>2</sub>またはHClを含むことが好ましい。

【0011】ゲート配線は外部から走査信号の伝達を受けてゲート線に伝達するゲートパッドをさらに含み、データ配線は外部から映像信号の伝達を受けてデータ線に伝達するデータパッドをさらに含み、保護膜はデータパッド及びゲート絶縁膜とともにゲートパッドを露出する第2及び第3接触孔を有し、画素電極と同一の層に第2及び第3接触孔を通じてゲートパッド及びデータパッドと電気的に連結される補助ゲートパッドと補助データパッドをさらに形成することができる。

【0012】データ配線及び半導体層は部分的に厚さの異なる感光膜パターンを利用した写真エッティング工程で同時に形成することができ、感光膜パターンは第1厚さを有する第1部分、第1厚さより厚い第2部分、第1及び第2部分を除いた厚さのない第3部分を含むことが好ましい。

【0013】写真エッティング工程で感光膜パターンは、第1領域、前記第1領域より低い透過率を有する第2領域及び前記第1領域より高い透過率を有する第3領域を含む光マスクを用いて形成することができ、写真エッティング工程で第1部分はソース電極とドレーン電極との間、第2部分はデータ配線の上部に位置するように形成することができる。

【0014】第1乃至第3領域の透過率を異なるように調節するために、光マスクには半透明膜または露光器の分解能より小さいスリットパターンが形成されることができ、第1部分の厚さは第2部分の厚さに対して1/2以下に形成することができる。

【0015】なお、半導体層とデータ配線との間に抵抗性接触層を形成する段階をさらに含むことができ、データ配線と接触層及び半導体層を一つのマスクを使用して形成することができる。この時、下部膜と接触層と半導体層とを連続して乾式エッティングでパターニングする。

#### 【0016】

【発明の実施の形態】以下、添付した図面を参考として本発明の実施例による薄膜トランジスタ基板の製造方法について、本発明の属する技術分野にて通常の知識を有する者が容易に実施することができるよう詳細に説明する。

【0017】まず、図1及び図2を参照して本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板の構造について詳細に説明する。

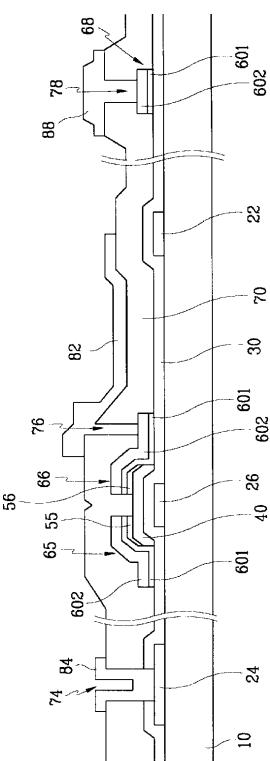

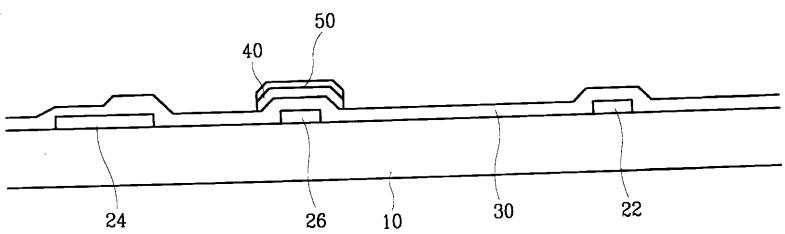

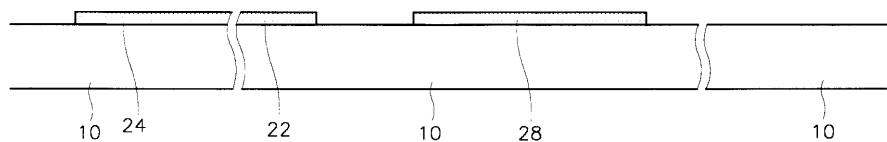

【0018】図1は本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板を示しており、図2は図1に示した薄膜トランジスタ基板をII-II'線に沿って切断して示した断面図である。

【0019】絶縁基板10の上に低抵抗を有するアルミニウム系列の金属物質からなるゲート配線が形成されている。ゲート配線は横方向に延びているゲート線22、

ゲート線22の端部に連結されていて外部からのゲート信号の印加を受けてゲート線に伝達するゲートパッド24及びゲート線22に連結されている薄膜トランジスタのゲート電極26を含む。

【0020】基板10の上には窒化ケイ素SiN<sub>x</sub>などからなるゲート絶縁膜30がゲート配線22、24、26を覆っており、ゲート絶縁膜30は以後に形成される保護膜70とともにゲートパッド24を露出する接触孔74を有する。

【0021】ゲート電極26のゲート絶縁膜30の上部には非晶質ケイ素などの半導体からなる半導体層40が島模様で形成されており、半導体層40の上部にはシリサイドまたはn型不純物が高濃度にドーピングされているn+水素化非晶質ケイ素などの物質で作られた抵抗性接触層54、56が各々形成されている。

【0022】抵抗性接触層54、56及びゲート絶縁膜30の上には、アルミニウム(Al)またはアルミニウム合金(Al alloy)、モリブデン(Mo)またはモリブデン-タングステン(MoW)合金、クロム(Cr)、タンタル(Ta)などの金属または導電体からなるデータ配線62、65、66、68が形成されている。データ配線は、縦方向に形成されてゲート線22と交差して画素を定義するデータ線62、データ線62の分枝であり抵抗性接触層55の上部まで延びているソース電極65、データ線62の一端部に連結されていて外部からの画像信号の印加を受けるデータパッド68、ソース電極65と分離されておりゲート電極26に対してソース電極65の反対側の抵抗性接触層56の上部に形成されているドレーン電極66を含む。

【0023】データ配線62、65、66、68はアルミニウム系列の単一膜で形成することが好ましいが、二重層以上に形成されることもできる。二重層以上に形成する場合には、一つの層は抵抗の小さい物質で形成し他の層は他物質との接触特性の良い物質で作ることが好ましい。その例としてはCr/A1(またはA1合金)またはA1/Moなどを挙げることができ、本発明の実施例においてデータ配線62、65、66、68は、Crの下部膜601とアルミニウム合金の上部膜602で形成されている。この時のCr膜601は上部膜602のアルミニウム系列の金属がケイ素層である半導体層40、抵抗性接触層55、56に拡散するのを防止する役割を果たす。

【0024】データ配線62、65、66、68及びこれらで遮られない半導体層40の上部には保護膜70が形成されている。保護膜70にはドレーン電極66及びデータパッド68を各々露出する接触孔76、78が各々形成されており、ゲート絶縁膜30とともにゲートパッド24を露出する接触孔74が形成されている。

【0025】保護膜70の上には接触孔76を通じてドレーン電極66と連結されており画素に位置する画素電

極82と接触孔74、78を通じて各々ゲートパッド24及びデータパッド68と連結されている補助ゲートパッド84及び補助データパッド88を含み、IZOからなる画素配線が形成されている。

【0026】ここで、画素電極82は図1及び図2のように、ゲート線22と重なって維持蓄電器を構成し、維持容量が不足した場合にはゲート配線22、24、26と同一の層に維持容量用配線を追加することもできる。

【0027】このような本発明の実施例による構造は低抵抗なアルミニウム系列の金属からなるゲート配線22、24、26及びデータ配線62、65、66、68を含んでいるため、大画面高精細の液晶表示装置に適用することができる。また、接触孔74、76、78でアルミニウム系列のゲートパッド24、データパッド68及びドレーン電極66は、IZOからなる補助ゲートパッド84、補助データパッド88及び画素電極82と各々連結されていてパッド部で腐食されないので、パッド部を含む接触部の信頼性を確保することができる。

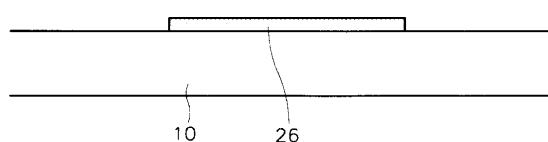

【0028】次に、このような本発明の第1実施例による構造の液晶表示装置用薄膜トランジスタ基板の製造方法について、図1及び図2と図3乃至図10を参照して詳細に説明する。

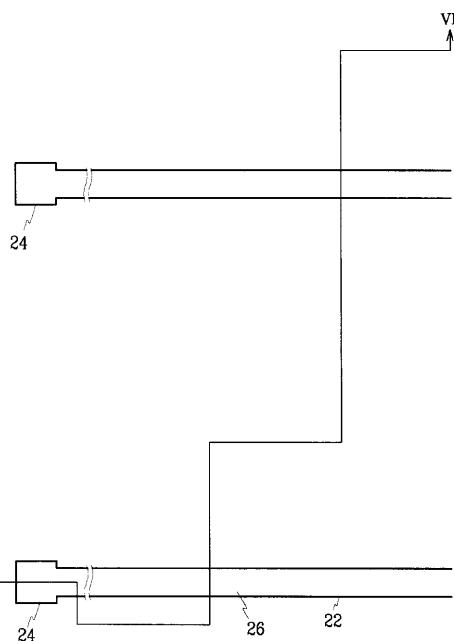

【0029】まず、図3及び図4に示したように基板10の上に低抵抗を有するアルミニウム系列の導電膜を2500程度の厚さで積層しパターニングして、ゲート線22、ゲート電極26及びゲートパッド24を含む横方向のゲート配線を形成する。

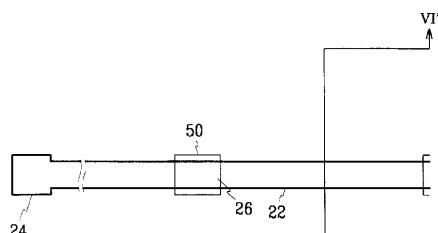

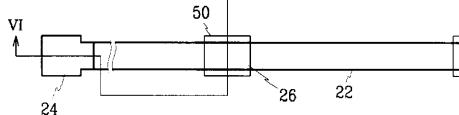

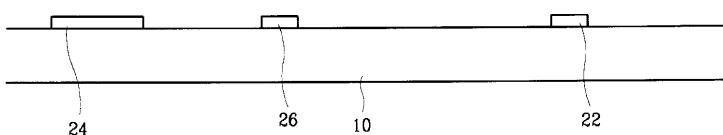

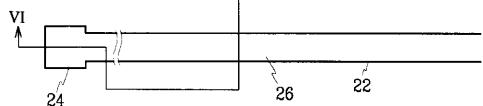

【0030】その後、図5及び図6に示したようにゲート絶縁膜30、非晶質ケイ素からなる半導体層40、ドーピングされた非晶質ケイ素層50の3層膜を連続して積層し、マスクを用いたパターニング工程で半導体層40とドーピングされた非晶質ケイ素層50をパターニングすることによってゲート電極24と対向するゲート絶縁膜30の上部に半導体層40と抵抗性接触層(ドーピングされた非晶質ケイ素に同じ)50を形成する。

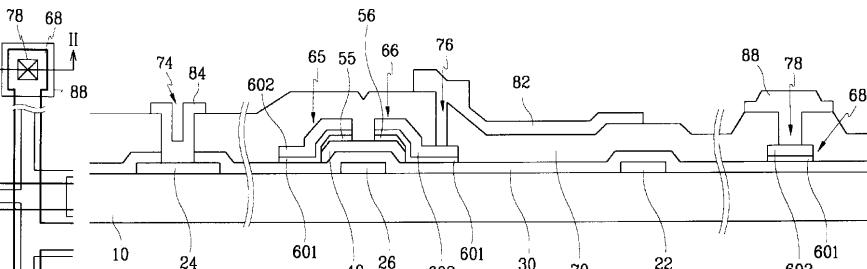

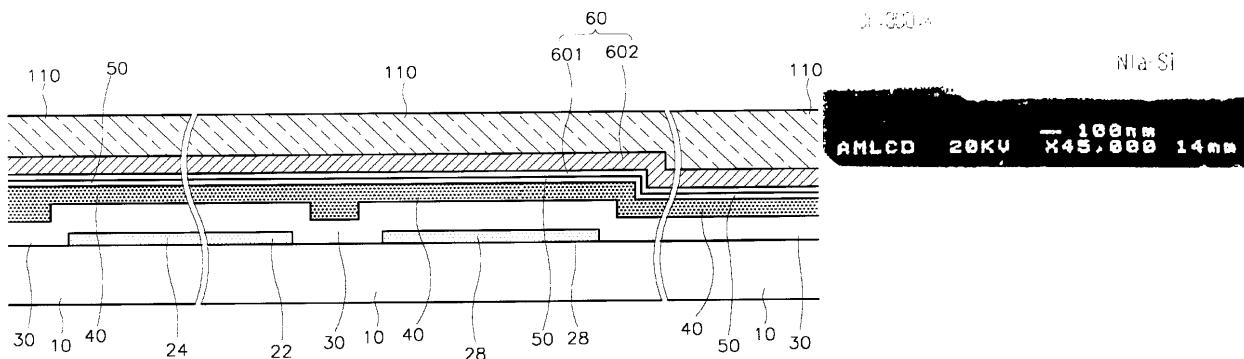

【0031】次に、図7乃至図8に示したようにクロムからなる下部膜601を300程度の厚さで、低抵抗を有するアルミニウム系列の金属からなる上部膜602を2500程度の厚さで各々順次に積層した後、マスクを利用した写真工程でパターニングして、ゲート線22と交差するデータ線62、データ線62と連結されてゲート電極26の上部まで延びているソース電極65、データ線62と一端部で連結されているデータパッド68及びソース電極65と分離されておりゲート電極26を中心としてソース電極65と対向するドレーン電極66を含むデータ配線を形成する。ここで、上部膜602は湿式または乾式エッチングでエッチングすることができ、クロムの下部膜601は乾式エッチングでエッチングし、このためにクロムの下部膜601は300以下に形成することが好ましい。

40

【0032】続いて、データ配線62、65、66、68で遮られないドーピングされた非晶質ケイ素層パターン50をエッチングしてゲート電極26を中心で両側で分離させる一方、両側のドーピングされた非晶質ケイ素層55、56の間の半導体層40を露出させる。続いで、露出された半導体層40の表面を安定化するために酸素プラズマ処理を実施することが好ましい。

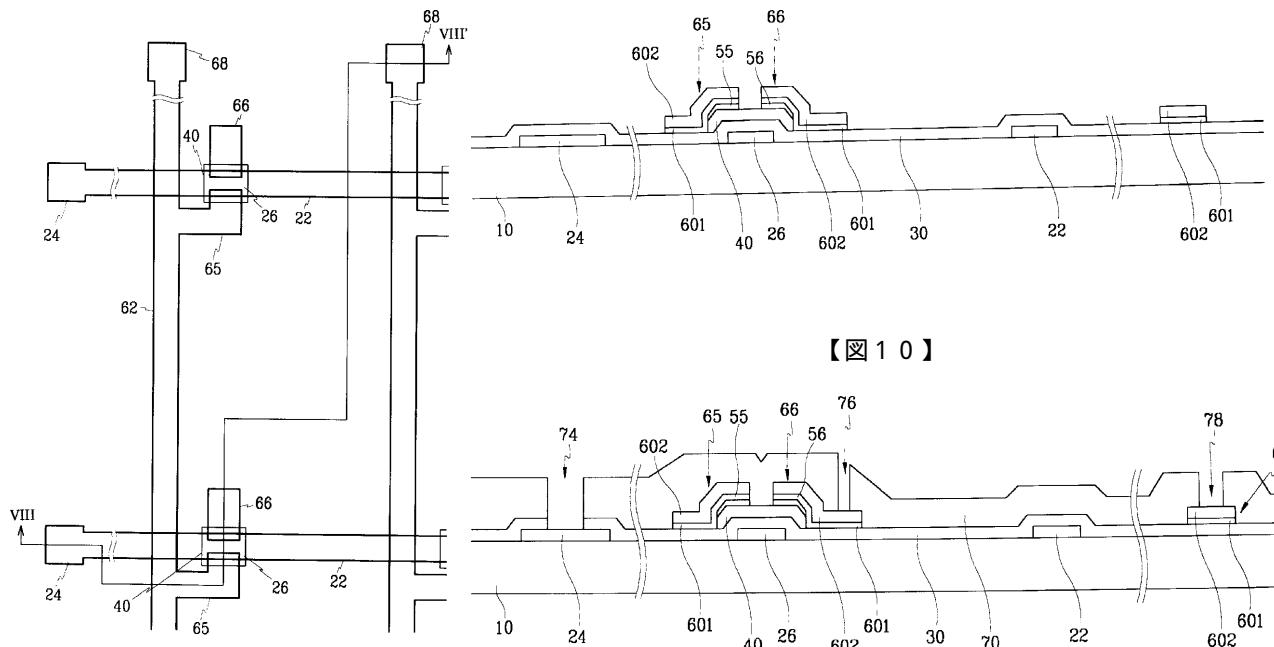

【0033】次に、図9及び図10に示したように、窒化ケイ素または有機絶縁膜からなる保護膜70を積層した後マスクを利用した写真エッチング工程でゲート絶縁膜30とともに乾式エッチングでパターニングして、ゲートパッド24、ドレーン電極66及びデータパッド68を露出させる接触孔74、76、78を形成する。続いで接触孔74、76、78を通じて露出されたゲートパッド24及びドレーン電極66とデータパッド68の上部膜602の表面を乾式洗浄する。この時に使用する気体としてはSF<sub>6</sub>/O<sub>2</sub>などを挙げることができる。続いで、以後に形成されるIZO膜である画素電極82、補助ゲートパッド84、補助データパッド88とアルミニウム膜であるドレーン電極66、ゲートパッド24、データパッド68との接触抵抗を最少化するためにアニーリング工程を通じてアルミニウム系列の金属膜66、24、68の上部に残留する物質を除去することができ、アルミニウム系列の金属膜66、24、68の上部にAl<sub>x</sub>Si<sub>x</sub>を含む低抵抗の反応層を形成することができ、アルミニウム系列のゲート配線22、24、26及びデータ配線62、65、66、68の上部膜を形成する時にケイ素を含むように形成することもできる。ここでアニーリング工程は保護膜70を積層した後に別途に形成することもでき、ゲート絶縁膜30または保護膜70を形成する時にアニーリング工程が含まれるように形成することもできる。

【0034】最後に、図1及び図2に示したようにIZOを積層しマスクを利用してパターニングを実施して、接触孔76を通じてドレーン電極66と連結される画素電極82と、接触孔74、78を通じてゲートパッド24及びデータパッド68と各々連結される補助ゲートパッド84及び補助データパッド88を各々形成する。

【0035】このような本発明の第1実施例による製造方法では、アルミニウム系列の金属膜601、24と連結される透明導電膜パターン82、84、88をIZOで形成しても接触部で腐食が発生しないため、透明導電膜パターン82、84、88を形成する前に接触孔を通じて露出されたアルミニウム金属膜を除去する必要がないので、製造工程を単純化することができる。

【0036】このような第1実施例では、前に説明したように5枚のマスクを用いる製造方法を適用することができるが、4枚のマスクを用いる液晶表示装置用薄膜トランジスタ基板の製造方法でも同様に適用することができる。これについては図面を参考として詳細に説明する

ことにする。

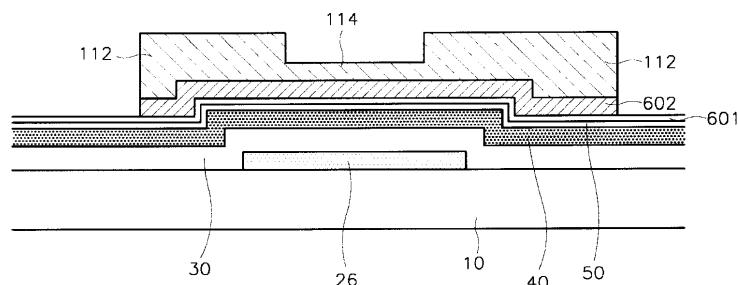

【0037】まず、図11乃至図13を参考として、本発明の実施例による4枚のマスクを用いて完成された液晶表示装置用薄膜トランジスタ基板の単位画素構造について詳細に説明する。

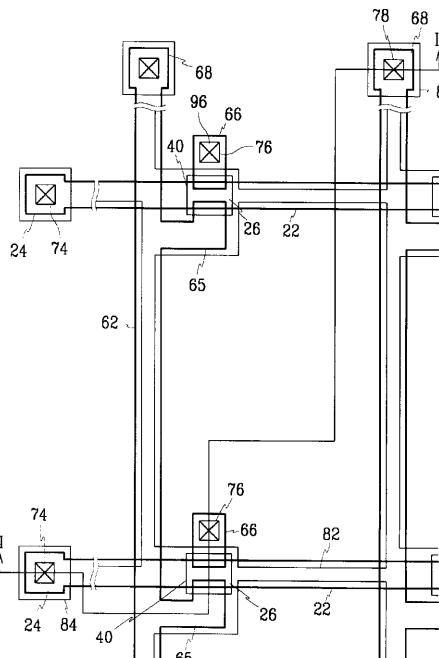

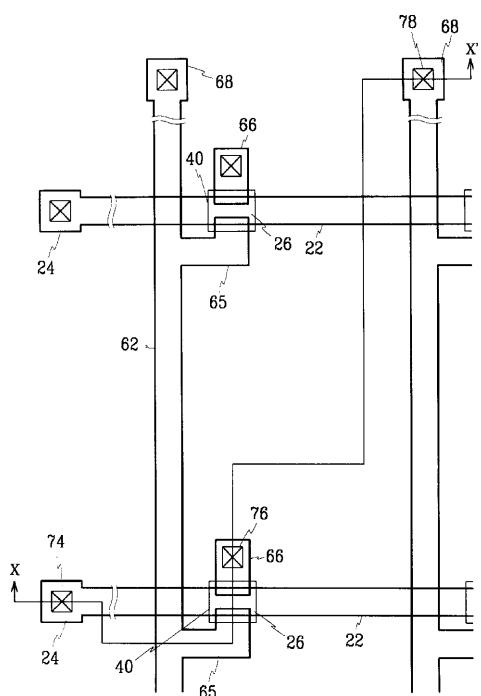

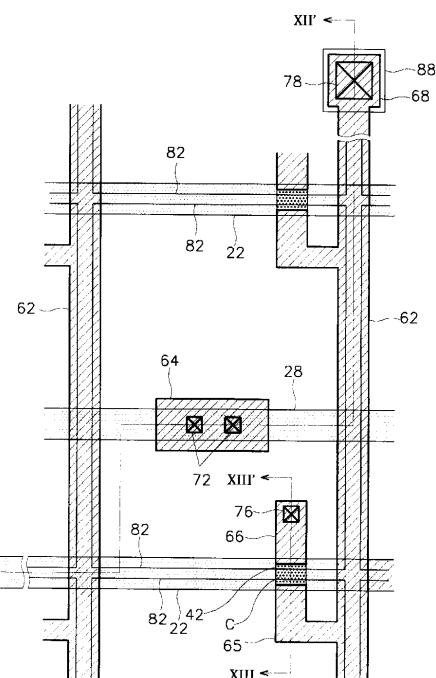

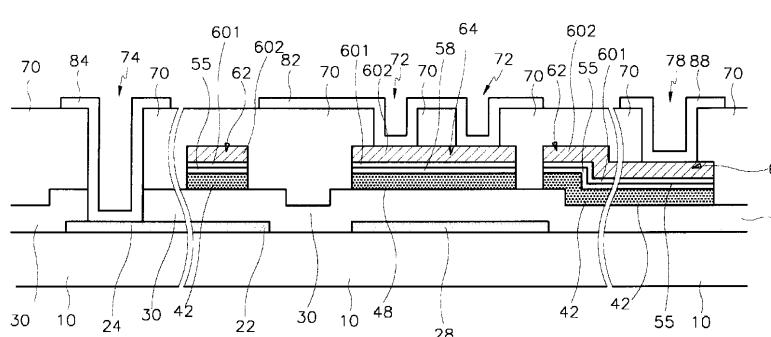

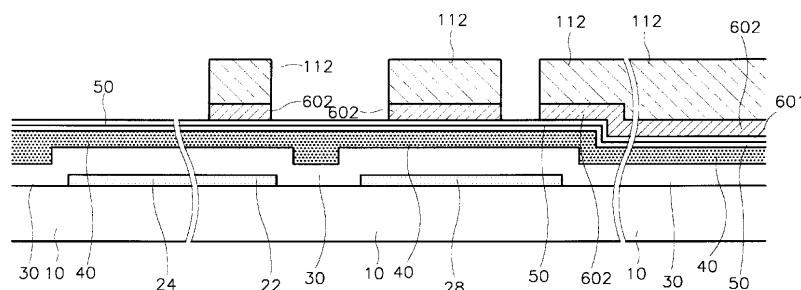

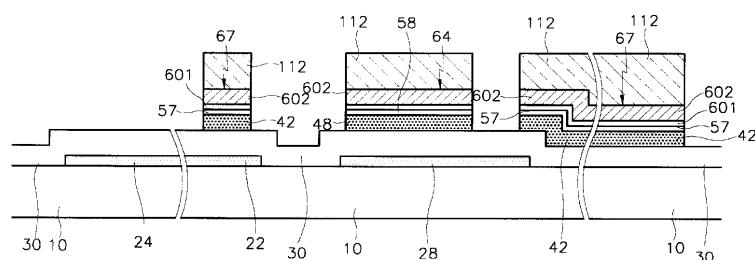

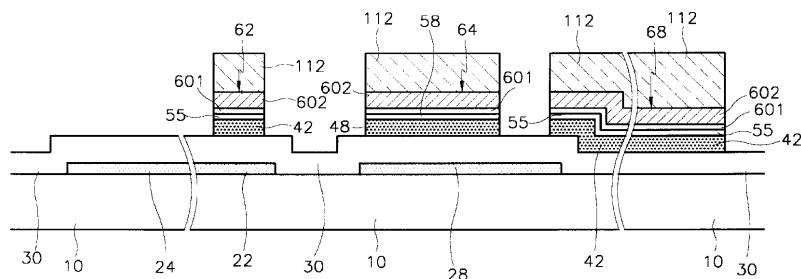

【0038】図11は本発明の第2実施例による液晶表示装置用薄膜トランジスタ基板の配置図であり、図12及び図13は各々図11に示した薄膜トランジスタ基板をXII-XII'線及びXIII-XIII'線に沿って切断して示した断面図である。

【0039】まず、絶縁基板10の上に第1実施例と同様にアルミニウム系列の金属からなるゲート線22、ゲートパッド24及びゲート電極26を含むゲート配線が形成されている。そして、ゲート配線は基板10の上部にゲート線22と平行しており上板の共通電極に入力される共通電極電圧などの電圧を外部から印加される維持電極28を含む。維持電極28は後述する画素電極82と連結された維持蓄電器用導電体パターン64と重なつて画素の電荷保存能力を向上させる維持蓄電器を構成し、後述する画素電極82とゲート線22との重複で発生する維持容量が十分である場合には形成しないこともある。

【0040】ゲート配線22、24、26、28の上には、窒化ケイ素SiN<sub>x</sub>などからなるゲート絶縁膜30が形成されてゲート配線22、24、26、28を覆っている。

【0041】ゲート絶縁膜30の上には水素化非晶質ケイ素(hydrogenated amorphous silicon)などの半導体からなる半導体パターン42、48が形成されており、半導体パターン42、48の上にはリン(P)などのn型不純物で高濃度にドーピングされている非晶質ケイ素などからなる抵抗性接触層(ohmic contact layer)パターンまたは中間層パターン55、56、58が形成されている。

【0042】抵抗性接触層パターン55、56、58の上には低抵抗を有するアルミニウム系列の導電物質からなるデータ配線が形成されている。データ配線は縦方向に形成されているデータ線62、データ線62の一端部に連結されて外部からの画像信号の印加を受けるデータパッド68、そしてデータ線62の分枝である薄膜トランジスタのソース電極65からなるデータ線部を含み、また、データ線部62、68、65と分離されておりゲート電極26または薄膜トランジスタのチャンネル部Cに対してソース電極65の反対側に位置する薄膜トランジスタのドレーン電極66と維持電極28の上に位置している維持蓄電器用導電体パターン64も含む。維持電極28を形成しない場合には維持蓄電器用導電体パターン64もまた形成しない。第2実施例においてデータ配線62、64、65、66、68は、第1実施例と同様にクロムの下部膜601とアルミニウム系列の上部膜6

02とからなる。

【0043】抵抗性接触層パターン55、56、58は、その下部の半導体パターン42、48とその上部のデータ配線62、64、65、66、68の接触抵抗を下げる役割を果たし、データ配線62、64、65、66、68と完全に同一な形態を有する。つまり、データ線部中間層パターン55はデータ線部62、68、65と同一であり、ドレーン電極用中間層パターン56はドレーン電極66と同一であり、維持蓄電器用中間層パターン58は維持蓄電器用導電体パターン64と同一である。

【0044】一方、半導体パターン42、48は薄膜トランジスタのチャンネル部Cを除けばデータ配線62、64、65、66、68及び抵抗性接触層パターン55、56、58と同一な模様をしている。具体的には、維持蓄電器用半導体パターン48と維持蓄電器用導電体パターン64及び維持蓄電器用接触層パターン58は同一な模様をしているが、薄膜トランジスタ用半導体パターン42はデータ配線及び接触層パターンの残りの部分と多少異なる。

【0045】つまり、薄膜トランジスタのチャンネル部Cにおいてデータ線部62、68、65、特にソース電極65とドレーン電極66とが分離されておりデータ線部中間層パターン55とドレーン電極用接触層パターン56も分離されているが、薄膜トランジスタ用半導体パターン42はここで切れずに連結されて薄膜トランジスタのチャンネルを生成する。

【0046】データ配線62、64、65、66、68の上には保護膜70が形成されており、保護膜70はドレーン電極66、データパッド68及び維持蓄電器用導電体パターン64を露出する接触孔76、78、72を有しており、またゲート絶縁膜30とともにゲートパッド24を露出する接触孔74を有している。保護膜70は窒化ケイ素やアクリル系などの有機絶縁物質からなり得る。

【0047】保護膜70の上には、薄膜トランジスタから画像信号を受けて上板の電極とともに電場を生成する画素電極82が形成されている。画素電極82はIZO(indium zinc oxide)などの透明な導電物質で作られ、接触孔76を通じてドレーン電極66と電気的に連結されて画像信号の伝達を受ける。画素電極82はまた隣接するゲート線22及びデータ線62と重なって開口率を高めているが、重ならないこともある。また、画素電極82は接触孔72を通じて維持蓄電器用導電体パターン64とも連結されて導電体パターン64に画像信号を伝達する。一方、ゲートパッド24及びデータパッド68の上には接触孔74、78を通じて各々これらと連結される補助ゲートパッド84及び補助データパッド88が形成されており、これらはパッド24、68と外部回路装置との接着性を補完しパッドを保護する役割を果

たすものとして必須なものではなく、これらを適用するか否かは選択的である。

【0048】ここでは画素電極82の材料の例として透明なIZOを挙げたが、反射型液晶表示装置の場合には不透明な導電物質を使用しても差支えない。

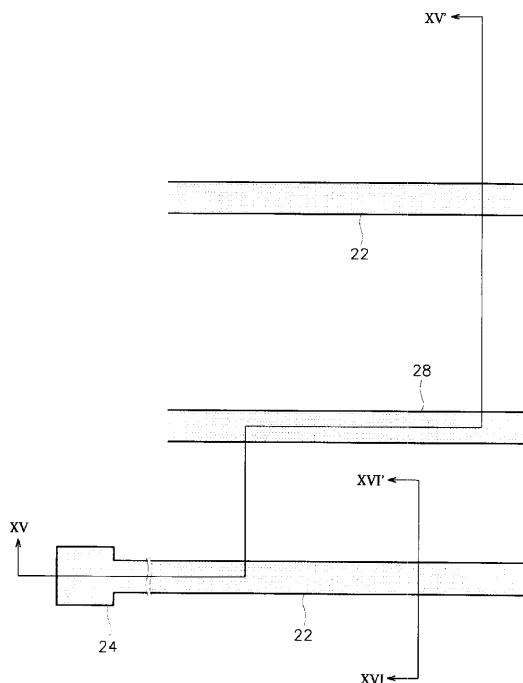

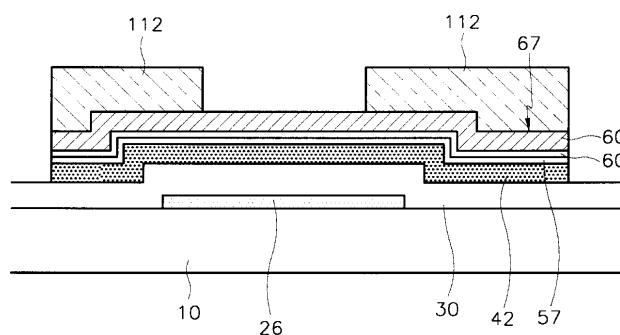

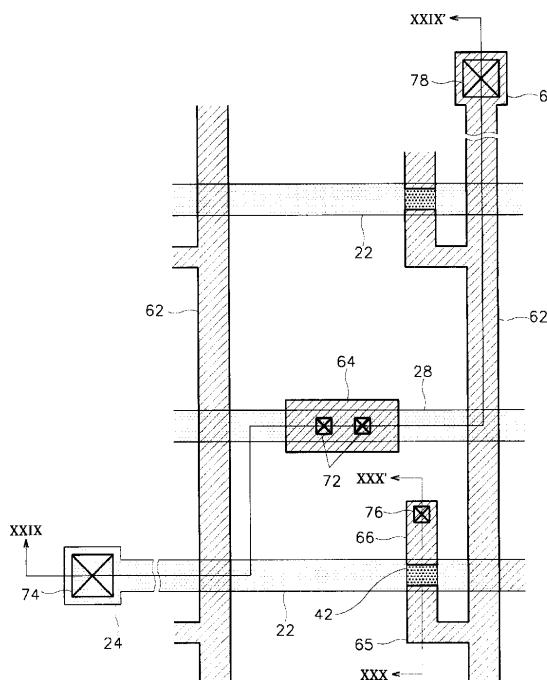

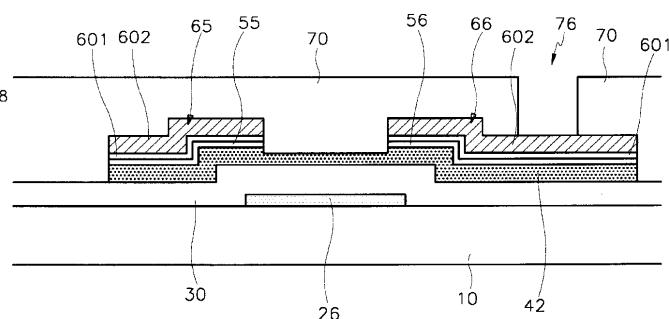

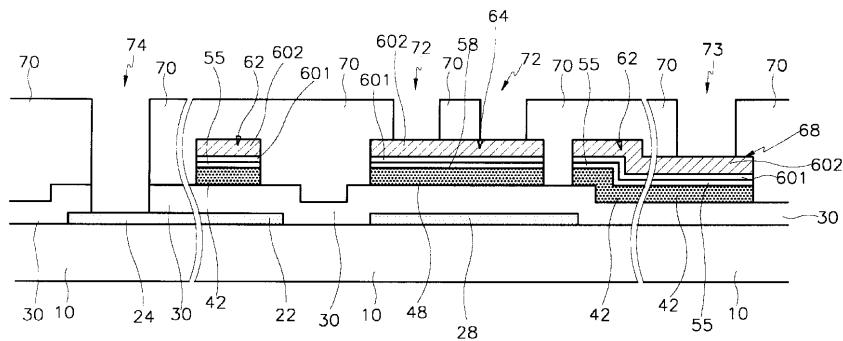

【0049】次に、図11乃至図13の構造を有する液晶表示装置用薄膜トランジスタ基板を4枚のマスクを用いて製造する方法について、図12と図14乃至図30を参照して詳細に説明する。

【0050】まず、図14乃至図16に示したように第1実施例と同様にアルミニウム系列の金属を積層し、第1マスクを利用した写真エッチング工程で基板10の上にゲート線22、ゲートパッド24、ゲート電極26及び維持電極28を含むゲート配線を形成する。

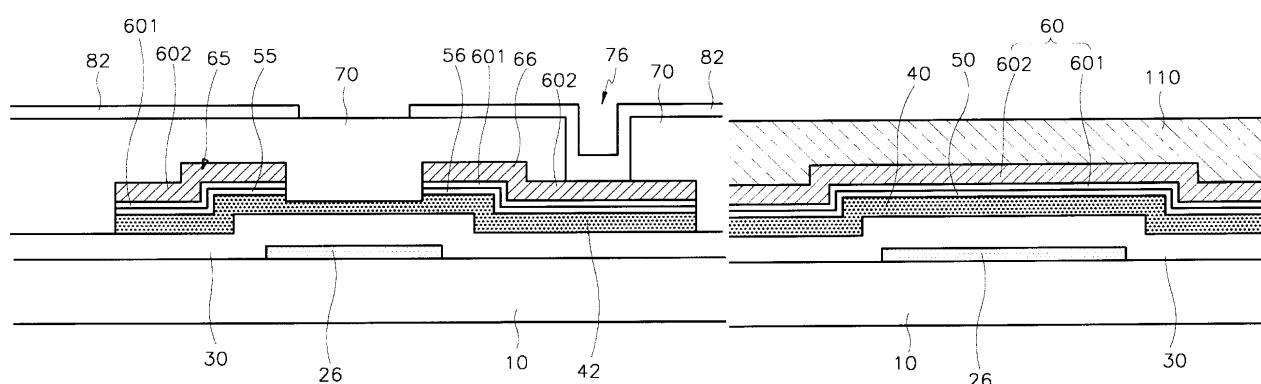

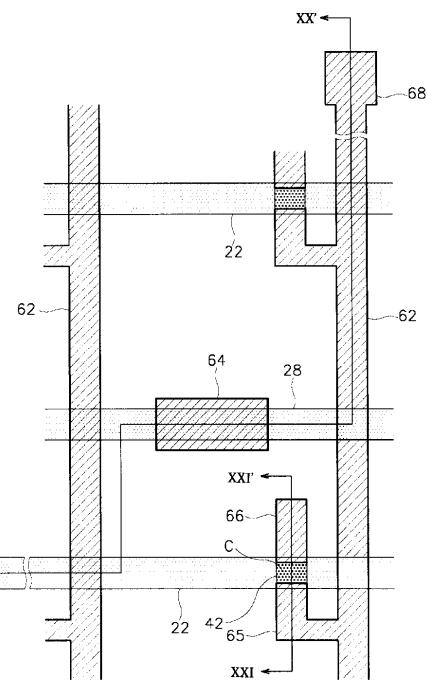

【0051】次に、図17及び図18に示したように、ゲート絶縁膜30、半導体層40、中間層50を化学気相蒸着法を用いて各々1500乃至5000、500乃至2000、300乃至600の厚さで連続蒸着し、クロムの下部膜601と低抵抗を有するアルミニウム系列の上部膜602とからなる導電層60をスパッタリングなどの方法で1500乃至3000の厚さで蒸着した後、その上に感光膜110を1μm乃至2μmの厚さで塗布する。この時、下部膜601は乾式エッチングが可能になるように薄く形成し、300以下であることが好ましい。

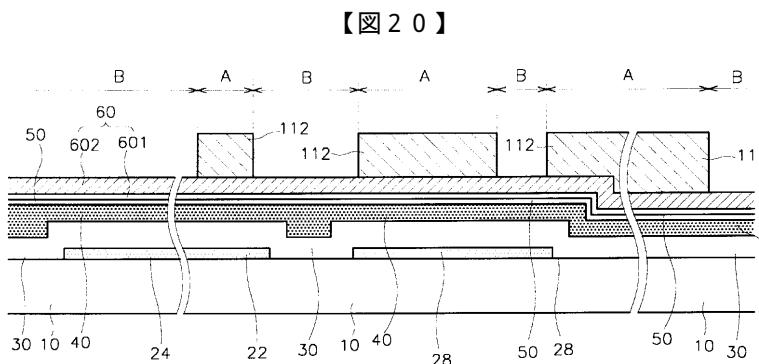

【0052】その後、第2マスクを通じて感光膜110に光を照射した後に現像して、図20及び図21に示したように、感光膜パターン112、114を形成する。この時、感光膜パターン112、114の中の薄膜トランジスタのチャンネル部C、つまりソース電極65とドレーン電極66との間に位置した第1部分114はデータ配線部A、つまりデータ配線62、64、65、66、68が形成される部分に位置した第2部分112より厚さが小さくなるようにし、その他の部分Bの感光膜は全て除去する。この時、チャンネル部Cに残っている感光膜114の厚さとデータ配線部Aに残っている感光膜112の厚さの比は後述するエッチング工程での工程条件によって異なるようにしなければならないが、第1部分114の厚さを第2部分112の厚さの1/2以下とすることが好ましく、例えば4000以下であるのが良い。

【0053】このように位置によって感光膜の厚さを異にする方法は多様なものがありうるし、A領域の光透過量を調節するために主にスリット(slit)や格子形態のパターンを形成したり半透明膜を使用する。

【0054】この時、スリットの間に位置したパターンの線幅やパターンの間の間隔、つまりスリットの幅は露光時に使用する露光器の分解能より小さいことが好ましく、半透明膜を用いる場合にはマスクを製作する時の透過率を調節するために他の透過率を有する薄膜を用いた

り厚さが異なる薄膜を用いることができる。

【0055】このようなマスクを通じて感光膜に光を照射すれば光に直接露出される部分では高分子が完全に分解され、スリットパターンや半透明膜が形成されている部分では光の照射量が少ないため高分子は完全に分解されていない状態であり、遮光膜で遮られた部分では高分子がほとんど分解されない。続いて感光膜を現像すれば高分子の分子が分解されない部分のみが残り、光が少なく照射された中央部分には光に全く照射されていない部分より薄い厚さの感光膜が残り得る。この時、露光時間10を長くすると全ての分子が分解されてしまうので注意しなければならない。

【0056】このような薄い厚さの感光膜114は、リフロー可能な物質からなる感光膜を用いて光が完全に透過できる部分と完全に透過できない部分とで分けられた通常のマスクで露光した後に現像し、リフローさせて感光膜が残留していない部分で感光膜の一部を流れるようにすることによって形成することもできる。

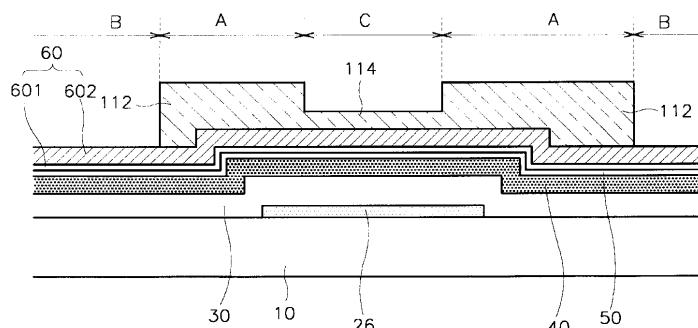

【0057】続いて、感光膜パターン114及びその下部の膜、つまり導電層60、中間層50及び半導体層40に対するエッティングを行う。この時、データ配線部Aにはデータ配線及びその下部の膜がそのまま残っておりチャンネル部Cには半導体層だけが残っていなければならず、残りの部分Bには上の3つの層60、50、40が全て除去されてゲート絶縁膜30が露出されなければならない。

【0058】まず、図22及び図23に示したように、他の部分Bの露出されているアルミニウム系列の上部膜602を乾式エッティングまたは湿式エッティングで除去する。

【0059】続いて、図24及び図25のように他の部分Bに露出されているクロムの下部膜601とその下部の中間層50と半導体層40とを乾式エッティング方法で連続してエッティングする。クロムの下部膜601と中間層50及び半導体層40を乾式エッティング工程を用いてインシチュー(in-situ)で行うことができ、そうでないこともある。クロムの下部膜601をエッティングするエッティング用気体としてはC<sub>1</sub>またはHClとO<sub>2</sub>の混合気体を使用することが好ましく、これに対する詳細な結果は後で説明する。

【0060】中間層50と半導体層40のエッティングは感光膜パターン112、114と中間層50及び半導体層40(半導体層と中間層はエッティング選択性がほとんど無い)が同時にエッティングされ、ゲート絶縁膜30はエッティングされない条件下で行わなければならず、特に感光膜パターン112、114と半導体層40に対するエッティング比がほとんど同一な条件でエッティングすることが好ましく、エッティング用気体としてはSF<sub>6</sub>またはHClの混合気体を用いる。感光膜パターン112、114と半導体層40に対するエッティング比が同一である

場合、第1部分114の厚さは半導体層40と中間層50の厚さを合せたものと同一であるかそれより小さくなればならない。このように下部膜601を薄く形成し、中間層50及び半導体層40とともに乾式エッティングで処理することによって製造工程を単純化することができる。ここで下部膜601はクロムだけでなく他の金属も用いることができ、中間層50及び半導体層40と一緒にパターニングが可能であればよい。

【0061】このようにすると、図24及び図25に示したようにチャンネル部C及びデータ配線部Bの導電層、つまり、ソース/ドレーン用導電体パターン67と維持蓄電器用導電体パターン64だけが残りその他の部分Bの導電体層60は全て除去される。この時、残った導電体パターン67、64はソース及びドレーン電極64、66が分離されずに連結されている点を除けばデータ配線62、64、65、66、68の形態と同一である。また、チャンネル部Cの第1部分114が除去されてソース/ドレーン用導電体パターン67が露出し、その他の部分Bの中間層50及び半導体層40が除去されてその下部のゲート絶縁膜30が露出する。一方、データ配線部Aの第2部分112もまたエッティングされるので厚さが薄くなる。なお、この段階で半導体パターン42、48が完成されるようになる。図面の符号57、58は各々ソース/ドレーン用導電体パターン67下部の中間層パターンと維持蓄電器用導電体パターン64下部の中間層パターンを指す。

【0062】ここで、チャンネル部Cのソース/ドレーン用導電体パターン67は別途のPRエッチャック(etch back)工程を通じて露出させることもでき、感光膜を十分にエッティングし得る条件ではPRエッチャック工程を省略することもできる。これはアッシング(ashsing)を通じてチャンネル部Cのソース/ドレーン用導電体パターン67の表面に残っている感光膜クズを除去する工程で行われる。

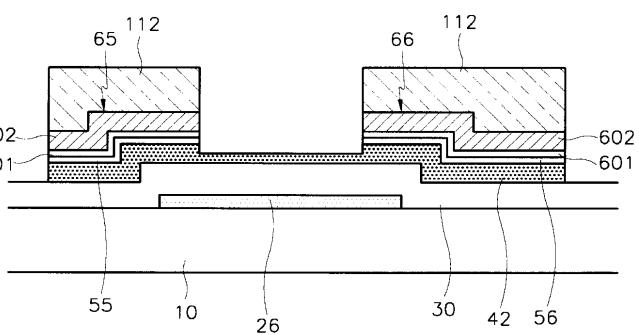

【0063】次に、図26及び図27に示したようにチャンネル部Cのソース/ドレーン用導電体パターン67及びその下部のソース/ドレーン用中間層パターン57をエッティングして除去する。この時、エッティングはソース/ドレーン用導電体パターン67と中間層パターン57の全てに対して乾式エッティングだけで処理することもでき、ソース/ドレーン用導電体パターン67に対しては湿式エッティングで、中間層パターン57に対しては乾式エッティングで行うこともできる。本発明の実施例ではアルミニウム系列の上部膜602は乾式エッティングまたは湿式エッティングでエッティングし、クロムの下部膜601と中間層パターン57は連続して乾式エッティングする。この時、クロムの下部膜601を薄く形成し中間層パターン57とともに乾式エッティングでパターニングすることによってパターニング工程を単純化することができる。ここで、クロムの下部膜601は乾式エッティング

も可能であるが、厚い場合には湿式エッティングを行うことができる。この時、図27に示したように半導体パターン42の一部が除去されて厚さが薄くなくこともあり、感光膜パターンの第2部分112もこの時にある程度の厚さにエッティングされる。この時のエッティングはゲート絶縁膜30がエッティングされない条件で行わなければならず、第2部分112がエッティングされてその下部のデータ配線62、64、65、66、68が露出されないように感光膜パターンが厚いことが好ましいのはもちろんである。

【0064】このようにすると、ソース電極65とドレーン電極66とが分離されるとともにデータ配線62、64、65、66、68とその下部の接触層パターン55、56、58が完成される。

【0065】最後に、データ配線部Aに残っている感光膜第2部分112を除去する。しかし、第2部分112の除去はチャンネル部Cソース/ドレーン用導電体パターン67を除去した後、その下の中間層パターン57を除去する前に行われることもありうる。

【0066】このようにしてデータ配線62、64、65、66、68を形成した後、図28乃至図30に示したように窒化ケイ素をCVD方法で蒸着したり有機絶縁物質をスピンドルーティングして3000以上の厚さを有する保護膜70を形成する。続いて第3マスクを用いて保護膜70をゲート絶縁膜30とともにエッティングしてドレーン電極66、ゲートパッド24、データパッド68及び維持蓄電器用導電体パターン64を各々露出する接触孔76、74、78、72を形成する。ここでも、以後に形成されるIZO膜82、84、88とアルミニウム膜66、24、68との接触抵抗を最少化するために、アニーリング工程を通じてアルミニウム系列の金属膜66、24、68の上部に残留する物質を除去することができ、アルミニウム系列の金属膜66、24、68の上部にAl<sub>1-x</sub>Si<sub>x</sub>を含む低抵抗の反応層を形成することができ、アルミニウム系列のゲート配線22、24、26、28及びデータ配線62、64、65、66、68の上部膜を形成する時にケイ素を含むように形成することもできる。ここで、保護膜70をエッティングする前にアニーリング工程は別途に実施することができ、ゲート絶縁膜30または保護膜70を形成する時にアニーリング工程が含まれるように形成することもできる。この時、アニーリング工程は280~400の温度の範囲で実施することが好ましい。

【0067】最後に、図11乃至図13に示したように400乃至500厚さのIZO層を蒸着し、第4マスクを使用してエッティングしてドレーン電極66及び維持蓄電器用導電体パターン64と連結された画素電極82、ゲートパッド24と連結された補助ゲートパッド84及びデータパッド68と連結された補助データパッド88を形成する。

【0068】このような本発明の第2実施例では、第1実施例による効果だけでなくデータ配線62、64、65、66、68とその下部の接触層パターン55、56、58及び半導体パターン42、48を一つのマスクを用いて形成し、この過程でソース電極65ドレーン電極66とが分離されて製造工程を単純化することができる。また、製造工程中にクロムの下部膜601と中間層50と半導体層40とを連続して乾式エッティング条件でパターニングすることによって製造工程を単純化することができる。

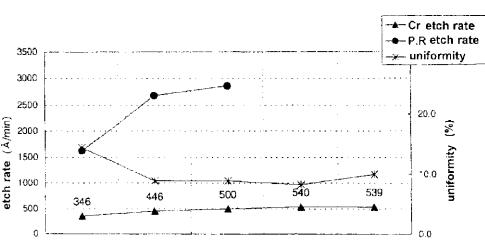

【0069】次いで、前に説明したように、乾式エッティング用気体であるC<sub>1</sub>またはHC<sub>1</sub>とO<sub>2</sub>の混合気体を用いてクロム膜をエッティングした実験結果について具体的に説明することにする。

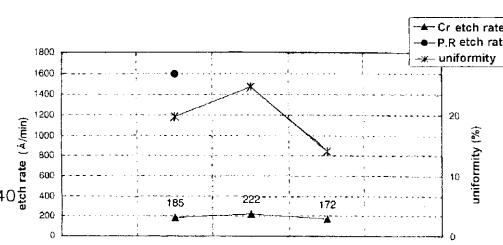

【0070】図31及び図32は本発明の実施例による液晶表示装置用薄膜トランジスタ基板の製造方法で、乾式エッティング用気体としてC<sub>1</sub>/O<sub>2</sub>とHC<sub>1</sub>/O<sub>2</sub>を使用した場合のクロム膜のエッティング特性をグラフで各々示したものである。

【0071】実験例においてクロム膜601は半導体層40及び中間層50をエッティングするためのプラズマエッティング方式の乾式エッティング装置を用いており、乾式エッティング条件において圧力は300mTであり、電力は1800Wであり、乾式エッティング用チャンバの電極間隔は60mmに設定して実験を行った。図31はC<sub>1</sub>を400sccm使用した実験結果であり、図32はHC<sub>1</sub>を400sccm使用した実験結果である。

【0072】図31及び図32で左側の縦軸はエッティング比を示したものであり、右側の縦軸はエッティングに対する均一度(uniformity)であり、横軸はO<sub>2</sub>の変化量を示したものである。

【0073】図31のように、乾式エッティング用気体としてC<sub>1</sub>を用いる場合のクロム膜のエッティング比は350~540程度が得られ、エッティング均一度は大部分10%程度に良好に測定された。この時、感光膜のエッティング量は1600~2800程度に測定されており、グラフには示していないがクロム膜と非晶質ケイ素層とのエッティング選択比は8~16:1程度であった。

【0074】図32のように、乾式エッティング用気体としてHC<sub>1</sub>を用いる場合のクロム膜のエッティング比は200程度が得られ、エッティング均一度は大部分14~25%程度であった。この時、感光膜のエッティング量は1600程度であった。

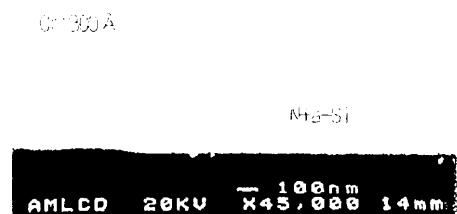

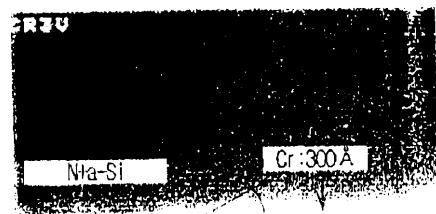

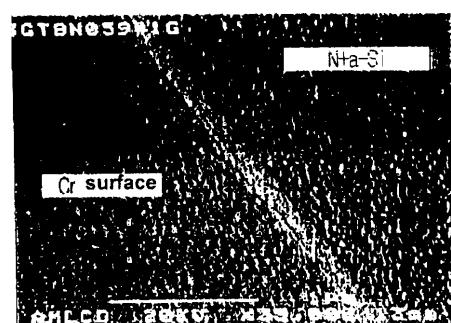

【0075】図33乃至図36は、本発明の実施例による薄膜トランジスタ基板の製造方法におけるクロム金属膜の表面をSEM(scanning electron microscope)を通じて示した写真である。図33乃至図36は、300mT/1800W/400sccm C<sub>1</sub>/6mmの条件下80"の間乾式エッティングを行った実験結果を示したものである。

【0076】図33乃至図36のように、クロム膜とドーピングされた非晶質ケイ素層(N+a-Si)の表面は良好であり、クロム膜のテーバー角度は25~30°であって良好なプロファイル(profile)を得ることができた。

#### 【0077】

【発明の効果】このように本発明によれば、金属層を薄く形成し半導体層と一緒にパターニングすることによって製造工程を単純化することができ、低抵抗のアルミニウムまたはアルミニウム合金で配線を形成することによって大画面高精細の製品の特性を向上させることができる。

#### 【図面の簡単な説明】

【図1】本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板を示した図である。

【図2】図1に示した薄膜トランジスタ基板をII-II'線に沿って切断して示した断面図である。

【図3】本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板を製造する中間過程における薄膜トランジスタ基板の配置図である。

【図4】図3aのIV-IV'線に沿って切断した断面図である。

【図5】本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板を製造する中間過程における薄膜トランジスタ基板の配置図である。

【図6】図5のVI-VI'線に沿って切断して示した図面として図4の次の段階を示した断面図である。

【図7】本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板を製造する中間過程における薄膜トランジスタ基板の配置図である。

【図8】図7のVIII-VIII'線に沿って切断して示した図面として図6の次の段階を示した断面図である。

【図9】本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板を製造する中間過程における薄膜トランジスタ基板の配置図である。

【図10】図9のX-X'線に沿って切断して示した図面として図8の次の段階を示した断面図である。

【図11】本発明の第2実施例による液晶表示装置用薄膜トランジスタ基板の配置図である。

【図12】図11に示した薄膜トランジスタ基板をXII-XII'線に沿って切断して示した断面図である。

【図13】図11に示した薄膜トランジスタ基板をXIII-XIII'線に沿って切断して示した断面図である。

【図14】本発明の第2実施例によって製造する初めての段階における薄膜トランジスタ基板の配置図である。

【図15】図14のXV-XV'線に沿って切断して示した断面図である。

【図16】図14のXVI-XVI'線に沿って切断して示した断面図である。

【図17】図14のXV-XV'線に沿って切断して示した

断面図として図15の次の段階を示した断面図である。

【図18】図14のXVI-XVI'線に沿って切断して示した断面図として図16の次の段階を示した断面図である。

【図19】図17及び18の次の段階での薄膜トランジスタ基板の配置図である。

【図20】図19のXX-XX'線に沿って切断して示した断面図である。

【図21】図19のXXI-XXI'線に沿って切断して示した断面図である。

【図22】図19のXX-XX'線に沿って切断して示した断面図として図20の次の段階を図20の次の段階を工程順序によって示した図である。

【図23】図19のXXI-XXI'線に沿って切断して示した断面図として図21の次の段階を工程順序によって示した図である。

【図24】図19のXX-XX'線に沿って切断して示した断面図として図20の次の段階を工程順序によって示した図である。

【図25】図19のXXI-XXI'線に沿って切断して示した断面図として図21の次の段階を工程順序によって示した図である。

【図26】図19のXX-XX'線に沿って切断して示した断面図として図20の次の段階を工程順序によって示した図である。

【図27】図19のXXI-XXI'線に沿って切断して示した断面図として図21の次の段階を工程順序によって示した図である。

【図28】図26及び図27の次の段階での薄膜トランジスタ基板の配置図である。

【図29】図28のXXIX-XXIX'線に沿って切断して示した断面図である。

【図30】図28のXXX-XXX'線に沿って切断して示した断面図である。

【図31】本発明の実施例による液晶表示装置用薄膜トランジスタ基板の製造方法において、乾式エッティング用気体としてC<sub>1</sub><sub>2</sub>/O<sub>2</sub>を使用した場合のクロム膜のエッティング特性を示したグラフである。

【図32】本発明の実施例による液晶表示装置用薄膜トランジスタ基板の製造方法において、乾式エッティング用気体としてHCl/O<sub>2</sub>を使用した場合のクロム膜のエッティング特性を示したグラフである。

【図33】本発明の実施例による薄膜トランジスタ基板の製造方法におけるクロム金属膜の表面をSEM(scanning electron microscope)を通じて示した写真である。

【図34】本発明の実施例による薄膜トランジスタ基板の製造方法におけるクロム金属膜の表面をSEM(scanning electron microscope)を通じて示した写真である。

【図35】本発明の実施例による薄膜トランジスタ基板の製造方法におけるクロム金属膜の表面をSEM (scanning electron microscope) を通じて示した写真である。

【図36】本発明の実施例による薄膜トランジスタ基板の製造方法におけるクロム金属膜の表面をSEM (scanning electron microscope) を通じて示した写真である。

【符号の説明】

- 10 絶縁基板

- 22 ゲート線

- 24 ゲートパッド

- 26 ゲート電極

- 28 維持電極

- 30 ゲート絶縁膜

- 40 半導体層

- 48 維持蓄電器用半導体パターン

- 50 非晶質ケイ素層

- 54 抵抗接触層

- 55 データ線部中間層パターン

- \* 5 6 ドレーン電極用接触層パターン

- 5 7 中間体パターン

- 5 8 維持蓄電器用接触層パターン

- 6 0 導電体層

- 6 2 データ線

- 6 4 維持蓄電器用導電体パターン

- 6 5 ソース電極

- 6 6 ドレーン電極

- 6 7 ソース/ドレーン用導電体パターン

- 10 6 8 データパッド

- 7 0 保護膜

- 7 2、7 4、7 6、7 8 接触孔

- 8 2 画素電極

- 8 4 補助ゲートパッド

- 8 8 補助データパッド

- 11 0 感光膜

- 11 2 第2部分

- 11 4 第1部分

- 6 0 1 下部膜

- \* 20 6 0 2 上部膜

【図1】

【図2】

【図5】

【図4】

【図3】

【図6】

【図16】

【図7】

【図8】

【図15】

【図9】

【図11】

【図12】

【図13】

【図18】

【図14】

【図19】

【図17】

【図33】

【図32】

【図21】

【図34】

【図22】

【図35】

Etching Profile: about 25~3°

【図23】

【図36】

【図24】

【図25】

【図27】

【図26】

【図28】

【図30】

【図29】

フロントページの続き

(51) Int.CI.<sup>7</sup>

H 0 1 L 21/336

識別記号

F I

H 0 1 L 29/78

テ-マコ-ト<sup>®</sup> (参考)

6 1 6 U

6 1 6 V

6 2 7 C

F ターム(参考) 2H092 GA29 JA24 JA37 JA41 JA46

KA10 MA04 MA17 MA19 MA27

NA25

5F033 HH38 JJ38 KK08 KK09 KK17

MM05 MM13 QQ01 QQ08 QQ09

QQ10 QQ11 QQ19 QQ26 QQ37

RR06 RR21 VV06 VV07 VV15

XX33

5F110 AA03 AA16 BB01 CC07 EE03

FF03 GG02 GG15 HK03 HK04

HK06 HK09 HK16 HK22 HK25

HK42 HL07 HL26 NN02 NN24

NN27 NN72 QQ02 QQ04 QQ09

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 制造用于液晶显示装置的薄膜晶体管基板的方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP2002055362A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2002-02-20 |

| 申请号            | JP2001046234                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2001-02-22 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| [标]发明人         | 金湘甲<br>洪むん杓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 金湘甲<br>洪▲むん▼杓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G02F1/1368 G02F1/136 H01L21/3205 H01L21/3213 H01L21/336 H01L21/768 H01L21/77 H01L21/84 H01L23/52 H01L27/12 H01L29/45 H01L29/49 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| CPC分类号         | H01L29/66765 G02F2001/13629 H01L27/124 H01L29/456 H01L29/4908                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G02F1/1368 H01L21/88.C H01L21/88.R H01L21/90.A H01L29/78.612.D H01L29/78.616.U H01L29/78.616.V H01L29/78.627.C G02F1/1343                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| F-TERM分类号      | 2H092/GA29 2H092/JA24 2H092/JA37 2H092/JA41 2H092/JA46 2H092/KA10 2H092/MA04 2H092 /MA17 2H092/MA19 2H092/MA27 2H092/NA25 5F033/HH38 5F033/JJ38 5F033/KK08 5F033/KK09 5F033/KK17 5F033/MM05 5F033/MM13 5F033/QQ01 5F033/QQ08 5F033/QQ09 5F033/QQ10 5F033 /QQ11 5F033/QQ19 5F033/QQ26 5F033/QQ37 5F033/RR06 5F033/RR21 5F033/VV06 5F033/VV07 5F033/VV15 5F033/XX33 5F110/AA03 5F110/AA16 5F110/BB01 5F110/CC07 5F110/EE03 5F110 /FF03 5F110/GG02 5F110/GG15 5F110/HK03 5F110/HK04 5F110/HK06 5F110/HK09 5F110/HK16 5F110/HK22 5F110/HK25 5F110/HK42 5F110/HL07 5F110/HL26 5F110/NN02 5F110/NN24 5F110 /NN27 5F110/NN72 5F110/QQ02 5F110/QQ04 5F110/QQ09 2H192/AA24 2H192/BC31 2H192/CB05 2H192/CC04 2H192/CC72 2H192/DA02 2H192/DA12 2H192/DA42 2H192/DA44 2H192/FA65 2H192 /HA44 2H192/HA63 2H192/HA80 |         |            |

| 优先权            | 1020000043505 2000-07-27 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 其他公开文献         | JP4790134B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

## 摘要(译)

(带更正) 提供一种具有优异的接触特性和低电阻布线的薄膜晶体管基板的制造方法。通过层压铝系列的导电材料在基板上形成包括栅极线，栅电极和栅极焊盘的栅极布线，并且依次形成栅极绝缘膜，半导体层和电阻接触层。然后，堆叠包括铬的下膜和铝的上膜的导电材料，以形成数据线，该数据线包括与栅极线，源电极，漏电极和数据焊盘相交的数据线。此时，使用包含Cl<sub>2</sub>或HCl的蚀刻气体对铬的下层膜进行构图。然后，层压保护膜以形成暴露漏电极，栅极焊盘和数据焊盘的接触孔，然后将IZO层压并构图以形成漏电极66，连接到栅极焊盘和数据焊盘的像素电极以及辅助电极。形成栅极焊盘和辅助数据焊盘。