# (19)日本国特許庁(JP) (12) **公 開 特 許 公 報**(A) (11)特許出願公開番号

特開2001 - 265298

(P2001 - 265298A)

(43)公開日 平成13年9月28日(2001.9.28)

| (51) Int.C | l 7 |   |   |       | 識別記号 | 庁内整理番号 | F | I |   |   |       |     |   | 技術表示箇所 |

|------------|-----|---|---|-------|------|--------|---|---|---|---|-------|-----|---|--------|

| G          | 0   | 9 | G | 3/36  |      |        | G | 0 | 9 | G | 3/36  |     |   |        |

| G          | 0   | 2 | F | 1/133 | 575  |        | G | 0 | 2 | F | 1/133 | 575 |   |        |

| G          | 0   | 9 | G | 3/20  | 621  |        | G | 0 | 9 | G | 3/20  | 621 | F |        |

### 審査請求 未請求 請求項の数 610 L (全 23数)

| (21)山陽笛写 - 待願2001 - 20041(12001 - 2004 | (21)出願番号 | 特願2001 - 28541(P2001 - 28541 |

|----------------------------------------|----------|------------------------------|

|----------------------------------------|----------|------------------------------|

(22)出願日 平成13年2月5日(2001.2.5)

(31)優先権主張番号 2000 - 5442

(32)優先日 平成12年2月3日(2000.2.3)

(33)優先権主張国 韓国(KR) (31)優先権主張番号 2000 - 43509

(32)優先日 平成12年7月27日(2000.7.27)

(33)優先権主張国 韓国(KR) (31)優先権主張番号 2000 - 73672

(32)優先日 平成12年12月6日(2000.12.6)

(33)優先権主張国 韓国(KR)

(71)出願人 390019839

三星電子株式会社

大韓民国京畿道水原市八達区梅灘洞416

(72) 発明者 李 白 雲

大韓民国京畿道龍仁市器興邑農書里山24番

地

(74)代理人 100094145

弁理士 小野 由己男 (外1名)

### (54)【発明の名称】 液晶表示装置とその駆動方法及び装置

### (57)【要約】

【課題】 TFT LCDのパネルの構造を変える必要なく、液晶の駆動方法を変えることによって液晶の応答速度を改善させるための液晶表示装置を提供することにある。

【解決手段】 本発明の液晶表示装置は、現在のフレームのデータ電圧と以前のフレームのデータ電圧とを同時に考慮して補正データ電圧を生成した後、生成された補正データ電圧をデータラインに印加する。前記の補正データ電圧をデータラインに印加することにより、画素電圧がすぐに目標レベルに到達し得るようにする。

### 【特許請求の範囲】

【請求項1】データ階調信号ソースから階調信号を受信 し、現在のフレームの階調信号と以前のフレームの階調 信号とを考慮して補正階調信号を出力するデータ階調信 号補正部と;前記データ階調信号補正部から出力される 前記補正階調信号に対応するデータ電圧に変えて画像信 号を出力するデータドライバー部と;走査信号を順次に 供給するゲートドライバー部と;前記走査信号を伝達す る多数のゲートラインと、前記画像信号を伝達し、前記 ゲートラインと絶縁して交差する多数のデータライン と、前記ゲートライン及び前記データラインによって囲 まれた領域に形成され、それぞれ前記ゲートライン及び 前記データラインに連結されているスイッチング素子を 有するマトリックスの形態に配列された多数の画素とを 含む液晶表示パネルとを含む液晶表示装置。

【請求項2】前記データ階調信号補正部は、

前記データ階調信号ソースから階調信号を受信し、一つ のフレームの間前記受信された階調信号を保存して出力 するフレームメモリと:前記フレームメモリの階調信号 の記録及び判読を制御するコントローラーと;前記デー 20 夕階調信号ソースから受信される現在のフレームの階調 信号と前記フレームメモリから受信される以前のフレー ムの階調信号とを考慮して前記補正階調信号を出力する データ階調信号変換器とを含む請求項1に記載の液晶表 示装置。

【請求項3】前記データ階調信号ソースから受信される 階調信号に同期するクロック周波数と前記コントローラ ーが同期するクロック周波数とが同一であることを特徴 とする請求項2に記載の液晶表示装置。

【請求項4】前記データ階調信号ソースから受信される30項10に記載の液晶表示装置。 階調信号に同期するクロック周波数と前記コントローラ が同期するクロック周波数とが相異することを特徴と する請求項2に記載の液晶表示装置。

【請求項5】前記データ階調信号ソースから伝送される 階調信号を受信し、前記コントローラーが同期するクロ ック周波数に合うように階調信号を合成して、合成され た階調信号を前記フレームメモリと前記データ階調信号 変換器とに出力する合成器と;前記データ階調信号変換 器から出力される階調信号を前記データ階調信号ソース から伝送される階調信号が同期する周波数に合うように 40 分離する分離器とをさらに含むことを特徴とする請求項 4に記載の液晶表示装置。

【請求項6】前記データ階調信号変換器は、

現在のフレームのデータ電圧をV、、以前のフレームの データ電圧を V \_ \_ \_ とすると、 V \_ ' = V \_ + f ( V<sub>n</sub> - V<sub>n-1</sub> )の式を満たす補正データ電圧 V 。'を出力するように階調信号を補正することを特徴とす る請求項2乃至5のいずれかに記載の液晶表示装置。

【請求項7】前記データ階調信号変換器は、

デジタル回路を用いて前記式を満たす補正された階調信 50 【請求項17】前記フレームメモリは、

号を出力することを特徴とする請求項6に記載の液晶表

【請求項8】前記データ階調信号変換器は、

以前のフレームの階調信号と現在のフレームの階調信号 とに対応する補正階調信号を記録するルックアップテー ブルを保存するメモリを含むことを特徴とする請求項2 乃至5のいずれかに記載の液晶表示装置。

【請求項9】前記ルックアップテーブルは、

前記補正データ電圧が第1電圧より大きい場合には前記 10 補正データ電圧を前記第1電圧とし、前記補正データ電 圧が第2電圧より小さい場合には前記補正データ電圧を 前記第2電圧とすることを特徴とする請求項8に記載の 液晶表示装置。

【請求項10】前記データ階調信号補正部は、

前記データ階調信号ソースからr、g、bに対するnビ ットの階調信号を受信し、前記 n ビットのうち現在のフ レームのmビットの階調信号と以前のフレームの前記m ビットの階調信号とを考慮した補正階調信号を出力する ことを特徴とする請求項1に記載の液晶表示装置。

【請求項11】前記データ階調信号補正部は、

前記データ階調信号ソースから前記mビットの階調信号 を受信し、一つのフレームの間前記受信された階調信号 を保存して出力するフレームメモリと;前記フレームメ モリの階調信号の記録及び判読を制御するコントローラ ーと;前記データ階調信号ソースから受信される現在の フレームの前記mビットの階調信号と前記フレームメモ リから受信される以前のフレームの前記mビットの階調 信号とを考慮して補正階調信号を生成して出力するデー 夕階調信号変換器とをさらに含むことを特徴とする請求

【請求項12】前記mは、前記nビットの階調信号のう ちLSBからi(0、1、2、...、n - 1) 個を除いた 残りのビットであることを特徴とする請求項11に記載 の液晶表示装置。

【請求項13】前記mは、r、g、bに応じてその値を 異にすることを特徴とする請求項11に記載の液晶表示 装置。

【請求項14】前記mは、前記bに対して最も大きいこ とを特徴とする請求項13に記載の液晶表示装置。

【請求項15】前記mは、前記gに対して最も小さいこ とを特徴とする請求項13に記載の液晶表示装置。

【請求項16】前記データ階調信号変換器は、

前記データ階調信号ソースから受信されるnビットの階 調信号のうち補正を行わない(n-m)ビットを受信 し、前記受信された(n-m)ビットを現在のフレーム の階調信号と以前のフレームの階調信号とを考慮して生 成した階調信号に足してnビットの補正階調信号を生成 することを特徴とする請求項11に記載の液晶表示装

前記データ階調信号ソースの奇数番目のmビットの階調 信号の出力をライトし、前記データ階調信号ソースの偶 数番号目のmビットの階調信号をリードする第1フレー ムメモリと;前記データ階調信号ソースの奇数番目のm ビットの階調信号の出力をリードし、偶数番号目のmビ ットの階調信号をライトする第2フレームメモリとを含 むことを特徴とする請求項11に記載の液晶表示装置。 【請求項18】前記データ階調信号変換器は、

現在のフレームのデータ電圧をV。、以前のフレームの データ電圧を V<sub>0.1</sub>とすると、 V<sub>0</sub>' = V<sub>0</sub> + f ( V<sub>n</sub> - V<sub>n,1</sub> )の式を満たす補正データ電圧 V ´を出力するように階調信号を補正することを特徴と する請求項11に記載の液晶表示装置。

【請求項19】前記データ階調信号変換器は、 デジタル回路を用いて前記式を満たす補正された階調信 号を出力することを特徴とする請求項18に記載の液晶 表示装置。

【請求項20】前記データ階調信号変換器は、 以前のフレームの階調信号と現在のフレームの階調信号 とに対応する補正階調信号を記録するルックアップテー 20 ブルを保存するメモリを含むことを特徴とする請求項1 1に記載の液晶表示装置。

【請求項21】前記ルックアップテーブルは、 前記補正データ電圧が第1電圧より大きい場合には前記 補正データ電圧を前記第1電圧とし、前記補正データ電 圧が第2電圧より小さい場合には前記補正データ電圧を 前記第2電圧とすることを特徴とする請求項20に記載 の液晶表示装置。

【請求項22】前記データ階調信号補正部は、

前記データ階調信号ソースからr、g、bに対するxビ 30 ットの階調データを受信して、現在のフレームの×ビッ トの階調データと以前のフレームの×ビットの階調デー タとから所定のMSBビットはルックアップテーブルを 用いて第1補正し、現在のフレームの階調データの残り のビットと以前のフレームの階調データの残りのビット とは所定の演算によって第2補正し、前記第1補正と第 2 補正とを通じて補正階調データを出力することを特徴 とする請求項1に記載の液晶表示装置。

【請求項23】前記データ階調信号補正部は、

前記データ階調信号ソースから×ビットの階調データを 40 受信し、一つのフレームの間前記受信された階調データ を保存して出力するフレームメモリと;前記フレームメ モリの階調データの記録及び判読を制御するコントロー ラーと;前記データ階調信号ソースから受信される現在 のフレームの×ビットの階調データと前記フレームメモ リから受信される以前のフレームの×ビットの階調デー タとを考慮して補正階調データを生成して前記データド ライバー部に出力するデータ階調信号変換器とを含むこ とを特徴とする請求項22に記載の液晶表示装置。

【請求項24】前記データ階調信号変換器は、

以前の画像データと現在の画像データとのxビットのデ ータのMSByビットのデータ各々の提供を受けて動画 像補正のための変数(f、a、b)を出力するルックア ップテーブルと;以前の画像データと現在の画像データ とのxビットのデータのLSBzビットのデータ各々の 提供を受け、前記変数(f、a、b)の提供を受けて補 正されたグレーデータを出力する演算部とを含むことを

【請求項25】前記補正されたグレーデータ(G<sub>0</sub>′)

特徴とする請求項23に記載の液晶表示装置。

$G_n' = f([G_n]_z, [G_{n-1}]_z) + a([G_n]_z, [G$  $\begin{bmatrix} 1 \\ 1 \end{bmatrix}_z$   $\times_y$   $\begin{bmatrix} G_n \end{bmatrix}$   $\times_z$   $\begin{bmatrix} G_{n-1} \end{bmatrix}_z$  $\times_{V} [G_n] / 2^{z}$

(ここで、zはx・y、[G゚]¸はG゚のLSBzビッ トを全て 0 で満たした値、 [ G , , , ] ¸ は G , , , の L S B z ビットを全て 0 で満たした値、 $_{v}$  [  $G_{r}$  ] は  $G_{r}$  の M SByビットを全て0で満たした値、aとbは全て正の整 数)に基づいて算出されることを特徴とする請求項24 に記載の液晶表示装置。

【請求項26】前記補正されたグレーデータ(G<sub>a</sub>′)

$G_{n}' = f'([G_{n}]_{z} + a([G_{n}]_{z}, [G_{n-1}]_{z}) \times_{v}$  $[G_n] / 2^z - b ([G_n]_z, [G_{n-1}]_z) \times_v [G_n]$

$(zz\overline{c}, z dx - y, f' = f([G_n]_x)$  $[G_{0.1}]_{,}$ ) -  $[G_{0}]_{4}$ ,  $[G_{0}]_{,}$ d $G_{0}$ OLSBzEットを全て0で満たした値、[G<sub>1,1</sub>],はG<sub>1,1</sub>のLS B z ビットを全て 0 で満たした値、 , [ G 。 ] は G 。の M SByビットを全て0で満たした値、aとbは全て正の 整数)に基づいて算出されることを特徴とする請求項2 4に記載の液晶表示装置。

【請求項27】前記補正されたグレーデータ(G\_´)

$G_n' = f'([G_n]_z, [G_{n-1}]_z + G_n + a'([G_n])$  $_{z}$ ,  $[G_{n-1}]_{z}$ )  $\times_{v}[G_{n}]$  /  $2^{z}$  - b (  $[G_{n}]_{z}$ ,  $[G_{n}]_{z}$  $_{n-1}$ ]  $_{z}$ )  $\times_{v}$  [ G  $_{n}$  ] / 2  $^{z}$

$(zzv, zkx - y, f' = f - G_n, [G_n]_tG_n$ のLSBzビットを全て0で満たした値、[G,,,],は G<sub>2</sub>,のLSBzビットを全て0で満たした値、

<sub>ູ</sub> [ G ၙ ] は G ၙの M S B y ビットを全て 0 で満たした 値、a ´は整数、b は正の整数)に基づいて算出される ことを特徴とする請求項24に記載の液晶表示装置。

【請求項28】前記[G。 ] 、 = [G。 , 、 ] 、である場合、  $G_a$   $' = G_a$  の条件を満たすためにはa - b = 16 でな ければならないことを特徴とする請求項25又は26に 記載の液晶表示装置。

【請求項29】前記 [ G 。 ] ¸ = [ G 。 , ₁ ] ¸である場合に は、 $G_{o}^{\prime} = G_{o,1}^{\prime}$ の条件を満たすためには $a^{\prime} - b = 0$ でなければならないことを特徴とする請求項27に記載 50 の液晶表示装置。

【請求項30】走査信号を伝達する多数のゲートライン と、データ電圧を伝達し、前記ゲートラインと絶縁して 交差する多数のデータラインと、前記ゲートライン及び データラインによって囲まれた領域に形成され、それぞ れ前記ゲートライン及びデータラインに連結されている スイッチング素子を有する行列の形態に配列された多数 の画素とを含む液晶表示装置パネルと;ゲートラインに 走査信号を順次に供給するゲートドライバー部と;デー タ電圧ソースからデータ電圧を受信し、現在のフレーム のデータ電圧と以前のフレームのデータ電圧とを考慮し 10 る請求項35に記載の液晶表示装置の駆動方法。 て補正データ電圧を出力するデータ電圧補正部と;前記 データ電圧補正部から出力される前記補正データ電圧を 前記データラインに供給するデータドライバー部とを含 む液晶表示装置。

【請求項31】前記データ電圧変換器は、

現在のフレームのデータ電圧をV。、以前のフレームの データ電圧を V , . . とすると、 V , ' = V , + f ( V。 - V。」 )の式を満たす補正データ電圧V ´を出力するようにデータ電圧を補正することを特徴 とする請求項30に記載の液晶表示装置。

【請求項32】多数のゲートラインと、前記ゲートライ ンと絶縁して交差する多数のデータラインと、前記ゲー トライン及びデータラインによって囲まれた領域に形成 され、それぞれ前記ゲートライン及びデータラインに連 結されているスイッチング素子を有する行列の形態に配 列された多数の画素とを含む液晶表示装置の駆動方法に おいて、

- (a) 前記ゲートラインに走査信号を順次に供給する段 階と;

- (b)画像信号ソースから画像信号を受信し、現在のフ 30 レームの画像信号と以前のフレームの画像信号とを考慮 して補正画像信号を生成する段階と;

- (c) 生成された前記補正画像信号に対応するデータ電 圧を前記データラインに供給する段階とを含む液晶表示 装置の駆動方法。

【請求項33】前記画像信号はアナログ電圧であること を特徴とする請求項32に記載の液晶表示装置の駆動方

【請求項34】前記画像信号はデジタル階調信号である ことを特徴とする請求項32に記載の液晶表示装置の駆 40 動方法。

【請求項35】前記段階(b)は、

(b-1)前記画像信号ソースから受信された階調信号 を一つのフレームだけ遅延させる段階と;

(b-2)前記画像信号から受信された現在のフレーム の階調信号と前記遅延された以前のフレームの階調信号 とを考慮して補正階調信号を生成する段階とを含むこと を特徴とする請求項34に記載の液晶表示装置の駆動方

【請求項36】前記補正画像信号は、

現在のフレームのデータ電圧をV゚、以前のフレームの データ電圧を $V_{n-1}$ とすると、  $V_n' = V_n + f$ ( V<sub>0</sub> - V<sub>0</sub> )の式を満たすことを特徴とする 請求項32乃至35のいずれかに記載の液晶表示装置の 駆動方法。

【請求項37】前記段階(b)は、

以前のフレームの階調信号と現在のフレームの階調信号 とに対応する補正階調信号を記録するルックアップテー ブルを検索して補正階調信号を生成することを特徴とす

【請求項38】前記ルックアップテーブルは、

前記補正データ電圧が第1電圧より大きい場合には前記 補正データ電圧を前記第1電圧とし、前記補正データ電 圧が第2電圧より小さい場合には前記補正データ電圧を 前記第2電圧とすることを特徴とする請求項37に記載 の液晶表示装置の駆動方法。

【請求項39】多数のゲートラインと、前記ゲートライ ンと絶縁して交差する多数のデータラインと、前記ゲー トライン及びデータラインによって囲まれた領域に形成 20 され、それぞれ前記ゲートライン及びデータラインに連 結されているスイッチング素子を有する行列の形態に配 列された多数の画素とを含む液晶表示装置の駆動方法に

- (a) 前記ゲートラインに走査信号を順次に供給する段 階と:

- (b) データ階調信号ソースから n ビットの階調信号を 受信し、nビットのうち現在のフレームのmビットの階 調信号と以前のフレームのmビットの階調信号とを考慮 して補正階調信号を生成する段階と;

- (c) 生成された前記補正階調信号に対応するデータ電 圧を前記データラインに供給する段階とを含む液晶表示 装置の駆動方法。

【請求項40】前記段階(b)は、

(b-1)前記データ階調信号ソースから受信されたn ビットの階調信号のうちmビットのみを一つのフレーム だけ遅延させる段階と;

(b-2)前記データ階調信号ソースから受信された現 在のフレームのmビットの階調信号と前記遅延された以 前のフレームのmビットの階調信号とを考慮してmビッ トの第1補正階調信号を生成する段階と;

(b-3)補正されずにバイパスされた(n-m)ビッ トを前記段階(b-2)で生成されたmビットの第1階 調信号に足して n ビットの第 2 補正階調信号を生成する 段階とを含む請求項39に記載の液晶表示装置の駆動方 法。

【請求項41】前記mは、前記nビットの階調信号のう ちLSBからi(0、1、2、...、n-1)個を除いた 残りのビットであることを特徴とする請求項40に記載 の液晶表示装置の駆動方法。

50 【請求項42】前記mは、r、g、bに応じてその値を

異にすることを特徴とする請求項41に記載の液晶表示 装置の駆動方法。

【請求項43】前記mは、前記bに対して最も大きいこ とを特徴とする請求項42に記載の液晶表示装置の駆動

【請求項44】前記mは、前記gに対して最も小さいこ とを特徴とする請求項42に記載の液晶表示装置の駆動

【請求項45】前記補正階調信号は、

$\vec{r}$ ータ電圧を $V_{0,1}$ とすると、  $V_0' = V_0 + f$ ( V<sub>0</sub> - V<sub>0-1</sub> )の式を満たすことを特徴とする 請求項39に記載の液晶表示装置の駆動方法。

【請求項46】前記段階(b-2)は、

以前のフレームの前記mビットの階調信号と現在のフレ ームの前記mビットの階調信号とに対応する補正階調信 号を記録するルックアップテーブルを検索して、第1補 正階調信号を生成することを特徴とする請求項40に記 載の液晶表示装置の駆動方法。

【請求項47】前記ルックアップテーブルは、

前記補正階調電圧が第1電圧より大きい場合には前記補 正データ電圧を前記第1電圧とし、前記補正データ電圧 が第2電圧より小さい場合には前記補正データ電圧を前 記第2電圧とすることを特徴とする請求項46に記載の 液晶表示装置の駆動方法。

【請求項48】多数のゲートラインと、前記ゲートライ ンと絶縁して交差する多数のデータラインと、前記ゲー トライン及びデータラインによって囲まれた領域に形成 され、それぞれ前記ゲートライン及びデータラインに連 結されているスイッチング素子を有するマトリックスの 30 形態に配列された多数の画素とを含む液晶表示装置の駆 動方法において、

- (a) 前記ゲートラインに走査信号を順次に供給する段 階と;

- (b)外部の画像信号ソースから×ビットの画像階調デ ータを受信する段階と;

- (c) 前記受信された画像階調データを一つのフレーム 遅延させる段階と;

- (d)前記一つのフレーム遅延されたデジタル階調デー タのMSByビットと現在のフレームで受信されるデジ 40 タル階調データのMSByビットとに基づいてルックア ップテーブルから動画像補正のための変数を導く段階 と;

- (e)前記一つのフレーム遅延されたデジタル階調デー タのLSB(x-y)ビットと、前記現在のフレームで 受信されるデジタル階調データのLSB( x - y ) ビッ トと、前記段階(d)で導いた変数とを演算処理して補 正されたグレーデータを生成する段階と;

- (f) 生成された前記補正されたグレーデータに対応す るデータ電圧を前記データラインに供給する段階とを含 50 形態に配列された多数の画素とを含む液晶表示装置の駆

む液晶表示装置の駆動方法。

【請求項49】前記補正されたグレーデータ(G)´)

$G_n' = f([G_n]_z, [G_{n-1}]_z + a([G_n]_z, [G$  $[G_n]_{r} = [G_n]_{r} / 2^{r} - b([G_n]_{r} [G_{n-1}]_{r})$  $\times$  [G<sub>n</sub>] / 2<sup>z</sup>

(ここで、zはx・y、[G゚]」はG゚のLSBzビッ トを全て0で満たした値、[G<sub>0.1</sub>],はG<sub>0.1</sub>のLSB z ビットを全て 0 で満たした値、 $_{_{V}}$  [  $G_{_{\Lambda}}$  ] は $G_{_{\Lambda}}$ のM S現在のフレームのデータ電圧を V<sub>0</sub>、以前のフレームの 10 By ビットを全て 0 で満たした値、aとbは全て正の整 数)に基づいて算出されることを特徴とする請求項48 に記載の液晶表示装置の駆動方法。

【請求項50】前記補正されたグレーデータ(G<sub>e</sub>´)

$G_{n}' = f'([G_{n}], a([G_{n}], [G_{n-1}],) \times$  $_{y}$  [  $G_{n}$  ] / 2  $^{z}$  - b ( [  $G_{n}$  ]  $_{z}$  [  $G_{n-1}$  ]  $_{z}$  )  $\times$   $_{y}$  [  $G_{n}$  ] / 2 <sup>z</sup>

$(zzv, zkx - y, f' = f([G_n]_x, y)$  $[G_{n-1}]_{\tau}$ ) -  $[G_n]_{4}$ ,  $[G_n]_{\tau}$ d $G_n$ OLSBzE20 ットを全て 0 で満たした値、 $\left[ G_{n-1} \right]_z$ は $G_{n-1}$ のLS B z ビットを全て 0 で満たした値、 , [ G 。 ] は G 。の M SByビットを全て0で満たした値、aとbは全て正の 整数)に基づいて算出されることを特徴とする請求項4 8に記載の液晶表示装置の駆動方法。

【請求項51】前記補正されたグレーデータ(G\_´)

$G_{n}' = f' ( [G_{n}]_{z}, [G_{n-1}]_{z} + G_{n} + a' ( [G_{n}]_{z})$  $_{z}$ ,  $[G_{n-1}]_{z}$ )  $\times_{v}[G_{n}] / 2^{z}$  - b (  $[G_{n}]_{z}$ ,  $[G_{n}]_{z}$  $_{n-1}$ ],  $\times$  [G<sub>n</sub>] / 2<sup>z</sup>

$(zzv, zkx - y, f' = f - G_n, [G_n]_zkG_n$ のLSBzビットを全て0で満たした値、[G<sub>0-1</sub>],は G \_ ,のLSBzビットを全て0で満たした値、

,[G,]はG,のMSByビットを全て0で満たした 値、a ´は整数、bは正の整数)に基づいて算出される ことを特徴とする請求項48に記載の液晶表示装置の駆

【請求項52】前記[G<sub>0</sub>]<sub>2</sub>=[G<sub>0-1</sub>]<sub>2</sub>である場合、  $G_n' = G_{n-1}$ の条件を満たすためにはa - b = 16でな ければならないことを特徴とする請求項49又は50に 記載の液晶表示装置の駆動方法。

【請求項53】前記[G゚。] ¸ = [G゚。 ₁ ] ¸ である場合、  $G_n = G_{n-1}$ の条件を満たすためにはa - b = 0でな ければならないことを特徴とする請求項51に記載の液 晶表示装置の駆動方法。

【請求項54】多数のゲートラインと、前記ゲートライ ンと絶縁して交差する多数のデータラインと、前記ゲー トライン及びデータラインによって囲まれた領域に形成 され、それぞれ前記ゲートライン及びデータラインに連 結されているスイッチング素子を有するマトリックスの

動装置において、

データ階調信号ソースから r、g、bに対する x ビット階調データを受信して、現在のフレームの x ビットの階調データと以前のフレームの x ビットの階調データとから所定のM S B ビットはルックアップテーブルを用いて第 1 補正し、現在のフレームの階調データの残りのビットと以前のフレームの階調データの残りのビットとは所定の演算によって第 2 補正し、前記第 1 補正と第 2 補正とを通じて補正階調データを出力するデータ階調信号補正部と;前記データ階調信号補正部から出力される前記 10 補正階調データに対応するデータ電圧に変えて画像信号を前記データラインに出力するデータドライバー部と;前記ゲートラインに走査信号を順次に供給するゲートドライバー部とを含む液晶表示装置の駆動装置。

【請求項55】前記データ階調信号補正部は、

前記データ階調信号ソースから×ビットの階調データを受信し、一つのフレームの間前記受信された階調データを保存して出力するフレームメモリと;前記フレームメモリの階調データの記録及び判読を制御するコントローラーと;前記データ階調信号ソースから受信される現在 20のフレームの×ビットの階調データと前記フレームメモリから受信される以前のフレームの×ビットの階調データとを考慮して補正階調データを生成して前記データドライバー部に出力するデータ階調信号変換器とを含むことを特徴とする請求項54に記載の液晶表示装置の駆動装置。

【請求項56】前記データ階調信号変換器は、

以前のフレームの画像データと現在のフレームの画像データとの×ビットのデータのMSByビットのデータ各々の提供を受けて、動画像補正のための変数(f、a、30b)を出力するルックアップテーブルと;以前の画像データと現在の画像データの×ビットのデータのLSBzビットのデータ各々の提供を受け、前記変数(f、a、b)の提供を受けて補正されたグレーデータを出力する演算部とを含むことを特徴とする請求項55に記載の液晶表示装置の駆動装置。

【請求項57】前記補正されたグレーデータ(G<sub>n</sub>´)は.

$G_n' = f'([G_n]_z, [G_{n-1}]_z + a([G_n]_z, [G_n]_z, [G_n]_z,$

(ここで、z はx - y、 $[G_n]_z$ は $G_n$ のL S B z ビットを全て0 で満たした値、 $[G_{n-1}]_z$ は $G_{n-1}$ のL S B z ビットを全て0 で満たした値、 $_y$   $[G_n]$  は $G_n$ のM S B y ビットを全て0 で満たした値、a b b は全て正の整数)に基づいて算出されることを特徴とする請求項5 6 に記載の液晶表示装置の駆動装置。

【請求項58】前記補正されたグレーデータ(G<sub>n</sub>′)

$G_{0}' = f'([G_{0}]_{1} + a([G_{0}]_{1}) \times *_{0}*50$  なものであり、この中でも薄膜トランジスタ(thin

\* [G<sub>n</sub>] / 2<sup>z</sup> - b ( [G<sub>n</sub>]<sub>z</sub>, [G<sub>n-1</sub>]<sub>z</sub>) x<sub>y</sub> [G<sub>n</sub>]

(ここで、z はx - y、f ´ = f ( [ $G_n$ ] $_z$ 、 [ $G_{n-1}$ ] $_z$ ) - [ $G_n$ ] $_4$ 、[ $G_n$ ] $_z$ は $G_n$ のL S B z ビットを全て0 で満たした値、[ $G_{n-1}$ ] $_z$ は $G_n$ のL S B z ビットを全て0 で満たした値、 $_y$  [ $G_n$ ]は $G_n$ のM S B y ビットを全て0 で満たした値、a と b は全て正の整数)に基づいて算出されることを特徴とする請求項5 6 に記載の液晶表示装置の駆動装置。

【請求項 5 9 】前記補正されたグレーデータ ( G ´ ) は

$G_{n}' = f'([G_{n}]_{z}, [G_{n-1}]_{z} + G_{n} + a'([G_{n}]_{z}, [G_{n-1}]_{z}) \times_{y} [G_{n}] / 2^{z} - b([G_{n}]_{z}, [G_{n-1}]_{z}) \times_{y} [G_{n}] / 2^{z}$

(ここで、z はx - y、f ´ = f - G<sub>n</sub>、[G<sub>n</sub>]  $_z$ はG<sub>n</sub> の L S B z ビットを全て 0 で満たした値、[G<sub>n-1</sub>  $_z$  は G<sub>n-1</sub> の L S B z ビットを全て 0 で満たした値、

$_y$  [  $G_n$  ] は $G_n$ のMSByビットを全て0で満たした値、a だを数、b は正の整数)に基づいて算出されることを特徴とする請求項5 6 に記載の液晶表示装置の駆動装置。

【請求項60】前記 [  $G_n$  ]  $_z$  = [  $G_{n-1}$  ]  $_z$  である場合、  $G_n$  ′ =  $G_{n-1}$  の条件を満たすためには a - b = 16 でなければならないことを特徴とする請求項57または58 に記載の液晶表示装置の駆動装置。

【請求項61】前記  $[G_n]_z = [G_{n-1}]_z$ である場合、 $G_n' = G_{n-1}$ の条件を満たすためにはa' - b = 0でなければならないことを特徴とする請求項59に記載の液晶表示装置の駆動装置。

### 【発明の詳細な説明】

[0001]

【発明の属する技術分野】本発明は液晶表示装置とその 駆動方法及び装置に係わり、特に、動画像具現に適する ように補償されたデータ電圧が印加される液晶表示装置 とその駆動方法及び装置に関するものである。

[0002]

【従来の技術】近来、パソコンやテレビなどの軽量化、 薄形化によってディスプレイ装置も軽量化、薄形化が要 求されており、このような要求に従って陰極線管(ca thode ray tube:CRT)の代わりに液晶 表示装置(liquid crystal displa y:LCD)のようなフラットパネル型ディスプレイが 開発されている。

【0003】LCDは二つの基板の間に注入されている 異方性誘電率を有する液晶物質に電界(electri cfield)を印加し、この電界の強さを調節して 基板に透過する光の量を調節することによって所望の画 像信号を得る表示装置である。このようなLCDは携帯 の簡便なフラットパネル型ディスプレイのうちの代表的 なものであり、この中でも薄膜トランジスタ(thin

film transistor: TFT) をスイッチ ング素子として用いたTFT LCDが主に用いられて いる。

11

【0004】最近は、TFT LCDがコンピュータの ディスプレイ装置だけでなくテレビのディスプレイ装置 として広く用いられるため、動画像を具現する必要が増 加してきた。しかしながら、従来のTFT LCDは応 答速度が遅いために動画像を具現するのは難しいという 短所があった。このような応答速度の問題を改善するた ensated band)モードを用いたり強誘電性 液晶(FLC; ferro-electricliqu id crystal)物質を用いたTFT LCDを用 いていた。

【0005】しかし、このようなOCBモードやFLC 物質を用いるためには従来のTFTLCDパネルの構造 を変えなければならないという問題点があった。

#### [0006]

【発明が解決しようとする課題】本発明が目的とする技 術的課題はこのような問題点を解決するためのものであ 20 り、本発明の第1目的は、TFT LCDのパネルの構 造を変える必要なく、液晶の駆動方法を変えることによ って液晶の応答速度を改善させるための液晶表示装置を 提供することにある。

【0007】また、本発明の第2目的は、前記液晶表示 装置の駆動方法を提供することにある。

【0008】また、本発明の第3目的は、前記液晶表示 装置の駆動装置を提供することにある。

# [0009]

【課題を解決するための手段】前記のような本発明の第 30 1目的を達成するための本発明の一つの特徴による液晶 表示装置は、データ階調信号ソースから階調信号を受信 し、現在のフレームの階調信号と以前のフレームの階調 信号とを考慮して補正階調信号を出力するデータ階調信 号補正部と;前記データ階調信号補正部から出力される 前記補正階調信号に対応するデータ電圧に変えて画像信 号を出力するデータドライバー部と;走査信号を順次に 供給するゲートドライバー部と:前記走査信号を伝達す る多数のゲートラインと、前記画像信号を伝達し、前記 ゲートラインと絶縁して交差する多数のデータライン と、前記ゲートライン及び前記データラインによって囲 まれた領域に形成され、それぞれ前記ゲートライン及び 前記データラインに連結されているスイッチング素子を 有するマトリックスの形態に配列された多数の画素とを 含む液晶表示パネルとを含んで構成される。

【0010】ここで、前記データ階調信号補正部は、前 記データ階調信号ソースから階調信号を受信し、一つの フレームの間前記受信された階調信号を保存して出力す るフレームメモリと;前記フレームメモリの階調信号の 階調信号ソースから受信される現在のフレームの階調信 号と前記フレームメモリから受信される以前のフレーム の階調信号とを考慮して前記補正階調信号を出力するデ - 夕階調信号変換器とを含む。

【0011】また、前記データ階調信号補正部は、前記 データ階調信号ソースから前記mビットの階調信号を受 信し、一つのフレームの間前記受信された階調信号を保 存して出力するフレームメモリと;前記フレームメモリ の階調信号の記録及び判読を制御するコントローラー めに、従来は、OCB(optically comp 10 と;前記データ階調信号ソースから受信される現在のフ レームの前記mビットの階調信号と前記フレームメモリ から受信される以前のフレームの前記mビットの階調信 号とを考慮して補正階調信号を生成して出力するデータ 階調信号変換器とを含み、前記データ階調信号ソースか らr、g、bに対するnビットの階調信号を受信し、前 記nビットのうち現在のフレームのmビットの階調信号 と以前のフレームの前記mビットの階調信号とを考慮し た補正階調信号を出力する。

> 【0012】また、前記データ階調信号補正部は、前記 データ階調信号ソースから x ビットの階調データを受信 し、一つのフレームの間前記受信された階調データを保 存して出力するフレームメモリと;前記フレームメモリ の階調データの記録及び判読を制御するコントローラー と;前記データ階調信号ソースから受信される現在のフ レームの×ビットの階調データと前記フレームメモリか ら受信される以前のフレームの×ビットの階調データと を考慮して補正階調データを生成して前記データドライ バー部に出力するデータ階調信号変換器とを含み、前記 データ階調信号ソースからr、g、bに対するxビット の階調データを受信して、現在のフレームの×ビットの 階調データと以前のフレームの×ビットの階調データと から所定のMSBビットはルックアップテーブルを用い て第1補正し、現在のフレームの階調データの残りのビ ットと以前のフレームの階調データの残りのビットとは 所定の演算によって第2補正し、前記第1補正と第2補 正とを通じて補正階調データを出力する。

【0013】また、前記のような本発明の第1目的を達 成するための本発明の他の一つの特徴による液晶表示装 置は、走査信号を伝達する多数のゲートラインと、デー 40 夕電圧を伝達し、前記ゲートラインと絶縁して交差する 多数のデータラインと、前記ゲートライン及びデータラ インによって囲まれた領域に形成され、それぞれ前記ゲ ートライン及びデータラインに連結されているスイッチ ング素子を有する行列の形態に配列された多数の画素と を含む液晶表示装置パネルと;ゲートラインに走査信号 を順次に供給するゲートドライバー部と;データ電圧ソ ースからデータ電圧を受信し、現在のフレームのデータ 電圧と以前のフレームのデータ電圧とを考慮して補正デ ータ電圧を出力するデータ電圧補正部と;前記データ電 記録及び判読を制御するコントローラーと;前記データ 50 圧補正部から出力される前記補正データ電圧を前記デー

タラインに供給するデータドライバー部とを含んで構成 される。

13

【0014】また、前記のような本発明の第2目的を達成するための本発明の一つの特徴による液晶表示装置の駆動方法は、多数のゲートラインと、前記ゲートラインと絶縁して交差する多数のデータラインと、前記ゲートライン及びデータラインによって囲まれた領域に形成され、それぞれ前記ゲートライン及びデータラインに連結されているスイッチング素子を有する行列の形態に配列された多数の画素とを含む液晶表示装置の駆動方法において、(a)前記ゲートラインに走査信号を順次に供給する段階と;(b)画像信号と以前のフレームの画像信号と考慮して補正画像信号を生成する段階と;

(c) 生成された前記補正画像信号に対応するデータ電 圧を前記データラインに供給する段階とを含んで構成さ れる。

【0015】また、前記のような本発明の第2目的を達 成するための本発明の他の一つの特徴による液晶表示装 置の駆動方法は、多数のゲートラインと、前記ゲートラ 20 インと絶縁して交差する多数のデータラインと、前記ゲ ートライン及びデータラインによって囲まれた領域に形 成され、それぞれ前記ゲートライン及びデータラインに 連結されているスイッチング素子を有する行列の形態に 配列された多数の画素とを含む液晶表示装置の駆動方法 において、(a)前記ゲートラインに走査信号を順次に 供給する段階と;(b)データ階調信号ソースからnビ ットの階調信号を受信し、n ビットのうちの現在のフレ ームのmビットの階調信号と以前のフレームのmビット の階調信号とを考慮して補正階調信号を生成する段階 と;(c)生成された前記補正階調信号に対応するデー タ電圧を前記データラインに供給する段階とを含んで構 成される。

【0016】また、前記のような本発明の第2目的を達 成するための本発明のまた他の一つの特徴による液晶表 示装置の駆動方法は、多数のゲートラインと、前記ゲー トラインと絶縁して交差する多数のデータラインと、前 記ゲートライン及びデータラインによって囲まれた領域 に形成され、それぞれ前記ゲートライン及びデータライ ンに連結されているスイッチング素子を有するマトリッ 40 クスの形態に配列された多数の画素とを含む液晶表示装 置の駆動方法において、(a)前記ゲートラインに走査 信号を順次に供給する段階と;(b)外部の画像信号ソ ースから×ビットの画像階調データを受信する段階と; (c) 前記受信された画像階調データを一つのフレーム 遅延させる段階と; (d)前記一つのフレーム遅延され たデジタル階調データのMSByビットと現在のフレー ムで受信されるデジタル階調データのMSB У ビットと に基づいてルックアップテーブルから動画像補正のため

れたデジタル階調データのLSB(×・y)ビットと、前記現在のフレームで受信されるデジタル階調データのLSB(×・y)ビットと、前記段階(d)で導いた変数とを演算処理して補正されたグレーデータを生成する段階と;(f)生成された前記補正されたグレーデータに対応するデータ電圧を前記データラインに供給する段階とを含んで構成される。

【0017】また、前記のような本発明の第3目的を達 成するための本発明の一つの特徴による液晶表示装置の 駆動装置は、多数のゲートラインと、前記ゲートライン と絶縁して交差する多数のデータラインと、前記ゲート ライン及びデータラインによって囲まれた領域に形成さ れ、それぞれ前記ゲートライン及びデータラインに連結 されているスイッチング素子を有するマトリックスの形 態に配列された多数の画素とを含む液晶表示装置の駆動 装置において、データ階調信号ソースからr、g、bに 対する×ビットの階調データを受信して、現在のフレー ムの×ビットの階調データと以前のフレームの×ビット の階調データとから所定のMSBビットはルックアップ テーブルを用いて第1補正し、現在のフレームの階調デ ータの残りのビットと以前のフレームの階調データの残 りのビットとは所定の演算によって第2補正し、前記第 1補正と第2補正とを通じて補正階調データを出力する データ階調信号補正部と;前記データ階調信号補正部か ら出力される前記補正階調データに対応するデータ電圧 に変えて画像信号を前記データラインに出力するデータ ドライバー部と;前記ゲートラインに走査信号を順次に 供給するゲートドライバー部とを含んで構成される。

【 0 0 1 8 】ここで、前記データ階調信号補正部は、前 記データ階調信号ソースから×ビットの階調データを受信し、一つのフレームの間前記受信された階調データを保存して出力するフレームメモリと;前記フレームメモリの階調データの記録及び判読を制御するコントローラーと;前記データ階調信号ソースから受信される現在のフレームの×ビットの階調データと前記フレームメモリから受信される以前のフレームの×ビットの階調データとを考慮して補正階調データを生成して前記データドライバー部に出力するデータ階調信号変換器とを含む。

[0019]

【発明の実施の形態】以下、本発明の実施例を詳細に説明する。

【0020】一般に、LCDは走査信号を伝達する多数のゲートラインと、このゲートラインに交差して形成され、データ電圧を伝達するデータラインとを含む。また、LCDはこのゲートライン及びデータラインによって囲まれた領域に形成され、それぞれゲートライン及びデータラインとスイッチング素子を通じて連結される行列の形態の多数の画素を含む。

に基づいてルックアップテーブルから動画像補正のため 【0021】LCDにおいて各画素は液晶を誘電体としの変数を導く段階と;(e)前記一つのフレーム遅延さ 50 て有するキャパシター、つまり液晶キャパシターにモデ

リングすることができるが、このような L C D における 各画素の等価回路は図 1 のとおりである。

15

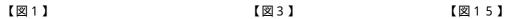

【 0 0 2 2 】図 1 に示したように、液晶表示装置の各画素は、データライン  $(D_m)$  とゲートライン  $(S_n)$  にそれぞれソース電極とゲート電極が連結される T F T 1 0 と、 T F T D がしーン電極と共通電圧  $(V_{oom})$  との間に連結される液晶キャパシター  $(C_n)$  と、  $(C_n)$  とを含む。

【0023】図1において、ゲートライン( $S_n$ )にゲ 10 ートオン信号が印加されてTFT10がターンオン(turnon)されると、データラインに供給されたデータ電圧( $V_a$ )がTFTを通じて各画素電極(図示せず)に印加される。そうすると、画素電極に印加される画素電圧( $V_p$ )と共通電圧( $V_{com}$ )との差に該当する電界が液晶(図1では等価的に液晶キャパシターで示した)に印加され、この電界の強さに対応する透過率で光が透過するようにする。この時、画素電圧( $V_p$ )は1フレームの間維持されなければならないが、図1においてストレージキャパシター( $C_{s_1}$ )は画素電極に印加さ 20れた画素電圧( $V_p$ )を維持するために補助として用いられる。

【0024】一方、液晶は異方性誘電率を有するため、液晶の方向によって誘電率が異なる特性がある。つまり、電圧が印加されるのに従って液晶の方向子が変わると誘電率も従って変わり、これによって液晶キャパシターのキャパシタンス(以下、これを液晶キャパシタンスという)値も変わるようになる。一度TFTがオンされる区間の間液晶キャパシターに電荷を供給した後でTFTがオフ状態となるが、Q=CVであるので、液晶キャ30パシタンスが変わると液晶にかかる画素電圧(Vg)もまた変わるようになる。

A / dになる。 T N モードに用いられる液晶の場合には - > 0 であるので、液晶に印加される画素 電圧が高くなるほど液晶キャパシタンスがより大きくなる。

【0026】n番目のフレームでフルブラックを具現す 50 が経過した後にはじめて目標画素電圧に到達するように

るためにTFTが充電するべき電荷量は $C(5V) \times 5$  Vである。しかし、すぐ前のフレームであるn-1番目のフレームでフルホワイト( $V_{n-1} = 0$  V)であったと仮定すれば、TFTのターンオン時間の間には液晶がまだ応答する前であるので液晶キャパシタンスはC(0 V)となる。従って、フルブラックを具現するためにの番目のフレームで5 Vのデータ電圧( $V_a$ )を印加しても実際に画素に充電される電荷量は $C(0V) \times 5$  Vとなり、C(0V) < C(5V)であるので液晶に実際に 供給される画素電圧( $V_p$ )は5 Vに及ばない画素電圧(例えば3.5 V)が印加されるためフルブラックが具現されない。

【0028】つまり、これを階調の観点から説明すると、任意の画素に印加される信号(画素電圧)が低い階調から高い階調に(または高い階調から低い階調に)変わる場合、現在のフレームの階調は以前のフレームの階調の影響を受けるのですぐに所望の階調に到達することができず、いくつかのフレームが経過した後にはじめて所望の階調に到達するようになる。同様に、現在のフレームの画素の透過率は以前のフレームの画素の透過率の影響を受けるのでいくつかのフレームが経過した後に所望の透過率を得ることができる。

【 0 0 2 9 】一方、n - 1 フレームがフルブラックであり、つまり画素電圧( $V_p$ )が5 Vであり、n フレームでフルブラックを具現するために5 V のデータ電圧が印加されたとすると、液晶キャパシタンスはC (5 V)であるので画素にはC (5 V) × 5 V に該当する電荷量が充電され、これによって液晶の画素電圧( $V_p$ ) は5 V となる。

【 0 0 3 0 】このように、液晶に実際に供給される画素電圧 ( $V_p$ ) は現在のフレームに供給されるデータ電圧だけでなく、以前のフレームの画素電圧 ( $V_p$ ) によっても決定される。

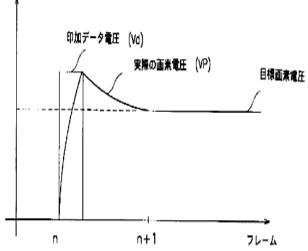

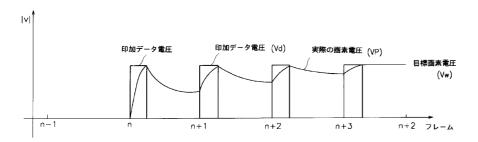

【0031】図2は従来の駆動方式で印加される場合の データ電圧及び画素電圧を示す図である。

【0032】図2に示したように、従来は以前のフレームの画素電圧( $V_p$ )を考慮せずに目標画素電圧( $V_w$ )に該当するデータ電圧( $V_a$ )を毎フレームごとに印加した。従って、実際に液晶に印加される画素電圧( $V_p$ )は先に説明したように以前のフレームの画素電圧に対応する液晶キャパシタンスによって目標画素電圧より低くまたは高くなる。従って、いくつかのフレームが経過した後にはじめて日標画表電圧に到達するとうに

なる。

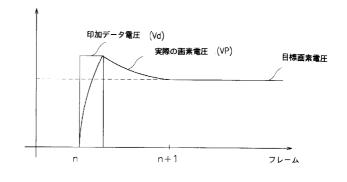

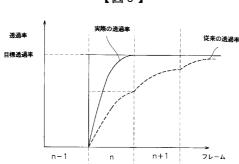

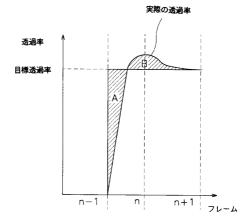

【0033】図3はこのような従来の駆動方法による液 晶表示装置の透過率を示す図である。

【0034】図3に示したように、従来は先に説明した ように実際の画素電圧が目標画素電圧より低くなるた め、液晶の応答時間が1フレーム以内である場合にもい くつかのフレームが経過した後にはじめて目標透過率に

【0035】本発明の実施例は、現在のフレームの画像 較して次のような補正信号(S\_')を生成した後、補 正された画像信号(S<sub>0</sub>′)を各画素に印加する。ここ で、画像信号(S゚)はアナログ駆動方式である場合に はデータ電圧を意味するが、デジタル駆動方式である場 合にはデータ電圧を制御するために二進化された階調信 号を用いるので、実際に画素に印加される電圧の補正は 階調信号の補正を通じて行われる。

【0036】まず、現在のフレームの画像信号(階調信 号またはデータ電圧)が以前のフレームの画像信号と同 一であれば補正を行わない。

【0037】次に、現在のフレームの階調信号(または データ電圧)が以前のフレームの階調信号(データ電 圧)より高い場合には現在の階調信号(データ電圧)よ り高い補正された階調信号(データ電圧)を出力し、現 在のフレームの階調信号 (データ電圧)が以前のフレー ムの階調信号(データ電圧)より低い場合には現在の階\*  $C_d=\langle C_i \rangle=1/3$  (  $\epsilon\parallel+2$   $\epsilon\perp$  ) A/d=5/3  $\epsilon\perp$  A/d=5/3  $C_0$

A / dである。

【0044】図4から、 (V)/ は次の数式2で 示すことができる。

[0045]

$$ε$$

(V)  $/ε \bot = 1/3$  (2 V + 1) [ 数 3 ]

C (V) = C<sub>1</sub>+C<sub>st</sub>=  $ε$  (V) A/d+5/3 C<sub>0</sub>=1/3 (2 V + 1) C<sub>0</sub>+5/3 C<sub>0</sub>=2/3 (V+3) C<sub>0</sub>

【0048】画素に印加される電荷量Qは保存されるの で、次の数式4が成立する。

[0049]

【数4】

$$Q=C(V_{n-1})V_n=C(V_f)V_f$$

【0050】ここで、V。は現在のフレームに印加され るデータ電圧(反転駆動式の場合にはデータ電圧の絶対 値)を示し、C (  $V_{n-1}$  ) は以前のフレーム ( n - 1 フ  $V_n$ = C (  $V_{n-1}$  )  $V_n$ = C (  $V_{r}$  )  $V_r$ = 2  $\not$  3 (  $V_{n-1}$  + 3 )  $V_n$ = 2  $\not$  3 (  $V_r$  + 3 )  $V_r$

【0053】従って、実際の画素電圧V,は次の数式6 で示すことができる。

[0054]

【数6】

$$V_f = \frac{-3 + \sqrt{9 + 4V_n(V_{n-1} + 3)}}{2}$$

\*調信号(データ電圧)より低い補正された階調信号(デ ータ電圧)を出力する。この時、補正が行われる程度は 現在の階調信号(データ電圧)と以前のフレームの階調 信号(データ電圧)との差に比例する。

【0038】以下、本発明の実施例によるデータ電圧の 補正方法を説明する。

【0039】図4は液晶表示装置の電圧 - 誘電率間の関 係を簡単にモデリングした図である。

【0040】図4において、横軸は画素電圧であり、縦 信号(S<sub>0</sub>)を以前のフレームの画像信号(S<sub>0.1</sub>)と比 10 軸は特定画素電圧Vでの誘電率( (V))と液晶が基 板に平行な方向に配列された場合、つまり液晶が光の透 過方向と垂直な場合の誘電率( )との比を示す。

> 【0041】図4においては、 (V)/ 値、つまり / を3と仮定し、VょとV﹏、とを 各々1V、4Vと仮定した。ここで、V・・・とV・・・・とと それぞれフルホワイト及びフルブラック(またはその反 対)に該当する画素電圧を示す。

【0042】ストレージキャパシターのキャパシタンス (以下、これを 'ストレージキャパシタンス 'とする) 20 が液晶キャパシタンスの平均値 C 、 と同一であると し、LCD基板の広さ及び基板間の距離を各々Aとdと すると、ストレージキャパシタンス C 、, は次の数式 1 で 示すことができる。

[0043]

【数1】

(10)

\*【0046】LCDの総キャパシタンスC(V)は液晶 キャパシタンスとストレージキャパシタンスとの合計で 30 あるので、LCDの総キャパシタンスはC(V)は数式 1及び2から次の数式3で示すことができる。

[0047]

レーム)の画素電圧に対応するキャパシタンスを示し、 C(V<sub>1</sub>)は現在のフレーム(nフレーム)の実際の画 素電圧(V,)に対応するキャパシタンスを示す。

【0051】数式3及び数式4から次の数式5が導かれ 40 る。

[0052]

【数5】

【0055】前記の数式6から明確に分かるように、実 際の画素電圧V、は現在のフレームに印加されたデータ 電圧(V。)と以前のフレームに印加された画素電圧 (V<sub>0.1</sub>)とによって決められる。

【0056】一方、nフレームで画素電圧が目標電圧 50 (V<sub>0</sub>)に到達するようにするために印加されるデータ

電圧をV<sub>a</sub>´とすれば、V<sub>a</sub>´は数式5から次の数式7で 示すことができる。

[0057]

【数7】

$$(V_{n-1}+3) V_n = (V_n+3) V_n$$

【 0 0 5 8 】従って、 V<sub>。</sub>´ は次の数式 8 で示すことが できる。

[0059]

【数8】

$$V_{n}' = \frac{V_{n} + 3}{V_{n-1} + 3} V_{n} = V_{n} + \frac{V_{n} - V_{n-1}}{V_{n-1} + 3} V_{n}$$

【0060】このように、現在のフレームの目標画素電 圧(V゚)と以前のフレームの画素電圧(V゚。゚゚)とを考 慮して前記数式8により求められるデータ電圧(V ´)を印加すれば、目標とする画素電圧 V 。にすぐ到達 することができる。

【0061】前記数式8は図4に示した図及びいくつか の基本仮定から導かれた式であり、一般的なLCDで適 用されるデータ電圧Void次の数式9で示すことがで きる。

[0062]

【数9】

$$|V_n| = |V_n| + f(|V_n| - |V_{n-1}|)$$

【0063】ここで、関数fはLCDの特性によって決 められる。関数 f は基本的に次の性質を有する。

【0064】つまり、V。とV。」とが同一である場合に f = 0となり、 $V_s$ が $V_{s,1}$ よりより大きい場合にfは0より大きく、V。がV。、より小さい場合にfは0より小

【0065】次に、本発明の実施例によるデータ電圧の 印加方法について説明する。

【0066】図5は本発明によるデータ電圧印加方法を 示す図である。

【0067】図5に示したように、本発明の第1実施例 では現在のフレームの目標画素電圧と以前のフレームの 画素電圧(データ電圧)とを考慮して補正されたデータ 電圧 V。´を印加して、画素電圧(V。)がすぐ目標電圧 に到達するようにする。つまり、本発明の第1実施例で は現在のフレームの目標電圧と以前のフレームの画素電 40 信号ソース(例えば、グラフィック制御器)からデータ 圧とが異なる場合、現在のフレームの目標電圧より高い 電圧(またはさらに低い電圧)を補正されたデータ電圧 として印加して第1フレームですぐ目標電圧レベルに到 達するようにした後、以降のフレームでは目標電圧をデ - 夕電圧として印加する。このようにして、液晶の応答 速度を改善することができる。

【0068】この時、補正されたデータ電圧(電荷量) は以前のフレームの画素電圧によって決定される液晶キ ャパシタンスを考慮して決められる。つまり、本願発明 は以前のフレームの画素電圧レベルを考慮して電荷量

(Q)を供給することにより、第1フレームにおいてす ぐ目標電圧レベルに到達するようにする。

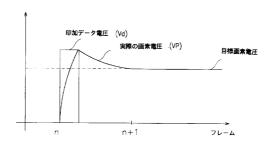

【 0 0 6 9 】図 6 は本発明の第 1 実施例によってデータ 電圧を印加した場合の液晶表示装置の透過率を示す図で ある。図6に示したように本発明の第1実施例によれ ば、補正されたデータ電圧を印加するため、現在のフレ ームにおいてすぐ目標透過率に到達する。

【0070】一方、本発明の第2実施例では目標電圧よ りやや高い補正された電圧V。´を画素電圧として印加 10 する。このように駆動する場合には、図7に示したよう に液晶の応答時間の約1/2以前では透過率が目標値よ リ小さくなるが、それ以後は目標値より過度になり(o vercompensate)、平均的な透過率が目標 透過率と同一となる。

【0071】次に、本発明の実施例による液晶表示装置 について説明する。

【0072】図8は本発明の実施例による液晶表示装置 を示す図である。図8に示した本発明の実施例による液 晶表示装置は、デジタル駆動方法を用いる。

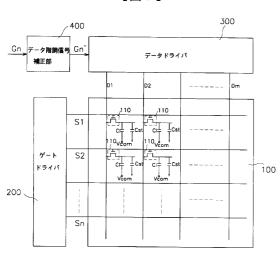

20 【0073】図8に示したように、本発明の実施例によ る液晶表示装置は、液晶表示装置パネル100、ゲート ドライバー200、データドライバー300及びデータ 階調信号補正部400を含む。

【0074】液晶表示装置パネル100には、ゲートオ ン信号を伝達するための多数のゲートライン(S、 S¸、S¸、…、S¸)が形成されており、補正されたデ ータ電圧を伝達するためのデータライン(D<sub>1</sub>、D<sub>2</sub>、 ...、D ( ) が形成されている。ゲートライン及びデータ ラインによって囲まれた領域は各々画素をなし、各画素 30 はゲートライン及びデータラインにそれぞれゲート電極 及びソース電極が連結される薄膜トランジスタ110 と、薄膜トランジスタ110のドレーン電極に連結され る画素キャパシター(C<sub>1</sub>)と、ストレージキャパシタ (C<sub>1</sub>)とを含む。

【0075】ゲートドライバー200はゲートラインに 順次にゲートオン電圧を印加して、ゲートオン電圧が印 加されたゲートラインにゲート電極が連結されるTFT をターンオンさせる。

【0076】データ階調信号補正部400はデータ階調 階調信号(G<sub>2</sub>)を受信した後、先に説明したように現 在のフレームのデータ階調信号と以前のフレームのデー 夕階調信号とを考慮して補正されたデータ階調信号(G ´)を出力する。この時、階調信号補正部はスタンド アローン(stand-alone)ユニットとして存 在することもでき、グラフィックカードやLCDモジュ ールに統合されることもできる。

【0077】データドライバー300は、データ階調信 号補正部400から受信された補正された階調信号(G 。´)を該当階調電圧(データ電圧)に変えて各々デー

(11)

(12)

タラインに印加する。

【0078】図9は本発明の実施例によるデータ階調信 号補正部400を詳細に示すブロック図である。

21

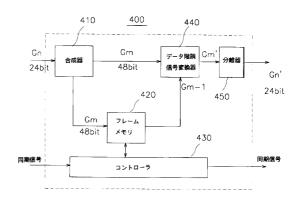

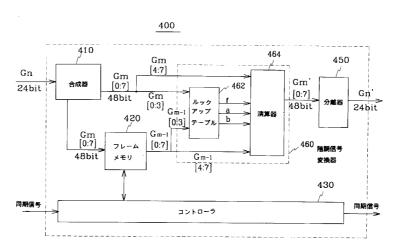

【0079】図9に示したように、本発明の実施例によ るデータ階調信号補正部400は合成器410、フレー ムメモリ420、コントローラー430、データ階調信 号変換器440及び分離器450を含む。

【0080】合成器410はデータ階調信号ソースから 伝送される階調信号(G<sub>0</sub>)を受信して、データ階調信 号補正部400が処理し得る速度にデータストリームの 10 周波数を変換する。例えば、データ階調信号ソースから 24ビットのデータが65MHzの周波数に同期して受 信され、データ階調信号補正部400の構成要素の処理 速度が50Mhzが限界であるとすれば、合成器410 は24ビットの階調信号を二個ずつ合わせて48ビット の階調信号(G\_)に合成してフレームメモリ420に 伝送する。

【0081】フレームメモリ40はコントローラー43 0の制御によって所定のアドレスに保存されている以前 の階調信号(Gm.1)をデータ階調信号変換器440に 20 動され、補正電圧を考慮して電圧が0Vから8Vまで必 出力すると同時に、合成器410から伝送される階調信 号(G\_)を前記所定のアドレスに保存する。データ階 調信号変換器440は合成器から出力される現在のフレ ームの階調信号(G<sub>m</sub>)とフレームメモリ420から出 力される以前のフレームの階調信号(G\_\_\_,)とを受信 し、現在のフレームの階調信号と以前のフレームの階調 信号とを考慮して補正された階調信号 G \_ ' を生成す る。

【0082】分離器450は、データ階調信号変換器4 40から出力される48ビットの補正されたデータ階調30ルの構成である。 信号(G\_^´)を分離して24ビットの補正された階調 信号(Gn')を出力する。

【0083】本発明の実施例では、データ階調信号に同 期するクロック周波数がフレームメモリにアクセスする クロック周波数と相異するためデータ階調信号を合成及 び分離する合成器410及び分離器450が必要であっ たが、データ階調信号に同期するクロック周波数とフレ ームメモリ420にアクセスするクロック周波数とが同 一である場合にはこのような合成器と分離器とは必要で なくなる。

【0084】本発明の実施例によるデータ階調信号変換 器440としては、先に説明した数式9を満たすデジタ ル回路を直接製造して使用することができる。

【0085】また、ルックアップテーブル(Lookup table)を作成してROM(read onl y memory)に保存した後にアクセスして階調信 号を補正することもできる。

【0086】実際は、補正データ電圧(V')は単に以 前のフレームのデータ電圧(V゚゚゚゚゚)と現在のフレーム のデータ電圧(V<sub>0</sub>)との差にだけ比例するのではなく 50

それぞれの絶対値にも依存する複雑な関数であるので、 このようにルックアップテーブルを構成すれば演算処理 に依存するより回路がはるかに簡単になるという長所が ある。

【0087】一方、本発明の実施例によってデータ電圧 を補正するためには実際に用いられるグレースケールの 範囲よりさらに広いダイナミックレンジを有しなければ ならず、アナログ回路では高電圧IC(integra ted circuit)を用いることによって解決す ることができるが、デジタル方式では分けられる階調の 数が限定されている。例えば、6ビット階調の場合に6 4個の階調レベルのうちの一部は実際の階調表示ではな い変調された電圧のために割り当てなければならない。 つまり、一部の階調レベルは電圧補正用に割り当てなけ ればならない。従って、表現すべき階調の数が減るよう

【0088】一方、階調数の減少を防ぐためには次のよ うなトランケーション(truncation)の概念 が導入され得る。例えば、液晶が1Vから4Vの間で駆 要であると仮定してみよう。この時、補正を充実に行う ために8 Vまでを6 4 個の段階に分けると、実際に表現 できる階調は30個程度に過ぎないようになる。従っ て、電圧幅を1 V から4 V に低くし、計算上矯正された 電圧(V\_´)が4Vを越す場合には全ての補正電圧を 4 V にトランケートすれば階調数の減少を減らすことが

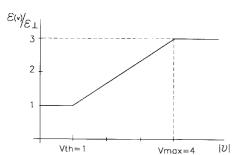

【0089】図10はこのようにトランケーション概念 が導入された本発明の実施例によるルックアップテーブ

【0090】以上では本発明の実施例について説明した が、本発明は前記実施例にのみ限定されるものではな く、その他の多様な変更や変形が可能である。

【0091】例えば、本発明の実施例では図8において はデジタル方式で駆動する液晶表示装置を説明したが、 その他にもアナログ方式で駆動する液晶表示装置にも本 発明が適用されることができる。

【 0 0 9 2 】この場合、図 8 で説明したデータ階調信号 補正部に対応する役割を果たすデータ階調補正部が必要 40 であり、このデータ階調補正部は数式9を満たすアナロ グ回路を通じて具現できる。

【0093】以上で説明したように、本発明によれば、 データ電圧を補正し、補正されたデータ電圧を画素に印 加することによって画素電圧がすぐに目標電圧レベルに 到達できるようにする。従って、TFT LCDのパネ ル構造を変える必要なく液晶の応答速度を改善すること ができる。

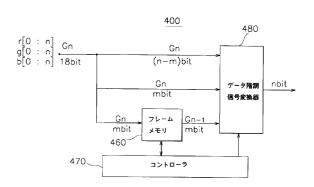

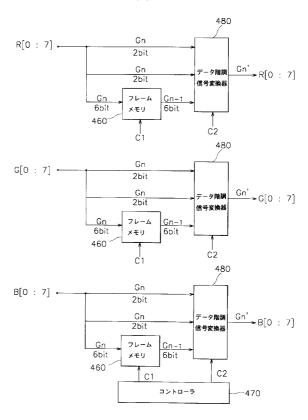

【0094】図11は本発明の他の実施例によるデータ 階調信号補正部400を詳細に示すブロック図である。 【 0 0 9 5 】図 1 1 に示したように、本発明の実施例に

よるデータ階調信号補正部400はフレームメモリ46 0と、コントローラー(controller)470 と、データ階調信号変換器480とを含み、データ階調 信号ソースからr(red)、g(green)、b (blue)のそれぞれに対するnビットの階調信号を 受信する。従って、データ階調信号補正部440に受信 される階調信号は総(3×n)ビットである。ここで、 当業者はデータ階調信号ソースから(3×n)ビットの 階調信号が同時にデータ階調信号変換部480に印加さ れるようにすることができ、nビットのr、g、b階調 10 信号の各々が順次に印加されるようにすることもでき る。

【0097】データ階調信号変換器480は、データ階調信号ソースから受信されるnビットのうちの補正が行われずにバイパスされる現在のフレーム(Gn)の(n-m)ビットと、補正のために受信される現在のフレーム(Gn)のmビットと、フレームメモリ460によって遅延された以前のフレーム(Gn)のmビットとを受信した後、現在及び以前のフレームのmビットを考慮して補正された階調信号(Gn)を生成する。

【 0 0 9 8 】前記の内容を図 1 2 を参照してさらに詳細 30 に説明する。

【0099】図12は本発明の第1実施例によるデータ電圧補正部の動作を概念的に説明した図である。図12でデータ階調信号ソースからデータ電圧補正部400に受信されるr、g、b階調信号は各々8ビットであると仮定する。

【0100】データ電圧補正部400で受信される8ビットのr階調信号のうち、LSBから2ビット(現在のフレームのビット)は補正が行われないビットであって、バイパスされてデータ階調信号変換器480に入力40される。そして、現在のフレームの残りの6ビットは補正のためにデータ階調信号変換器480に入力され、同時にフレームメモリ460の所定のアドレスに保存される。

【0101】ここで、フレームメモリ460は現在のフレームのビットを1フレームの間保存して出力するので、データ階調信号変換器480には以前のフレームの6ビット階調信号が出力される。

【 0 1 0 2 】 そうすると、データ階調信号変換器 4 8 0 は現在のフレームの 6 ビットの階調信号と以前のフレー 50

ムの6 ビットの r 階調信号とを受信し、以前のフレームと現在のフレームとの6 ビットの r 階調信号を考慮した補正された階調信号を生成する。そして、生成された補正された6 ビットの階調信号と L S B である現在のフレームの2 ビットの階調信号とを足して、最終補正された8 ビットの階調信号(G\_^´)を出力する。

【0103】同様に、データ階調信号変換器480は、8ビットのg階調信号と、8ビットのb階調信号も前記 r階調信号と同様に6ビットの以前のフレームと現在のフレームの階調信号とを考慮した8ビットの補正された階調信号を出力する。このように出力された8ビットの補正階調信号は、データドライバーによって該当電圧に変換されてデータラインに印加される。

【0104】ここで、フレームメモリ460に保存される r、g、bの6ビットの階調信号は設定されたアドレスに各々保存される。一方、当業者は一つのフレームメモリ460を用いて r、g、bを担当するアドレス領域を指定する方式を使用することができ、r、g、bを担当する3つのフレームメモリで一つのフレームメモリを用いるような効果を出すように設計することができる。【0105】図12を参照した説明から、データ階調信号ソースから8ビットの階調信号が入力される際、従来のフレームメモリのSXGA(1280×1024)の場合には8ビットの r、g、b階調信号を保存しなければならないので最少30Mbのメモリを必要とするが、本発明の実施例によるフレームメモリ460は6ビットの階調信号のみを保存すればいいので従来に比べて少ない容量のメモリを使用することができるという長所がある。

【 0 1 0 6 】ここで、フレームメモリ4 6 0 に保存される階調信号のビットの数が少ないほど、フレームメモリ4 6 0 の容量は従来に比べてはるかに少なくすることができる。

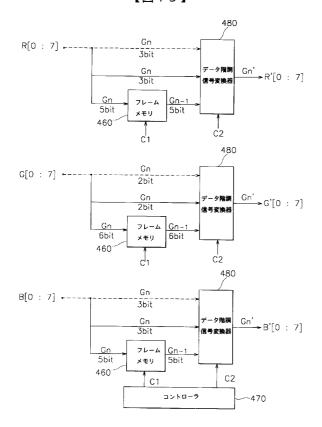

【0107】以下、図13を参照して本発明の第2実施例によるデータ電圧補正部の動作を説明する。図13は本発明の第2実施例によるデータ電圧補正部の動作を概念的に説明した図であって、理解を助けるために一つのフレームメモリと一つのデータ階調信号変換器とで設計した場合を例に挙げて説明する。しかし、フレームメモリとデータ階調信号変換器とはLCDパネルの等級、階調信号のビット数、及び設計者の意図によってその使用個数を変えることができる。例えば、フレームメモリとデータ階調信号変換器とを構成するメモリの数を3つにしてr、g、bの各々を担当するようにすることができる。

【0108】そして、当業者は前記フレームメモリをr、g、bの各階調信号に対応してリードとライトを専担する2つの第1及び第2メモリで構成してデータ処理速度を向上させることができる。

【0109】つまり、階調信号が順次にフレームメモリ

に入力される時、奇数番目の階調信号を第1メモリに保 存し、偶数番目の階調信号を第2メモリに保存し、奇数 番目の階調信号が第1メモリに保存される時には第2メ モリからリードし、偶数番目の階調信号が第2メモリに 保存される時には第1メモリからリードして、データが フレームメモリから迅速にリード及びフレームメモリに 迅速にライトされるようにすることができる。

【0110】図13において、データ電圧補正部400 は第1実施例によるデータ電圧補正部400とその構成 は同一である。しかし、第2実施例によるデータ電圧補 10 正部400は入力される階調信号のビット数に比べて出 力する階調信号のビット数を減らす動作を行うことによ り、第1実施例とは区別される。第2実施例によるデー タ電圧補正部400の動作は以下のようである。

【0111】データ階調電圧ソースからr、g、bに対 する8ビットの階調信号が受信されると、8ビットのr 階調信号のうちの下位ビットである3ビットは補正され ないビットであって点線ラインに沿ってバイパスされ、 残りの現在のフレームの5ビットはデータ階調信号変換 器430とフレームメモリ410とに入力される。

【0112】フレームメモリ410に入力される現在の フレームの 5 ビットの r 階調信号は所定のアドレスに保 存されて次のフレームに出力され、以前のフレームの5 ビットの r 階調信号がデータ階調信号変換器 4 3 0 に出 力される。そうすると、データ階調信号変換器430は 現在のフレーム(G。)の5ビットのr階調信号と以前 のフレーム (G<sub>0-1</sub>) の 5 ビットの r 階調信号とを受信 するようになり、現在のフレームと以前のフレームとの 階調信号の差に比例する補正された階調信号(G<sub>g</sub>´) を生成して出力する。この時、出力される補正されたr 30 階調信号 $(G_a^*)$ は、補正された5ビットと補正され ていない3ビットとが合わせられた8ビットである。

【0113】そして、8ビットのG階調信号は点線ライ ンに沿って2ビットがバイパスされ、残りの6ビットの 階調信号(G<sub>1</sub>)はデータ階調信号変換器430とフレ ームメモリ410とに入力される。ここで、フレームメ モリ410は、現在のフレームの6ビットのg階調信号 を所定のアドレスに保存し、以前のフレーム(G\_\_\_\_) の6ビットのg階調信号を出力する。従って、データ階 調信号変換器430は現在及び以前のフレームの6ビッ 40 スサイズは通常、×4、×8、×16、×32などにな トのg階調信号を用いて補正された階調信号(G\_´) を出力する。この時、補正されたg階調信号(G。 は、補正された6ビットと補正されていない2ビットと が合わせられた8ビットである。

【0114】最後に、8ビットのb階調信号は点線ライ ンに沿って3ビットがバイパスされ、残りの5ビットの 階調信号(G<sub>g</sub>)はデータ階調信号変換器430とフレ ームメモリ410とに入力される。ここで、フレームメ モリ410は、現在のフレームの5ビットのg階調信号 を所定のアドレスに保存し、以前のフレーム( $G_{a,1}$ ) 50 t s) 6 つのみを補正し、残りの 2 つの t S t S t は補正

の5ビットのg階調信号を出力する。従って、データ階 調信号変換器430は現在及び以前のフレームの5ビッ トのg階調信号を用いて補正された階調信号(G<sub>g</sub>´) を出力する。この時、補正された g 階調信号 ( G 。 は、補正された5ビットと補正されていない3ビットと が合わせられた8ビットである。

【 0 1 1 5 】前記において、8 ビットのr、g、b 階調 信号のうちでバイパスされるビットはLSBから始まる のが好ましく、当業者によってバイパスされるビットの 数を異にすることができる。従って、当業者は、構成さ れるフレームメモリの容量及び個数とデータ階調信号変 換器の容量及び個数とを異にすることができる。

【0116】本発明の実施例によるデータ階調信号変換 器430では、先に説明した数式9を満たすデジタル回 路を直接製造して使用することができ、ルックアップテ ーブルを作成してROMに保存した後でアクセスして階 調信号を補正することもできる。

【 0 1 1 7 】実際に、補正データ電圧(V , ')は単に以 前のフレームのデータ電圧(V ,, ,)と現在のフレーム 20 のデータ電圧(V<sub>0</sub>)との差だけに比例するのではなく それぞれの絶対値にも依存する複雑な関数であるので、 このようにルックアップテーブルを構成すれば演算処理 に依存するより回路がはるかに簡単になるという長所が

【0118】ここで、図12と図13を参考にした説明 から、本発明は次のような効果が現れる。

【0119】例えば、LCDパネルがSXGA(128 0 × 1 0 2 4 ) 級であり、8 ビットの階調信号が印加さ れる場合について説明する。

【0120】この場合、従来のフレームメモリは最少3 0 M b が必要であり、データ階調信号変換器はコントロ ーラー420から出力する制御信号の一クロック当り2 つの r、g、bピクセルを処理する場合には512Kb ×6個、一クロック当り一つのr、g、bピクセルを処 理する場合には512Kb×3個のメモリが必要にな

【0121】より詳細にいえば、一クロック当り2ピク セルを処理する場合、データ階調信号補正部400は4 8 ビットの入力信号を受けるようになるが、メモリのバ っているので、16ビットワイド(wide)メモリを 3つ使って48ビットバスを構成する。

【0122】しかし、本発明の場合には、nビット階調 信号のうちLSBからi(i=1、2、...、n-1)個 のビットを補正せずに残りの部分のみを階調補正するこ とにより、フレームメモリとデータ階調信号変換器との 容量を減らすことができる。

【0123】例えば、n=8であり、iが2である場 合、MSBs (Most Significant Bi

(15)

28

しなくても済むので、フレームメモリは1280×10 24×3×6ビット(bits)=22.5Mbの容量 だけが必要であり、データ階調信号変換器は8ビット階 調テーブルメモリ(512Kb)の代わりに6ビットを 用いることができるので、24Kb(1ピクセル/クロ ックである場合)、6×24Kb(2ピクセル/クロッ クである場合)のようにサイズが画期的に減るようにな

【0124】一方、本発明の階調信号の補正において補 正ビット数を省略するのは、動画像表現時に人の目は停 10 止画像を見る時ほど敏感ではないためであり、補正ビッ ト数は、動画像表現時に人の目に階調表現が露出されな い範囲以内で省略するのが好ましい。

【0125】そして、r、g、b色に対して人の目はそ の敏感度が異なるので、該当色の階調信号に対して補正 ビット数の省略を異にするのが好ましい。つまり、人の 目はg色に最も敏感であり、b色に最も鈍感であるの で、補正ビット数(i)はg r bの順になるのが好 ましい。

【0126】以上で説明したように、本発明の他の実施 20 例によれば、nビットの階調信号のうちm(m<n)ビ ットのみを用いてデータ電圧を補正し、補正されたデー 夕電圧を画素に印加することにより、画素電圧がすぐ目 標電圧レベルに到達することができるようにする。従っ て、TFT LCDのパネルの構造を変える必要なく液 晶の応答速度を改善させることができる。

【0127】また、本発明の他の実施例によれば、nビ ット階調信号のうちmビットのみを用いることによって データ電圧補正時に必要とするメモリの個数及び容量を\* \*減らすことができるので、パネルの収率を向上させるこ とができ、原価を節減することができる。

【0128】以上で説明したように、液晶の応答速度を 向上させるための画像信号補正回路を図9と図11とに 示した。

【0129】特に、前記画像信号補正回路の原価を節減 するためにLSBの一部を除いて補正する方法を導入し ており、このアルゴリズムは簡単であり適用が容易であ るという長所がある。

【0130】しかし、例えば8ビットグレーを4ビット のみ補正するとすると、量子化による問題が発生し得 る。このような問題は大きく2種類であり、次の通りで

【0131】208(11010000)グレーレベル (G<sub>1</sub>)から192(11000000)グレーレベ ル(G<sub>0</sub>)に変化する時、DCC補正値168(101 0 1 0 0 0 ) グレーレベル ( G<sub>g</sub> ′ ) を与えてはじめて 応答速度が最高価となると仮定する。8ビットを全て補 正する時には何ら問題がないが、原価節減のためにMS B4ビットのみを補正するとすると、まずグレールック アップテーブルの中には168という値は入ることがで きない。従って、これをくり上げて176(10110 000)またはくり下げて160(10100000) を代わりに入力する。つまり、省略するLSBビットの 分の補正誤差が生じるようになる。これは次のような区 間ではさらに問題となり得る。

[0132]

【表1】

| $G_{n-1}$ |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |

|-----------|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|

| $G_n$     |   | 0 | 1 | 3 | 4 | 6 | 8 | 9 | 11 | 12 | 14 | 16 | 17 | 19 | 20 | 22 | 24 | 25 |

|           |   | U | 6 | 2 | 8 | 4 | 0 | 6 | 2  | 8  | 4  | 0  | 6  | 2  | 8  | 4  | 0  | 5  |

| G         | 3 | 3 | 3 | 3 | 3 | 2 | 2 | 2 | 22 | 20 | 16 | 12 | a  | 6  |    | _  |    | _  |

| n         | 2 | 3 | 3 | 2 | 0 | 8 | 6 | 4 | 22 | 20 |    | 12 | 9  | b  | Z  | "  | "  | 0  |

【0133】この区間は補正が少しずつ順次に行われる 部分である。この区間を4ビットのみを使って構成する

[0134] 【表2】

と、下記の表2のように変わる。

| 7 |    |     |   | G <sub>n-1</sub> |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |

|---|----|-----|---|------------------|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|

|   | G, | n ´ | 0 | 1                | 3 | 4 | 6 | 8 | 9 | 11 | 12 | 14 | 16 | 17 | 19 | 20 | 22 | 24 | 25 |

|   |    |     | U | 6                | 2 | 8 | 4 | 0 | 6 | 2  | 8  | 4  | 0  | 6  | 2  | 8  | 4  | 0  | 5  |

|   | G  | 3   | 3 | 3                | 3 | 3 | 3 | 3 | 3 |    | 10 |    | 10 | 10 | _  | _  |    |    |    |

|   | n  | 2   | 2 | 2                | 2 | 2 | 2 | 2 | 2 | 16 | 16 | 16 | 16 | 16 | 0  | 0  | U  | 0  | 0  |

【0135】第2の問題は次の通りである。

【0136】前記の例のように、208グレーレベルか ら192グレーレベルに変化する時に補正値として17 6 グレーレベルを与えると仮定すると、207 グレーレ ベルから192グレーレベルに変化する場合に、最大の 液晶応答速度を出すためにはおそらく176グレーレベ ルまたは175グレーレベル値を与えなければならな L10

【0137】しかしながら、4ビットのみを補正する場 合には207(11001111)のMSB4ビットは50【0139】以上で説明したように、液晶の応答速度を

192(11000000)のMSB4ビットと同一で あるため補正が行われないで192がそのまま出力され

【0138】特に、動画像の場合、208グレーレベル の程度のユニフォームな画面であっても実際には209 と207グレーレベルなどの階調も多く分布するように なり、208と207グレーの階調の差は1に過ぎない が補償される程度は大きな差が出るので、ディスプレー される若干の染みがより誇張されて現れ得る。

向上させるための画像信号補正回路で発生し得る2種類はすべて量子化エラーと言えるが、補正を行わずに省略するLSB数が多くなるほど、量子化エラーはひどくなるという問題点がある。

【 0 1 4 0 】以下、前記量子化エラーの発生を低減する ための液晶表示装置の一例について説明する。

【 0 1 4 1 】図 1 4 は本発明のまた他の実施例によるデータ階調信号補正部を詳細に説明するための図であり、前記図 9 と比較して重なる部分は同一の図面符号を付与し、その説明を省略する。

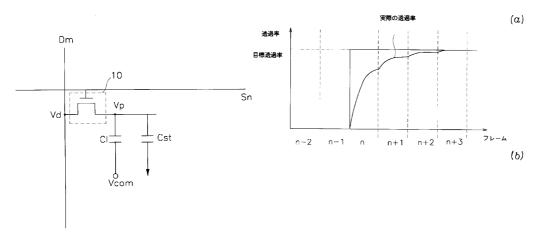

【0142】図14を参照すると、本発明の他の実施例によるデータ階調信号補正部のデータ階調信号変換器460は、ルックアップテーブル462と演算器464とを含む。

【 0 1 4 3 】合成器 4 1 0 から提供される現在のフレームの階調データM S B 4 ビット、 $G_m$  [ 0 : 3 ] と以前のフレームの階調データM S B 4 ビット、 $G_{m-1}$  [ 0 : 3 ] とによってルックアップテーブル(LUT)に保存された値 f、a、b は導出され、演算器 4 6 4 に提供される。

【 0 1 4 4 】演算器 4 6 4 は、合成器 4 1 0 から現在のフレームの階調データ L S B 4 ビット  $G_m$  [ 4 : 7 ] と、フレームメモリ 4 2 0 から以前のフレームの階調データ L S B 4 ビット  $G_{m-1}$  [ 4 : 7 ] との提供を受け、ルックアップテーブルから動画像補正のための変数 f、a、b 各々の提供を受けて、所定の演算を通じて第 1 補正されたグレーデータ  $G_m$   $f_m$  [ 0 : 7 ] を分離器 4 5 0 に出力する。

【 0 1 4 5 】 分離器 4 5 0 に提供された 4 8 ビットの第 1 補正されたグレーデータはデータ分割されて、 2 4 ビ 30 ットの補正されたグレーデータ ( $G_n$ ) をデータドライバー部 3 0 0 に出力する。

【 0 1 4 6 】以上では本発明の実施例について説明したが、本発明は前記実施例にのみ限定されるのではなく、 その他の多様な変更や変形が可能である。

【 0 1 4 7 】例えば、本発明の実施例の図 8 においては デジタル方式で駆動する液晶表示装置を説明したが、そ の他のアナログ方式で駆動する液晶表示装置にも本発明 が適用できることはもちろんである。

【0148】以下、前記本発明の他の実施例によって低40減される量子化エラーの低減の効果をより詳細に説明する。

\*ットは演算によって補正する。

(16)

【 0 1 5 0 】以下、x = 8、y = 4 である時の例を挙げて説明し、説明の便宜のために次を定義する。

【 0 1 5 1 】 [ A ]  $_{n}$ はAを越えない最も大きい 2  $^{n}$ の倍数である。例えば、 [ 2 0 7 ]  $_{4}$  = [ 2 0 6 ]  $_{4}$  = [ 2 0 6 ]  $_{4}$  = [ 2 0 6 ]  $_{4}$  = 1 9 2  $_{4}$  = 1 9 2  $_{4}$  = 1 9 2  $_{6}$  とおりである。

$_{m}$  [ A ]  $_{n}$  は A の M S B m ビット、 L S B n ビットを全て 0 で満たした値である。補正用グレールックアップテーブルによるマッピングを f (  $G_{n}$ 、  $G_{n-1}$  ) とすると、本 発明における補正は下記する数式 1 0 のとおりである。

#### [0153]

【数 1 0 】  $G_n' = f([G_n]_4; [G_{n-1}]_4) + a([G_n]_4; [G_{n-1}]_4) \times \frac{4[G_n]}{16} - b([G_n]_4; [G_{n-1}]_4) \times \frac{4[G_n]}{16}$

【 0 1 5 4 】ここで、  $[G_n]_4$ は $G_n$ の L S B 4 ビット 20 を全て 0 で満たした値、  $[G_{n-1}]_4$ は $G_{n-1}$ の L S B 4 ビットを全て 0 で満たした値、  $_4$   $[G_n]$  は $G_n$ の M S B 4 ビットを全て 0 で満たした値、 a と b は全て正の整数 である。

【 0 1 5 5 】前記数式 1 0 によれば、グレールックアップテーブルによるマッピング、つまり [ f ( [  $G_n$  ]  $_4$  、 [  $G_{n-1}$  ]  $_4$  )] とともに第 2 項 ( a ( [  $G_n$  ]  $_4$  [  $G_{n-1}$  ]  $_4$  )× $_4$  [  $G_n$  ] / 1 6 )と第 3 項 ( - b ( [  $G_n$  ]  $_4$  [  $G_{n-1}$  ]  $_4$  )× $_4$  [  $G_n$  ] / 1 6 )との演算を通じて量子化エラー ( Q u a n t i z a t i o n e r r o r ) を減らすことができる。

【 0 1 5 6 】前記数式 1 0 において f 、 a 、 b は基本的 に次のように与えられる。

【0157】つまり、 $f([G_n]_4, [G_{n-1}]_4) = G_n$ 、 $([G_n]_4, [G_{n-1}]_4)$ であり、 $a([G_n]_4, [G_{n-1}]_4)$  =  $G_n$  、 $([G_n]_4 + 16, [G_{n-1}]_4)$  -  $G_n$  、 $([G_n]_4, [G_{n-1}]_4)$  であり、 $b([G_n]_4, [G_{n-1}]_4) = G_n$  、 $([G_n]_4, [G_n]_4, [G_n]_4) = G_n$  、 $([G_n]_4, [G_n]_4, [G_n]_4) = G_n$  、 $([G_n]_4, [G_n]_4, [G_n]_4) = G_n$

【 0 1 5 8 】従って、 f 、 a 、 b の値はこの関係を基本として設定される。実測を通じて下記する表 3 のような補正用グレールックアップテーブルが得られたと仮定してみよう。

[0159]

【表3】

【0160】例えば、[Gn]4=128、[Gn-1]4= a([Gn]4、[Gn-1]4)=160-140=20、64とすれば、f([Gn]4、[Gn-1]4)=140-136=4とな

る。しかしながら、この値は絶対的なものではなく、この  $1.6 \times 1.6$  区間の値が最も誤差の少ない値になるように決められる。

31

【 0 1 6 1 】 例えば、前記値が $G_n$  = 1 4 4 、  $G_{n-1}$  = 8 0 である場合を数式 1 0 によって近似するとすれば、 $G_n$  f = 1 f 4 f 9 + 2 f 8 + 1 f 7 f 6 - 4 \* 1 f 7 f 7 f 8 とは差が出るようになる。この程度の誤差は無視しても差支えないが、もしもこの差が大きくなれば、f 7 f 8 f 8 f 8 f 8 f 8 f 8 f 8 f 8 f 8 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9 f 9

【 0 1 6 2 】反面、例外的に気を使うべき部分は  $[G_n]_4 = [G_n]_4$ のブロックである。この場合は $G_n$   $' = G_n$ が絶対に守られなければならないため  $f = [G_n]_4$ に固定され、a と b との値をそれに合わせて調節しなければならない。前記数式 1 0 において  $G_n = G_n$  であれば、a - b = 1 6 になってはじめて  $G_n$   $' = G_n$  の条件が満たされる。

【0163】それでは一つの例を挙げて前記数式10によって演算される補正されたグレーデータを説明する。 【0164】例えば、以前の階調データ(G<sub>n-1</sub>)が72階調レベルであり、現在の階調データ(G<sub>n</sub>)が136階調レベルである場合、前記表3の補正用グレールックアップテーブルには各々の階調データが存在しないため、これを所定の演算を通じて図12aに示したように導かなければならない。

【0165】つまり、 $f([G_n]_4, [G_{n-1}]_4) = f([136]_4, [72]_4)$ であるのでf(128, 64) = 140であり、 $a([G_n]_4, [G_{n-1}]_4) = 160 - 140 = 20$ であり、 $b([G_n]_4, [G_{n-1}]_4) = 140 - 136 = 4$ である。

【 0 1 6 7 】また、ルックアップテーブルに保存される ビット数を減らすための他の方法としては、下記の数式 1 1 を用いてブレークダウン(break down) することができる。

[0168]

$\begin{array}{c} \{\{X,Y,Y,Y\}\} \\ G_n' = f' + [G_n]_4 + a([G_n]_4 [G_{n-1}]_4) \times \frac{4[G_n]}{16} - b([G_n]_4 [G_{n-1}]_4) \times \frac{4[G_n]}{16} \end{array}$

【0170】それでは、前記数式11によって演算される補正されたグレーデータを一例を挙げて説明する。

【0171】例えば、以前の階調データ(G,)が72階調レベルであり、現在の階調データ(G,)が136階調レベルである場合、前記表3の補正用グレールックアップテーブルには各々の階調データが存在しないので、これを所定の演算を通じて図12cに示したように導かなければならない。

【0172】つまり、f´=f([G<sub>n</sub>]<sub>4</sub>、[7 [G<sub>n-1</sub>]<sub>4</sub>)-[G<sub>n</sub>]<sub>4</sub>=f([136]<sub>4</sub>、[7 2]<sub>4</sub>)-128=f(128、64)-128=14 0-128=12であり、a"([G<sub>n</sub>]<sub>4</sub>、 [G<sub>n-1</sub>]<sub>4</sub>)=a´([G<sub>n</sub>]<sub>4</sub>、[G<sub>n-1</sub>]<sub>4</sub>)+2<sup>4</sup>= 4+16=20、b([G<sub>n</sub>]<sub>4</sub>、[G<sub>n-1</sub>]<sub>4</sub>)=4であ

【 0 1 7 3 】したがって、前記数式 1 1 にこれを代入すると、 G <sub>n</sub> ′ = 1 2 8 + 1 2 + 2 0 \* (136 - 128) / 16 - 4 \* (72 - 64) / 16 = 148である。

【 0 1 7 4 】一方、前記図 1 0 に示したルックアップテーブルに保存されるビット数を減らすための一つの方法 20 として、下記の数式 1 2 を用いてブレークダウン(break down) することができる。

[0175]

【数12】

$$G_n' = f' + G_n + a([G_n]_4 [G_{n-1}]_4) \times \frac{4[G_n]}{16} - b([G_n]_4 [G_{n-1}]_4) \times \frac{4[G_n]}{16}$$

【 0 1 7 7 】つまり、 a ´ ( [ G n ] 4、 [ G n - 1 ] 4) = a ( [ G n ] 4、 [ G n - 1 ] 4) - 2 ⁴である。

【0178】それでは、前記数式12によって演算される補正されたグレーデータを一例を挙げてより詳細に説明する。

【 0 1 7 9 】例えば、以前の階調データ( G , , , ) が 7 2 階調レベルであり、現在の階調データ( G , ) が 1 3 6 階調レベルである場合、前記表 3 の補正用グレールックアップテーブルには各々の階調データが存在しないの で、これを所定の演算を通じて図 1 5 b に示したように 導かなければならない。

【0180】つまり、 $f([G_n]_4, [G_{n-1}]_4) = f([136]_4, [72]_4) = f(128, 64) = 140$ であるので、 $f'=f([G_n]_4, [G_{n-1}]_4) - G_n = 140 - 128 = 12, G_n = 136, a'([G_n]_4, [G_{n-1}]_4) = a' - 16 = 4, b([G_n]_4, [G_{n-1}]_4) = 4$ である。

\*-タ全部を保存しない場合もあり得る。

【0185】例えば、DRAMの次元(dimensi

on)は4、8、16、32などのようになっており、

r、g、bそれぞれの24ビットの色情報を保存するた

めには32を使用しなければならないが、原価負担のた めに32を適用することができない場合もある。従っ

て、32の代りに16を用いてr5ビット、g6ビッ

ト、b5ビットのみを保存することもできる。この場合

【0182】この場合はa´の値も小さくなるので(-16) a ´に割り当てるビット数を減らすことができる という利点があるが、区間によってa´が負の数になら なければならない場合が生じるため、サインビット(s ign bit)をもう一つ割り当てなければならな l1.

【0183】以上で説明したように、補正階調データ用 ルックアップテーブルの大きさは数式10、11、12 の順序で小さくなり、ロジックの複雑性はこれと反対に 増加する。

【0184】以上では8ビット全てを補正することをそ の例として説明した。しかし、フレームメモリの大きさ をさらに減らさなければならない場合や、i/Oピンの

数を減らさなければならないなどの理由で8ビットのデ\*

の変更は次のように行われる。 10 【 0 1 8 6 】 つまり、 6 ビットの場合は下記の数式 1 3 のように補正グレー値を出力する。 [0187]

【数13】

$$G_n' = f([G_n]_4, [G_{n-1}]_4) + a([G_n]_4, [G_{n-1}]_4) \times \frac{4[G_n]}{16} - b([G_n]_4, [G_{n-1}]_4) \times \frac{4[G_n] >> 2}{4}$$

\*しては22で割った効果を有する。

【0189】また、5ビットの場合には下記の数式14 のように補正グレー値を出力する。

\*くなって高速演算が難しくなる場合には、現在のフレー

ムの階調データ ( G ¸ ) さえもLSBいくつかを省略し

て補正する方法を取ることもできる。 G を 6 ビット、

G 1 を 6 ビットのみ補正する場合の変換は下記の数式

[0190]

【数14】

フトさせる機能を行い、結果と\*

$$G_n'=f([G_n]_4:[G_{n-1}]_4)+a([G_n]_4:[G_{n-1}]_4)\times\frac{4[G_n]}{16}-b([G_n]_4:[G_{n-1}]_4)\times\frac{4[G_n]>>3}{2}$$

【0188】ここで、[G<sub>2</sub>] はG<sub>2</sub>のLSB4ビット を全て0で満たした値、[G<sub>0.1</sub>]<sub>4</sub>はG<sub>0.1</sub>のLSB4 ビットを全て0で満たした値、<sub>4</sub> [G<sub>n</sub>]はGnのMSB 4ビットを全て0で満たした値、aとbは全て正の整数 20 であり、<sub>4</sub> [ G o ] >> 2 は 4 [ G o ] を演算したバイナリデ ータを2ビット右側にシフトさせる機能を行い、結果と\*

【 0 1 9 1 】 ここで、 [ G 。 ] ₄は G 。の L S B 4 ビット を全て0で満たした値、[G<sub>0.1</sub>]<sub>4</sub>はG<sub>0.1</sub>のLSB4 ビットを全て0で満たした値、<sub>4</sub>[G<sub>0.1</sub>]はG<sub>0.1</sub>のM SB4ビットを全て0で満たした値、aとbは全て正の 整数であり、<sub>4</sub> [ G<sub>n-1</sub> ] >> 3 は<sub>4</sub> [ G<sub>n-1</sub> ] を演算したバ イナリデータを3ビット右側にシフトさせる機能を行 い、結果としては2°で割った効果を有する。

【0192】また、解像度によってピクセル周波数が高\*

像度によってピクセル制波数が高\*

$$G_n'=f([G_n]_4[G_{n-1}]_4)+a([G_n]_4[G_{n-1}]_4)\times \frac{_4[G_n]>>2}{_4}-b([G_n]_4[G_{n-1}]_4)\times \frac{_4[G_n]>>2}{_4}$$

30 [0193] 【数15】

【0194】以上で説明したように、一般に、pビット のグレールックアップテーブルを用いて、 q ビットの G 。、rビットのG。」のみを補正する場合には、下記の数 式 1 6 で整理することができる(q、r>p)

甫正する場合には、下記の数 【 0 1 9 5 】

$$G_n'=f([G_n]_{8-p'}[G_{n-1}]_{8-p})+a([G_n]_{8-p}[G_{n-1}]_{8-p})\cdot \frac{{}_p[G_n]_{8-q}>>(8-q)}{2^{(q-p)}}$$

15のとおりである。

$$-b([G_n]_{8-p}[G_{n-1}]_{8-p})\cdot \frac{{}_p[G_{n-1}]_{8-r}>> (8-r)}{2^{(r-p)}}$$

【0196】本発明による動画像補正機能を有する液晶 表示装置の動作を簡略に説明すると次の通りである。

【0197】前記のように、本発明では動画像具現時の 引きずられ現象を除去するために、一つのフレームの画 像信号(G<sub>0</sub>)をそれ以前のフレームの画像信号 (G<sub>0.1</sub>)と下記の数式17乃至20に基づいて比較し て補正する。

[0198]

【数17】

$G_n = G_n$ , if  $G_n = G_{n-1}$

[0199]

【数18】

$$G_n > G_n$$

、 if  $G_n > G_{n-1}$

[0200]

【数19】

$$G_n < G_n$$

、 if  $G_n < G_{n-1}$

[0201]

50 【数20】

$$G_n - G_n \propto \frac{35}{G_n - G_{n-1}}$$

【0202】つまり、現在のフレームで印加される画像 信号がそれ以前のフレームの画像信号と変わらなければ 数式17のように補正を行わず、現在の階調(または階 調電圧)が以前の階調(または階調電圧)より高くなれ ば補正回路は数式18のように現在の階調(または階調 電圧)をさらに高くして出力し、現在の階調(または階 調電圧)が以前の階調(または階調電圧)より低くなれ ば補正回路は数式19のように階調(または階調電圧) をさらに低くして出力する。この時の補正が行われる程 10 り短い時間に2 Vに該当する透過率に到達するようにな 度は、数式20のように現在の階調(または階調電圧) と以前の階調 (または階調電圧)との差に比例する関数

【0203】このような補正過程を通じてLCDパネル の応答速度は速くなるが、これは次の原理に基づく。 【0204】まず、窮極的に意図した電圧が加えられる ようにする。つまり、液晶セルに5 V を加えようと意図 したとするなら実際にも5 V が加えられるようにする。 液晶が電気場に反応して液晶の方向子の方向が変わると 液晶のキャパシタンスも変わるので、実際にはじめに加 20 えられた電圧とは違う電圧が液晶に加えられるようにな

【0205】つまり、液晶物質自体の応答速度が1フレ -ム(16.7ms、@60Hz)以内に入るとしても、 現在のAMLCD駆動方式では前記メカニズムによる正 確な電圧が加えられずにその以前電圧との間の値が加え られるようになるので、LCDパネルにおける実際の応 答速度は1フレームよりはるかに遅くなる。

【0206】ここで信号補正を通じて意図していた電圧 が実際にも加えられるようにして正確な応答が行われる 30 によって画素電圧をすぐに目標電圧レベルに到達するよ ようにする。この時、過度補償(overcompen sate)して液晶が応答する時間の間の透過率誤差を 補償することもできる。

【0207】次に、ほとんどの液晶物質は電圧の変化が 大きいほど応答速度自体もまた速くなる。例えば、ライ ジング(rising)の場合、1Vから2Vに変わる 時より1Vから3Vに変わる時の応答速度が一般により 速く、フォーリング(falling)の場合、3Vか ら2 Vに変わる時より3 Vから1 Vに変わる時の応答速 度がより速い。

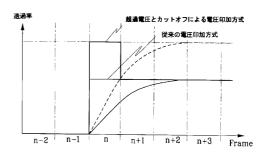

【0208】このような傾向は液晶物質によって、また はLCDの動作モードによって多少差があるが、大体は 守られている。例えば、ツイストネマチックモード(T wisted Nematic mode) の場合、ライ ジングは電圧の差が大きくなるのに伴って最高15倍ま で応答速度が速くなり、フォーリングは最高1.5倍ま で速くなる。

【0209】その次に、液晶物質自体の応答時間が1フ レーム (16.7 m s) を越える場合には、強制牽引方 式によって1フレームに応答時間を短くすることができ\*50 た場合の液晶表示装置の透過率を示す図である。

\*る。1 Vから2 Vに変わるまでの応答時間が30 msで ある液晶があると仮定しよう。言い換えれば、2 V に該

36

当する透過率を得るために2Vを加えると30msが所 要される。 【0210】同一な液晶が1Vから3Vまで到達するの

にかかる時間も30msであるとすれば(殆どの場合は これよりは短い)、2Vに該当する透過率は図16に示 したように30ms以前に到達する。つまり、2Vに該 当する透過率を得るために3 Vを加えると、30 m s よ

【0211】もちろん、続けて3Vを加えれば液晶は窮 極的に3 Vの水準に到達するので、2 Vの水準に到達し た時にこの超過電圧をカット - オフ(cut-off) し、2 Vをかければ液晶は2 Vの水準に30msより短 い時間に到達することができる。カット - オフ( c u t - o f f ) をする時点、つまり、電圧を変えて加えるこ とができる時点はフレームが変わる時である。したがっ て、液晶が1フレーム(16.7ms)後に2Vの水準 に到達する電圧、例えば、3 Vを加えた後にその次のフ レームで元来の2Vに逆戻りをすれば応答時間は16. 7 m s に短くなるわけである。この場合にも過度補償 (overcompensation)方式を導入して 液晶の応答時間(例えば、16.7ms)の間の透過率 誤差部分を相殺することができる。

### [0212]

【発明の効果】以上で説明したように、本発明のまた他 の実施例によれば、液晶表示装置において、データ電圧 を補正し、補正されたデータ電圧を画素に印加すること うにすることができる。従って、TFT LCDのパネ ル構造を変更する必要なく液晶の応答速度を改善させる ことができる。

【0213】また、液晶表示装置の駆動時、特に動画像 具現時に液晶の応答速度を向上させるための画像信号補 正回路において、グレールックアップテーブルの大きさ は減らして量子化エラーを除去することができる。

### 【図面の簡単な説明】

【図1】液晶表示装置における各画素の等価回路を示す 40 図である。

【図2】従来の駆動方式で印加されるデータ電圧及び画 素電圧を示す図である。

【図3】従来の駆動方式による液晶表示装置の透過率を 示す図である。

【図4】液晶表示装置の電圧 - 誘電率の間の関係をモデ リングした図である。

【図5】本発明の一実施例によるデータ電圧の印加方法 を示す図である。

【図6】本発明の一実施例によってデータ電圧を印加し

【図7】本発明の他の実施例によってデータ電圧を印加 した場合の液晶表示装置の透過率を示す図である。

37

【図8】本発明による液晶表示装置を示す図である。

【図9】本発明の一実施例によるデータ階調信号補正部 を示す図である。

【図10】本発明の一実施例によるルックアップテーブ ルを示す図である。

【図11】本発明の他の実施例によるデータ電圧補正部 を示す図である。

【図12】前記図11の第1実施例によるデータ電圧補10300 データドライバー 正部の動作を概念的に説明した図である。

【図13】前記図11の第2実施例によるデータ電圧補 正部の動作を概念的に説明した図である。

【図14】本発明のまた他の実施例によるデータ階調信 号補正部を詳細に説明するための図である。

【図15】(a)本発明のまた他の実施例によって演算 される補正されたグレーデータの変換を説明するための 図である。

(b) 本発明のまた他の実施例によって演算される補正\*

\*されたグレーデータの変換を説明するための図である。 (c) 本発明のまた他の実施例によって演算される補正 されたグレーデータの変換を説明するための図である。

【図16】従来の電圧印加方式と本発明による電圧印加 方式とを比較した波形図である。

### 【符号の説明】

100 液晶表示装置パネル

110 薄膜トランジスタ

200 ゲートドライバー

400 データ階調信号補正部

4 1 0 合成器

420、460 フレームメモリ

430、470 コントローラー

440、480 データ階調信号変換器

450 分離器

462 ルックアップテーブル

464 演算器

| Gr |     | G           | n-l       |

|----|-----|-------------|-----------|

| Gr | 1   | 64          | 80        |

|    | 128 | 140<br>a=20 | 136<br>=4 |

| Gn | 144 | 160         | 158       |

| G   |     | G             | n-1 |  |  |  |

|-----|-----|---------------|-----|--|--|--|

| UI. | 1   | 64            | 80  |  |  |  |

|     |     | 140           | 136 |  |  |  |

| _   | 128 | b=4<br>12 → 8 |     |  |  |  |

| Gn  |     | 160           | 158 |  |  |  |

|     | 144 | a=20<br>32    | 30  |  |  |  |

(c)

| ľ | 図 | 2 | 1 |

|---|---|---|---|

$G_{n-1}$ 64 140 136 128 b=4 12 160 | 158 a # 4 144 16

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

|      |                |             | Gn     |             |   |       |             |     |     |  |  |  |  |

|------|----------------|-------------|--------|-------------|---|-------|-------------|-----|-----|--|--|--|--|

| Gr   | ) <sup>'</sup> | 0           | 1      | 2           | 2 | • • • | 253         | 254 | 255 |  |  |  |  |

|      | 0              | 0           | 1      | 3           | 5 |       | 255         | 255 | 255 |  |  |  |  |

|      | 1              | 0           | 1      | 3           | 4 |       | 255         | 255 | 255 |  |  |  |  |

|      | 2              | 0           | 1      | 2           | 3 | • • • | 255         | 255 | 255 |  |  |  |  |

|      | 3              | 0           | 0      | 2           | 3 |       | 255         | 255 | 255 |  |  |  |  |

| Gn-1 | 0              | 6<br>0<br>0 | o<br>o | a<br>a<br>o | 0 | •     | 0<br>a<br>b | •   |     |  |  |  |  |

|      | 253            | 0           | 0      | 0           | 0 | • • • | 253         | 254 | 255 |  |  |  |  |

|      | 254            | 0           | 0      | 0           | 0 | • • • | 253         | 254 | 255 |  |  |  |  |

|      | 255            | 0           | 0      | 0           | 0 |       | 252         | 253 | 255 |  |  |  |  |

【図12】

【図13】

【図16】

【図14】

| 专利名称(译)        | 液晶显示装置及其驱动方法和装置                                                                                                                                                                                                                                                                                                                                                                         |         |                              |  |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------|--|--|--|--|--|

| 公开(公告)号        | JP2001265298A                                                                                                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2001-09-28                   |  |  |  |  |  |

| 申请号            | JP2001028541                                                                                                                                                                                                                                                                                                                                                                            | 申请日     | 2001-02-05                   |  |  |  |  |  |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                |         |                              |  |  |  |  |  |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                |         |                              |  |  |  |  |  |

| [标]发明人         | 李白雲                                                                                                                                                                                                                                                                                                                                                                                     |         |                              |  |  |  |  |  |

| 发明人            | 李白雲                                                                                                                                                                                                                                                                                                                                                                                     |         |                              |  |  |  |  |  |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36 G09G5/39                                                                                                                                                                                                                                                                                                                                                    |         |                              |  |  |  |  |  |

| CPC分类号         | G09G3/2011 G09G3/3648 G09G5/39 G09G2320/02 G09G2320/0252 G09G2340/16                                                                                                                                                                                                                                                                                                                    |         |                              |  |  |  |  |  |

| FI分类号          | G09G3/36 G02F1/133.575 G09G3/<br>G09G3/20.650.M G09G3/20.660.V                                                                                                                                                                                                                                                                                                                          |         | 09G3/20.641.P G09G3/20.641.R |  |  |  |  |  |

| F-TERM分类号      | 2H093/NA55 2H093/NC16 2H093/NC29 2H093/NC34 2H093/NC49 2H093/NC66 2H093/ND06 2H093 /ND34 2H093/ND58 2H093/NH18 2H193/ZA04 2H193/ZD25 2H193/ZE01 2H193/ZH40 2H193/ZH43 5C006/AC11 5C006/AC21 5C006/AF11 5C006/AF46 5C006/BB16 5C006/BC16 5C006/BF02 5C006 /FA14 5C006/GA02 5C080/AA10 5C080/BB05 5C080/DD01 5C080/DD08 5C080/EE19 5C080/EE29 5C080/FF11 5C080/GG12 5C080/JJ02 5C080/JJ05 |         |                              |  |  |  |  |  |

| 优先权            | 1020000005442 2000-02-03 KR<br>1020000043509 2000-07-27 KR<br>1020000073672 2000-12-06 KR                                                                                                                                                                                                                                                                                               |         |                              |  |  |  |  |  |

| 其他公开文献         | JP5095889B2                                                                                                                                                                                                                                                                                                                                                                             |         |                              |  |  |  |  |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                                                               |         |                              |  |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                         |         |                              |  |  |  |  |  |

# 摘要(译)

解决的问题:提供一种通过改变液晶的驱动方法而不改变TFT LCD的面板结构来提高液晶的响应速度的液晶显示装置。 本发明的液晶显示装置通过同时考虑当前帧的数据电压和前一帧的数据电压来生成校正数据电压,然后将所生成的校正数据电压施加至数据线。 要做。 通过将校正数据电压施加到数据线,像素电压可以立即达到目标电平。