(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4805587号

(P4805587)

(45) 発行日 平成23年11月2日(2011.11.2)

(24) 登録日 平成23年8月19日(2011.8.19)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

G02F 1/1368

G02F 1/1343 (2006.01)

G02F 1/1343

請求項の数 5 (全 12 頁)

(21) 出願番号 特願2005-48251 (P2005-48251)

(22) 出願日 平成17年2月24日 (2005.2.24)

(65) 公開番号 特開2006-235134 (P2006-235134A)

(43) 公開日 平成18年9月7日 (2006.9.7)

審査請求日 平成19年8月20日 (2007.8.20)

(73) 特許権者 504011210

エーユー オプトロニクス コーポレイシ

ョン

AU Opttronics Corp.

台湾 シンチュー, サイエンス-ペイスト

インダストリアル パーク, リーシン

ロード 2, ナンバー 1

(74) 代理人 100087398

弁理士 水野 勝文

(74) 代理人 100067541

弁理士 岸田 正行

(74) 代理人 100103506

弁理士 高野 弘晋

最終頁に続く

(54) 【発明の名称】 液晶表示装置とその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、ドレイン配線に接続された絵素電極を有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、少なくとも、

第1の透明性絶縁基板の一主面上に走査線と、絶縁ゲート型トランジスタと、信号線が形成され、その上に感光性有機絶縁層であるパシベーション絶縁層が形成され、

前記感光性有機絶縁層には、前記ドレイン配線及び走査線の端子部までに達する開口部が形成されるとともに、絵素電極同士と電極端子同士を分離する部分である走査線 信号線交差部、TFT部、及び走査線端子部の両側に該当する領域に前記感光性有機絶縁層の底まで届かない幅の細い溝が一つの単位絵素において複数本並列して形成され、

前記感光性有機絶縁層上に絵素電極となる導電膜が被着されていることを特徴とする液晶表示装置。

## 【請求項 2】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、ドレイン配線に接続された絵素電極を有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に

10

20

液晶を充填してなる液晶表示装置の作製に当たりコンタクトホール形成工程で、少なくとも、

第1の透明性絶縁基板の一主面上に走査線と、絶縁ゲート型トランジスタと、信号線を形成し、

その上に感光性有機絶縁膜を塗布して表面が平坦な電気絶縁膜を形成し、

コンタクト形成領域を白、絵素電極形成領域を黒、絵素電極の周囲は光源からの照射光を位相シフトさせて通過させる中間調領域とする位相シフトフォトマスクを用いて、前記感光性有機絶縁膜を露光・現像し、

前記感光性有機絶縁膜には、前記ドレイン配線及び走査線の端子部までに達する開口部を形成するとともに、絵素電極同士と電極端子同士を分離する部分である走査線 信号線交差部、TFT部、及び走査線端子部の両側に該当する領域に前記感光性有機絶縁層の底まで届かない幅の細い溝を一つの単位絵素において複数本並列して形成し、

前記感光性有機絶縁層上に絵素電極となる導電膜を被着することを特徴とする液晶表示装置の製造方法。

#### 【請求項3】

絵素電極用導電膜としてITOまたはIZOあるいはこれらの混晶をスパッタで形成することを特徴とする請求項2に記載の液晶表示装置の製造方法。

#### 【請求項4】

絵素電極用導電膜としてITO、IZO、IN<sub>2</sub>O<sub>3</sub>、ZnO等の透明導電性粉体を少なくとも一つ以上分散させた塗布膜を用いて、加熱処理により安定化させることを特徴とする請求項2に記載の液晶表示装置の製造方法。

#### 【請求項5】

絵素電極用導電膜としてAL及びAL合金、または銀及び銀合金等の高反射率金属をスパッタで形成することを特徴とする請求項2に記載の液晶表示装置の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は液晶表示装置等の平面型表示装置に用いられるTFTアレイ基板及びその製造方法に関する。

##### 【背景技術】

##### 【0002】

近年、CRTディスプレイに代わる平面型表示装置が盛んに商品開発されており、中でも液晶表示装置は、モバイル用小型ディスプレイ用途から大型テレビディスプレイ用途まで幅広く普及している。

##### 【0003】

液晶表示装置は一对の2枚の基板間に液晶を挟持してなる電気光学装置で、表示性能の優れたアクティブ型の液晶表示装置ではガラス基板等の透明絶縁基板の一主面上に複数本の信号線と走査線を格子状に形成し、信号線と走査線の交差点毎にアモルファスシリコン等の半導体薄膜を用いた薄膜トランジスタ（以下、TFTと略す）をスイッチング素子として設けたアレイ基板が広く使用されている。TFTアレイ基板を作成するためには半導体集積回路のようにフォトマスクを用いた複数回のフォトリソグラフィィ工程が不可欠であり、このフォトリソグラフィィ工程を含めて製造工程数を削減する事が液晶表示装置の生産性向上とコストダウンに大きく寄与することは自明である。

##### 【0004】

現在、アクティブマトリックス型アモルファスシリコンTFTアレイ基板の作製において、5回あるいは4回のフォトリソグラフィ工程を経るプロセスが一般的であり、以下に「特開2002-206571号公報」で開示されている特許公報及び「SID2000、Digest、1016ページ～1009ページA NOVEL FOUR MASK COUNT PROCESS ARCHITECTURE FOR TFT-LCD'S」で報告されているハーフトーンフォトプロセス技術を用いた4枚マスクプロセスを公知の從

10

20

30

40

50

来例として紹介する。これは下記に説明するようにハーフトーン露光技術を用いてチャネルを含む半導体層の島化工程とソース・ドレイン配線工程を1枚のフォトマスクで形成する合理化技術である。

【特許文献1】特開2002-206571号公報

【非特許文献1】SID2000, Digest of Technical Papers

### 【0005】

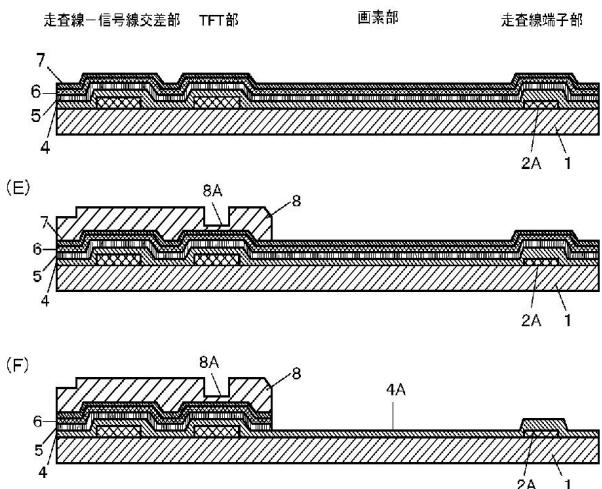

特許文献1を説明するに当たり、図1～図5を参照して走査線と信号線が交差する走査線信号線交差部、スイッチング素子としてのTFT部、絵素部(画素部)及び走査線周辺回路に配置される電極端子部を並べた断面部分を製造工程の進捗に対応して模式的に示す。

10

### 【0006】

先ず、図1(A)に示すようにガラス基板1の一主面上にスパッタリング装置等の製膜装置を用いて、例えばクロム、モリブデン、タンタル、アルミニウム、銅あるいはそれらの合金もしくは積層を第1の金属膜2として被着する。次に第1の金属膜2の膜面上にフォトレジストを塗布し、1枚目のフォトマスクを使用して、図1(B)に示すレジストパターン3を選択的に形成する。その後、レジストパターン3をマスクとして第1の金属膜2のエッチングを行い、レジストを除去して図1(C)に示すような走査線も兼ねるゲート電極膜2Aを形成する。ゲート電極膜2Aの膜厚は通常、0.1～0.3μmの範囲で設定される。

### 【0007】

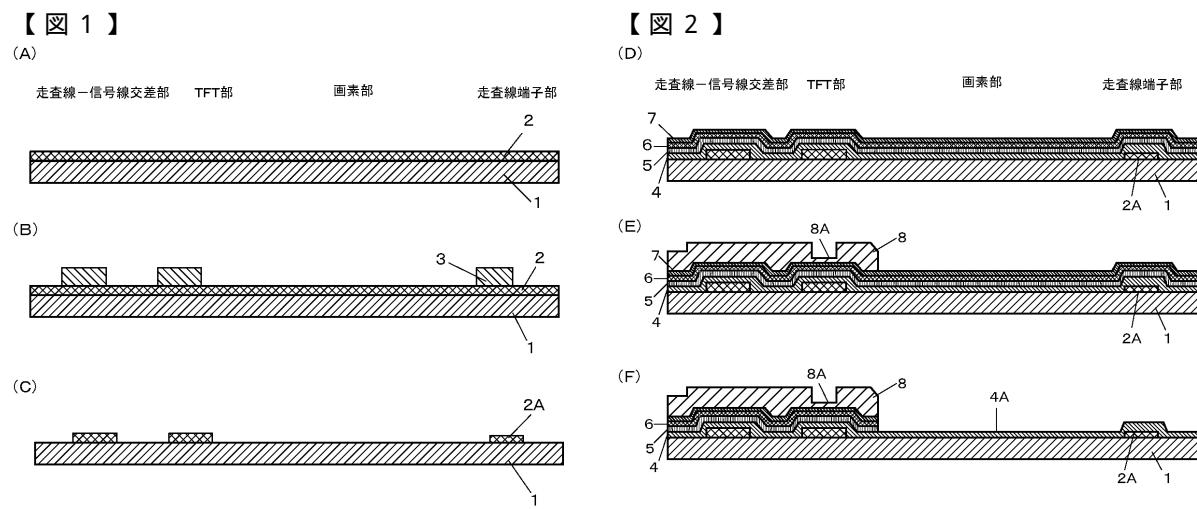

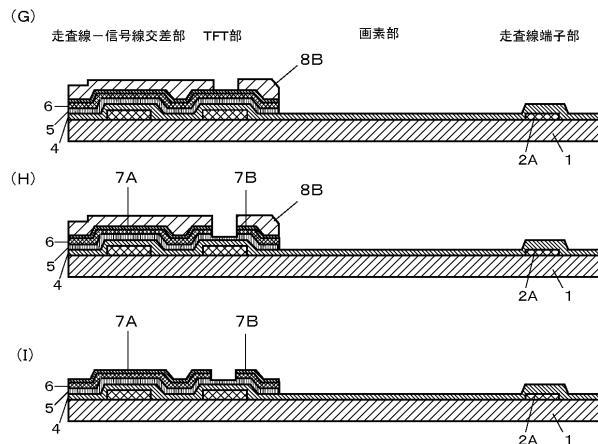

次にプラズマCVD装置やスパッタリング装置等の製膜装置を用いて、図2(D)に示すようにゲート絶縁層としての第1のシリコン窒化膜4、トランジスタのチャネルとして不純物を殆ど含まない第1の非晶質シリコン膜(a-Si)5及びトランジスタのソース・ドレインとしてN型不純物をドープした第2の非晶質シリコン膜(N+a-Si)6と3種類の薄膜を、例えば0.3-0.2-0.05μmの膜厚で被着する。さらにスパッタリング装置等を用いて、例えばクロム、モリブデン、アルミニウム、銅あるいはそれらの合金や積層を第2の金属膜7として被着する。ここでも膜厚は0.3μm程度が一般的である。その後、スリットパターン、ドットパターン等により透過する露光エネルギーを調整した2枚目のフォトマスクあるいは、半透過膜により透過する露光エネルギーを調整した2枚目のフォトマスクを使用し、未露光部分、完全露光部分及びハーフトーン露光部分を形成し、図2(E)に示すように領域によって膜厚が異なるレジストパターン8を作成する。同図において8Aはハーフトーン露光によりパターニングされたチャネル部分を示し、この領域は他のソース・ドレイン配線に対応した領域よりも膜厚が薄いことが特徴である。次に図2(F)に示すように、レジストパターン8をマスクとして第2の金属膜7及び第2のシリコン層6と第1のシリコン層5のエッチングを行ってソース・ドレイン配線を形成し、ゲート絶縁層4Aを露出する。続いて、図3(G)に示すように酸素プラズマ等のアッシング手段によりチャネル部分8Aのレジスト除去を行い、信号線層7を露出する。そして図3(H)に示すように、膜厚が減少したレジストパターン8Bをマスクとして再び、信号線層7、第2のシリコン層6及び第1のシリコン層5をエッチングし、第1のシリコン層5は0.05～0.10μm程度残すことでソース・ドレイン配線間の第2のシリコン膜を除去する。すなわち、TFTのチャネルとなる不純物を殆ど含まない第1のシリコン膜の選択的形成も行うとともにソース・ドレイン配線(SD配線)7A,7Bの分離を行う。その後、図3(I)に示すようにレジストパターン8Bの除去を行う。

20

30

40

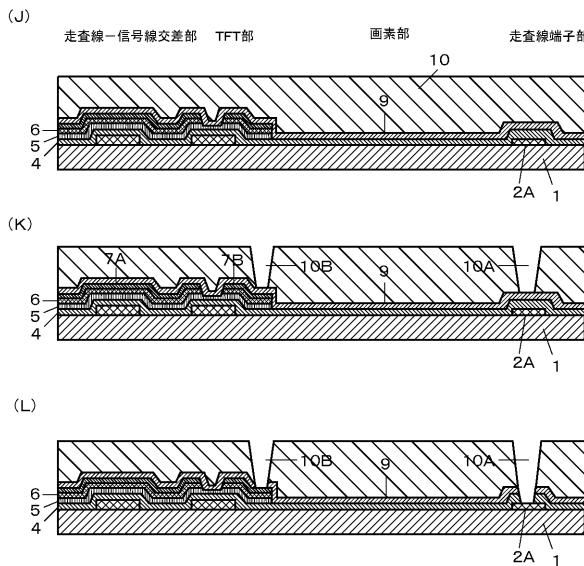

### 【0008】

続いて図4(J)に示すように、例えば0.3μm程度の膜厚を有する第2のシリコン窒化膜等の保護膜またはパシベーション絶縁層9をスパッタリング法、あるいはCVD法により被着し、さらにアレイ基板1の表面を平坦にするための平坦化膜として感光性アクリル樹脂膜10の塗布を行う。通常、平坦化膜としては3μm以上厚く塗布している。その後、図4(K)に示すように4枚目のフォトマスクを使用して、第1の金属膜2A、第2の金属膜7Bに到達するためのコンタクトホール10A、10Bを作成する。そして図4

50

(L)に示すようにコンタクトホール部分10A、10B内の絶縁膜である第2のシリコン窒化膜9と第1シリコン窒化膜4のエッチングを行い、第1の金属膜2Aと第2の金属膜7Bを部分的に露出させる。

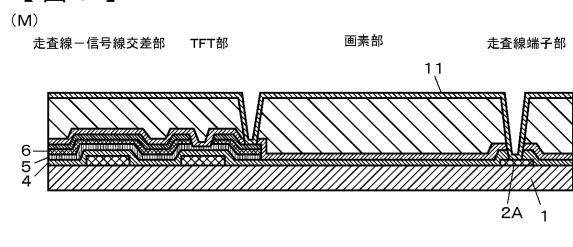

#### 【0009】

引き続き図5(M)に示すように、スパッタリング法や塗布法等によって透明導電膜11をガラス基板1の全面に被着形成する。透明導電膜11とは、例えば酸化インジニウム錫(ITO)等の金属酸化膜が一般的である。その後、5枚目のフォトマスクを使用して図5(N)に示すレジストパターン12をマスクとして透明導電膜11を選択的にエッチングして絵素電極11Aのパターニングを行い、そして図5(O)に示すように不要なレジストパターン12の除去を行えば、ガラス基板1はアクティブマトリクス型アモルファスシリコン TFT アレイ基板として完成する。10

#### 【0010】

このようにして得られたTFTアレイ基板とカラーフィルタを貼り合せて液晶パネルを作製し、続いてバックライトと駆動用の回路基板を実装したものが液晶モジュールとして各種の液晶表示装置に組み込まれている。上記のアクティブマトリクス型アモルファスシリコン TFT アレイ基板の製作方法においては4枚のフォトマスクが必要であるが、例えば特開2002-250935号公報においては、撥水処理技術を用いて図4に示したコンタクト形成工程と図5に示した絵素電極の形成工程を1枚のフォトマスクで構成し、合計3枚のフォトマスクでTFTアレイ基板を形成する製造工程の削減技術が開示されている。さらに特開2002-98996号公報においては、化学的機械研磨処理技術を用いて上記の2つのパターニング工程を同様に1枚のフォトマスクで構成し、合計3枚のフォトマスクでTFTアレイ基板を形成する別の削減技術も開示されている。20

【特許文献2】特開2002-250935号公報

【特許文献3】特開2002-98996号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0011】

このように、アクティブマトリクス型アモルファスシリコン TFT アレイ基板を作成するためには現時点では5枚あるいは4枚のフォトマスクが必要であり、プロセスリードタイムの長時間化や歩留まり低下の要因となっている。また、特許文献2に示されている先行技術では必要なフォトマスク枚数は3枚に削減されるが、撥水性処理を施す工程と撥水性を除去する工程が新たに必要となり、生産性を低下させる要因となる。また、絵素電極11Aの下地である平坦化膜がハーフトーンプロセスにさらされるためにアレイ基板1の表面の平坦性が損なわれ、コントラスト低下等のディスプレイ表示性能が悪化する恐れが高いと考えられる。そして特許文献3に示される先行技術においては新たに化学的機械研磨処理工程の追加が必要であり、加えて一辺が1mを超えるような大面積のガラス基板の研磨工程ではガラス基板の平坦度を維持することが困難であり、特許文献2と同様にハーフトーンプロセスによる表示性能への悪影響が懸念される。30

#### 【課題を解決するための手段】

#### 【0012】

請求項1は、一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、ドレイン配線に接続された絵素電極を有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、少なくとも、第1の透明性絶縁基板の一主面上に走査線と、絶縁ゲート型トランジスタと、信号線が形成され、その上に感光性有機絶縁層であるパシベーション絶縁層が形成され、前記感光性有機絶縁層には、前記ドレイン配線及び走査線の端子部までに達する開口部が形成されるとともに、絵素電極同士と電極端子同士を分離する部分である走査線 信号線交差部、TFT部、及び走査線端子部の両側に該当する領域に前記感光性有機絶縁層の底まで届かない幅の細い溝が一40

つの単位絵素において複数本並列して形成され、前記感光性有機絶縁層上に絵素電極となる導電膜が被着されていることを特徴とする。

#### 【0013】

この構成により、絵素電極形成領域外の領域に設けられた感光性有機絶縁膜の底まで届かない幅の細い溝が感光性有機絶縁膜上に被着された導電膜を物理的、電気的に絶縁分離するので、透明導電膜は自動的に個々に独立して形成されることになる。すなわち、感光性樹脂パターンを用いた微細加工技術により絵素電極をパターニングした場合と同等の効果が得られる。導電膜は上記の物理的、電気的な絶縁分離が容易に行えるのであればその種類は問われないので、導電膜に透明導電膜を用いれば透過型の、また反射率の高い金属薄膜を用いれば反射型の液晶表示装置を得ることができる。

10

#### 【0014】

請求項2は、請求項1に記載の液晶表示装置の製造方法であって、

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、ドレイン配線に接続された絵素電極を有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、コンタクトホール形成工程で、少なくとも、

第1の透明性絶縁基板の一主面上に走査線と、絶縁ゲート型トランジスタと、信号線を形成し、

その上に感光性有機絶縁膜を塗布して表面が平坦な電気絶縁膜を形成し、

20

コンタクト形成領域を白、絵素電極形成領域を黒、絵素電極の周囲は光源からの照射光を位相シフトさせて通過させる中間調領域とする位相シフトフォトマスクを用いて、前記感光性有機絶縁膜を露光・現像し、

前記感光性有機絶縁膜には、前記ドレイン配線及び走査線の端子部までに達する開口部を形成するとともに、絵素電極同士と電極端子同士を分離する部分である走査線 信号線交差部、TFT部、及び走査線端子部の両側に該当する領域に前記感光性有機絶縁層の底まで届かない幅の細い溝を一つの単位絵素において複数本並列して形成し、

前記感光性有機絶縁層上に絵素電極となる導電膜を被着することを特徴とする。

#### 【0015】

30

この構成により中間調領域における位相シフト効果によって、該当領域の感光性有機絶縁膜の断面部のテーパ角度が90度に近づき、また露光機の解像力限界以上の微細なライン&スペースをパターニングする事が可能になり、絵素周辺の限られた領域により多くの溝を形成する事が可能になる。また、露光機の解像力限界以上のライン&スペースでは、該当領域に照射される露光エネルギーは減衰し、パターニングされたスペース(溝)部分の底面は感光性有機絶縁膜の底まで至らない。一方、コンタクト形成領域は一般的なバイナリーマスクの透明部分と同様の原理でパターニングされるため、コンタクトホールに必要な比較的穏やかなテーパ角を形成出来る。絵素電極形成領域は一般的なバイナリーマスクの遮光部分と同様にパターニングされない。このように所定の開口部と細い溝を形成した後、絵素電極となる導電膜を被着すれば、位相シフト効果によってパターニングされた絵素電極の周辺領域において、感光性有機絶縁膜で形成されたパターンの形状(溝)により導電膜が断線するため、絵素電極形成領域が孤立して絵素電極として形成される。さらに、位相シフト効果により解像力以下のパターニングが可能となるため、限られた領域に複数本の溝の形成が可能となり、上記の断線確率を向上する事が容易となる。このため、位相シフトマスクを使用してコンタクトホール形成と絵素電極のパターニングを1回のフォトリソグラフィ工程で行う事が出来るので、従来の製法とは異なり絵素電極形成工程においてフォトリソグラフィ工程が必要で無くなる。

40

#### 【0016】

請求項3によれば請求項2の液晶表示装置の製造方法において、絵素電極用の透明導電膜を従来通りのスパッタリング法で形成することが出来る。

50

**【 0 0 1 7 】**

請求項 4 によれば請求項 2 の液晶表示装置の製造方法において、絵素電極用の透明導電膜を、真空装置を必要としない塗布法によって形成することが出来る。

**【 0 0 1 8 】**

請求項 5 によれば請求項 2 の液晶表示装置の製造方法において、反射絵素電極用の高反射率金属薄膜を従来通りのスパッタリング法で形成することが出来る。

**【発明の効果】****【 0 0 1 9 】**

以上述べたように、感光性アクリル樹脂膜を含むコンタクトホール形成工程において位相シフトマスクを使用することにより、1度のフォトリソグラフィ工程のみで通常のコンタクト形成に必要なテーパ形状を有する開口パターンと細かくて比較的垂直に近いテーパ形状を有する溝状のパターンを同時に形成し、この細かくて比較的垂直に近いテーパ形状が、絵素電極形成工程においてフォトリソグラフィ工程を必要とせずに次工程で被着される導電層を分断してパターン化する事が可能となる。このように平坦化膜である感光性アクリル樹脂膜に形成された細くかつ深い溝の段差により、絵素電極の分離を行う新規な液晶表示装置用アレイ基板を提供する事ができる。10

**【 0 0 2 0 】**

本発明では、液晶表示用アレイ基板の製作に当たりフォトリソグラフィ工程を1工程分、削減することができるので、公知の4枚マスクプロセスとの組み合わせにより、3枚マスクプロセスが実現し、製造コストの低減にも大きく貢献する。また、この技術は反射型の液晶表示差内においても同様に実施可能である。20

**【 0 0 2 1 】**

本発明によれば絵素電極用導電性膜を従来例と同様にスパッタリング法で形成することができる。あるいは絵素電極用透明導電性膜を塗布法で形成することもできるのでスパッタ装置のような高価な真空装置や生産機械を必要とせず、更なる製造コストの低減も推進される。

**【 0 0 2 2 】**

本発明の優位性は、図4と図5に示したコンタクト形成工程と絵素電極の形成工程を1枚のフォトマスクで作製出来る技術を提供するだけではなく、前述した先行技術に示されるような追加工程を必要としないので、プロセスリードタイムがより短く、生産性がさらに高くなる点にある。また、絵素電極形成領域にはハーフトーンプロセスを使用しないため、アレイ基板の平坦性が損なわれることは無く、コントラスト等の表示性能を悪化させることもない。30

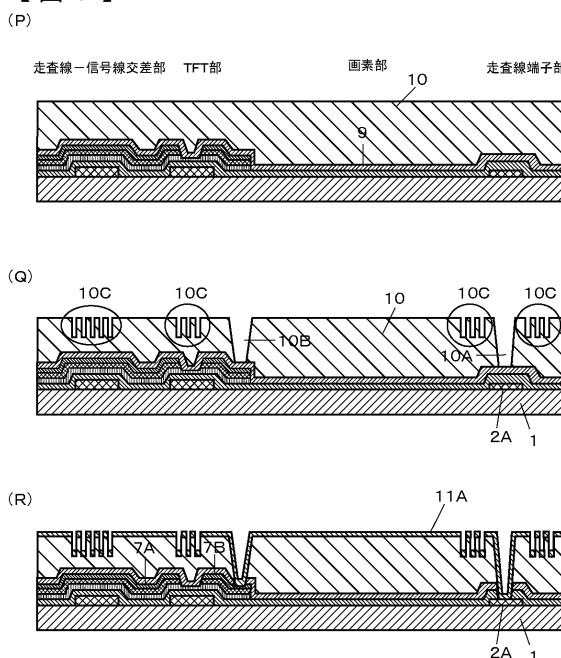

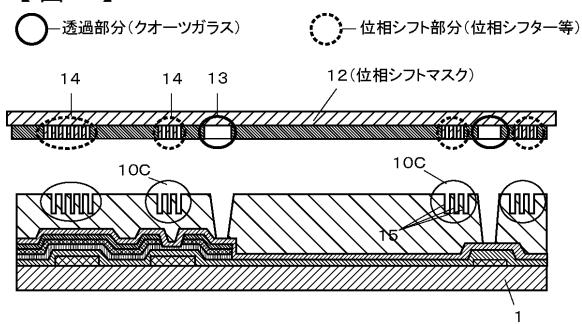

**【発明を実施するための最良の形態】****【 0 0 2 3 】**

図1(A)～図4(J)までの製造工程は従来例で説明した製造工程と同一である。それ以降の本発明の実施例による製造工程の断面図を図6で示す。また図7は位相差マスクを説明する位相差マスクの概略断面図である。製造工程の断面図は先述したように、走査線と信号線とが交差する走査線 信号線交差部、スイッチング素子としてのTFT部及び絵素部及び走査線の周辺回路に配置される電極端子部を並べた断面部分を模式的に示す。40

**【実施例1】****【 0 0 2 4 】**

まず、図1(A)に示すようにガラス基板1の一主面上にスパッタリング装置等の製膜装置を用いて、例えばクロム、モリブデン、タンタル、アルミニウム、銅あるいはそれらの合金や積層を第1の金属膜2として形成する。次に第1の金属膜2の一主面上にフォトレジストを塗布し、1枚目のフォトマスクを使用して、図1(B)に示すレジストパターン3を形成する。その後、レジストパターン3をマスクとして第1の金属膜2のエッチングを行った後、レジストパターン3を除去して図1(C)に示すようなゲート電極膜2Aを形成する。

**【 0 0 2 5 】**

50

次にプラズマ C V D 装置やスパッタリング装置等を使用して、図 2 ( C ) に示すようにゲート絶縁層としての第 1 のシリコン窒化膜 4 、トランジスタのチャネルとしての第 1 のシリコン膜 5 、 N 型不純物をドープした第 2 のシリコン膜 6 を被着する。さらにスパッタリング装置等を利用して、例えばクロム、モリブデン、アルミニウム、銅あるいはそれらの合金や積層を第 2 の金属膜 7 として被着する。その後、スリットパターン、ドットパターン等により、透過する露光エネルギーを調整した 2 枚目のフォトマスクあるいは、半透過膜により透過する露光エネルギーを調整した 2 枚目のフォトマスクを使用し、未露光部分、完全露光部分及びハーフトーン露光部分を形成し、図 2 ( E ) に示すレジストパターン 8 を作成する。図 2 ( F ) に示すように、レジストパターン 8 をマスクとして第 2 の金属膜 7 及び第 2 のシリコン層 6 と第 1 のシリコン層 5 のエッチングを行った後、図 3 ( G ) に示すように酸素プラズマ等のアッシングプロセスによりチャネル部分 8 A のレジスト除去を行い、信号線層 7 を露出させる。その後、図 3 ( H ) に示すように膜厚が減少したレジストパターン 8 B をマスクとして再び信号線層 7 、第 2 のシリコン層 6 及び第 1 のシリコン層 5 をエッチングし、第 1 のシリコン層は 0.05 ~ 0.1 μm 程度残す。その後、図 3 ( I ) に示すように残されたレジスト除去を行い、ソース・ドレイン配線 7 A , 7 B の形成を終える。

#### 【 0026 】

次に図 6 ( P ) ( 図 4 ( J ) と同一 ) に示すように、例えば第 2 の窒化シリコン膜等の保護膜あるいはパシベーション絶縁層 9 をスパッタリング法、あるいは C V D 法により形成し、さらに平坦化膜として例えば 3 ~ 6 μm の厚さの感光性アクリル樹脂膜 10 の塗布を行う。

#### 【 0027 】

その後、3 枚目のフォトマスクとして、例えば図 7 に示すような位相シフトマスク 12 を用いて感光性アクリル樹脂膜 10 のパターニングを行う。位相シフトマスクとしては、例えばモリブデンシリサイド膜、ジルコニウムシリサイド膜を位相シフターとして機能させるものや、フォトマスクの母材となるクオーツガラスを掘り込むことにより、位相を変える掘り込み型、あるいはクロムレス位相シフトマスク等がある。これらの位相シフトマスク 12 を使用して図 6 ( Q ) と図 7 に示すように、コンタクトホール形成領域 10 A 、 10 B に該当する部分には通常のバイナリーマスクと同様に透過部分 13 を透過した光によりコンタクトホールに必要なテーパ形状を有するパターンを形成する。この時、 10 A 、 10 B の開口部分は保護膜 9 の表面まで到達している。また、絵素電極同士と電極端子同士を分離する部分、あるいは電気的に導電膜を必要としない部分 10 C に該当する領域には位相シフト部分 14 を持たしているため、コンタクトホール形成領域に比べて垂直に深い溝 15 がパターニングされる。そして露光機の解像力を超えた細かなパターン形成も可能となる。これらの溝 15 は露光機の解像力と同等以上に細かいため、感光性アクリル樹脂膜 10 に照射されるエネルギーはコンタクト形成領域に比べて小さくなり、溝 15 の底辺は感光性アクリル樹脂膜 10 の底辺まで到達することはない。例えば、溝 15 のスリット幅は 1 ~ 3 μm 、深さは 1 ~ 4 μm 程度とするような位相差シフト部分 14 のパターン設計が可能である。位相シフト ( 位相シフト効果 ) 部分 14 は、隣り合うパターンの位相を変換することにより、パターンのエッジ部分を強調するように調整されている。なお上記の説明ではポジティブ型の感光性アクリル樹脂膜を例にとったが、位相シフト露光は化学增幅型のネガティブ型の感光性アクリル樹脂膜にも適用出来ることは言うまでもない。そして図 6 ( Q ) に示すように、このような位相差シフトマスク 12 を用いて得られた感光性アクリル樹脂膜のパターンをマスクとしてエッチングを行い、第 2 の窒化シリコン膜 9 と第 1 の窒化シリコン膜 4 を選択的に除去する。

#### 【 0028 】

その後、図 6 ( R ) に示すように、例えば 0.04 ~ 0.2 μm 程度の厚さの透明導電膜 11 をスパッタリング法あるいは、塗布法によりパターン化された感光性アクリル樹脂膜 10 上に被着させる。塗布法の場合は、導電材を含む溶液を塗布した後、加熱して透明導電性膜を物理的、化学的に安定させると良い。透明導電性膜は一般的に上記のように膜厚

が薄く（0.1 μm程度）、前工程で形成された電気的に導電膜を必要としない領域10Cの深く（1 μm以上）細かな溝15により容易に物理的、電気的に分断されて絵素電極形成領域に透明導電性の絵素電極11Aが自動的に形成されるが、絵素電極11Aはコンタクト部分10BでTFTのドレイン7Bと物理的、電気的に接続されている。

#### 【実施例2】

##### 【0029】

実施例1で明らかなように本発明では、絵素電極はパターンングの必要が無く、感光性アクリル樹脂膜10に形成された深い溝15によって絵素電極用の導電性薄膜が電気的、物理的に分断されれば良い。したがって絵素電極用の導電性薄膜にAL及びAL合金、または銀及び銀合金等の高反射率金属を用いると反射型液晶表示装置の絵素電極（反射電極）を得ることができる。これらの金属は通常スパッタで被着形成され、その膜厚は透過型の透明電極と同じく0.1 μm程度が一般的である。これは膜厚の増大に伴う結晶の成長によって反射率が低下するのを回避する意味合いも含まれている。10

##### 【0030】

ただし、図示はしないが反射型液晶表示装置の絵素電極は鏡面反射を回避するため、その下地が平坦ではなく、深さが0.5～1 μm前後の凹凸面が必要である。多くの場合、このような凹凸面を有する下地の形成にも感光性アクリル樹脂が用いられており、コスト的な課題はあるが、1層目の感光性アクリル樹脂層で凹凸を形成し、さらに2層目の感光性アクリル樹脂層を所謂、最終的なパシベーション絶縁層として被着形成し、絵素電極とドレイン電極との間を接続するための開口部を形成した後、絵素電極を形成すれば反射型の液晶表示装置が得られる。この場合には2層目の感光性アクリル樹脂層に本発明を適用すればプロセス削減の目的は達せられる。20

##### 【0031】

感光性アクリル樹脂を1層だけ用いて本発明で提案する深い溝と、その表面に凹凸を持たせるためには、例えば凹凸形成領域のみに局所的に熱エネルギー、光エネルギーを与えるような技術開発が必要と推察されるが、それでも感光性アクリル樹脂層を2層用いて凹凸を形成する場合の長いプロセス処理と比較するとコストメリットが大きく、本発明による深い溝共々、反射型液晶表示装置の低コスト化に寄与することは間違いない。

##### 【0032】

以上の説明からも明らかなように、本発明においては絵素電極形成工程でフォトマスクを使用しないため、透過型の液晶表示装置用TFTアレイ基板を3枚のフォトマスクで製造することが可能である。30

##### 【0033】

最後に本発明において感光性有機絶縁層（アクリル樹脂膜）10は必須の構成部位であるが、チャネル上に保護絶縁層を有するエッチストップ型の絶縁ゲート型トランジスタを用いた液晶表示装置ではパシベーション絶縁膜あるいは保護膜9は必ずしも必要ではない事も補足しておく。

#### 【図面の簡単な説明】

##### 【0034】

【図1】本発明及び従来例の液晶表示用アレイ基板の断面図（ゲート電極形成工程）40

【図2】本発明及び従来例の液晶表示用アレイ基板の断面図（SD配線形成工程）

【図3】本発明及び従来例の液晶表示用アレイ基板の断面図（半導体層形成工程）

【図4】従来例の液晶表示用アレイ基板の断面図（コンタクト形成工程）

【図5】従来例の液晶表示用アレイ基板の断面図（絵素電極形成工程）

【図6】本発明の液晶表示用アレイ基板の断面図（コンタクト形成工程と絵素電極形成工程）

【図7】本発明で使用する位相シフトマスク

#### 【符号の説明】

##### 【0035】

1 - ガラス基板、2 - 第1の金属膜、3 - レジストパターン、4 - 第1のシリコン窒化膜50

、5 - 第1のシリコン膜、6 - 第2のシリコン膜、7 - 第2の金属膜、8 - レジストバーン、8A - チャネル部分、9 - 第2のシリコン窒化膜、10 - 感光性アクリル樹脂膜、10A, 10B - コンタクト部分(開口部)、10C - 導電膜を必要としない部分(溝形成領域)、11 - 透明導電膜、11A - 絵素電極、12 - 位相差シフトマスク、13 - 透過部分、14 - 位相シフト部分、15 - 感光性有機絶縁層に形成された(微少な)溝。

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(74)代理人 303016443

クオンタ・ディスプレイ・ジャパン株式会社

(73)特許権者 303016443

クオンタ・ディスプレイ・ジャパン株式会社

大阪府大阪市中央区内平野町3丁目2番12号 HPCビル内

(72)発明者 堀野 滋和

大阪府大阪市中央区内平野町3丁目2番12号

クオンタ・ディスプレイ・

ジャパン株式会社内

(72)発明者 董 峻 豪

台湾桃園縣龜山鄉華亞2路189号

廣輝電子股 ふん 有限公司内

(72)発明者 曾 賢 楷

台湾桃園縣龜山鄉華亞2路189号

廣輝電子股 ふん 有限公司内

審査官 小濱 健太

(56)参考文献 特開2004-102256(JP,A)

特開2004-191557(JP,A)

特開2003-098537(JP,A)

特開2004-271989(JP,A)

特開2002-206571(JP,A)

特開2002-250935(JP,A)

特開2002-098996(JP,A)

特開平10-325964(JP,A)

特開平11-064890(JP,A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1343

G02F 1/1368

|                |                                                                                                                                                                                                                                                                                                                                                                              |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP4805587B2</a>                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2011-11-02 |

| 申请号            | JP2005048251                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2005-02-24 |

| [标]申请(专利权)人(译) | 广辉日本<br>HiroshiTeru电子裆粪便                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 广辉日本有限公司<br>广辉电子股▲ふん▼有限公司                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 当前申请(专利权)人(译)  | 友达光电股份有限公司<br>广辉日本有限公司                                                                                                                                                                                                                                                                                                                                                       |         |            |

| [标]发明人         | 堀野滋和<br>董峻豪<br>曾賢楷                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 堀野 滋和<br>董 ▲峻▼ 豪<br>曾 賢 楷                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G02F1/1368 G02F1/1343                                                                                                                                                                                                                                                                                                                                                        |         |            |

| CPC分类号         | G02F1/136227 G02F2001/136236 H01L27/124 H01L27/1288 H01L29/78633                                                                                                                                                                                                                                                                                                             |         |            |

| FI分类号          | G02F1/1368 G02F1/1343                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 2H092/GA29 2H092/JA26 2H092/JA46 2H092/JB07 2H092/JB57 2H092/JB58 2H092/KA10 2H092 /KA12 2H092/KA18 2H092/KB04 2H092/KB11 2H092/KB22 2H092/KB24 2H092/KB25 2H092/MA05 2H092/MA08 2H092/MA10 2H092/MA13 2H092/MA14 2H092/MA17 2H092/MA27 2H092/NA27 2H192 /AA24 2H192/BC31 2H192/BC72 2H192/CB05 2H192/EA43 2H192/EA64 2H192/EA67 2H192/EA72 2H192/HA23 2H192/HA44 2H192/HA80 |         |            |

| 代理机构(译)        | 广辉日本有限公司                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 其他公开文献         | <a href="#">JP2006235134A</a>                                                                                                                                                                                                                                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                    |         |            |

## 摘要(译)

要解决的问题：为了降低液晶显示装置等的制造成本，通过提供用于液晶显示装置等的TFT阵列基板，光刻处理的数量和光掩模的数量小于修道院的那个。SOLUTION：通过形成具有新锥形形状的图案10A和10B以及具有相对接近垂直度的锥形形状的精细图案10C，能够在不使用光刻工艺的情况下分离像素电极图案作为后续工艺的新技术仅使用具有相移效应的光掩模通过一次光刻工艺在正常的接触孔部分中，使用光敏丙烯酸树脂10进行接触形成的光刻工艺，并结合已知的四掩模工艺，以提供能够形成TFT阵列的新技术用于具有三个光掩模的显示装置的基板。