(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-213063

(P2007-213063A)

(43) 公開日 平成19年8月23日(2007.8.23)

(51) Int.C1.

G02F 1/1368 (2006.01)

G02F 1/1345 (2006.01)

G09F 9/30 (2006.01)

F 1

G02F 1/1368

G02F 1/1345

G09F 9/30 338

G09F 9/30 330Z

テーマコード(参考)

2 H 092

5 C 094

審査請求 未請求 請求項の数 18 O L (全 16 頁)

(21) 出願番号 特願2007-23473 (P2007-23473)

(22) 出願日 平成19年2月1日 (2007.2.1)

(31) 優先権主張番号 10-2006-0011110

(32) 優先日 平成18年2月6日 (2006.2.6)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市八達区梅灘洞416

番地

(74) 代理人 100094145

弁理士 小野 由己男

(74) 代理人 100106367

弁理士 稲積 朋子

(72) 発明者 張 鐘 雄

大韓民国忠清南道天安市佛堂洞大東多スッ

プアパート107棟104号

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】本発明は画質を向上させることのできる液晶表示装置を提供する。

【解決方法】第1基板上の共通電極と、液晶を介して第1基板と対向する第2基板上に交差するように形成されたゲートライン及びデータラインと、前記ゲートライン及びデータラインに接続された薄膜トランジスタと、前記ゲートライン方向の長辺と前記データライン方向の短辺を有する各サブピクセル領域に形成されて前記薄膜トランジスタに接続された画素電極と、回路フィルム上に実装されて前記データラインを駆動させる駆動チップと、前記駆動チップからの駆動信号を前記データラインに供給するファンアウトラインと、異なる前記駆動チップに接続された前記ファンアウトライン間に形成されて前記共通電極に共通電圧を供給する第1導電スペースと、同一の前記駆動チップに接続された前記ファンアウトライン間に形成されて前記共通電極に共通電圧を供給する第2導電スペースとを備える。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

第1基板に形成された共通電極と、

液晶を介して第1基板と合着剤により貼り合わせられる第2基板上に交差するように形成されたゲートライン及びデータラインと、

前記ゲートライン及びデータラインに接続された薄膜トランジスタと、

前記ゲートライン方向の長辺と前記データライン方向の短辺を有する各サブピクセル領域に形成されて前記薄膜トランジスタに接続された画素電極と、

複数の駆動チップから受信された駆動信号をデータラインに供給するファンアウトラインと、

異なる前記駆動チップに接続された前記ファンアウトライン間に形成されて前記共通電極に共通電圧を供給する第1導電スペースと、

同一の前記駆動チップに接続された前記ファンアウトライン間に形成されて前記共通電極に共通電圧を供給する第2導電スペースとを備えることを特徴とする液晶表示装置。10

**【請求項 2】**

前記ファンアウトラインと交差するように形成されて前記第1及び第2導電スペースを接続する共通電圧供給ラインをさらに備えることを特徴とする請求項1に記載の液晶表示装置。20

**【請求項 3】**

前記共通電圧供給ラインが前記同一の駆動チップに接続されたファンアウトライン毎に区分されるように複数形成されることを特徴とする請求項2に記載の液晶表示装置。

**【請求項 4】**

前記共通電極には前記ファンアウトラインに対応する領域毎に異なる共通電圧が供給されることを特徴とする請求項3に記載の液晶表示装置。

**【請求項 5】**

前記第2導電スペースが、前記同一の駆動チップに接続された前記ファンアウトラインのうち中央に位置するファンアウトラインと隣接するように形成されることを特徴とする請求項4に記載の液晶表示装置。

**【請求項 6】**

前記短辺方向に沿って前記サブピクセルを経由するように形成された複数のストレージラインをさらに備えることを特徴とする請求項1に記載の液晶表示装置。30

**【請求項 7】**

前記同一の駆動チップに接続された前記ファンアウトライン毎に形成され、前記ストレージラインに共通に接続されたストレージ供給ラインをさらに備えることを特徴とする請求項6に記載の液晶表示装置。

**【請求項 8】**

前記ストレージ供給ラインが、前記同一の駆動チップに接続されたファンアウトラインに対応する領域に位置するストレージライン毎に異なるストレージ電圧を供給することを特徴とする請求項7に記載の液晶表示装置。

**【請求項 9】**

前記ファンアウトラインと交差する前記ストレージ供給ラインが前記合着剤と重なるように形成されることを特徴とする請求項7に記載の液晶表示装置。

**【請求項 10】**

前記合着剤がソフトスペースを含むことを特徴とする請求項7に記載の液晶表示装置。

**【請求項 11】**

前記ファンアウトラインを覆うように形成され、前記合着剤の圧力を緩衝することができる程度の厚さを有する保護膜をさらに含むことを特徴とする請求項7に記載の液晶表示装置。

**【請求項 12】**

第1基板に形成された共通電極と、

10

20

40

50

液晶を介して第1基板と合着剤により貼り合わせられる第2基板上に交差するように形成されたゲートライン及びデータラインと、

前記ゲートライン及びデータラインに接続された薄膜トランジスタと、

前記ゲートライン方向の長辺と前記データライン方向の短辺を有する各サブピクセル領域に形成されて前記薄膜トランジスタに接続された画素電極と、

前記短辺方向に沿って前記サブピクセルを経由するように形成された複数のストレージラインと、

前記複数のストレージラインに共通に接続されるストレージ供給ラインとを備えることを特徴とする液晶表示装置。

【請求項13】

前記第2基板上に形成されて前記共通電極に共通電圧を供給する導電スペースと、

前記導電スペースと隣接するように形成されて前記共通電圧をフィードバックするフィードバックスペースとをさらに備えることを特徴とする請求項12に記載の液晶表示装置。

【請求項14】

フィードバックされた共通電圧と逆位相を有する補償信号を前記フィードバックスペースを経由して前記ストレージラインに供給することを特徴とする請求項13に記載の液晶表示装置。

【請求項15】

前記ストレージ供給ラインの幅が4～6mmであることを特徴とする請求項12に記載の液晶表示装置。

【請求項16】

前記合着剤がソフトスペースを含むことを特徴とする請求項12に記載の液晶表示装置。

【請求項17】

前記ファンアウトラインを覆うように形成され、前記合着剤の圧力を緩衝することができる程度の厚さを有する保護膜をさらに含むことを特徴とする請求項12に記載の液晶表示装置。

【請求項18】

前記ストレージ供給ラインが前記合着剤の少なくとも一部分と重なることを特徴とする請求項12に記載の液晶表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は液晶表示装置に関する。

【背景技術】

【0002】

液晶表示装置は液晶の電気的及び光学的特性を利用した画素マトリクスにより映像を表示する。液晶表示装置の各画素は、データ信号による液晶配列を変化させて光透過率を調節する赤、緑、青のサブピクセルの組み合わせにより所望の色を実現する。各サブピクセルは、スイッチング素子である薄膜トランジスタを介して画素電極に供給されたデータ信号と共に供給された共通電圧との差電圧を充電して液晶を駆動する。薄膜トランジスタは、ゲートラインに供給されたゲートオン電圧によりターンオンしてデータラインに供給されたデータ信号を画素電極に充電し、ゲートラインに供給されたゲートオフ電圧によりターンオフして画素電極に充電されたデータ信号が維持されるようにする。ここで、ゲートラインに供給されたゲートオフ電圧は、画素電極に充電されたデータ信号が維持されるように安定した電圧を維持しなければならない。

【発明の開示】

【発明が解決しようとする課題】

【0003】

10

20

30

40

50

しかし、液晶表示装置においては、液晶を介して重なったデータラインと共通電極との間に存在する寄生容量のカップリング作用により、データラインに供給されるデータ信号によって共通電圧がスイングするリップル現象が発生してクロストークが発生する。特に画面に極性の偏りが激しい特定パターンを表示する場合、共通電圧のリップル成分が増加することによってクロストークは激しくなる。

【0004】

従って、本発明が達成しようとする技術的課題は、クロストークを防止して画質を向上させることのできる液晶表示装置を提供することにある。

【課題を解決するための手段】

【0005】

前記技術的課題を達成するために、本発明1による液晶表示装置は、第1基板に形成された共通電極と、液晶を介して第1基板と合着剤により貼り合わせられる第2基板上に交差するように形成されたゲートライン及びデータラインと、前記ゲートライン及びデータラインに接続された薄膜トランジスタと、前記ゲートライン方向の長辺と前記データライン方向の短辺を有する各サブピクセル領域に形成されて前記薄膜トランジスタに接続された画素電極と、回路フィルム上に実装されて前記データラインを駆動させる駆動チップと、前記駆動チップからの駆動信号を前記データラインに供給するファンアウトラインと、異なる前記駆動チップに接続された前記ファンアウトライン間に形成されて前記共通電極に共通電圧を供給する第1導電スペースと、同一の前記駆動チップに接続された前記ファンアウトライン間に形成されて前記共通電極に共通電圧を供給する第2導電スペースとを備えることを特徴とする。

【0006】

また、発明2は、発明1において、前記液晶表示装置は、前記ファンアウトラインと交差するように形成されて前記第1及び第2導電スペースを接続する共通電圧供給ラインをさらに備えることを特徴とする。

ここで、発明3は、発明2において、前記共通電圧供給ラインは、前記同一の駆動チップに接続されたファンアウトライン毎に区分されるように複数形成されることを特徴とする。

【0007】

また、発明4は、発明3において、前記共通電極には、前記ファンアウトラインに対応する領域毎に異なる共通電圧が供給されることを特徴とする。

また、発明5は、発明4において、前記第2導電スペースは、前記同一の駆動チップに接続された前記ファンアウトラインのうち中央に位置するファンアウトラインと隣接するように形成されることを特徴とする。

【0008】

一方、発明6は、発明1において、前記液晶表示装置は、前記短辺方向に沿って前記サブピクセルを経由するように形成された複数のストレージラインをさらに備えることを特徴とする。

また、発明7は、発明6において、前記液晶表示装置は、前記同一の駆動チップに接続された前記ファンアウトライン毎に形成されて前記ストレージラインに共通に接続されたストレージ供給ラインをさらに備えることを特徴とする。

【0009】

ここで、発明8は、発明7において、前記ストレージ供給ラインは、前記同一の駆動チップに接続されたファンアウトラインに対応する領域に位置するストレージライン毎に異なるストレージ電圧を供給することを特徴とする。

一方、発明9は、発明7において、前記ファンアウトラインと交差する前記ストレージ供給ラインは、前記合着剤と重なるように形成されることを特徴とする。

【0010】

ここで、発明10は、発明7において、前記合着剤はソフトスペースを含むことを特徴とする。

10

20

30

40

50

又は、発明11は、発明7において、前記ファンアウトラインを覆うように形成された保護膜は、有機絶縁膜から形成されることを特徴とする。

前記技術的課題を達成するために、本発明12による液晶表示装置は、第1基板に形成された共通電極と、液晶を介して第1基板と合着剤により貼り合わせられる第2基板上に交差するように形成されたゲートライン及びデータラインと、前記ゲートライン及びデータラインに接続された薄膜トランジスタと、前記ゲートライン方向の長辺と前記データライン方向の短辺を有する各サブピクセル領域に形成されて前記薄膜トランジスタに接続された画素電極と、前記短辺方向に沿って前記サブピクセルを経由するように形成された複数のストレージラインと、前記複数のストレージラインに共通に接続されて前記合着剤と少なくとも一部重なったストレージ供給ラインとを備えることを特徴とする。

10

#### 【0011】

また、発明13は、発明12において、前記液晶表示装置は、前記第2基板上に形成されて前記共通電極に共通電圧を供給する導電スペースと、前記導電スペースと隣接するように形成されて前記共通電圧をフィードバックするフィードバックスペースとをさらに備えることを特徴とする。

また、発明14は、発明13において、前記フィードバックスペースを介してフィードバックされた共通電圧と逆位相の補償信号を前記ストレージラインに供給することを特徴とする。

#### 【0012】

一方、発明15は、発明12において、前記ストレージ供給ラインの幅は4~6mmであることを特徴とする。

20

発明16は、発明12において、前記合着剤がソフトスペースを含むことを特徴とする。

発明17は、発明12において、前記ファンアウトラインを覆うように形成され、前記合着剤の圧力を緩衝することのできる程度の厚さを有する保護膜をさらに含むことを特徴とする。

#### 【0013】

発明18は、発明12において、前記ストレージ供給ラインが前記合着剤の少なくとも一部分と重なることを特徴とする。

30

#### 【発明の効果】

#### 【0014】

本発明によれば、クロストークを防止して画質を向上させることのできる液晶表示装置を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0015】

前記技術的課題以外の本発明の他の技術的課題及び利点は、添付図面を参照した本発明の好ましい実施形態についての説明により明白になるであろう。

以下、添付図面を参照して本発明の実施形態について説明する。

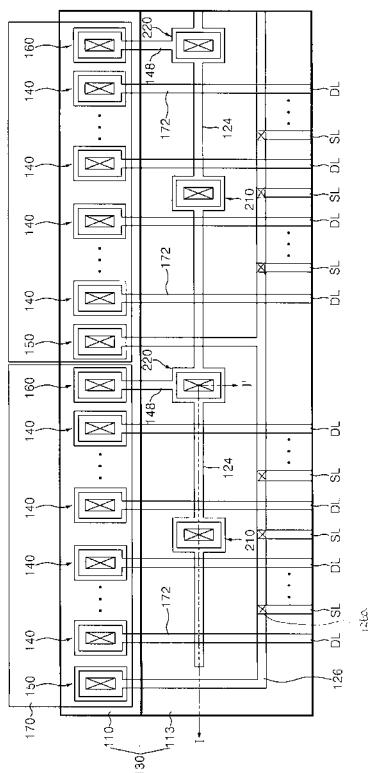

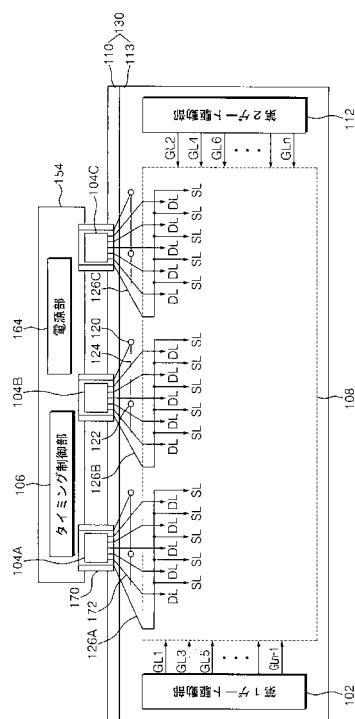

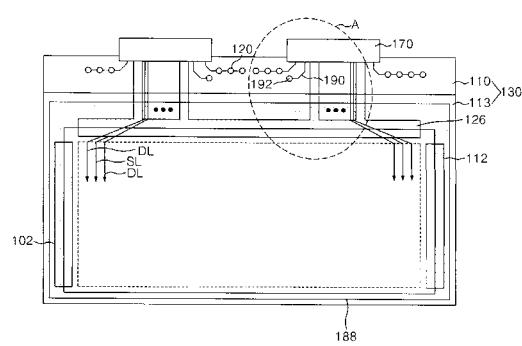

図1は本発明の第1実施形態による液晶表示装置を概略的に示す図である。図2は図1に示す液晶表示装置の薄膜トランジスタ基板における2つのサブピクセルを示す平面図、図3は図1に示す液晶表示装置における回路フィルムと第1及び第2導電スペースに接続されるパッドとを示す平面図である。

40

#### 【0016】

図1に示す液晶表示装置は、液晶表示パネル130と、プリント基板(Printed Circuit Board: PCB)154と、回路フィルム170とを備え、液晶表示パネル130には画像表示部108と、画像表示部108のゲートラインGLを駆動するゲート駆動部(第1ゲート駆動部102、第2ゲート駆動部112)とが形成され、プリント基板154にはデータラインDLを駆動するデータ駆動チップ104が形成され、回路フィルム170はプリント基板154と液晶表示パネル130との間を接続する。また、PCB154は、タイミング制御部106と電源部164とを備える。

50

## 【0017】

第1ゲート駆動部102及び第2ゲート駆動部112は、画像表示部108の両側部に位置してゲートラインGLを分割駆動する。例えば、第1ゲート駆動部102は奇数ゲートラインGL1、GL3、…、GLn-1を駆動し、第2ゲート駆動部112は偶数ゲートラインGL2、GL4、…、GLnを駆動する。第1ゲート駆動部102及び第2ゲート駆動部112は複数の薄膜トランジスタを含むシフトレジスタから構成されるので、液晶表示パネル130の画像表示部108の薄膜トランジスタ及び複数の信号ラインDL、GL、SL(ストレージライン)と共に形成され、非表示領域に内蔵される。第1ゲート駆動部102及び第2ゲート駆動部112は、タイミング制御部106からのゲート制御信号並びに電源部164からのゲートオン電圧及びゲートオフ電圧を利用して画像表示部108のゲートラインGL1～GLnを順次駆動する。

## 【0018】

画像表示部108のデータラインDLを分割駆動する複数のデータ駆動チップ104のそれぞれは回路フィルム170上に実装され、回路フィルム170は異方性導電フィルム(Anisotropic Conductive Film: ACF)を介して液晶表示パネル130及びPCB154に付着される。データ駆動チップ104を実装した回路フィルム170としては、TCP(Tape Carrier Package)又はCOF(Chip On Film)が利用される。これとは異なり、データ駆動チップ104は回路フィルム170を使用しないで液晶表示パネル130の薄膜トランジスタ基板上にCOG(Chip On Glass)方式で直接実装されてもよい。データ駆動チップ104は、タイミング制御部106からのデジタルデータをガンマ電圧部(図示せず)からのガンマ電圧を利用してアナログデータ信号に変換し、画像表示部108のゲートラインGL1～GLnが駆動される各水平期間に同期してデータラインDLにアナログデータ信号を供給する。

## 【0019】

PCB154に実装されたタイミング制御部106は、データ駆動チップ104並びに第1ゲート駆動部102及び第2ゲート駆動部112を制御する。タイミング制御部106からのデータ信号と複数のデータ制御信号はPCB154と回路フィルム170を経由して各データ駆動チップ104に供給され、複数のゲート制御信号はPCB154、回路フィルム170、及び液晶表示パネル130の薄膜トランジスタ基板110を経由して第1ゲート駆動部102及び第2ゲート駆動部112に供給される。

## 【0020】

液晶表示パネル130の画像表示部108は、赤(以下、Rという)、緑(以下、Gという)、青(以下、Bという)サブピクセルで構成された複数の画素がマトリクス状に配列されて画像を表示する。画像表示部108は、R、G、Bサブピクセル毎に薄膜トランジスタTFTが形成された薄膜トランジスタ基板110と、カラーフィルタが形成されたカラーフィルタ基板113とが液晶を介して貼り合わせられて形成される。R、G、Bサブピクセルは垂直方向に交互に繰り返し配列され、同じ色のサブピクセルは水平方向のストライプ状に配列される。画像表示部108にR、G、Bサブピクセルが垂直方向に配列されることにより、R、G、Bサブピクセルが水平方向に配列された液晶表示装置よりデータラインDL数が1/3に減少し、この結果データラインDL1～DLm(m=1以上の整数)を駆動するデータ駆動チップ104の数も減少する。つまり、従来の液晶パネルの場合、垂直方向に長い、例えば3つのサブ画素が水平方向に順に配置されるため、各サブ画素の画素電極にデータ電圧を供給するためには、3本のデータラインが必要である。一方、上記の本発明の構成によれば、サブ画素が3つの場合、水平方向に長いサブ画素が垂直方向に順に配置されるため、データラインを垂直方向に配置させることで、各サブ画素の画素電極に共通にデータ電圧を供給することができる。よって、従来よりもデータライン数を1/3に減らすことができる。

## 【0021】

ここで、R、G、Bサブピクセルの垂直方向配列にデータラインが減少した分だけゲートラインGLが増加して第1及び第2ゲート駆動部102、112のサイズが大きくなる

10

20

30

40

50

が、ゲート駆動部 102、112 の回路構成がデータ駆動チップ 104 より簡単なので製造コストは節減される。つまり、従来の液晶パネルの場合は水平方向に配置されるゲートライン GL により 3 つのサブ画素に共通にゲート電圧を供給可能であるが、上記本発明の構成によれば 3 つのサブ画素にゲート電圧を供給するには 3 本のゲートライン GL が必要となる。特に、ゲート駆動部 102、112 がアモルファスシリコン (Amorphous Silicon) 薄膜を利用した薄膜トランジスタ基板に内蔵されるので製造コストはさらに節減される。

#### 【0022】

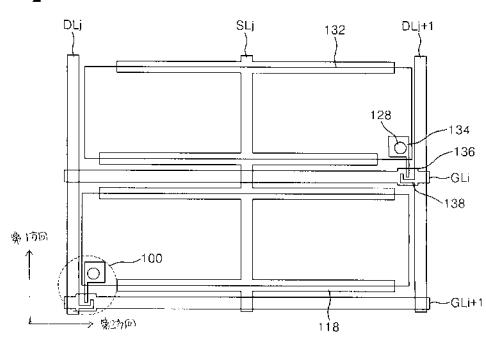

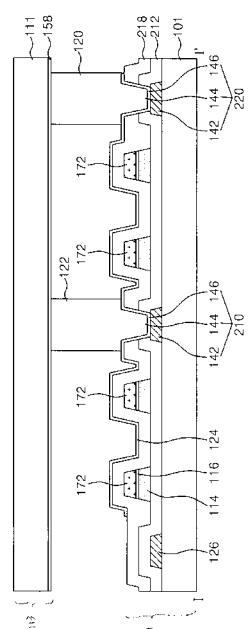

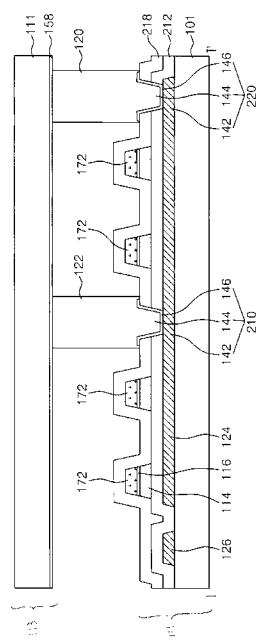

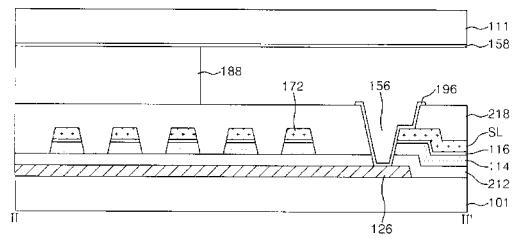

薄膜トランジスタ基板 110 は、図 2 に示すように、ゲートライン GL とデータライン DL の交差により定義されたサブピクセル領域に形成された画素電極 132 と、ゲートライン GL 及びデータライン DL と画素電極 132 間に接続された薄膜トランジスタ 100 とを含む。10

ゲートライン GL とデータライン DL は、ゲート絶縁膜 212 (図 4 A、図 4 B 参照) を介して交差するように絶縁基板上に形成される。ゲートライン GL とデータライン DL の交差構造により各サブピクセル領域が区分される。ストレージライン SL は、絶縁性の下部基板 101 (図 4 A、図 4 B 参照) 上にデータライン DL と並んで形成され、その幹部が各サブピクセルの中央部を短軸方向 (図 2 中、第 1 方向) に延在する。また、ストレージライン SL は、第 1 方向に延在する幹部から、図 2 に示すように第 2 方向に延在する枝部 118 を有している。20

#### 【0023】

図 2 に示すように、薄膜トランジスタ 100 は、下部基板 101 (図 4 A、図 4 B 参照) 上に、ゲートライン GL に含まれるゲート電極 136 と、データライン DL に接続されたソース電極 138 と、画素電極 132 に接続されたドレイン電極 134 と、ソース電極 138 及びドレイン電極 134 に接続された半導体層とを備える。例えば、ゲート電極 136 は下部基板 101 上に形成され、ゲート電極 136 上にはゲート絶縁膜 212 が形成され、ゲート絶縁膜 212 上に活性層 114 及びオーミック接触層 116 を含む半導体層が形成され、半導体層上にソース電極 138 及びドレイン電極 134 が形成される。また、ソース電極 138 及びドレイン電極 134 上には保護膜 218 が形成され、その上部に画素電極 132 が形成される。半導体層は、ソース電極 138 とドレイン電極 134 との間にチャネルを形成する活性層 114 と、活性層 114 とソース電極 138 及びドレイン電極 134 のそれぞれとのオーミック接触のためのオーミック接触層 116 とから構成される。このような半導体層は、データライン DL 及びストレージライン SL の下部にもさらに形成される。特に、上下に隣接する 2 つのサブピクセルにそれぞれ形成された薄膜トランジスタ 100 は、極性の異なる左右データライン DL にそれぞれ接続される。すなわち、データライン DL に接続された薄膜トランジスタ 100 の接続方向を垂直方向 (図 2 中、第 1 方向) に沿って順番に変わるようにする。例えば、奇数ゲートライン GL i に接続された奇数水平ラインの薄膜トランジスタ 100 は、データライン DL j + 1 の左側に位置する画素電極 132 に接続される。偶数ゲートライン GL i + 1 に接続された偶数水平ラインの薄膜トランジスタ 100 は、データライン DL j の右側に位置する画素電極 132 に接続される。これにより、各データライン DL j、DL j + 1 に供給されるデータ信号の極性が隣接するデータライン DL のデータ信号と異なり、フレーム単位でのみ反転しても画素電極 132 は水平及び垂直方向に隣接する画素電極 132 と異なる極性のデータ信号を充電してドット反転方式で駆動される。30

#### 【0024】

画素電極 132 は保護膜を貫通するコンタクトホール 128 を介して各薄膜トランジスタ 100 のドレイン電極 134 に接続される。画素電極 132 は、カラーフィルタ基板 113 の共通電極間に電界を形成し、これにより液晶分子が配列される。また、画素電極 132 は、ストレージライン SL と少なくとも一層の絶縁膜を介して重なってストレージキャパシタを形成する。このストレージキャパシタにより、画素電極 132 に充電されたデータ信号を安定して維持することができる。このようなストレージキャパシタを形成する40

ストレージライン S L は、各回路フィルム 170 の最左側に位置する出力パッドに接続された共通ストレージパッド 150 に接続されたストレージ供給ライン 126 を介して電源部 164 からのストレージ電圧が供給される（図 3 参照）。なお、下部基板 101 直上のストレージ供給ライン 126 と、ストレージライン S L とがゲート絶縁層 212 を挟んで配置されており、互いに図 3 のコンタクト 126a を介して電気的に接続されている。

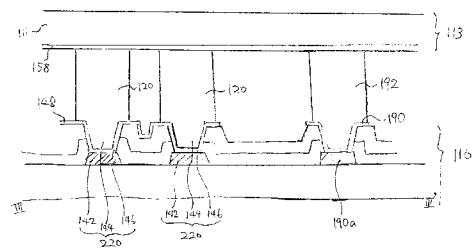

【0025】

図 4 A、図 4 B に示すように、画素電極 132 と共に液晶を駆動する共通電極は、カラーフィルタ基板 113 に形成される。図 4 A は図 3 の第 1 及び第 2 導電スペーサ部分の I-I' 線断面図、図 4 B は図 3 の第 1 及び第 2 導電スペーサ部分の I-I' 線断面図である。この共通電極 158 は上部基板 11 上に形成、図 3 及び図 4 に示すように、各回路フィルム 170 の最右側に位置する出力パッドに接続された共通電圧入力パッド 160、第 1 共通電圧供給ライン 148、第 1 共通電圧パッド 220、及び第 1 導電スペーサ 120 を経由して電源部 164 からの共通電圧が供給される。なお、導電スペーサは、導電性を有する物質から形成されている。ここで、第 1 共通電圧パッド 220 は異なるデータ駆動チップ 104 に接続されたデータファンアウトライン 172 間に形成される。このような第 1 共通電圧パッド 220 上には第 1 導電スペーサ 120 が形成される。なお、データファンアウトライン 172 とは、データ入力パッド 140 と、データライン DL とを接続するラインであり、データ駆動チップ 104 からのアナログデータ信号をデータライン DL に伝達する。

【0026】

また、共通電極 158 は、第 1 共通電圧パッド 220 に接続された第 2 共通電圧供給ライン 124、第 2 共通電圧パッド 210、及び第 2 導電スペーサ 122 を経由して電源部 164 からの共通電圧が供給される。第 2 共通電圧供給ライン 124 は、複数のデータライン DL に接続された複数のデータファンアウトライン 172 のそれぞれと交差するように形成される。このために、第 2 共通電圧供給ライン 124 はデータファンアウトライン 172 と異なる平面上に形成される。例えば、第 2 共通電圧供給ライン 124 は、図 4 A に示すように、パッド上部電極 146 と同一金属で保護膜 218 上に形成されるか、又は、図 4 B に示すように、パッド下部電極 142 と同一金属で下部基板 101 上に形成される。また、第 2 共通電圧供給ライン 124 は、隣接する各データファンアウトライン 172 と交差するように形成された第 2 共通電圧供給ライン 124 と互いに接続されるように形成されて共通電圧の遅延を防止する。

【0027】

第 2 共通電圧パッド 210 は、同一のデータ駆動チップ 104 に接続されたデータファンアウトライン 172 間に形成される。特に、第 2 共通電圧パッド 210 は、図 3 に示すように、同一のデータ駆動チップ 104 に接続されたデータファンアウトライン 172 のうち中央に位置するデータファンアウトライン 172 と隣接するように形成される。このような第 2 共通電圧パッド 210 上には第 2 導電スペーサ 122 が形成される。

【0028】

このような第 1 共通電圧パッド 220 及び第 2 共通電圧パッド 210 は、ゲートライン GL と同一金属で同一平面上に形成されたパッド下部電極 142 と、パッド下部電極 142 を覆うように形成されたゲート絶縁膜 212 及び保護膜 218 を貫通するパッドコンタクトホール 144 と、パッドコンタクトホール 144 によりパッド下部電極 142 に接続されたパッド上部電極 146 とを備える。なお、図 4 A ではパッド上部電極 146 は、第 2 共通電圧供給ライン 124 の一部であり、一方図 4 B ではパッド下部電極 142 は、第 2 共通電圧供給ライン 124 の一部である。

【0029】

このように、本発明による液晶表示装置は、データライン DL の数を減少させる構造において、データファンアウトライン 172 間に形成された第 2 共通電圧パッド 210 及び第 2 導電スペーサ 122 により共通電圧の歪みを補償できる。つまり、第 2 共通電圧供給ライン 124 を第 2 方向に配置し、複数の第 1 共通電圧パッド 220、複数の第 2 共通電

10

20

30

40

50

圧パッド 210、複数の第1導電スペースサ120、複数の第2導電スペースサ122等を介して、共通電極158に共通電圧が供給されている。このように回路フィルム170毎に、つまり各ユニットごとに共通電圧ラインから直に、共通電圧が共通電極158に供給されるため、データライン及び共通電極により例え寄生容量が発生したとしても、共通電極の共通電圧がスイングするリップル現象を弱め、クロストークを抑制することができる。

【0030】

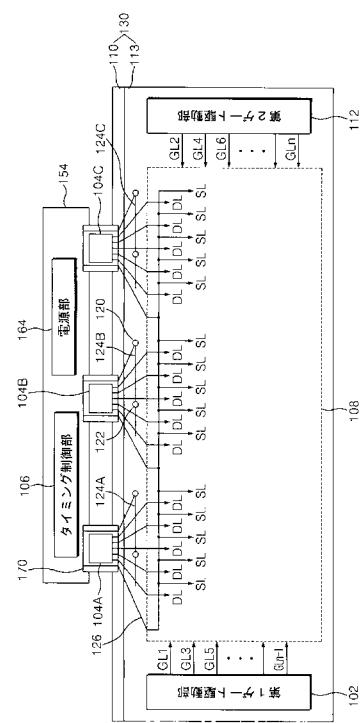

図5は本発明の第2実施形態による液晶表示装置を概略的に示す図である。

図5に示す液晶表示装置は、図1に示す液晶表示装置に比して、第2共通電圧供給ラインが各データ駆動チップ毎に区分されることを除いては同じ構成要素を備える。よって、同じ構成要素についての詳細な説明は省略する。

第2共通電圧供給ライン124は、複数のデータラインDLに接続された複数のデータファンアウトライン172のそれぞれと交差するように形成される。ここで、第2共通電圧供給ライン124は、データ駆動チップ104に接続されたデータファンアウトライン172毎に互いに分離されるように形成される。例えば、第1～第3データ駆動チップ104A、104B、104Cのそれぞれに接続されたデータファンアウトライン172と交差するように形成された第2共通電圧供給ライン124A、124B、124Cは、互いに分離されるように形成される。この場合、第1～第3データ駆動チップ104A、104B、104Cのいずれか1つに接続されたデータファンアウトライン172と第2共通電圧供給ライン124間に並列に接続された寄生容量の総容量値は、図2に示すデータファンアウトライン172の全てと第2共通電圧ライン124間に並列に接続された寄生容量の総容量値より小さい。これにより、データファンアウトライン172のRC遅延差が除去され、データ信号の偏差を減らすことができる。

【0031】

また、第2共通電圧供給ライン124がデータ駆動チップ104毎に分離されることにより、データ駆動チップ104毎に異なる共通電圧を供給できる。これにより、位置によって共通電極158の歪みの程度に差が発生した場合、歪みの程度に応じて位置に対応した異なる共通電圧を供給する。

このように、本発明による液晶表示装置は、データラインDLの数を減少させる構造において、データファンアウトライン172間に形成された第2共通電圧パッド210及び第2導電スペースサ122により共通電圧の歪みを補償できる。また、本発明による液晶表示装置は、データ駆動チップ毎に第2共通電圧供給ラインが分離されることにより、データ駆動チップ毎に異なる共通電圧を供給し、共通電圧の歪みに応じて最適に制御することができる。

【0032】

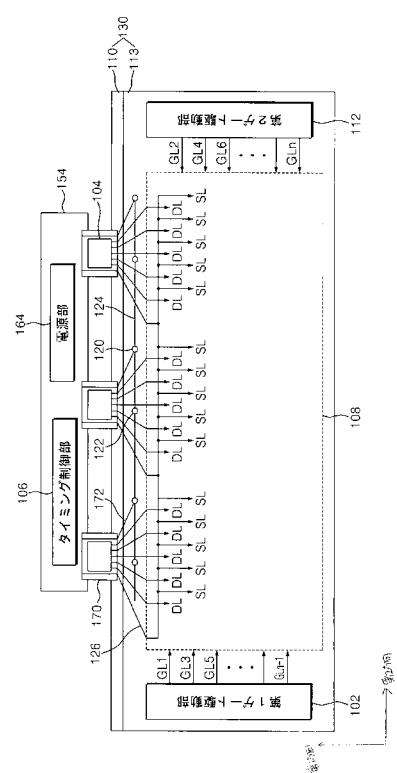

図6は本発明の第3実施形態による液晶表示装置を概略的に示す図である。

図6に示すように、本発明の第3実施形態による液晶表示装置は、図5に示す液晶表示装置に比して、ストレージ供給ラインが各データ駆動チップ毎に区分されることを除いては同じ構成要素を備える。よって、同じ構成要素についての詳細な説明は省略する。

ストレージ供給ライン126は、複数のデータラインDLと交差するように形成され、データ駆動チップ104毎に互いに分離されるように形成される。例えば、第1～第3データ駆動チップ104A、104B、104Cのそれぞれに対応する第1～第3ストレージ供給ライン126A、126B、126Cは、互いに分離されるように形成される。互いに分離された第1～第3ストレージ供給ライン126A、126B、126Cのそれぞれは、該当ストレージ供給ライン126A、126B、126Cに接続されたストレージラインSLに、独立してストレージ電圧を供給する。ここで、第1～第3ストレージ供給ライン126A、126B、126Cのそれぞれは、画像表示部108の位置によってストレージ電圧に偏差が発生した場合、該当ストレージラインSL毎に異なるストレージ電圧を供給する。

【0033】

このように、本発明による液晶表示装置は、データラインDLの数を減少させる構造に

10

20

30

40

50

おいて、データファンアウトライン 172 間に形成された第 2 共通電圧パッド 210 及び第 2 導電スペースサ 122 により共通電圧の歪みを補償できる。また、本発明による液晶表示装置は、データ駆動チップ毎に第 2 共通電圧供給ラインが分離されることにより、データ駆動チップ毎に異なる共通電圧を供給し、共通電圧の歪みに応じて最適に制御することができる。それだけでなく、本発明による液晶表示装置は、データ駆動チップ毎にストレージ供給ラインが分離されることにより、位置によるストレージ電圧の偏差に応じて異なるストレージ電圧を供給できる。

#### 【0034】

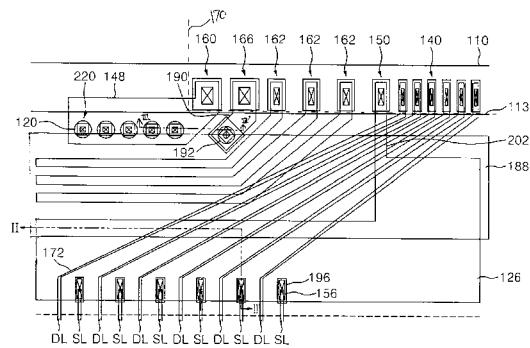

図 7 は本発明の第 4 実施形態による液晶表示装置を概略的に示す図、図 8 A は 8 は図 7 の A 部分を拡大した平面図、図 8 B は図 8 A の液晶表示装置の I I I - I I I ' 線断面図、図 9 は図 8 A の液晶表示装置の I I - I I ' 線断面図である。

図 7 に示すように、本発明の第 4 実施形態による液晶表示装置は、共通電圧をフィードバックして共通電圧の歪みの程度によってその共通電圧の逆位相となる信号をストレージラインに印加することにより、データ信号の電位変動を最小化する構造である。このために、本発明の第 4 実施形態による液晶表示装置は、図 2 に示す液晶表示装置に比して、共通電圧を共通電極に供給する共通電圧パッドと、その共通電圧パッドと隣接するように形成されたフィードバックスペースサ及びラインと、共通電圧の歪みの程度によって逆位相信号をストレージラインに供給するストレージ供給ラインとを除いては同じ構成要素を備える。よって、同じ構成要素についての詳細な説明は省略する。

#### 【0035】

図 8 A に示すように、共通電圧供給ライン 148 は、共通電圧パッド 220 と、回路フィルム 170 に接続された共通電圧入力パッド 160 とを最短距離で接続させる。この共通電圧供給ライン 148 は、他のラインに比べて相対的に大きな幅に形成されて共通電圧供給ライン 148 自体のライン抵抗を減少させる。これにより、共通電圧供給ライン 148 の自体の抵抗が減少することにより、共通電極 158 に供給される共通電圧の偏差を最小化できる。ここで、共通電圧パッド 220 は、前述の図 3、図 4 A、図 4 B 等と同様に、例えば図 8 B に示すようにパッド下部電極 142、パッド下部電極 142 を覆うように形成されたゲート絶縁膜 212 及び保護膜 218 を貫通するパッドコンタクトホール 144 と、パッドコンタクトホール 144 によりパッド下部電極 142 に接続されたパッド上部電極 146 とを備える。図 8 B では、パッド上部電極 146 が、共通電圧入力パッド 160 から共通電圧が印加される共通電圧供給ライン 148 の一部を構成している。よって、共通電極 158 には、共通電圧入力パッド 160、共通電圧供給ライン 148、複数の共通電圧パッド 220、及び複数の第 1 導電スペースサ 120 を経由して電源部 164 からの共通電圧が供給される。

#### 【0036】

フィードバックスペースサ 192 は、ゲートパッド 162 と隣接するように形成されたフィードバックパッド 166 及びフィードバックライン 190 を介して回路フィルム 170 に接続され、第 1 導電スペースサ 120 と隣接するように形成されており、第 1 導電スペースサ 120 を介して共通電極 158 に印加された共通電圧をフィードバックする。つまり、図 8 B に示すように、フィードバックスペースサ 192 が共通電極 158 から共通電圧の入力を受け、パッド下部電極 190 a 及びフィードバックライン 190 を介して、フィードバックパッド 166 に共通電圧をフィードバックする。このような第 1 導電スペースサ 120 及びフィードバックスペースサ 192 は、同一の回路フィルム 170 の一方に隣接するように形成される。

#### 【0037】

ストレージ供給ライン 126 は合着剤 188 と重なるように形成され、ストレージ供給ライン 126 の幅が相対的に広くなる。例えば、ストレージ供給ライン 126 の幅は約 4 ~ 6 mm に形成される。これにより、ストレージ供給ライン 126 自体の抵抗が減少するので、ストレージライン S L に供給されるストレージ電圧の偏差を最小化できる。ここで、ストレージ供給ライン 126 とストレージ供給パッド 150 を最短距離で接続するため

10

20

30

40

50

に、これらを接続させるストレージ接続ライン 202 は直線状に形成される。なお、合着剤 188 は、薄膜トランジスタ基板 110 とカラーフィルタ基板 113 とを合着させるための接着剤である。

【0038】

一方、ストレージ供給ライン 126 は、図 9 に示すように、ゲートライン GL と同一金属で下部基板 101 上に形成され、データファンアウトライン 172 はデータライン DL と同一金属でゲート絶縁膜 212 上にストレージ供給ライン 126 を横切るように形成される。ストレージライン SL は、データライン DL と同一金属でゲート絶縁膜 212 上に形成される。このようなストレージライン SL とストレージ供給ライン 126 は、保護膜 218 及びゲート絶縁膜 212 を貫通する接続コンタクトホール 156 を介して露出される。露出したストレージライン SL 及びストレージ供給ライン 126 は、接続電極 196 を介して互いに接続される。

【0039】

データファンアウトライン 172 上に形成された保護膜 218 は、合着剤 188 に伝達された圧力を緩衝することのできる厚い有機膜で約 2  $\mu$ m 以上に形成される。これは液晶表示パネル 130 に所定の圧力が加えられると、その圧力がグラスファイバなどからなる合着剤 188 に伝達されて合着剤 188 下部に位置するストレージ供給ライン 126 及びデータファンアウトライン 172 間の短絡現象が発生するためである。それ以外にも、外部からの衝撃によるデータファンアウトライン 172 とストレージ供給ライン 126 間の短絡現象を防止するために、合着剤 188 は弾力を有するソフトスペーサが含まれる材質で形成される。

【0040】

このように、本発明による液晶表示装置は、合着剤と重なって相対的に大きな幅を有するようにストレージ供給ラインが形成される。これにより、本発明による液晶表示装置は、ストレージ供給ライン自体のライン抵抗が減少するので、ストレージ電圧の偏差を最小化できる。

前述したように、本発明による液晶表示装置は、データラインの数を減少させる構造において、データファンアウトライン間に形成された共通電圧パッド及び導電スペーサにより共通電圧の歪みを補償できる。また、本発明による液晶表示装置は、データラインの数を減少させる構造において、合着剤と重なって相対的に大きな幅を有するストレージ供給ラインにより、ストレージ電圧の偏差を最小化できる。

【0041】

以上、説明した内容により、当業者であれば本発明の技術思想を逸脱しない範囲で多様な変更及び修正が可能であることを理解するであろう。従って、本発明の技術的範囲は明細書の詳細な説明に記載された内容に限定されるのではなく、特許請求の範囲により定義されるべきである。

【産業上の利用可能性】

【0042】

本発明は、クロストークを防止して画質を向上させることができるため、各種表示装置に適用可能である。

【図面の簡単な説明】

【0043】

【図 1】本発明の第 1 実施形態による液晶表示装置を概略的に示す図である。

【図 2】図 1 に示す液晶表示装置の薄膜トランジスタ基板における 2 つのサブピクセルを示す平面図である。

【図 3】図 1 に示す液晶表示装置における回路フィルムと第 1 及び第 2 導電スペーサに接続されるパッドとを示す平面図である。

【図 4 A】図 3 の第 1 及び第 2 導電スペーサ部分の I - I' 線断面図である。

【図 4 B】図 3 の第 1 及び第 2 導電スペーサ部分の I - I' 線断面図である。

【図 5】本発明の第 2 実施形態による液晶表示装置を概略的に示す図である。

10

20

30

40

50

【図6】本発明の第3実施形態による液晶表示装置を概略的に示す図である。

【図7】本発明の第4実施形態による液晶表示装置を概略的に示す図である。

【図8A】図7のA部分を拡大した平面図である。

【図8B】図8Aの液晶表示装置のI—I—I—I—I’線断面図である。

【図9】図8Aの液晶表示装置のI—I—I—I’線断面図である。

【符号の説明】

【0044】

|              |     |           |     |

|--------------|-----|-----------|-----|

| 薄膜トランジスタ     | 100 |           |     |

| 下部基板         | 101 |           |     |

| 第1ゲート駆動部     | 102 | 10        |     |

| 第2ゲート駆動部     | 112 |           |     |

| 第3データ駆動チップ   | 104 |           |     |

| タイミング制御部     | 106 |           |     |

| 画像表示部        | 108 |           |     |

| 薄膜トランジスタ基板   | 110 |           |     |

| カラーフィルタ基板    | 113 |           |     |

| 活性層          | 114 |           |     |

| オーム接触層       | 116 |           |     |

| 第1導電スペーサ     | 120 |           |     |

| 第2導電スペーサ     | 122 | 20        |     |

| 第2共通電圧供給ライン  | 124 |           |     |

| ストレージ供給ライン   | 126 |           |     |

| 液晶表示パネル      | 130 |           |     |

| 画素電極         | 132 |           |     |

| ドレイン電極       | 134 |           |     |

| ゲート電極        | 136 |           |     |

| ソース電極        | 138 |           |     |

| データ入力パッド     | 140 |           |     |

| パッド下部電極      | 142 |           |     |

| パッド上部電極      | 146 | 30        |     |

| 共通電圧供給ライン    | 148 |           |     |

| PCB          | 154 |           |     |

| 共通電極         | 158 |           |     |

| 共通電圧入力パッド    | 160 |           |     |

| 電源部          | 164 |           |     |

| フィードバックパッド   | 166 |           |     |

| 回路フィルム       | 170 |           |     |

| データファンアウトライン | 172 |           |     |

| 合着剤          | 188 |           |     |

| フィードバックライン   | 190 | 40        |     |

| フィードバックスペーサ  | 192 | 第2共通電圧パッド | 210 |

| ゲート絶縁層       | 212 |           |     |

| 保護膜          | 218 |           |     |

| 第1共通電圧パッド    | 220 |           |     |

【図1】

【図2】

【図3】

【図4A】

【 図 4 B 】

【 四 5 】

【図6】

【 四 7 】

【 図 8 A 】

【図8B】

【図9】

---

フロントページの続き

(72)発明者 金 東 奎

大韓民国京畿道龍仁市風德川2洞三星5次アパート523棟1305号

Fターム(参考) 2H092 GA29 GA39 GA41 GA46 JA24 JB13 JB23 JB32 PA03

5C094 AA09 BA03 BA43 DA09 DB01 EA10

|                |                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2007213063A</a>                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2007-08-23 |

| 申请号            | JP2007023473                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2007-02-01 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 張鐘雄<br>金東奎                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 发明人            | 張 鐘 雄<br>金 東 奎                                                                                                                                                                                                                                                                                                                                                             |         |            |

| IPC分类号         | G02F1/1368 G02F1/1345 G09F9/30                                                                                                                                                                                                                                                                                                                                             |         |            |

| CPC分类号         | G02F1/136286 G02F1/1345 G02F1/1362 G02F1/136213 G02F1/1368 G02F2201/123                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G02F1/1368 G02F1/1345 G09F9/30.338 G09F9/30.330.Z G09F9/30.330                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 2H092/GA29 2H092/GA39 2H092/GA41 2H092/GA46 2H092/JA24 2H092/JB13 2H092/JB23 2H092/JB32 2H092/PA03 5C094/AA09 5C094/BA03 5C094/BA43 5C094/DA09 5C094/DB01 5C094/EA10 2H192/AA24 2H192/BC01 2H192/BC31 2H192/CB05 2H192/CC04 2H192/DA12 2H192/DA71 2H192/FA15 2H192/FA22 2H192/FA26 2H192/FA35 2H192/FA37 2H192/FA44 2H192/FA76 2H192/FB46 2H192/FB52 2H192/GA42 2H192/GD61 |         |            |

| 优先权            | 1020060011110 2006-02-06 KR                                                                                                                                                                                                                                                                                                                                                |         |            |

| 其他公开文献         | JP2007213063A5<br>JP4960716B2                                                                                                                                                                                                                                                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                  |         |            |

### 摘要(译)

要解决的问题：提供一种能够通过防止串扰来改善图像质量的液晶显示装置。 ŹSOLUTION：液晶显示装置包括：第一基板上的公共电极；栅极线和数据线形成为在跨越液晶的与第一基板相对的第二基板上彼此交叉；薄膜晶体管连接到栅极线和数据线；像素电极形成在子像素区域中，每个像素电极具有在栅极线方向上的长边和在数据线方向上的短边并连接到薄膜晶体管；驱动芯片制作在电路薄膜上并驱动数据线；扇形线用于从驱动芯片向数据线提供驱动信号；第一导电间隔物形成在连接到不同驱动芯片的扇出线之间，用于向公共电极提供公共电压；第二导电垫片形成在连接到同一驱动芯片的扇出线之间，用于将公共电压提供给公共电极。 Ź