(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-86791

(P2007-86791A)

(43) 公開日 平成19年4月5日(2007.4.5)

| (51) Int.CI.                 | F 1            | テーマコード (参考) |

|------------------------------|----------------|-------------|

| <b>G02F 1/1343 (2006.01)</b> | G02F 1/1343    | 2H092       |

| <b>G02F 1/133 (2006.01)</b>  | G02F 1/133 575 | 2H093       |

| <b>G02F 1/1368 (2006.01)</b> | G02F 1/133 550 | 5C006       |

| <b>G09G 3/36 (2006.01)</b>   | G02F 1/1368    | 5C080       |

| <b>G09G 3/20 (2006.01)</b>   | G09G 3/36      |             |

審査請求 未請求 請求項の数 54 O L (全 26 頁) 最終頁に続く

|              |                              |          |                                                                                  |

|--------------|------------------------------|----------|----------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2006-258289 (P2006-258289) | (71) 出願人 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区梅灘洞416 |

| (22) 出願日     | 平成18年9月25日 (2006.9.25)       | (74) 代理人 | 100094145<br>弁理士 小野 由己男                                                          |

| (31) 優先権主張番号 | 10-2005-0088460              | (74) 代理人 | 100106367<br>弁理士 稲積 朋子                                                           |

| (32) 優先日     | 平成17年9月23日 (2005.9.23)       | (72) 発明者 | 申 ▲キヨン▼ 周<br>大韓民国京畿道華城市台安邑半月里新靈通<br>現代1次アパート105棟1102号                            |

| (33) 優先権主張国  | 韓国(KR)                       | (72) 発明者 | チャン ハク ソン<br>大韓民国京畿道龍仁市豊徳川洞ドンブアパ<br>ート103棟203号                                   |

最終頁に続く

(54) 【発明の名称】 液晶パネル、その駆動方法、及びそれを用いた液晶表示装置

## (57) 【要約】

【課題】マルチ - ドメインVAモードで側面視認性とサブ画素の光透過率をいずれも向上できる液晶パネルとその駆動方法とを提供する。

【解決手段】本発明による液晶パネルでは、各サブ画素が上下に分割され、面積の異なる第1階調領域と第2階調領域とに分割されている。各階調領域の両辺は水平方向に対して対称に折れ曲がっている。第1階調領域と第2階調領域とは水平方向と上下方向とのそれぞれで交互に配列され、特に各階調領域の折れ曲がり部分の頂点が水平方向に配列されている。それにより、上下方向に並ぶ階調領域の境界線がジグザグ模様を成す。そのように上下方向から斜めに傾いた階調領域の境界線により、サブ画素間に生じる側面電界の方向が各サブ画素のドメイン内のフリンジ電界の方向に揃う。複数のゲートラインの一つが駆動されるときに第1階調領域が駆動され、ゲートラインの別の一つが駆動されるときに第2階調領域が駆動される。

【選択図】図9

**【特許請求の範囲】****【請求項 1】**

それが面積の異なる第1階調領域と第2階調領域とに分割された複数のサブ画素であり、水平方向で隣接した二つのサブ画素間では第1階調領域と第2階調領域とが上下方向で反対に配列された複数のサブ画素。

サブ画素の第1階調領域と第2階調領域とを独立に駆動する複数の薄膜トランジスタ、前記薄膜トランジスタに接続され、サブ画素の第1階調領域には第1データ信号を供給し、第2階調領域には第2データ信号を供給する複数のデータライン、及び、前記薄膜トランジスタを水平同期期間単位で駆動するゲートライン、を具備する液晶パネル。

10

**【請求項 2】**

サブ画素の第1階調領域と第2階調領域とがV字形であり、各V字形の頂点が水平方向に配列され、前記第1階調領域と前記第2階調領域とのそれぞれの両辺が水平方向に対し対称に折れ曲がっている、請求項1に記載の液晶パネル。

**【請求項 3】**

前記複数のゲートラインの一つが前記第1階調領域と前記第2階調領域との各V字形の頂点に重なり、前記複数のゲートラインの別の一つが、上下方向で隣接する二つのサブ画素間の境界部と重なっている、請求項2に記載の液晶パネル。

20

**【請求項 4】**

前記液晶パネルが、前記境界部と重なっているストレージライン、を更に具備し、前記ストレージラインに近接し、又は重なっている接続部によって前記薄膜トランジスタがサブ画素の第1階調領域と第2階調領域とのそれぞれの画素電極に接続された、請求項3に記載の液晶パネル。

**【請求項 5】**

同じサブ画素に含まれる第1階調領域と第2階調領域との間の面積比率が(1.5~3):1である、請求項1に記載の液晶パネル。

30

**【請求項 6】**

それが面積の異なる第1階調領域と第2階調領域とに分割された複数のサブ画素であり、水平方向で隣接する二つのサブ画素間では第1階調領域と第2階調領域とが上下方向で反対に配列された複数のサブ画素。

40

サブ画素の第1階調領域と第2階調領域とを独立に駆動する複数の薄膜トランジスタ、前記薄膜トランジスタに接続され、サブ画素の第1階調領域には第1データ信号を供給し、第2階調領域には第2データ信号を供給する複数のデータライン、及び、前記薄膜トランジスタを水平同期期間単位で駆動するゲートライン、

を具備する液晶パネル、を駆動する方法であり、

ルックアップテーブルを用いて入力データ信号を前記第1データ信号と前記第2データ信号とに変調する段階、

前記第1データ信号と前記第2データ信号とを交互に出力する段階、

ガンマ電圧を用いて前記第1データ信号と前記第2データ信号とを交互にアナログ信号に変換する段階、及び、

アナログ信号に変換された前記第1データ信号と前記第2データ信号とを水平同期期間ごとに交互に前記複数のデータラインのそれぞれに同期して供給する段階、

を含む、液晶パネルの駆動方法。

**【請求項 7】**

サブ画素の第1階調領域と第2階調領域とがV字形であり、各V字形の頂点が水平方向に配列され、前記第1階調領域と前記第2階調領域とのそれぞれの両辺が水平方向に対し対称に折れ曲がっている、請求項6に記載の液晶パネルの駆動方法。

**【請求項 8】**

同じサブ画素に含まれる第1階調領域と第2階調領域との間の面積比率が(1.5~3):1である、請求項6に記載の液晶パネルの駆動方法。

50

**【請求項 9】**

それが面積の異なる第1階調領域と第2階調領域とに分割された複数のサブ画素であり、水平方向で隣接する二つのサブ画素間では第1階調領域と第2階調領域とが上下方向で反対に配列された複数のサブ画素、

サブ画素の第1階調領域と第2階調領域とを独立に駆動する複数の薄膜トランジスタ、前記薄膜トランジスタに接続され、サブ画素の第1階調領域には第1データ信号を供給し、第2階調領域には第2データ信号を供給する複数のデータライン、及び、前記薄膜トランジスタを水平同期期間単位で駆動するゲートライン、

を有する液晶パネル；

前記複数のゲートラインを駆動するゲートドライバ；

10

前記複数のデータラインを駆動するデータドライバ；並びに、

前記ゲートドライバと前記データドライバとを制御し、外部から入力されたデータ信号を前記第1データ信号と前記第2データ信号とに変調して前記データドライバに供給するタイミングコントローラ；

を具備する液晶表示装置。

**【請求項 10】**

サブ画素の第1階調領域と第2階調領域とがV字形であり、各V字形の頂点が水平方向に配列され、前記第1階調領域と前記第2階調領域とのそれぞれの両辺が水平方向に対し対称に折れ曲がっている、請求項9に記載の液晶表示装置。

**【請求項 11】**

外部から入力されるデータ信号を第1データ信号と第2データ信号との間に予め対応させたルックアップテーブル、を用いて前記タイミングコントローラが前記データ信号を前記第1データ信号と前記第2データ信号との間に変調し、水平同期期間ごとに前記第1データ信号と前記第2データ信号とを交互に出力する、請求項9に記載の液晶表示装置。

20

**【請求項 12】**

同じサブ画素に含まれる第1階調領域と第2階調領域との間の面積比率が(1.5~3)：1である、請求項9に記載の液晶表示装置。

**【請求項 13】**

前記複数のゲートラインの一つが駆動されるとき、前記薄膜トランジスタがサブ画素の第1階調領域を駆動し、前記複数のゲートラインの別の一つが駆動されるとき、前記薄膜トランジスタが前記サブ画素の第2階調領域を駆動する、請求項1に記載の液晶パネル。

30

**【請求項 14】**

同じサブ画素に含まれる第1階調領域と第2階調領域とがV字形であり、各V字形の頂点が水平方向に配列され、前記第1階調領域と前記第2階調領域との両辺が水平方向に対し対称に折れ曲がっている、請求項13に記載の液晶パネル。

**【請求項 15】**

上下方向に隣接した第1階調領域と第2階調領域との間の境界部に重なっているストレージライン、を前記液晶パネルが更に具備し、

前記複数のゲートラインの一つ（以下、第1ゲートラインという）は前記第1階調領域と前記第2階調領域とのそれぞれのV字形の頂点に重なり、前記複数のゲートラインの別の一つ（以下、第2ゲートラインという）は前記境界部に重なっている、

40

請求項14に記載の液晶パネル。

**【請求項 16】**

前記第1ゲートラインに接続された薄膜トランジスタは、前記ストレージラインの上下に位置する第1階調領域のそれぞれに接続され、

前記第2ゲートラインに接続された薄膜トランジスタは、前記ストレージラインの上下に位置する第2階調領域のそれぞれに接続されている、

請求項15に記載の液晶パネル。

**【請求項 17】**

前記薄膜トランジスタのドレイン電極が前記ストレージラインに向かって延び、そのス

50

トレージラインと近接し、又は重なっているコンタクト部を介して第1階調領域又は第2階調領域に接続されている、請求項16に記載の液晶パネル。

【請求項18】

前記第1ゲートラインに接続された薄膜トランジスタと前記第1階調領域との間のコンタクト部は前記ストレージラインに沿ってそのストレージラインの上下に交互に位置し、

前記第2ゲートラインに接続された薄膜トランジスタと前記第2階調領域との間のコンタクト部は前記ストレージラインに沿ってそのストレージラインの上下に交互に位置する

、

請求項16に記載の液晶パネル。

【請求項19】

一つのサブ画素に含まれた第1階調領域と第2階調領域とのそれぞれに接続された二つの薄膜トランジスタが、互いに隣接した二つのデータラインのそれぞれに接続されている、請求項18に記載の液晶パネル。

【請求項20】

前記第1ゲートラインに接続された薄膜トランジスタは前記二つのデータラインの一方に接続され、前記第2ゲートラインに接続された薄膜トランジスタは前記二つのデータラインの他方に接続されている、請求項19に記載の液晶パネル。

【請求項21】

前記複数のゲートラインのそれぞれが、上下方向で隣接した第1階調領域と第2階調領域との間の境界部に重なり、

第1階調領域と第2階調領域とのそれぞれのV字形の頂点に重なっているストレージライン、を前記液晶パネルが更に具備する、

請求項14に記載の液晶パネル。

【請求項22】

前記複数のゲートラインの一つ（以下、第1ゲートラインという）に接続された薄膜トランジスタはその第1ゲートラインの上下に位置する第1階調領域のそれぞれに接続され

、

前記複数のゲートラインの別の一つ（以下、第2ゲートラインという）に接続された薄膜トランジスタはその第2ゲートラインの上下に位置する第2階調領域のそれぞれに接続されている、

請求項21に記載の液晶パネル。

【請求項23】

前記第1階調領域は前記第1ゲートラインに沿って前記第1ゲートラインの上下に交互に配列され、前記第2階調領域は前記第2ゲートラインに沿って前記第2ゲートラインの上下に交互に配列されている、請求項22に記載の液晶パネル。

【請求項24】

水平方向で隣接した第1階調領域と第2階調領域とでは、前記第1ゲートラインと前記第2ゲートラインとのそれぞれに接続された薄膜トランジスタが上下方向で反対に位置する、請求項22に記載の液晶パネル。

【請求項25】

前記第1ゲートラインに接続された薄膜トランジスタと前記第1階調領域との間のコンタクト部がその第1ゲートラインに沿ってその第1ゲートラインの上下に交互に位置し、

前記第2ゲートラインに接続された薄膜トランジスタと前記第2階調領域との間のコンタクト部がその第2ゲートラインに沿ってその第2ゲートラインの上下に交互に位置する

、

請求項22に記載の液晶パネル。

【請求項26】

薄膜トランジスタと第1階調領域又は第2階調領域との間のコンタクト部は、前記ストレージラインに重なっている、請求項25に記載の液晶パネル。

【請求項27】

10

20

30

40

50

一つのサブ画素に含まれた第1階調領域と第2階調領域とのそれぞれに接続された二つの薄膜トランジスタが、互いに隣接した二つのデータラインのそれぞれに接続されている、請求項22に記載の液晶パネル。

**【請求項28】**

同じサブ画素に含まれる第1階調領域と第2階調領域との間の面積比率が(1.5~3):1である、請求項13に記載の液晶パネル。

**【請求項29】**

第1ガンマ曲線に基づく第1データ信号が供給される第1階調領域と、第2ガンマ曲線に基づく第2データ信号が供給される第2階調領域と、前記第2階調領域に接続された第3階調領域と、を有するサブ画素、

10

前記第1階調領域を駆動する第1薄膜トランジスタ、

前記第2階調領域と前記第3階調領域とを駆動する第2薄膜トランジスタ、

前記第1薄膜トランジスタと前記第2薄膜トランジスタとに接続され、それぞれに前記第1データ信号と前記第2データ信号とを供給するデータライン、

前記第1薄膜トランジスタを駆動する第1ゲートライン、及び、

前記第2薄膜トランジスタを駆動する第2ゲートライン、

を具備する液晶パネル。

**【請求項30】**

サブ画素のそれでは、第1階調領域が第1ゲートラインの上に位置し、第2階調領域と第3階調領域とのいずれか一つ又は両方が同じ第1ゲートラインの下に位置する、請求項29に記載の液晶パネル。

20

**【請求項31】**

水平方向で隣接した二つのサブ画素の一方では第2階調領域と第3階調領域とが第1ゲートラインの下に位置し、前記二つのサブ画素の他方では第2階調領域と第3階調領域とが同じ第1ゲートラインの上下に分かれて位置している、請求項30記載の液晶パネル。

**【請求項32】**

同じサブ画素に含まれる第1階調領域と第2階調領域との間の面積比率が(1.5~3):1である、請求項31に記載の液晶パネル。

**【請求項33】**

第1乃至第3階調領域のそれぞれの両辺が水平方向に対して対称に折れ曲がっている、

30 請求項30に記載の液晶パネル。

**【請求項34】**

上下方向で隣接した二つのサブ画素間の境界部に重なっているストレージライン、を前記液晶パネルが更に具備し、

前記第1薄膜トランジスタと前記第1階調領域との間のコンタクト部、及び、前記第2薄膜トランジスタと前記第2階調領域又は前記第3階調領域との間のコンタクト部、が前記ストレージラインに重なっている、

請求項33に記載の液晶パネル。

**【請求項35】**

第1ガンマ曲線に基づいて第1ガンマ電圧セットを生成する段階、

40 第2ガンマ曲線に基づいて第2ガンマ電圧セットを生成する段階、

水平同期期間ごとに、第1ガンマ電圧セットと第2ガンマ電圧セットとのいずれか一つを選択する段階、及び、

選択されたガンマ電圧セットを用い、外部から入力されたデータ信号を水平同期期間ごとに、サブ画素の第1階調領域に供給されるべき第1データ信号、または、同じサブ画素の第2階調領域に供給されるべき第2データに変換してデータラインに供給する段階、

を含む、液晶パネルの駆動方法。

**【請求項36】**

それが面積の異なる第1階調領域と第2階調領域とに分割された複数のサブ画素であり、水平方向で隣接した二つのサブ画素間では第1階調領域と第2階調領域とが上下方

50

向で反対に配列された複数のサブ画素、

サブ画素の第1階調領域と第2階調領域とを独立に駆動する複数の薄膜トランジスタ、

前記薄膜トランジスタに接続され、サブ画素の第1階調領域には第1データ信号を供給し、第2階調領域には第2データ信号を供給する複数のデータライン、及び、

前記薄膜トランジスタを水平同期期間単位で駆動する複数のゲートライン、

を液晶パネルが具備し；

前記複数のゲートラインの一つが駆動されるとき、前記薄膜トランジスタがサブ画素の第1階調領域を駆動し、前記複数のゲートラインの別の一つが駆動されるとき、前記薄膜トランジスタが前記サブ画素の第2階調領域を駆動する；

請求項35に記載の液晶パネルの駆動方法。

10

#### 【請求項37】

第1階調領域と第2階調領域とがV字形であり、各V字形の頂点が水平方向に配列され、第1階調領域と第2階調領域とのそれぞれの両辺が水平方向に対して対称に折れ曲がっている、請求項36に記載の液晶パネルの駆動方法。

#### 【請求項38】

前記複数のゲートラインの一つに接続された薄膜トランジスタが一つのストレージラインの上下に位置した第1階調領域のそれぞれに接続され、

前記複数のゲートラインの別の一つに接続された薄膜トランジスタが前記ストレージラインの上下に位置した第2階調領域のそれぞれに接続されている、

請求項37に記載の液晶パネルの駆動方法。

20

#### 【請求項39】

一つのサブ画素に含まれた第1階調領域と第2階調領域とのそれぞれに接続された薄膜トランジスタが、互いに隣接した二つのデータラインのそれぞれに接続されている、請求項37に記載の液晶パネルの駆動方法。

#### 【請求項40】

同じサブ画素に含まれる第1階調領域と第2階調領域との間の面積比率が(1.5~3)：1である、請求項36に記載の液晶パネルの駆動方法。

#### 【請求項41】

液晶パネルが、

第1ガンマ曲線に基づく第1データ信号が供給される第1階調領域と、第2ガンマ曲線に基づく第2データ信号が供給される第2階調領域と、前記第2階調領域に接続された第3階調領域とを具備するサブ画素、

30

前記第1階調領域を駆動する第1薄膜トランジスタ、

前記第2階調領域と前記第3階調領域とを駆動する第2薄膜トランジスタ、

前記第1薄膜トランジスタと前記第2薄膜トランジスタとに接続され、それぞれに前記第1データ信号と前記第2データ信号とを供給するデータライン、

前記第1薄膜トランジスタを駆動する第1ゲートライン、及び、

前記第2薄膜トランジスタを駆動する第2ゲートライン、

を具備する、請求項35に記載の液晶パネルの駆動方法。

#### 【請求項42】

サブ画素のそれぞれでは、前記第1薄膜トランジスタに接続された第1階調領域が第1ゲートラインの上に位置し、前記第2薄膜トランジスタに接続された第2階調領域と第3階調領域とのいずれか一つ又は両方が同じ第1ゲートラインの下に位置し、

水平方向で隣接する二つのサブ画素の一方では、第2階調領域と第3階調領域とが第1ゲートラインの下に位置し、前記二つのサブ画素の他方では、第2階調領域と第3階調領域とが前記第1ゲートラインの上下に分かれて位置している、

請求項41に記載の液晶パネルの駆動方法。

40

#### 【請求項43】

同じサブ画素に含まれる第2階調領域と第3階調領域との間の面積比率が(1.5~3)：1である、請求項42に記載の液晶パネルの駆動方法。

50

**【請求項 4 4】**

第1乃至第3階調領域のそれぞれがV字形であり、各V字形の頂点が水平方向に配列され、第1乃至第3階調領域のそれぞれの両辺が水平方向に対して対称に折れ曲がっている、請求項41に記載の液晶パネルの駆動方法。

**【請求項 4 5】**

液晶パネル、

前記液晶パネルのゲートラインを駆動するゲートドライバ、

第1ガンマ曲線に基づいて第1ガンマ電圧セットを生成する第1ガンマ電圧生成部、

第2ガンマ曲線に基づいて第2ガンマ電圧セットを生成する第2ガンマ電圧生成部、

水平同期期間ごとに前記第1ガンマ電圧セットと前記第2ガンマ電圧セットとのいずれか一つを選択して出力するスイッチ、10

前記スイッチを介して供給されたガンマ電圧セットを用い、外部から入力されたデータ信号を水平同期期間ごとに、前記液晶パネルのサブ画素の第1階調領域に供給されるべき第1データ信号、または前記サブ画素の第2階調領域に供給されるべき第2データ信号に変換して前記液晶パネルのデータラインに供給するデータドライバ、及び、

前記ゲートドライバと前記データドライバとを制御するタイミングコントローラ、

を具備する液晶表示装置。

**【請求項 4 6】**

前記液晶パネルが、

それぞれが面積の異なる第1階調領域と第2階調領域とに分割された複数のサブ画素で

あり、水平方向で隣接した二つのサブ画素間では第1階調領域と第2階調領域とが上下方

向で反対に配列された複数のサブ画素、20

サブ画素の第1階調領域と第2階調領域とを独立に駆動する複数の薄膜トランジスタ、

前記薄膜トランジスタに接続され、サブ画素の第1階調領域には前記第1データ信号を

供給し、サブ画素の第2階調領域には前記第2データ信号を供給する複数のデータライン

、及び、

前記複数の薄膜トランジスタを水平同期期間単位で駆動する複数のゲートライン、

を具備し；

前記複数のゲートラインの一つが駆動されるとき、前記薄膜トランジスタがサブ画素の

第1階調領域を駆動し、前記複数のゲートラインの別の一つが駆動されるとき、前記薄膜

トランジスタが前記サブ画素の第2階調領域を駆動する；30

請求項45に記載の液晶表示装置。

**【請求項 4 7】**

サブ画素の第1階調領域と第2階調領域とがV字形であり、各V字形の頂点が水平方向

に配列され、第1階調領域と第2階調領域とのそれぞれの両辺が水平方向に対して対称に

折れ曲がっている、請求項46に記載の液晶表示装置。

**【請求項 4 8】**

前記複数のゲートラインの一つに接続された薄膜トランジスタがストレージラインの上

下に位置した第1階調領域のそれぞれに接続され、

前記複数のゲートラインの別の一つに接続された薄膜トランジスタが同じストレージラ

インの上下に位置した第2階調領域のそれぞれに接続されている、40

請求項47に記載の液晶表示装置。

**【請求項 4 9】**

一つのサブ画素に含まれた第1階調領域と第2階調領域とのそれぞれに接続された薄膜

トランジスタが、隣接した二つのデータラインのそれぞれに接続されている、請求項47

に記載の液晶表示装置。

**【請求項 5 0】**

同じサブ画素に含まれる第1階調領域と第2階調領域との間の面積比率が(1.5~3) : 1

である、請求項46に記載の液晶パネルの駆動方法。

**【請求項 5 1】**

50

前記液晶パネルが、

第1ガンマ曲線に基づく第1データ信号が供給される第1階調領域と、第2ガンマ曲線に基づく第2データ信号が供給される第2階調領域と、前記第2階調領域に接続された第3階調領域とを具備するサブ画素、

前記第1階調領域を駆動する第1薄膜トランジスタ、

前記第2階調領域と前記第3階調領域とを駆動する第2薄膜トランジスタ、

前記第1薄膜トランジスタと前記第2薄膜トランジスタとに接続され、それぞれに前記第1データ信号と前記第2データ信号とを供給するデータライン、

前記第1薄膜トランジスタを駆動する第1ゲートライン、及び、

前記第2薄膜トランジスタを駆動する第2ゲートライン、

を具備する、請求項45に記載の液晶表示装置。

10

#### 【請求項52】

サブ画素のそれでは、第1階調領域が第1ゲートラインの上に位置し、第2階調領域と第3階調領域とのいずれか一つ又は両方が同じ第1ゲートラインの下に位置し、

水平方向で隣接する二つのサブ画素の一方では第2階調領域と第3階調領域とが第1ゲートラインの下に位置し、前記二つのサブ画素の他方では第2階調領域と第3階調領域とが同じ第1ゲートラインの上下に分かれて位置している、

請求項51に記載の液晶表示装置。

#### 【請求項53】

同じサブ画素に含まれる第2階調領域と第3階調領域との間の面積比率が(1.5~3):1である、請求項52に記載の液晶表示装置。

20

#### 【請求項54】

第1乃至第3階調領域がV字形であり、各V字形の頂点が水平方向に配列され、第1乃至第3階調領域のそれぞれの両辺が水平方向に対して対称に折れ曲がっている、請求項51に記載の液晶表示装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は液晶表示装置に関し、特に、それに搭載された液晶パネルとその駆動方法に関する。

30

#### 【背景技術】

#### 【0002】

液晶表示装置は、液晶セルのマトリックスにより画像を表示する液晶パネルと、その液晶パネルを駆動する駆動回路とを具備する。液晶表示装置は、駆動回路により各液晶セル内に電界を生成し、その電界により液晶分子の配向方向を制御して各液晶セルの光透過率を調節する。それにより、液晶パネルには画像が表示される。

#### 【0003】

液晶表示装置では一般に、画面を斜めに見るほど画像が歪曲して見える。画像の歪曲が小さい範囲(視野角)を拡げるための代表的な技術としては、マルチ-ドメインVA(Multi-domain Vertical Alignment)が知られている。VAを用いた液晶表示装置(以下、VAモードの液晶表示装置という)では一般に、液晶セルに対して電界が印加されていないとき、負の誘電率異方性を示す液晶分子の配向方向が液晶パネルの表面に対してほぼ垂直に設定されている。そのとき、液晶パネルに設置された偏光子によりその液晶セルを透過した光が遮断される(ノーマリブラック)。液晶セルに対して電界が印加されているとき、液晶分子がその電界の方向に対して斜めに傾く。そのとき、上記の偏光子により、液晶分子の傾斜角に応じて液晶セルの光透過率が上昇する。更に、マルチ-ドメインVAモードの液晶表示装置では、各液晶セル(すなわち、サブ画素)に含まれる液晶層が複数のドメインに分割され、ドメインごとに液晶分子の傾斜方向が異なる。特に、液晶分子の傾斜方向を対称的に変化させることにより、視角に応じた各サブ画素の光透過率の変化が抑えられるので、広い視野角が得られる。ここで、複数のドメインの形成には、各サブ画

40

50

素の液晶層を挟む基板の表面に形成された突起、または各サブ画素に含まれる電極に形成されたスリットが用いられている。

【発明の開示】

【発明が解決しようとする課題】

【0004】

複数のドメインが基板表面の突起を用いて形成されている液晶表示装置では、各サブ画素に対して電界がまだ印加されていないときに液晶分子が既に小さく傾斜している（プリチルト状態）。プリチルトの方向はドメインごとに異なり、特に上記の突起に対して対称に分布している。プリチルト状態にある液晶分子に対して電界が印加されると、液晶分子がプリチルトの方向に更に大きく傾く。その結果、液晶分子の傾斜方向がドメインごとに変化する。しかし、特に突起の近傍では液晶分子の受ける拘束力が弱いので液晶分子の配向に乱れが生じやすく、その乱れに起因する光漏れが発生しやすい。それ故、側面視認性を更に向上させることが困難である。

【0005】

複数のドメインが共通電極と画素電極との各スリットパターンを用いて形成されている液晶表示装置（すなわち、PVAモードの液晶表示装置）では、各電極に対して電圧が印加されるとき、サブ画素の液晶層にはそのスリットによって基板表面に平行な電界（フリンジ電界）が発生する。そのフリンジ電界により液晶分子の傾斜方向がドメインごとに変化し、特にスリットに対して対称的に分布する。しかし、従来のPVAモードの液晶表示装置ではサブ画素が矩形状であるので、サブ画素の端部で発生する側面電界により液晶分子の配向が乱れやすく、エッジテクスチャのような画像の欠陥が発生しやすい。それ故、液晶パネルの側面視認性を更に向上させること、及びサブ画素の光透過率を更に向上させることがいずれも困難である

【0006】

本発明の目的は、マルチ・ドメインVAモードで側面視認性とサブ画素の光透過率とをいずれも更に向上できる液晶パネルとその駆動方法、及びそれを用いた液晶表示装置、を提供することにある。

【課題を解決するための手段】

【0007】

本発明一つの観点による液晶パネルは、

それぞれが面積の異なる第1階調領域と第2階調領域とに分割された複数のサブ画素であり、水平方向で隣接した二つのサブ画素間では第1階調領域と第2階調領域とが上下方向で反対に配列された複数のサブ画素、

サブ画素の第1階調領域と第2階調領域とを独立に駆動する複数の薄膜トランジスタ、

その薄膜トランジスタに接続され、サブ画素の第1階調領域には第1データ信号を供給し、第2階調領域には第2データ信号を供給する複数のデータライン、及び、

上記の薄膜トランジスタを水平同期期間単位で駆動する複数のゲートライン、を具備する。好ましくは、第1階調領域と第2階調領域とが水平方向と上下方向との両方で交互に配列されている。更に好ましくは、第1階調領域と第2階調領域とのそれぞれの両辺が水平方向に対して対称に折れ曲がっている。それにより、上下方向に並ぶ階調領域の境界線がジグザグ模様を成す。

【0008】

好ましくは、複数のゲートラインの一つ（以下、第1ゲートラインという）が第1階調領域と第2階調領域とのそれぞれの折れ曲がった部分の頂点に重なり、複数のゲートラインの別の一つ（以下、第2ゲートラインという）が、上下方向で隣接した二つのサブ画素間の境界部に重なっている。好ましくは、ストレージラインが、上下方向で隣接した第1階調領域と第2階調領域との間の境界部に重なっている。上記の薄膜トランジスタは、ストレージラインに近接し、又は重なっている接続部によって第1階調領域と第2階調領域とのそれぞれの画素電極に接続されている。好ましくは、第1ゲートラインに接続された薄膜トランジスタが一つのストレージラインの上下に位置した第1階調領域のそれぞれに

10

20

30

40

50

接続され、第2ゲートラインに接続された薄膜トランジスタが同じストレージラインの上下に位置した第2階調領域のそれぞれに接続されている。

【0009】

その他に、複数のゲートラインのそれぞれが、上下方向に隣接した第1階調領域と第2階調領域との間の境界部に重なり、ストレージラインが、第1階調領域と第2階調領域とのそれぞれの折れ曲がった部分の頂点に重なっていても良い。その場合、好ましくは、複数のゲートラインの一つに接続された薄膜トランジスタがそのゲートラインの上下に位置した第1階調領域のそれぞれに接続され、複数のゲートラインの別の一つに接続された薄膜トランジスタがそのゲートラインの上下に位置した第2階調領域のそれぞれに接続されている。

10

【0010】

本発明による上記の液晶パネルでは好ましくは、複数のゲートラインの一つが駆動されるとき、上記の薄膜トランジスタがサブ画素の第1階調領域を駆動し、複数のゲートラインの別の一つが駆動されるとき、上記の薄膜トランジスタが同じサブ画素の第2階調領域を駆動する。

【0011】

本発明の別の観点による液晶パネルは、

第1ガンマ曲線に基づく第1データ信号が供給される第1階調領域と、第2ガンマ曲線に基づく第2データ信号が供給される第2階調領域と、第2階調領域に接続された第3階調領域と、を有するサブ画素、

20

第1階調領域を駆動する第1薄膜トランジスタ、

第2階調領域と第3階調領域とを駆動する第2薄膜トランジスタ、

第1薄膜トランジスタと第2薄膜トランジスタとに接続され、それぞれに第1データ信号と第2データ信号とを供給するデータライン、

第1薄膜トランジスタを駆動する第1ゲートライン、及び、

第2薄膜トランジスタを駆動する第2ゲートライン、を具備する。好ましくは、サブ画素のそれぞれでは、第1階調領域が第1ゲートラインの上に位置し、第2階調領域と第3階調領域とのいずれか一つ又は両方が同じ第1ゲートラインの下に位置する。更に好ましくは、水平方向で隣接する二つのサブ画素の一方では第2階調領域と第3階調領域とが第1ゲートラインの下に位置し、他方では第2階調領域と第3階調領域とが同じ第1ゲートラインの上下に分かれて位置する。好ましくは、第1乃至第3階調領域のそれぞれの両辺が水平方向に対して対称に折れ曲がっている。それにより、上下方向に並ぶ階調領域の境界線がジグザグ模様を成す。

30

【0012】

本発明の一つの観点による液晶パネルの駆動方法は、

ルックアップテーブルを用いて入力データ信号を第1データ信号と第2データ信号とに変調する段階、

第1データ信号と第2データ信号とを交互に出力する段階、

ガンマ電圧を用いて第1データ信号と第2データ信号とを交互にアナログ信号に変換する段階、及び、

40

アナログ信号に変換された第1データ信号と第2データ信号とを水平同期期間ごとに交互に複数のデータラインのそれぞれに同期して供給する段階、を含む。

【0013】

本発明の別の観点による液晶パネルの駆動方法は、

第1ガンマ曲線に基づいて第1ガンマ電圧セットを生成する段階、

第2ガンマ曲線に基づいて第2ガンマ電圧セットを生成する段階、

水平同期期間ごとに第1ガンマ電圧セットと第2ガンマ電圧セットとのいずれか一つを選択する段階、及び、

選択されたガンマ電圧セットを用い、外部から入力されたデータ信号を水平同期期間ごとに、サブ画素の第1階調領域に供給されるべき第1データ信号、または、同じサブ画素

50

の第2階調領域に供給されるべき第2データ信号に変換してデータラインに供給する段階、を含む。

#### 【0014】

本発明の一つの観点による液晶表示装置は、本発明の一つの観点による上記の液晶パネルの他に、

液晶パネルのゲートラインを駆動するゲートドライバ、

液晶パネルのデータラインを駆動するデータドライバ、及び、

ゲートドライバとデータドライバとを制御し、外部から入力されたデータ信号を第1データ信号と第2データ信号とに変調してデータドライバに供給するタイミングコントローラ、を具備する。タイミングコントローラは好ましくは、外部から入力されるデータ信号を第1データ信号と第2データ信号との対に予め対応させたルックアップテーブル、を用い、外部から入力されたデータ信号を第1データ信号と第2データ信号との対に変調し、水平同期期間ごとに第1データ信号と第2データ信号とを交互に出力する。10

#### 【0015】

本発明の別の観点による液晶表示装置は、本発明の別の観点による上記の液晶パネルの他に、

液晶パネルのゲートラインを駆動するゲートドライバ、

第1ガンマ曲線に基づいて第1ガンマ電圧セットを生成する第1ガンマ電圧生成部、

第2ガンマ曲線に基づいて第2ガンマ電圧セットを生成する第2ガンマ電圧生成部、

水平同期期間ごとに第1ガンマ電圧セットと第2ガンマ電圧セットとのいずれか一つを選択して出力するスイッチ、20

そのスイッチを通じて供給されたガンマ電圧セットを用い、外部から入力されたデータ信号を水平同期期間ごとに、液晶パネルのサブ画素の第1階調領域に供給されるべき第1データ信号、または、同じサブ画素の第2階調領域に供給されるべき第2データ信号に変換して液晶パネルのデータラインに供給するデータドライバ、及び、

ゲートドライバとデータドライバとを制御するタイミングコントローラ、を具備する。好ましくは、上記のスイッチはデータドライバに内蔵される。

#### 【発明の効果】

#### 【0016】

本発明による液晶パネルでは上記の通り、各サブ画素が面積の異なる第1階調領域と第2階調領域とに分割されている。各階調領域では特に、両辺が水平方向に対して対称に折れ曲がっている。第1階調領域と第2階調領域とは水平方向と上下方向とのそれぞれで交互に配列され、特に各階調領域の折れ曲がり部分の頂点が水平方向に配列されている。それにより、上下方向に並ぶ階調領域の境界線がジグザグ模様を成す。そのように、階調領域の境界線を上下方向に対して斜めに傾かせることにより、サブ画素間に生じる側面電界の方向を各サブ画素のドメイン内のフリンジ電界の方向に揃えることができる。従って、従来の液晶パネルとは異なり、液晶分子の受ける拘束力が強いので、液晶分子の配向が乱れにくい。その結果、サブ画素の光透過率及びコントラスト比が向上するので、液晶パネルの視野角が拡大されると共に、側面視認性が向上する。30

#### 【発明を実施するための最良の形態】

#### 【0017】

以下、添付図面を参照して、本発明の好ましい実施例を詳細に説明する。

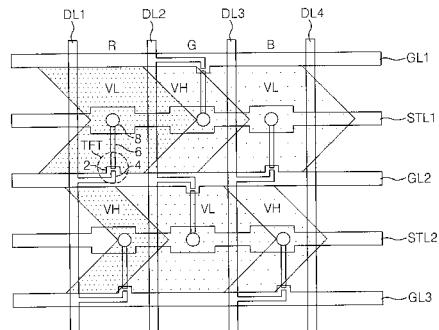

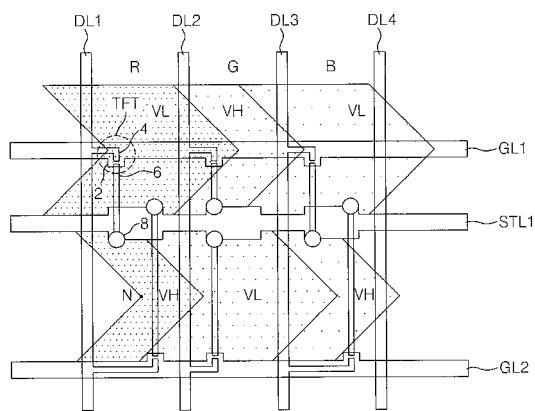

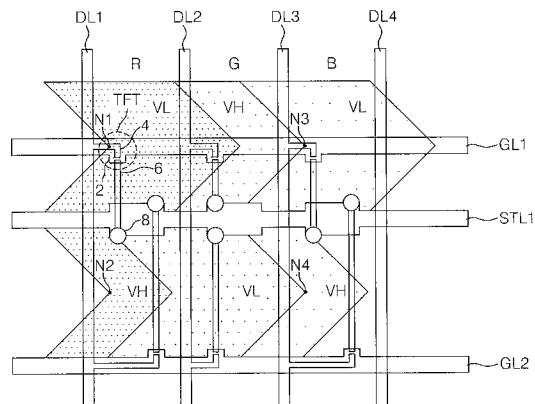

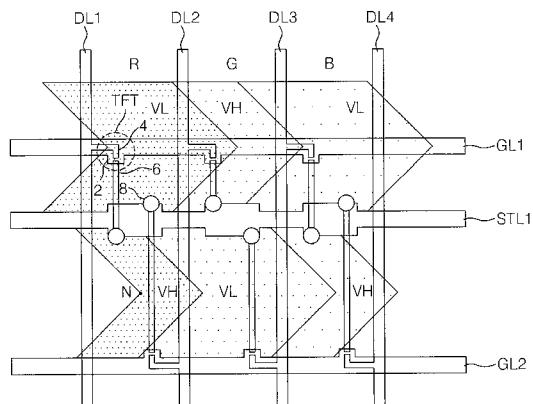

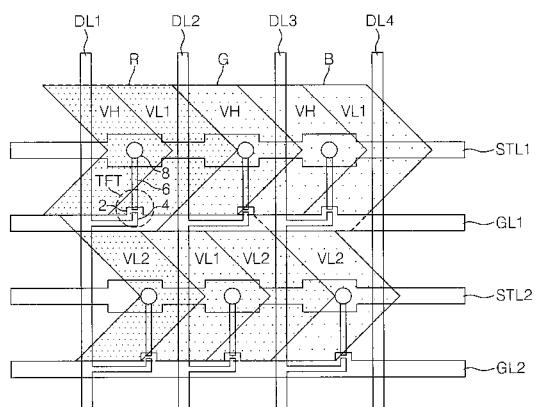

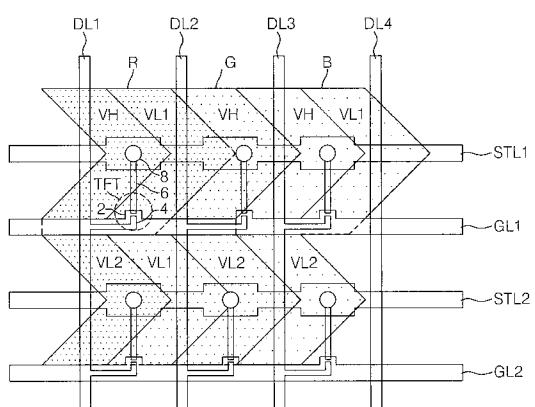

図1は本発明の第1実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図であり、図2は本発明の第2実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。図1及び図2に示された液晶パネルの各画素はジグザグ構造のR、G、Bサブ画素を具備する。

#### 【0018】

R、G、Bサブ画素のそれぞれは側面視認性の向上のために、互いに異なるガンマ曲線により駆動される高階調領域VHと低階調領域VLとに分割されている。高階調領域VHと低階調領域VLとは、異なる薄膜トランジスタTFTによって独立に駆動される。各サブ画素の高40

階調領域VHと低階調領域VLとは好ましくは(1.5~3)：1の面積比率（更に好ましくは1:2の面積比率）で分割されている。各サブ画素では高階調領域VHと低階調領域VLとが上下に配置され、水平方向に隣接した二つのサブ画素間では高階調領域VHと低階調領域VLとが上下方向で反対に配置されている。それにより、水平方向と上下方向とのそれぞれで高階調領域VHと低階調領域VLとが交互に配置されている。

#### 【0019】

各サブ画素の高階調領域VH及び低階調領域VLは左右の両辺が上下方向から傾き、ジグザグ模様を成す。例えば図1及び図2では、高階調領域VH及び低階調領域VLのそれぞれの左右の両辺が中央部で水平方向に対して対称に折れ曲がり、特にその折れ曲がりの頂点では水平方向と45°の傾斜角で交わっている。それにより、各サブ画素の高階調領域VHと低階調領域VLの左右の両辺が、その高階調領域VH及び低階調領域VLのそれぞれを左右二つのドメインに分割するために画素電極及び共通電極に形成されたスリット（図1、2には示されていない）と平行に並ぶ。その結果、水平方向に隣接する二つのサブ画素間に生じる側面電界が、各サブ画素内での液晶分子の配向制御に利用されるフリンジ電界を補うように作用する。こうして、各サブ画素では光透過率及びコントラスト比が共に向上する。

#### 【0020】

このようなジグザグの境界線で区切られた各サブ画素の高階調領域VHと低階調領域VLとは、図1に示されたようにセンターアライン（Center Aligned）構造に整列し、又は図2に示されたようにエッジアライン（Edge Aligned）構造に整列する。図1に示されたセンターアライン構造では、高階調領域VHの左辺の頂点Nが、隣接した2つのデータラインDL1、DL2の間の中心点と一致するように、高階調領域VH及び低階調領域VLが整列している。図2に示されたエッジアライン構造では、上下方向で隣接した高階調領域VHと低階調領域VLとで、左右いずれか同じ側の辺の頂点の対（N2、N1）又は（N3、N4）が同一の垂直線上に位置するように、高階調領域VH及び低階調領域VLが整列している。

#### 【0021】

このようなジグザグ構造のサブ画素は、高階調領域VH及び低階調領域VLのそれぞれに形成された画素電極の形状と、各画素電極に重ねられたR、G、Bそれぞれのカラーフィルタの形状とによって決定される。言い換えれば、各サブ画素の高階調領域VH及び低階調領域VLに形成された画素電極とR、G、Bカラーフィルタとが上述のジグザグ構造を有する。

#### 【0022】

画素電極は各サブ画素の高階調領域VH及び低階調領域VLのそれぞれに独立に形成され、異なる薄膜トランジスタTFTによって駆動される。このような画素電極は薄膜トランジスタTFTと共に同じ基板に形成され、別の基板に形成された共通電極と液晶層を挟んで対向する。画素電極と共に形成された共通電極との間に生じる電界が、二枚の基板の間に挟まれた液晶層内で垂直配向された液晶分子を駆動する。高階調領域VH及び低階調領域VLのそれぞれでは更に、マルチ・ドメインを形成するために画素電極と共に形成されたスリットが、水平方向と上下方向とのそれぞれで交互に形成されている。例えば、高階調領域VHは共通電極及び画素電極に形成されたスリットによって上下左右に配列された4個のドメインに分割され、低階調領域VLは8個のドメインに分割される。

#### 【0023】

薄膜トランジスタTFTはゲートラインGLからのスキャン信号に応じてデータラインDLからのデータ信号を画素電極に供給する。薄膜トランジスタTFTは、ゲートラインGLに接続されたゲート電極2、データラインDLに接続されたソース電極4、コンタクト部8を介して画素電極に接続されたドレイン電極6、及び、ソース電極4とドレイン電極6との間にチャネルを形成する半導体層（図示せず）を具備する。特に、各サブ画素では高階調領域VH及び低階調領域VLが、異なるゲートラインGLに接続された薄膜トランジスタTFTを介して独立に駆動される。例えば、図1及び図2に示されたように、第1乃至第3データラインDL1、DL2、DL3のそれぞれと第1ゲートラインGL1との間に接続された薄膜トランジスタTFTによって第1ゲートラインGL1が駆動されるとき、R低階調領域VL、G高階調領域VH、B

10

20

30

40

50

低階調領域VLが駆動される。一方、第1乃至第3データラインDL1、DL2、DL3のそれぞれと第2ゲートラインGL2との間に接続された薄膜トランジスタTFTによって第2ゲートラインGL2が駆動されるとき、R高階調領域VH、G低階調領域VL、B高階調領域VHが駆動される。それにより、R、G、Bサブ画素の階調が、高階調領域VHに表現された高階調と、低階調領域VLに表現された低階調との組み合わせで表現される。その結果、液晶パネルの側面視認性が向上する。

#### 【0024】

好ましくは、第1ゲートラインGL1は、各サブ画素の上側に位置する低階調領域VLまたは高階調領域VHの折れ曲がり部分の頂点に重なり、第2ゲートラインGL2は、上下方向で隣接した二つのサブ画素の境界部に重なっている。それにより、サブ画素の光透過率が向上する。第1乃至第4データラインDL1～DL4は、第1ゲートラインGL1及び第2ゲートラインGL2と絶縁膜（図示せず）を間において交差している。更に、第1ゲートラインGL1及び第2ゲートラインGL2の間では、第1ストレージラインSTL1が、各サブ画素の高階調領域VH及び低階調領域VLの間の境界部に重なっている。第1ゲートラインGL1に接続された薄膜トランジスタTFTは、第1ストレージラインSTL1の上に位置する高階調領域VHまたは低階調領域VLの画素電極に接続されている。第2ゲートラインGL2に接続された薄膜トランジスタTFTは、第1ストレージSTL1の下に位置する高階調領域VHまたは低階調領域VLの画素電極に接続されている。より具体的には、第1ゲートラインGL1に接続された薄膜トランジスタTFTでは、そのドレイン電極6が下側の第1ストレージラインSTL1まで延び、その第1ストレージラインSTL1に重なり、又は近接したコンタクト部8を通じて低階調領域VLまたは高階調領域VHの画素電極に接続されている。一方、第2ゲートラインGL2に接続された薄膜トランジスタTFTでは、そのドレイン電極6が上側の第1ストレージラインSTL1まで延び、その第1ストレージラインSTL1に重なり、又は近接したコンタクト部8を介して高階調領域VHまたは低階調領域VLの画素電極に接続されている。ここで、コンタクト部8を通じて高階調領域VHまたは低階調領域VLの画素電極に接続されたドレイン電極6は第1ストレージラインSTL1に重なり、ストレージキャパシタを形成する。

#### 【0025】

以上のように、本発明の第1実施例及び第2実施例による液晶パネルの各サブ画素はジグザグ構造であり、好ましくは1:2の面積比を有する高階調領域VHと低階調領域VLとに分割されている。その結果、各サブ画素の光透過率が向上し、液晶パネルの側面視認性が向上する。

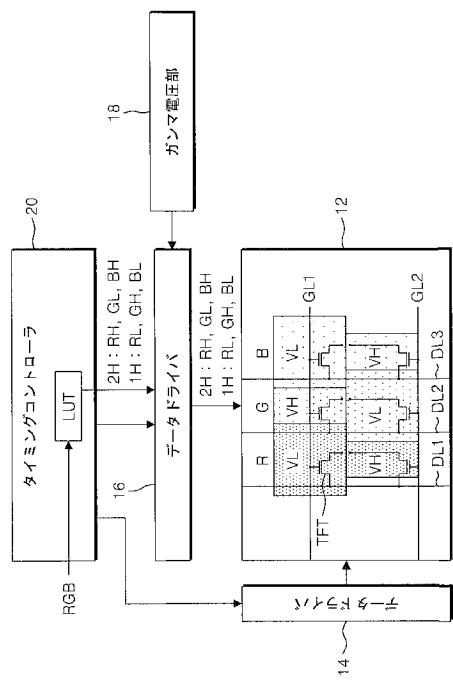

#### 【0026】

図3は、図1及び図2に示された液晶パネルを有する、本発明の第1実施例による液晶表示装置を示したブロック図である。図3に示された液晶表示装置は、液晶パネル12、液晶パネル12のゲートラインGLを駆動するゲートドライバ14、液晶パネル12のデータラインDLを駆動するデータドライバ16、及び、ゲートドライバ14とデータドライバ16とを制御するタイミングコントローラ20、を具備する。液晶パネル12は図1及び図2に示されたように、ジグザグ構造であり、好ましくは1:2の面積比を有する高階調領域VHと低階調領域VLとの対で構成されたR、G、Bサブ画素を具備する。尚、図3では、R、G、Bサブ画素が単純化されて示されている。各サブ画素の高階調領域VHと低階調領域VLとは異なる薄膜トランジスタTFTによって駆動され、水平方向で隣接した二つのサブ画素間では高階調領域VH及び低階調領域VLが上下方向で反対に配置されている。例えば、第1ゲートラインGL1に接続された薄膜トランジスタTFTによって、R低階調領域VL、G高階調領域VH、B低階調領域VLが駆動され、第2ゲートラインGL2に接続された薄膜トランジスタTFTによって、R高階調領域VH、G低階調領域VL、B高階調領域VHが駆動される。

#### 【0027】

タイミングコントローラ20は、外部から入力された同期信号及びクロック信号を用い、ゲートドライバ14を制御するためのゲート制御信号と、データドライバ16を制御するためのデータ制御信号とを生成する。また、タイミングコントローラ20は、外部からR、G、Bデータ信号を入力し、予め貯蔵されたルックアップテーブルLUTを利用して高階調領域

10

20

30

40

50

に対する高階調データ信号RH、GH、BHと低階調領域に対する低階調データ信号RL、GL、BLとに変調し、メモリに貯蔵する。その後、タイミングコントローラ20は、メモリに貯蔵された高階調データ信号及び低階調データ信号を、各サブ画素の高階調領域VHと低階調領域VLとの配置に合わせた順序でデータドライバ16に供給する。例えば、タイミングコントローラ20は、ある水平同期期間1Hではデータ信号をRL、GH、BLの順でデータドライバ16に供給し、次の水平期間2HではRH、GL、BHの順で供給する。ここで、タイミングコントローラ20は、R、G、Bデータ信号を高階調データ信号と低階調データ信号とに分割してデータドライバ16に供給しなければならぬので、高速で動作する必要がある。

#### 【0028】

ゲートドライバ14はタイミングコントローラ20からのゲート制御信号に応じて液晶パネル12のゲートラインGLを順番に駆動する。データドライバ16はガンマ電圧部18からのガンマ電圧を用い、タイミングコントローラ20からのデータ信号をアナログ信号に変換し、液晶パネル12のゲートラインGLが駆動されるごとにデータラインDLに供給する。例えば、第1ゲートラインGL1が駆動されるとき、データドライバ16はタイミングコントローラ20からのデータ信号RL、GH、BLをアナログ信号に変換し、第1乃至第3データラインDL1、DL2、DL3のそれぞれに供給する。それにより、第1ゲートラインGL1と第1乃至第3データラインDL1、DL2、DL3との間に接続された薄膜トランジスタTFTを通じ、R低階調領域VLには低階調データ信号RLが供給され、G高階調領域VHには高階調データ信号GHが供給され、B低階調領域VLには低階調データ信号BLが供給される。続いて、第2ゲートラインGL2が駆動されるとき、データドライバ16はタイミングコントローラ20からのデータ信号RH、GL、BHをアナログ信号に変換し、第1乃至第3データラインDL1、DL2、DL3のそれぞれに供給する。それにより、第2ゲートラインGL2と第1乃至第3データラインDL1、DL2、DL3との間に接続された薄膜トランジスタTFTを通じ、R高階調領域VHには高階調データ信号RHが供給され、G低階調領域VLには低階調データ信号GLが供給され、B高階調領域VHには高階調データ信号BHが供給される。その結果、R、G、Bサブ画素のそれぞれは、高階調領域VHと低階調領域VLとのそれぞれに供給されたデータ信号に応じた高階調と低階調との組み合わせで階調を表現する。

#### 【0029】

このように、本発明の第1実施例による液晶表示装置では、タイミングコントローラ20がルックアップテーブルLUTを用いたデジタル変調方式により、R、G、Bデータ信号を高階調データ信号と低階調データ信号とに分離し、液晶パネル12の各サブ画素の高階調領域VH及び低階調領域VLのそれぞれに供給する。

#### 【0030】

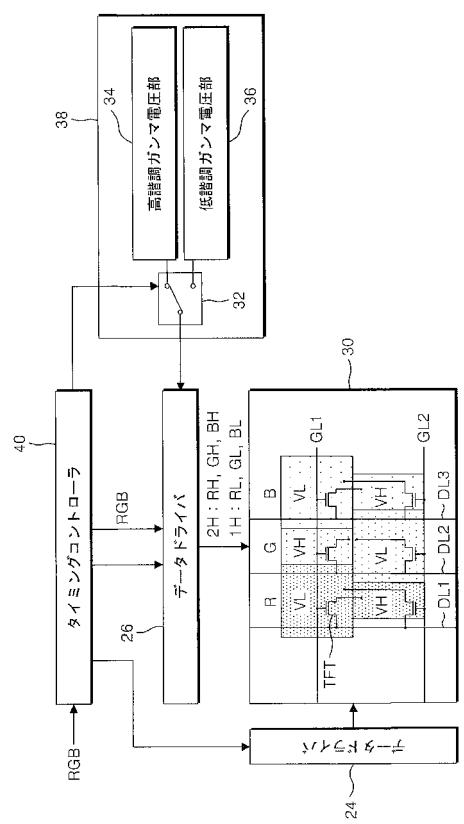

図4は本発明の第2実施例による液晶表示装置を示したブロック図である。図4に示された液晶表示装置は、高階調ガンマ電圧と低階調ガンマ電圧とを用いたアナログ変調方式により、R、G、Bデータ信号を高階調データ信号と低階調データ信号とに分離し、各サブ画素の高階調領域VH及び低階調領域VLのそれぞれに独立に供給する。図4に示された液晶表示装置は、液晶パネル30、液晶パネル30のゲートラインGLを駆動するゲートドライバ24、液晶パネル30のデータラインDLを駆動するデータドライバ26、ゲートドライバ24とデータドライバ26とを制御するタイミングコントローラ40、及び、データドライバ26に高階調ガンマ電圧と低階調ガンマ電圧とを選択させるガンマ電圧部38、を具備する。

#### 【0031】

タイミングコントローラ40は、外部から入力された同期信号及びクロック信号を用い、ゲートドライバ24を制御するためのゲート制御信号と、データドライバ26を制御するためのデータ制御信号とを生成する。また、タイミングコントローラ40は、外部から入力されたR、G、Bデータ信号を再構成してデータドライバ26に供給する。ゲートドライバ24は、タイミングコントローラ40からのゲート制御信号に応じて液晶パネル30のゲートラインGLを順番に駆動する。データドライバ26はタイミングコントローラ40からのデータ信号をアナログ信号に変換する。そのとき、データドライバ26は、ガンマ電圧部38により生成された高階調ガンマ電圧と低階調ガンマ電圧とを用い、データ信号を高階調データ信号と低

10

20

30

40

50

階調データ信号とにそれぞれ変換して液晶パネル30に供給する。

【0032】

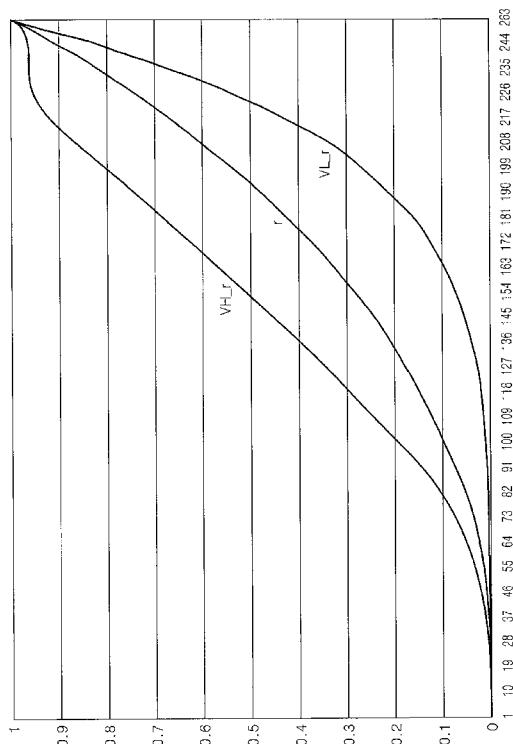

ガンマ電圧部38は、複数の高階調ガンマ電圧を生成する高階調ガンマ電圧部34、複数の低階調ガンマ電圧部を生成する低階調ガンマ電圧部36、及び、高階調ガンマ電圧部34の出力と低階調ガンマ電圧部36の出力とのいずれかを選択して出力するアナログスイッチ32、を具備する。高階調ガンマ電圧部34は、図5に示された高階調ガンマ曲線VH\_rに従って設計された抵抗素子列を用いて複数の高階調ガンマ電圧を生成する。低階調ガンマ電圧部36は、図5に示された低階調ガンマ曲線VL\_rに従って設計された抵抗素子列を用いて複数の低階調ガンマ電圧を生成する。アナログスイッチ32は、ある一つの水平同期期間では高階調ガンマ電圧部34からの高階調ガンマ電圧をデータドライバ26に供給し、その次の水平同期期間では低階調ガンマ電圧部36からの低階調ガンマ電圧をデータドライバ26に供給する。アナログスイッチ32はこのスイッチング動作を水平同期期間毎に反復する。アナログスイッチ32の動作はタイミングコントローラ40の制御に従い、データドライバ26によるデータ信号の液晶パネル30への出力動作と同期する。尚、アナログスイッチ32はガンマ電圧部38に代え、データドライバ26に内蔵されていても良い。アナログスイッチ32のスイッチング動作により、データドライバ26はタイミングコントローラ40からのR、G、Bデータ信号を、ある一つの水平同期期間では高階調ガンマ電圧を用いて高階調データ信号に変換して液晶パネル30に供給し、その次の水平同期期間では低階調ガンマ電圧を用いて低階調データ信号に変換して液晶パネル30に供給する。

【0033】

液晶パネル30は、ジグザグ模様を成し、かつ好ましくは1:2の面積比を有する高階調領域VHと低階調領域VLとに分割されたR、G、Bの各サブ画素を具備する。但し、図4では簡単のため、R、G、Bサブ画素を単純化して示す。各サブ画素の高階調領域VHと低階調領域VLとのそれぞれは薄膜トランジスタTFTによって駆動される。水平方向で隣接した二つのサブ画素間では高階調領域VHと低階調領域VLとが上下方向で反対に配置されている。特に、ガンマ電圧部38を用いたアナログ変調により、R、G、Bサブ画素の高階調領域VHと低階調領域VLとは、高階調データ信号が供給される水平同期期間と、低階調データ信号が供給される水平同期期間とで、別々に駆動される。例えば、第1ゲートラインGL1に接続された薄膜トランジスタTFTは、R、G、Bサブ画素の高階調領域VHに接続され、第2ゲートラインGL2に接続された薄膜トランジスタTFTは、R、G、Bサブ画素の低階調領域VLに接続されている。より具体的には、第1ゲートラインGL1に接続され、かつ、Rサブ画素の上部に位置するR低階調領域VLとBサブ画素の上部に位置するB低階調領域VLとのそれぞれに配置された薄膜トランジスタTFTでは、そのドレイン電極が下方に延び、各サブ画素の下部に位置するR高階調領域VH及びB高階調領域VHのそれぞれに接続されている。第2ゲートラインGL2に接続され、かつRサブ画素の下部に位置するR高階調領域VHとBサブ画素の下部に位置するB高階調領域VHとのそれぞれに配置された薄膜トランジスタTFTでは、そのドレイン電極が上方に延び、各サブ画素の上部に位置するR低階調領域VL及びB低階調領域VLのそれぞれに接続されている。第1ゲートラインGL1に接続され、かつGサブ画素の上部に位置するG高階調領域VHに配置された薄膜トランジスタTFTはそのG高階調領域VHに接続され、第2ゲートラインGL2に接続され、かつGサブ画素の下部に位置するG低階調領域VLに配置された薄膜トランジスタTFTは、そのG低階調領域VLに接続されている。それにより、第1ゲートラインGL1が駆動される水平同期期間1Hでは、データドライバ26から第1乃至第3データラインDL1、DL2、DL3のそれぞれに供給された高階調データ信号RH、GH、BHが、R、G、B高階調領域VHのそれぞれに供給される。続いて、第2ゲートラインGL2が駆動される水平同期期間2Hでは、データドライバ26から第1乃至第3データラインDL1、DL2、DL3のそれぞれに供給された低階調データ信号RL、GL、BLが、R、G、B低階調領域VLのそれぞれに供給される。それにより、R、G、Bサブ画素のそれぞれは、高階調領域VHと低階調領域VLとのそれぞれに供給されたデータ信号に応じた高階調及び低階調の組み合わせで発光し、図5に示されたガンマ曲線rに従う階調を表現する。

10

20

30

40

50

## 【0034】

以上の通り、本発明の第2実施例による液晶表示装置は、高階調ガンマ電圧と低階調ガンマ電圧とを用いたアナログ変調方式でR、G、Bデータを高階調データ信号及び低階調データ信号に分離し、各サブ画素を上下に分割する高階調領域VH及び低階調領域VLのそれぞれに供給する。上記のアナログ変調方式では、ルックアップテーブルLUTを用いたデジタル変調方式とは異なり、タイミングコントローラの高速動作が不要であるので、その高速動作に伴うノイズに起因する画質低下が防止される。また、デジタル変調方式では一つのガンマ曲線に基づいて高階調及び低階調が表現されねばならないので、階調表現の更なる精密化が難しい。それに対し、アナログ変調方式では高階調及び低階調のそれぞれが異なるガンマ曲線に基づいて別々に調整されるので、階調表現の更なる精密化が可能である。

10

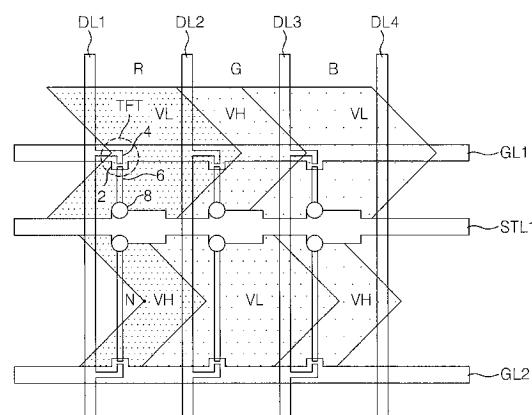

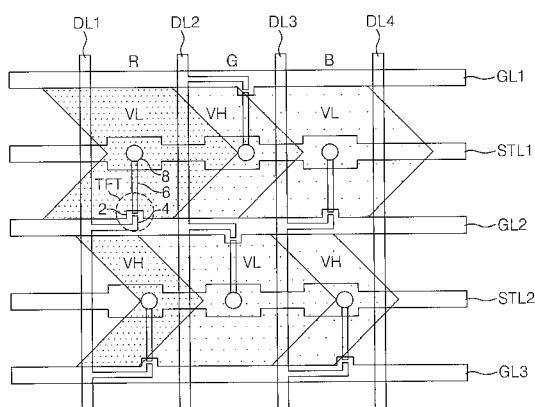

## 【0035】

以下では、図4に示されたアナログ変調方式に適用可能なVAモードの液晶パネルを具体的に見てみる。

図6は本発明の第3実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図であり、図7は本発明の第4実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。図6及び図7に示された液晶パネルは、図4に示された液晶パネル30のR、G、Bサブ画素のジグザグ構造を示したものであり、図1及び図2に示された液晶パネルとは異なり、水平方向で隣接した二つのサブ画素間では、高階調領域VH及び低階調領域VLのそれと薄膜トランジスタTFTとの間を接続するコンタクト部8が、上下方向で反対に配置されている。尚、その他の構成要素は同様であるので、それら同様な構成要素については、図1及び図2に示された液晶パネルに関する上記の説明を援用する。

20

## 【0036】

図6及び図7に示されたR、G、Bサブ画素のそれぞれは、好ましくは1:2の面積比を有する高階調領域VH及び低階調領域VLとで上下に分割されている。高階調領域VHと低階調領域VLとの配置は、図6に示されたセンターライン構造であっても良く、図7に示されたエッジアライン構造であっても良い。また、各サブ画素の高階調領域VHと低階調領域VLとは、水平方向で隣接した別のサブ画素の高階調領域VH及び低階調領域VLとは上下方向で反対に配置されている。

30

## 【0037】

ある一つの水平同期期間ではR、G、Bサブ画素の高階調領域VHが同時に駆動され、その後の水平同期期間ではR、G、Bサブ画素の低階調領域VLが同時に駆動される。それにより、図4に示されたアナログ変調方式で分離された高階調データ信号及び低階調データ信号が、各サブ画素の高階調領域VHと低階調領域VLとのそれぞれに供給される。例えば、第1ゲートラインGL1に接続された薄膜トランジスタTFTは、R、G、Bサブ画素の高階調領域VHをそれぞれ駆動し、第2ゲートラインGL2に接続された薄膜トランジスタTFTは、R、G、Bサブ画素の低階調領域VLをそれぞれ駆動する。

## 【0038】

第1ゲートラインGL1に接続された薄膜トランジスタTFTは、その第1ゲートラインGL1に重なっている低階調領域VLまたは高階調領域VHの折れ曲がり部分に形成されている。R高階調領域VH及びB高階調領域VHのそれぞれを駆動する薄膜トランジスタTFTのドレイン電極6は下方に延び、第1ストレージラインSTL1の下辺に位置するコンタクト部8を通じてその第1ストレージラインSTL1の下に位置するR高階調領域VH及びB高階調領域VHのそれぞれに接続されている。G高階調領域VHを駆動する薄膜トランジスタTFTのドレイン電極6は下方に延び、第1ストレージSTL1の上辺に位置するコンタクト部8を通じてその第1ストレージラインSTL1の上に位置するG高階調領域VHに接続されている。特に、第1ゲートラインGL1に接続された薄膜トランジスタTFTと低階調領域VLまたは高階調領域VHとの間を接続するコンタクト部8は、第1ストレージラインSTL1に沿ってその上下に交互に位置する。

40

## 【0039】

50

第2ゲートラインGL2に接続された薄膜トランジスタTFTは、上下方向に隣接した二つのサブ画素間の境界部に形成されている。ここで、その境界部には第2ゲートラインGL2が重なっている。R低階調領域VL及びB低階調領域VLのそれぞれを駆動する薄膜トランジスタTFTのドレイン電極6は上方に延び、第1ストレージラインSTL1の上辺に位置するコンタクト部8を通じてその第1ストレージラインSTL1の上に位置するR低階調領域VL及びB低階調領域VLのそれぞれに接続されている。G低階調領域VLを駆動する薄膜トランジスタTFTのドレイン電極6は上方に延び、第1ストレージラインSTL1の下辺に位置するコンタクト部8を通じてその第1ストレージラインSTL1の下に位置するG低階調領域VLに接続されている。特に、第2ゲートラインGL2に接続された薄膜トランジスタTFTと高階調領域VHまたは低階調領域VLとの間を接続するコンタクト部8は、第1ストレージラインSTL1に沿ってその上下に交互に位置する。

10

## 【0040】

第1ゲートラインGL1が駆動される水平同期期間では、高階調ガンマ電圧に基づく高階調データ信号が、R、G、Bサブ画素の高階調領域VHのそれぞれに供給される。一方、第2ゲートラインGL2が駆動される水平同期期間では、低階調ガンマ電圧に基づく低階調データ信号が、R、G、Bサブ画素の低階調領域VLのそれぞれに供給される。その結果、R、G、Bサブ画素のそれでは、高階調領域VHと低階調領域VLとのそれぞれで表現される高階調及び低階調の組み合わせにより、目標の階調が表現される。

20

## 【0041】

図8は本発明の第5実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。図8に示された液晶パネルは、図6に示された液晶パネルとは異なり、一つのサブ画素の高階調領域VHと低階調領域VLとのそれぞれを駆動する薄膜トランジスタTFTが、異なるデータラインDLに接続されている。その他の構成要素は同様であるので、それら同様な構成要素については、図6に示された液晶パネルに関する上記の説明を援用する。

30

## 【0042】

図8に示された、一つのサブ画素を上下に分割する高階調領域VHと低階調領域VLとのそれを駆動する2つの薄膜トランジスタTFTは、異なるゲートラインGLに接続されると共に、異なるデータラインDLに接続されている。それにより、図6のように、一つのサブ画素の高階調領域VHと低階調領域VLとのそれを駆動する2つの薄膜トランジスタTFTが同一のデータラインDLに接続される構成に比べ、ソース電極4とゲートラインGLとの重なり部分が短いので、それらの間の寄生キャパシタンスが小さい。例えば、第1ゲートラインGL1に接続された薄膜トランジスタTFTは左側に隣接したデータラインに接続され、第2ゲートラインGL2に接続された薄膜トランジスタTFTは右側に隣接したデータラインに接続される。より具体的には、第1ゲートラインGL1に接続され、かつR、G、Bサブ画素それぞれの高階調領域VHを駆動する薄膜トランジスタTFTは、左側に隣接した第1乃至第3データラインDL1～DL3のそれぞれに接続されている。ここで、第1ゲートラインGL1に接続された薄膜トランジスタTFTのそれは、左側のデータラインDL1～DL3のそれぞれに接続されたソース電極4と、下方に延びてR、G、Bサブ画素それぞれの高階調領域VHに接続されたドレイン電極6とを具備する。一方、第2ゲートラインGL2に接続され、R、G、Bサブ画素それぞれの低階調領域VLを駆動する薄膜トランジスタTFTは、右側に隣接した第2乃至第4データラインDL2～DL4のそれぞれに接続されている。ここで、第2ゲートラインDL2に接続された薄膜トランジスタTFTのそれは、右側のデータラインDL2～DL4のそれぞれに接続されたソース電極4と、上方に延びてR、G、Bサブ画素それぞれの低階調領域VLに接続されたドレイン電極6とを具備する。特に、第2ゲートラインGL2に接続された薄膜トランジスタが右側のデータラインに接続されているので、図6のように左側のデータラインに接続された場合より、ソース電極4と第2ゲートラインGL2との間の重なり部分が短縮可能である。その結果、第2ゲートラインGL2とソース電極4との間の重なりに起因する寄生キャパシタンスが減少するので、その寄生キャパシタンスに起因する信号の歪曲が防止される。

40

50

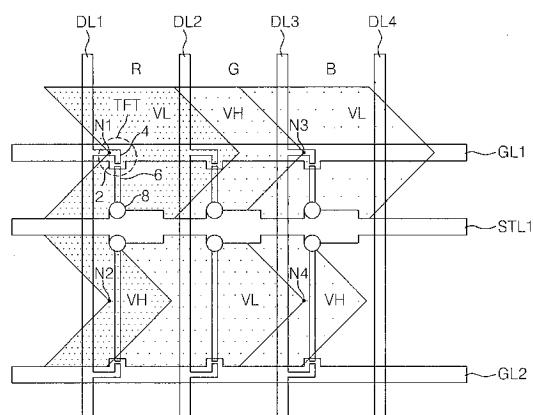

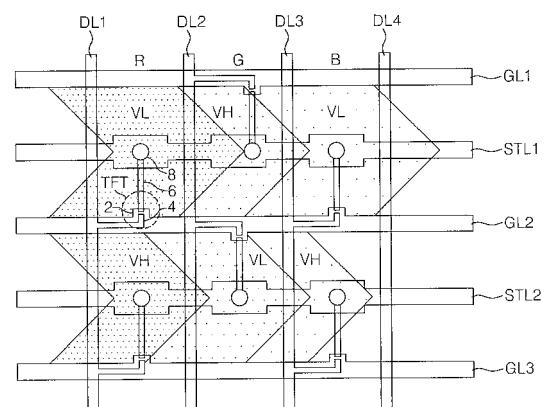

## 【 0 0 4 3 】

図9は本発明の第6実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図であり、図10は本発明の第7実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。図9及び図10に示された液晶パネルは、図6及び図7に示された液晶パネルと比べ、ゲートラインとストレージラインの数、及び薄膜トランジスタTFTの配置が異なる。その他の構成要素は同様であるので、それら同様な構成要素については図6及び図7に関する上記の説明を援用する。

## 【 0 0 4 4 】

図9及び図10に示された、R、G、Bサブ画素のそれぞれを上下に分割する高階調領域VHと低階調領域VLとは、水平方向で隣接した二つのサブ画素間では上下方向で反対に配置されている。R、G、Bサブ画素は、図9に示されたようなセンターライン構造に配置されていても良く、図10に示されたようなエッジアライン構造に配置されていても良い。

## 【 0 0 4 5 】

水平方向で隣接した二つのサブ画素間では、それぞれの高階調領域VHと低階調領域VLとを駆動する2つの薄膜トランジスタTFTの対が、上下方向で反対に配置されている。例えば、Rサブ画素の低階調領域VL及び高階調領域VHのそれぞれを駆動する2つの薄膜トランジスタTFTは、それぞれの上に位置するコンタクト部8を通じて低階調領域VL及び高階調領域VHのそれに接続されている。一方、Gサブ画素の高階調領域VH及び低階調領域VLのそれを駆動する2つの薄膜トランジスタTFTは、それぞれの下に位置するコンタクト部8を介して高階調領域VH及び低階調領域VLのそれに接続されている。

## 【 0 0 4 6 】

第1ゲートラインGL1は、その上下に隣接した二つのサブ画素間の境界部に重なっている。第2ゲートラインGL1は、各サブ画素の高階調領域VHと低階調領域VLとの間の境界部に重なっている。第3ゲートラインGL3は、第1ゲートラインGL1に重なっているサブ画素とその下に隣接したサブ画素との間の境界部に重なっている。第1ストレージラインSTL1は、第2ゲートラインGL2の上に位置する高階調領域VH及び低階調領域VLのそれぞれの折れ曲がり部分の頂点に重なっている。第2ストレージラインSTL2は、第2ゲートラインGL2の下に位置する高階調領域VH及び低階調領域VLのそれぞれの折れ曲がり部分の頂点に重なっている。

## 【 0 0 4 7 】

Rサブ画素及びBサブ画素それぞれの高階調領域VHと低階調領域VLとのそれを駆動する薄膜トランジスタTFTは、それらの高階調領域(VH)又は低階調領域(VL)の下端に位置する第2ゲートラインGL2又は第3ゲートラインGL3によって駆動される。特に、第2ゲートラインGL2に接続され、かつR低階調領域VL及びB低階調領域VLのそれを駆動する薄膜トランジスタTFTのドレイン電極6は上方に延び、第1ストレージラインSTL1に重なっているコンタクト部8を通じてR低階調領域VL及びB低階調領域VLのそれに接続されている。一方、第3ゲートラインGL3に接続され、かつR高階調領域VH及びB高階調領域VHのそれを駆動する薄膜トランジスタTFTのドレイン電極6は上方に延び、第2ストレージラインSTL2に重なっているコンタクト部8を介してR高階調領域VH及びB高階調領域VHのそれに接続されている。

## 【 0 0 4 8 】

Gサブ画素の高階調領域VHと低階調領域VLのそれを駆動する薄膜トランジスタTFTは、それらの高階調領域VH又は低階調領域VLの上端に位置する第1ゲートラインGL1又は第2ゲートラインGL2によって駆動される。特に、第1ゲートラインGL1に接続され、かつG高階調領域VHを駆動する薄膜トランジスタTFTのドレイン電極6は下方に延び、第1ストレージラインSTL1に重なっているコンタクト部8を介してG高階調領域VHに接続されている。第2ゲートラインGL2に接続され、かつG低階調領域VLを駆動する薄膜トランジスタTFTのドレイン電極6は下方に延び、第2ストレージラインSTL2に重なっているコンタクト部8を介してG低階調領域VLに接続されている。

10

20

30

40

50

## 【0049】

第1ゲートラインGL1が駆動される水平同期期間では、G低階調領域VLに低階調データ信号が供給される。第2ゲートラインGL2が駆動される水平同期期間では、R、G、B低階調領域VLのそれぞれに低階調データ信号が供給される。第3ゲートラインGL3が駆動される水平同期期間では、R高階調領域VH及びB高階調領域VHのそれぞれに高階調データ信号が供給される。それと同時に、第3ゲートラインGL3の下に隣接するGサブ画素の高階調領域VHにも高階調データ信号が供給される。こうして、各水平同期期間ではサブ画素のマトリックスの隣接する2行に対してデータ信号が供給されなければならない。従って、タイミングコントローラは、サブ画素に対するデータ信号を、サブ画素のマトリックスの隣接する2行ずつ組み合わせてデータドライバに供給する。その場合、タイミングコントローラは好ましくは、標準装備のフレームメモリ、又はオプションのラインメモリを用い、サブ画素のマトリックスの各2行に対するデータ信号を組み合わせる。その結果、R、G、Bサブ画素のそれぞれでは、高階調領域VHと低階調領域VLとで表現される高階調及び低階調の組み合わせにより、目標の階調が表現される。10

## 【0050】

図9及び図10に示された液晶パネルでは、上下方向に隣接した高階調領域VHと低階調領域VLとの間の各境界部にゲートラインが一つずつ形成されている。更に、各階調領域に接続された薄膜トランジスタTFTが、水平方向で隣接した二つの階調領域間では上下方向で反対に配置されている。それにより、薄膜トランジスタTFTのドレイン電極6の長さが図6及び図7に示された液晶パネルでの長さより減少するので、サブ画素の開口率が上昇する。20

## 【0051】

また、図6及び図7に示された液晶パネルでは、薄膜トランジスタTFTのドレイン電極6が、他のデータ信号が供給される階調領域を経由するので、その階調領域とドレイン電極6に接続された階調領域との間の寄生キャパシタに起因するカップリング偏差が発生しやすい。それに対し、図9及び図10に示された液晶パネルでは、薄膜トランジスタTFTのドレイン電極6が、他のデータ信号が供給される階調領域には重なっていないので、上記のカップリング偏差が防止される。例えば、図6及び図7に示されたRサブ画素では、下部にある高階調領域VHを駆動する上側の薄膜トランジスタTFTのドレイン電極6が、上部にある低階調領域VLを経由し、低階調領域VLを駆動する下側の薄膜トランジスタのドレイン電極が高階調領域VHを経由する。一方、Gサブ画素では、高階調領域VHと低階調領域VLとのそれを駆動する薄膜トランジスタのドレイン電極が駆動対象の階調領域のみを経由する。特にフリッカー対策として点反転駆動が行われる場合、Rサブ画素及びGサブ画素では、水平方向と上下方向とのそれぞれで隣接した高階調領域VHと低階調領域VLとの間でデータ信号の極性が反転する。それにより、Rサブ画素での高階調領域VHと低階調領域VLとの間の寄生キャパシタンスが、Gサブ画素での高階調領域VHと低階調領域VLとの間の寄生キャパシタンスより大きく増加するので、カップリング偏差が発生しやすい。それに伴い、液晶パネルの画像には縦線染みが発生するおそれがある。それに対し、図9及び図10に示された液晶パネルでは、水平方向で隣接した二つのサブ画素間で薄膜トランジスタTFTの位置が上下方向で反転している。従って、それぞれのドレイン電極6が、駆動対象とは別の階調領域には重なることなく、駆動対象の階調領域にのみ重なっている。それ故、上述のようなサブ画素間での寄生キャパシタンスの差異に起因するカップリング偏差が防止される。30

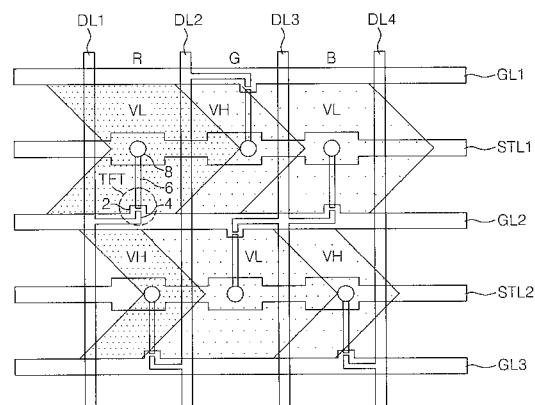

## 【0052】

図11は本発明の第8実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。図11に示された液晶パネルは、図9に示された液晶パネルとは異なり、一つのサブ画素の高階調領域VHと低階調領域VLとのそれを駆動する薄膜トランジスタTFTが異なるデータラインに接続されている。その他の構成要素は同様であるので、それら同様な構成要素については図9に関する上記の説明を援用する。40

## 【0053】

図11では、一つのサブ画素を上下に分割する高階調領域VHと低階調領域VLとのそれぞれを駆動する2つの薄膜トランジスタTFTが、異なるゲートラインに接続されると共に、異なるデータラインに接続されている。それにより、図9のように、一つのサブ画素の高階調領域VHと低階調領域VLとのそれぞれを駆動する2つの薄膜トランジスタTFTが同一のデータラインに接続されている構成に比べ、ソース電極とゲートラインとの重なり部分が短いので、それらの間の寄生キャパシタンスが小さい。従って、薄膜トランジスタTFTのソース電極4とゲートラインとの間の重なりに起因する寄生キャパシタンスが減少するので、その寄生キャパシタンスに起因する信号の歪曲が防止される。

#### 【0054】

図12は本発明の第9実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図であり、図13は本発明の第10実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。図12及び図13に示された液晶パネルでは、R、G、Bサブ画素のそれぞれが、好ましくは1:2の面積比を有する高階調領域VH及び低階調領域に分割され、各低階調領域が更に、面積の等しい第1低階調領域VL1と第2低階調領域VL2とに分割されている。R、G、Bサブ画素は、図12に示されたようなセンターライン構造に配置されていても良く、図13に示されたようなエッジアライン構造に配置されていても良い。

#### 【0055】

水平方向で隣接した2つのサブ画素の一方では、高階調領域VHが上部に配置され、第1低階調領域VL1と第2低階調領域VL2とが下部に配置されている。それら2つのサブ画素の他方では、高階調領域VHと第1低階調領域VL1とが上部に配置され、第2低階調領域VL2が下部に配置され、上部に位置する第1低階調領域VL1に接続されている。すなわち、各サブ画素では、高階調領域VHが上部に位置するのに対し、第1低階調領域VL1と第2低階調領域VL2とのいずれか一方又は両方が下部に位置する。例えば図12では、Gサブ画素の高階調領域VHが上部に配置され、第1低階調領域VL1と第2低階調領域VL2とが共に下部に配置されている。一方、Gサブ画素の両側に隣接したRサブ画素及びBサブ画素では、高階調領域VHと第1低階調領域VL1とが上部に配置され、第2低階調領域VL2が下部に配置されている。尚、第2低階調領域VL2は、上部に位置する第1低階調領域VL1に接続されている。こうして、R、G、Bサブ画素のいずれでも高階調領域VHが上部に位置する一方、Gサブ画素では第1低階調領域VL1と第2低階調領域VL2とが共に下部に位置し、Rサブ画素及びBサブ画素では第1低階調領域VL1と第2低階調領域VL2とがそれぞれ、上下に位置する。

#### 【0056】

R、G、Bサブ画素では、高階調領域VHが、第1ゲートラインGL1に接続された薄膜トランジスタTFTによって駆動され、低階調領域VL1、VL2が、第2ゲートラインGL2に接続された薄膜トランジスタTFTによって駆動される。ここで、第1ゲートラインGL1は、各サブ画素を上下に分割する二つの階調領域の間の境界部に重なっている。第2ゲートラインGL2は、上下方向で隣接した二つのサブ画素間の境界部に重なっている。第1ストレージラインSTL1は、第1ゲートラインGL1の上に位置する各階調領域の折れ曲がり部分の頂点に重なっている。第2ストレージラインSTL2は、第1ゲートラインGL1の下に位置する各階調領域の折れ曲がり部分の頂点に重なっている。R、G、B高階調領域VHは、第1ゲートラインGL1と第1乃至第3データラインDL1、DL2、DL3のそれぞれとで形成された薄膜トランジスタTFTによって駆動される。これらの薄膜トランジスタTFTは、第1ストレージラインSTL1に重なっているコンタクト部8を介して各高階調領域VHに接続されている。一方、R、G、B低階調領域VL1、VL2は、第2ゲートラインGL2と第1乃至第3データラインDL1、DL2、DL3とのそれぞれで形成された薄膜トランジスタTFTによって駆動される。これらの薄膜トランジスタTFTは、第2ストレージラインSTL2に重なっているコンタクト部8を介して第1低階調領域VL1と第2低階調領域VL2とのいずれかに接続されている。第1ゲートラインGL1が駆動される水平同期期間では、R、G、B高階調領域VHのそれぞれに高階調データ信号が供給される。第2ゲートラインGL2が駆動される水平同期期間では、R、G

10

20

30

40

50

、B低階調領域VL1、VL2のそれぞれに低階調データ信号が供給される。その結果、R、G、Bサブ画素のそれぞれでは、高階調領域VHと低階調領域VL1、VL2とで表現される高階調及び低階調の組み合わせにより、目標の階調が表現される。

#### 【0057】

以上のように、図12及び図13に示された液晶パネルでは、サブ画素のマトリックスの各行の高階調領域VHが同一の水平ライン上に配置され、同じゲートラインGL1に接続されている。一方、第1低階調領域VL1と第2低階調領域VL2との少なくともいずれかが、高階調領域VHの配置された水平ラインとは別の水平ラインに配置され、高階調領域VHに接続されたゲートラインGL1とは別のゲートラインGL2に接続されている。それにより、図4に示されたアナログ変調方式で一つのデータ信号から分離された高階調データ信号及び低階調データ信号に従い、高階調領域VHと低階調領域VL1、VL2とを別々に駆動できる。更に、全ての薄膜トランジスタTFTがゲートラインから同じ方向に突出しているので、例えば図8のように、薄膜トランジスタごとに突出方向が上下に変化する構成より、サブ画素の開口率を向上できる。

#### 【画面の簡単な説明】

#### 【0058】

【図1】本発明の第1実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。

【図2】本発明の第2実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。

【図3】図1及び図2に示された液晶パネルを用いた本発明の第1実施例による液晶表示装置を示したブロック図である。

#### 【図4】本発明の第2実施例による液晶表示装置を示したブロック図である。

#### 【図5】図4に示されたガンマ電圧部で適用されるガンマ特性を示したグラフである。

【図6】本発明の第3実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。

【図7】本発明の第4実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。

【図8】本発明の第5実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。

【図9】本発明の第6実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。

【図10】本発明の第7実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。

【図11】本発明の第8実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。

【図12】本発明の第9実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。

【図13】本発明の第10実施例によるVAモード液晶パネルの一つの画素の構造を示した平面図である。

#### 【符号の説明】

#### 【0059】

VH 高階調領域

VL 低階調領域

2 ゲート電極

4 ソース電極

6 ドレイン電極

8 コンタクト部

12、30 液晶パネル

14、24 ゲートドライバ

10

20

30

40

50

- 16、26 データドライバ

18、38 ガンマ電圧部

32 スイッチ

20、40 タイミングコントローラ

34 高階調ガンマ電圧部

36 低階調ガンマ電圧部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

| (51)Int.Cl. | F I     | テーマコード(参考)   |

|-------------|---------|--------------|

|             | G 0 9 G | 3/20 6 4 1 Q |

|             | G 0 9 G | 3/20 6 4 1 G |

|             | G 0 9 G | 3/20 6 4 1 C |

|             | G 0 9 G | 3/20 6 4 1 K |

(72)発明者 柳 承 厚

大韓民国京畿道城南市盆唐区藪内洞口ヤルフェリスハウスビルビー - 1202号

(72)発明者 金 賢 ウク

大韓民国京畿道龍仁市器興邑 三星電子(株) 器興工場エルシーディー総括エルシーディー開発室

液晶技術チーム

(72)発明者 都 熙 旭

大韓民国京畿道水原市勸善区梅橋洞177-99スヨンアートビル302号

(72)発明者 金 ヨン 周

大韓民国京畿道水原市靈通区梅灘洞111-74番地202号

F ターム(参考) 2H092 GA13 GA20 HA04 JA24 JB05 JB46 JB69 NA01 PA06 QA09

2H093 NA16 NA43 NA53 NA54 NC10 NC12 NC16 NC34 NC66 ND06

ND13 NE03 NF09

5C006 AA12 AA16 AA17 AA22 AF46 AF51 BB16 FA54

5C080 AA10 BB05 CC03 DD03 EE29 EE30 FF11 JJ02 JJ04 JJ05

JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶面板的驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP2007086791A5</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2009-10-22 |

| 申请号            | JP2006258289                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2006-09-25 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 申キヨン周<br>チャンハクスン<br>柳承厚<br>金賢ウク<br>都熙旭<br>金ヨン周                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 申 ▲キヨン▼ 周<br>チャン ハク スン<br>柳 承 厚<br>金 賢 ▲ウク▼<br>都 熙 旭<br>金 ▲ヨン▼ 周                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号         | G02F1/1343 G02F1/133 G02F1/1368 G09G3/36 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | G09G3/3648 G02F2001/134345 G09G3/3696 G09G2300/0443 G09G2300/0447 G09G2320/0673                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| FI分类号          | G02F1/1343 G02F1/133.575 G02F1/133.550 G02F1/1368 G09G3/36 G09G3/20.641.Q G09G3/20.641.G G09G3/20.641.C G09G3/20.641.K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号      | 2H092/GA13 2H092/GA20 2H092/HA04 2H092/JA24 2H092/JB05 2H092/JB46 2H092/JB69 2H092/NA01 2H092/PA06 2H092/QA09 2H093/NA16 2H093/NA43 2H093/NA53 2H093/NA54 2H093/NC10 2H093/NC12 2H093/NC16 2H093/NC34 2H093/NC66 2H093/ND06 2H093/ND13 2H093/NE03 2H093/NF09 5C006/AA12 5C006/AA16 5C006/AA17 5C006/AA22 5C006/AF46 5C006/AF51 5C006/BB16 5C006/FA54 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD03 5C080/EE29 5C080/EE30 5C080/FF11 5C080/JJ02 5C080/JJ04 5C080/JJ05 5C080/JJ06 2H192/AA24 2H192/AA43 2H192/BA13 2H192/BA25 2H192/BC24 2H192/BC31 2H192/DA12 2H192/DA43 2H192/DA72 2H192/EA42 2H192/GD61 2H192/JA13 2H193/ZA04 2H193/ZD23 2H193/ZD24 2H193/ZF22 2H193/ZF36 2H193/ZH40 2H193/ZH43 2H193/ZP03 2H193/ZQ08 |         |            |

| 优先权            | 1020050088460 2005-09-23 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 其他公开文献         | JP2007086791A<br>JP5059363B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

**摘要(译)**

要解决的问题：提供一种能够改善多畴VA模式中的子像素的侧面可视性和透射率的液晶面板，一种用于驱动该液晶面板的方法，以及使用该液晶面板的液晶显示装置。解决方案：液晶面板包括分割上下的子像素，并分成第一灰度区域和具有不同区域的第二灰度区域。每个灰度区域的两侧在水平方向上对称地弯曲。第一灰度区域和第二灰度区域分别在水平方向和垂直方向上交替布置，并且特别地，每个灰度区域的弯曲部分中的顶点沿水平方向布置。结果，在垂直方向上排列的灰度区域的边界线构成Z字形排列。通过以这样的方式从垂直方向倾斜地倾斜的灰度区域的边界线，在子像素之间产生的侧电场的方向与每个子像素的域内的边缘电场的方向对齐。。当驱动多条栅极线中的一条栅极线时驱动第一灰度级区域，而当驱动另一条栅极线时驱动第二灰度级区域。Ž