(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-293373

(P2006-293373A)

(43) 公開日 平成18年10月26日(2006.10.26)

(51) Int.CI.

G02F 1/1343 (2006.01)

F 1

G02F 1/1343

テーマコード(参考)

2 H 0 9 2

審査請求 未請求 請求項の数 21 O L (全 27 頁)

(21) 出願番号 特願2006-110134 (P2006-110134)

(22) 出願日 平成18年4月12日 (2006.4.12)

(31) 優先権主張番号 10-2005-0030678

(32) 優先日 平成17年4月13日 (2005.4.13)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国 443-742 京畿道水原市靈通

区梅灘洞 416

(74) 代理人 110000051

特許業務法人共生国際特許事務所

(72) 発明者 金 東 奎

大韓民国 京畿道 龍仁市 豊徳川2洞

三星5次アパート 523棟 1305号

F ターム(参考) 2H092 GA12 GA14 HA03 JA24 NA01

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】一つの画素を二つの副画素に分割して、二つの副画素に別途の互いに異なるデータ電圧を印加することによって、側面視認性を向上させることができる、液晶表示装置を提供する。

【解決手段】行列形態に配列され、第1及び第2副画素を含む複数の画素を有する液晶表示装置において、前記各副画素は、第1及び第2副画素電極と、第1及び第2維持電極と、第1及び第2スイッチとを有し、前記第1及び第2スイッチは、第1及び第2ゲート電極と、前記各々のスイッチの第1及び第2ソース電極と、前記第1及び第2副画素電極に連結されている前記各々のスイッチの第1及び第2ドレン電極とを有し、第1の所定の電圧が前記第1副画素電極に印加され、第2の所定の電圧が前記第2副画素電極に印加される。

【選択図】 図6

**【特許請求の範囲】****【請求項 1】**

行列形態に配列され、第1及び第2副画素を含む複数の画素を有する液晶表示装置において、

前記各副画素は、第1及び第2副画素電極と、

第1及び第2維持電極と、

第1及び第2スイッチとを有し、

前記第1及び第2スイッチは、第1及び第2ゲート電極と、前記各々のスイッチの第1及び第2ソース電極と、前記第1及び第2副画素電極に連結されている前記各々のスイッチの第1及び第2ドレイン電極とを有し、

第1の所定の電圧が前記第1副画素電極に印加され、第2の所定の電圧が前記第2副画素電極に印加されることを特徴とする液晶表示装置。

**【請求項 2】**

前記第1の所定の電圧は、前記第2の所定の電圧より低いことを特徴とする請求項1に記載の液晶表示装置。

**【請求項 3】**

前記第1及び第2ドレイン電極は、前記第1及び第2維持電極と重なり、前記第1ドレイン電極と前記第1維持電極との重なり面積は、前記第2ドレイン電極と前記第2維持電極との重なり面積より大きいことを特徴とする請求項1に記載の液晶表示装置。

**【請求項 4】**

前記第1及び第2ゲート電極にゲート信号を各々伝達する第1及び第2ゲート線と、前記第1及び第2ソース電極にデータ電圧を各々伝達するデータ線とをさらに有することを特徴とする請求項1に記載の液晶表示装置。

**【請求項 5】**

前記第1及び第2ゲート線に印加されるゲート信号の時期は互いに異なることを特徴とする請求項4に記載の液晶表示装置。

**【請求項 6】**

前記ゲート信号を前記第1及び第2ゲート電極に伝達するゲート線と、

前記データ電圧を前記第1及び第2ソース電極に伝達する第1及び第2データ線とをさらに有することを特徴とする請求項1に記載の液晶表示装置。

**【請求項 7】**

前記ゲート信号を前記第1及び第2ゲート電極に伝達するゲート線と、

前記データ電圧を前記第1及び第2ソース電極に伝達するデータ線とをさらに有することを特徴とする請求項1に記載の液晶表示装置。

**【請求項 8】**

前記第1及び第2維持電極は、前記第1及び第2ドレイン電極と各々重なり、物理的電気的に互いに分離されていることを特徴とする請求項7に記載の液晶表示装置。

**【請求項 9】**

前記第1及び第2副画素電極に印加されるデータ電圧の大きさは互いに異なることを特徴とする請求項1に記載の液晶表示装置。

**【請求項 10】**

前記第1スイッチは第1薄膜トランジスタであり、前記第2スイッチは第2薄膜トランジスタであり、

前記第1薄膜トランジスタのチャンネルの幅とチャンネルの長さの比は、前記第2薄膜トランジスタのチャンネルの幅とチャンネルの長さの比より大きいことを特徴とする請求項1に記載の液晶表示装置。

**【請求項 11】**

前記第1副画素電極の面積は、前記第2副画素電極の面積より大きいことを特徴とする請求項1に記載の液晶表示装置。

**【請求項 12】**

10

20

30

40

50

行列形態に配列され、第1及び第2副画素を各々含む複数の画素と、

前記第1副画素に連結される第1ゲート線と、

前記第1ゲート線と交差して前記第1副画素に連結される第1データ線とを有し、

前記第2副画素は前記第1ゲート線及び前記第1データ線のうちの少なくとも一つに連結されることを特徴とする液晶表示装置。

【請求項13】

前記第1副画素のキックバック電圧と前記第2副画素のキックバック電圧の大きさは実質的に同一であり、

前記第1副画素に所定の電圧が印加され、前記第1副画素は前記第2副画素に印加された電圧より大きい電圧が印加されることを特徴とする請求項12に記載の液晶表示装置。 10

【請求項14】

前記第2副画素に連結される第2ゲート線をさらに有し、

前記第2副画素は、前記第1データ線に連結されることを特徴とする請求項12に記載の液晶表示装置。

【請求項15】

前記第1副画素は、前記第1ゲート線及び前記第1データ線に連結される第1スイッチング素子と、該第1スイッチング素子及び第1ストレージキャパシタに連結される第1液晶キャパシタとを有し、

前記第2副画素は、前記第2ゲート線及び前記第1データ線に連結される第2スイッチング素子と、該第2スイッチング素子に連結され前記第1液晶キャパシタより容量が小さい第2液晶キャパシタと、前記第2スイッチング素子に連結され、前記第1ストレージキャパシタより容量が小さい第2ストレージキャパシタとを有することを特徴とする請求項14に記載の液晶表示装置。 20

【請求項16】

前記第2副画素に連結される第2データ線をさらに有し、

前記第2副画素は、前記第1ゲート線に連結されることを特徴とする請求項12に記載の液晶表示装置。

【請求項17】

前記第1副画素は、前記第1ゲート線及び前記第1データ線に連結される第1スイッチング素子と、該第1スイッチング素子に連結される第1液晶キャパシタと、前記第1スイッチング素子に連結される第1ストレージキャパシタとを有し、 30

前記第2副画素は、前記第1ゲート線及び前記第2データ線に連結される第2スイッチング素子と、該第2スイッチング素子に連結され、前記第1液晶キャパシタより容量が小さい第2液晶キャパシタと、前記第2スイッチング素子に連結され、前記第1ストレージキャパシタより容量が小さい第2ストレージキャパシタとを有することを特徴とする請求項16に記載の液晶表示装置。

【請求項18】

行列形態に配列され、各々第1及び第2副画素を含む画素の列と、

前記第1副画素に連結される複数の第1ゲート線と、

前記第1ゲート線と交差して前記第1副画素に連結される複数の第1データ線とを有し。 40

前記各々の第1副画素は、前記第1ゲート線及び前記第1データ線に連結される第1スイッチング素子と、該第1スイッチング素子及び第1ストレージキャパシタに連結される第1液晶キャパシタとを有し、

前記各々の第2副画素は、前記第1ゲート線及び前記第1データ線のうちの少なくとも一つに連結される第2スイッチング素子と、該第2スイッチング素子に連結され、前記第1液晶キャパシタより容量が小さい第2液晶キャパシタと、前記第2スイッチング素子に連結され、前記第1ストレージキャパシタより容量が小さい第2ストレージキャパシタとを有することを特徴とする液晶表示装置。

【請求項19】

前記第1副画素は、所定の電圧が印加され、前記第1副画素は前記第2副画素に印加された電圧より大きい電圧が印加されることを特徴とする請求項18に記載の液晶表示装置。

#### 【請求項20】

前記第2スイッチング素子に各々連結される複数の第2ゲート線をさらに有し、

前記第2スイッチング素子のうちの一つは、前記第1データ線のうちの一つに連結されることを特徴とする請求項18に記載の液晶表示装置。

#### 【請求項21】

前記第2スイッチング素子に各々連結される複数の第2データ線をさらに有し、

前記第2スイッチング素子のうちの一つは、前記第1ゲート線のうちの一つに連結されることを特徴とする請求項18に記載の液晶表示装置。 10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は液晶表示装置に関し、特に一つの画素を二つの副画素に分割し、側面視認性の向上及びフリッカーなどの画質劣化を防止することのできる液晶表示装置に関する。 20

##### 【背景技術】

##### 【0002】

液晶表示装置は、現在最も広く使用されている平板表示装置のうちの一つであって、画素電極や共通電極などの電界生成電極が形成されている二枚の表示板、及びその間に挿入されている液晶層からなって、電界生成電極に電圧を印加して液晶層に電界を生成し、これにより液晶層の液晶分子の配向を決定して入射光の偏光を制御することによって、画像を表示する。 20

##### 【0003】

液晶表示装置の中でも、電圧が印加されない状態で液晶分子の長軸が上下表示板に対して垂直に配向された垂直配向モードの液晶表示装置は、コントラスト比が大きくて広い基準視野角の実現が容易であるので、脚光を浴びている。ここで、基準視野角とは、コントラスト比が1:10の視野角または階調間輝度反転限界角度を意味する。

垂直配向モードの液晶表示装置において、広視野角を実現するための手段としては、電界生成電極に切開部を形成する方法、及び電界生成電極上に突起を形成する方法などがある。切開部及び突起によって液晶分子の傾斜方向を決定することができるので、これらを使用して液晶分子の傾斜方向を多様な方向に分散させることによって、基準視野角を広くすることができる。 30

##### 【0004】

しかし、垂直配向モードの液晶表示装置は、前面視認性に比べて側面視認性が劣っている。例えば、切開部が形成されたPVA (p a t t e r n e d v e r t i c a l l y a l i g n e d) モードの液晶表示装置の場合には、側面に行くほど画像が明るくなり、深刻な場合には、高い階調の間の輝度差がなくなって画像がゆがんで見えることもある。

側面視認性を改善するために、一つの画素を二つの副画素に分割して、二つの副画素を容量性結合させた後、一方の副画素には電圧を直接印加し、他方の副画素には容量性結合による電圧下降を起こさせて、二つの副画素の電圧を異ならせることによって、透過率を異ならせる方法が提示された。 40

##### 【0005】

しかし、このような方法は、二つの副画素の透過率を所望の水準に正確に合わせることができず、特に色相によって光の透過率が異なるので、各色相に対する電圧配合を異ならせなければならないにもかかわらず、そうすることができない。また、容量性結合のための導電体の追加などにより開口率が低下し、容量性結合による電圧降下によって透過率が減少するという問題があった。

#### 【発明の開示】

**【発明が解決しようとする課題】****【0006】**

そこで、本発明は上記従来の液晶表示装置における問題点に鑑みてなされたものであつて、本発明の目的は、行列形態に配列され、第1及び第2副画素を含む複数の画素を有する液晶表示装置において、側面視認性を向上させ、また、フリッカーなどの画質劣化を防止することのできる液晶表示装置を提供することにある。

**【課題を解決するための手段】****【0007】**

上記目的を達成するためになされた本発明による液晶表示装置は、行列形態に配列され、第1及び第2副画素を含む複数の画素を有する液晶表示装置において、前記各副画素は、第1及び第2副画素電極と、第1及び第2維持電極と、第1及び第2スイッチとを有し、前記第1及び第2スイッチは、第1及び第2ゲート電極と、前記各々のスイッチの第1及び第2ソース電極と、前記第1及び第2副画素電極に連結されている前記各々のスイッチの第1及び第2ドレイン電極とを有し、第1の所定の電圧が前記第1副画素電極に印加され、第2の所定の電圧が前記第2副画素電極に印加されることを特徴とする。

**【0008】**

前記第1の所定の電圧は、前記第2の所定の電圧より低いことが好ましい。

前記第1及び第2ドレイン電極は、前記第1及び第2維持電極と重なり、前記第1ドレイン電極と前記第1維持電極との重なり面積は、前記第2ドレイン電極と前記第2維持電極との重なり面積より大きいことが好ましい。

前記第1及び第2ゲート電極にゲート信号を各々伝達する第1及び第2ゲート線と、前記第1及び第2ソース電極にデータ電圧を各々伝達するデータ線とをさらに有することが好ましい。

前記第1及び第2ゲート線に印加されるゲート信号の時期は互いに異なることが好ましい。

前記ゲート信号を前記第1及び第2ゲート電極に伝達するゲート線と、前記データ電圧を前記第1及び第2ソース電極に伝達する第1及び第2データ線とをさらに有することが好ましい。

前記ゲート信号を前記第1及び第2ゲート電極に伝達するゲート線と、前記データ電圧を前記第1及び第2ソース電極に伝達するデータ線をさらに有することが好ましい。

前記第1及び第2維持電極は、前記第1及び第2ドレイン電極と各々重なり、物理的電気的に互いに分離されていることが好ましい。

前記第1及び第2副画素電極に印加されるデータ電圧の大きさは互いに異なることが好ましい。

前記第1スイッチは第1薄膜トランジスタであり、前記第2スイッチは第2薄膜トランジスタであり、前記第1薄膜トランジスタのチャンネルの幅とチャンネルの長さの比は、前記第2薄膜トランジスタのチャンネルの幅とチャンネルの長さの比より大きいことが好ましい。

前記第1副画素電極の面積は前記第2副画素電極の面積より大きいことが好ましい。

**【0009】**

また、上記目的を達成するためになされた本発明による液晶表示装置は、行列形態に配列され、第1及び第2副画素を各々含む複数の画素と、前記第1副画素に連結される第1ゲート線と、前記第1ゲート線と交差して前記第1副画素に連結される第1データ線とを有し、前記第2副画素は前記第1ゲート線及び前記第1データ線のうちの少なくとも一つに連結されることを特徴とする。

**【0010】**

前記第1副画素のキックバック電圧及び前記第2副画素のキックバック電圧の大きさは実質的に同一であり、前記第1副画素に所定の電圧が印加され、前記第1副画素は前記第2副画素に印加された電圧より大きい電圧が印加されることが好ましい。

前記第2副画素に連結される第2ゲート線をさらに有し、前記第2副画素は、前記第1

10

20

20

30

40

50

データ線に連結されることが好ましい。

前記第1副画素は、前記第1ゲート線及び前記第1データ線に連結される第1スイッチング素子と、該第1スイッチング素子及び第1ストレージキャパシタに連結される第1液晶キャパシタとを有し、前記第2副画素は、前記第2ゲート線及び前記第1データ線に連結される第2スイッチング素子と、該第2スイッチング素子に連結され、前記第1液晶キャパシタより容量が小さい第2液晶キャパシタと、前記第2スイッチング素子に連結され、前記第1ストレージキャパシタより容量が小さい第2ストレージキャパシタとを有することが好ましい。

前記第2副画素に連結される第2データ線をさらに有し、前記第2副画素は、前記第1ゲート線に連結されることが好ましい。

前記第1副画素は、前記第1ゲート線及び前記第1データ線に連結される第1スイッチング素子と、該第1スイッチング素子に連結される第1液晶キャパシタと、前記第1スイッチング素子に連結される第1ストレージキャパシタとを有し、前記第2副画素は、前記第1ゲート線及び前記第2データ線に連結される第2スイッチング素子と、該第2スイッチング素子に連結され、前記第1液晶キャパシタより容量が小さい第2液晶キャパシタと、前記第2スイッチング素子に連結され、前記第1ストレージキャパシタより容量が小さい第2ストレージキャパシタとを有することが好ましい。

#### 【0011】

また、上記目的を達成するためになされた本発明による液晶表示装置は、行列形態に配列され、各々第1及び第2副画素を含む画素の列と、前記第1副画素に連結される複数の第1ゲート線と、前記第1ゲート線と交差して前記第1副画素に連結される複数の第1データ線とを有し、前記各々の第1副画素は、前記第1ゲート線及び前記第1データ線に連結される第1スイッチング素子と、該第1スイッチング素子及び第1ストレージキャパシタに連結される第1液晶キャパシタとを有し、前記各々の第2副画素は、前記第1ゲート線及び前記第1データ線のうちの少なくとも一つに連結される第2スイッチング素子と、該第2スイッチング素子に連結され、前記第1液晶キャパシタより容量が小さい第2液晶キャパシタと、前記第2スイッチング素子に連結され、前記第1ストレージキャパシタより容量が小さい第2ストレージキャパシタとを有することを特徴とする。

#### 【0012】

前記第1副画素は、所定の電圧が印加され、前記第1副画素は前記第2副画素に印加された電圧より大きい電圧が印加されることが好ましい。

前記第2スイッチング素子に各々連結される複数の第2ゲート線をさらに有し、前記第2スイッチング素子のうちの一つは、前記第1データ線のうちの一つに連結されることが好ましい。

前記第2スイッチング素子に各々連結される複数の第2データ線をさらに有し、前記第2スイッチング素子のうちの一つは、前記第1ゲート線のうちの一つに連結されることが好ましい。

#### 【発明の効果】

#### 【0013】

本発明に係る液晶表示装置によれば、一つの画素を二つの副画素に分割して、二つの副画素に別途の互いに異なるデータ電圧を印加することによって、側面視認性を向上させることができるという効果がある。

また、二つの副画素の面積を異ならすことによって、側面ガンマ曲線の歪曲を減少させることができ、特に二つの副画素の保持容量を調節することによって、二つの副画素のキックバック電圧を同一にすることができる、これによりフリッカーなどの画質劣化を防止することができるという効果がある。

#### 【発明を実施するための最良の形態】

#### 【0014】

次に、本発明に係る液晶表示装置を実施するための最良の形態の具体例を図面を参照しながら説明する。

図面では、各層及び領域を明確に表現するために、厚さを拡大して示した。明細書全体にかけて類似した部分については、同一の図面符号を付けた。層、膜、領域、板などの部分が他の部分の“上”にあるとする時、これは他の部分の“直上”にある場合だけでなく、その中間に他の部分がある場合も意味する。反対に、ある部分が他の部分の“直上”にあるとする時、これはその中間に他の部分がない場合を意味する。

#### 【0015】

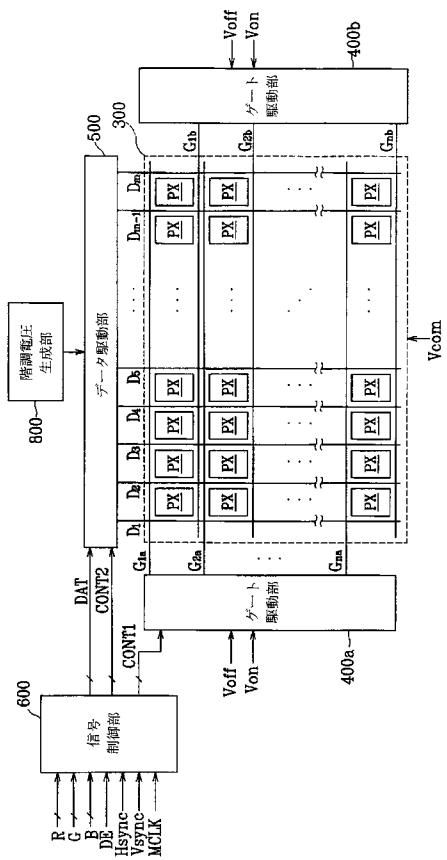

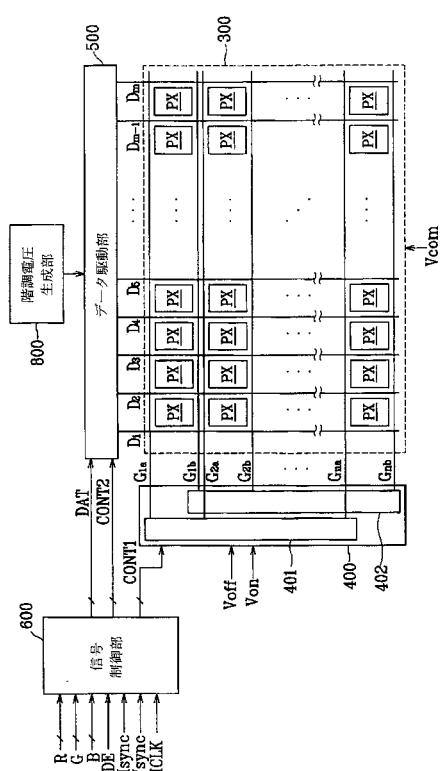

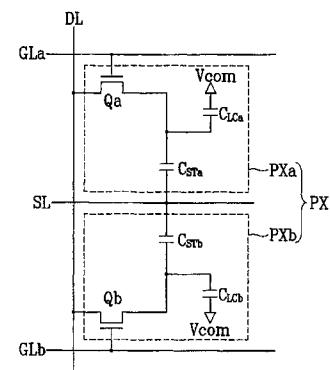

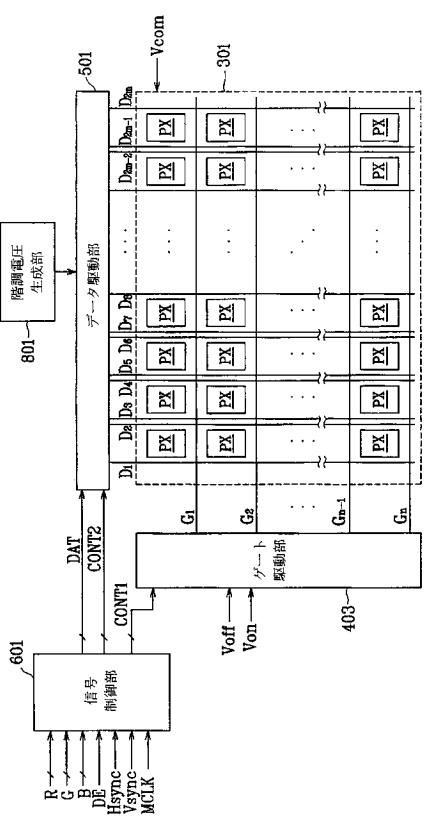

図1乃至図3は本発明の一実施形態による液晶表示装置のブロック図であり、図4は本発明の一実施形態による液晶表示装置の一つの画素に対する等価回路図であり、図5は本発明の一実施形態による液晶表示装置の一つの副画素に対する等価回路図である。

#### 【0016】

図1乃至図3を参照すれば、本発明の一実施形態による液晶表示装置は、液晶表示板組立体 (liquid crystal panel assembly) 300、これに連結された一対または一つのゲート駆動部 400a、400b、400及びデータ駆動部 500、データ駆動部 500に連結された階調電圧生成部 800、そしてこれらを制御する信号制御部 600を含む。

液晶表示板組立体 300は、等価回路で見る時、複数の表示信号線 ( $G_{1a}$  -  $G_{n_b}$ 、 $D_1$  -  $D_m$ )、及びこれに連結されていて、ほぼ行列形態に配列されている複数の画素 ( $P_X$ )を含む。反面、図5に示したように、液晶表示板組立体 300は、構造で見る時、互いに対向する下部及び上部表示板 100、200、及びこれらの間に挿入されている液晶層 3を含む。

表示信号線 ( $G_{1a}$  -  $G_{n_b}$ 、 $D_1$  -  $D_m$ )は、下部表示板 100に形成されていて、ゲート信号(走査信号ともいう)を伝達する複数のゲート線 ( $G_{1a}$  -  $G_{n_b}$ )及びデータ信号を伝達するデータ線 ( $D_1$  -  $D_m$ )を含む。ゲート線 ( $G_{1a}$  -  $G_{n_b}$ )は、ほぼ行方向にのびていて、互いにほぼ平行であり、データ線 ( $D_1$  -  $D_m$ )は、ほぼ列方向にのびていて、互いにほぼ平行である。

#### 【0017】

図4には、表示信号線及び一つの画素 ( $P_X$ )の等価回路が示されているが、図面符号  $GL_a$ 、 $GL_b$ で示したゲート線及び図面符号  $DL$ で示したデータ線以外にも、表示信号線は、ゲート線 ( $GL_a$ 、 $GL_b$ )とほぼ平行にのびた維持電極線 ( $SL$ )をさらに含む。

各画素 ( $P_X$ )は、一対の副画素 ( $P_Xa$ 、 $P_Xb$ )を含み、各副画素 ( $P_Xa$ 、 $P_Xb$ )は、ゲート線 ( $GL_a$ 、 $GL_b$ )及びデータ線 ( $DL$ )に連結されているスイッチング素子 ( $Q_a$ 、 $Q_b$ )、これに連結されている液晶キャパシタ (liquid crystal capacitor) ( $C_{LCa}$ 、 $C_{LCb}$ )、そしてスイッチング素子 ( $Q_a$ 、 $Q_b$ )及び維持電極線 ( $SL$ )に連結されているストレージキャパシタ (storage capacitor) ( $C_{STa}$ 、 $C_{STb}$ )を含む。

#### 【0018】

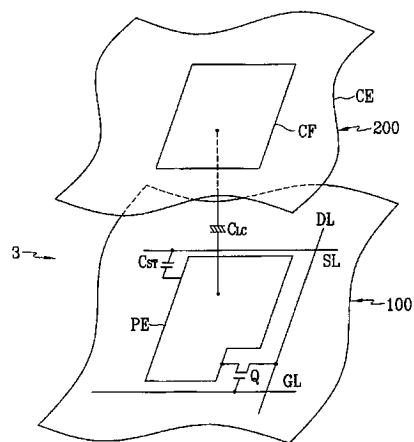

図5を参照すれば、各副画素 ( $P_Xa$ 、 $P_Xb$ )のスイッチング素子 ( $Q$ )は、下部表示板 100に形成されている薄膜トランジスタなどからなり、各ゲート線 ( $GL$ )に連結されている制御端子、データ線 ( $DL$ )に連結されている入力端子、そして液晶キャパシタ ( $C_{LC}$ )及びストレージキャパシタ ( $C_{ST}$ )に連結されている出力端子を含む三端子素子である。

液晶キャパシタ ( $C_{LC}$ )は、下部表示板 100の副画素電極 ( $PE$ )及び上部表示板 200の共通電極 ( $CE$ )を二つの端子とし、二つの電極 ( $PE$ 、 $CE$ )の間の液晶層 3は誘電体として機能する。副画素電極 ( $PE$ )は、スイッチング素子 ( $Q$ )に連結され、共通電極 ( $CE$ )は、上部表示板 200の全面に形成されていて、共通電圧  $V_{com}$ の印加を受ける。図5とは異なって、共通電極 ( $CE$ )が下部表示板 100に形成される場合もあり、この時には、二つの電極 ( $PE$ 、 $CE$ )のうちの少なくとも一つが線状または棒状に形成されることができる。

#### 【0019】

10

20

30

40

50

液晶キャパシタ (C<sub>Lc</sub>) の補助的な役割を果たすストレージキャパシタ (C<sub>sT</sub>) は、下部表示板 100 に形成された維持電極線 (SL) 及び画素電極 (PE) が絶縁体を間において重畳して形成されて、維持電極線 (SL) には共通電圧 V<sub>com</sub> などの決められた電圧が印加される。しかし、ストレージキャパシタ (C<sub>sT</sub>) は、副画素電極 (PE) 及び真上の前段ゲート線が絶縁体を間において重畳して形成されることもできる。

#### 【0020】

一方、色表示を実現するためには、各画素が原色 (primary color) のうちの一つを固有に表示したり (空間分割)、各画素が時間によって交互に三原色を表示する (時間分割) ようにして、これら三原色の空間的、時間的合計によって所望の色相が認識されるようとする。原色の例としては、赤色、緑色、及び青色がある。図 5 は空間分割の一例として、上部表示板 200 の各画素領域に原色のうちの一つを示す色フィルタ (CF) が形成されていることが示されている。図 5 とは異なって、色フィルタ (CF) は下部表示板 100 の副画素電極 (PE) 上または下に形成されることもできる。

#### 【0021】

図 1 乃至図 3 を参照すれば、ゲート駆動部 400a、400b、400 は、ゲート線 (G<sub>1a</sub> - G<sub>nb</sub>) に連結されて、外部からのゲートオン電圧 (V<sub>on</sub>) 及びゲートオフ電圧 (V<sub>off</sub>) の組合せからなるゲート信号をゲート線 (G<sub>1a</sub> - G<sub>nb</sub>) に印加する。図 1 に示した一対のゲート駆動部 400a、400b は、各々液晶表示板組立体 300 の左右に位置して、奇数番目及び偶数番目のゲート線 (G<sub>1a</sub> - G<sub>nb</sub>) に各々連結され、図 2 及び図 3 に示した一つのゲート駆動部 400 は、液晶表示板組立体 300 の一側に位置して、全てのゲート線 (G<sub>1a</sub> - G<sub>nb</sub>) に連結されているが、図 3 の場合、ゲート駆動部 400 内に二つの駆動回路 401、402 が内蔵されていて、各々奇数番目及び偶数番目のゲート線 (G<sub>1a</sub> - G<sub>nb</sub>) に連結されている。

#### 【0022】

階調電圧生成部 (gray voltage generator) 800 は、画素の透過率に関する二つの階調電圧の集合 (または基準階調電圧の集合) を生成する。二つの階調電圧の集合は、一つの画素を構成する二つの副画素に独立的に提供されるものであって、各階調電圧の集合は、共通電圧 V<sub>com</sub> に対して正の値を有するもの及び負の値を有するものを含む。しかし、二つの (基準) 階調電圧の集合の代わりに、一つの (基準) 階調電圧の集合のみを生成することもできる。

データ駆動部 500 は、液晶表示板組立体 300 のデータ線 (D<sub>1</sub> - D<sub>m</sub>) に連結されて、階調電圧生成部 800 からの二つの階調電圧の集合のうちの一つを選択し、選択された階調電圧の集合に属する一つの階調電圧をデータ電圧として画素に印加する。しかし、階調電圧生成部 800 が階調全体に対する電圧を提供せずに基準階調電圧のみを提供する場合、データ駆動部 500 は、基準階調電圧を分圧して階調全体に対する階調電圧を生成して、この中からデータ電圧を選択する。

#### 【0023】

ゲート駆動部 400、400a、400b またはデータ駆動部 500 は、一つ以上の駆動集積回路チップの形態で液晶表示板組立体 300 上に直接装着されたり、可撓性印刷回路膜 (flexible printed circuit film) (図示せず) 上に装着されて TCP (tape carrier package) の形態で液晶表示板組立体 300 に付着することができる。これとは異なって、ゲート駆動部 400、400a、400b またはデータ駆動部 500 は、液晶表示板組立体 300 に集積することもできる。

信号制御部 600 は、ゲート駆動部 400 及びデータ駆動部 500 などの動作を制御する。

#### 【0024】

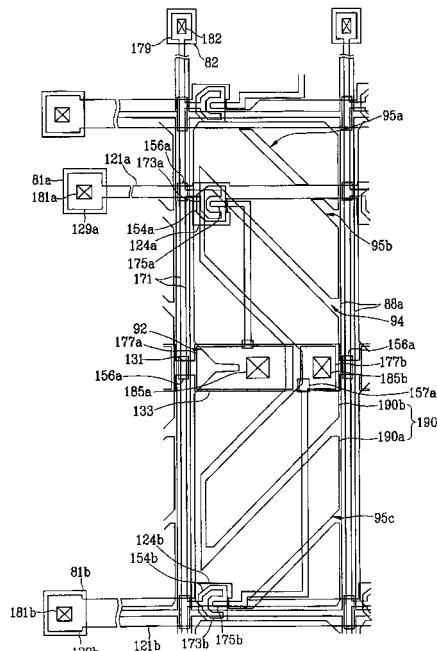

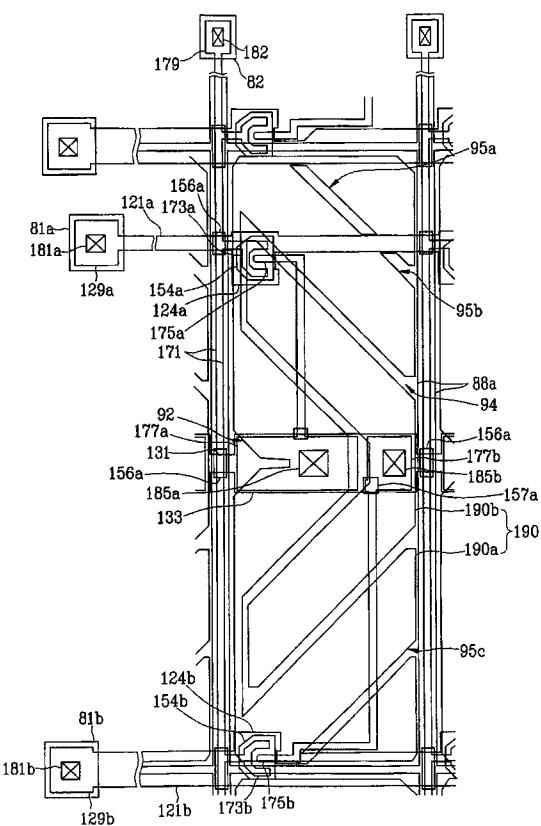

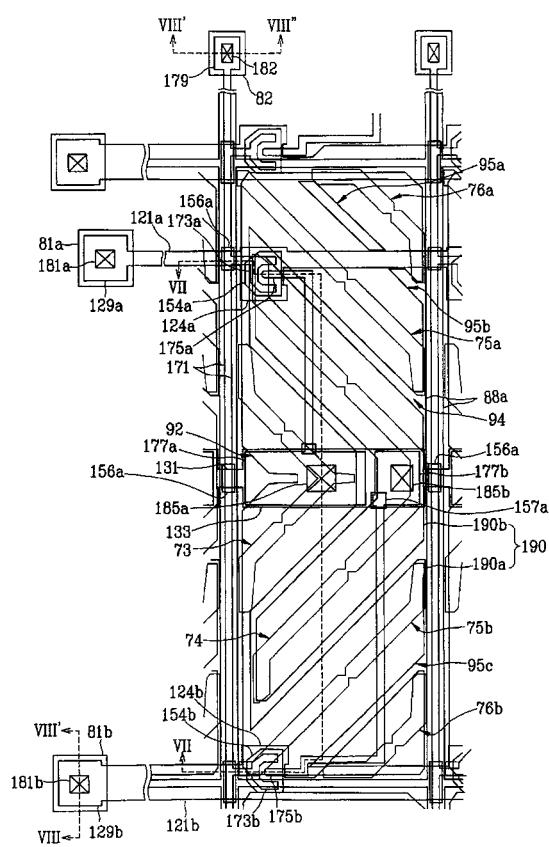

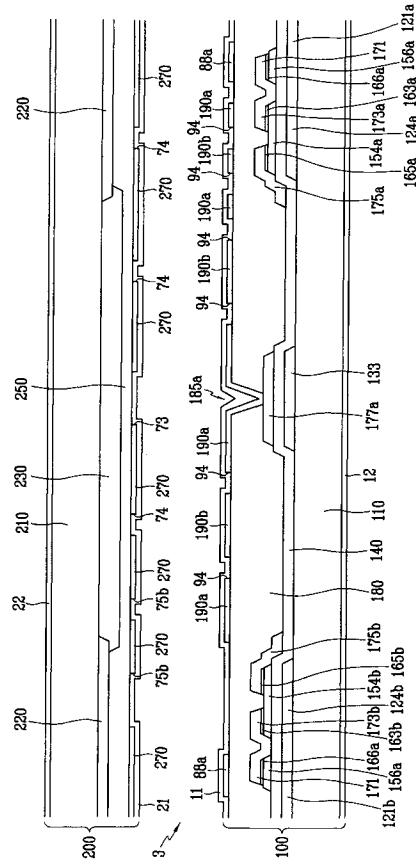

次に、このような液晶表示板組立体 300 の構造について、図 6 乃至図 10 を参照して詳細に説明する。

図 6 は本発明の一実施形態による液晶表示装置の下部表示板の配置図であり、図 7 は本

10

20

30

40

50

発明の一実施形態による液晶表示装置の上部表示板の配置図であり、図8は図6の下部表示板及び図7の上部表示板を含む液晶表示板組立体の配置図である。図9及び図10は各々図8の液晶表示板組立体のVII-VII線、及びVII'I-VII'I'線、VII'I'-VII'I''線に沿った断面図である。

#### 【0025】

図6乃至図10を参照すれば、本実施形態による液晶表示装置は、下部表示板100、これと対向している上部表示板200、及びこれらの間に挿入されている液晶層3を含む。

まず、図6、図8乃至図10を参照して、下部表示板100について詳細に説明する。

透明なガラスまたはプラスチックなどからなる絶縁基板110上に、複数対の第1及び第2ゲート線(gate line)121a、121b及び複数の維持電極線(storage electrode lines)131が形成されている。

#### 【0026】

第1及び第2ゲート線121a、121bは、主に横方向にのびていて、物理的、電気的に互いに分離されていて、ゲート信号を伝達する。第1及び第2ゲート線121a、121bは、各々上側及び下側に配置されていて、下側及び上側に突出した複数の第1及び第2ゲート電極124a、124bと他の層または外部駆動回路との連結のために、面積が拡張されて、左側に配置されている端部129a、129bを含む。しかし、これら端部129a、129bは、二つとも右側に配置されたり、各々左側及び右側に配置することもできる。

維持電極線131は、主に横方向にのびていて、第2ゲート線121bより第1ゲート線121aに近く、複数の維持電極133を含む。維持電極133は、ほぼ長方形で、維持電極線131に対称である。しかし、維持電極133をはじめとする維持電極線131の形状及び配置は、多様に変更することができる。維持電極線131には、上部表示板200の共通電極(common electrode)270に印加される共通電圧(common voltage)などの所定の電圧が印加される。

#### 【0027】

ゲート線121a、121b及び維持電極線131は、アルミニウム(A1)やアルミニウム合金などのアルミニウム系金属、銀(Ag)や銀合金などの銀系金属、銅(Cu)や銅合金などの銅系金属、モリブデン(Mo)やモリブデン合金などのモリブデン系金属、クロム(Cr)、チタニウム(Ti)、タンタル(Ta)などからなることができる。

しかし、ゲート線121a、121b及び維持電極線131は、物理的性質が異なる二つの導電膜(図示せず)を含む多重膜構造からなることもできる。この時、このうちの一つの導電膜は、ゲート線121a、121b及び維持電極線131の信号遅延や電圧降下を減少させることができるように、低い比抵抗(resistivity)の金属、例えばアルミニウム系金属、銀系金属、銅系金属などからなる。

#### 【0028】

これとは異なって、他の一つの導電膜は、他の物質、特にITO(indium tin oxide)及びIZO(indium zinc oxide)との接触特性が優れている物質、例えばモリブデン系金属、クロム、チタニウム、タンタルなどからなる。これらの組合せの好ましい例としては、クロムの下部膜及びアルミニウム(合金)の上部膜や、アルミニウム(合金)の下部膜及びモリブデン(合金)の上部膜がある。しかし、ゲート線121a、121b及び維持電極線131は、この他にも多様な金属及び導電体からなることができる。

#### 【0029】

また、ゲート線121a、121b及び維持電極線131の側面は、基板110の表面に対して傾いていて、その傾斜角は約30~80°であることが好ましい。

ゲート線121a、121b及び維持電極線131上には、窒化ケイ素(SiNx)などからなるゲート絶縁膜(gate insulating layer)140が形成されている。

10

20

30

40

50

ゲート絶縁膜 140 上には、水素化非晶質シリコン (hydrogenated amorphous silicon) (非晶質シリコンは略して a-Si とする) または多結晶シリコン (polycrystalline silicon) などからなる複数の島型の半導体 154a、154b、156a、157a が形成されている。半導体 154a、154b は、各々ゲート電極 124a、124b 上に位置する。

## 【0030】

半導体 154a、154b、156a 上には、シリサイド (silicide) またはリンなどの n 型不純物が高濃度にドーピングされている n+ 水素化非晶質シリコンなどの物質からなる複数の島型の抵抗性接触部材 (ohmic contact) 163a、163b、165a、165b、166a が形成されている。抵抗性接触部材 163a、165a 及び抵抗性接触部材 163b、165b は、各々対をなして半導体 154a、154b 上に位置し、抵抗性接触部材 166a は、半導体 156a 上に位置する。

半導体 154a、154b、156a、157a 及び抵抗性接触部材 163a、163b、165a、165b、166a の側面も、基板 110 の表面に対して傾いていて、その傾斜角は 30~80° である。

## 【0031】

抵抗性接触部材 163a、163b、165a、165b、166a 及びゲート絶縁膜 140 上には、複数のデータ線 (data line) 171 及び複数対の第 1 及び第 2 ドレイン電極 (drain electrode) 175a、175b が形成されている。

データ線 171 は、主に縦方向にのびていて、ゲート線 121a、121b 及び維持電線 131 と交差してデータ電圧 (data voltage) を伝達する。各データ線 171 は、第 1 及び第 2 ゲート電極 124a、124b に向かって各々のびた複数の第 1 及び第 2 ソース電極 (source electrode) 173a、173b と他の層または外部装置との接続のために、幅が拡張されている端部 179 を含む。

## 【0032】

第 1 及び第 2 ドレイン電極 175a、175b は、データ線 171 と分離されていて、各々ゲート電極 124a、124b を中心にソース電極 173a、173b と対向している。第 1 及び第 2 ドレイン電極 175a、175b は、各々半導体 154a、154b 上に位置した棒状の端部から始まって維持電極 133 と重畳する面積が広い拡張部 177a、177b を有し、棒状の端部は、U 字型に曲がったソース電極 173a、173b で一部が囲まれている。ここで、第 2 ドレイン電極 175b の拡張部 177b の面積は、第 1 ドレイン電極 175a の拡張部 177a の面積より小さい。

第 1、第 2 ゲート電極 124a、124b、第 1、第 2 ソース電極 173a、173b、及び第 1、第 2 ドレイン電極 175a、175b は、半導体 154a、154b と共に第 1、第 2 薄膜トランジスタ (Qa、Qb) を構成し、薄膜トランジスタ (Qa、Qb) のチャンネルは、第 1、第 2 ソース電極 173a、173b 及び第 1、第 2 ドレイン電極 175a、175b の間の半導体 154a、154b に形成される。

## 【0033】

データ線 171 及びドレイン電極 175a、175b は、モリブデン、クロム、タンタル、及びチタニウムなどの耐火性金属 (refractory metal) またはこれらの合金からなるのが好ましく、耐火性金属膜 (図示せず) 及び低い比抵抗の導電膜 (図示せず) を含む多重膜構造からなることができる。多重膜構造の例としては、クロムまたはモリブデン (合金) の下部膜及びアルミニウム (合金) の上部膜の二重膜、モリブデン (合金) の下部膜、アルミニウム (合金) の中間膜、及びモリブデン (合金) の下部膜の三重膜がある。しかし、データ線 171 及びドレイン電極 1175a、175b は、この他にも多様な金属または導電体からなることができる。

データ線 171 及びドレイン電極 175a、175b の側面も、ゲート線 121a、121b 及び維持電線 131 と同様に傾いていて、その傾斜角は各々約 30~80° の角度である。

10

20

30

40

50

## 【0034】

抵抗性接触部材 163a、163b、165a、165b、166a は、その下部の半導体 154a、154b、156a、157a 及びその上部のデータ線 171 及びドレイン電極 175a、175b の間にだけ存在して、接触抵抗を低くする役割を果たす。島型の半導体 154a、154b は、ソース電極 173a、173b 及びドレイン電極 175a、175b で覆われずに露出された部分を有し、半導体 156a、157a は、ゲート線 121a、121b 及び維持電極線 131 の表面のプロファイルをスムーズにして、データ線 171 及びドレイン電極 175a、175b の断線を防止する。

## 【0035】

データ線 171 及びドレイン電極 175a、175b、及び露出された半導体 154a、154b 上には、保護膜 (passivation layer) 180 が形成されている。保護膜 180 は、窒化ケイ素や酸化ケイ素などの無機絶縁物、有機絶縁物、低誘電率絶縁物などからなる。有機絶縁物及び低誘電率絶縁物の誘電定数は 4.0 以下であるのが好ましく、低誘電率絶縁物の例としては、プラズマ化学気相蒸着 (plasma enhanced chemical vapor deposition; PECVD) で形成される a-Si:C:O、a-Si:O:F などがある。有機絶縁物のうちの感光性 (photosensitivity) を有するもので保護膜 180 を形成することもでき、保護膜 180 の表面は平坦でありえる。しかし、保護膜 180 は、有機膜の優れた絶縁特性を生かしながら、露出された半導体 154a、154b 部分に被害を及ぼさないように、下部無機膜及び上部有機膜の二重膜構造からなることもできる。

## 【0036】

保護膜 180 には、データ線 171 の端部 179 及びドレイン電極 175a、175b の拡張部 177a、177b を各々露出する複数の接触孔 182、185a、185b が形成され、保護膜 180 及びゲート絶縁膜 140 には、ゲート線 121a、121b の端部 129a、129b を露出する複数の接触孔 181a、181b が各々形成されている。

保護膜 180 上には、第 1 及び第 2 副画素電極 (subpixel electrode) 190a、190b を含む複数の画素電極 (pixel electrode) 190、遮蔽電極 (shielding electrode) 88a、及び複数の接触補助部材 (contact assistant) 81a、81b、82 が形成されている。これらは、ITO または IZO などの透明導電物質やアルミニウム、銀またはその合金などの反射性金属からなる。

## 【0037】

第 1、第 2 副画素電極 190a、190b は、接触孔 185a、185b を通じて第 1、第 2 ドレイン電極 175a、175b と物理的・電気的に連結されて、第 1、第 2 ドレイン電極 175a、175b からデータ電圧の印加を受ける。一対の副画素電極 190a、190b には、一つの入力画像信号に対して予め設定されている互いに異なるデータ電圧が印加されるが、その大きさは副画素電極 190a、190b の大きさ及び形状によって設定される。また、副画素電極 190a、190b の面積は互いに異なることもある。

一例として、第 2 副画素電極 190b は、第 1 副画素電極 190a に比べて高い電圧の印加を受けて、第 1 副画素電極 190a より面積が小さい。

## 【0038】

データ電圧が印加された副画素電極 190a、190b は、共通電極 270 と共に電場を生成することによって、二つの電極 190、270 の間の液晶層 3 の液晶分子の配向を決定する。

また、上述説明したように、各副画素電極 190a、190b 及び共通電極 270 は、液晶キャパシタ ( $C_{LCa}$ 、 $C_{LCb}$ ) を構成して、薄膜トランジスタ ( $Qa$ 、 $Qb$ ) がターンオフされた後にも印加された電圧を維持し、電圧維持能力を強化するために、液晶キャパシタ ( $C_{LCa}$ 、 $C_{LCb}$ ) と並列に連結されたストレージキャパシタ ( $C_{STA}$ 、 $C_{STb}$ ) は、第 1 及び第 2 副画素電極 190a、190b 及びこれに連結されている

10

20

30

40

50

ドレイン電極 175a、175b の拡張部 177a、177b と維持電極 133 との重畠などによって形成される。

【0039】

第1副画素電極 190a の面積が第2副画素電極 190b の面積より大きいので、第1液晶キャパシタ ( $C_{Lc_a}$ ) の容量値が第2液晶キャパシタ ( $C_{Lc_b}$ ) の容量値より大きく、維持電極 133 と重畠する第1ドレイン電極 175a の拡張部 177a の面積が第2ドレイン電極 175b の拡張部 177b の面積より大きいので、第1ストレージキャパシタ ( $C_{ST_a}$ ) の容量値が第2ストレージキャパシタ ( $C_{ST_b}$ ) の容量値より大きい。したがって、第1薄膜トランジスタ ( $Q_a$ ) が第2薄膜トランジスタ ( $Q_b$ ) より電流駆動能力が大きくなければならないので、第1薄膜トランジスタ ( $Q_a$ ) の  $W : L$  の比の大きさが第2薄膜トランジスタ ( $Q_b$ ) の  $W : L$  の比の大きさより大きい。ここで、 $W$  はチャンネルの幅であり、 $L$  はチャンネルの長さである。

10

【0040】

各画素電極 190 は、4 つの角が面取りされていて、面取りされた斜辺はゲート線 121a、121b に対して約 45° の角度をなす。

一つの画素電極 190 を構成する一対の第1及び第2副画素電極 190a、190b は、間隙 (gap) 94 を間に置いて互いに噛み合っていて、画素電極 190 の外側境界はほぼ四角形である。第2副画素電極 190b は、ほぼ回転した等辺台形であって、下辺が台形にへこんでいて、大部分が第1副画素電極 190a で囲まれている。第1副画素電極 190a は、左側辺で互いに連結されている上部、下部、及び中央台形部からなる。第1副画素電極 190a は、上部台形部の上辺及び下部台形部の下辺から右側辺に向かってのびた切開部 95a、95b、95c を有している。切開部 95a、95b の間にゲート線 121a が通過する。

20

【0041】

第1副画素電極 190a の中央台形部は、第2副画素電極 190b のへこんでいる下辺に嵌合している。第1副画素電極 190a は、維持電極線 131 に沿ってのびた切開部 92 を有し、切開部 92 は、第1副画素電極 190a の左側辺に入口を有し、入口から横方向にのびた横部を有している。切開部 92 の入口は、維持電極線 131 に対して約 45° の角度をなす一対の斜辺を有している。第1副画素電極 190a 及び第2副画素電極 190b の間の間隙 94 は、ほぼ均一な幅を有してゲート線 121a、121b と約 45° の角度をなす二対の上部及び下部斜線部、及び実質的に均一な幅を有する三つの縦部を含む。

30

以下では、説明の便宜のために、間隙 94 も切開部と表現する。切開部 92、94、95a、95b、95c は、維持電極線 131 に対してほぼ反転対称 (inversion symmetry) をなしていて、これらはゲート線 121a、121b に対して約 45° の角度をなして互いに垂直にのびている。画素電極 190 は、これら切開部 92、94、95a、95b、95c によって複数の領域 (domain) に分割される。

【0042】

したがって、画素電極 190 を横方向に二等分する維持電極線 131 を中心にした上半部及び下半部は、切開部 92、94、95a～95c によって各々 4 つの領域に分割される。この時、領域の数または切開部の数は、画素の大きさ、画素電極 190 の横辺及び縦辺の長さの比、液晶層 3 の種類や特性などの設計要素によって変化する。

40

また、第1副画素電極 190a は、第1及び第2ゲート線 121a、121b と重畠し、第2副画素電極 190b は、第1ゲート線 121a と重畠して、第1ゲート線 121a は、画素電極 190 の上半部中心付近を通過する。

【0043】

遮蔽電極 88a は、データ線 171 に沿ってのびた縦部、及び第2ゲート線 121b に沿ってのびた横部を含むが、縦部はデータ線 171 を完全に覆っており、横部はゲート線 121b の境界線内側に位置する。遮蔽電極 88a は、保護膜 180 及びゲート絶縁膜 140 の接触孔 (図示せず) を通じて維持電極線 131 に連結されたり、共通電圧  $V_{com}$

50

を下部表示板 100 から上部表示板 200 に伝達する短絡点 (short point) (図示せず) に連結することもできる。

遮蔽電極 88a は、共通電圧  $V_{com}$  の印加を受けて、データ線 171 及び画素電極 190 の間、そしてデータ線 171 及び共通電極 270 の間で形成される電界を遮断して、画素電極 190 の電圧歪曲及びデータ線 171 が伝達するデータ電圧の信号遅延を減少させる。

#### 【0044】

また、画素電極 190 及び遮蔽電極 88a の短絡を防止するために、これらの間に距離をおかなければならぬので、画素電極 190 がデータ線 171 からさらに遠くなつて、これらの間の寄生容量が減少する。さらに、液晶層 3 の誘電率 (permittivity) が保護膜 180 の誘電率より高いため、データ線 171 及び遮蔽電極 88a の間の寄生容量が遮蔽電極 88a がない時のデータ線 171 及び共通電極 270 の間の寄生容量に比べて小さい。

それだけでなく、画素電極 190 及び遮蔽電極 88a が同一層に形成されるため、これらの間の距離が一定に維持されて、これによりこれらの間の寄生容量が一定になる。この時、開口率の低下が最少になるように、遮蔽電極 88a 及び画素電極 190 の間の距離を最少にするのが好ましい。

しかし、このような遮蔽電極 88a は必要に応じて省略することもできる。

#### 【0045】

接触補助部材 81a、81b、82 は、接触孔 181a、181b、182 を通じてゲート線 121a、121b の端部 129a、129b 及びデータ線 171 の端部 179 と各々連結される。接触補助部材 81a、81b、82 は、ゲート線 121a、121b の露出された端部 129a、129b 及びデータ線 171 の露出された端部 179 と外部装置との接着性を補完して、これらを保護する役割を果たす。

画素電極 190、遮蔽電極 88a、接触補助部材 81a、81b、82、及び保護膜 180 上には、液晶層 3 を配向する配向膜 11 が塗布されている。配向膜 11 は、水平配向膜でありうる。

#### 【0046】

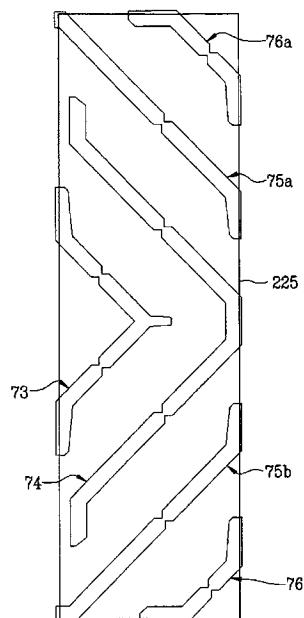

次に、図 7、図 9 を参照して、上部表示板 200 について詳細に説明する。透明なガラスなどからなる絶縁基板 210 上に、光漏れを防止するためのブラックマトリックスという遮光部材 220 が形成されている。遮光部材 220 は、画素電極 190 と対向して、画素電極 190 とほぼ同一な形状の複数の開口部 225 を有している。これとは異なつて、遮光部材 220 は、データ線 171 に対応する部分及び薄膜トランジスタ (Qa、Qb) に対応する部分からなることもできる。しかし、遮光部材 220 は、画素電極 190 及び薄膜トランジスタ (Qa、Qb) の付近での光漏れを遮断するために、多様な形状からなることができる。

#### 【0047】

基板 210 上には、また、複数の色フィルタ 230 が形成されている。色フィルタ 230 は、遮光部材 220 で囲まれた領域内に大部分が位置し、画素電極 190 に沿って縦方向に長くのびている。色フィルタ 230 は、赤色、緑色、及び青色などの原色のうちの一つを表示することができる。

色フィルタ 230 及び遮光部材 220 上には、色フィルタ 230 が露出されるのを防止して、平坦面を提供するための蓋膜 250 が形成されている。

蓋膜 250 上には、ITO、IZO などの透明な導電体などからなる共通電極 270 が形成されている。

#### 【0048】

共通電極 270 は、複数組の切開部 73、74、75a、75b、76a、76b の集合を有する。

一組の切開部 73 ~ 76b は、一つの画素電極 190 と対向していて、中央切開部 73、74、上部切開部 75a、76a、及び下部切開部 75b、76b を含む。切開部 73

10

20

30

40

50

~ 7 6 b は、隣接した画素電極 1 9 0 の切開部 9 2 ~ 9 5 c の間、及び周縁切開部 9 5 a ~ 9 5 c 及び画素電極 1 9 0 の角の間に配置されている。また、各切開部 7 3 ~ 7 6 b は、画素電極 1 9 0 の切開部 9 2 ~ 9 5 c と平行にのびた少なくとも一つの斜線部を含む。

上部及び下部切開部 7 5 a ~ 7 6 b は、画素電極 1 9 0 のほぼ右側辺から下側または上側辺に向かってのびた斜線部、そして斜線部の各端部から画素電極 1 9 0 の辺に沿って辺と重畠しながらのびて、斜線部と鈍角をなしている横部及び縦部を含む。

#### 【 0 0 4 9 】

中央切開部 7 3 は、維持電極 1 3 3 から維持電極 1 3 3 とほぼ斜角をなして画素電極 1 9 0 の左側辺に向かってのびた一対の斜線部、及び斜線部の各端部から画素電極 1 9 0 の左側辺に沿って左側辺と重畠しながらのびて、斜線部と鈍角をなしている縦断縦部を含む。中央切開部 7 4 は、画素電極 1 9 0 の右側辺に沿って右側辺と重畠しながらのびた縦部、縦部の各端部から画素電極 1 9 0 の左側辺に向かってのびた一対の斜線部、そして斜線部の各端部から副画素電極 1 9 0 b の左側辺に沿って左側辺と重畠しながらのびて、斜線部と鈍角をなしている縦断縦部を含む。

切開部 7 3 ~ 7 6 b の斜線部には、三角形のノッチ (n o t c h) が形成されている。このようなノッチは、四角形、台形、または半円形からなることができ、膨らむように、またはへこむように形成することもできる。このようなノッチは、切開部 7 3 ~ 7 6 b に対応する領域の境界に位置する液晶分子 3 の配向方向を決定する。

切開部 7 3 ~ 7 6 b の数は設計要素によって変化し、遮光部材 2 2 0 が切開部 7 3 ~ 7 6 b と重畠して、切開部 7 3 ~ 7 6 b 付近の光漏れを遮断することができる。

#### 【 0 0 5 0 】

共通電極 2 7 0 及び遮蔽電極 8 8 a に同一な共通電圧が印加されるので、これらの間には電界がほとんど生成されない。したがって、共通電極 2 7 0 及び遮蔽電極 8 8 a の間に位置した液晶分子は、初期の垂直配向状態をそのまま維持するので、この部分に入射された光は透過されずに遮断される。

共通電極 2 7 0 及び蓋膜 2 5 0 上には、液晶層 3 を配向する配向膜 2 1 が塗布されている。配向膜 2 1 は水平配向膜でありうる。

#### 【 0 0 5 1 】

表示板 1 0 0 、 2 0 0 の外側面には偏光板 1 2 、 2 2 が形成されているが、二つの偏光板 1 2 、 2 2 の透過軸は直交して、これらのうちの一つの透過軸（または吸収軸）は横方向に平行である。反射型液晶表示装置である場合には、二つの偏光板 1 2 、 2 2 のうちの一つを省略することができる。

液晶層 3 は、負の誘電率異方性を有し、液晶層 3 の液晶分子は、電界が生成されない状態でその長軸が二つの表示板の表面に対して垂直に配向されている。

#### 【 0 0 5 2 】

共通電極 2 7 0 に共通電圧を印加して画素電極 1 9 0 にデータ電圧を印加すれば、表示板 1 0 0 、 2 0 0 の表面にほぼ垂直な電界が生成される。電極 1 9 0 、 2 7 0 の切開部 9 2 ~ 9 5 c 、 7 3 ~ 7 6 b は、このような電界を歪曲して、切開部 9 2 ~ 9 5 c 、 7 3 ~ 7 6 b の辺に対して垂直な水平成分を形成する。

これにより、電界は、表示板 1 0 0 、 2 0 0 の表面に垂直な方向に対して傾いた方向を指す。液晶分子は、電界に応答してその長軸が電界の方向に対して垂直をなすように方向を変化させようとするが、この時、切開部 9 2 ~ 9 5 c 、 7 3 ~ 7 6 b 及び画素電極 1 9 0 の辺付近の電界は、液晶分子の長軸方向と平行でなく一定の角度をなすので、液晶分子の長軸方向及び電界がなす平面上で移動距離が短い方向に液晶分子が回転する。したがって、一つの切開部の集合 9 2 ~ 9 5 c 、 7 3 ~ 7 6 b 及び画素電極 1 9 0 の辺は、画素電極 1 9 0 上に位置した液晶層 3 部分を液晶分子の傾斜方向が異なる複数のドメインに分割し、これにより基準視野角が拡大される。

少なくとも一つの切開部 9 2 ~ 9 5 c 、 7 3 ~ 7 6 b は、突起や陥没部に代替することができ、切開部 9 2 ~ 9 5 c 、 7 3 ~ 7 6 b の形状及び配置は変更することができる。

#### 【 0 0 5 3 】

10

20

30

40

50

次に、本実施形態による液晶表示装置の表示動作について、図1～図5を参照して詳細に説明する。

信号制御部600は、外部のグラフィック制御機(図示せず)から入力画像信号(R、G、B)及びその表示を制御する入力制御信号、例えば垂直同期信号(Vsync)及び水平同期信号(Hsync)、メインクロック信号(MCLK)、データタイネーブル信号(DE)などの提供を受ける。信号制御部600は、入力画像信号(R、G、B)及び入力制御信号に基づいて画像信号(R、G、B)を液晶表示板組立体300の動作条件に合うように適切に処理して、ゲート制御信号(CONT1)及びデータ制御信号(CONT2)などを生成した後、ゲート制御信号(CONT1)をゲート駆動部400に出力し、データ制御信号(CONT2)及び処理した画像信号データ(DAT)をデータ駆動部500に出力する。10

#### 【0054】

ゲート制御信号(CONT1)は、ゲートオン電圧(Von)の走査開始を指示する走査開始信号(STV)及びゲートオン電圧(Von)の出力を制御する少なくとも一つのクロック信号などを含む。

データ制御信号(CONT2)は、一つの画素行のデータ伝送を知らせる水平同期開始信号(STH)、データ線(D<sub>1</sub> - D<sub>m</sub>)に当該データ電圧の印加を指示するロード信号(Load)、及びデータクロック信号(HCLK)を含む。データ制御信号(CONT2)は、また、共通電圧Vcomに対するデータ電圧の極性(以下、“共通電圧に対するデータ電圧の極性”は略して“データ電圧の極性”とする)を反転させる反転信号(RVS)を含むことができる。20

#### 【0055】

信号制御部600からのデータ制御信号(CONT2)によって、データ駆動部500は、一組の副画素(PXa、PXb)に対する画像データ(DAT)を受信し、階調電圧生成部800からの二つの階調電圧の集合のうちの一つの集合を選択して、選択した階調電圧の集合の中から各画像データ(DAT)に対応する階調電圧を選択することによって画像データ(DAT)を当該データ電圧に変換した後、これを当該データ線(D<sub>1</sub> - D<sub>m</sub>)に印加する。

これとは異なって、データ駆動部500ではなく、別個に形成された外部の選択回路(図示せず)で二つの階調電圧の集合のうちのいずれか一つを選択してデータ駆動部500に伝達したり、階調電圧生成部800から値が変化する基準電圧の提供を受けて、データ駆動部500がこれを分圧して階調電圧を形成することもできる。30

#### 【0056】

ゲート駆動部400は、信号制御部600からのゲート制御信号(CONT1)によってゲートオン電圧(Von)をゲート線(G<sub>1a</sub> - G<sub>nb</sub>)に印加し、このゲート線(G<sub>1a</sub> - G<sub>nb</sub>)に連結されたスイッチング素子(Qa、Qb)をターンオンさせて、これによりデータ線(D<sub>1</sub> - D<sub>m</sub>)に印加されたデータ電圧がターンオンされたスイッチング素子(Qa、Qb)を通じて当該副画素(PXa、PXb)に印加される。

副画素(PXa、PXb)に印加されたデータ電圧と共通電圧Vcomとの差は、液晶キャパシタ(C<sub>Lc</sub>)の充電電圧、つまり画素電圧として現れる。液晶分子は、画素電圧の大きさによってその配向が異なって、これにより液晶層3を通過する光の偏光が変化する。このような偏光の変化は、表示板100、200に付着された偏光子(図示せず)によって光の透過率の変化として現れる。40

#### 【0057】

上記で説明した二つの階調電圧の集合は、互いに異なるガンマ曲線を示し、これらが一つの画素(PX)の二つの副画素(PXa、PXb)に印加されるので、一つの画素(PX)のガンマ曲線はこれらを合成した曲線になる。二つの階調電圧の集合を決定する時には、合成ガンマ曲線が正面での基準ガンマ曲線に近くなるようにするが、例えば正面での合成ガンマ曲線は、最も適切に決められた正面での基準ガンマ曲線と一致するようにし、側面での合成ガンマ曲線は、正面での基準ガンマ曲線と最も近くなるようにする。このよ50

うにすることによって、側面視認性が向上する。

【0058】

また、上記で説明したように、高い電圧の印加を受ける第2副画素電極190bの面積を第1副画素電極190aの面積より小さくすることによって、側面ガンマ曲線の歪曲を小さくすることができる。特に、第1及び第2副画素電極190a、190bの面積比が約2:1である場合に、側面でのガンマ曲線が正面でのガンマ曲線により近くなつて、側面視認性がさらに向上する。

【0059】

1/2水平周期(または1/2H)[水平同期信号H syncの半周期]を単位として、データ駆動部500及びゲート駆動部400は同一な動作を繰り返す。このような方式で、1フレーム(frame)の間に全てのゲート線( $G_{1a}$  -  $G_{n_b}$ )に対して順次にゲートオン電圧( $V_{on}$ )を印加して、全ての画素にデータ電圧を印加する。1フレームが終わると次のフレームが始まって、各画素に印加されるデータ電圧の極性が直前のフレームでの極性と反対になるように、データ駆動部500に印加される反転信号(RVS)の状態が制御される(フレーム反転)。この時、1フレーム内でも反転信号(RSV)の特性によって一つのデータ線を通じて流れるデータ電圧の極性が反転したり(例:行反転、ドット反転)、隣接するデータ線を通じて同時に流れるデータ電圧の極性が互いに反転することもある(例:列反転、ドット反転)。

【0060】

一方、図5を参照すれば、下記の式1のように定義されるキックバック電圧( $V_k$ )は、ゲートオン電圧( $V_{on}$ )からゲートオフ電圧( $V_{off}$ )に変換される時のスイッチング素子( $Q$ )の制御端子及び出力端子の間の寄生容量( $C_{gd}$ )によるカップリング現象によって生成されて、画素電極(PE)に印加された電圧を低下させる。

【数1】

$$V_k = \frac{C_{gd}}{C_{LC} + C_{ST} + C_{gd}} \Delta V_g$$

30

ここで、 $V_g$ はゲートオン電圧( $V_{on}$ )とゲートオフ電圧( $V_{off}$ )との差電圧である。

【0061】

本発明の実施形態による液晶表示装置の第1及び第2副画素(PIXa、PIXb)のキックバック電圧( $V_{ka}$ 、 $V_{kb}$ )の大きさは、実質的に同一である。第1及び第2副画素(PIXa、PIXb)の液晶キャパシタ( $C_{Lca}$ 、 $C_{Lcb}$ )の容量値は、第1及び第2副画素電極190a、190bの面積比によって決定され、寄生容量( $C_{gda}$ 、 $C_{gdb}$ )も設計要素によって決定される。したがつて、維持電極133と重畳する第1及び第2ドレイン電極175a、175bの面積を適切に設定することによって、キックバック電圧( $V_{ka}$ 、 $V_{kb}$ )の大きさを同一にすることができる第1及び第2ストレージキャパシタ( $C_{sta}$ 、 $C_{stb}$ )の容量値を形成することができる。

これに加えて、第1及び第2副画素(PIXa、PIXb)に印加されるゲート信号を異ならせることもできる。一例として、ゲートオン電圧( $V_{on}$ )の大きさを異なるようにして $V_g$ を調節することによって、キックバック電圧( $V_{ka}$ 、 $V_{kb}$ )の大きさを同一にすることもできる。このように第1及び第2副画素(PIXa、PIXb)のキックバック電圧( $V_{ka}$ 、 $V_{kb}$ )の大きさを同一にすることによって、画面がちらつくフリッカー(flicker)現象などを防止することができる。

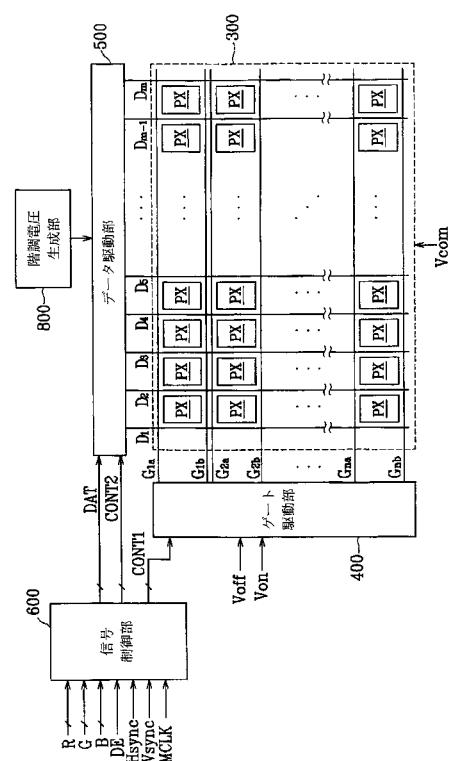

【0062】

次に、本発明の他の実施形態による液晶表示装置について、図11及び図12を参照し

40

50

て詳細に説明する。

図11は本発明の他の実施形態による液晶表示装置のプロック図であり、図12は本発明の他の実施形態による液晶表示装置の一つの画素に対する等価回路図である。

本発明の他の実施形態による液晶表示装置は、液晶表示板組立体301、これに連結されたゲート駆動部403及びデータ駆動部501、データ駆動部501に連結された階調電圧生成部801、そしてこれらを制御する信号制御部601を含む。

#### 【0063】

液晶表示板組立体301は、等価回路で見る時、複数の表示信号線( $G_1 - G_n$ 、 $D_1 - D_{2m}$ )、及びこれに連結されていて、ほぼ行列形態に配列されている複数の画素( $P_X$ )を含む。

表示信号線( $G_1 - G_n$ 、 $D_1 - D_{2m}$ )は、ゲート信号を伝達する複数のゲート線( $G_1 - G_n$ )及びデータ信号を伝達するデータ線( $D_1 - D_{2m}$ )を含む。ゲート線( $G_1 - G_n$ )は、ほぼ行方向にのびていて、互いにほぼ平行であり、データ線( $D_1 - D_{2m}$ )は、ほぼ列方向にのびていて、互いにほぼ平行である。一つの画素( $P_X$ )の両側に各々一つのデータ線( $D_1 - D_{2m}$ )が配置されている。また、表示信号線は、ゲート線( $G_1 - G_n$ )及びデータ線( $D_1 - D_{2m}$ )以外にも、ゲート線( $G_1 - G_n$ )とほぼ平行にのびた維持電極線を含むことができる。

#### 【0064】

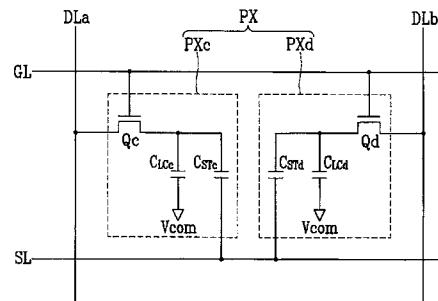

図12には、表示信号線及び一つの画素( $P_X$ )の等価回路が示されているが、図面符号 $GL$ で示したゲート線及び図面符号 $DLa$ 、 $DLb$ で示したデータ線以外にも、表示信号線は、ゲート線( $GL$ )とほぼ平行にのびた維持電極線( $SL$ )をさらに含む。

各画素( $P_X$ )は、一対の副画素( $P_Xc$ 、 $P_Xd$ )を含み、各副画素( $P_Xc$ 、 $P_Xd$ )は、各々当該ゲート線( $GL$ )及びデータ線( $DLa$ 、 $DLb$ )に連結されているスイッチング素子( $Qc$ 、 $Qd$ )、これに連結された液晶キャパシタ( $C_{Lcc}$ 、 $C_{Lcd}$ )、及びストレージキャパシタ( $C_{STc}$ 、 $C_{STD}$ )を含む。

各副画素( $P_Xc$ 、 $P_Xd$ )は、図5に示した副画素と実質的に同一なので、これに対する詳細な説明は省略する。

#### 【0065】

階調電圧生成部801は、副画素( $P_Xc$ 、 $P_Xd$ )の透過率に関する二組の複数の階調電圧を生成する。二組のうちの一組は共通電圧 $V_{com}$ に対して正の値を有し、他の一組は負の値を有する。

ゲート駆動部403は、液晶表示板組立体301のゲート線( $G_1 - G_n$ )に連結されて、外部からのゲートオン電圧( $V_{on}$ )及びゲートオフ電圧( $V_{off}$ )の組合せからなるゲート信号をゲート線( $G_1 - G_n$ )に印加する。

データ駆動部501は、液晶表示板組立体301のデータ線( $D_1 - D_{2m}$ )に連結されて、階調電圧生成部801からの階調電圧を選択して、データ信号として副画素( $P_Xc$ 、 $P_Xd$ )に印加する。

信号制御部601は、ゲート駆動部403及びデータ駆動部501などの動作を制御する。

#### 【0066】

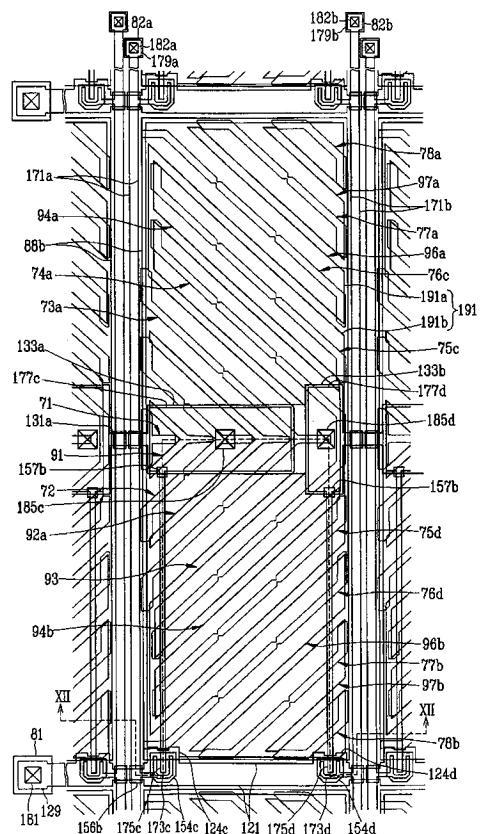

次に、このような液晶表示板組立体301の構造について、図13及び図14を参照して詳細に説明する。

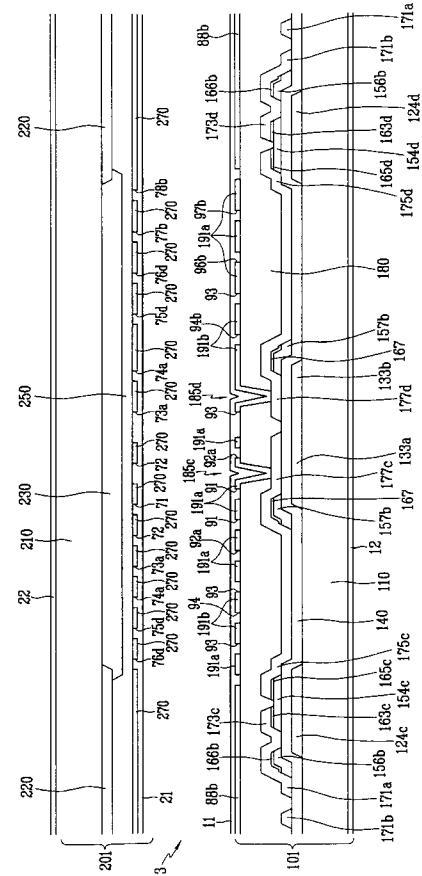

図13は本発明の他の実施形態による液晶表示板組立体の配置図であり、図14は図13の液晶表示板組立体のXII-XII線に沿った断面図である。

図13及び図14を参照すれば、本実施形態による液晶表示装置は、下部表示板101、これと対向している上部表示板201、及びこれらの間に挿入されている液晶層3を含む。

#### 【0067】

まず、下部表示板101について詳細に説明する。

透明なガラスなどからなる絶縁基板110上に、複数のゲート線121及び複数の維持

電極線 131a が形成されている。

ゲート線 121 は、主に横方向にのびていて、互いに分離されていて、ゲート信号を伝達する。各ゲート線 121 は、複数のゲート電極 124c、124d を構成する複数の突出部と他の層または外部装置との接続のために、面積が拡張されている端部 129 を含む。

維持電極線 131a は、主に横方向にのびていて、維持電極 133a、133b を構成する複数の突出部を含む。維持電極 133a、133b は、ほぼ長方形で、維持電極線 131a に対称である。維持電極 133a の面積は、維持電極 133b の面積より大きい。

#### 【0068】

ゲート線 121 及び維持電極線 131a 上には、窒化ケイ素 (SiNx) などからなるゲート絶縁膜 (gate insulating layer) 140 が形成されている。

ゲート絶縁膜 140 上には、水素化非晶質シリコンまたは多結晶シリコンなどからなる複数の島型の半導体 154c、154d、156b、157b が形成されている。半導体 154c、154d は、各々ゲート電極 124c、124d 上に位置する。

半導体 154c、154d、156b、157b 上には、シリサイド (silicid) またはリンなどのn型不純物が高濃度にドーピングされているn+水素化非晶質シリコンなどの物質からなる複数の島型の抵抗性接触部材 163c、163d、165c、165d、166b、167 が形成されている。抵抗性接触部材 163c、165c 及び抵抗性接触部材 163d、165d は、各々対をなして半導体 154c、154d 上に位置し、抵抗性接触部材 166b、167 は、各々半導体 156b、157b 上に位置する。

#### 【0069】

ゲート絶縁膜 140 及び抵抗性接触部材 163c、163d、165c、165d、166b、167 上には、複数のデータ線 171a、171b、及びこれから各々分離されている複数のドレイン電極 175c、175d が形成されている。

データ線 171a、171b は、主に縦方向にのびていて、ゲート線 121 及び維持電極線 131a と交差してデータ電圧を伝達する。データ線 171a、171b は、ゲート電極 124c、124d に向かって各々のびた複数のソース電極 173c、173d と他の層または外部装置との接続のために、幅が拡張されている端部 179a、179b を含む。

#### 【0070】

第1及び第2ドレイン電極 175c、175d は、データ線 171a、171b と分離されていて、各々ゲート電極 124c、124d を中心にソース電極 173c、173d と対向している。第1及び第2ドレイン電極 175c、175d は、各々半導体 154c、154d 上に位置した棒状の端部から始まって維持電極 133a、133b と各々重畳する面積が広い拡張部 177c、177d を有し、棒状の端部は、U字型に曲がったソース電極 173c、173d で一部が囲まれている。ここで、第2ドレイン電極 175d の拡張部 177d の面積は、第1ドレイン電極 175c の拡張部 177c の面積より小さい。

#### 【0071】

第1、第2ゲート電極 124c、124d、第1、第2ソース電極 173c、173d、及び第1、第2ドレイン電極 175c、175d は、半導体 154c、154d と共に第1、第2薄膜トランジスタ (Qc、Qd) を構成し、薄膜トランジスタ (Qc、Qd) のチャンネルは、第1、第2ソース電極 173c、173d 及び第1、第2ドレイン電極 175c、175d の間の半導体 154c、154d に形成される。

抵抗性接触部材 163c、163d、165c、165d、166b、167 は、その下部の半導体 154c、154d、156b、157b 及びその上部のデータ線 171a、171b 及びドレイン電極 175c、175d の間にだけ存在して、接触抵抗を低くする役割を果たす。島型の半導体 154c、154d は、ソース電極 173c、173d 及びドレイン電極 175c、175d で覆われずに露出された部分を有し、半導体 156b

10

20

30

40

50

、157bは、ゲート線121及び維持電極線131aの表面のプロファイルをスムーズにして、データ線171a、171b及びドレイン電極175c、175dの断線を防止する。

【0072】

データ線171a、171b及びドレイン電極175c、175d、及び露出された半導体154c、154d上には、保護膜180が形成されている。

保護膜180には、ドレイン電極175c、175dの拡張部177c、177d及びデータ線171a、171bの端部179a、179bを各々露出する複数の接触孔185c、185d、182a、182bが形成され、保護膜180及びゲート絶縁膜140には、ゲート線121の端部129を露出する複数の接触孔181が形成されている。

保護膜180上には、第1及び第2副画素電極191a、191bを含む複数の画素電極191、複数の遮蔽電極88b、及び複数の接触補助部材81、82a、82bが形成されている。

【0073】

第1、第2副画素電極191a、191bは、接触孔185c、185dを通じて第1、第2ドレイン電極175c、175dと物理的・電気的に連結されて、第1、第2ドレイン電極175c、175dからデータ電圧の印加を受ける。一対の副画素電極191a、191bには、一つの入力画像信号に対して予め設定されている互いに異なるデータ電圧が印加されるが、その大きさは副画素電極191a、191bの大きさ及び形状によって設定される。また、副画素電極191a、191bの面積は互いに異なることもある。第2副画素電極191bは、第1副画素電極191aに比べて高い電圧の印加を受けて、第1副画素電極191aより面積が小さい。

データ電圧が印加された副画素電極191a、191bは、共通電極270と共に電場を生成することによって、二つの電極191、270の間の液晶層3の液晶分子の配向を決定する。

【0074】

また、上記で説明したように、各副画素電極191a、191b及び共通電極270は、液晶キャパシタ( $C_{Lcc}$ 、 $C_{Lcd}$ )を構成して、薄膜トランジスタ( $Q_c$ 、 $Q_d$ )がターンオフされた後にも印加された電圧を維持し、電圧維持能力を強化するために、液晶キャパシタ( $C_{Lcc}$ 、 $C_{Lcd}$ )と並列に連結されたストレージキャパシタ( $C_{sTc}$ 、 $C_{sTd}$ )は、各々第1及び第2副画素電極191a、191b及びこれに連結されているドレイン電極175c、175dの拡張部177c、177dと維持電極133a、133bとの重畠などによって形成される。

【0075】

第1副画素電極191aの面積が第2副画素電極191bの面積より大きいので、第1液晶キャパシタ( $C_{Lcc}$ )の容量値が第2液晶キャパシタ( $C_{Lcd}$ )の容量値より大きく、維持電極133a及びこれと重畠する第1ドレイン電極175cの拡張部177cの面積が維持電極133b及びこれと重畠する第2ドレイン電極175dの拡張部177dの面積より大きいので、第1ストレージキャパシタ( $C_{sTc}$ )の容量値が第2ストレージキャパシタ( $C_{sTd}$ )の容量値より大きい。したがって、第1薄膜トランジスタ( $Q_c$ )が第2薄膜トランジスタ( $Q_d$ )より電流駆動能力が大きくななければならないので、第1薄膜トランジスタ( $Q_c$ )のW:Lの比の大きさが第2薄膜トランジスタ( $Q_d$ )のW:Lの比の大きさより大きい。ここで、Wはチャンネルの幅であり、Lはチャンネルの長さである。

【0076】

一つの画素電極191を構成する一対の第1及び第2副画素電極191a、191bは、間隙93を間に置いて互いに噛み合っていて、画素電極191の外側境界はほぼ四角形である。第2副画素電極191bは、ほぼ回転した等辺台形であって、下辺が台形にへこんでいて、大部分が第1副画素電極191aで囲まれている。第1副画素電極191aは、左側辺で互いに連結されている上部、下部、及び中央台形部からなる。第1副画素電極

10

20

30

40

50

191aの中央台形部は、第2副画素電極191bのへこんでいる下辺に嵌合している。第1副画素電極191a及び第2副画素電極191bの間の間隙93は、ほぼ均一な幅を有してゲート線121と約45°の角度をなす二対の上部及び下部斜線部、及び実質的に均一な幅を有する三つの縦部を含む。以下では、説明の便宜のために、間隙93も切開部と表現する。

#### 【0077】

第1副画素電極191aは、上部台形部の上辺及び下部台形部の下辺から右側辺に向かってのびた切開部96a、96b、97a、97bを有している。第1副画素電極191aは、維持電極線131aに沿ってのびた切開部91、92aを有し、切開部91、92aは、中央から横方向にのびた横部、及び維持電極線131aに対して約45°の角度をなす一対の斜辺を有している。第2副画素電極192bは、左側辺から右側辺に向かってのびた切開部94a、94bを有している。切開部91、92a、94a、94b、96a、96b、97a、97bは、維持電極線131aに対してほぼ反転対称をなしていて、これらはゲート線121に対して約45°の角度をなして互いに垂直にのびている。画素電極191の上半部及び下半部は、切開部91～97bによって各々8つの領域に分割される。

#### 【0078】

遮蔽電極88bは、データ線171a、171bに沿ってのびた縦部、及びゲート線121に沿ってのびた横部を含むが、縦部はデータ線171a、171bを完全に覆っており、横部もゲート線121を完全に覆っている。

遮蔽電極88bは、データ線171a、171b及び画素電極191の間、そしてデータ線171a、171b及び共通電極270の間で形成される電界を遮断して、画素電極191の電圧歪曲及びデータ線171a、171bが伝達するデータ電圧の信号遅延を減少させる。

また、画素電極191及び遮蔽電極88bの短絡を防止するために、これらの間に距離をおかなければならぬので、画素電極191がデータ線171a、171b及びゲート線121からさらに遠くなつて、これらの間の寄生容量が減少する。

#### 【0079】

接触補助部材81、82a、82bは、接触孔181、182a、182bを通じてゲート線121の端部129及びデータ線171a、171bの端部179a、179bと各々連結される。

画素電極191、接触補助部材81、82a、82b、及び保護膜180上には、液晶層3を配向する配向膜11が塗布されている。

#### 【0080】

次に、図14を参照して上部表示板201について詳細に説明する。

透明なガラスなどからなる絶縁基板210上に、遮光部材220、複数の色フィルタ230、蓋膜250、及び共通電極270が順次に形成されている。

#### 【0081】

共通電極270は、複数組の切開部71、72、73a、74a、75c、75d、76c、76d、77a、77b、78a、78bの集合を有する。

一組の切開部71～78bは、一つの画素電極191と対向していて、中央切開部71、72、73a、74a、上部切開部75c、76c、77a、78a、及び下部切開部75d、76d、77b、78bを含む。切開部71～78bは、画素電極191の左側辺中央、隣接した画素電極191の切開部91～97bの間、及び周縁切開部97a、97b及び画素電極191の角の間に配置されている。また、切開部72～78bは、画素電極191の切開部91～97bと平行にのびた少なくとも一つの斜線部を含む。

#### 【0082】

下部及び上部切開部75c～78bは、画素電極191のほぼ右側辺から下側または上側辺に向かってのびた斜線部、そして斜線部の各端部から画素電極191の辺に沿って辺と重畳しながらのびて、斜線部と鈍角をなしている横部及び縦部を含む。

10

20

20

30

40

50

中央切開部 7 1 は、画素電極 1 9 1 の左側辺に沿って左側辺と重畠しながらのびた縦部、及び縦部の中央から維持電極線 1 3 1 a に沿ってのびた横部を含む。中央切開部 7 2、7 3 a は、維持電極線 1 3 1 a にほぼ沿ってのびた横部、これから維持電極線 1 3 1 a と斜角をなして画素電極 1 9 1 の左側辺に向かってのびた一対の斜線部、及び斜線部の各端部から画素電極 1 9 1 の左側辺に沿って左側辺と重畠しながらのびて、斜線部と鈍角をなしている縦断縦部を含む。中央切開部 7 4 a は、画素電極 1 9 1 の右側辺に沿って右側辺と重畠しながらのびた縦部、縦部の各端部から画素電極 1 9 1 の左側辺に向かってのびた一対の斜線部、そして斜線部の各端部から第 2 副画素電極 1 9 1 b の左側辺に沿って左側辺と重畠しながらのびて、斜線部と鈍角をなしている縦断縦部を含む。

## 【 0 0 8 3 】

10

切開部 7 2 ~ 7 7 b の斜線部には、三角形のノッチが形成されている。このようなノッチは、四角形、台形、または半円形からなることができ、膨らむように、またはへこむように形成することもできる。

共通電極 2 7 0 及び蓋膜 2 5 0 上には、液晶層 3 を配向する配向膜 2 1 が塗布されている。

表示板 1 0 1、2 0 1 の外側面には偏光板 1 2、2 2 が形成されている。

## 【 0 0 8 4 】

本実施形態による液晶表示装置の表示動作は、前記実施形態と実質的に同一なので、これに対する説明は省略する。

本実施形態の液晶表示装置でも、第 1 及び第 2 副画素 (P X c、P X d) のキックバック電圧 (V k c、V k d) の大きさは実質的に同一である。第 1 及び第 2 副画素 (P X c、P X d) の液晶キャパシタ (C L c c、C L c d) の容量値は第 1 及び第 2 副画素電極 1 9 1 a、1 9 1 b の面積比によって決定され、寄生容量 (C g d c、C g d d) も設計要素によって決定される。したがって、維持電極 1 3 3 a、1 3 3 b と各々重畠する第 1 及び第 2 ドレイン電極 1 7 5 a、1 7 5 b の面積を適切に設定することによって、キックバック電圧 (V k c、V k d) の大きさを同一にすることができる第 1 及び第 2 ストライジキャパシタ (C s t c、C s t d) の容量値を形成することができる。このように、第 1 及び第 2 副画素 (P X c、P X d) のキックバック電圧 (V k c、V k d) の大きさを同一にすることによって、画面がちらつくフリッカー (f l i c k e r) 現象などを防止することができる。

20

## 【 0 0 8 5 】

30

また、高い電圧の印加を受ける第 2 副画素電極 1 9 1 b の面積を第 1 副画素電極 1 9 1 a の面積より小さくすることによって、側面ガンマ曲線の歪曲を小さくすることができ、特に、第 1 及び第 2 副画素電極 1 9 1 a、1 9 1 b の面積比が約 2 : 1 である場合に、側面視認性が向上する。

上記で説明した図 1 乃至図 1 0 の液晶表示装置に対する多くの特徴が、図 1 1 乃至図 1 4 の液晶表示装置にも適用される。

## 【 0 0 8 6 】

40

次に、本発明のさらに他の実施形態による液晶表示装置について、図 1 5 を参照して詳細に説明する。

図 1 5 は本発明のさらに他の実施形態による液晶表示装置の一つの画素に対する等価回路図である。

図 1 5 には、表示信号線及び一つの画素 (P X) の等価回路が示されているが、表示信号線は、図面符号 G L で示したゲート線及び図面符号 D L で示したデータ線、そしてゲート線 (G L) とほぼ平行にのびた一対の第 1 及び第 2 維持電極線 (S L a、S L b) を含む。

## 【 0 0 8 7 】

50

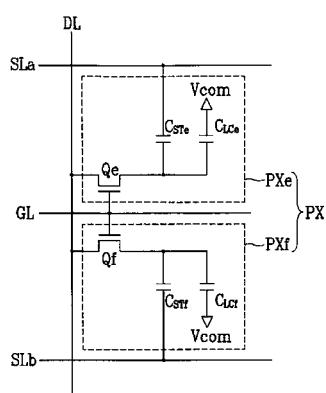

各画素 (P X) は、一対の副画素 (P X e、P X f) を含み、各副画素 (P X e、P X f) は、ゲート線 (G L) 及びデータ線 (D L) に連結されているスイッチング素子 (Q e、Q f)、これに連結されている液晶キャパシタ (C L c e、C L c f)、そしてスイ

ツチング素子 (Q<sub>e</sub>、Q<sub>f</sub>) 及び維持電極線 (S<sub>L</sub><sub>a</sub>、S<sub>L</sub><sub>b</sub>) に連結されているストレージキャパシタ (C<sub>S</sub><sub>T</sub><sub>e</sub>、C<sub>S</sub><sub>T</sub><sub>f</sub>) を含む。

第1及び第2維持電極線 (S<sub>L</sub><sub>a</sub>、S<sub>L</sub><sub>b</sub>) は、第1及び第2共通電圧 (V<sub>c</sub><sub>o</sub><sub>m</sub>1、V<sub>c</sub><sub>o</sub><sub>m</sub>2) の印加を受ける。第1及び第2共通電圧 (V<sub>c</sub><sub>o</sub><sub>m</sub>1、V<sub>c</sub><sub>o</sub><sub>m</sub>2) は、高電圧及び低電圧の間をスイングして互いに180度の位相差を有する。ゲート信号によって一つのデータ電圧が各副画素 (P<sub>X</sub><sub>e</sub>、P<sub>X</sub><sub>f</sub>) に印加されて充電される。副画素 (P<sub>X</sub><sub>e</sub>、P<sub>X</sub><sub>f</sub>) に充電された画素電圧は、各々維持電極線 (S<sub>L</sub><sub>a</sub>、S<sub>L</sub><sub>b</sub>) に印加された第1及び第2共通電圧 (V<sub>c</sub><sub>o</sub><sub>m</sub>1、V<sub>c</sub><sub>o</sub><sub>m</sub>2) によって高電圧及び低電圧 (または低電圧及び高電圧) に変換されて、互いに異なる電圧になる。このように副画素 (P<sub>X</sub><sub>e</sub>、P<sub>X</sub><sub>f</sub>) に互いに異なる画素電圧を印加することによって、側面視認性を向上させることができる。10

#### 【0088】

本実施形態でも、第1及び第2副画素 (P<sub>X</sub><sub>e</sub>、P<sub>X</sub><sub>f</sub>) のキックバック電圧 (V<sub>k</sub><sub>e</sub>、V<sub>k</sub><sub>f</sub>) の大きさは実質的に同一である。第1及び第2副画素 (P<sub>X</sub><sub>e</sub>、P<sub>X</sub><sub>f</sub>) の液晶キャパシタ (C<sub>L</sub><sub>c</sub><sub>e</sub>、C<sub>L</sub><sub>c</sub><sub>f</sub>) の容量値は互いに異なり、寄生容量 (C<sub>g</sub><sub>d</sub><sub>e</sub>、C<sub>g</sub><sub>d</sub><sub>f</sub>) も設計要素によって互いに異なる。したがって、第1及び第2ストレージキャパシタ (C<sub>S</sub><sub>T</sub><sub>e</sub>、C<sub>S</sub><sub>T</sub><sub>f</sub>) の容量値を適切に設定することによって、キックバック電圧 (V<sub>k</sub><sub>e</sub>、V<sub>k</sub><sub>f</sub>) の大きさを同一にすることができる。このように、第1及び第2副画素 (P<sub>X</sub><sub>e</sub>、P<sub>X</sub><sub>f</sub>) のキックバック電圧 (V<sub>k</sub><sub>e</sub>、V<sub>k</sub><sub>f</sub>) の大きさを同一にすることによって、画面がちらつくフリッカー (flicker) 現象などを防止することができる。20

#### 【0089】

尚、本発明は、上述の実施形態に限られるものではない。本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

#### 【図面の簡単な説明】

#### 【0090】

【図1】本発明の一実施形態による液晶表示装置のブロック図である。

【図2】本発明の一実施形態による液晶表示装置のブロック図である。

【図3】本発明の一実施形態による液晶表示装置のブロック図である。

【図4】本発明の一実施形態による液晶表示装置の一つの画素に対する等価回路図である。30

【図5】本発明の一実施形態による液晶表示装置の一つの副画素に対する等価回路図である。

【図6】本発明の一実施形態による液晶表示装置の下部表示板の配置図である。

【図7】本発明の一実施形態による液晶表示装置の上部表示板の配置図である。

【図8】図6の下部表示板及び図7の上部表示板を含む液晶表示板組立体の配置図である。

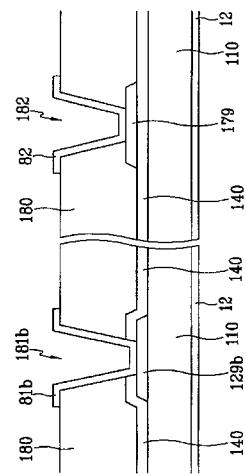

【図9】図8の液晶表示板組立体のV<sub>I</sub><sub>I</sub> - V<sub>I</sub><sub>I</sub>線に沿った断面図である。

【図10】図8の液晶表示板組立体の及びV<sub>I</sub><sub>I</sub><sub>I</sub> - V<sub>I</sub><sub>I</sub><sub>I</sub>線、V<sub>I</sub><sub>I</sub><sub>I</sub>' - V<sub>I</sub><sub>I</sub><sub>I</sub>'線に沿った断面図である。40

【図11】本発明の他の実施形態による液晶表示装置のブロック図である。

【図12】本発明の他の実施形態による液晶表示装置の一つの画素に対する等価回路図である。

【図13】本発明の他の実施形態による液晶表示板組立体の配置図である。

【図14】図13の液晶表示板組立体のX<sub>I</sub><sub>I</sub> - X<sub>I</sub><sub>I</sub>線に沿った断面図である。

【図15】本発明のさらに他の実施形態による液晶表示装置の一つの画素に対する等価回路図である。

#### 【符号の説明】

#### 【0091】

|                                   |             |    |

|-----------------------------------|-------------|----|

| 1 1 、 2 1                         | 配向膜         |    |

| 1 2 、 2 2                         | 偏光版         |    |

| 1 0 0 、 1 0 1                     | 下部表示板       |    |

| 1 1 0 、 2 1 0                     | 絶縁基板        |    |

| 1 2 1 a 、 b                       | ゲート線        |    |

| 1 2 4 a 、 b                       | ゲート電極       |    |

| 1 2 9 a 、 b                       | ゲート線端部      |    |

| 1 3 1                             | 維持電極線       |    |

| 1 3 3                             | 維持電極        |    |

| 1 4 0                             | ゲート絶縁膜      | 10 |

| 1 5 4 、 1 5 6 、 1 5 7             | 半導体         |    |

| 1 6 3 、 1 6 5 、 1 6 6 、 1 6 7     | 抵抗性接触部材     |    |

| 1 7 1 a 、 b                       | データ線        |    |

| 1 7 3 c 、 d                       | ソース電極       |    |

| 1 7 5 c 、 d                       | ドレイン電極      |    |

| 1 7 7 c 、 d                       | ドレイン電極拡張部   |    |

| 1 7 9 a 、 b                       | データ線端部      |    |

| 1 8 0                             | 保護膜         |    |

| 1 8 1 a 、 b 、 1 8 2 、 1 8 5 a 、 b | 接触孔         |    |

| 1 9 0 、 1 9 1                     | 画素電極        | 20 |

| 1 9 0 a 、 b                       | 第1及び第2副画素電極 |    |

| 2 0 0 、 2 0 1                     | 上部表示板       |    |

| 2 2 0                             | 遮光部材        |    |

| 2 2 5                             | 開口部         |    |

| 2 3 0                             | 色フィルタ       |    |

| 2 5 0                             | 蓋膜          |    |

| 2 7 0                             | 共通電極        |    |

| 3 0 0 、 3 0 1                     | 液晶表示板組立体    |    |

| 4 0 0 、 4 0 3                     | ゲート駆動部      |    |

| 5 0 0 、 5 0 1                     | データ駆動部      | 30 |

| 6 0 0 、 6 0 1                     | 信号制御部       |    |

| 8 0 0 、 8 0 1                     | 階調電圧生成部     |    |

| 8 1 、 8 2                         | 接触補助部材      |    |

| 8 8 a 、 8 8 b                     | 遮蔽電極        |    |

| 9 3 、 9 4 、 9 5                   | 切開部(間隙)     |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 6 】

【図7】

【 四 8 】

【 四 9 】

【 図 1 1 】

【 図 1 0 】

【 図 1 2 】

【 図 1 3 】

【 図 1 4 】

【 図 1 5 】

|                |                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2006293373A</a>                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2006-10-26 |

| 申请号            | JP2006110134                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2006-04-12 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 金東奎                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | 金 東 奎                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号         | G02F1/1343                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| CPC分类号         | G02F1/136277 G02F1/136213 G02F1/13624 H01L27/124 H01L27/13                                                                                                                                                                                                                                                                                                                                         |         |            |

| FI分类号          | G02F1/1343 G02F1/133.550 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 2H092/GA12 2H092/GA14 2H092/HA03 2H092/JA24 2H092/NA01 2H192/AA24 2H192/BA22 2H192 /BA25 2H192/BC24 2H192/BC31 2H192/CB05 2H192/CB42 2H192/CB61 2H192/CB71 2H192/CC12 2H192/CC26 2H192/CC32 2H192/CC42 2H192/CC52 2H192/CC72 2H192/DA12 2H192/DA72 2H192 /EA22 2H192/EA43 2H192/FA35 2H192/FA44 2H192/FA65 2H192/GA02 2H192/GD61 2H192/JA13 2H193/ZA04 2H193/ZA07 2H193/ZA08 2H193/ZA19 2H193/ZF24 |         |            |

| 优先权            | 1020050030678 2005-04-13 KR                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 其他公开文献         | <a href="#">JP5027437B2</a>                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                          |         |            |

## 摘要(译)

解决的问题：提供一种液晶显示装置，该液晶显示装置能够通过将一个像素划分为两个子像素并对两个子像素施加单独的不同数据电压来改善侧面可视性。在具有以矩阵布置的并且包括第一和第二子像素的多个像素的液晶显示装置中，每个子像素包括第一和第二子像素电极以及第一和第二子像素电极。维持电极以及第一和第二开关，其中，第一和第二开关是第一和第二栅电极，各个开关的第一和第二源电极以及第一开关。并且每个开关的第一漏极和第二漏极连接到第二子像素电极，第一预定电压被施加到第一子像素电极，第二预定电压被施加到第二子像素电极。电压被施加到第二子像素电极。[选择图]图6