(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-276582

(P2006-276582A)

(43) 公開日 平成18年10月12日(2006.10.12)

(51) Int.Cl.

**G02F 1/1368 (2006.01)**

**H01L 29/786 (2006.01)**

**H01L 21/336 (2006.01)**

F 1

G02F 1/1368

H01L 29/78 612Z

テーマコード(参考)

2H092

5F11O

審査請求 未請求 請求項の数 5 O L (全 13 頁)

(21) 出願番号

(22) 出願日

特願2005-97193 (P2005-97193)

平成17年3月30日 (2005.3.30)

(71) 出願人 304053854

三洋エプソンイメージングデバイス株式会社

東京都港区浜松町二丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107076

弁理士 藤岡 英吉

(74) 代理人 100107261

弁理士 須澤 修

(72) 発明者 佐藤 尚

東京都港区浜松町二丁目4番地1号 三洋

エプソンイメージングデバイス株式会社内

Fターム(参考) 2H092 GA11 JA24 JA34 JA37 JA41

JB13 NA01 NA07 PA01 PA06

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】 画素分割によって視角特性を改善した場合でも、画素開口率の低下を抑えることのできる液晶表示装置を提供すること。

【解決手段】 液晶表示装置の複数の画素 Pにおいて、補助容量 C は、直列に接続された 2 つの副補助容量 C<sub>1</sub>、C<sub>2</sub>に分割され、液晶容量 L は、2 つの副補助容量 C<sub>1</sub>、C<sub>2</sub>によって容量分割された電圧が印加される 2 つの副液晶容量 L<sub>1</sub>、L<sub>2</sub>に分割されている。従って、画素 P は、2 つの副液晶容量 L<sub>1</sub>、L<sub>2</sub>の各々対応する 2 つの副画素 P<sub>1</sub>、P<sub>2</sub>に分割されている。

【選択図】 図 2

**【特許請求の範囲】****【請求項 1】**

複数の走査線と複数のデータ線との交差に対応して設けられた複数の画素を備え、当該画素は、画素スイッチング用の薄膜トランジスタを介して前記データ線に電気的に接続する液晶容量と、該液晶容量に並列に電気的に接続された補助容量とを備えた液晶表示装置において、

前記補助容量は、直列に接続された複数の副補助容量に分割され、

前記液晶容量は、前記複数の副補助容量によって容量分割された電圧が印加される複数の副液晶容量に分割され、

前記画素は、前記複数の副補助容量の各々に対応する複数の副画素に分割されていることを特徴とする液晶表示装置。 10

**【請求項 2】**

液晶層を挟んで対向配置された素子基板および対向基板を有し、

前記素子基板には、前記走査線、前記データ線、前記薄膜トランジスタ、前記複数の副補助容量、および前記複数の副画素に対応する複数の副画素電極が形成され、

前記対向基板には、前記複数の副画素電極の各々との間に前記複数の副液晶容量を構成する対向電極が形成されていることを特徴とする請求項 1 に記載の液晶表示装置。

**【請求項 3】**

液晶層を挟んで対向配置された素子基板および対向基板を有し、

前記素子基板には、前記走査線、前記データ線、前記薄膜トランジスタ、前記複数の副補助容量、前記複数の副画素に対応する複数の副画素電極、および当該複数の副画素電極の各々との間に前記複数の副液晶容量を構成する共通電極が形成されていることを特徴とする請求項 1 に記載の液晶表示装置。 20

**【請求項 4】**

前記素子基板上には複数の絶縁層が積層されているとともに、当該複数の絶縁層の下層、層間および上層の各々に導電層が形成され、

前記複数の副補助容量はいずれも、前記複数の導電層のうち、絶縁層を挟んで対向する 2 つの導電層を下電極および上電極として構成され、

前記複数の副補助容量のうち、下層側に形成された下層側副補助容量の上電極と、当該下層側副補助容量の上層に形成された上層側副補助容量の下電極とは、共通の導電層からなることを特徴とする請求項 2 または 3 に記載の液晶表示装置。 30

**【請求項 5】**

前記複数の副補助容量を構成する複数の導電層には、前記薄膜トランジスタのゲート電極と同層位置に形成された導電層、前記薄膜トランジスタのソース電極と同層位置に形成された導電層、および前記複数の副画素電極の全てが含まれていることを特徴とする請求項 4 に記載の液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、画素スイッチング用の薄膜トランジスタ（以下、TFT（Thin Film Transistor）という）および画素電極を備えた画素が複数の副画素に分割された液晶表示装置に関するものである。 40

**【背景技術】****【0002】**

液晶表示装置において、1つの画素を複数の副画素に分割し、各副画素の液晶層に印加する電圧を変化させることによって、広い視野角で良好な多階調表示をさせて視角特性を改善する技術は、画素分割法と称せられる従来技術として周知である。このような画素分割法は、例えば、画素スイッチング素子として TFT を用いた液晶表示装置において、各画素に補助容量とは別に制御容量を形成することにより実現されている（例えば、特許文献 1 参照）。 50

【特許文献1】特開平7-325322号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、上記特許文献に記載の技術のように、各画素に補助容量とは別に制御容量を形成した場合には、画素内に制御容量を追加した分、画素内において表示光が出射される領域の比率（画素開口率）が低下し、明るい表示を行えなくなるという問題点がある。

【0004】

以上の問題点に鑑みて、本発明の課題は、画素分割によって視角特性を改善した場合でも、画素開口率の低下を抑えることのできる液晶表示装置を提供することにある。 10

【課題を解決するための手段】

【0005】

上記課題を解決するために、本発明では、複数の走査線と複数のデータ線との交差に対応して設けられた複数の画素を備え、当該画素は、画素スイッチング用の薄膜トランジスタを介して前記データ線に電気的に接続する液晶容量と、該液晶容量に並列に電気的に接続された補助容量とを備えた液晶表示装置において、前記補助容量は、直列に接続された複数の副補助容量に分割され、前記液晶容量は、前記複数の副補助容量によって容量分割された電圧が印加される複数の副液晶容量に分割され、前記画素は、前記複数の副補助容量の各々に対応する複数の副画素に分割されていることを特徴とする。 20

【0006】

本発明では、画素を複数の副画素に分割することによって視角特性を改善するにあたり、液晶容量に並列に電気的に接続される補助容量を複数の副補助容量に分割し、複数の補助容量によって容量分割された電圧が複数の副液晶容量に印加されるように構成してある。このため、補助容量の他に制御容量を追加する必要がない。従って、画素分割によって視角特性を改善した場合でも、画素開口率の低下を抑えることができる。 30

【0007】

本発明において、液晶層を挟んで対向配置された素子基板および対向基板を有し、前記素子基板には、前記走査線、前記データ線、前記TFT、前記複数の副補助容量、および前記複数の副画素に対応する複数の副画素電極が形成され、前記対向基板には、前記複数の副画素電極の各々との間に前記複数の副液晶容量を構成する対向電極が形成されている。すなわち、本発明は、IPSモード( In - Plane Switching )以外の各種液晶を用いた液晶表示装置に適用することができる。 30

【0008】

また、IPSモードなどの横電界を利用する場合には、液晶層を挟んで対向配置された素子基板および対向基板のうち、前記素子基板の方に、前記走査線、前記データ線、前記TFT、前記複数の副補助容量、前記複数の副液晶容量に対応する複数の副画素電極、および当該複数の副画素電極の各々との間に前記複数の副液晶容量を構成する共通電極を形成すればよい。

【0009】

本発明において、前記素子基板上には複数の絶縁層が積層されているとともに、当該複数の絶縁層の下層、層間および上層の各々に導電層が形成され、前記複数の副補助容量はいずれも、前記複数の導電層のうち、絶縁層を挟んで対向する2つの導電層を下電極および上電極として構成され、前記複数の副補助容量のうち、下層側に形成された下層側副補助容量の上電極と、当該下層側副補助容量の上層に形成された上層側副補助容量の下電極とは、共通の導電層からなることが好ましい。このように構成すると、複数の副補助容量を構成するための導電層が少なくて済むため、TFTなどを構成する複数の導電層と同時に形成された導電層のみで2つの副補助容量を構成でき、さらに多数の副補助容量を構成する場合でも、追加すべき導電層の数が少なくて済む。また、下層側副補助容量と上層側副補助容量とを平面的に重なる領域に形成できるので、画素分割によって視角特性を改善し 40

50

た場合でも、画素開口率の低下を抑えることができる。

#### 【0010】

本発明において、前記複数の副補助容量を構成する複数の導電層には、前記TFTのゲート電極と同層位置に形成された導電層、前記TFTのソース電極と同層位置に形成された導電層、および前記複数の副画素電極の全てが含まれていることが好ましい。このように構成すると、これらの導電層で2つの副補助容量を構成することができるので、画素を2分割した場合には、新たな導電層が一切、不要である。

#### 【発明を実施するための最良の形態】

#### 【0011】

以下、本発明の実施形態を図面に基づいて説明する。なお、参照する各図において、図面上で認識可能な大きさとするために縮尺が各層や各部材ごとに異なる場合がある。10

#### 【0012】

##### [実施の形態1]

##### (液晶表示装置の基本構成)

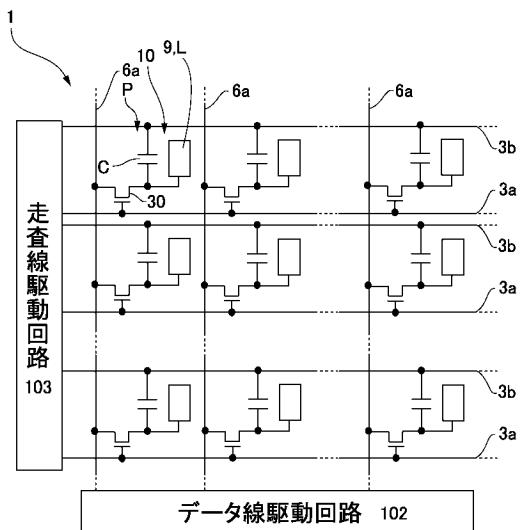

図1は、画素スイッチング素子としてTFTを用いた液晶表示装置の基本的な電気的構成を示すブロック図である。

#### 【0013】

図1に示す液晶表示装置1は、画素スイッチング素子としてTFTを用いたアクティブマトリクス型液晶表示装置であり、データ線6aと走査線3aとの交差に対応する各々の位置に画素Pを備えている。これらの画素Pの各々には、画素電極9を制御するための画素スイッチング用のTFT30が形成されており、画像信号を供給するデータ線6aが当該TFT30のソースに電気的に接続されている。データ線6aに書き込む画像信号は、データ線駆動回路102から供給される。また、TFT30のゲートには走査線3aが電気的に接続されており、所定のタイミングで、走査線3aにパルス的に走査信号が走査線駆動回路103から供給される。画素電極9は、TFT30のドレインに電気的に接続されており、スイッチング素子であるTFT30を一定期間だけそのオン状態とすることにより、データ線6aから供給される画像信号を各画素に所定のタイミングで書き込む。ここで、画素電極9は、後述する対向電極との間に液晶容量Lを構成しており、画素電極9を介して液晶容量Lに書き込まれた所定レベルの画像信号は、一定期間保持される。また、保持された画像信号がリークするのを防ぐことを目的に、液晶容量Lと並列に補助容量Cを付加することがある。この補助容量Cによって、画素電極9の電圧は、例えば、ソース電圧が印加された時間よりも3桁も長い時間だけ保持される。これにより、液晶容量Lにおける電荷の保持特性が改善され、コントラスト比の高い表示を行うことのできる電気光学装置が実現できる。なお、補助容量Cを形成する方法としては、容量線3bを利用する他、前段の走査線3aからの延設部分を利用することができるが、以下の説明では、容量線3bを利用した構成を説明する。2030

#### 【0014】

##### (画素構成)

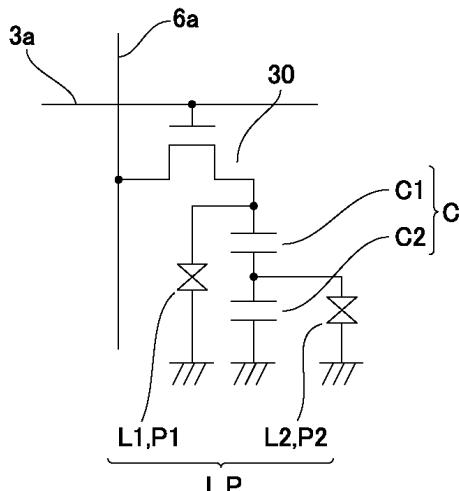

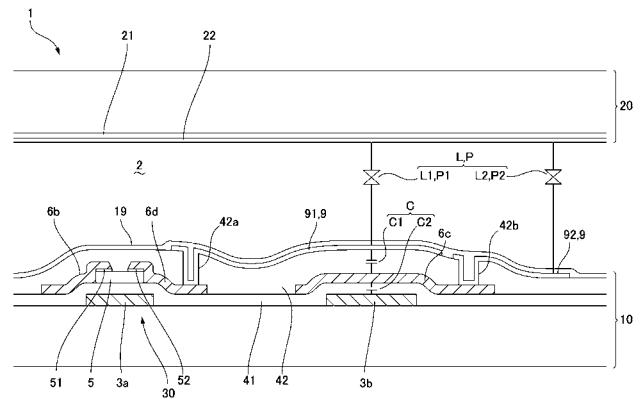

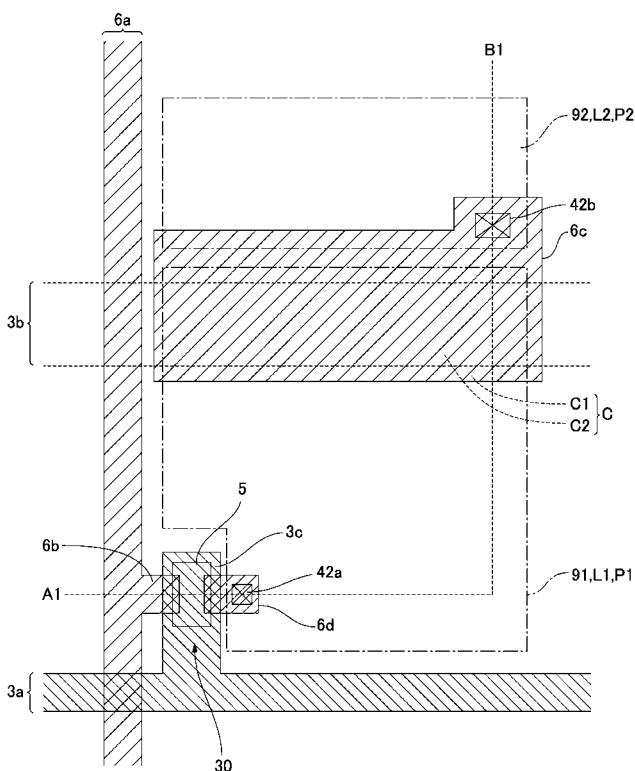

図2、図3および図4は、本発明の実施の形態1に係る液晶表示装置の画素1つ分の等価回路図、この液晶表示装置の画素1つ分の断面図、および素子基板の画素1つ分の平面図である。なお、図3は、図4のA1-B1線での断面図に相当する。また、図4には、データ線と同時形成された導電膜に対しては右上がりの斜線を付し、走査線と同時形成された導電膜に対しては、右下がりの斜線を付し、画素電極については一点鎖線で示してある。40

#### 【0015】

図2に示すように、本形態では、補助容量Cは、直列に接続された2つの副補助容量C1、C2に分割され、液晶容量Lは、2つの副補助容量C1、C2によって容量分割された電圧が印加される2つの副液晶容量L1、L2に分割されている。従って、画素Pは、2つの副液晶容量L1、L2の各々対応する2つの副画素P1、P2に分割されている。2つの副液晶容量L1、L2のうち、第1の副液晶容量L1は、2つの副補助容量C1、50

C<sub>2</sub>からなる補助容量Cに並列に電気的に接続し、第2の副液晶容量L<sub>2</sub>は、2つの副補助容量C<sub>1</sub>、C<sub>2</sub>のうち、第2の副補助容量C<sub>2</sub>に並列に電気的に接続している状態にある。

#### 【0016】

このように構成した液晶表示装置1では、TFT30がオンした際、データ線6aの電位が第1の副補助容量C<sub>1</sub>と第2の副補助容量C<sub>2</sub>とによって分割され、第2の副補助容量C<sub>2</sub>および第2の副液晶容量L<sub>2</sub>には、同一の画素P内に形成された第1の副補助容量C<sub>1</sub>および第1の副液晶容量L<sub>1</sub>と比較して低い電位が印加される。それ故、第1の副液晶容量L<sub>1</sub>に対応する第1の副画素P<sub>1</sub>の視角特性と、第2の副液晶容量L<sub>2</sub>に対応する第2の副画素P<sub>2</sub>の視角特性が補完し合う結果、視角特性の向上が図られる。

10

#### 【0017】

本形態の液晶表示装置1を構成するにあたっては、図3に示すように、素子基板10と対向基板20とが対向配置され、かつ、これらの基板間に液晶層2が保持されている。本形態では、液晶層2には、後述するIPSモード以外の全ての液晶、例えば、TN液晶、ECBモードの液晶、ゲストホストタイプの液晶、垂直配向の液晶が用いられるので、対向基板20には、ITO層からなる対向電極21、および配向膜22がこの順に形成されている。

#### 【0018】

このような液晶表示装置1における素子基板10の平面構成は、図4に示すように表され、データ線6aと交差する方向に走査線3aが形成されるとともに、走査線3aと並列して容量線3bが形成されている。データ線6aは、TFT30のソース電極6bと一緒に形成され、走査線3aは、TFT30のゲート電極3cと一緒に構成されている。

20

#### 【0019】

容量線3bと平面的に重なる領域には、制御電極6cが形成され、制御電極6と容量線3bとの間に第2の副補助容量C<sub>2</sub>が形成されている。

#### 【0020】

TFT30のドレイン領域には、ドレイン電極6dを介して第1の副画素P<sub>1</sub>(第1の副液晶容量L<sub>1</sub>)を形成するための第1の副画素電極91が電気的に接続され、この第1の副画素電極91の一部は制御電極6cと平面的に重なって第1の副補助容量C<sub>1</sub>を形成している。また、画素Pには、第2の副画素P<sub>2</sub>(第2の副液晶容量L<sub>2</sub>)を形成するための第2の副画素電極92が形成され、第2の副画素電極92は、制御電極6cにコンタクトホール42bを介して接続している。

30

#### 【0021】

このように構成した素子基板20の断面構成は、図3に示すように、素子基板10の下層側から上層側に向かって、TFT30のゲート電極3c、厚さが約300nmのシリコン窒化膜などからなるゲート絶縁膜41、厚さが約150nmのシリコン膜などからなる半導体膜5、ソース電極6b、厚さが約180nmのシリコン窒化膜などからなる層間絶縁膜42、画素電極9、配向膜19が積層された構造になっている。ゲート電極3cと同層位置(ゲート絶縁膜41の下層)には、容量線3bが形成され、これらの導電層はいずれも、例えば、厚さが約250nmのアルミニウム層と、厚さが約250nmのモリブデン層との積層体として構成されている。また、ソース電極6bと同層位置(ゲート絶縁膜41と層間絶縁膜42の層間)には、ドレイン電極6dおよび制御電極6cが形成され、これらの導電層はいずれも、例えば、厚さが約250nmのアルミニウム層と、厚さが約250nmのモリブデン層との積層体として構成されている。さらに、層間絶縁膜42の上層側には、画素電極9として、第1の副画素電極91および第2の副画素電極92が形成され、これらの導電層はいずれも、例えば、厚さが約50nmのITOによって構成されている。

40

#### 【0022】

第1の副画素電極91は、層間絶縁膜42のコンタクトホール42aを介してドレイン電極6dに電気的に接続し、第2の副画素電極92は、層間絶縁膜42のコンタクトホー

50

ル 4 2 b を介して制御電極 6 c に電気的に接続している。なお、半導体膜 5 のソース電極 6 b と接する領域、およびドレイン領域と接する領域は、高濃度の不純物がドープされた、厚さが約 50 nm の高濃度 n 型半導体層 5 1、5 2 が形成されている。

#### 【 0 0 2 3 】

このように構成した液晶表示装置 1 では、容量線 3 b、ゲート絶縁膜 4 1、制御電極 6 c、層間絶縁膜 4 2、第 1 の副画素電極 9 1 が平面的に重なる領域で積層されている。従って、容量線 3 b と第 1 の副画素電極 9 1 との間には保持容量 C が構成され、かつ、保持容量 C は、第 1 の副補助容量 C 1 と第 2 の副補助容量 C 2 とに分割されている。ここで、第 2 の副補助容量 C 2 は、容量線 3 b を下電極とし、ゲート絶縁膜 4 1 を誘電体層とし、制御電極 6 c を上電極としており、第 1 の副補助容量 C 1 は、制御電極 6 c を下電極とし、層間絶縁膜 4 2 を誘電体層とし、第 1 の副画素電極 9 1 を上電極としている。10

#### 【 0 0 2 4 】

従って、第 2 の副補助容量 C 2 を下層側副補助容量とし、第 1 の副補助容量 C 1 を上層側副補助容量とみなしたとき、下層側副補助容量（第 2 の副補助容量 C 2 ）の上電極と、上層側副補助容量（第 1 の副補助容量 C 1 ）の下電極とは、共通の導電層（制御電極 6 c）によって構成されている。

#### 【 0 0 2 5 】

また、本形態の液晶表示装置 1 では、第 1 の副画素電極 9 1 と対向電極 2 1 との間に第 1 の副液晶容量 L 1 が構成され、第 2 の副画素電極 9 2 と対向電極 2 1 との間に第 2 の副液晶容量 L 2 が構成されている。ここで、容量線 3 b は、対向電極 2 1 と同一の電位に保持されるので、副液晶容量 9 1、9 2 と、副補助容量 C 1、C 2 との電気的な接続は、図 2 を参照して説明したとおりである。20

#### 【 0 0 2 6 】

##### （ 製造方法 ）

このような液晶表示装置 1 を製造するにあたって、素子基板 1 0 は概ね、以下の工程

ゲート電極 3 c、容量線 3 b の形成工程

ゲート絶縁膜 4 1 の形成工程

半導体膜 5 の形成工程

高濃度 n 型半導体層 5 1、5 2 の形成工程

ソース電極 6 b、制御電極 6 c、ドレイン電極 6 c の形成工程

層間絶縁膜 4 2 の形成工程

コンタクトホール 4 2 a、4 2 b の形成工程

副画素電極 9 1、9 2 の形成工程

により製造でき、画素分割を行わない場合と同様、5 回のフォトリソグラフィ工程で済む。すなわち、フォトリソグラフィ工程で用いるマスクパターンを一部変更するだけで、画素分割を採用した液晶表示装置 1 を製造できる。30

#### 【 0 0 2 7 】

##### （ 本形態の効果 ）

以上説明したように、本形態では、画素分割を行うにあたって、液晶容量 L に並列に電気的に接続される補助容量 C を複数の副補助容量 C 1、C 2 に分割し、複数の副補助容量 C 1、C 2 によって容量分割された電圧が複数の副液晶容量 L 1、L 2 に印加されるよう構成してあるため、補助容量 C の他に制御容量を追加する必要がない。従って、画素分割によって視角特性を改善した場合でも、画素開口率の低下を抑えることができる。40

#### 【 0 0 2 8 】

また、2 つの副補助容量 C 1、C 2 はいずれも、絶縁層を挟んで対向する 2 つの導電層を下電極および上電極として構成され、下層側副補助容量（第 2 の副補助容量 C 2 ）の上電極と、上層側副補助容量（第 1 の副補助容量 C 1 ）の下電極とは、共通の導電層（制御電極 6 c）によって構成されている。このため、2 つの副補助容量 C 1、C 2 を構成するための導電層が少なくて済むため、TFT 3 0などを構成する複数の導電層と同時形成された導電層のみで 2 つの副補助容量 C 1、C 2 を構成できる。また、下層側副補助容量（50

第2の副補助容量C2)と、上層側副補助容量(第1の副補助容量C1)とを平面的に重なる領域に形成できるので、画素分割によって視角特性を改善した場合でも、画素開口率の低下を抑えることができる。

#### 【0029】

##### [実施の形態2]

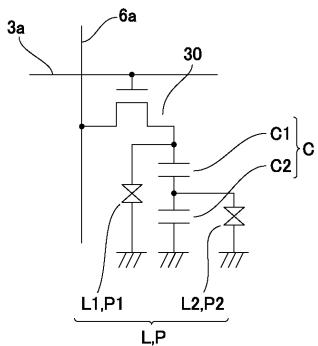

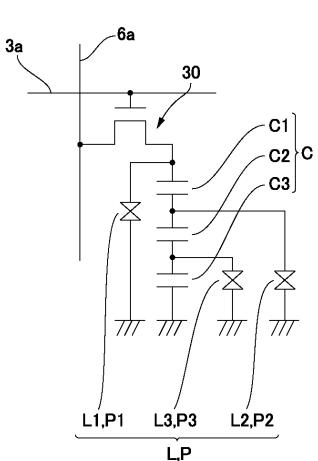

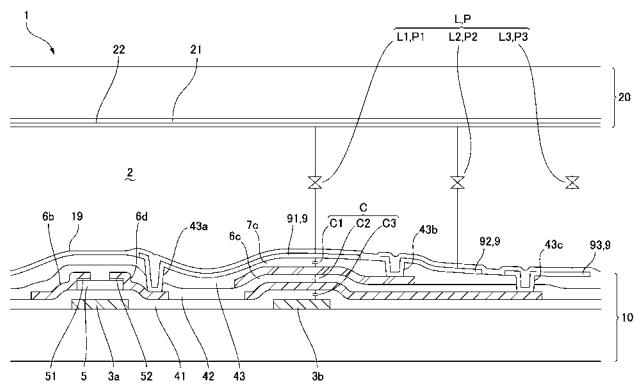

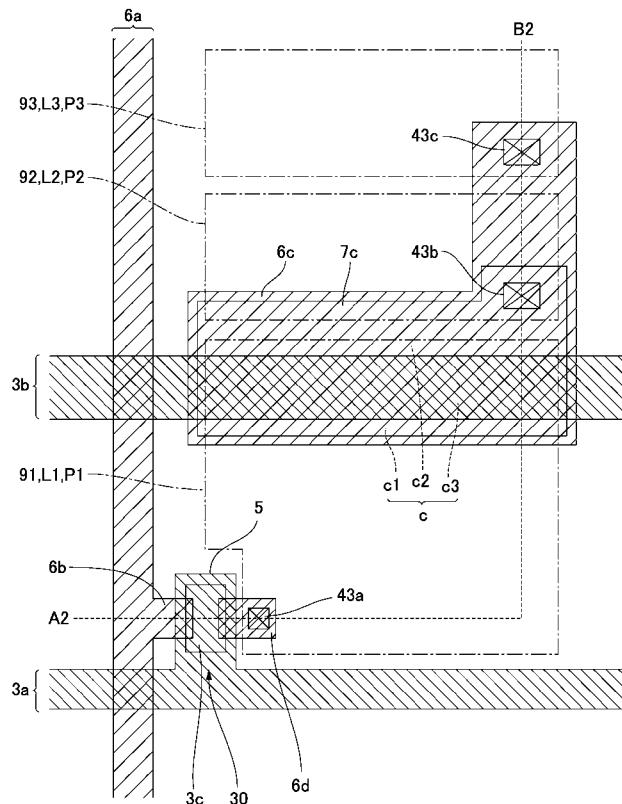

図5、図6および図7は、本発明の実施の形態2に係る液晶表示装置の画素1つ分の等価回路図、この液晶表示装置の画素1つ分の断面図、および素子基板の画素1つ分の平面図である。なお、図6は、図7のA2-B2線での断面図に相当する。また、図7には、データ線と同時形成された導電膜に対しては右上がりの斜線を付し、走査線と同時形成された導電膜に対しては、右下がりの斜線を付し、画素電極については一点鎖線で示してある。本形態の液晶表示装置は、基本的な構成が実施の形態1と同様であるため、共通する機能を有する部分には同一の符号を付してそれらの説明を省略する。

#### 【0030】

図5に示すように、本形態の液晶表示装置1は、複数の画素Pの各々に液晶容量Lおよび補助容量Cを備えており、補助容量Cは、直列に接続された3つの副補助容量C1、C2、C3に分割され、液晶容量Lは、3つの副補助容量C1、C2、C3によって容量分割された電圧が印加される3つの副液晶容量L1、L2、L3に分割されている。従って、画素Pは、3つの副液晶容量L1、L2、L3の各々に対応する3つの副画素P1、P2、P3に分割されている。3つの副液晶容量L1、L2、L3のうち、第1の副液晶容量L1は、3つの副補助容量C1、C2、C3を合成した容量に並列に電気的に接続し、第2の副液晶容量L2は、2つの副補助容量C2、C3を合成した容量に並列に電気的に接続し、第3の副液晶容量L3は、第3の副補助容量C3に並列に電気的に接続している状態にある。

#### 【0031】

このように構成した液晶表示装置1では、TFT30がオンした際、データ線6aの電位が3つの副補助容量C1、C2、C3とによって分割され、以下の高低で示す電位

第3の副補助容量C3および第3の副液晶容量L3

<第2の副補助容量C2および第2の副液晶容量L2

<第1の副補助容量C1および第1の副液晶容量L1

が印加されることになる。

#### 【0032】

このように本形態では、画素分割を行うにあたって、液晶容量Lに並列に電気的に接続される補助容量Cを複数の副補助容量C1、C2、C3に分割し、複数の副補助容量C1、C2、C3によって容量分割された電圧が複数の副液晶容量L1、L2、L3に印加されるように構成してあるため、補助容量Cの他に制御容量を追加する必要がない。従って、画素分割によって視角特性を改善した場合でも、画素開口率の低下を抑えることができる。

#### 【0033】

本形態の液晶表示装置1を構成するにあたっては、図6に示すように、素子基板10と対向基板20とが対向配置され、かつ、これらの基板間に液晶層2が保持されている。本形態では、液晶層2には、後述するIPSモード以外の全ての液晶が用いられるので、対向基板20には、ITO層からなる対向電極21、および配向膜29がこの順に形成されている。

#### 【0034】

このような液晶表示装置1における素子基板10の平面構成は、図7に示すように表される。データ線6a、走査線3a、TFT30などの構成は、実施の形態1と同様であるため、説明を省略するが、容量線3bと平面的に重なる領域には、第1の制御電極6cが形成され、第3の副補助容量C3が形成されている。第1の制御電極6cと平面的に重なる領域には、第2の制御電極7cが形成され、第2の副補助容量C2が形成されている。

#### 【0035】

10

20

30

40

50

ここで、画素 P には、第 1 の副画素 P 1 (第 1 の副液晶容量 L 1 ) を形成するため第 1 の副画素電極 9 1 が電気的に接続され、この第 1 の副画素電極 9 1 の一部は第 2 の制御電極 7 c と平面的に重なって第 1 の副補助容量 C 1 を形成している。また、画素 P には、第 2 の副画素 P 2 (第 2 の副液晶容量 L 2 ) を形成するための第 2 の副画素電極 9 2 が形成され、第 2 の副画素電極 9 2 は、第 2 の制御電極 4 c にコンタクトホール 4 3 b を介して接続している。さらに、画素 P には、第 3 の副画素 P 3 (第 3 の副液晶容量 L 3 ) を形成するための第 3 の副画素電極 9 3 が形成され、第 3 の副画素電極 9 2 は、第 1 の制御電極 6 c にコンタクトホール 4 3 c を介して接続している。

#### 【 0 0 3 6 】

このように構成した素子基板 2 0 の断面構成は、図 7 に示すように、素子基板 1 0 の下層側から上層側に向かって、TFT 3 0 のゲート電極 3 c 、厚さが約 3 0 0 nm のシリコン窒化膜などからなるゲート絶縁膜 4 1 、厚さが約 1 5 0 nm のシリコン膜などからなる半導体膜 5 、ソース電極 6 b 、厚さが約 1 8 0 nm のシリコン窒化膜などからなる第 1 の層間絶縁膜 4 2 、第 2 の制御電極 7 c 、厚さが約 1 8 0 nm のシリコン窒化膜などからなる第 2 の層間絶縁膜 4 3 、画素電極 9 、配向膜 1 9 が積層された構造になっている。

#### 【 0 0 3 7 】

ここで、ゲート電極 3 c と同層位置 (ゲート絶縁膜 4 1 の下層) には、容量線 3 b が形成され、これらの導電層はいずれも、例えば、厚さが約 2 5 0 nm のアルミニウム層と、厚さが約 2 5 0 nm のモリブデン層との積層体として構成されている。また、ソース電極 6 b と同層位置 (ゲート絶縁膜 4 1 と層間絶縁膜 4 2 の層間) には、ドレイン電極 6 d および第 1 の制御電極 6 c が形成され、これらの導電層はいずれも、例えば、厚さが約 2 5 0 nm のアルミニウム層と、厚さが約 2 5 0 nm のモリブデン層との積層体として構成されている。さらに、層間絶縁膜 4 2 の上層側には、画素電極 9 として、第 1 の副画素電極 9 1 、第 2 の副画素電極 9 2 、および第 3 の副画素電極 9 3 が形成され、これらの導電層はいずれも、例えば、厚さが約 5 0 nm のITOによって構成されている。なお、第 2 の制御電極 7 c も、例えば、厚さが約 2 5 0 nm のアルミニウム層と、厚さが約 2 5 0 nm のモリブデン層との積層体として構成されている。

#### 【 0 0 3 8 】

第 1 の副画素電極 9 1 は、層間絶縁膜 4 2 、4 3 のコンタクトホール 4 3 a を介してドレイン電極 6 d に電気的に接続し、第 2 の副画素電極 9 2 は、第 2 の層間絶縁膜 4 3 のコンタクトホール 4 3 b を介して第 2 の制御電極 7 c に電気的に接続し、第 3 の副画素電極 9 3 は、層間絶縁膜 4 2 、4 3 のコンタクトホール 4 3 c を介して第 1 の制御電極 6 c に電気的に接続している。

#### 【 0 0 3 9 】

このように構成した液晶表示装置 1 では、容量線 3 b 、ゲート絶縁膜 4 1 、第 1 の制御電極 6 c 、第 1 の層間絶縁膜 4 2 、第 2 の制御電極 7 c 、第 2 の層間絶縁膜 4 3 、第 1 の副画素電極 9 1 が平面的に重なる領域で積層されている。従って、容量線 3 b と第 1 の副画素電極 9 1 との間には保持容量 C が構成され、かつ、保持容量 C は、3 つの副補助容量 C 1 、C 2 、C 3 に分割されている。ここで、第 3 の副補助容量 C 3 は、容量線 3 b を下電極とし、ゲート絶縁膜 4 1 を誘電体層とし、第 1 の制御電極 6 c を上電極としており、第 2 の副補助容量 C 1 は、第 1 の制御電極 6 c を下電極とし、層間絶縁膜 4 2 を誘電体層とし、第 2 の制御電極 7 c を上電極としており、第 1 の副補助容量 C 1 は、第 2 の制御電極 7 c を下電極とし、第 2 の層間絶縁膜 4 3 を誘電体層とし、第 1 の副画素電極 9 1 を上電極としている。従って、下層側に位置する副補助容量と、上層側に位置する副補助容量とは、電極を共有しているので、3 つの副補助容量 C 1 、C 2 、C 3 を構成する場合でも、導電層が少なくて済む。しかも、3 つの副補助容量 C 1 、C 2 、C 3 を平面的に重なる領域に形成できるので、画素分割によって視角特性を改善した場合でも、画素開口率の低下を抑えることができる。

#### 【 0 0 4 0 】

#### [ 実施の形態 3 ]

10

20

30

40

50

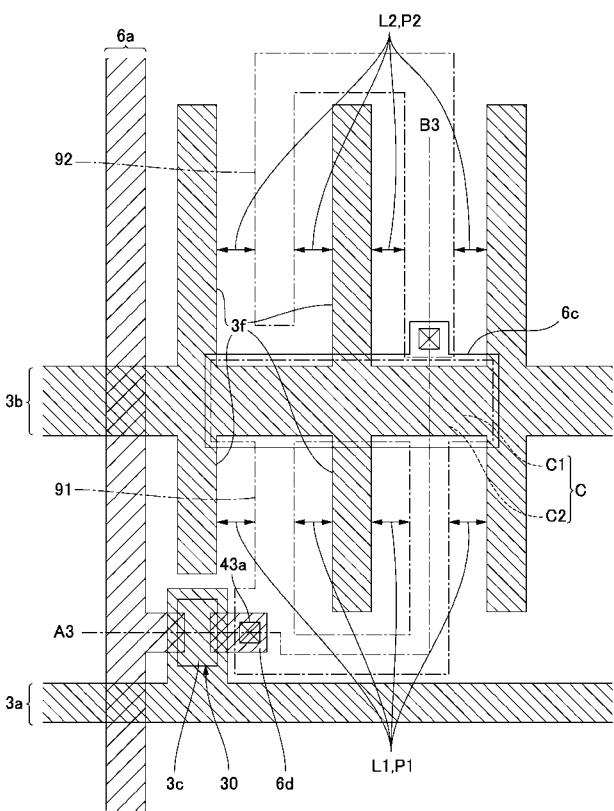

図8は、本発明の実施の形態3に係る液晶表示装置の平面図であり、データ線と同時形成された導電膜に対しては右上がりの斜線を付し、走査線と同時形成された導電膜に対しては、右下がりの斜線を付し、画素電極については一点鎖線で示してある。

#### 【0041】

本形態の液晶表示装置1は、実施の形態1において図2を参照して説明したように、補助容量Cは、直列に接続された2つの副補助容量C1、C2に分割され、液晶容量Lは、2つの副補助容量C1、C2によって容量分割された電圧が印加される2つの副液晶容量L1、L2に分割されている。従って、画素Pは、2つの副液晶容量L1、L2の各々対応する2つの副画素P1、P2に分割されている。

#### 【0042】

本形態の液晶表示装置1を構成するにあたっては、素子基板と対向基板とが対向配置され、かつ、これらの基板間に液晶層が保持されている。本形態では、液晶層にはIPS(In-Plane Switching)モードの液晶が用いられているため、対向基板には、ITO層からなる対向電極が形成されているが、配向膜は形成されていない。

#### 【0043】

このような液晶表示装置1において、素子基板10に副補助容量C1、C2を構成するための断面構成は、実施の形態1と略同様であるが、IPSモードでは、液晶に水平方向の電界を印加するため、副液晶容量L1、L2(副画素P1、P2)を構成する副画素電極91、92に対向する共通電極も、素子基板20の方に形成する必要がある。従って、本形態の液晶表示装置1において、素子基板10は、図8に示す平面構成を有している。

#### 【0044】

図8において、データ線6aと交差する方向に走査線3aが形成されるとともに、走査線3aと並列して容量線3bが形成されている。データ線6aは、TFT30のソース電極6bと一体に形成され、走査線3aは、TFT30のゲート電極3cと一体に構成されている。また、容量線3bと平面的に重なる領域には、制御電極6cが形成され、制御電極6と容量線3bとの間に第2の副補助容量C2が形成されている。TFT30のドレン領域には、ドレン電極6dを介して第1の副画素P1(第1の副液晶容量L1)を形成するための第1の副画素電極91が電気的に接続され、この第1の副画素電極91の一部は制御電極6cと平面的に重なって第1の副補助容量C1を形成している。また、画素Pには、第2の副画素P2(第2の副液晶容量L2)を形成するための第2の副画素電極92が形成され、第2の副画素電極92は、制御電極6cにコンタクトホール42bを介して接続している。

#### 【0045】

本形態では、容量線3bの一部を櫛歯状に形成し、櫛歯状の共通電極3fが形成されている。また、第1の副画素電極91および第2の副画素電極92は、櫛歯状の共通電極3fと横方向で対向するように、櫛歯状の共通電極3fの間に向けて櫛歯状に形成されている。従って、第1の副画素電極91と共通電極3fとの間に第1の副液晶容量L1(第1の副画素P2)が構成され、第2の副画素電極92と共通電極3fとの間に第2の副液晶容量L2(第1の副画素P2)が構成されている。なお、本形態では、第1の副画素電極91には、制御電極6cと平面的に重なって第1の副補助容量C1を形成するための矩形部分が櫛歯部分の先端に形成されている。

#### 【0046】

このように構成したIPSモードの液晶表示装置1でも、画素分割を行うにあたって、液晶容量Lに並列に電気的に接続される補助容量Cを複数の副補助容量C1、C2に分割し、複数の副補助容量C1、C2によって容量分割された電圧が複数の副液晶容量L1、L2に印加されるように構成してあるため、補助容量Cの他に制御容量を追加する必要がない。従って、画素分割によって視角特性を改善した場合でも、画素開口率の低下を抑えることができるなど、実施の形態1と同様な効果を奏する。

#### 【0047】

また、本形態ではIPSモードを用いたが、それに限る必要は無く、同じく横電界を用

10

20

30

40

50

いるFFS(Fring e Field Switching)などでも同様に用いることができる。

【0048】

【電子機器への搭載例】

本発明を適用した電気光学装置は、携帯電話機やモバイル型のパーソナルコンピュータの他、マルチメディア対応のパーソナルコンピュータ(PC)、エンジニアリング・ワークステーション(EWS)、ペーディヤ、ワードプロセッサ、テレビ、ビューファインダ型またはモニタ直視型のビデオテープレコーダ、電子手帳、電子卓上計算機、カーナビゲーション装置、POS端末、タッチパネルなどの電子機器に適用できる他、30インチを越えるような大画面を備えた電子機器を構成するのに用いることもできる。 10

【図面の簡単な説明】

【0049】

【図1】画素スイッチング素子としてTFTを用いた液晶表示装置の基本的な電気的構成を示すブロック図である。

【図2】本発明の実施の形態1に係る液晶表示装置の画素1つ分の等価回路図である。

【図3】本発明の実施の形態1に係る液晶表示装置の画素1つ分の断面図である。

【図4】本発明の実施の形態1に係る液晶表示装置の画素1つ分の平面図である。

【図5】本発明の実施の形態2に係る液晶表示装置の画素1つ分の等価回路図である。

【図6】本発明の実施の形態2に係る液晶表示装置の画素1つ分の断面図である。

【図7】本発明の実施の形態2に係る液晶表示装置の画素1つ分の平面図である。

【図8】本発明の実施の形態3に係る液晶表示装置の画素1つ分の平面図である。 20

【符号の説明】

【0050】

1…液晶表示装置、2…液晶層、3a…走査線、3b…容量線、3c…ゲート電極、3f…櫛歯状の共通電極、5…半導体膜、6a…データ線、6b…ソース電極、6c、7c…制御電極、6d…ドレイン電極、9…画素電極、10…素子基板、20…対向基板、21…対向電極、30…TFT、41…ゲート絶縁膜、42、43…層間絶縁膜、91、92、93…副画素電極、C…補助容量、C1、C2、C3…副補助容量、L…液晶容量、L1、L2、L3…副液晶容量、P…画素、P1、P2、P3…副画素 30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

F ターム(参考) 5F110 AA30 BB01 CC07 EE03 EE04 EE14 FF03 GG02 GG24 HK03

HK04 HK08 HK22 NN04 NN24 NN72 NN73

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)     | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号     | <a href="#">JP2006276582A</a>                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2006-10-12 |

| 申请号         | JP2005097193                                                                                                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2005-03-30 |

| 申请(专利权)人(译) | 三洋爱普生影像设备公司                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人      | 佐藤尚                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人         | 佐藤 尚                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号      | G02F1/1368 H01L29/786 H01L21/336                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| F1分类号       | G02F1/1368 H01L29/78.612.Z                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| F-TERM分类号   | 2H092/GA11 2H092/JA24 2H092/JA34 2H092/JA37 2H092/JA41 2H092/JB13 2H092/NA01 2H092 /NA07 2H092/PA01 2H092/PA06 5F110/AA30 5F110/BB01 5F110/CC07 5F110/EE03 5F110/EE04 5F110/EE14 5F110/FF03 5F110/GG02 5F110/GG24 5F110/HK03 5F110/HK04 5F110/HK08 5F110 /HK22 5F110/NN04 5F110/NN24 5F110/NN72 5F110/NN73 2H192/AA24 2H192/BB02 2H192/BC26 2H192/BC31 2H192/CB05 2H192/CC32 2H192/CC72 2H192/DA12 2H192/DA13 2H192/DA23 2H192 /DA32 2H192/DA42 2H192/DA65 |         |            |

| 代理人(译)      | 须泽 修                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接        | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

### 摘要(译)

解决的问题：提供一种即使在通过分割像素而改善了视角特性的情况下，也能够抑制像素开口率的降低的液晶显示装置。在液晶显示装置的多个像素P中，存储电容器C被分为串联连接的两个子存储电容器C1和C2，液晶电容器L被分为两个子存储电容器C1和C2。它被分成两个子液晶电容器L1和L2，对其施加电压除以电容。因此，像素P被分为分别与两个子液晶电容器L1和L2相对应的两个子像素P1和P2。[选择图]图2