(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-184903

(P2006-184903A)

(43) 公開日 平成18年7月13日(2006.7.13)

(51) Int.CI.

G02F 1/1343 (2006.01)

G02F 1/1368 (2006.01)

F 1

G02F 1/1343

G02F 1/1368

テーマコード(参考)

2 H 0 9 2

審査請求 有 請求項の数 41 O L (全 26 頁)

(21) 出願番号 特願2005-369463 (P2005-369463)

(22) 出願日 平成17年12月22日 (2005.12.22)

(31) 優先権主張番号 2004-112578

(32) 優先日 平成16年12月24日 (2004.12.24)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 501426046

エルジー・フィリップス エルシーテー

カンパニー、リミテッド

大韓民国 ソウル、ヨンドゥンポーク、ヨ

イドードン 20

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100094112

弁理士 岡部 謙

(74) 代理人 100096943

弁理士 白井 伸一

(74) 代理人 100101498

弁理士 越智 隆夫

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその製造方法

## (57) 【要約】

【課題】本発明は、工程を単純化できる水平電界薄膜トランジスタ基板を用いた液晶表示装置及びその製造方法を提供する。

【解決手段】本発明の液晶表示装置に用いる薄膜トランジスタ基板は、ゲートライン102及び共通ライン120は少なくとも二重導電層を有する第1導電層グループで形成され、共通電極122は共通ライン120の中少なくとも一つの導電層が延びて形成され、データライン104、ソース電極110、及びドレーン電極112は少なくとも二重導電層を有する第2導電層グループで形成され、画素電極118はドレーン電極112の中少なくとも一つの導電層が延びて形成されたことを特徴とする。

【選択図】 図2

## 【特許請求の範囲】

## 【請求項 1】

基板上に形成されたゲートラインと、

前記ゲートラインとゲート絶縁膜を挟んで交差して画素領域を定義するデータラインと、

前記ゲートラインと接続したゲート電極、前記データラインと接続したソース電極、前記ソース電極と対向するドレーン電極、前記ソース電極とドレーン電極との間のチャネルを形成する半導体パターンを含む薄膜トランジスタと、

前記ゲートラインと並んで前記基板上に形成された共通ラインと、

前記共通ラインから前記画素領域に延びて形成された共通電極と、

前記ドレーン電極から前記画素領域に、前記共通電極と水平電界とを形成するように伸張された画素電極とを備え、

前記ゲートライン及び共通ラインは、少なくとも二重導電層を有する第1導電層グループで形成され、前記共通電極は、前記共通ラインの中少なくとも一つの導電層が延びて形成され、前記データライン、ソース電極及びドレーン電極は、少なくとも二重導電層を有する第2導電層グループで形成され、前記画素電極は、前記ドレーン電極の中少なくとも一つの導電層が延びて形成されたことを特徴とする液晶表示装置。

## 【請求項 2】

前記ドレーン電極が、前記ゲート絶縁膜を挟んで前記共通電極の一部分と重畠されて形成されたストレージキャパシタをさらに含むことを特徴とする請求項1に記載の液晶表示装置。 20

## 【請求項 3】

前記共通電極は前記共通ラインの最下部層から延びて形成され、前記画素電極は前記ドレーン電極の最下部層から延びて形成されたことを特徴とする請求項1に記載の液晶表示装置。

## 【請求項 4】

前記第1及び第2導電層グループの前記共通電極及び画素電極を形成する前記少なくとも一つの導電層が、透明導電層、Ti及びWの中少なくとも1つを含むことを特徴とする請求項1または3に記載の液晶表示装置。

## 【請求項 5】

前記少なくとも一つの導電層を除外した残りの導電層は、Mo、Ti、Cu、Al、Cr、Mo合金、Cu合金及びAl合金の各単層構造と、該単層構造を組み合わせて構成される二重層構造との中少なくとも1つを備えることを特徴とする請求項4に記載の液晶表示装置。 30

## 【請求項 6】

前記第1導電層グループで形成され、前記ゲート絶縁膜を貫通するコンタクトホールを通じて前記データラインと接続されたデータリンクをさらに含むことを特徴とする請求項1に記載の液晶表示装置。

## 【請求項 7】

前記ゲートラインと接続されたゲートパッド、前記データリンクと接続されたデータパッド、及び前記共通ラインと接続された共通パッドをさらに含み、 40

前記ゲートパッド、データパッド及び共通パッドの各々は、前記第1導電層グループで形成されたパッド下部電極と、

前記ゲート絶縁膜を貫通して前記パッド下部電極を露出させるコンタクトホールと、

前記コンタクトホールを通じて前記パッド下部電極と接続され、前記第2導電層グループの最下部層で形成されたパッド上部電極と、

を含むことを特徴とする請求項6に記載の液晶表示装置。

## 【請求項 8】

前記データパッドの前記パッド上部電極は、前記データラインの最下部層と一体化したこととを特徴とする請求項7に記載の液晶表示装置。 50

**【請求項 9】**

前記ゲートラインと接続されたゲートパッド、前記データリンクと接続されたデータパッド、及び前記共通ラインと接続された共通パッドをさらに含み、

前記ゲートパッド、データパッド及び共通パッドの各々は、前記第1導電層グループで形成されたことを特徴とする請求項6に記載の液晶表示装置。

**【請求項 10】**

前記ゲートパッド、データパッド及び共通パッドの各々は、前記第1導電層グループの中、最下部層で形成されたパッド下部電極と、

前記パッド下部電極上の前記第1導電層グループの残りの上部層で形成されるパッド上部電極と、

前記ゲート絶縁膜を貫通して前記パッド下部電極を露出させるコンタクトホールと、をさらに含むことを特徴とする請求項9に記載の液晶表示装置。

**【請求項 11】**

前記パッド上部電極は、前記コンタクトホールと非重畠されて前記ゲート絶縁膜により保護されることを特徴とする請求項10に記載の液晶表示装置。

**【請求項 12】**

前記データリンク、ソース電極、ドレーン電極及び画素電極は、前記基板とは異なる他基板との合着時にシーリング材により封入される領域に位置することを特徴とする請求項1に記載の液晶表示装置。

**【請求項 13】**

前記コンタクトホールは、前記基板とは異なる他基板との合着時にシーリング材により封入される領域に位置することを特徴とする請求項6に記載の液晶表示装置。

**【請求項 14】**

前記データリンク、前記ソース電極、前記ドレーン電極及び前記画素電極を覆う配向膜をさらに含むことを特徴とする請求項1に記載の液晶表示装置。

**【請求項 15】**

前記データリンク、前記ソース電極、前記ドレーン電極、前記画素電極及び前記コンタクトホールを覆う配向膜をさらに含むことを特徴とする請求項6に記載の液晶表示装置。

**【請求項 16】**

前記半導体パターンは、前記薄膜トランジスタが形成される位置に形成されることを特徴とする請求項1に記載の液晶表示装置。

**【請求項 17】**

前記第1及び第2導電層グループの各々は、透明導電層と、銅金属層または銅合金層とを有する構造で形成されたことを特徴とする請求項1に記載の液晶表示装置。

**【請求項 18】**

前記第1及び第2導電層グループの中少なくとも一つの導電層グループは、階段形態で段差を有するように形成されたことを特徴とする請求項1に記載の液晶表示装置。

**【請求項 19】**

前記半導体パターン、前記ソース電極、前記ドレーン電極及び前記画素電極の少なくとも2層は、直四角形の階段形態を持つ段差を有するように形成されたことを特徴とする請求項1に記載の液晶表示装置。

**【請求項 20】**

少なくとも二重導電層を含む第1導電層グループ構造を有するゲートライン、前記ゲートラインと接続されたゲート電極、前記ゲートラインと並んでいる共通ライン、及び前記共通ラインの前記導電層中少なくとも一つの導電層から延びた共通電極を含む第1マスクパターン群を形成する第1マスク工程と、

前記第1マスクパターン群を覆うゲート絶縁膜と、その上に半導体パターンを形成する第2マスク工程と、

データリンク、前記データリンクと接続され少なくとも二重導電層を含む第2導電層グループ構造を有するソース電極と、前記ソース電極と対向するドレーン電極と、前記半導

10

20

30

40

50

体パターンを有するゲート絶縁膜上の前記ドレーン電極の前記導電層の中少なくとも一つの導電層から伸びた画素電極とを含む第3マスクパターン群を形成する第3マスク工程と、

を含むことを特徴とする液晶表示装置の製造方法。

【請求項 21】

前記ドレーン電極で前記ゲート絶縁膜を挟んで、前記共通電極の一部分と重畠されてストレージキャパシタを形成するステップをさらに含むことを特徴とする請求項20に記載の液晶表示装置の製造方法。

【請求項 22】

前記共通電極は前記共通ラインの最下部層が伸びて形成され、前記画素電極は前記ドレーン電極の最下部層が伸びて形成されることを特徴とする請求項20に記載の液晶表示装置の製造方法。 10

【請求項 23】

前記第1及び第2導電層グループの前記共通電極及び画素電極の前記少なくとも一つの導電層が、透明導電層、Ti及びWの中少なくとも1つを含むことを特徴とする請求項20または22に記載の液晶表示装置の製造方法。

【請求項 24】

前記少なくとも一つの導電層を除外した残りの導電層は、Mo、Ti、Cu、Al、Cr、Mo合金、Cu合金及びAl合金の各単層構造と、該単層構造を組み合わせて構成する二重層構造との中少なくとも1つを備えることを特徴とする請求項23に記載の液晶表示装置の製造方法。 20

【請求項 25】

前記第1マスク工程は、前記第1導電層グループで形成されて前記データラインと一部が重畠されたデータリンクを形成するステップを含み、前記第2マスク工程は、前記ゲート絶縁膜を貫通して前記データリンクとデータラインを接続させるコンタクトホールを形成するステップを含むことを特徴とする請求項20に記載の液晶表示装置の製造方法。 30

【請求項 26】

前記第1マスク工程は、

前記基板上に前記第1導電層グループを形成するステップと、

ハーフトーンマスク及び回折露光マスクの中、1つを利用したフォトリソグラフィ工程により厚さが異なる第1フォトレジストパターンを形成するステップと、 30

前記第1フォトレジストパターンを利用したエッチング工程により前記第1導電層グループ構造の共通電極を含む前記第1マスクパターン群を形成するステップと、

前記第1フォトレジストパターンを利用したエッチング工程により前記共通電極の最下部層として残るように前記共通電極をエッチングするステップと、

を含むことを特徴とする請求項25に記載の液晶表示装置の製造方法。 40

【請求項 27】

前記第1マスク工程は、前記第1導電層グループで、前記ゲートライン、前記データリンク及び前記共通ラインの中少なくとも1つと接続されたパッド下部電極を形成するステップをさらに含み、前記第2マスク工程は、前記ゲート絶縁膜を貫通して前記パッド下部電極を露出させるコンタクトホールを形成するステップをさらに含み、前記第3マスク工程は、前記第2導電層グループの最下部層で、前記コンタクトホールを通じて前記パッド下部電極と接続されたパッド上部電極を形成するステップをさらに含むことを特徴とする請求項26に記載の液晶表示装置の製造方法。

【請求項 28】

前記データパッドの前記パッド上部電極は、前記データラインの最下部層と一体化して形成されることを特徴とする請求項27に記載の液晶表示装置の製造方法。

【請求項 29】

前記第2マスク工程は、前記第1マスクパターン群を覆うゲート絶縁膜、非晶質シリコン層、及び不純物がドーピングされた非晶質シリコン層を形成するステップと、 50

ハーフトーンマスク及び回折露光マスクの中、1つを利用したフォトリソグラフィ工程により厚さが異なる第2フォトレジストパターンを形成するステップと、

前記第2フォトレジストパターンを利用したエッチング工程により前記コンタクトホールと、前記半導体パターンを形成するステップと、

を含むことを特徴とする請求項27に記載の液晶表示装置の製造方法。

#### 【請求項30】

前記第3マスク工程は、前記半導体パターンを有するゲート絶縁膜上に前記第2導電層グループを形成するステップと、

ハーフトーンマスク及び回折露光マスクの中、1つを利用して厚さが異なる第3フォトレジストパターンを形成するステップと、10

前記第3フォトレジストパターンを利用したエッチング工程により前記第2導電層グループをパターニングして前記パッド上部電極を含む第3マスクパターン群を形成するステップと、

前記ソース電極とドレーン電極との間に露出された不純物がドーピングされた非晶質シリコン層を除去するステップと、

前記第3フォトレジストパターンをマスクとして利用したエッチング工程により前記画素電極及びパッド上部電極の最下部層のみ残るように前記共通電極をエッチングするステップと、

を含むことを特徴とする請求項29に記載の液晶表示装置の製造方法。

#### 【請求項31】

前記第1マスク工程は、前記第1導電層で、前記ゲートライン、前記データリンク及び前記共通ラインの中、少なくとも1つと接続されたパッドを形成するステップを更に含み、前記第2マスク工程は、前記パッドを露出させるコンタクトホールを形成するステップを更に含むことを特徴とする請求項26に記載の液晶表示装置の製造方法。20

#### 【請求項32】

前記パッドを形成するステップは、前記フォトレジストパターンを利用したエッチング工程により前記第1導電層グループ構造のパッド下部電極及びパッド上部電極を有するパッドを形成するステップと、

アッシングされたフォトレジストパターンを利用したエッチング工程により前記パッド上部電極を貫通して前記パッド下部電極を露出させるステップと、30

を含むことを特徴とする請求項31に記載の液晶表示装置の製造方法。

#### 【請求項33】

前記コンタクトホールは、前記パッド上部電極と非重畠されて前記パッド下部電極が露出されるように形成されることを特徴とする請求項32に記載の液晶表示装置の製造方法。40

#### 【請求項34】

前記データライン、前記ソース電極、前記ドレーン電極及び前記画素電極は、前記基板とは異なる他基板との合着時にシーリング材により封入される領域に形成されることを特徴とする請求項20に記載の液晶表示装置の製造方法。

#### 【請求項35】

前記コンタクトホールは、前記基板とは異なる他基板との合着時にシーリング材により封入される領域に形成されることを特徴とする請求項25に記載の液晶表示装置の製造方法。

#### 【請求項36】

前記データライン、前記ソース電極、前記ドレーン電極及び前記画素電極を覆う配向膜を形成するステップを更に含むことを特徴とする請求項20に記載の液晶表示装置の製造方法。

#### 【請求項37】

前記データライン、前記ソース電極、前記ドレーン電極、前記画素電極及び前記コンタクトホールを覆う配向膜を形成するステップを更に含むことを特徴とする請求項25に記50

載の液晶表示装置の製造方法。

【請求項 3 8】

前記半導体パターンは、前記薄膜トランジスタが形成される位置に形成されることを特徴とする請求項 2 0 に記載の液晶表示装置の製造方法。

【請求項 3 9】

前記第 1 及び第 2 導電層グループの各々は、透明導電層と、銅金属層または銅合金層とを持つ構造を有することを特徴とする請求項 2 0 に記載の液晶表示装置の製造方法。

【請求項 4 0】

前記第 1 及び第 2 導電層グループの中、少なくとも一つの導電層グループは、直四角形の階段形態で段差を有するように形成されることを特徴とする請求項 2 0 に記載の液晶表示装置の製造方法。

【請求項 4 1】

前記半導体パターン、前記ソース電極、前記ドレーン電極及び前記画素電極の中の少なくとも 2 層は、直四角形の階段形態で段差を有するように形成されることを特徴とする請求項 2 0 に記載の液晶表示装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、水平電界を利用する液晶表示装置に係り、特に、工程を単純化できる水平電界薄膜トランジスタ基板を用いた液晶表示装置及びその製造方法に関する。

【背景技術】

【0 0 0 2】

液晶表示装置は、電界を利用して誘電異方性を有する液晶の光透過率を調節することによって画像を表示することになる。このために、液晶表示装置は液晶セルマトリックスを通じて画像を表示する液晶表示パネル（以下、「液晶パネル」という。）と、その液晶パネルを駆動する駆動回路とを備える。

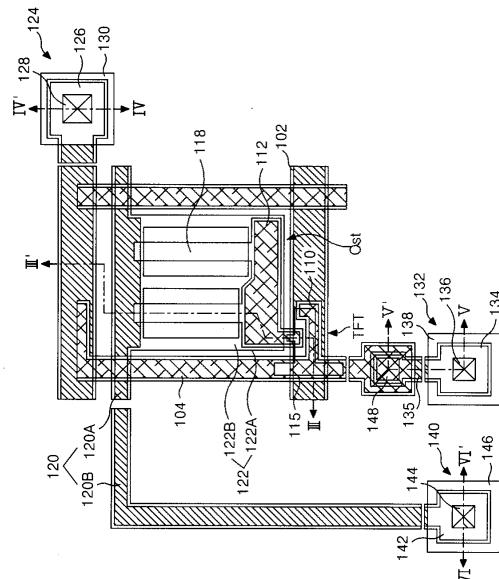

【0 0 0 3】

図 1 を参照すれば、従来の液晶パネルは、液晶 2 4 を挟んで接合されたカラーフィルタ基板 1 0 と薄膜トランジスタ基板 2 0 とから構成される。

【0 0 0 4】

カラーフィルタ基板 1 0 は、上部ガラス基板 2 上に順に形成されたブラックマトリックス 4、カラーフィルタ 6 及び共通電極 8 を備える。ブラックマトリックス 4 は、上部ガラス基板 2 にマトリックス形態で形成される。このようなブラックマトリックス 4 は、上部ガラス基板 2 の領域をカラーフィルタ 6 が形成される複数のセル領域に分け、隣接したセルの間の光干渉及び外部光反射を防止する。カラーフィルタ 6 は、ブラックマトリックス 4 により区分されたセル領域に赤（R）、緑（G）、青（B）に区分されるように形成されて、赤、緑及び青色の光を各々透過させる。共通電極 8 は、カラーフィルタ 6 上に全面塗布された透明導電層で、液晶 2 4 駆動時の基準となる共通電圧（Vcom）を供給する。そして、カラーフィルタ 6 の平坦化のためにカラーフィルタ 6 と共通電極 8 との間にはオーバーコート層（図示せず）が更に形成される場合もある。

【0 0 0 5】

薄膜トランジスタ基板 2 0 は、下部ガラス基板 1 2 において、ゲートライン 1 4 とデータライン 1 6 との交差により定義されたセル領域毎に形成された薄膜トランジスタ 1 8 と、画素電極 2 2 とを備える。薄膜トランジスタ 1 8 は、ゲートライン 1 4 からのゲート信号に応答してデータライン 1 6 からのデータ信号を画素電極 2 2 に供給する。透明導電層で形成された画素電極 2 2 は、薄膜トランジスタ 1 8 からのデータ信号を供給して液晶 2 4 を駆動させるようにする。

【0 0 0 6】

誘電異方性を有する液晶 2 4 は、画素電極 2 2 のデータ信号と共通電極 8 の共通電圧（Vcom）により形成された電界により回転して光透過率を調節することによって階調が具現

10

20

30

40

50

されるようとする。

【0007】

そして、液晶パネルは、カラーフィルタ基板10と薄膜トランジスタ基板20とのセルギャップを一定に維持するためのスペーサ(図示せず)を更に備える。

【0008】

このような液晶パネルのカラーフィルタ基板10及び薄膜トランジスタ基板20は、複数のマスク工程を利用して形成される。一つのマスク工程は、薄膜蒸着(コーティング)工程、洗浄工程、フォトリソグラフィ工程、エッチング工程、フォトレジスト剥離工程、検査工程などの多数の工程を含む。

【0009】

特に、薄膜トランジスタ基板は、半導体工程を含むと共に、複数のマスク工程を必要とするため製造工程が複雑で液晶パネル製造コストの上昇の重要原因となっている。これによって、薄膜トランジスタ基板は、標準マスク工程であった5マスク工程でマスク工程数を縮める方に発展している。

【0010】

一方、液晶表示装置は、液晶を駆動させる電界の方向によって垂直電界印加型と水平電界印加型に大別される。

【0011】

垂直電界印加型液晶表示装置は、上下部の基板に対向するように配置された画素電極と共通電極との間に形成される垂直電界によりTN(Twisted Nematic)モードの液晶を駆動することになる。垂直電界印加型液晶表示装置は開口率が大きい長所を有する反面、視野角が90度程度で狭いという短所を有する。

【0012】

水平電界印加型液晶表示装置は、下部基板に並んで配置された画素電極と共通電極との間の水平電界によりインプレーンスイッチング(以下、「IPS」という。)モードの液晶を駆動することになる。水平電界印加型液晶表示装置は視野角が160度程度に広いという長所を有する。

【0013】

このような水平電界印加型液晶表示装置の薄膜トランジスタ基板も半導体工程を含む多数のマスク工程を必要とするので、製造工程が複雑であるという短所がある。したがって、製造コストを低減するためにはマスク工程数の短縮が必要である。

【発明の開示】

【発明が解決しようとする課題】

【0014】

したがって、本発明の目的は、工程を単純化できる水平電界薄膜トランジスタを用いた液晶表示装置及びその製造方法を提供することにある。

【課題を解決するための手段】

【0015】

上記目的の達成のために、本発明を適用した液晶表示装置は、基板上に形成されたゲートラインと、ゲートラインとゲート絶縁膜を挟んで交差して画素領域を定義するデータラインと、ゲートラインと接続したゲート電極、データラインと接続したソース電極、ソース電極と対向するドレーン電極、ソース電極とドレーン電極との間のチャネルを形成する半導体パターンを含む薄膜トランジスタと、ゲートラインと並んで基板上に形成された共通ラインと、共通ラインから画素領域に延びて形成された共通電極と、ドレーン電極から画素領域に共通電極と水平電界を形成するように伸張された画素電極とを備え、ゲートライン及び共通ラインは少なくとも二重導電層を有する第1導電層グループで形成され、共通電極は共通ラインの中少なくとも一つの導電層が延びて形成され、データライン、ソース電極及びドレーン電極は少なくとも二重導電層を有する第2導電層グループで形成され、画素電極はドレーン電極の中少なくとも一つの導電層が延びて形成されたことを特徴とする。

## 【0016】

また、本発明を適用した液晶表示装置の製造方法は、少なくとも二重導電層を含む第1導電層グループ構造を有するゲートライン、ゲートラインと接続されたゲート電極、ゲートラインと実際に並んでいる共通ライン及び共通ラインの導電層中、少なくとも一つの導電層から伸びた共通電極を含む第1マスクパターン群を形成する第1マスク工程と、第1マスクパターン群を覆うゲート絶縁膜と、その上に半導体パターンを形成する第2マスク工程と、データライン、データラインと接続され、少なくとも二重導電層を含む第2導電層グループ構造を有するソース電極、ソース電極と対向するドレーン電極及び半導体パターンを有するゲート絶縁膜上のドレーン電極の導電層中、少なくとも一つの導電層から伸びた画素電極を含む第3マスクパターン群を形成する第3マスク工程とを含むことを特徴とする。10

## 【発明の効果】

## 【0017】

本発明の液晶表示装置及びその製造方法は、第1ハーフトーン（または、回折露光）マスクを利用して単層構造の共通電極を複層構造の他の第1マスクパターン群と共に形成する。

## 【0018】

また、本発明の液晶表示装置及びその製造方法は、第2ハーフトーン（または、回折露光マスクを利用して半導体パターン及びコンタクトホールを形成する。

## 【0019】

また、本発明の液晶表示装置及びその製造方法は、第3ハーフトーン（または、回折露光）マスクを利用して保護膜なしに単層構造の画素電極及びパッド上部電極を複層構造の他の第3マスクパターン群と共に形成する。20

## 【0020】

これによって、本発明の液晶表示装置及びその製造方法は、3マスク工程で工程を単純化することによって材料費用及び設備投資費用などを低減すると共に、歩留まりを向上させることができることになる。

## 【0021】

そして、本発明に係る水平電界薄膜トランジスタが適用された液晶パネルは、薄膜トランジスタ基板で保護膜部材に露出されたデータライン、ソース電極、ドレーン電極及び画素電極をその上に塗布される配向膜、または、シーリング材で封入される領域に詰められた液晶により十分保護されるようとする。また、薄膜トランジスタ基板のパッドが全て同一な構造を有するようにし、データパッドと接続されたデータリンクはシーリング材により封入される領域内でコンタクトホールを通じてデータラインと接続されるようとする。これによって、保護膜の不在による電食問題などを防止できることになる。30

## 【0022】

また、本発明の液晶表示装置及びその製造方法は、共通電極及び画素電極が透明導電層で形成されて開口率に寄与できるので開口率が向上する。

## 【発明を実施するための最良の形態】

## 【0023】

以下、本発明の好ましい実施形態を図2乃至図13を参照しつつ詳細に説明する。40

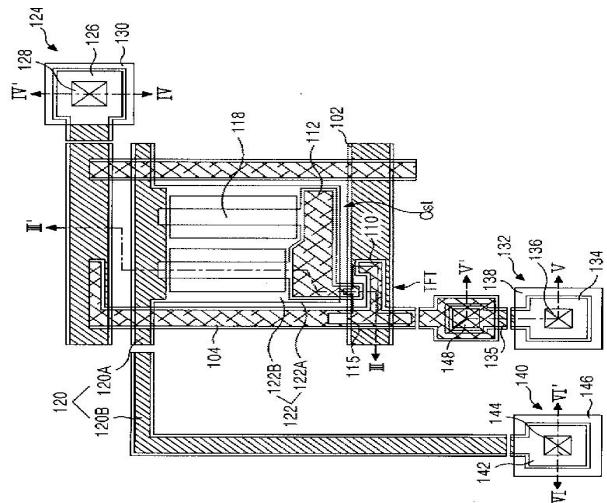

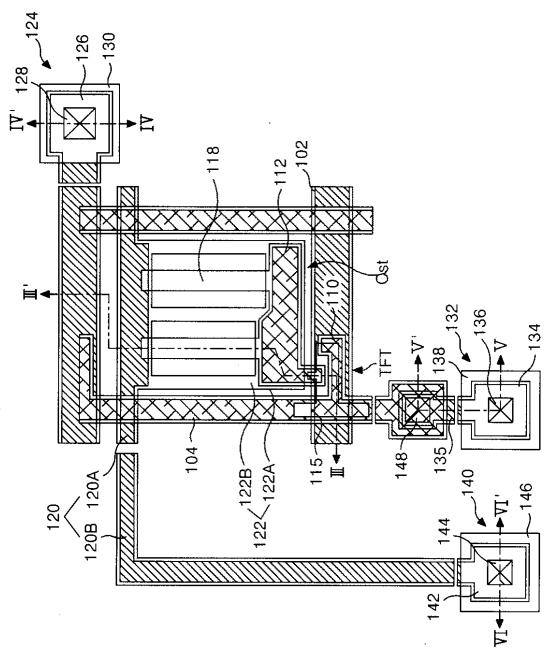

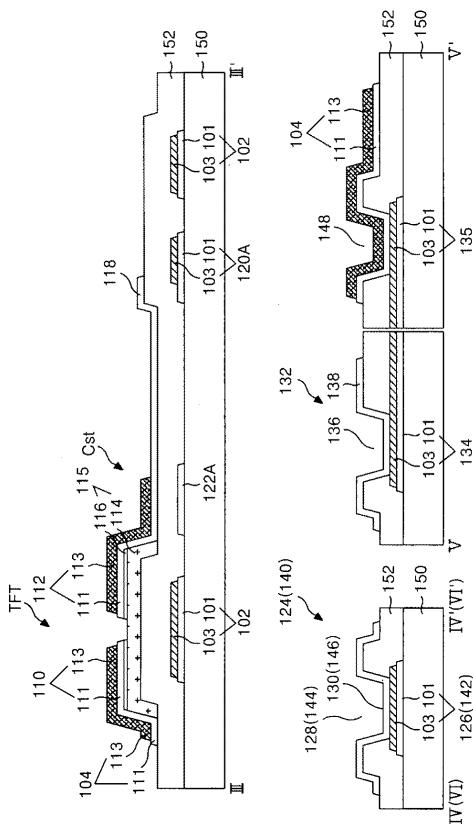

## 【0024】

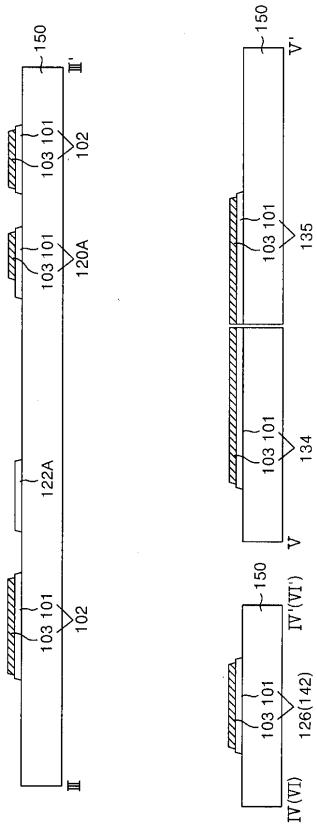

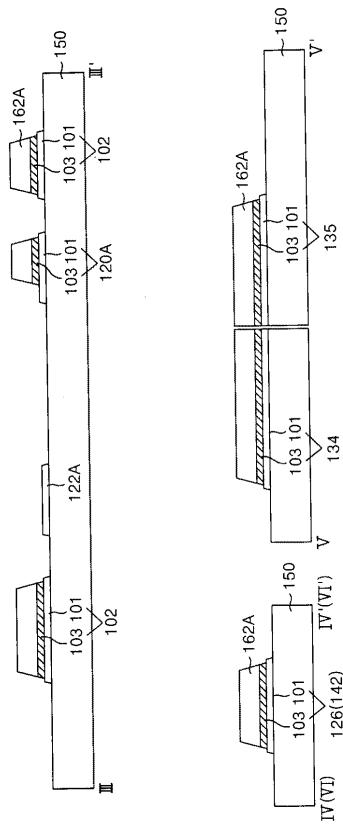

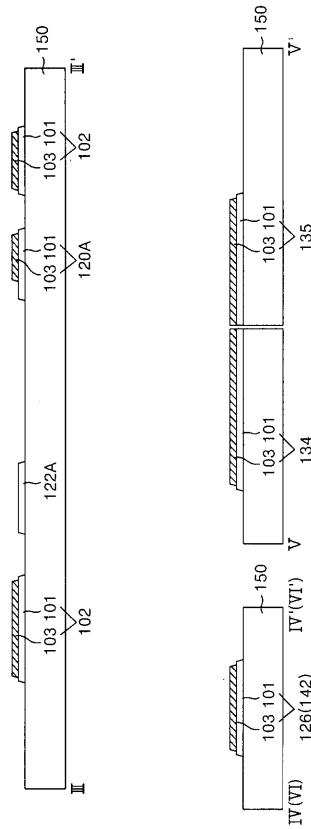

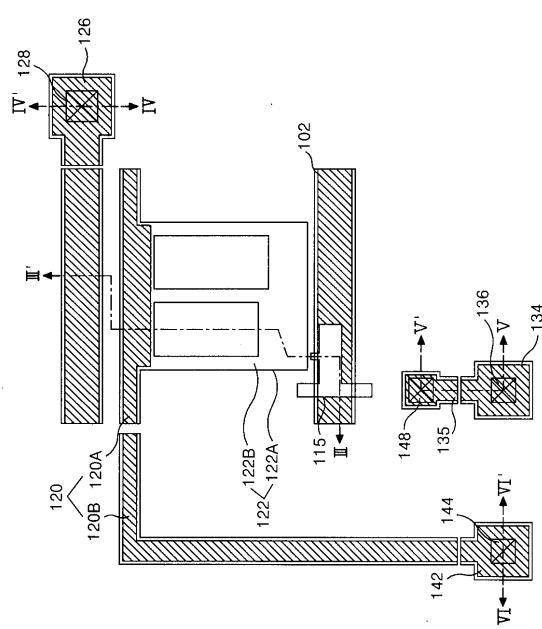

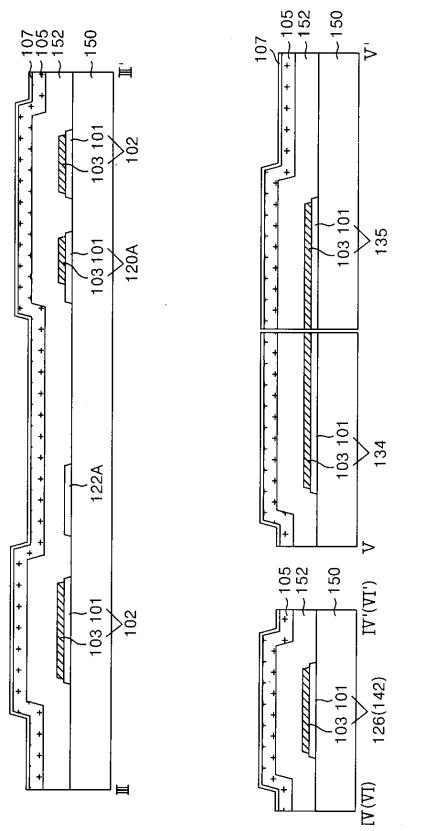

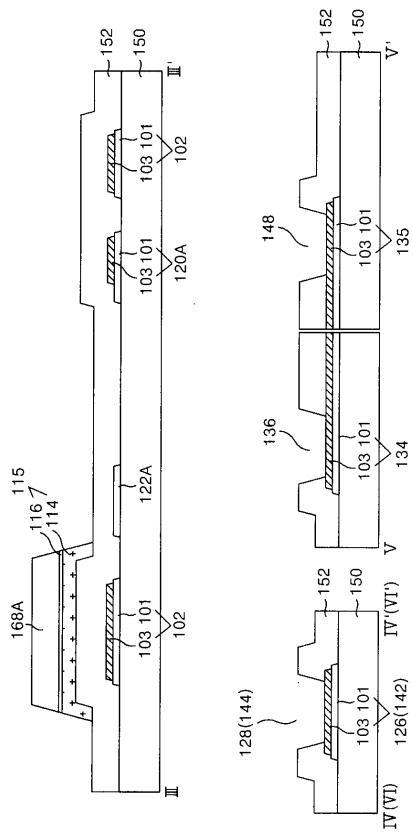

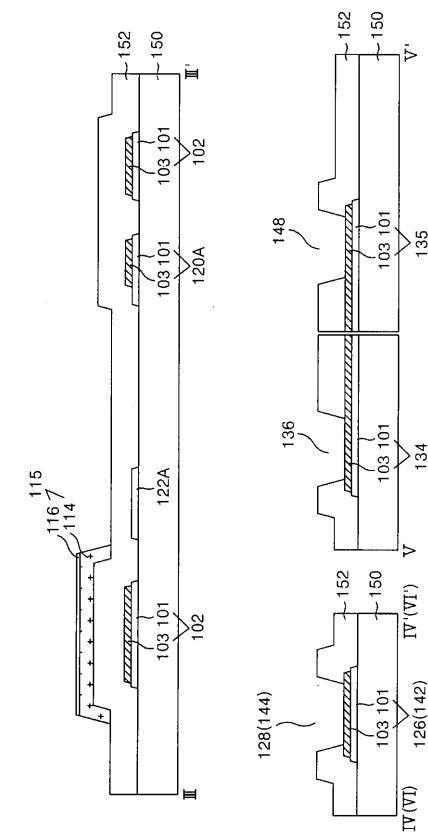

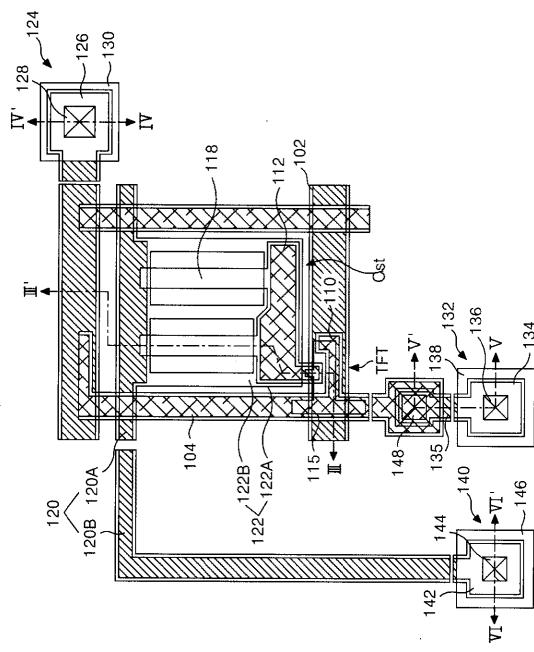

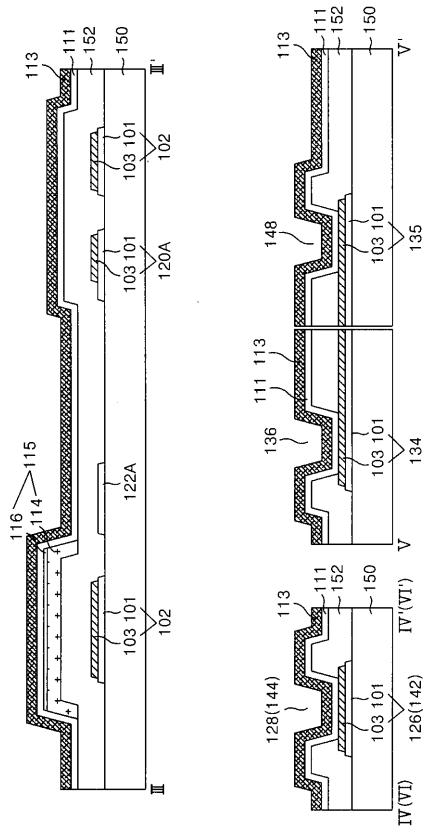

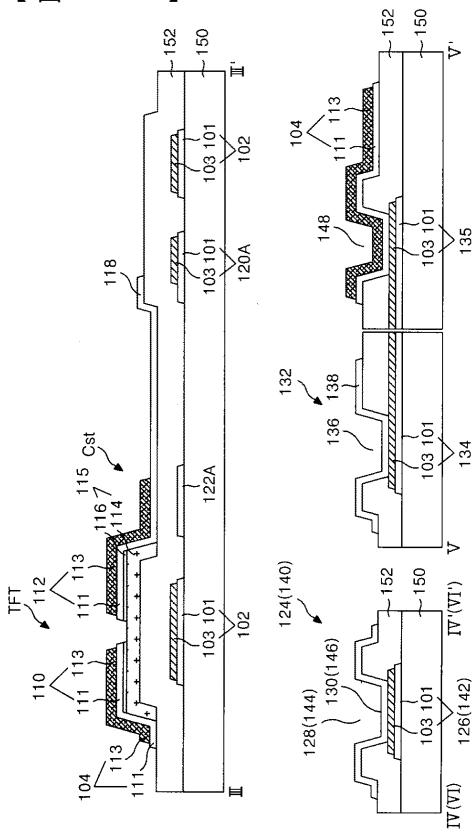

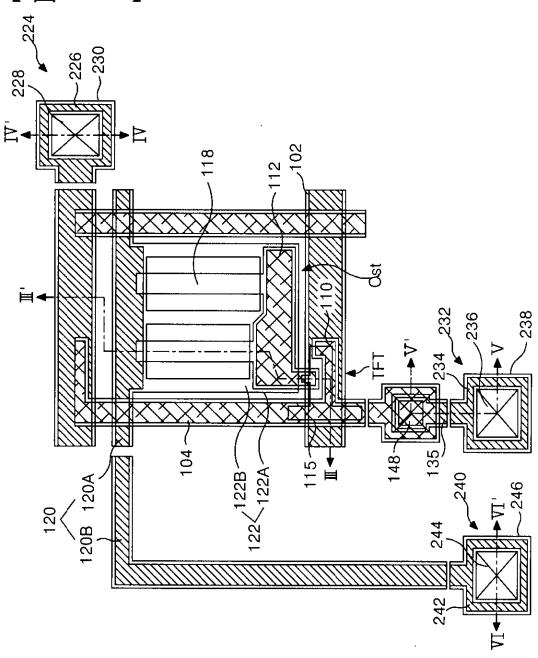

図2は、本発明の実施形態にある水平電界薄膜トランジスタを示す平面図であり、図3は、図2に図示した薄膜トランジスタ基板を線III-III'、線IV-IV'、線V-V'、線VI-VI'に沿って切断した断面図である。

## 【0025】

図2及び図3に図示した薄膜トランジスタ基板は、下部基板150上にゲート絶縁膜152を挟んで交差して画素領域を定義するゲートライン102及びデータライン104、そのゲートライン102及びデータライン104と画素電極118とに接続された薄膜トランジスタ(TFT)、画素領域に水平電界を形成するように形成された画素電極118及

び共通電極 122、共通電極 122 と接続された共通ライン 120、及び共通電極 122 とドレーン電極 112 の重畠部に形成されたストレージキャパシタ (Cst) を備える。そして、薄膜トランジスタ基板は、ゲートライン 102 と接続されたゲートパッド 124、データライン 104 と接続されたデータパッド 132、及び共通ライン 120 と接続された共通パッド 140 を更に備える。

【0026】

ゲートライン 102 はゲートドライバ (図示せず) からのスキャン信号を、データライン 104 はデータドライバ (図示せず) からのビデオ信号を供給する。このようなゲートライン 102 及びデータライン 104 は、ゲート絶縁膜 152 を挟んで交差して各画素領域を定義する。

10

【0027】

ゲートライン 102 は、基板 150 上に透明導電層を含んだ少なくとも二重層以上の複層構造で形成される。例えば、図 3 に示すように、透明導電層を利用した第 1 導電層 101 と、不透明な金属を利用した第 2 導電層 103 が積層された二重層構造で形成される。データライン 104 は、ゲート絶縁膜 152 上に透明導電層を含んだ少なくとも二重層以上の複層構造で形成される。例えば、図 3 に示すように、透明導電層を利用した第 3 導電層 111 と、不透明な金属を利用した第 4 導電層 113 とが積層された二重層構造で形成される。この場合、第 1 及び第 3 導電層 101、111 としては、ITO、TO、IZO、ITZO などが、第 2 及び第 4 導電層 103、113 としては、Cu、Mo、Al、Cu 合金、Mo 合金、Al 合金などが利用される。

20

【0028】

薄膜トランジスタ (TFT) は、ゲートライン 102 のスキャン信号に応答してデータライン 104 上のビデオ信号が画素電極 118 に充電されて維持されるようにする。このために、薄膜トランジスタ (TFT) は、ゲートライン 102 に含まれたゲート電極と、データライン 104 と接続されたソース電極 110 と、ソース電極 110 と対向し画素電極 118 と接続されたドレーン電極 112 と、ゲート絶縁膜 152 を挟んでゲートライン 102 と重畠されたソース電極 110 とドレーン電極 112 との間にチャネルを形成する活性層 114 と、ソース電極 110 及びドレーン電極 112 とのオーミック接触のためにチャネル部を除外した活性層 114 上に形成されたオーミックコンタクト層 116 とを備える。ここで、ソース電極 110 及びドレーン電極 112 は、前述のデータライン 104 と共に半導体パターン 115 が形成されたゲート絶縁膜 152 上に、第 3 及び第 4 導電層 111、113 が積層された二重構造で形成される。

30

【0029】

共通ライン 120 と共通電極 122 は、液晶駆動のための基準電圧、即ち、共通電圧を各画素に供給する。

【0030】

このために、共通ライン 120 は、表示領域でゲートライン 102 と並んで形成された内部共通ライン 120A と、非表示領域で内部共通ライン 120A と共に接続された外部共通ライン 120B とを備える。共通ライン 120 は、前述のゲートライン 102 と共に基板 150 上に第 1 及び第 2 導電層 101、103 が積層された二重層構造で形成される。

40

【0031】

共通電極 122 は、画素領域内に形成されて内部共通ライン 120A と接続される。具体的には、共通電極 122 は、ゲートライン 102 と隣接してドレーン電極 112 と重畠された水平部 122A と、水平部 122A から画素領域側に伸張されて内部共通ライン 120A と接続されたフィンガー部 122B とを備える。このような共通電極 122 は、共通ライン 120 の第 1 導電層 101、即ち、透明導電層で形成される。

【0032】

ストレージキャパシタ (Cst) は、共通電極 122 の第 1 水平部 122A がゲート絶縁膜 152 を挟んでドレーン電極 112 と重畠されて形成される。ここで、ドレーン電極 1

50

12は、薄膜トランジスタ(TFT)、即ち、ゲートライン102との重畠部から延びて共通電極122の第1水平部122Aと最大限広く重畠されるように形成される。これによって、共通電極122とドレーン電極112との広い重畠面積によりストレージキャパシタ(Cst)の容量が増加することによって、ストレージキャパシタ(Cst)は画素電極118に充電されたビデオ信号を次の信号が充電される時まで安定的に維持させることができる。

【0033】

画素電極118は、共通電極122のフィンガー部122Bと並んでフィンガー形状を有するようにドレーン電極112から伸張され、その端部は内部共通ライン120Aと重畠される。特に、画素電極118は、ドレーン電極112から延びた第3導電層111、即ち、透明導電層で形成される。このような画素電極118に薄膜トランジスタ(TFT)を通じてビデオ信号が供給されれば、画素電極118と共に電圧が供給された共通電極122のフィンガー部122Bとの間には水平電界が形成される。このような水平電界により薄膜トランジスタ基板とカラーフィルタ基板との間で水平方向に配列された液晶分子が誘電異方性により回転することになる。そして、液晶分子の回転程度によって画素領域を透過する光透過率が変わることになって、階調を具現することになる。

【0034】

ここで、透明導電層で形成された共通電極122及び画素電極118が水平電界を形成する場合、共通電極122のフィンガー部122Bと画素電極118の両側部(エッジ部から内側に約1μm程度)が開口率に寄与できるので開口率が向上する。

【0035】

また、共通電極122のフィンガー部122Bと画素電極118は、図4に示すように、ジグザグ形状で形成されることができる。この場合、共通電極122のフィンガー部122Bでデータライン104と隣接したエッジ部は、データライン104と並んで形成されたり、ジグザグ形状で形成されることができる。また、データライン104が隣接した共通電極122のフィンガー部122Bに沿ってジグザグ形状で形成される場合もある。

【0036】

ゲートライン102は、ゲートパッド124を通じてゲートドライバ(図示せず)と接続される。ゲートパッド124は、ゲートライン102から延びたゲートパッド下部電極126、ゲート絶縁膜152を貫通する第1コンタクトホール128を通じてゲートパッド下部電極126と接続されたゲートパッド上部電極130を備える。

【0037】

データライン104は、データパッド132を通じてデータドライバ(図示せず)と接続される。データパッド132は、データリンク135と接続されたデータパッド下部電極134、ゲート絶縁膜152を貫通する第2コンタクトホール136を通じてデータパッド下部電極134と接続されたデータパッド上部電極138を備える。

【0038】

共通ライン120は、共通パッド140を通じて共通電圧源(図示せず)からの基準電圧を供給受けることになる。共通パッド140は、外部共通ライン120Bから延びた共通パッド下部電極142、ゲート絶縁膜152を貫通する第3コンタクトホール144を通じて共通パッド下部電極142と接続された共通パッド上部電極146を備える。

【0039】

このような本発明の薄膜トランジスタ基板において、データパッド132は、ゲートパッド132及び共通パッド140が同一な構造で形成される。具体的には、ゲートパッド下部電極126、共通パッド下部電極142、データパッド下部電極134、及びデータリンク135は、前述したゲートライン102と共に基板150上に第1及び第2導電層101、103が積層された二重層構造で形成される。また、ゲートパッド上部電極130、共通パッド上部電極146、及びデータパッド上部電極138は、データライン104と共にゲート絶縁膜152上に形成され、第4導電層113が除去された第3導電層111、即ち、透明導電層で形成される。

10

20

20

30

40

50

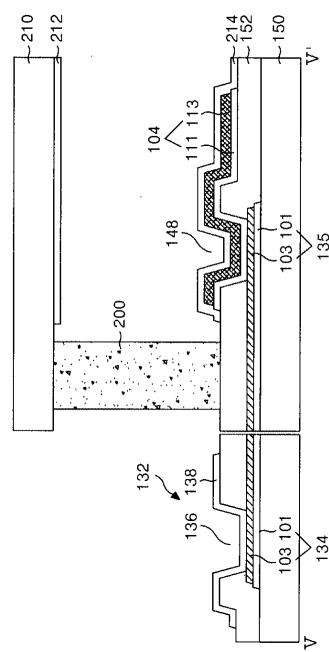

## 【0040】

これによって、基板150上に形成されたデータリンク135は、ゲート絶縁膜152を貫通する第4コンタクトホール148を通じてデータライン104と接続される。データリンク135は、データパッド下部電極134から伸張されるので、第1及び第2導電層101、103が積層された構造を有する。このようなデータリンク135の第2導電層103が、第4コンタクトホール148を通じて露出されてデータライン104の第3導電層111と接続される。この場合、データライン104の第3導電層111は、データパッド上部電極138と一体化した構造で形成されることがある。このようなデータライン104は、保護膜の不在により露出される。これによって、データライン104の第4導電層113が外部に露出して酸化されることを防止するために、図5に示すように、第4コンタクトホール148はシーリング材200により封入する領域に位置することになる。これによって、封入領域に位置するデータライン104の第4導電層113はその上に塗布される下部配向膜214により保護される。

## 【0041】

具体的に、下部配向膜214が塗布された薄膜トランジスタ基板と、上部配向膜212が塗布されたカラーフィルタ基板210は、図5に示すように、シーリング材200により合着され、シーリング材200により形成された2基板間のセルギャップに液晶が詰められることになる。この際、液晶は両基板を合着した後、液晶を注入する真空注入方式の他にも、少なくとも一つの基板に液晶を滴下した後、合着することによって、液晶層を形成する液晶滴下方式で形成されることがある。上下部配向膜212、214は、有機絶縁物質で両基板の画像表示領域に各々塗布される。シーリング材200は、接着力の強化のために、上下部配向膜212、214と接触させないように、離隔して塗布される。これによって、薄膜トランジスタ基板に形成されたデータライン104、ソース電極110、ドレーン電極112、画素電極118はシーリング材200により封入される領域に位置して、その上に塗布される下部配向膜214だけでなく、封入領域に詰められた液晶により十分保護される。

## 【0042】

このように、保護膜のない本発明の水平電界薄膜トランジスタ基板は次のように3つのマスク工程で形成される。

## 【0043】

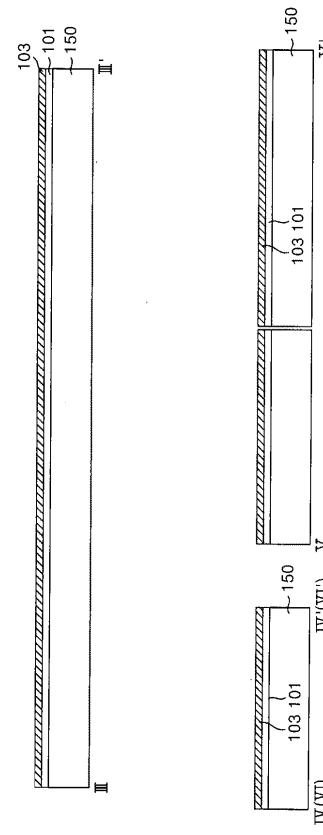

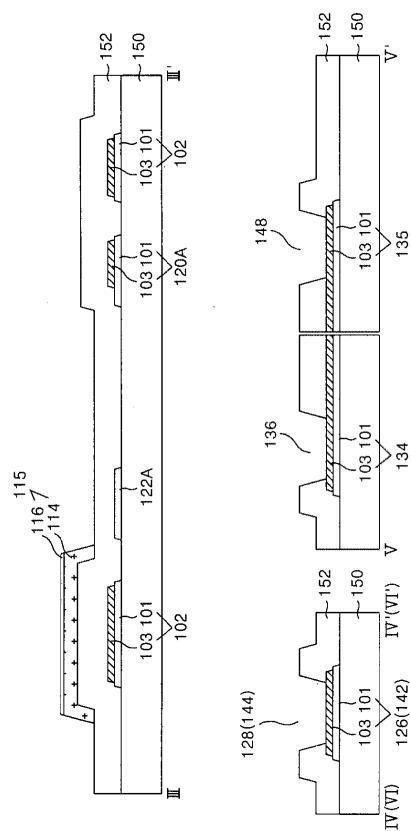

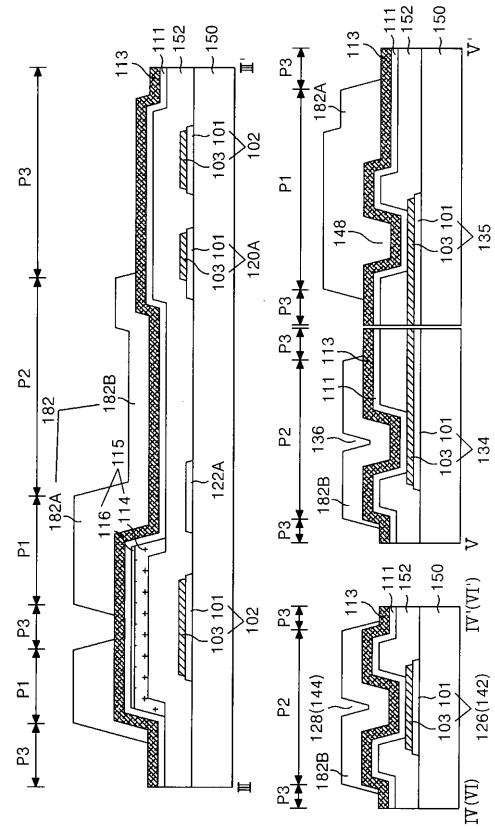

図6A及び図6Bは、本発明の実施形態における水平電界薄膜トランジスタ基板製造方法の中、第1マスク工程を説明するための平面図及び断面図を示す図であり、図7A乃至図7Eは、第1マスク工程を具体的に説明するための断面図を示す図である。

## 【0044】

第1マスク工程により下部基板150上にゲートライン102、ゲートパッド下部電極126、共通ライン120、共通電極122、共通パッド下部電極142、データリンク135及びデータパッド下部電極134を含む第1マスクパターン群が形成される。ここで、共通電極122を除外した第1マスクパターン群は少なくとも2個の導電層が積層された複層構造で形成されるが、説明の便宜上、以下では第1及び第2導電層101、103が積層された二重構造のみを説明する。共通電極122は、透明導電層である第1導電層101の単層構造で形成される。このように複層及び単層構造を有する第1マスクパターン群は、ハーフトーン(Half Tone)マスク、または、回折露光マスクを利用して、一つのマスク工程で形成される。以下では、第1マスクとしてハーフトーンマスクを利用した場合を例として説明する。

## 【0045】

図7Aを参照すれば、下部基板150上にスパッタリング方法などの蒸着方法を通じて第1及び第2導電層101、103が積層される。第1導電層101には、ITO、TO、IZO、ITZOなどの透明導電物質が、第2導電層103には、Mo、Ti、Cu、AlNd、Al、Cr、Mo合金、Cu合金、Al合金などの金属物質が単層に利用されたり、Al/Cr、Al/Mo、AlNd/Al、AlNd/Cr、Mo/AlNd/M

o、Cu/Mo、Ti/AlNd/Ti、Mo/Al、Mo/Ti/AlNd、Cu合金/Mo、Cu合金/Al、Cu合金/Mo合金、Cu合金/Al合金、Al/Mo合金、Mo合金/Al、Al合金/Mo合金、Mo合金/Al合金、Mo/Al合金などのように二重層以上が積層された構造で利用される。

【0046】

図7Bを参照すれば、ハーフトーンマスクを利用したフォトリソグラフィ工程により段差を有する第2フォトレジストパターン162が形成される。ハーフトーンマスクは、紫外線を遮断する遮断部、位相シフト物質を利用して紫外線を部分的に透過させるハーフトーン透過部、及び全て透過させる透過部を備える。このようなハーフトーンマスクを利用したフォトリソグラフィ工程により形成された互いに異なる厚さの第1A及び第1Bフォトレジストパターン162A、162Bと、開口部とを有する第1フォトレジストパターン162が形成される。相対的に厚い第1Aフォトレジストパターン162Aは、ハーフトーンマスクの遮断部と重畳された第1フォトレジストの遮断領域P1に、第1Aフォトレジストパターン162Aより薄い第1Bフォトレジストパターン162Bは、ハーフトーン透過部と重畳されたハーフトーン露光部P2に、開口部は、透過部と重畳されたフル露光領域P3に、それぞれ形成される。

【0047】

図7Cを参照すれば、第1フォトレジストパターン162をマスクとして利用したエッチング工程により、第1及び第2導電層101、103の露出部分がエッチングされる。これにより、二重構造のゲートライン102、ゲートパッド下部電極126、共通ライン120、共通電極122、共通パッド下部電極142、データリンク135、データパッド下部電極134を含む第1マスクパターン群が形成される。

【0048】

図7Dを参照すれば、酸素(02)プラズマを利用したアッシング工程により第1Aフォトレジストパターン162Aの厚さは薄くなり、第1Bフォトレジストパターン162Bは除去される。そして、アッシングされた第1Aフォトレジストパターン162Aをマスクとして利用したエッチング工程により共通電極122上の第2導電層103が除去される。この際、アッシングされた第1Aフォトレジストパターン162Aに沿って、パターニングされた第2導電層103の両側部がもう一度エッチングされることにより、第1マスクパターン群の第1及び第2導電層101、103は階段形態で一定の段差を有することになる。これによって、第1及び第2導電層101、103の側面部が高さのある急傾斜を有するため、その上で発生するゲート絶縁膜152のステップカバレージ不良を防止することができるようになる。

【0049】

図7Eを参照すれば、図7Dに示した工程において第1マスクパターン群の上に残存した第1Aフォトレジストパターン162Aがストリップ工程により除去される。

【0050】

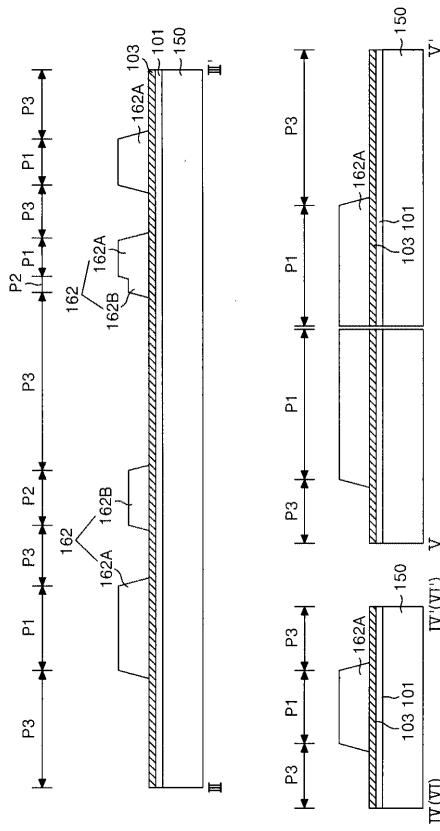

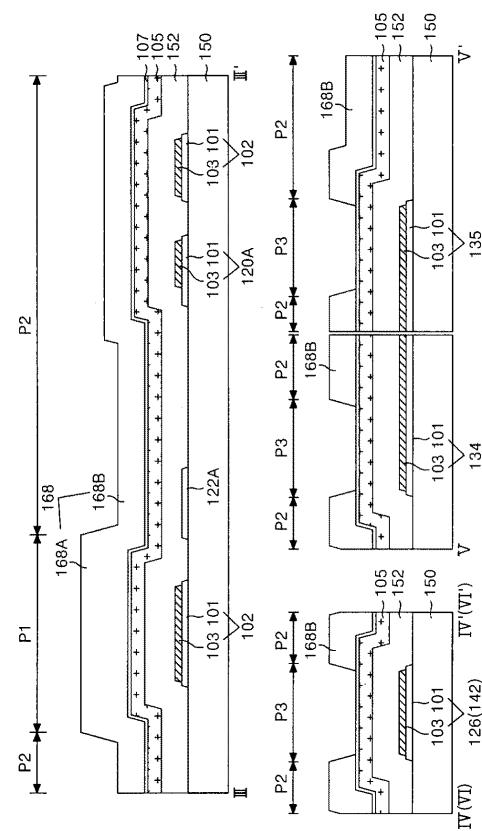

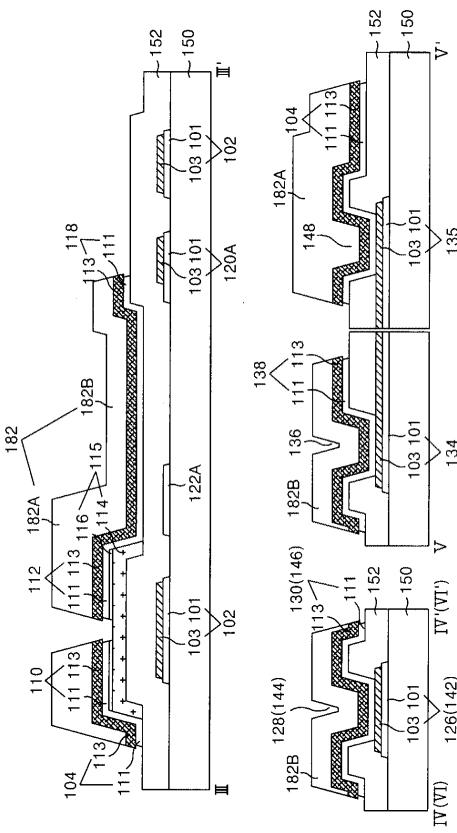

図8A及び図8Bは、本発明の実施形態における水平電界薄膜トランジスタ基板製造方法の中、第2マスク工程を説明するための平面図及び断面図を示す図であり、図9A乃至図9Fは、第2マスク工程を具体的に説明するための断面図を示す図である。

【0051】

第1マスクパターン群が形成された下部基板150上に第2マスク工程により第1乃至第4コンタクトホール128、136、144、148を含むゲート絶縁膜152と、半導体パターン115が形成される。このような半導体パターン115と、ゲート絶縁膜152のコンタクトホール128、136、144、148は回折露光マスクまたはハーフトーンマスクを利用した一つのマスク工程で形成される。以下では、第2マスクにハーフトーンマスクを利用した場合を説明する。

【0052】

図9Aを参照すれば、第1マスクパターン群が形成された下部基板150上にPECVDなどの蒸着方法によりゲート絶縁膜152、非晶質シリコン層105、不純物(n+また

10

20

30

40

50

はp+)がドーピングされた非晶質シリコン層107が順に形成される。ゲート絶縁膜152としては、SiO<sub>x</sub>、SiN<sub>x</sub>などのような無機絶縁物質が利用される。

【0053】

図9Bを参照すれば、ハーフトーンマスクを利用したフォトリソグラフィ工程により段差を有する第2フォトレジストパターン168が形成される。ハーフトーンマスクは、紫外線を遮断する遮断部、位相シフト物質を利用して紫外線を部分的に透過させるハーフトーン透過部、及び全て透過させる透過部を備える。このようなハーフトーンマスクを利用したフォトリソグラフィ工程により形成された互いに異なる厚さの第2A及び第2Bフォトレジストパターン168A、168Bと、開口部とを有する第2フォトレジストパターン168が形成される。相対的に厚い第2Aフォトレジストパターン168Aは、ハーフトーンマスクの遮断部と重畳された第2フォトレジストの遮断領域P1に、第2Aフォトレジストパターン168Aより薄い第2Bフォトレジストパターン168Bは、ハーフトーン透過部と重畳されたハーフトーン露光部P2に、開口部は、透過部と重畳されたフル露光領域P3に、それぞれ形成される。

【0054】

図9Cを参照すれば、第2フォトレジストパターン168をマスクとして利用したエッチング工程により不純物がドーピングされた非晶質シリコン層107からゲート絶縁膜152まで貫通する第1乃至第4コンタクトホール128、136、144、148が形成される。第1コンタクトホール128はゲートパッド下部電極126を、第2コンタクトホール136はデータパッド下部電極134を、第3コンタクトホール144は共通パッド下部電極142を、第4コンタクトホール148はデータリンク135を、それぞれ露出させる。

【0055】

図9Dを参照すれば、酸素(O<sub>2</sub>)プラズマを利用したアッシング工程により第2Aフォトレジストパターン168Aの厚さは薄くなり、第2Bフォトレジストパターン168Bは除去される。

【0056】

図9Eを参照すれば、アッシングされた第2Aフォトレジストパターン168Aをマスクとして利用したエッチング工程により、不純物がドーピングされた非晶質シリコン層107及び非晶質シリコン層105がパターニングされる。これにより、活性層114及びオーミック接触層116を有する半導体パターン115が形成される。

【0057】

図9Fを参照すれば、図9Eに示した工程で半導体パターン115上に残存した第2Aフォトレジストパターン168Aはストリップ工程により除去される。

【0058】

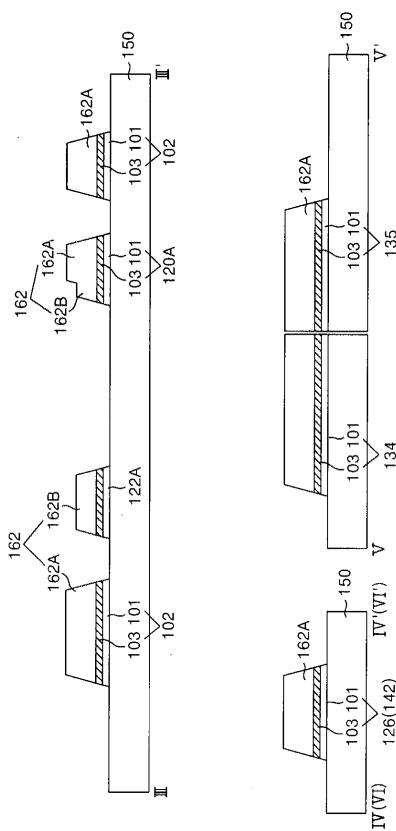

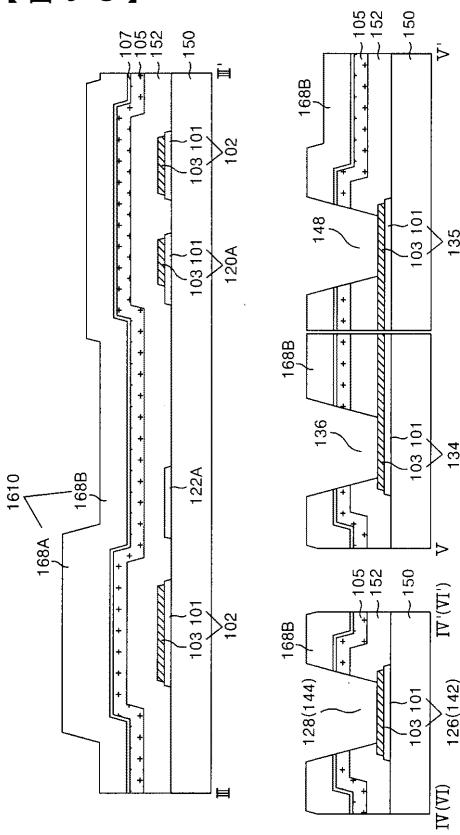

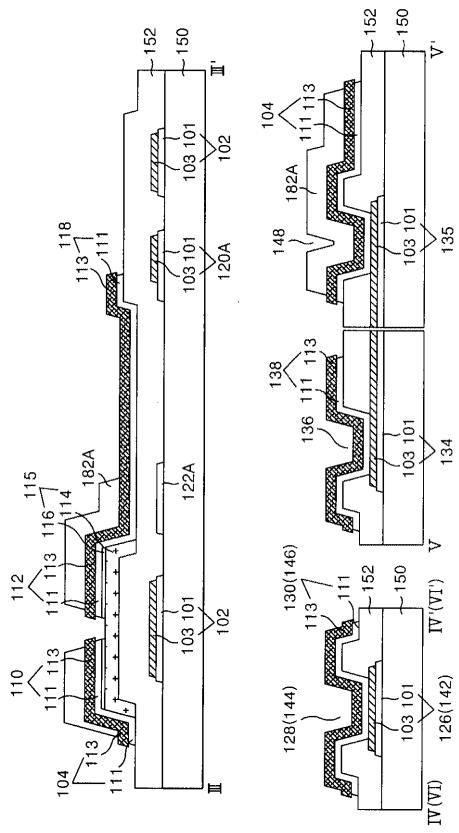

図10A及び図10Bは、本発明の実施形態における水平電界薄膜トランジスタ基板製造方法の中、第3マスク工程を説明するための平面図及び断面図であり、図12A乃至図12Eは、第3マスク工程を具体的に説明するための断面図である。

【0059】

第3マスク工程により半導体パターン115が形成されたゲート絶縁膜152上に、データライン104、ソース電極110、ドレーン電極112、画素電極118、ゲートパッド上部電極130、データパッド上部電極138、及び共通パッド上部電極146を含む第3マスクパターン群が形成される。このような第3マスクパターン群において、データライン104、ソース電極110、ドレーン電極112を含む第3Aマスクパターン群は少なくとも2個の導電層が積層された複層構造で形成されるが、説明の便宜上、以下では第3及び第4導電層111、113が積層された二重層構造のみを説明する。画素電極118、ゲートパッド上部電極130、データパッド上部電極138、及び共通パッド上部電極146を含む第3Bマスクパターン群は、第3Aマスクパターン群の第3導電層111からなる単層構造で形成される。このように、二重層構造の第3Aマスクパターン群と、単層構造の第3Bマスクパターン群を含む第3マスクパターン群は回折露光マスクま

10

20

30

40

50

たはハーフトーンマスクを利用した第3マスク工程で形成される。以下では、第3マスクとしてハーフトーンマスクを利用した場合を説明する。

#### 【0060】

具体的には、図11Aのように、半導体パターン115が形成されたゲート絶縁膜152上に、第3及び第4導電層111、113がスパッタリングなどの蒸着方法を通じて順に形成される。第3導電層111としては、ITO、TO、IZO、ITZOなどのような透明導電層、または、Ti、Wなどのように耐蝕性が強くて強度の高い不透明な金属が利用される。第4導電層113としては、Mo、Ti、Cu、AlNd、Al、Cr、Mo合金、Cu合金、Al合金などのように、金属物質が単層で利用されたり、Al/Cr、Al/Mo、AlNd/Al、AlNd/Cr、Mo/AlNd/Mo、Cu/Mo、Ti/AlNd/Ti、Mo/Al、Mo/Ti/AlNd、Cu合金/Mo、Cu合金/Al、Cu合金/Mo合金、Cu合金/Al合金、Al/Mo合金、Mo/Al合金などのように、二重層以上が積層された構造で利用される。

#### 【0061】

図11Bを参照すれば、ハーフトーンマスクを利用したフォトリソグラフィ工程により段差を有する第3フォトレジストパターン182が形成される。ハーフトーンマスクは、紫外線を遮断する遮断部、位相シフト物質を利用して紫外線を部分的に透過させるハーフトーン透過部、及び全て透過させる透過部を備える。このようなハーフトーンマスクを利用したフォトリソグラフィ工程により形成された互いに異なる厚さの第3A及び第3Bフォトレジストパターン182A、182Bと、開口部とを有する第3フォトレジストパターン182が形成される。相対的に厚い第3Aフォトレジストパターン182Aは、ハーフトーンマスクの遮断部と重畳された第3フォトレジストの遮断領域P1に、第3Aフォトレジストパターン182Aより薄い第3Bフォトレジストパターン182Bは、ハーフトーン透過部と重畳されたハーフトーン露光部P2に、開口部は、透過部と重畳されたフル露光領域P3に、それぞれ形成される。

#### 【0062】

図11Cを参照すれば、第3フォトレジストパターン182をマスクとして利用した湿式エッチング工程により第3及び第4導電層111、113がパターニングされることにより、二重層構造を有するデータライン104、ソース電極110、ドレーン電極112、画素電極118、ゲートパッド上部電極130、データパッド上部電極138、及び共通パッド上部電極146が形成される。データライン104は、データリンク135と重畳され、第4コンタクトホール148を通じてデータリンク135と接続される。この際、互いに異なるエッチャントを利用して第4導電層113がエッチングされた後、第3導電層111がエッチングされるので、上部の第4導電層113より下部の第3導電層111が過エッチングされてアンダー・カット(Under-cut)部分が発生することができる。また、ソース電極110及びドレーン電極112をマスクとして利用したエッチング工程、例えば、乾式エッチング工程により、その間のオーミック接触層116が除去されて活性層114が露出される。

#### 【0063】

図11Dを参照すれば、アッシング工程により第3Aフォトレジストパターン182Aの厚さは薄くなり、第3Bフォトレジストパターン182Bは除去される。このようなアッシング工程は、オーミック接触層116を分離する乾式エッチング工程と同一チャンバー内で遂行される。第3Bフォトレジストパターン182Bの除去により、画素電極118、ゲートパッド上部電極130、データパッド上部電極138、及び共通パッド上部電極146の第4導電層113が露出される。また、アッシングされた第3Aフォトレジストパターン182Aのエッジ部は、パターニングされた第4導電層113のエッジ部の内側に位置することになる。

#### 【0064】

図11Eを参照すれば、アッシングされた第3Aフォトレジストパターン182Aをマ

10

20

30

40

50

スクとして利用したエッティング工程により、画素電極 118、ゲートパッド上部電極 130、データパッド上部電極 138、及び共通パッド上部電極 146 の第 4 導電層 113 がエッティングされることにより、画素電極 118、ゲートパッド上部電極 130、データパッド上部電極 138、及び共通パッド上部電極 146 は、第 3 導電層 111 の単層構造で形成される。この際、第 3 A フォトレジストパターン 182A のエッジ部を通じて露出された第 4 導電層 113 の両側部がもう一度エッティングされる。これによって、データライン 104 と、ソース電極 110 と、ドレーン電極 112 との第 3 及び第 4 導電層 111、113 は、階段形態で一定の段差を有することになる。そして、第 3 A フォトレジストパターン 182A はストリップ工程により除去される。

## 【0065】

10 このような第 3 マスク工程において、第 3 及び第 4 導電層 111、113 のエッティング工程を、湿式エッティングまたは乾式エッティングへと進めることができる。但し、この場合には湿式エッティングが工程上有利である。

## 【0066】

この結果、本発明の実施形態における薄膜トランジスタ基板は、保護膜の不在によりデータライン 104、ソース電極 110、ドレーン電極 112、及び画素電極 118 が露出された構造を有することになるが、これらは全てシーリング材により封入される領域に位置するので、その上に塗布される下部配向膜だけでなく、封入領域に詰められた液晶によっても十分保護される。

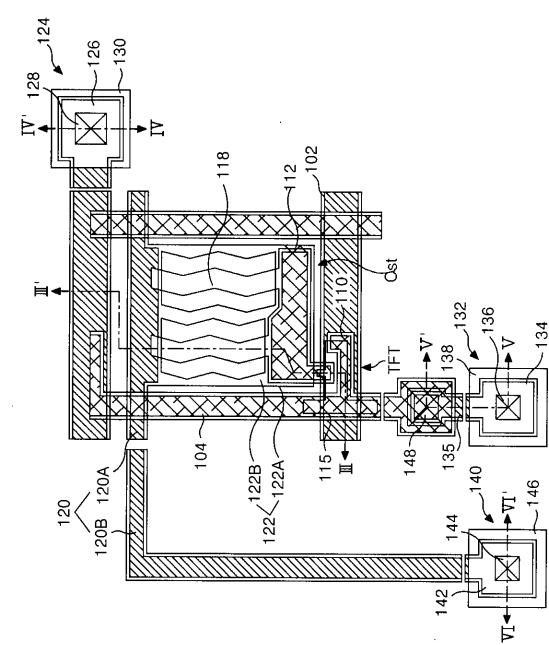

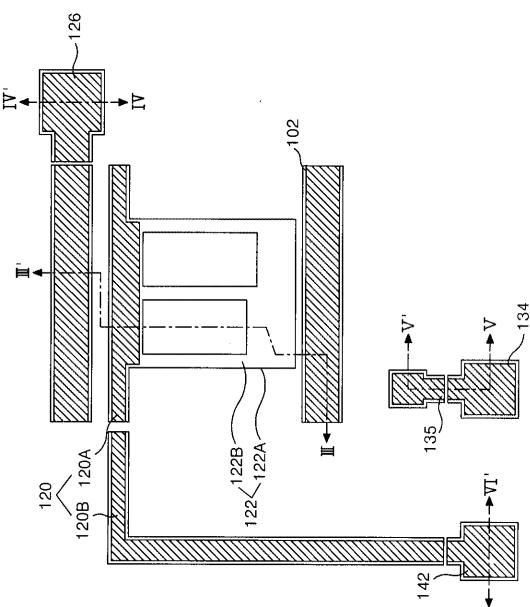

## 【0067】

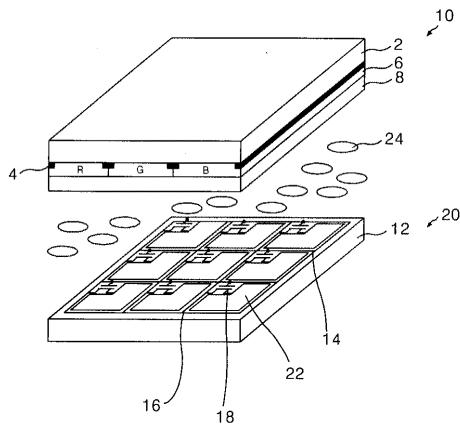

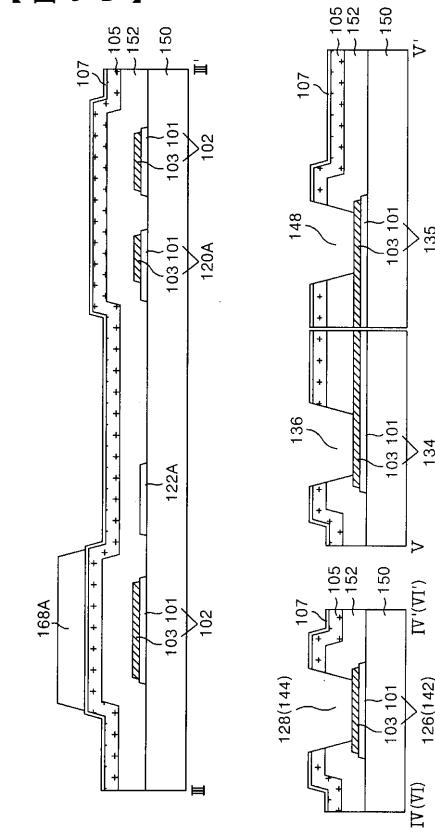

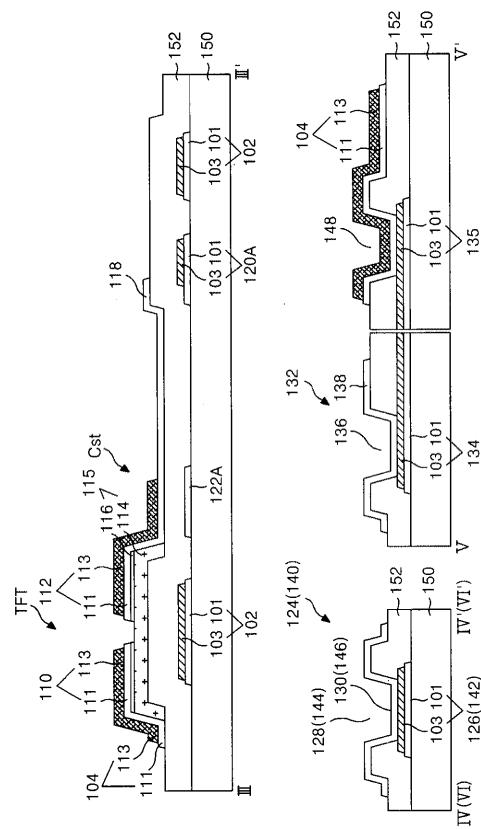

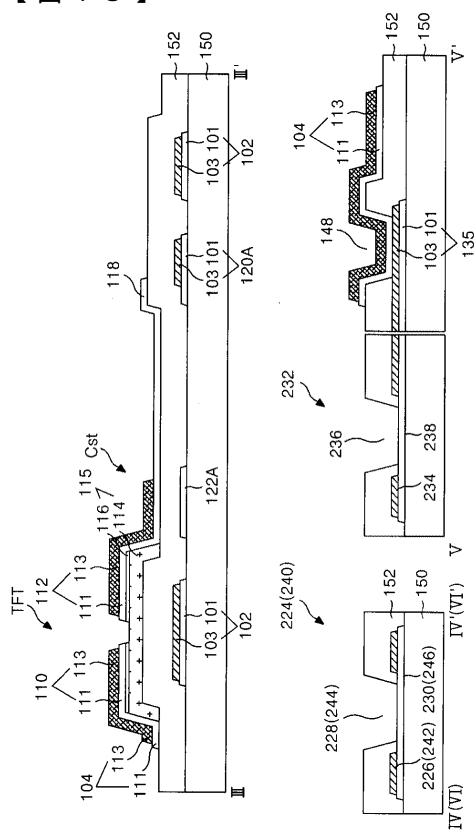

20 図 12 は、本発明の他の実施形態における水平電界薄膜トランジスタ基板の一部を示す平面図であり、図 13 は、図 12 に図示した薄膜トランジスタ基板を線 III-III'、線 IV-V'、線 V-V'、線 VI-VI' に沿って切断した断面図である。

## 【0068】

図 12 及び図 13 に図示した薄膜トランジスタ基板は、図 2 及び図 3 に図示した薄膜トランジスタ基板と対比して、ゲートパッド 224、データパッド 232、及び共通パッド 240 が第 1 マスク工程で形成されて第 1 マスクパターン群の構造を有することを除いては同一な構成要素を備えるので、重畠された構成要素についての説明は省略する。

## 【0069】

図 12 及び図 13において、ゲートパッド下部電極 230、データパッド下部電極 238、及び共通パッド下部電極 246 は、第 1 マスクパターン群の第 1 導電層 101 で形成される。このようなゲートパッド下部電極 230、データパッド下部電極 238、及び共通パッド下部電極 246 は、第 1 乃至第 3 コンタクトホール 228、236、244 の各々を通じて露出される。ゲートパッド上部電極 226、データパッド上部電極 234、及び共通パッド上部電極 242 は、第 1 マスクパターン群の第 2 導電層 103 に形成される。このようなパッド上部電極 226、234、242 は、パッド下部電極 230、238、246 上にコンタクトホール 228、236、244 と非重畠されるように残存してゲート絶縁膜 152 により保護される。例えば、パッド上部電極 226、234、242 は、パッド下部電極 230、238、246 の縁に沿って残存してゲート絶縁膜 152 により保護される。

## 【0070】

40 このように、パッド上部電極 226、234、242 を通じてパッド下部電極 230、238、246 が露出された構造は、図 6A 乃至図 7E で前述した第 1 マスク工程によりハーフトーン露光領域 P2 を適用して、第 1 導電層 101 が露出されるように第 2 導電層 103 のみをエッティングすることにより形成される。

## 【0071】

上述のように、本発明に係る水平電界薄膜トランジスタ基板を用いた液晶表示装置及びその製造方法は、第 1 ハーフトーン（または、回折露光）マスクを利用して単層構造の共通電極を複層構造の他の第 1 マスクパターン群と共に形成する。

## 【0072】

10

20

30

40

50

また、本発明に係る水平電界薄膜トランジスタ基板を用いた液晶表示装置及びその製造方法は、第2ハーフトーン（または、回折露光）マスクを利用して半導体パターン及びコンタクトホールを形成することになる。

#### 【0073】

また、本発明に係る水平電界薄膜トランジスタ基板を用いた液晶表示装置及びその製造方法は、第3ハーフトーン（または、回折露光）マスクを利用して保護膜なしに単層構造の画素電極及びパッド上部電極を複層構造の他の第3マスクパターン群と共に形成する。

#### 【0074】

これによって、本発明に係る水平電界薄膜トランジスタ基板を用いた液晶表示装置及びその製造方法は、3マスク工程により工程を単純化することによって、材料費用及び設備投資費用などを低減すると共に、歩留まりを向上させることができることになる。

#### 【0075】

そして、本発明に係る水平電界薄膜トランジスタが適用された液晶パネルは、薄膜トランジスタ基板で保護膜の不在により露出されたデータライン、ソース電極、ドレーン電極、及び画素電極を、その上に塗布される配向膜、または、シーリング材で封入される領域に詰められた液晶により十分保護されるようとする。また、薄膜トランジスタ基板のパッドが全て同一な構造を有するようにし、データパッドと接続されたデータリンクはシーリング材により封入される領域内でコンタクトホールを通じてデータラインと接続されるようとする。これによって、保護膜の不在による電食問題などを防止できることになる。

#### 【0076】

また、本発明に係る水平電界薄膜トランジスタ基板を用いた液晶表示装置及びその製造方法は、共通電極及び画素電極が透明導電層で形成されて開口率に寄与できるので開口率が向上する。

#### 【0077】

以上、説明した内容を通じて当業者であれば本発明の技術思想から外れない範囲で多様な変更及び修正が可能であることが分かる。したがって、本発明の技術的範囲は明細書の詳細な説明に記載された内容に限られるものではなく、特許請求範囲により定めるはずである。

#### 【図面の簡単な説明】

#### 【0078】

【図1】従来の液晶パネル構造を概略的に示す斜視図である。

【図2】本発明の実施形態の水平電界薄膜トランジスタ基板を示す平面図である。

【図3】図2に図示した薄膜トランジスタ基板を線III-III'、線IV-IV'、線V-V'、線VI-VI'に沿って切断した断面図である。

【図4】本発明の他の実施形態の水平電界薄膜トランジスタ基板を示す平面図である。

【図5】図3に図示した薄膜トランジスタ基板を利用した液晶パネルにおけるデータパッド領域を示す断面図である。

【図6A】本発明の実施形態の水平電界薄膜トランジスタ基板の製造方法における第1マスク工程を説明するための平面図である。

【図6B】本発明の実施形態の水平電界薄膜トランジスタ基板の製造方法における第1マスク工程を説明するための断面図である。

【図7A】本発明の第1マスク工程を具体的に説明するための断面図である。

【図7B】本発明の第1マスク工程を具体的に説明するための断面図である。

【図7C】本発明の第1マスク工程を具体的に説明するための断面図である。

【図7D】本発明の第1マスク工程を具体的に説明するための断面図である。

【図7E】本発明の第1マスク工程を具体的に説明するための断面図である。

【図8A】本発明の実施形態の水平電界薄膜トランジスタ基板の製造方法における第2マスク工程を説明するための平面図である。

【図8B】本発明の実施形態の水平電界薄膜トランジスタ基板の製造方法における第2マスク工程を説明するための断面図である。

10

20

30

40

50

【図 9 A】本発明の第 2 マスク工程を具体的に説明するための断面図である。

【図 9 B】本発明の第 2 マスク工程を具体的に説明するための断面図である。

【図 9 C】本発明の第 2 マスク工程を具体的に説明するための断面図である。

【図 9 D】本発明の第 2 マスク工程を具体的に説明するための断面図である。

【図 9 E】本発明の第 2 マスク工程を具体的に説明するための断面図である。

【図 9 F】本発明の第 2 マスク工程を具体的に説明するための断面図である。

【図 10 A】本発明の実施形態の水平電界薄膜トランジスタ基板の製造方法における第 3 マスク工程を説明するための平面図である。

【図 10 B】本発明の実施形態の水平電界薄膜トランジスタ基板の製造方法における第 3 マスク工程を説明するための断面図である。 10

【図 11 A】本発明の第 3 マスク工程を具体的に説明するための断面図である。

【図 11 B】本発明の第 3 マスク工程を具体的に説明するための断面図である。

【図 11 C】本発明の第 3 マスク工程を具体的に説明するための断面図である。

【図 11 D】本発明の第 3 マスク工程を具体的に説明するための断面図である。

【図 11 E】本発明の第 3 マスク工程を具体的に説明するための断面図である。

【図 12】本発明の他の実施形態の水平電界薄膜トランジスタ基板を示す平面図である。

【図 13】図 12 に図示した薄膜トランジスタ基板を線 III-III'、線 IV-IV'、線 V-V'、線 VI-VI' 線に沿って切断した断面図である。 20

#### 【符号の説明】

##### 【0079】

2 上部ガラス基板

4 ブラックマトリックス

6 カラーフィルタ

8 共通電極

10 カラーフィルタ基板

12 下部ガラス基板

14、102 ゲートライン

16、104 データライン

18、TFT 薄膜トランジスタ

20 薄膜トランジスタ基板

22、118 画素電極

24 液晶

110 ソース電極

112 ドレーン電極

128、136、144、148、236、244、248 コンタクトホール

120 共通ライン

122 共通電極

124、224 ゲートパッド

126、230 ゲートパッド下部電極

130、226 ゲートパッド上部電極

132、232 データパッド

134、238 データパッド下部電極

138、234 データパッド上部電極

140、240 共通パッド

142、246 共通パッド下部電極

146、242 共通パッド上部電極

150 基板

152 ゲート絶縁膜

114 活性層

116 オーミック接触層

20

30

40

50

- |               |                                |

|---------------|--------------------------------|

| 1 5 4         | 保 護 膜                          |

| 1 0 1         | 第 1 導 電 層                      |

| 1 0 3         | 第 2 導 電 層                      |

| 1 0 5         | 非 晶 質 シ リ コン 層                 |

| 1 0 7         | 不 純 物 ド ー ピ ン グ さ れ た シ リ コン 層 |

| 1 1 1         | 第 3 導 電 層                      |

| 1 1 3         | 第 4 導 電 層                      |

| 1 2 2 A       | 共 通 電 極 水 平 部                  |

| 1 2 2 B       | 共 通 電 極 フ イ ン ガ ー 部            |

| 1 3 5         | デ ー タ リ ン ク                    |

| 1 6 8 、 1 8 2 | フォ ト レ ジ ス ト パ タ ー ン           |

| 1 1 5         | 半 導 体 パ タ ー ン                  |

| P 1           | 遮 断 領 域                        |

| P 2           | ハ ー フ ト ー ン 露 光 領 域            |

| P 3           | フ ル 露 光 領 域                    |

10

【 図 1 】

(從來技術)

【 図 2 】

【 図 3 】

【図5】

【 図 4 】

【図6A】

【 図 6 B 】

【 図 7 A 】

【図7B】

【 図 7 C 】

【 図 7 D 】

【 図 7 E 】

【図 8 A】

【 図 8 B 】

【 図 9 A 】

【 図 9 B 】

【 図 9 C 】

【 図 9 D 】

【 図 9 E 】

【 図 9 F 】

【 図 1 0 A 】

【 図 1 0 B 】

【 図 1 1 A 】

【図11B】

【 1 1 C 】

【 図 1 1 D 】

【 図 1 1 E 】

【図12】

【 図 1 3 】

---

フロントページの続き

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100128657

弁理士 三山 勝巳

(72)発明者 安 炳 哲

大韓民国 京畿道 安養市 東安区 坪村洞 899-2番地 ヒヤンチョン アパートメント

203-903号

F ターム(参考) 2H092 GA14 GA34 GA40 JB14 JB24 JB33 JB66 JB69

|                |                                                                                                                                                                                                                                                              |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2006184903A</a>                                                                                                                                                                                                                                | 公开(公告)日 | 2006-07-13 |

| 申请号            | JP2005369463                                                                                                                                                                                                                                                 | 申请日     | 2005-12-22 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | Eruji. 菲利普斯杜天公司, 有限公司                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 安炳哲                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 安炳哲                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                        |         |            |

| CPC分类号         | G02F1/134363 G02F2001/136231 G02F2001/13629                                                                                                                                                                                                                  |         |            |

| FI分类号          | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 2H092/GA14 2H092/GA34 2H092/GA40 2H092/JB14 2H092/JB24 2H092/JB33 2H092/JB66 2H092/JB69 2H192/AA24 2H192/BB02 2H192/BB53 2H192/BB73 2H192/CB05 2H192/CC32 2H192/CC72 2H192/CC75 2H192/DA23 2H192/DA24 2H192/DA32 2H192/FA65 2H192/HA44 2H192/HA47 2H192/JA33 |         |            |

| 代理人(译)         | 白井伸一<br>朝日伸光                                                                                                                                                                                                                                                 |         |            |

| 优先权            | 1020040112578 2004-12-24 KR                                                                                                                                                                                                                                  |         |            |

| 其他公开文献         | JP4612539B2                                                                                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                    |         |            |

## 摘要(译)

本发明提供一种使用水平电场薄膜晶体管基板的液晶显示装置及其制造方法，可以简化工艺。在根据本发明的液晶显示装置中使用的薄膜晶体管基板具有由至少具有双导电层的第一导电层组形成的栅极线和公共线，以及具有至少该公共线的公共电极122。形成一个导电层以延伸，数据线104，源电极110和漏电极112由具有至少双导电层的第二导电层组形成，并且像素电极118是漏电极112中的至少一个。其特征在于形成两个导电层以使其延伸。[选择图]图2