(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-139288

(P2006-139288A)

(43) 公開日 平成18年6月1日(2006.6.1)

| (51) Int.C1.                           | F 1                                      | テーマコード (参考) |

|----------------------------------------|------------------------------------------|-------------|

| <b>G09G 3/36</b> (2006.01)             | G09G 3/36                                | 2 H 093     |

| <b>G02F 1/133</b> (2006.01)            | G02F 1/133                               | 5 C 006     |

| <b>G09G 3/20</b> (2006.01)             | G02F 1/133                               | 5 C 080     |

|                                        | GO9G 3/20                                | 6 4 2 A     |

|                                        | GO9G 3/20                                | 6 2 2 C     |

| 審査請求 未請求 請求項の数 62 O L (全 47 頁) 最終頁に続く  |                                          |             |

| (21) 出願番号 特願2005-329431 (P2005-329431) | (71) 出願人 390019839                       |             |

| (22) 出願日 平成17年11月14日 (2005.11.14)      | 三星電子株式会社                                 |             |

| (31) 優先権主張番号 10-2004-0092607           | Samsung Electronics                      |             |

| (32) 優先日 平成16年11月12日 (2004.11.12)      | C o., L t d.                             |             |

| (33) 優先権主張国 韓国 (KR)                    | 大韓民国京畿道水原市靈通区梅灘洞 416                     |             |

| (31) 優先権主張番号 10-2004-0098028           | 416, Maetan-dong, Yeongtong-gu, Suwon-si |             |

| (32) 優先日 平成16年11月26日 (2004.11.26)      | Gyeonggi-do, Republic                    |             |

| (33) 優先権主張国 韓国 (KR)                    | of Korea                                 |             |

| (31) 優先権主張番号 10-2005-0002543           | (74) 代理人 100094145                       |             |

| (32) 優先日 平成17年1月11日 (2005.1.11)        | 弁理士 小野 由己男                               |             |

| (33) 優先権主張国 韓国 (KR)                    | (74) 代理人 100106367                       |             |

| (31) 優先権主張番号 10-2005-0004526           | 弁理士 稲積 朋子                                |             |

| (32) 優先日 平成17年1月18日 (2005.1.18)        |                                          |             |

| (33) 優先権主張国 韓国 (KR)                    |                                          |             |

最終頁に続く

(54) 【発明の名称】表示装置及びその駆動方法

(57) 【要約】 (修正有)

【課題】上下に隣接した二つの画素の形態を正確に一致させ、画素の開口率を正確に一致させ、二つの画素の電気的、光学的特性が変わらない様にし、画素電極にV字状の切開部を設ける場合、横縞または縦縞が生じないようにした液晶表示装置を提供する。

【解決手段】行列状に配列され各々第1及び第2副画素を含む画素P X、第1副画素P X aに連結され第1ゲート信号を伝達する第1ゲート線G L a、第2副画素P X bに連結され第2ゲート信号を伝達する第2ゲート線G L b、及び第1及び第2ゲート線と交差して第1及び第2副画素に連結されデータ電圧を伝達するデータ線D Lを含む。各画素の第1及び第2副画素に印加されるデータ電圧の大きさは、互いに異なり、一つの画像情報から得られる。

【選択図】図4 a

**【特許請求の範囲】****【請求項 1】**

第1及び第2副画素を含む複数の画素、

前記第1副画素と連結されていて、第1信号を伝達する第1信号線、

前記第2副画素と連結されていて、第2信号を伝達する第2信号線、

前記第1及び第2信号線と交差し、前記第1及び第2副画素のうちの少なくとも一つに

連結されていて、第3信号を伝達する第3信号線、及び

前記第1及び第2信号線と交差し、第4信号を伝達する第4信号線

を含み、

前記第1及び第2副画素は互いに異なる大きさのデータ電圧の印加を受け、

前記第1副画素に印加されるデータ電圧と前記第2副画素に印加されるデータ電圧は一

つの画像情報から得られた、

表示装置。 10

**【請求項 2】**

前記第1副画素は、前記第1信号線と連結されている第1スイッチング素子、及びこれ

に連結されている第1液晶キャパシタを含み、

前記第2副画素は、前記第2信号線と連結されている第2スイッチング素子、及びこれ

に連結されている第2液晶キャパシタを含む、請求項1に記載の表示装置。 20

**【請求項 3】**

前記第1液晶キャパシタは、前記第1スイッチング素子と連結されている第1副画素電

極を含み、

前記第2液晶キャパシタは、前記第2スイッチング素子と連結されている第2副画素電

極を含む、請求項2に記載の表示装置。 20

**【請求項 4】**

前記第1及び第2副画素電極は、前記第1乃至第4信号線と斜角をなす間隙をあいてい

る、請求項3に記載の表示装置。 30

**【請求項 5】**

前記第1及び第2副画素電極のうちの少なくとも一つは、前記第1乃至第4信号線と斜

角をなす切開部を有する、請求項3に記載の表示装置。 30

**【請求項 6】**

前記第1及び第2副画素電極は、前記第1及び第2副画素電極と対向する共通電極を共

通にさらに含み、

前記共通電極は、前記第1乃至第4信号線と斜角をなす切開部を有する、請求項3に記

載の表示装置。 40

**【請求項 7】**

前記第1スイッチング素子は前記第1及び第3信号線と連結されており、前記第2スイ

ッチング素子は前記第2及び第3信号線と連結されている、請求項2に記載の表示装置。 40

**【請求項 8】**

前記第1スイッチング素子は、前記第1信号線からの信号によって導通して前記第3信

号線からの信号を伝達し、 40

前記第2スイッチング素子は、前記第2信号線からの信号によって導通して前記第3信

号線からの信号を伝達する、請求項7に記載の表示装置。

**【請求項 9】**

前記第1スイッチング素子は、前記第3信号線からの信号によって導通して前記第1信

号線からの信号を伝達し、

前記第2スイッチング素子は、前記第3信号線からの信号によって導通して前記第2信

号線からの信号を伝達する、請求項7に記載の表示装置。

**【請求項 10】**

前記第1副画素は前記第1及び第3信号線と連結されており、前記第2副画素は前記第

2及び第4信号線と連結されている、請求項2に記載の表示装置。 50

**【請求項 1 1】**

前記第1副画素は、前記第1スイッチング素子と連結されている第1ストレージキャバシタをさらに含み、

前記第2副画素は、前記第2スイッチング素子と連結されている第2ストレージキャバシタをさらに含む、請求項2に記載の表示装置。

**【請求項 1 2】**

互いに異なる第1及び第2階調電圧集合を生成し、前記画像情報に該当する階調電圧を前記第1及び前記第2階調電圧集合から各々選択して前記第1及び第2副画素に各々印加する、請求項1に記載の表示装置。

**【請求項 1 3】**

前記画像情報を処理して第1画像信号と第2画像信号を生成し、前記第1画像信号と第2画像信号に対応するそれぞれのデータ電圧を一つの階調電圧集合から選択して前記第1及び第2副画素に各々印加する、請求項1に記載の表示装置。

**【請求項 1 4】**

前記各画素の第1副画素と第2副画素は容量性結合されている、請求項1に記載の表示装置。

**【請求項 1 5】**

第1及び第2副画素を含む画素、

前記第1及び第2副画素に連結されていて、ゲート信号を伝達するゲート線、

前記ゲート線と交差して前記第1副画素に連結されていて、第1データ電圧を伝達する第1データ線、及び

前記ゲート線と交差して前記第2副画素に連結されていて、第2データ電圧を伝達する第2データ線、

を含む、表示装置。

**【請求項 1 6】**

前記第1データ電圧は、前記第2データ電圧と異なり、一つの画像情報から得られた、請求項15に記載の液晶表示装置。

**【請求項 1 7】**

前記第1データ電圧の極性は、前記第2データ電圧の極性と反対である、請求項16に記載の液晶表示装置。

**【請求項 1 8】**

前記第1データ電圧の極性は、所定時間一定であることを特徴とする請求項17に記載の液晶表示装置。

**【請求項 1 9】**

行列状に配列されていて、各々第1及び第2副画素を含む複数の画素、

前記第1副画素に連結されていて、第1ゲートオン電圧を伝達する複数の第1ゲート線、

前記第2副画素に連結されていて、第2ゲートオン電圧を伝達する複数の第2ゲート線、

前記第1及び第2ゲート線と交差して前記第1及び第2副画素に連結されていて、データ電圧を伝達する複数のデータ線、

第1及び第2階調信号集合を生成する階調信号生成回路、

前記第1及び第2階調信号集合を交互に選択して出力する選択回路、

前記選択回路からの階調信号集合に基づいて画像データに対応する前記データ電圧を生成して前記データ線に印加するデータ駆動部、及び

前記第1及び第2ゲート線に順次に前記第1及び第2ゲートオン電圧を印加するゲート駆動部、

を含む、表示装置。

**【請求項 2 0】**

前記階調信号はアナログ階調電圧を含む、請求項19に記載の表示装置。

10

20

30

40

50

**【請求項 2 1】**

前記選択回路はアナログスイッチを含む、請求項 2 0 に記載の表示装置。

**【請求項 2 2】**

前記選択回路はアナログマルチプレクサーを含む、請求項 2 0 に記載の表示装置。

**【請求項 2 3】**

前記選択回路は前記データ駆動部と統合されている、請求項 2 0 に記載の表示装置。

**【請求項 2 4】**

前記階調信号生成回路は各々複数の抵抗列を有する複数のアナログ電圧生成回路を含む、請求項 2 0 に記載の表示装置。

**【請求項 2 5】**

前記階調信号はデジタル階調データを含む、請求項 1 9 に記載の表示装置。

**【請求項 2 6】**

前記選択回路が選択したデジタル階調データ集合の各階調データをアナログ変換して、複数の階調電圧を生成するデジタル - アナログ変換器をさらに含む、請求項 2 5 に記載の表示装置。

**【請求項 2 7】**

前記選択回路は前記階調信号生成回路に連結されている複数のマルチプレクサーを含む、請求項 2 6 に記載の表示装置。

**【請求項 2 8】**

前記第 1 ゲートオン電圧の印加時間と前記第 2 ゲートオン電圧の印加時間とは少なくとも一部重畠する、請求項 1 9 に記載の表示装置。

**【請求項 2 9】**

前記第 1 ゲートオン電圧の印加時間と前記第 2 ゲートオン電圧の印加時間とは同一である、請求項 2 8 に記載の表示装置。

**【請求項 3 0】**

前記第 1 ゲートオン電圧の印加時間は前記第 2 ゲートオン電圧の印加時間よりも短い、請求項 2 8 に記載の表示装置。

**【請求項 3 1】**

行列状に配列されていて、各々第 1 及び第 2 副画素を含む複数の画素、

前記第 1 副画素に連結されていて、第 1 ゲートオン電圧を伝達する複数の第 1 ゲート線

、前記第 2 副画素に連結されていて、第 2 ゲートオン電圧を伝達する複数の第 2 ゲート線

、前記第 1 及び第 2 ゲート線と交差して前記第 1 及び第 2 副画素に連結されていて、データ電圧を伝達する複数のデータ線、

周期的に値が変化する複数の基準電圧を生成する基準電圧生成回路、

前記基準電圧に基づいて複数の階調電圧を生成する階調電圧生成回路、

前記階調電圧生成回路からの階調電圧集合より画像データに対応する階調電圧を選択して、前記データ電圧として前記データ線に印加するデータ駆動部、及び

前記第 1 及び第 2 ゲート線に順次に前記第 1 及び第 2 ゲート信号を印加するゲート駆動部、

を含む、表示装置。

**【請求項 3 2】**

互いに並んで延在して分離されている第 1 及び第 2 ゲート線、

前記第 1 及び第 2 ゲート線と交差するデータ線、

前記第 1 ゲート線と前記データ線に連結されている第 1 薄膜トランジスタ、

前記第 2 ゲート線と前記データ線に連結されている第 2 薄膜トランジスタ、及び

前記第 1 及び第 2 薄膜トランジスタに各々連結されていて、互いに対向する傾いた斜辺を有する第 1 及び第 2 表示電極、

を含む、液晶表示装置。

10

20

30

40

50

## 【請求項 3 3】

第1方向に延在して分離されている第1及び第2ゲート線、

第2方向に延在しているデータ線、

前記第1ゲート線と前記データ線に連結されている第1薄膜トランジスタ、

前記第2ゲート線と前記データ線に連結されている第2薄膜トランジスタ、及び

前記第1及び第2薄膜トランジスタに各々連結されていて、第1及び第2表示電極、

を含み、

前記第2表示電極の前記第2方向の長さが前記第1表示電極よりも長く、前記第1表示

電極は前記第2表示電極の第2方向の長さ内に位置する、液晶表示装置。

## 【請求項 3 4】

第1方向に延在して分離されている第1及び第2ゲート線、

第2方向に延在しているデータ線、

前記第1ゲート線と前記データ線に連結されている第1薄膜トランジスタ、

前記第2ゲート線と前記データ線に連結されている第2薄膜トランジスタ、及び

前記第1及び第2薄膜トランジスタに各々連結されていて、第1及び第2表示電極

を含み、

前記第1及び第2表示電極は各々前記第1方向に延在した一つの直線を中心に実質的に

対称の形状を有している、液晶表示装置。

## 【請求項 3 5】

前記第1及び第2電極と対向する第3表示電極をさらに含む、請求項32乃至34のうち

のいずれか一項に記載の液晶表示装置。 20

## 【請求項 3 6】

前記第1または第2表示電極のうちの少なくとも一つは切開部を有している、請求項35に記載の液晶表示装置。

## 【請求項 3 7】

前記第3表示電極は切開部または突起を有している、請求項36に記載の液晶表示装置。

## 【請求項 3 8】

前記第1または第2表示電極のうちの少なくとも一つと前記第3表示電極とは、交互に

配列されている切開部を有する、請求項35に記載の液晶表示装置。 30

## 【請求項 3 9】

前記第1表示電極と前記第2表示電極の間の間隙と前記第3表示電極の切開部とは、交

互に配列されている、請求項38に記載の液晶表示装置。

## 【請求項 4 0】

前記第1及び第2表示電極と重畳する維持電極線をさらに含む、請求項32乃至34のうち

のいずれか一項に記載の液晶表示装置。

## 【請求項 4 1】

前記第1及び第2薄膜トランジスタは、各々前記第1または第2ゲート線と連結されて

いるゲート電極、前記データ線と連結されているソース電極及び前記第1または第2表示

電極と連結されているドレイン電極を含み、

前記維持電極線は前記ドレイン電極と重畳する、請求項40に記載の液晶表示装置。 40

## 【請求項 4 2】

前記第1表示電極の電圧は前記第2表示電極の電圧と異なる、請求項32乃至34のうち

のいずれか一項に記載の液晶表示装置。

## 【請求項 4 3】

前記第1表示電極の電圧と所定電圧との差は、前記第2表示電極の電圧と前記所定電圧

との差よりも小さい、請求項42に記載の液晶表示装置。

## 【請求項 4 4】

前記データ線と重畳し、前記第1及び第2表示電極と同一層に位置する遮蔽電極をさら

に含む、請求項32乃至34のうちのいずれか一項に記載の液晶表示装置。 50

## 【請求項 4 5】

絶縁基板上に形成されているゲート線、

前記ゲート線と絶縁されて交差している第1及び第2データ線、

前記ゲート線と前記第1データ線に連結されていて、第1ドレイン電極を含む第1薄膜トランジスタ、

前記ゲート線と前記第2データ線に連結されていて、第2ドレイン電極を含む第2薄膜トランジスタ、

前記ゲート線、前記第1及び第2データ線及び前記第1及び第2薄膜トランジスタを覆っており、前記第1データ線の一部を露出する第1接触孔と、前記第2データ線の一部を露出する第2接触孔を有する保護膜、及び

前記第1接触孔を通じて前記第1ドレイン電極と連結されている第1副画素電極と、前記第2接触孔を通じて前記第2ドレイン電極と連結されている第2副画素電極とを含む画素電極、

を含む薄膜トランジスタ表示板。

## 【請求項 4 6】

前記第1及び第2副画素電極と絶縁されていて、前記ゲート線または前記第1及び第2データ線と少なくとも一部重畳している遮蔽電極をさらに含む、請求項45に記載の薄膜トランジスタ表示板。

## 【請求項 4 7】

前記画素電極と前記遮蔽電極は前記保護膜上部に位置する、請求項46に記載の薄膜トランジスタ表示板。

## 【請求項 4 8】

前記第1及び第2ドレイン電極と重畳して保持容量を形成する維持電極を有する維持電極線をさらに含む、請求項46に記載の薄膜トランジスタ表示板。

## 【請求項 4 9】

前記遮蔽電極と前記維持電極は実質的に同一の電圧の印加を受ける、請求項48に記載の薄膜トランジスタ表示板。

## 【請求項 5 0】

前記遮蔽電極は前記第1及び第2データ線を完全に覆う、請求項49に記載の薄膜トランジスタ表示板。

## 【請求項 5 1】

前記第1副画素電極の面積は前記第2副画素電極の面積と異なる、請求項45に記載の薄膜トランジスタ表示板。

## 【請求項 5 2】

画像データの入力を受ける段階、

前記入力画像データを二つ以上のデータ電圧に変換する段階、及び

前記変換されたデータ電圧を当該副画素に印加する段階、

を含む、液晶表示装置の駆動方法。

## 【請求項 5 3】

前記変換段階は、

二つ以上の階調電圧集合を生成する段階、及び

前記二つ以上の階調電圧集合のそれぞれから前記入力画像データに対応する階調電圧を選択してデータ電圧にする段階、

を含む、請求項52に記載の液晶表示装置の駆動方法。

## 【請求項 5 4】

前記変換段階は、

前記入力画像データを二つ以上の出力画像データに変換する段階、及び

一つの階調電圧集合から前記二つ以上の出力画像データに対応する階調電圧を選択してデータ電圧にする段階、

を含む、請求項52に記載の液晶表示装置の駆動方法。

10

20

30

40

50

**【請求項 5 5】**

行列状に配列されていて、第1及び第2副画素を各々含む複数の画素を含む液晶表示装置の駆動方法であって、

前記第1副画素に第1極性の第1データ電圧を印加する段階、及び

前記第2副画素に前記第1極性と反対である第2極性の第2データ電圧を印加する段階

、

を含む、液晶表示装置の駆動方法。

**【請求項 5 6】**

前記第1データ電圧と前記第2データ電圧は一つの画像データから生成された、請求項5 5に記載の液晶表示装置の駆動方法。

10

**【請求項 5 7】**

行方向に隣接した画素の対応副画素に印加されるデータ電圧は極性が反対である、請求項5 6に記載の液晶表示装置の駆動方法。

**【請求項 5 8】**

列方向に隣接した画素の対応副画素に印加されるデータ電圧は極性が同一である、請求項5 7に記載の液晶表示装置の駆動方法。

**【請求項 5 9】**

前記各データ電圧は二つ以上の副画素に同時に印加される、請求項5 8に記載の液晶表示装置の駆動方法。

**【請求項 6 0】**

第1及び第2副画素を各々含む複数の画素を含む液晶表示装置の駆動方法であって、

画像データを伝送する段階、

第1階調電圧集合を出力する段階、

前記画像データを前記第1階調電圧集合の階調電圧の中から選択された第1データ電圧に変換する段階、

前記第1データ電圧を前記第1副画素に印加する段階、

マルチプレクサーを利用して前記第1階調電圧集合を前記第1階調電圧集合と値の異なる第2階調電圧集合に代替して出力する段階、

前記画像データを前記第2階調電圧集合の階調電圧の中から選択された第2データ電圧に変換する段階、及び

30

前記第2データ電圧を前記第2副画素に印加する段階、

を含む、液晶表示装置の駆動方法。

**【請求項 6 1】**

前記駆動方法は前記第1及び第2階調電圧集合を生成する段階をさらに含み、

前記第1階調電圧集合の出力段階は、前記マルチプレクサーを利用して前記第1及び第2階調電圧集合の中から前記第1階調電圧集合を選択する段階を含み、

前記第2階調電圧集合の出力段階は、前記マルチプレクサーを利用して前記第1及び第2階調電圧集合の中から前記第2階調電圧集合を選択する段階を含む、請求項6 0に記載の液晶表示装置の駆動方法。

**【請求項 6 2】**

前記駆動方法は第1及び第2デジタル階調データ集合を記憶する段階をさらに含み、

前記第1階調電圧集合の出力段階は、

前記マルチプレクサーを利用して前記第1及び第2デジタル階調データ集合の中から前記第1デジタル階調データ集合を選択する段階、及び

前記第1デジタル階調データ集合をアナログ変換して前記第1階調電圧集合を生成する段階、

40

を含み、

前記第2階調電圧集合の出力段階は、

前記マルチプレクサーを利用して前記第1及び第2デジタル階調データ集合の中から前記第2デジタル階調データ集合を選択する段階、及び

50

前記第2デジタル階調データ集合をアナログ変換して前記第2階調電圧集合を生成する段階、

を含む、請求項60に記載の液晶表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置及びその駆動方法に関する。

【背景技術】

【0002】

一般的な液晶表示装置（LCD）は、画素電極及び共通電極が具備された二つの表示板と、その間にあってる誘電率異方性を有する液晶層とを含む。画素電極は、行列状に配列されており、薄膜トランジスタ（TFT）などのスイッチング素子に連結されて一行ずつ、順次、データ電圧の印加を受ける。共通電極は、表示板の全面に亘って形成されており、共通電圧の印加を受ける。画素電極と共通電極及びその間の液晶層は、回路的に見れば液晶キャパシタを成し、液晶キャパシタは、これに連結されたスイッチング素子と共に画素を構成する基本単位となる。

【0003】

このような液晶表示装置では、二つの電極に電圧を印加して液晶層に電界を生成し、この電界の強さを調節して液晶層を通過する光の透過率を調節することによって所望の画像を得る。

その中でも、電界が印加されていない状態で液晶分子の長軸を上下表示板に対して垂直をなすように配列した垂直配向モード液晶表示装置は、コントラスト比が大きく広い基準視野角実現が容易であるため、脚光を浴びている。ここで、基準視野角とは、コントラスト比が1:10である視野角または階調間輝度反転限界角度を意味する。

【0004】

垂直配向方式液晶表示装置において、広視野角を実現するための手段としては、電界生成電極に切開部を形成する方法と、電界生成電極上に突起を形成する方法などがある。切開部と突起によって液晶分子が傾く方向を決定することができるので、これらを用いて液晶分子の傾斜方向をいろいろな方向に分散させることによって基準視野角を広くすることができる。

【0005】

しかし、垂直配向方式の液晶表示装置は前面視認性に比べて側面視認性が劣る問題点がある。例えば、切開部が具備されたPVA方式液晶表示装置の場合には、側面に行くほど画像が明るくなつて、激しい場合には高い階調の間の輝度差がなくなり画像が歪んで見える場合も発生する。

このような問題点を改善するために、一つの画素を二つの副画素に分割し、二つの副画素を容量性結合させた後、一方の副画素には直接電圧を印加し、他方の副画素には容量性結合による電圧下降を起こして、二つの副画素の電圧を異にすることによって透過率を異にする方法が提示されている。

【0006】

しかし、このような方法は、二つの副画素の透過率を所望の水準に正確に合わせることができないという問題点がなく、特に色相によって光透過率が異なるので、各色相に対する電圧配合を異にしなければならないにもかかわらず、これを行うことができない。また、容量性結合のための導電体の追加などによる開口率の低下が現れ、容量性結合による電圧降下によって透過率が減少する問題がある。

【0007】

一方、この時、液晶層に一方向の電界が長く印加されることによって発生する劣化現象などを防止するために、フレーム毎に、所定数の行または列毎に、または画素毎に共通電圧に対するデータ電圧の極性を反転させる。このようなデータ電圧の反転方式の中で、所定列毎にデータ電圧の極性を反転させる列反転（column inversion）の

10

20

30

40

50

場合、一つのデータ線を流れるデータ電圧の極性が1フレーム内では一定に維持されるので、データ線の信号遅延問題が大幅減るだけでなく、消費電力が小さいという長所がある。

#### 【0008】

しかし、列反転は垂直フリッカー現象や垂直クロストルク現象などによって液晶表示装置の画質が良好でないことがある。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

これを改善するために、データ線を流れるデータ電圧の極性反転形態は列反転を維持し、各画素列の画素を左右のデータ線に交互に連結して、実質的にドット反転 (dot inversion) の形態を有するようにする方法がある。

しかし、このように画素を設計する場合、下上に隣接した二つの画素の形態を正確に一致させ難いため、次のような問題が発生することがある。第一に、二つの画素の開口率を正確に一致させ難く、開口率が一致しない場合には使用者の目に立ちやすい。第二に、開口率を同一に設計しても整列偏差によって二つの画素の電気的、光学的特性が変わることがある。第三に、画素電極にV字状 (chevron) の切開部を設ける場合、開口率などを同一にするためには二つの画素の切開部方向を反対にしなければならず、このようなパターンの不一致によって横縞または縦縞が生じることがある。最後に、液晶表示装置を検査する時、上下二つの画素を一つの単位として検査を行わなければならないので面倒である。

#### 【0010】

本発明が目的とする技術的課題はこのような問題点を解決することである。

#### 【課題を解決するための手段】

#### 【0011】

本発明の一つの特徴による表示装置は、行列状に配列されていて、各々第1及び第2副画素を含む複数の画素、前記第1副画素と連結されていて、第1信号を伝達する第1信号線、前記第2副画素と連結されていて、第2信号を伝達する第2信号線、前記第1及び第2信号線と交差し、前記第1及び第2副画素のうちの少なくとも一つに連結されていて、第3信号を伝達する第3信号線、及び前記第1及び第2信号線と交差し、第4信号を伝達する第3信号線を含み、前記第1及び第2副画素は互いに異なる大きさのデータ電圧の印加受け、前記第1副画素に印加されるデータ電圧と前記第2副画素に印加されるデータ電圧は一つの画像情報から得られる。

#### 【0012】

前記第1副画素は、前記第1信号線と連結されている第1スイッチング素子及びこれに連結されている第1液晶キャパシタを含み、前記第2副画素は、前記第2信号線と連結されている第2スイッチング素子及びこれに連結されている第2液晶キャパシタを含むことができる。

前記第1液晶キャパシタは、前記第1スイッチング素子と連結されている第1副画素電極を含み、前記第2液晶キャパシタは、前記第2スイッチング素子と連結されている第2副画素電極を含むことができる。

#### 【0013】

前記第1及び第2副画素電極は、前記第1乃至第4信号線と斜角をなす間隙をおくことができ、前記第1及び第2副画素電極のうちの少なくとも一つは、前記第1乃至第4信号線と斜角をなす切開部を有することができる。

前記第1及び第2副画素電極は、前記第1及び第2副画素電極と対向する共通電極を共通にさらに含み、前記共通電極は、前記第1乃至第4信号線と斜角をなす切開部を有することができる。

#### 【0014】

前記第1スイッチング素子は前記第1及び第3信号線と連結されており、前記第2スイ

10

20

30

40

50

ツチング素子は前記第2及び第3信号線と連結されていることができる。

前記第1スイッチング素子は、前記第1信号線からの信号によって導通して前記第3信号線からの信号を伝達し、前記第2スイッチング素子は、前記第2信号線からの信号によって導通して前記第3信号線からの信号を伝達することができる。

【0015】

前記第1スイッチング素子は、前記第3信号線からの信号によって導通して前記第1信号線からの信号を伝達し、前記第2スイッチング素子は、前記第3信号線からの信号によって導通して前記第2信号線からの信号を伝達することができる。

前記第1副画素は、前記第1及び第3信号線と連結されており、前記第2副画素は、前記第2及び第4信号線と連結されていることができる。

10

【0016】

前記第1副画素は、前記第1スイッチング素子と連結されている第1ストレージキャパシタをさらに含み、前記第2副画素は、前記第2スイッチング素子と連結されている第2ストレージキャパシタをさらに含むことができる。

前記表示装置は、互いに異なる第1及び第2階調電圧集合を生成し、前記画像情報に該当する階調電圧を前記第1及び前記第2階調電圧集合から各々選択して、前記第1及び第2副画素に各々印加することができる。

【0017】

これとは異なり、前記表示装置は前記画像情報を処理して第1画像信号と第2画像信号を生成し、前記第1画像信号と第2画像信号に対応するそれぞれのデータ電圧を一つの階調電圧集合から選択して前記第1及び第2副画素に各々印加することができる。

20

前記各画素の第1副画素と第2副画素は、容量性結合されていることができる。

本発明の他の実施形態による表示装置は、第1及び第2副画素を含む画素、前記第1及び第2副画素に連結されていて、ゲート信号を伝達するゲート線、前記ゲート線と交差し、前記第1副画素に連結されていて、第1データ電圧を伝達する第1データ線、及び前記ゲート線と交差し、前記第2副画素に連結されていて、第2データ電圧を伝達する第2データ線を含む。

【0018】

前記第1データ電圧は前記第2データ電圧と異なり、一つの画像情報から得られることができ。

30

前記第1データ電圧の極性は前記第2データ電圧の極性と反対でありうる。

前記第1データ電圧の極性は所定時間一定でありうる。

本発明の他の実施形態による表示装置は、行列状に配列されていて、各々第1及び第2副画素を含む複数の画素、前記第1副画素に連結されていて、第1ゲートオン電圧を伝達する複数の第1ゲート線、前記第2副画素に連結されていて、第2ゲートオン電圧を伝達する複数の第2ゲート線、前記第1及び第2ゲート線と交差し、前記第1及び第2副画素に連結されていて、データ電圧を伝達する複数のデータ線、第1及び第2階調信号集合を生成する階調信号生成回路、前記第1及び第2階調信号集合を交互に選択して出力する選択回路、前記選択回路からの階調信号集合に基づいて画像データに対応する前記データ電圧を生成して前記データ線に印加するデータ駆動部、及び前記第1及び第2ゲート線に順次に前記第1及び第2ゲートオン電圧を印加するゲート駆動部を含む。

40

【0019】

前記階調信号はアナログ階調電圧を含むことができる。

この時、前記選択回路はアナログスイッチまたはアナログマルチプレクサーを含むことができる。前記選択回路は前記データ駆動部と統合されていることができる。前記階調電圧生成回路は各々複数の抵抗列を含む複数のアナログ電圧生成回路を含むことができる。

前記階調信号はデジタル階調データを含む表示装置である。

【0020】

この時、前記表示装置は、前記選択回路が選択したデジタル階調データ集合の各階調データをアナログ変換して複数の階調電圧を生成するデジタル-アナログ変換器をさらに含

50

むことができる。前記選択回路は前記階調信号生成回路に連結されている複数のマルチブレクサーを含むことができる。

前記第1ゲートオン電圧の印加時間と前記第2ゲートオン電圧の印加時間とは、少なくとも一部重畠することができる。

#### 【0021】

前記第1ゲートオン電圧の印加時間は、前記第2ゲートオン電圧の印加時間と同一か、または短いことができる。

本発明の他の実施形態による表示装置は、行列状に配列されていて、各々第1及び第2副画素を含む複数の画素、前記第1副画素に連結されていて、第1ゲートオン電圧を伝達する複数の第1ゲート線、前記第2副画素に連結されていて、第2ゲートオン電圧を伝達する複数の第2ゲート線、前記第1及び第2ゲート線と交差し、前記第1及び第2副画素に連結されていて、データ電圧を伝達する複数のデータ線、周期的に値が変化する複数の基準電圧を生成する基準電圧生成回路、前記基準電圧に基づいて複数の階調電圧を生成する階調電圧生成回路、前記階調電圧生成回路からの階調電圧集合より画像データに対応する階調電圧を選択して、前記データ電圧として前記データ線に印加するデータ駆動部、及び前記第1及び第2ゲート線に順次に前記第1及び第2ゲート信号を印加するゲート駆動部を含む。

#### 【0022】

本発明の他の実施形態による液晶表示装置は、互いに並んで延在していて、互いに分離されている第1及び第2ゲート線、前記第1及び第2ゲート線と交差するデータ線、前記第1ゲート線と前記データ線に連結されている第1薄膜トランジスタ、前記第2ゲート線と前記データ線に連結されている第2薄膜トランジスタ、及び前記第1及び第2薄膜トランジスタに各々連結されていて、互いに対向する傾いた斜辺を有する第1及び第2表示電極を含む。

#### 【0023】

本発明の他の実施形態による液晶表示装置は、第1方向に延在していて、互いに分離されている第1及び第2ゲート線、第2方向に延在しているデータ線、前記第1ゲート線と前記データ線に連結されている第1薄膜トランジスタ、前記第2ゲート線と前記データ線に連結されている第2薄膜トランジスタ、及び前記第1及び第2薄膜トランジスタに各々連結されていて、第1及び第2表示電極を含み、前記第2表示電極の前記第2方向の長さが前記第1表示電極よりも長く、前記第1表示電極は前記第2表示電極の第2方向の長さ内に位置する。

#### 【0024】

本発明の他の実施形態による液晶表示装置は、第1方向に延在していて、互いに分離されている第1及び第2ゲート線、第2方向に延在しているデータ線、前記第1ゲート線と前記データ線に連結されている第1薄膜トランジスタ、前記第2ゲート線と前記データ線に連結されている第2薄膜トランジスタ、及び前記第1及び第2薄膜トランジスタに各々連結されていて、第1及び第2表示電極を含み、前記第1及び第2表示電極は各々前記第1方向に延在する一つの直線を中心に実質的に対称の形状を有している。

#### 【0025】

この液晶表示装置は、前記第1及び第2電極と対向する第3表示電極をさらに含むことができる。

前記第1または第2表示電極のうちの少なくとも一つは切開部を有することができ、前記第3表示電極は切開部または突起を有することができる。これら切開部または突起は交互に配列でき、前記第1表示電極と前記第2表示電極の間の間隙と前記第3表示電極の切開部とが交互に配列されることもできる。

#### 【0026】

前記第1ゲート線は前記第1及び第2表示電極と重畠することができ、前記第2ゲート線は前記第2表示電極と重畠し、前記第1表示電極とは重畠しないことができる。

前記液晶表示装置は前記第1及び第2表示電極と重畠する維持電極線をさらに含むこと

10

20

30

40

50

ができる。

前記第1及び第2薄膜トランジスタは、各々前記第1または第2ゲート線と連結されているゲート電極、前記データ線と連結されているソース電極及び前記第1または第2表示電極と連結されているドレイン電極を含み、前記維持電極線は前記ドレイン電極と重畠することができる。

【0027】

前記液晶表示装置は前記第2表示電極と連結されており、前記第1表示電極と重畠する結合電極をさらに含むことができる。

前記第1表示電極の電圧は前記第2表示電極の電圧とは異なることができ、前記第1表示電極の電圧と所定電圧との差は、前記第2表示電極の電圧と前記所定電圧との差よりも小さいことができる。

【0028】

前記液晶表示装置は、前記データ線と重畠し、前記画素電極と同一層に位置した遮蔽電極をさらに含むことができる。

本発明の他の実施形態による薄膜トランジスタ表示板は、絶縁基板上に形成されているゲート線、前記ゲート線と絶縁されて交差している第1及び第2データ線、前記ゲート線と前記第1データ線に連結されていて、第1ドレイン電極を含む第1薄膜トランジスタ、前記ゲート線と前記第2データ線に連結されていて、第2ドレイン電極を含む第2薄膜トランジスタ、前記ゲート線、前記第1及び第2データ線及び前記第1及び第2薄膜トランジスタを覆っており、前記第1データ線の一部を露出する第1接触孔と、前記第2データ線の一部を露出する第2接触孔とを有する保護膜、及び前記第1接触孔を通じて前記第1ドレイン電極と連結されている第1副画素電極と、前記第2接触孔を通じて前記第2ドレイン電極と連結されている第2副画素電極とを含む画素電極を含む。

【0029】

前記第1及び第2副画素電極と絶縁されていて、前記ゲート線または前記第1及び第2データ線と少なくとも一部重畠している遮蔽電極をさらに含むことができる。

前記画素電極と前記遮蔽電極は前記保護膜上部に位置することができる。

前記第1及び第2ドレイン電極と重畠して保持容量を形成する維持電極を有する維持電極線をさらに含むことができ、前記遮蔽電極と前記維持電極とは実質的に同一の電圧の印加を受けることができる。

【0030】

前記遮蔽電極は前記第1及び第2データ線を完全に覆うことができる。

前記第1副画素電極の面積は前記第2副画素電極の面積とは異なることができる。

本発明の一つの実施形態による液晶表示装置の駆動方法は、画像データの入力を受ける段階、前記入力画像データを二つ以上のデータ電圧に変換する段階、及び前記変換されたデータ電圧を当該副画素に印加する段階を含むことができる。

【0031】

前記変換段階は、二つ以上の階調電圧集合を生成する段階、及び前記二つ以上の階調電圧集合それぞれから前記入力画像データに対応する階調電圧を選択してデータ電圧にする段階を含むことができる。

前記変換段階は、前記入力画像データを二つ以上の出力画像データに変換する段階、一つの階調電圧集合から前記二つ以上の出力画像データに対応する階調電圧を選択してデータ電圧にする段階を含むことができる。

【0032】

本発明の一実施形態による液晶表示装置の駆動方法は、行列状に配列されていて、第1及び第2副画素を各々有する複数の画素を含む液晶表示装置の駆動方法であって、前記第1副画素に第1極性の第1データ電圧を印加する段階、及び前記第2副画素に前記第1極性と反対である第2極性の第2データ電圧を印加する段階を含む。

前記第1データ電圧と前記第2データ電圧は、一つの画像データから生成できる。

【0033】

10

20

30

40

50

行方向に隣接した画素の対応副画素に印加されるデータ電圧は、極性が反対でありうる。

列方向に隣接した画素の対応副画素に印加されるデータ電圧は、極性が同一でありうる。

前記各データ電圧は、2個以上の副画素に同時に印加できる。

【0034】

本発明の一実施形態による液晶表示装置の駆動方法は、第1及び第2副画素を各々有する複数の画素を含む液晶表示装置の駆動方法であって、画像データを伝送する段階、第1階調電圧集合を出力する段階、前記画像データを前記第1階調電圧集合の階調電圧の中から選択された第1データ電圧に変換する段階、前記第1データ電圧を前記第1副画素に印加する段階、マルチプレクサーを利用して前記第1階調電圧集合を前記第1階調電圧集合と値の異なる第2階調電圧集合に代替して出力する段階、前記画像データを前記第2階調電圧集合の階調電圧の中から選択された第2データ電圧に変換する段階、及び前記第2データ電圧を前記第2副画素に印加する段階を含む。

【0035】

前記駆動方法は、前記第1及び第2階調電圧集合を生成する段階をさらに含み、前記第1階調電圧集合出力段階は、前記マルチプレクサーを利用して前記第1及び第2階調電圧集合の中から前記第1階調電圧集合を選択する段階を含み、前記第2階調電圧集合の出力段階は、前記マルチプレクサーを利用して前記第1及び第2階調電圧集合の中から前記第2階調電圧集合を選択する段階を含むことができる。

【0036】

前記駆動方法は第1及び第2デジタル階調データ集合を記憶する段階をさらに含み、前記第1階調電圧集合の出力段階は、前記マルチプレクサーを利用して前記第1及び第2デジタル階調データ集合の中から前記第1デジタル階調データ集合を選択する段階、及び前記第1デジタル階調データ集合をアナログ変換して前記第1階調電圧集合を生成する段階を含み、前記第2階調電圧集合の出力段階は、前記マルチプレクサーを利用して前記第1及び第2デジタル階調データ集合の中から前記第2デジタル階調データ集合を選択する段階、及び前記第2デジタル階調データ集合をアナログ変換して前記第2階調電圧集合を生成する段階を含むことができる。

【発明の効果】

【0037】

本発明によれば、二つの副画素電圧を所望の水準に正確に合わせることによって、視認性を向上し、開口率を高め、透過率を向上させる。

【発明を実施するための最良の形態】

【0038】

添付図面を参照して本発明の実施形態について本発明の属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。しかし、本発明は多様な相異なる形態に実現でき、ここで説明する実施形態に限定されない。

図面において、複数の層及び領域を明確に表現するために厚さを拡大して示した。明細書全体にわたって類似な部分については同一図面符号を付けた。層、膜、領域、板などの部分が他の部分の“上”にあるとする時、これは他の部分の“直上”にある場合だけでなく、その中間に他の部分がある場合も含む。逆に、ある部分が他の部分の“直上”にあるとする時は中間に他の部分がないことを意味する。

【0039】

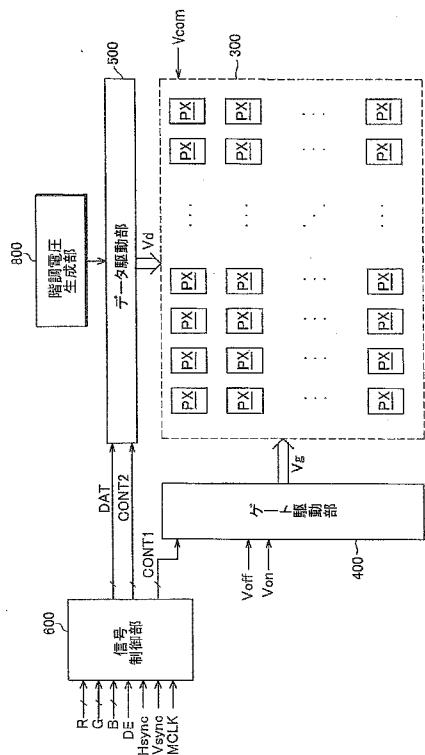

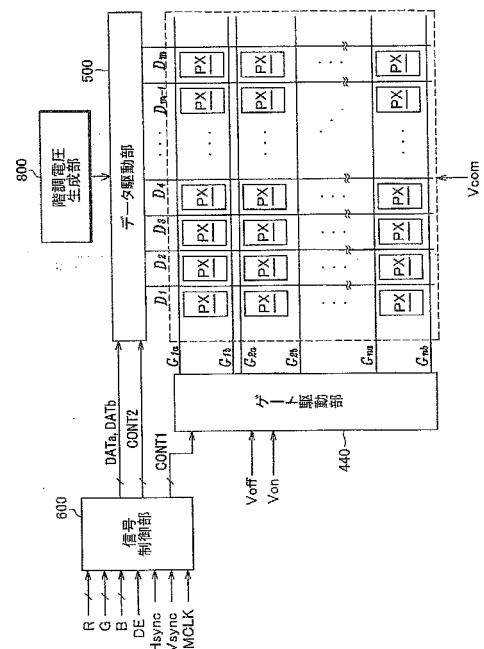

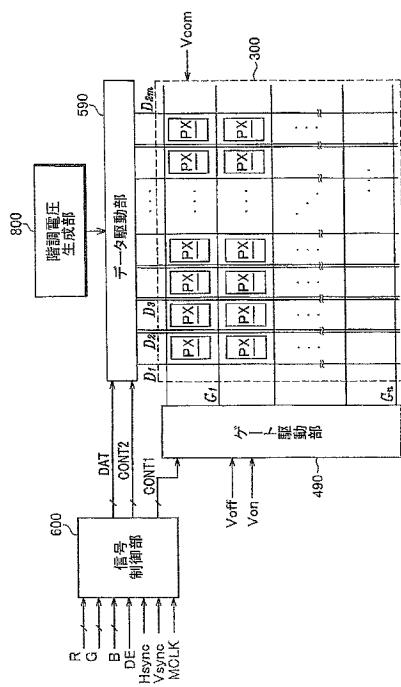

まず、図1及び図2を参照して本発明の一実施形態による液晶表示装置について詳細に説明する。

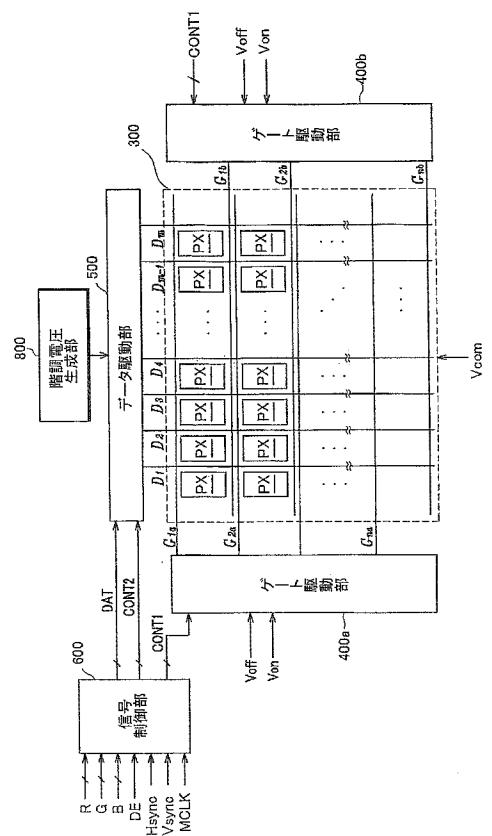

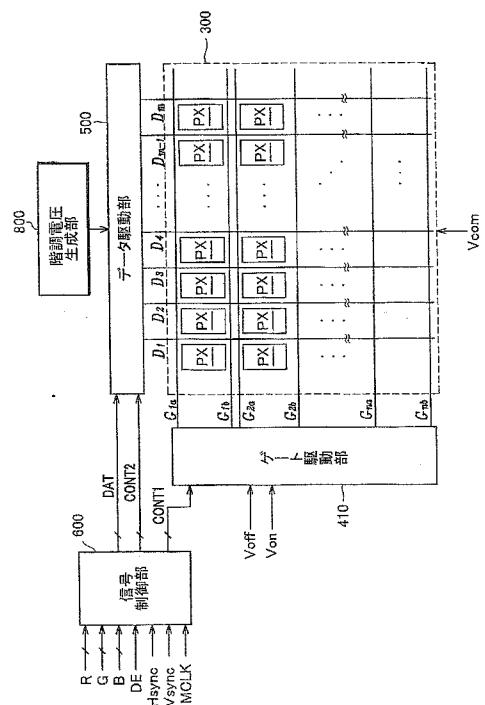

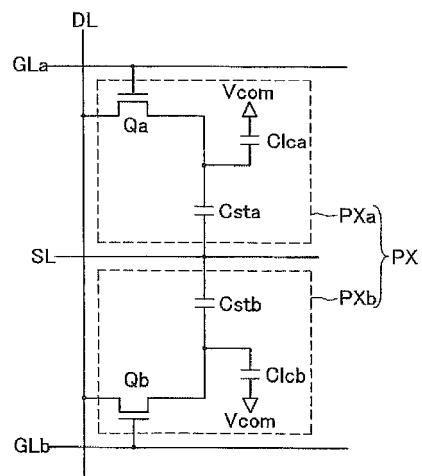

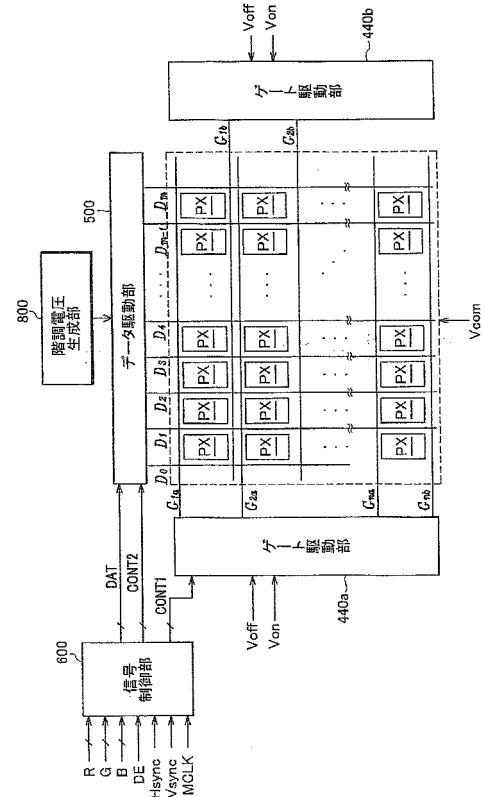

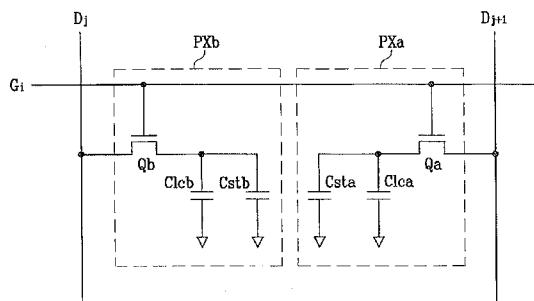

図1は本発明の一実施形態による液晶表示装置のブロック図であり、図2は本発明の一実施形態による液晶表示装置の二つの副画素に対する等価回路図である。

図1を参考すれば、本発明の一実施形態による液晶表示装置は、液晶表示板組立体300と、これに連結されたゲート駆動部400、データ駆動部500、データ駆動部500

10

20

30

40

50

に連結された階調電圧生成部 800、並びにこれらを制御する信号制御部 600 を含む。

【0040】

液晶表示板組立体 300 は、等価回路的には、複数の信号線（図示せず）と、これに連結されてほぼ行列状に配列された複数の画素  $P_X$  を含む。反面、図 2 に示した構造を参考すれば、液晶表示板組立体 300 は、互いに対向する下部表示板 100 及び上部表示板 200 と、その間に入っている液晶層 3 を含む。

信号線は、ゲート信号（“走査信号”とも言う）を伝達する複数のゲート線（図示せず）と、データ信号を伝達する複数のデータ線（図示せず）を含む。ゲート線は、ほぼ行方向に延在して、互いにほぼ平行であり、データ線は、ほぼ列方向に延在して、互いにほぼ平行である。

【0041】

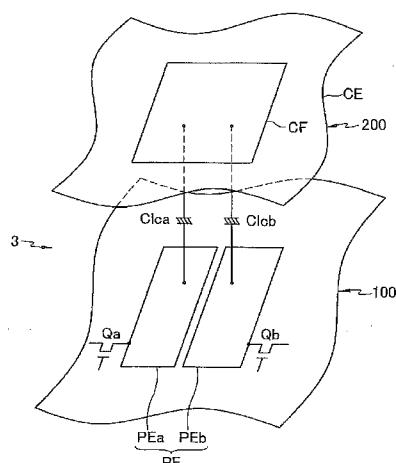

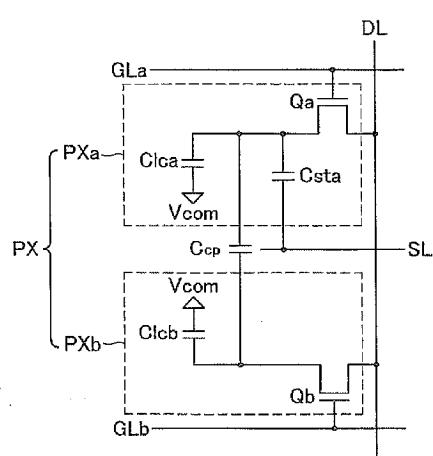

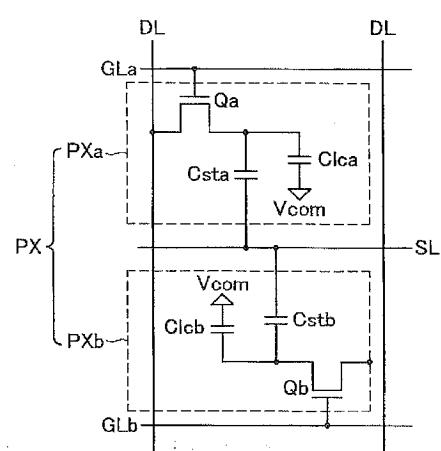

図 2 を参考すれば、各画素  $P_X$  は一对の副画素を含み、各副画素は液晶キャパシタ  $C_{1ca}/C_{1cb}$  と、ゲート線、データ線及び液晶キャパシタ  $C_{1ca}/C_{1cb}$  と連結されたスイッチング素子  $Q_a/Q_b$  を含む。

各スイッチング素子  $Q_a/Q_b$  は、下部表示板 100 に備えられている薄膜トランジスタなどからなり、ゲート線と連結されている制御端子、データ線と連結されている入力端子、並びに液晶キャパシタ  $C_{1ca}/C_{1cb}$  と連結されている出力端子を有する三端子素子である。

【0042】

液晶キャパシタ  $C_{1ca}/C_{1cb}$  は、下部表示板 100 の副画素電極  $P_{Ea}/P_{Eb}$  と上部表示板 200 の共通電極  $C_E$  とを二つの端子とし、副画素電極  $P_{Ea}/P_{Eb}$  と共通電極  $C_E$  との間の液晶層 3 が誘電体として機能する。一对の副画素電極  $P_{Ea}/P_{Eb}$  は、互いに分離されており、一つの画素電極  $P_E$  をなす。共通電極  $C_E$  は、上部表示板 200 の全面に形成されており、共通電圧  $V_{com}$  の印加を受ける。図 2 とは異なって、共通電極  $C_E$  が下部表示板 100 に備えられることもあり、その場合には二つの電極  $P_E$ 、 $C_E$  のうちの少なくとも一つを線状または棒状に作ることができる。

【0043】

一方、色表示を実現するため、各画素  $P_X$  が基本色のうちの一つを固有に表示したり（空間分割）、各画素  $P_X$  が時間によって交互に基本色を表示するように（時間分割）し、これら基本色の空間的、時間的の作用によって所望の色相が認識できるようとする。基本色の例としては、赤色、緑色、青色などの三原色がある。図 2 は、空間分割の一例であって、各画素  $P_X$  が上部表示板 200 の領域に基本色のうちの一つの色のカラーフィルタ  $C_F$  を備えている様子を示す。図 2 とは異なって、カラーフィルタ  $C_F$  は、下部表示板 100 の副画素電極  $P_{Ea}/P_{Eb}$  上または下に形成することもできる。

【0044】

表示板 100、200 の外側面には、各々偏光子（図示せず）が付着されているが、反射型液晶表示装置の場合には二つの偏光子のうちの一つを省略することができる。

再び図 1 を参考にすれば、階調電圧生成部 800 は、画素  $P_X$  の透過率に関わる複数の階調電圧を生成する。しかし、階調電圧生成部 800 が全階調に対する階調電圧を直接生成せず、階調電圧を生成する基準となる階調基準電圧のみを生成して出力することもできる。

【0045】

ゲート駆動部 400 は、液晶表示板組立体 300 のゲート線に連結され、ゲートオン電圧  $V_{on}$  とゲートオフ電圧  $V_{off}$  の組み合わせからなるゲート信号  $V_g$  をゲート線に印加する。

データ駆動部 500 は、液晶表示板組立体 300 のデータ線に連結され、階調電圧生成部 800 からの階調電圧を選択して、これをデータ信号  $V_d$  としてデータ線に印加する。しかし、階調電圧生成部 800 が全階調に対する電圧を全て提供せず、決められた数の基準階調電圧のみを提供する場合に、データ駆動部 500 は基準階調電圧を分圧して全体階調に対する階調電圧を生成し、この中でデータ信号  $V_d$  を選択する。

## 【0046】

信号制御部 600 は、ゲート駆動部 400 及びデータ駆動部 500 などを制御する。

このような駆動装置 400、500、600、800 は、各々少なくとも一つの集積回路チップの形態で液晶表示板組立体 300 上に直接装着されたり、可撓性印刷回路膜（図示せず）上に装着されて、TCP（tape carrier package）の形態で液晶表示板組立体 300 に付着されたり、別途の印刷回路基板（図示せず）上に装着されることもできる。これとは異なって、これら駆動装置 400、500、600、800 が液晶表示板組立体 300 に集積されることもできる。また、駆動装置 400、500、600、800 は、單一チップで集積されることが可能、この場合にはこれらのうちの少なくとも一つまたはこれらをなす少なくとも一つの回路素子が單一チップの外側に位置することができる。

10

## 【0047】

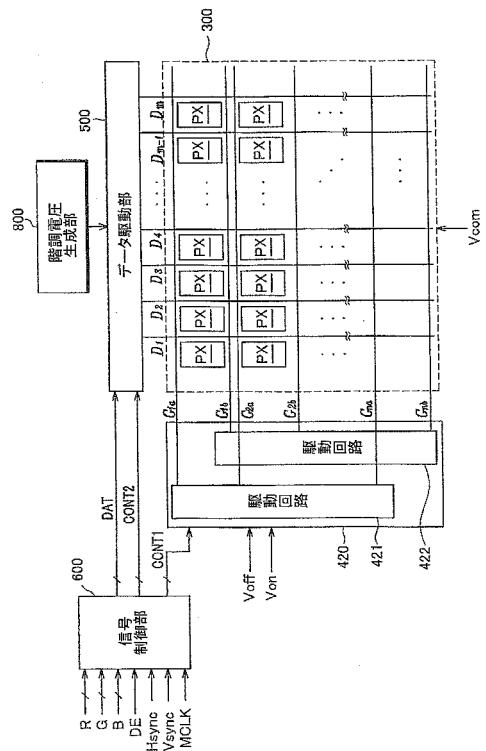

以下、図 3a 乃至図 4b を参照して、本発明の一実施形態による液晶表示装置について詳細に説明する。

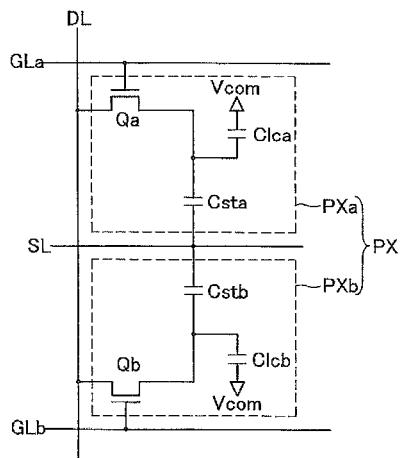

図 3a 乃至図 3c は、本発明の実施形態による液晶表示装置のプロック図であり、図 4a 及び図 4b は、本発明の実施形態による液晶表示装置の一画素に対する等価回路図である。

## 【0048】

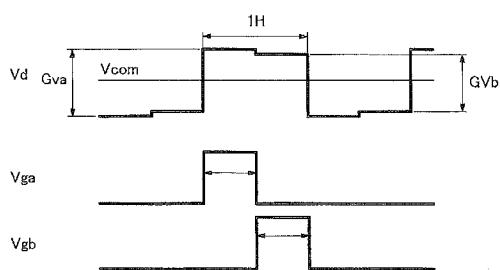

図 3a 乃至図 3c を参考すれば、本発明の実施形態による液晶表示装置は、液晶表示板組立体 300、一対または一つのゲート駆動部 400a、400b、410、420、データ駆動部 500、階調電圧生成部 800、並びに信号制御部 600 を含む。

液晶表示板組立体 300 は、複数の信号線と、これに連結されてほぼ行列状に配列された複数の画素 PX を含む。

## 【0049】

信号線は、下部表示板 100（図 2 参照）に備えられており、ゲート信号（“走査信号”とも言う）を伝達する複数のゲート線 G<sub>1a</sub> - G<sub>n b</sub> と、データ信号を伝達するデータ線 D<sub>1</sub> - D<sub>m</sub> を含む。

図 4a 及び図 4b には、信号線と画素 PX の等価回路が示されているが、図面符号 GL<sub>a</sub>、GL<sub>b</sub> で示した上部及び下部ゲート線と、図面符号 DL で示したデータ線、その他にも表示信号線は、ゲート線 G<sub>1</sub> - G<sub>2b</sub> とほぼ並んで延在した維持電極線 SL を含む。

30

## 【0050】

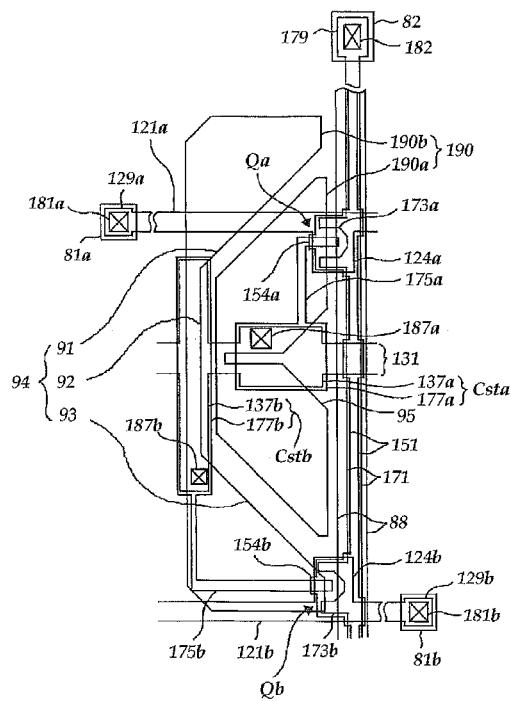

図 4a に示した液晶表示装置の場合、各画素 PX は、一対の副画素 PX<sub>a</sub>、PX<sub>b</sub> を含み、各副画素 PX<sub>a</sub> / PX<sub>b</sub> は、該当ゲート線 GL<sub>a</sub> / GL<sub>b</sub> 及びデータ線 DL に連結されているスイッチング素子 Q<sub>a</sub> / Q<sub>b</sub>、これに連結された液晶キャパシタ C<sub>1ca</sub> / C<sub>1cb</sub>、並びにスイッチング素子 Q<sub>a</sub> / Q<sub>b</sub> と維持電極線 SL の間に連結されているストレージキャパシタ C<sub>sta</sub> / C<sub>stb</sub> を含む。ストレージキャパシタ C<sub>sta</sub>、C<sub>stb</sub> は、必要に応じて省略することができ、その場合には維持電極線 SL も必要ない。

## 【0051】

図 4b に示した液晶表示装置の場合、各画素 PX は、一対の副画素 PX<sub>a</sub>、PX<sub>b</sub> と、これらの間に連結されている結合キャパシタ C<sub>cp</sub> を含み、各副画素 PX<sub>a</sub> / PX<sub>b</sub> は、該当ゲート線 GL<sub>a</sub> / GL<sub>b</sub> 及びデータ線 DL に連結されているスイッチング素子 Q<sub>a</sub> / Q<sub>b</sub> と、これに連結された液晶キャパシタ C<sub>1ca</sub> / C<sub>1cb</sub> を含む。そして、二つの副画素 PX<sub>a</sub>、PX<sub>b</sub> のうちの一つ PX<sub>a</sub> は、スイッチング素子 Q<sub>a</sub> と維持電極線 SL の間に連結されているストレージキャパシタ C<sub>sta</sub> を含む。

40

## 【0052】

液晶キャパシタ C<sub>1ca</sub> / C<sub>1cb</sub> の補助的な役割を果たすストレージキャパシタ C<sub>sta</sub> / C<sub>stb</sub> は、構造的な側面で、維持電極線 SL と画素電極 PE<sub>a</sub> / PE<sub>b</sub> が絶縁体を介在して重畳してなり、維持電極線 SL には共通電圧 V<sub>com</sub> などの決められた電圧が印加される。しかし、ストレージキャパシタ C<sub>sta</sub>、C<sub>stb</sub> は、副画素電極 PE<sub>a</sub>、PE<sub>b</sub> が絶縁体を媒介としてすぐ上の前段ゲート線と重畳してなることができる。

50

## 【0053】

再び図3a乃至図3cを参考すれば、ゲート駆動部400a、400b、410、420は、ゲート線G<sub>1a</sub>-G<sub>nb</sub>に連結され、外部からのゲートオン電圧V<sub>on</sub>とゲートオフ電圧V<sub>off</sub>の組み合わせからなるゲート信号をゲート線G<sub>1a</sub>-G<sub>nb</sub>に印加する。図3aでは、一対のゲート駆動部400a、400bが、各々液晶表示板組立体300の左右に位置し、奇数番目及び偶数番目ゲート線G<sub>1a</sub>-G<sub>nb</sub>に各々連結され、図3b及び図3cに示した一つのゲート駆動部410、420は、液晶表示板組立体300の一側に位置し、全ゲート線G<sub>1a</sub>-G<sub>nb</sub>に連結されており、図3cの場合、ゲート駆動部420内に二つの駆動回路421、422が内装されており、各々奇数番目及び偶数番目ゲート線G<sub>1a</sub>-G<sub>nb</sub>に連結される。

10

## 【0054】

階調電圧生成部800は、画素の透過率に関わる二つの階調電圧集合（または、基準階調電圧集合）を生成する。二つの階調電圧集合は、一つの画素PXを構成する二つの副画素PXa、PXbに独立的に提供されるものであって、各階調電圧集合は、共通電圧V<sub>com</sub>に対して正の値を有するものと、負の値を有するものを含む。しかし、二つの（基準）階調電圧集合の代わりに、一つの（基準）階調電圧集合のみを生成することもできる。

## 【0055】

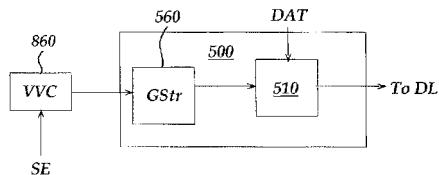

以下、図3a乃至図4bに示した液晶表示装置における階調電圧生成部とデータ駆動部の多様な例について、図5a乃至5cを参照して詳細に説明する。

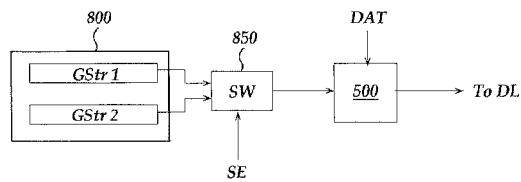

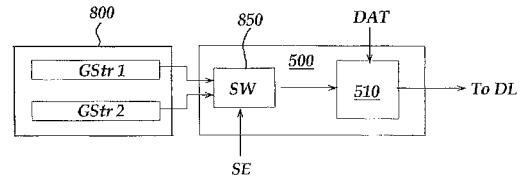

図5aに示した例の液晶表示装置は、二つの電圧生成抵抗列G<sub>Str1</sub>、G<sub>Str2</sub>を含む階調電圧生成部800と、データ駆動部500の他に、これらの間に連結され、選択信号SEによって階調電圧生成部800からの二つの階調電圧集合のうちの一つを選択するアナログスイッチSW850を別個の部分としてさらに含む。

20

## 【0056】

図5bに示した例の液晶表示装置は、図5aに示したアナログスイッチ850をデータ駆動部500内に統合した構造を有している。図面において、図面符号510は、従来のデータ駆動部機能ブロックを示す。

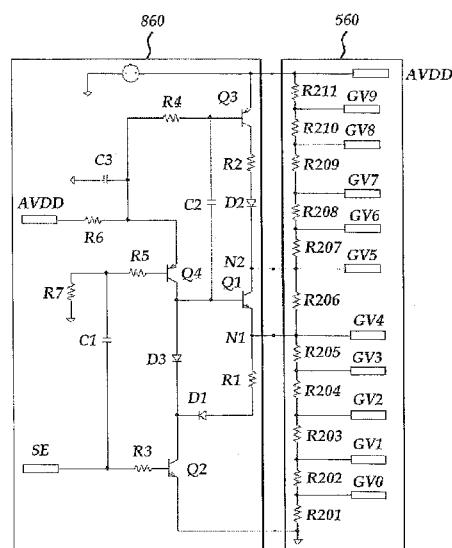

図5cに示した例の液晶表示装置は、階調電圧生成部800の代わりに、基準電圧変更回路V<sub>CC860</sub>のみを設けて、選択信号SEによって大きさが変わる所定数の基準電圧を生成するようにし、データ駆動部500内に階調電圧を生成することができる電圧生成抵抗列G<sub>Str560</sub>を設けて、基準電圧変更回路V<sub>VCC860</sub>から供給される基準電圧によって互いに異なる複数のガンマ電圧集合を生成するようにしている。

30

## 【0057】

図5cに示した基準電圧変更回路と電圧生成抵抗列の一例を図6に示した。

図6を参考すれば、電圧生成抵抗列560は、一列に連結されている複数の抵抗R<sub>201</sub>～R<sub>211</sub>を含み、中央の抵抗R<sub>206</sub>と、その両側に連結されており、各々五つの抵抗R<sub>201</sub>～R<sub>205</sub>、R<sub>207</sub>～R<sub>211</sub>を含む第1及び第2抵抗集合に分けることができる。第1抵抗集合R<sub>201</sub>～R<sub>205</sub>と第2抵抗集合R<sub>207</sub>～R<sub>211</sub>の一端は、各々接地電圧などの低電圧と電源電圧(AVDD)に連結されている。

40

## 【0058】

基準電圧変更回路860は、中央抵抗R<sub>206</sub>、第1抵抗集合R<sub>201</sub>～R<sub>205</sub>、及び第2抵抗集合R<sub>207</sub>～R<sub>211</sub>の両端に各々連結されているNPN及びPNP双極性(bipolar)トランジスタQ1、Q2、Q3、その間に連結されており、直列に連結された抵抗R1、R2、及びダイオードD1、D2対を含む。電源電圧AVDDが入力される高電圧入力端とトランジスタQ3の間には、抵抗R5、R7を介してベースに低電圧の印加を受けるPNPトランジスタQ4が、ダイオードD3を介在して連結されている。NPNトランジスタQ2は、抵抗R3を介して選択信号SE入力端に連結されており、PNPトランジスタQ3は、抵抗R4、R6を介して高電圧入力端に連結されている。トランジスタQ1、Q3のベースの間にはキャパシタC2が、トランジスタQ2、Q4の間には抵抗R3、R5を介在してキャパシタC1が連結されており、抵抗R4、R6の間に

50

はキャパシタC3が連結されている。

【0059】

このような基準電圧変更回路860において、トランジスタQ3は常に導通状態であるので、その一端には電源電圧AVDDが印加される。選択信号SEが低い値である場合、トランジスタQ4はターンオフされて、高電圧との連結を遮断し、トランジスタQ2は導通して、低電圧との通路を作る。これによって、接点N1、N2には低い電圧が印加される。逆に、選択信号SEが高い値である場合、トランジスタQ2がターンオフされて、低電圧との連結を遮断し、トランジスタQ4が導通して、高電圧との通路を作る。これによって、接点N1、N2には抵抗R1、R6などによって決定される高い電圧が印加される。

10

【0060】

以下、このような液晶表示装置の表示動作について詳細に説明する。

信号制御部600は、外部のグラフィック制御器（図示せず）から入力画像信号R、G、B、及びその表示を制御する入力制御信号を受信する。入力画像信号R、G、Bは、各画素PXの輝度情報を含んでおり、輝度は決められた数、例えば、1024（=2<sup>10</sup>）、256（=2<sup>8</sup>）、または64（=2<sup>6</sup>）個の階調を有している。入力制御信号の例としては、垂直同期信号Vsync、水平同期信号Hsync、メインクロックMCLK、データイネーブル信号DEなどがある。

【0061】

信号制御部600は、入力画像信号R、G、Bと入力制御信号に基づいて画像信号R、G、Bを液晶表示板組立体300の動作条件に合うように適切に処理し、ゲート制御信号CONT1及びデータ制御信号CONT2などを生成した後、ゲート制御信号CONT1をゲート駆動部400a、400b、410、420に送出し、データ制御信号CONT2と処理した画像信号DATをデータ駆動部500に送出する。

20

【0062】

ゲート制御信号CONT1は、走査開始を指示する走査開始信号STVと、ゲートオン電圧Vonの出力周期を制御する少なくとも一つのクロック信号を含む。ゲート制御信号CONT1は、また、ゲートオン電圧Vonの持続時間を限定する出力イネーブル信号OEを含むことができる。ここで、クロック信号は、図5a乃至図5c及び図6に示した選択信号SEとして使用されることができる。

30

【0063】

データ制御信号CONT2は、一束の副画素PXa、PXbに対するデジタル画像信号DATの伝送を知らせる水平同期開始信号STHとデータ線D<sub>1</sub> - D<sub>m</sub>に該当データ電圧の印加を指示するロード信号LOAD、及びデータクロック信号HCLKを含む。データ制御信号CONT2は、また、共通電圧Vcomに対するデータ電圧の極性（以下、“共通電圧に対するデータ電圧の極性”を略して“データ電圧の極性”という）を反転させる反転信号RVSを含むことができる。

【0064】

信号制御部600からのデータ制御信号CONT2によって、データ駆動部500は、一束の副画素PXa、PXbに対する画像データDATを受信し、階調電圧生成部800からの二つの階調電圧集合のうちの一つの集合を選択し、選択した階調電圧集合のうちの各画像データDATに対応する階調電圧を選択することによって、画像データDATを該当データ電圧に変換した後、これを該当データ線D<sub>1</sub> - D<sub>m</sub>に印加する。

40

【0065】

これとは異なって、図5aのように、データ駆動部500ではなく、別途に具備された外部の選択回路850で二つの階調電圧集合のうちのいずれか一つを選択してデータ駆動部500に伝達したり、図5cのように、階調電圧生成部800は値が変化する基準電圧を提供し、データ駆動部500はこれを分圧して自ら階調電圧を生成することもできる。

ゲート駆動部400a、400b、410、420は、信号制御部600からのゲート制御信号CONT1によって、ゲートオン電圧Vonをゲート線G<sub>1a</sub> - G<sub>nb</sub>に印加し、こ

50

のゲート線  $G_{1a}$  -  $G_{n_b}$  に連結されたスイッチング素子  $Q_a$ 、 $Q_b$  を導通させる。これによつて、データ線  $D_1$  -  $D_m$  に印加されたデータ電圧が、導通したスイッチング素子  $Q_a$ 、 $Q_b$  を介して該当副画素  $PX_a$ 、 $PX_b$  に印加される。

#### 【0066】

副画素  $PX_a$ 、 $PX_b$  に印加されたデータ電圧と共通電圧  $V_{com}$  の差は、液晶キャパシタ  $C_{1ca}$ 、 $C_{1cb}$  の充電電圧、つまり、画素電圧として現れる。液晶分子は、画素電圧の大きさに応じてその配列を異にし、そのため液晶層 3 を通過する光の偏光が変化する。このような偏光の変化は表示板 100、200 に付着された偏光子（図示せず）によって光透過率の変化として現れ、これによって、画素  $PX$  は画像信号 DAT の階調が示す輝度を表示する。

#### 【0067】

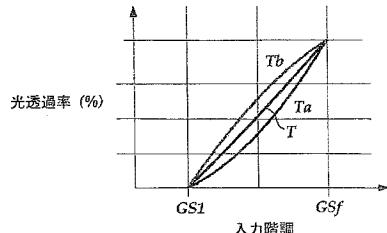

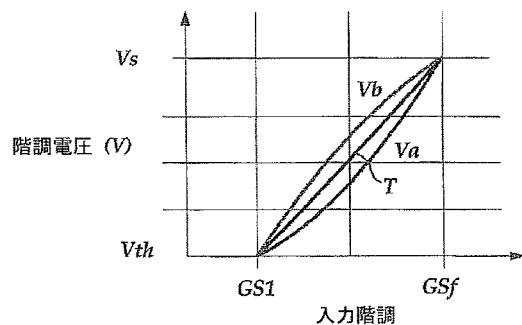

前述の二つの階調電圧集合は、図 7a に示したように、互いに異なるガンマ曲線  $T_a$ 、 $T_b$  を示し、これらが一つの画素  $PX$  の二つの副画素  $PX_a$ 、 $PX_b$  に印加されるので、一つの画素  $PX$  のガンマ曲線は、これらを合成した曲線  $T$  となる。二つの階調電圧集合を決定する際には合成ガンマ曲線  $T$  が正面での基準ガンマ曲線に近くなるようにし、例えば、正面での合成ガンマ曲線  $T$  は、最も適するように決められた正面での基準ガンマ曲線と一致するようにし、側面での合成ガンマ曲線  $T$  は正面での基準ガンマ曲線と最も近くなるようにする。図 7a において、GS1 と GSf は、最も低い入力階調と最も高い入力階調を意味する。例えば、下方に位置したガンマ曲線を低階調でさらに低くすれば、視認性がさらに向上することができる。

#### 【0068】

1/2 水平周期（または“1/2H”）[水平同期信号 H sync 及びゲートクロック CPV の一周期]を単位として、データ駆動部 500 とゲート駆動部 400a、400b、410、420 は、同一の動作を繰り返す。このような方法で、1 フレーム期間中、全ゲート線  $G_1$  -  $G_{2n}$  に対して、順次ゲートオン電圧  $V_{on}$  を印加して全画素にデータ電圧を印加する。1 フレームが終了すれば次のフレームが開始し、各画素に印加されるデータ電圧の極性が直前フレームでの極性と逆になるように、データ駆動部 500 に印加される反転信号 RVS の状態が制御される（フレーム反転）。この時、1 フレーム期間内であつても反転信号 RVS の特性に応じて、一つのデータ線を介して流れるデータ電圧の極性が変わったり（例：行反転、ドット反転）、隣接データ線を介して同時に流れるデータ電圧の極性も互いに異なることができる（例：列反転、ドット反転）。

#### 【0069】

しかし、このような液晶表示装置の場合、通常の液晶表示装置に比べて 2 倍のゲート線を有するので、通常の方法でデータ電圧を印加すれば、電圧充電時間が短いため画素が目標輝度に到達できないことがあり、これは極性反転のためさらにそうである。したがって、隣接した二つのゲート線にゲートオン電圧  $V_{on}$  を印加する時間を一部重畳することができ、これは図 3a 及び図 3c に示したゲート駆動部を採用すれば可能である。

#### 【0070】

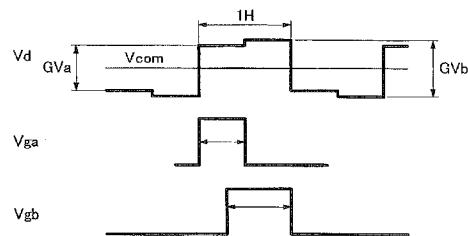

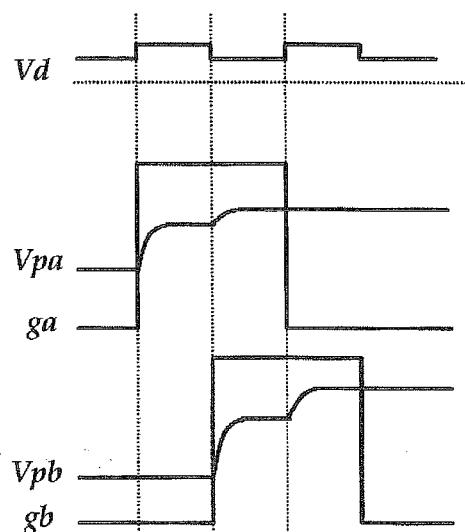

以下、多様なデータ電圧印加類型について、図 8a 乃至図 8c を参照して詳細に説明する。

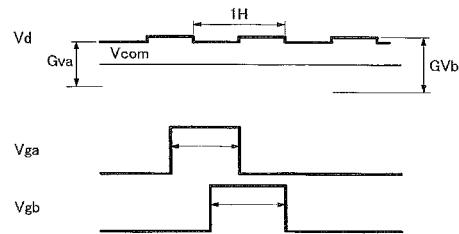

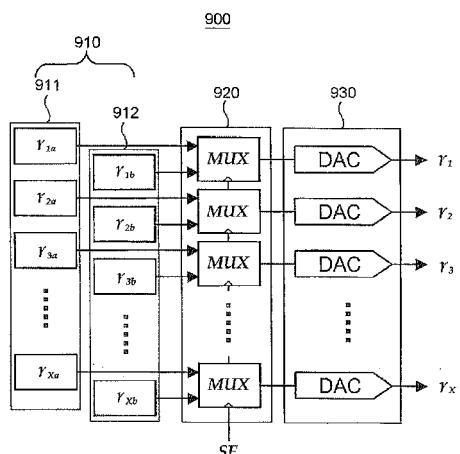

図 8a 乃至図 8c は、本発明の実施形態による液晶表示装置の信号波形を時間によって示した図面であつて、 $V_{ga}$  は上部ゲート線に印加されるゲート信号、 $V_{gb}$  は下部ゲート線に印加されるゲート信号、 $V_d$  は一つのデータ線に流れるデータ電圧である。

#### 【0071】

ドット反転である場合には、隣接画素の極性が逆であるので、隣接画素のデータ電圧の印加を受けることが充電時間を減らすのにあまり役立たない。したがって、図 8a に示したように、隣接画素の充電時間は重ならないようにし、一つの画素の二つの副画素の充電時間を重畳させるのが好ましい。これによって、後で充電される副画素は充電時間が減るので、図 8a 及び図 8b に示したように、最初に充電される副画素に印加される階調電圧集合の大きさ  $V_{ga}$  より、後で充電される副画素に印加される階調電圧集合の大きさ  $V_g$

10

20

30

40

50

b を大きくするのが好ましい。

【 0 0 7 2 】

しかし、列反転の場合には、上下に隣接した画素の極性が同一なので、隣接画素のデータ電圧を印加して事前充電をすることができる。したがって、図 8 b に示したように、全副画素の充電時間を一定時間以上重畠させることができる。

図 8 c は、図 1 B のゲート駆動部のように、一回に一つのゲート線にゲートオン電圧  $V_{on}$  を印加することができる場合を示す。

【 0 0 7 3 】

以下、本発明の他の実施形態による液晶表示装置について、図 9 乃至図 11 を参照して詳細に説明する。

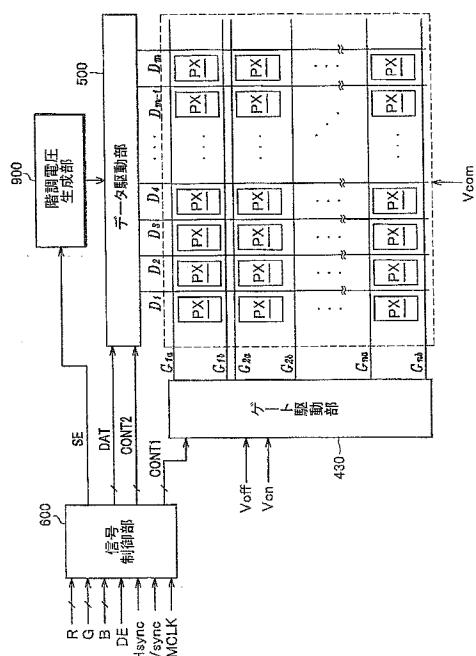

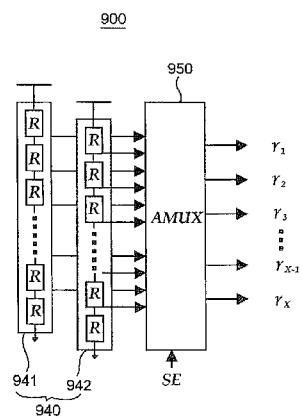

図 9 は、本発明の他の実施形態による液晶表示装置のブロック図であり、図 10 は、本発明の一実施形態による階調電圧生成部のブロック図であり、図 11 は、本発明の他の実施形態による液晶表示装置の階調電圧生成部のブロック図である。

【 0 0 7 4 】

図 9 に示した液晶表示装置は、図 3 b に示した液晶表示装置とほぼ同一である。つまり、本実施形態による液晶表示装置は、液晶表示板組立体 300、これに連結された一つのゲート駆動部 430、データ駆動部 500、データ駆動部 500 に連結された階調電圧生成部 900、並びにこれらを制御する信号制御部 600 を含む。

本実施形態による信号制御部 600 は、ゲート制御信号  $CONT_1$  及びデータ制御信号  $CONT_2$  の他にも、階調電圧生成部 600 を制御する選択信号  $SE$  を生成して出力する。

【 0 0 7 5 】

また、本実施形態による階調電圧生成部 900 は、二つのアナログ階調電圧集合を別個に生成し、選択信号  $SE$  によって二つの階調電圧集合を交互に出力したり、予め保存されている二つのデジタル階調データ集合を選択信号  $SE$  によって交互に選択し、選択したデジタル階調データ集合に基づいてアナログ階調電圧集合を生成して出力する。後者の場合、二つのデジタル階調データ集合に各々対応する二つのアナログ階調電圧集合が交互に生成されると見ることができる。二つの階調電圧集合は、一つの画素を構成する二つの副画素に独立的に提供されるものであり、各階調電圧集合は、共通電圧  $V_{com}$  に対して正の値を有するものと、負の値を有するものを含む。前述したように、階調電圧生成部 900 が全階調に対する階調電圧を直接生成せず、階調電圧を生成する基準となる階調基準電圧のみを生成して出力することもできる。

【 0 0 7 6 】

図 10 に示した階調電圧生成部 900 は、一対のデジタルレジスター 911、912 を含むレジスター部 910、デジタルレジスター 911、912 に連結されている複数のマルチプレクサー  $MUX$  を含むデータ選択部 920、及びマルチプレクサー  $MUX$  に各々連結されている複数の D C - A C 変換器  $DAC$  を含む変換部 930 を含む。

二つのデジタルレジスター 911、912 は、互いに異なるデジタル階調データ集合  $1a - x_a$ 、 $1b - x_b$  を記憶し、二つの階調データ集合  $1a - x_a$ 、 $1b - x_b$  は、対をなして互いに対応する。

【 0 0 7 7 】

各マルチプレクサー  $MUX$  は、二つのデジタルレジスター 911、912 から対応する一対の電圧  $r_{1a} \cdot r_{1b}$ 、 $r_{2a} \cdot r_{2b}$ 、 $r_{xa} \cdot r_{xb}$  を入力で受け、選択信号  $SE$  によって二つのうちの一つを選択して出力する。

各 D C - A C 変換器  $DAC$  は、マルチプレクサー  $MUX$  からのデジタルデータをアナログ電圧  $r_1$ 、 $r_2$ 、 $r_x$  に変換して出力する。

【 0 0 7 8 】

図 11 に示した階調電圧生成部 900 は、一対の抵抗列 941、942 を含む電圧生成部 940 と、これに連結されているアナログマルチプレクサー  $AMUX$  950 を含む。

各抵抗列 941 は、複数の階調電圧からなる一つの階調電圧集合を生成し、二つの抵抗

10

20

30

40

50

列 9 4 1 の階調電圧は互いに異なる。

アナログマルチプレクサー 950 は、電圧生成部 940 から入力を受けた二対の階調電圧集合のうちで一対の階調電圧集合を選択信号 S E によって選択して出力する。

【 0 0 7 9 】

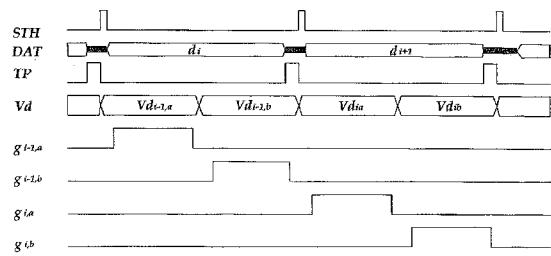

以下、図 9 乃至図 11 に示した液晶表示装置の動作について図 12 を参照して詳細に説明する。

図 12 は、図 9 乃至図 11 に示した液晶表示装置に使用される多様な信号の波形図である。

前述の実施形態で説明したように、信号制御部 600 は、入力画像信号 R、G、B と入力制御信号に基づいて画像信号 R、G、B を処理する。信号制御部 600 は、ゲート制御信号 C O N T 1、データ制御信号 C O N T 2、及び選択信号 S E などを生成した後、ゲート制御信号 C O N T 1 をゲート駆動部 430 に送出し、データ制御信号 C O N T 2 と処理した画像信号 D A T をデータ駆動部 500 に送出し、選択信号 S E は階調電圧生成部 900 に送出する。

10

【 0 0 8 0 】

ゲート制御信号 C O N T 1 は、走査開始信号 S T V と少なくとも一つのクロック信号を含み、出力イネーブル信号 O E をさらに含むことができる。データ制御信号 C O N T 2 は、水平同期開始信号 S T H、ロード信号 T P、及びデータクロック信号 H C L K を含み、反転信号 R V S をさらに含むことができる。

選択信号 S E は、階調電圧生成部 900 が生成した二つの階調電圧集合のうちのいずれか一つを選択することを指示する信号であって、水平同期開始信号 S T H、ロード信号 T P などと周期が同一である。

20

【 0 0 8 1 】

一方、前述でゲート制御信号のうちのクロック信号の周期は、水平同期開始信号 S T H の 2 倍であることができ、この場合、これを選択信号 S E として使用することができる。

信号制御部 600 からの水平同期開始信号 S T H パルスに応答して、データ駆動部 500 は、一束の画素 P X、例えば、i 番目画素行に対する画像データ d i をデータクロック信号 H C L K に合せて受信する。画像データ d i を受信する期間中、データ駆動部 500 は、以前画素行に対するデータ電圧をデータ線 D 1 - D m に印加する。画像データ d i の受信が終了すれば、階調電圧生成部 900 は、信号制御部 600 からの選択信号 S E によって決められた一つの階調（基準）電圧集合を出力し、データ駆動部 500 は、信号制御部 600 からのロード信号 T P のパルスによって、階調電圧生成部 900 からの階調電圧のうちで各画像データ d i に対応する階調電圧を選択することによって、画像データ d i を該当データ電圧に変換した後、これを該当データ線 D 1 - D m に印加する。

30

【 0 0 8 2 】

前述したように、階調電圧生成部 900 は階調基準電圧のみを提供する場合には、データ駆動部 500 は階調基準電圧を分圧して自ら階調電圧を生成することもできる。

ゲート駆動部 430 は、信号制御部 600 からのゲート制御信号 C O N T 1 によって、ゲートオン電圧 V o n をゲート線 G 1a - G n b、例えば、i 番目画素行の上側副画素 P X a に連結されたゲート線 G 1a に印加して、このゲート線 G 1a に連結されたスイッチング素子 Q a をターンオンさせ、そのためデータ線 D 1 - D m に印加されたデータ電圧が導通したスイッチング素子 Q a を介して該当副画素 P X a に印加される。

40

【 0 0 8 3 】

次に、信号制御部 600 は、選択信号 S E の値を変えて、階調電圧生成部 900 が異なる階調（基準）電圧集合を生成してデータ駆動部 500 に供給するようにする。これによって、データ駆動部 500 は、新たな階調電圧のうちで各画像データ d i に対応する階調電圧を再び選択し、これをデータ電圧として該当データ線 D 1 - D m に印加する。

ゲート駆動部 430 は、信号制御部 600 からのゲート制御信号 C O N T 1 によってゲートオン電圧 V o n を次のゲート線 G 1a - G n b、つまり、i 番目画素行の下側副画素 P X b に連結されたゲート線 G 1b に印加して、このゲート線 G 1b に連結されたスイッチング素子 Q b を介して該当副画素 P X b に印加される。

50

子  $Q_b$  をターンオンさせ、そのためデータ線  $D_1 - D_m$  に印加されたデータ電圧が導通したスイッチング素子  $Q_b$  を介して該当副画素  $P_Xb$  に印加される。

【0084】

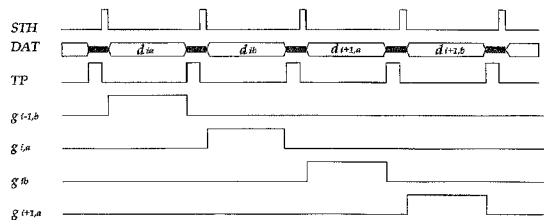

次に、図13及び図14を参照して本発明の他の実施形態による液晶表示装置について詳細に説明する。

図13は本発明の実施形態による液晶表示装置のブロック図であり、図14は図13に示す液晶表示装置に使用される多様な信号の波形図である。

図13を参照すれば、本発明の一実施形態による液晶表示装置は図9に示す液晶表示装置とほぼ同一な構造を有する。つまり、本実施形態による液晶表示装置は液晶表示板組立体300、ゲート駆動部440、データ駆動部500、階調電圧生成部800、及び信号制御部600を含む。

【0085】

但し、本実施形態の信号制御部600は別途に選択信号SEを生成することなく、階調電圧生成部800及びデータ駆動部500は画素の透過率に係る一つの（基準）階調電圧の集合のみを生成し、これを基準にデータ電圧を生成する。

その代わりに信号制御部600は一つの入力画像信号R、G、Bを一対の出力画像信号DATAa、DATbに変換して出力する。ここで、画像信号の変換は実験などによって予め決められて、ルックアップテーブル（図示せず）に記憶されているマッピング（mapping）を通じて行われるか信号制御部600の演算を通じて行われる。

【0086】

信号制御部600からの水平同期開始信号STH及びデータクロック信号HCLKによって、データ駆動部500は一組の副画素  $P_Xa$ 、 $P_Xb$ 、例えば、i番目の画素行の上側副画素  $P_Xa$  に対する画像データ  $d_{ia}$  を受信する。画像データ  $d_{ia}$  を受信する間、データ駆動部500は直前の画素行の下側副画素  $P_Xb$  に対するデータ電圧をデータ線  $D_1 - D_m$  に印加する。画像データ  $d_{ia}$  の受信が終われば、データ駆動部500は信号制御部600からのロード信号TPのパルスによって階調電圧生成部800からの階調電圧の中で各画像データ  $d_{ia}$  に対応する階調電圧を選択する。これによって画像データ  $d_{ia}$  を当該データ電圧に変換した後、これを当該データ線  $D_1 - D_m$  に印加する。

【0087】

ゲート駆動部440は信号制御部600からのゲート制御信号CONT1によってゲートオン電圧  $V_{on}$  をゲート線  $G_{1a} - G_{nb}$ 、例えば、i番目の画素行の上部ゲート線  $G_{ia}$  に印加して、このゲート線  $G_{ia}$  に連結されたスイッチング素子  $Q_a$  をターンオンさせる。これによってデータ線  $D_1 - D_m$  に印加されたデータ電圧がターンオンされたスイッチング素子  $Q_a$  を通じて当該副画素  $P_Xa$  に印加される。図14で、 $g_{ia}$ 、 $g_{ib}$  は各々i番目の画素行の上部及び下部ゲート線  $G_{ia}$ 、 $G_{ib}$  に印加されるゲート信号を示す。

【0088】

一方、信号制御部600はi番目の画素行の上側副画素  $P_Xa$  に対する画像データ  $d_{ia}$  の伝送を終えた後、i番目の画素行の下側副画素  $P_Xb$  に対する画像データ  $d_{ib}$  を水平同期信号STHの新たなパルスと共にデータ駆動部500に伝送する。その後、再びロード信号TPにパルスを与えてデータ駆動部500が再び階調電圧の中で各画像データ  $d_{ib}$  に対応する階調電圧を選択して、これをデータ電圧として当該データ線  $D_1 - D_m$  に印加するようとする。

【0089】

ゲート駆動部440は信号制御部600からのゲート制御信号CONT1によってゲートオン電圧  $V_{on}$  を次のゲート線  $G_{1a} - G_{nb}$ 、つまり、i番目の画素行の下部ゲート線  $G_{ib}$  に印加して、このゲート線  $G_{ib}$  に連結されたスイッチング素子  $Q_b$  をターンオンさせる。これによってデータ線  $D_1 - D_m$  に印加されたデータ電圧がターンオンされたスイッチング素子  $Q_b$  を通じて当該副画素  $P_Xb$  に印加される。

【0090】

前述のように、一つの入力画像データは一対の出力画像データに変換され、これらは一

対の副画素  $P_X a$ 、 $P_X b$  に互いに異なる透過率を付与する。したがって、図 7 a に示すように、二つの副画素  $P_X a$ 、 $P_X b$  は互いに異なるガンマ曲線  $T a$ 、 $T b$  を示し、一つの画素  $P_X$  のガンマ曲線はこれらを合成した曲線  $T$  になる。二つのガンマ曲線  $T a$ 、 $T b$  を決定する時には、合成ガンマ曲線  $T$  が正面での基準ガンマ曲線に近くなるようにする。

#### 【0091】

次に、本発明の他の実施形態による液晶表示装置について図 15 乃至図 18 を参照して詳細に説明する。

図 15 は本発明の他の実施形態による液晶表示装置のブロック図であり、図 16 は本発明の他の実施形態による液晶表示装置の一つの画素の等価回路図であり、図 17 a は本発明の一実施形態による液晶表示装置の概略的な画素配置及びデータ電圧の極性を示した図面であり、図 17 b は図 17 a に示す液晶表示装置における各副画素の極性を示した表であり、図 18 は図 17 a に示す液晶表示装置に使用される各種信号の波形図である。

#### 【0092】

図 15 乃至図 18 に示す液晶表示装置は、図 3 a に示す液晶表示装置とほぼ同一である。つまり、本実施形態による液晶表示装置は液晶表示板組立体 300、一対のゲート駆動部 440 a、440 b、データ駆動部 500、階調電圧生成部 800、及びこれらを制御する信号制御部 600 を含む。

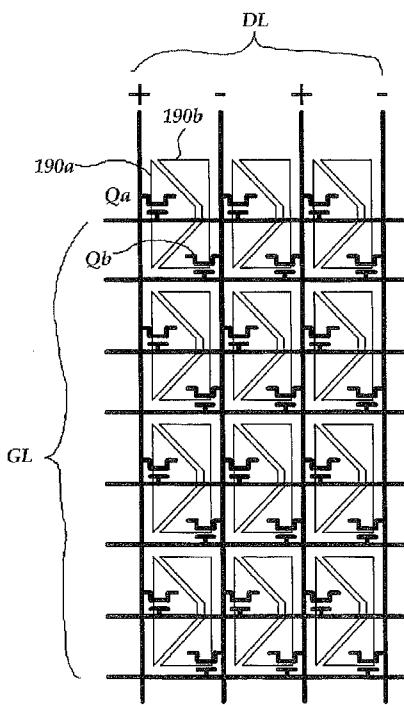

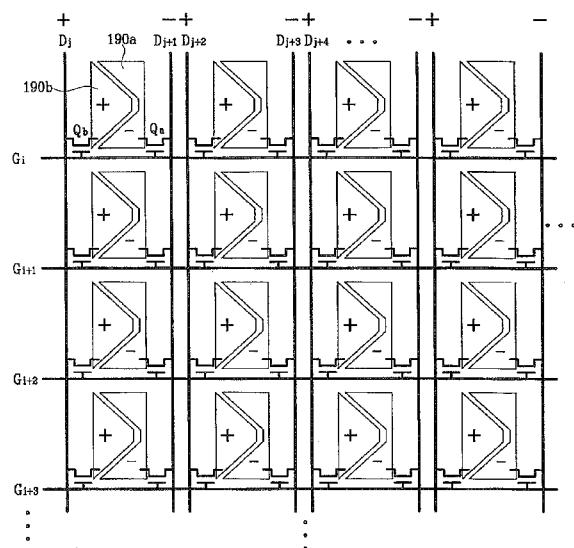

図 15 に示すように、液晶表示板組立体 300 は複数対のゲート線  $G_{1a} - G_{n_b}$ 、複数のデータ線  $D_0 - D_m$  及び複数の画素  $P_X$  を含み、データ線  $D_0 - D_m$  の数が図 3 a に示す液晶表示装置よりも一つ多い。

#### 【0093】

図 16 及び図 17 a に示すように、本実施形態による液晶表示装置の各画素  $P_X$  は二つの副画素  $P_X a$ 、 $P_X b$  を含む。二つの副画素  $P_X a$ 、 $P_X b$  のうちの一つ  $P_X a$  (以下、第 1 副画素という) は、上部ゲート線及び左側データ線に連結されたスイッチング素子  $Q a$  と液晶キャパシタ  $C_{1c a}$  及びストレージキャパシタ  $C_{s t a}$  を含む。液晶キャパシタ  $C_{1c a}$  を構成する副画素電極 190 a はほぼ三角形である。もう一つの副画素  $P_X b$  (以下、第 2 副画素という) は、下部ゲート線及び右側データ線に連結されたスイッチング素子  $Q b$  と液晶キャパシタ  $C_{1c b}$  及びストレージキャパシタ  $C_{s t b}$  を含む。液晶キャパシタ  $C_{1c b}$  を構成する副画素電極 190 b は第 1 副画素  $P_X a$  の副画素電極 190 a と噛み合って第 1 副画素  $P_X a$  の副画素電極 190 a と共にほぼ長方形をなす。

#### 【0094】

反転形態は列反転であって、図 17 b に示すように各画素  $P_X$  の第 1 副画素  $P_X a$  と第 2 副画素  $P_X b$  とは極性が反対である。列方向に隣接した画素  $P_X$  に対応する副画素  $P_X a$ 、 $P_X b$  は同一極性を有し、行方向に隣接した画素  $P_X$  に対応する副画素  $P_X a$ 、 $P_X b$  は反対極性を有する。

この時、図 18 に示すように、ゲート線の数が従来に比べて 2 倍に増えることによって充電時間が足りなくなる。これを補充するために、隣接した二つのゲート線にゲート信号  $g a$ 、 $g b$  を印加する時間を重畠することで事前充電を行うことができる。図 17 a の連結関係を見れば、第 1 副画素  $P_X a$  は上側画素行の左側画素  $P_X$  の第 2 副画素  $P_X b$  に印加されるデータ電圧で事前充電される。第 2 副画素  $P_X b$  は右側画素  $P_X$  の第 1 副画素  $P_X a$  のデータ電圧で事前充電される。ドット反転を行う場合には、一つのデータ線に印加される電圧の極性が変わるために事前充電が難しい反面、列反転の場合には事前充電が容易である。図 18 で  $V d$  は特定のデータ線に印加されるデータ電圧を意味し、 $V p a$  は第 1 副画素の画素電圧、 $V p b$  は第 2 副画素の画素電圧を意味する。

#### 【0095】

このように一つの画素の副画素を互いに異なるデータ線に連結してデータ駆動部 500 で列反転を行えば、副画素を基準に見る時にはドット反転と同一な形態になるので、列反転の長所とドット反転の長所を両方有するようになる。

また、各画素の形態が完全に同一なので、前述した開口率などのいろんな問題が発生しない。

10

20

30

40

50

## 【0096】

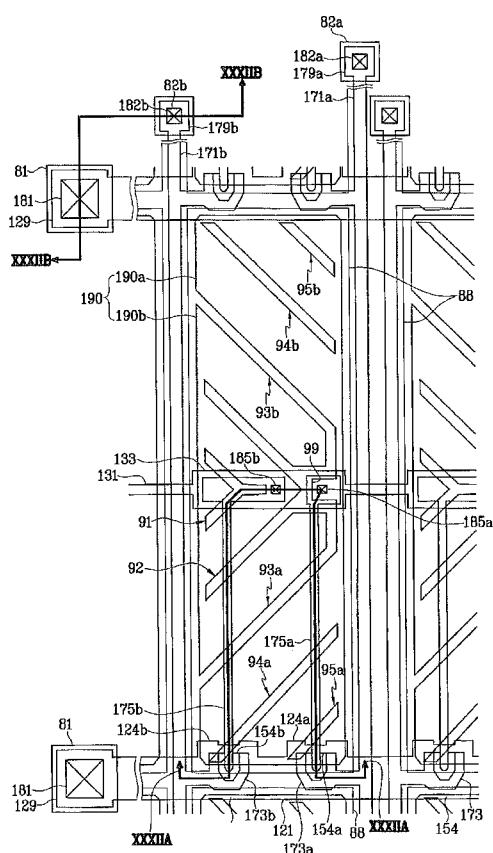

以下、前述した液晶表示板組立体の例について図19乃至図24を参照して詳細に説明する。

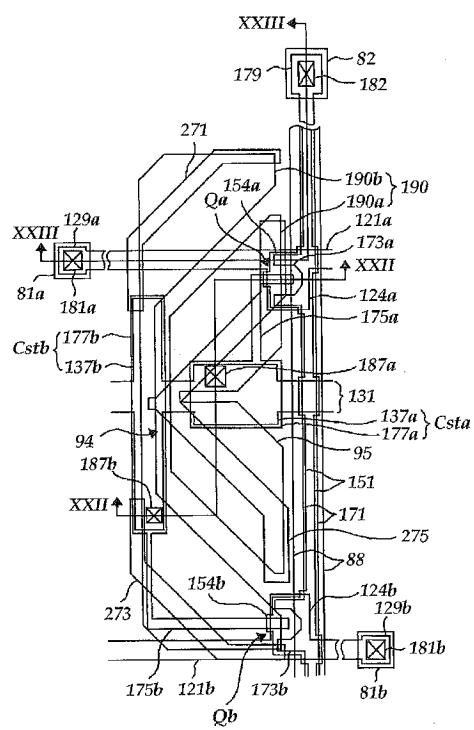

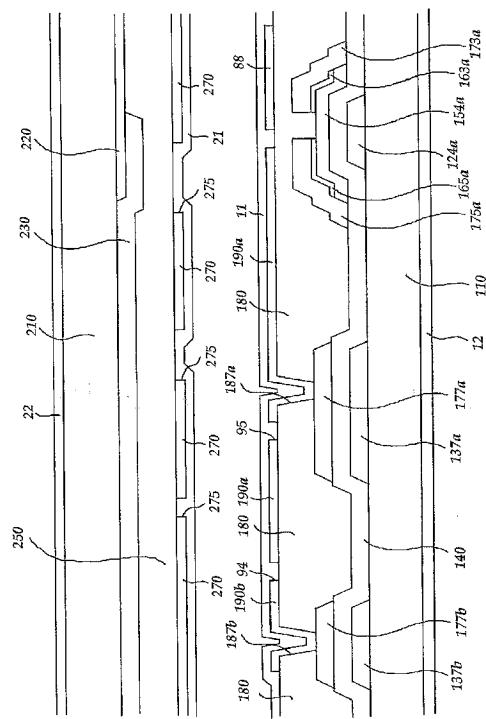

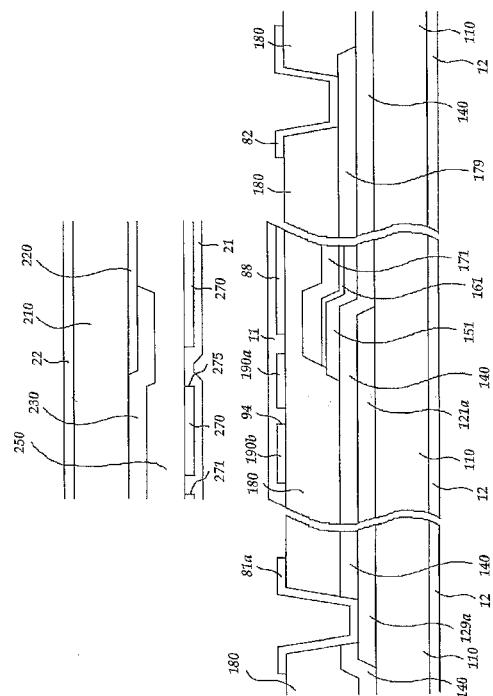

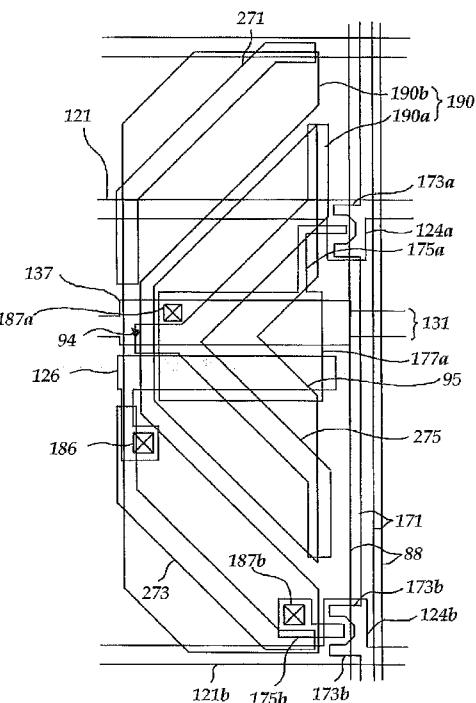

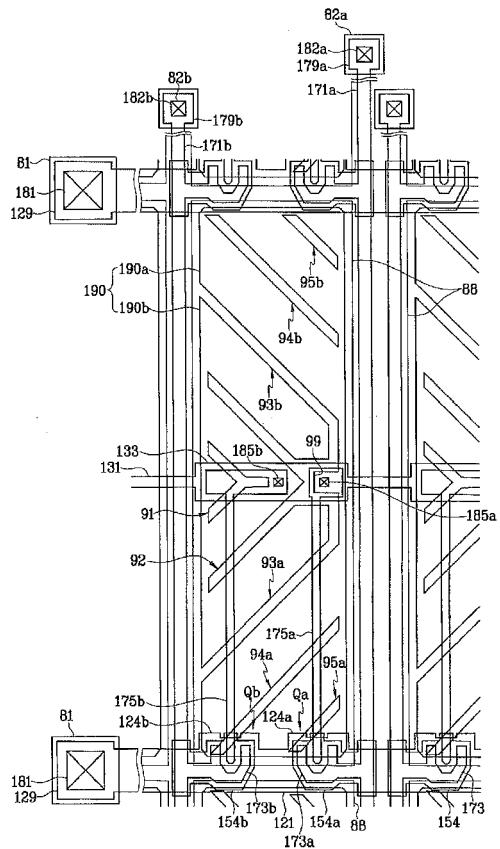

図19は本発明の一実施形態による下部表示板の配置図であり、図20は本発明の一実施形態による上部表示板の配置図であり、図21は図19の下部表示板及び図20の上部表示板を含む液晶表示板組立体の配置図であり、図22及び図23は各々図21の液晶表示板組立体をX X I I - X X I I線及びX X I I I - X X I I I線に沿って切断した断面図であり、図24は本発明の他の実施形態による液晶表示板組立体の配置図である。図19乃至図23は図4aに示す液晶表示装置の液晶表示板組立体の一例であり、図24は図4bに示す液晶表示装置の液晶表示板組立体の一例である。

10

## 【0097】

以下、図19乃至図23に示す液晶表示板組立体を主に説明するが、図24に示す液晶表示板組立体については異なる部分だけ説明する。

図19乃至図23を参照すれば、本実施形態による液晶表示板組立体300は下部表示板100、これと対向している上部表示板200及びこれらの間に入っている液晶層3を含む。

## 【0098】

まず、図19、図21乃至図23及び図24を参照して下部表示板100について詳細に説明する。

透明なガラスまたはプラスチックなどで作られた絶縁基板110上に複数対の第1及び第2ゲート線121a、121bと複数の維持電極線131が形成されている。図24の場合には基板110上にまた複数の結合電極126が形成されている。

20

## 【0099】

ゲート線121a、121bはゲート信号を伝達し、主に横方向に延在して物理的、電気的に互いに分離されている。第1及び第2ゲート線121a、121bは各々上側及び下側に配置されており、上下に突出した複数の第1及び第2ゲート電極124a、124bと他の層または外部駆動回路との連結のために面積が広く、各々左側及び右側に配置されている端部129a、129bを含む。しかし、これら端部129a、129bは二つとも左側または右側に配置されることもできる。ゲート信号を生成するゲート駆動回路(図示せず)は基板110上に付着される可撓性印刷回路膜(図示せず)上に装着されるか、基板110上に直接装着されるか、基板110に集積される。ゲート駆動回路が基板110上に集積されている場合、ゲート線121が延在してこれと直接連結されることもできる。

30

## 【0100】

維持電極線131は共通電圧など所定の電圧の印加を受けて、ゲート線121a、121bと並んで延在した分岐と、これから分かれた複数対の第1及び第2維持電極137a、137bを含む。維持電極線131各々は第1ゲート線121aと第2ゲート線121bとの間に位置し、第2ゲート線121bより第1ゲート線121aの方に近い。

第1維持電極137aは第2維持電極137bに比べて長さは長くて幅は狭い。その反面、図24に示す維持電極線131は第1維持電極137aとほぼ対応する一つの維持電極137だけを含む。しかし、維持電極137a、137b、137をはじめとする維持電極線131の形態及び配置は多様に変更できる。

40

## 【0101】

図24の結合電極126は維持電極137と隣接して並んで延在しており、他の層との接続のために下に延在して拡張された突出部を有している。

ゲート線121及び維持電極線131はアルミニウム(A1)やアルミニウム合金などアルミニウム系金属、銀(Ag)や銀合金など銀系金属、銅(Cu)や銅合金など銅系金属、モリブデン(Mo)やモリブデン合金などモリブデン系金属、クロム(Cr)、タンタル(Ta)及びチタニウム(Ti)などで作られることができる。しかし、これらは物理的性質が異なる二つの導電膜(図示せず)を含む多重膜構造を有することもできる。こ

50

のうちの一つの導電膜は信号遅延や電圧降下を減らすことができるように比抵抗の低い金属、例えば、アルミニウム系金属、銀系金属、銅系金属などで作る。これとは違って、他の導電膜は他の物質、特にITO(indium tin oxide)及びIZO(indium zinc oxide)との物理的、化学的、電気的接触特性に優れている物質、例えばモリブデン系金属、クロム、タンタル、チタニウムなどで作る。このような組み合わせの良い例としては、クロム下部膜とアルミニウム(合金)上部膜、及びアルミニウム(合金)下部膜とモリブデン(合金)上部膜などが挙げられる。しかし、ゲート線121及び維持電極線131は、その他にも多様な金属または導電体で作ることができる。

#### 【0102】

ゲート線121と維持電極線131の側面は、基板110の表面に対して傾斜しており、その傾斜角は約30°～約80°であるのが好ましい。

ゲート線121a、121b及び維持電極線131上には窒化ケイ素(SiNx)または酸化ケイ素(SiOx)などで構成されるゲート絶縁膜140が形成されている。

ゲート絶縁膜140上には水素化非晶質シリコン(非晶質シリコンは略称a-Siという)または多結晶シリコンなどで構成される複数の線状半導体151が形成されている。線状半導体151は主に縦方向に延在しており、第1及び第2ゲート電極124a、124bに向かって各々のび出た複数の第1及び第2突出部154a、154bを含む。また、線状半導体151はゲート線121a、121b及び維持電極線131と合う地点付近で幅が広くなっている。

#### 【0103】

半導体151上には複数の線状及び島状抵抗性接触部材161、165aが形成されている。抵抗性接触部材161、165aはシリサイドまたはn型不純物が高濃度にドーピングされているn+水素化非晶質シリコンなどの物質で作られる。線状接触部材161は複数の突出部163aを有しており、この突出部163aと島状接触部材165aは対をなして半導体151の突出部154a上に位置する。

#### 【0104】

一方、図示していないが、半導体151の第2突出部154b上にも線状接触部材161の突出部と島状接触部材が対をなして備えられている。

半導体151と抵抗性接触部材161、165aの側面もまた基板110の表面に対して傾斜しており、その傾斜角は30°～80°程度である。

抵抗接触部材161、165a及びゲート絶縁膜140上には、複数のデータ線171と複数対の第1及び第2ドレイン電極175a、175bが形成されている。

#### 【0105】

データ線171はデータ電圧を伝達し、主に縦方向に延在してゲート線121及び維持電極線131と交差する。各データ線171は第1及び第2ゲート電極124a、124bに向かって各々延在してC字形に曲がった複数の第1及び第2ソース電極173a、173bと他の層または外部装置との接続のための広い端部179を含む。データ電圧を生成するデータ駆動回路(図示せず)は、基板110上に付着される可撓性印刷回路膜(図示せず)上に装着されるか、基板110上に直接装着されるか、基板110に集積される。データ駆動回路が基板110上に集積されている場合、データ線171が延在してこれと直接連結されることもできる。

#### 【0106】

第1及び第2ドレイン電極175a、175bはデータ線171と分離されており、各々第1及び第2ゲート電極124a、124bを中心にソース電極173a、173bと対向する。第1及び第2ドレイン電極175a、175b各々は、広い一端部177a、177b及び棒状であるもう一方の端部を含む。広い端部は第1及び第2維持電極131a、131bと重畳し、棒状である端部は半導体151の第1及び第2突出部154a、154b上に位置し、第1及び第2ソース電極173a、173bで一部囲まれている。しかし、図24の第2ドレイン電極175bは長く延在されず短く延在しており、第1ド

10

20

30

40

50

レイン電極 175a は維持電極 137 及び結合電極 126 と重畳する。

【0107】

第 1 / 第 2 ゲート電極 124a / 124b、第 1 / 第 2 ソース電極 173a / 173b 及び第 1 / 第 2 ドレイン電極 175a / 175b は半導体 151 の第 1 / 第 2 突出部 154a / 154b 及び第 1 / 第 2 ドレイン電極 175a / 175b と共に第 1 / 第 2 薄膜トランジスタ (TFT) Qa / Qb を構成する。薄膜トランジスタ Qa / Qb のチャンネルは第 1 / 第 2 ソース電極 173a / 173b 及び第 1 / 第 2 ドレイン電極 175a / 175b との間の突出部 154a / 154b に形成される。

【0108】

データ線 171 及びドレイン電極 175a、175b はモリブデン、クロム、タンタル及びチタニウムなど耐火性金属またはこれらの合金で作ることが好ましく、耐火性金属膜 (図示せず) 及び低抵抗導電膜 (図示せず) を含む多重膜構造を有することができる。多重膜構造の例としては、クロムまたはモリブデン (合金) 下部膜とアルミニウム (合金) 上部膜の二重膜、モリブデン (合金) 下部膜とアルミニウム (合金) 中間膜とモリブデン (合金) 上部膜の三重膜などが挙げられる。しかし、データ線 171 及びドレイン電極 175a、175b は、その他にも多様な金属または導電体で作ることができる。

【0109】

データ線 171 及びドレイン電極 175a、175b もまた基板 110 の表面に対して傾斜しており、その傾斜角は 30° ~ 80° 程度であるのが好ましい。

抵抗性接触部材 161、165a はその下部の半導体 151 とその上部のデータ線 171 及びドレイン電極 175a、175b の間にだけ存在して接触抵抗を低くする。殆どの所では線状半導体 151 がデータ線 171 より狭いが、既に説明したようにゲート線 121a、121b 及び維持電極線 131 と合う部分で幅が広くなって表面のプロファイルをスムースにすることによってデータ線 171 の断線を防止する。線状半導体 151 にはソース電極 173a、173b 及びドレイン電極 175a、175b の間にをはじめ、データ線 171 及びドレイン電極 175a、175b で覆われず露出された部分がある。

【0110】

データ線 171 及びドレイン電極 175a、175b と半導体 151 の露出された部分の上には保護膜 180 が形成されている。保護膜 180 は無機絶縁物または有機絶縁物などで作られて表面が平坦であり得る。無機絶縁物の例としては、窒化ケイ素及び酸化ケイ素が挙げられる。有機絶縁物は感光性を有することができ、その誘電常数は約 4.0 以下であるのが好ましい。しかし、保護膜 180 は有機膜の優れる絶縁特性を生かしながらも半導体 151 の露出された部分には害を及ぼさないように、下部無機膜と上部有機膜との二重膜構造を有することができる。

【0111】

保護膜 180 にはデータ線 171 の端部 179 及びドレイン電極 175a、175b の広い端部 177a、177b を各々露出する複数の接触孔 182、187a、187b が形成されており、保護膜 180 及びゲート絶縁膜 140 にはゲート線 121a、121b の端部 129a、129b を露出する複数の接触孔 181a、181b が形成されている。図 24 の場合、保護膜 180 及びゲート絶縁膜 140 には結合電極 126 の端部 129a、129b を露出する複数の接触孔 186 が形成されている。

【0112】

保護膜 180 上には第 1 及び第 2 副画素電極 190a、190b を各々含む複数の画素電極 190、複数の遮蔽電極 88 及び複数の接触補助部材 81a、81b、82 が形成されている。画素電極 190 及び接触補助部材 81a、81b、82 はITO またはIZO などの透明導電体またはアルミニウム、銀、クロムまたはその合金などの反射性導電体で作る。

【0113】

第 1 / 第 2 副画素電極 190a / 190b は接触孔 187a / 187b を通じて第 1 / 第 2 ドレイン電極 175a / 175b と物理的・電気的に連結されて、第 1 / 第 2 ドレイン電極 175a / 175b からデータ電圧の印加を受ける。図 24 の場合、第 2 副画素電

10

20

30

40

50

極 190b は接触孔 186 を通じて結合電極 126 と連結されており、第 1 副画素電極 190a は結合電極 126 と重畠する。

【0114】

データ電圧が印加された副画素電極 190a、190b は共通電極 270 と共に電場を生成することによって二つの電極 190、270 の間の液晶層 3 の液晶分子の配列を決定する。

また、前述したように、各副画素電極 190a、190b 及び共通電極 270 は液晶キャパシタ C1ca、C1cb を構成して薄膜トランジスタ Qa、Qb がターンオフされた後にも印加された電圧を維持する。電圧維持能力を強化するために液晶キャパシタ C1ca、C1cb と並列に連結されたストレージキャパシタ Csta、Cstb は、第 1 及び第 2 副画素電極 190a、190b 及びこれに連結されているドレイン電極 175a、175b と第 1 及び第 2 維持電極 137a、137b の重畠などで作られる。10

【0115】

各画素電極 190 は左側角部が面取りされており、面取りされた斜辺はゲート線 121a、121b に対して約 45° の角度を構成する。

一つの画素電極 190 をなす一対の第 1 及び第 2 副画素電極 190a、190b は間隙 94 を間に置いて互いに噛み合っており、その外側境界はほぼ四角形である。第 1 副画素電極 190a は回転した等辺台形であって、第 2 維持電極 137b の付近に位置した左辺とその向い側の右辺、そしてゲート線 121a、121b とほぼ 45° を構成する上の斜辺及び下の斜辺を有する。第 2 副画素電極 190b は第 1 副画素電極 190a の斜辺と対向する一対の台形部及び第 1 副画素電極 190a の左辺と対向する縦部を含む。従って、第 1 副画素電極 190a と第 2 副画素電極 190b との間の間隙 94 は、ほぼ均一な幅を有し、ゲート線 121a、121b と約 45° を構成する上部及び下部斜線部 91、93 と実質的に均一な幅を有する縦部 92 を含む。20

【0116】

第 1 副画素電極 190a は維持電極線 131 に沿って延在した切開部 95 を有し、この切開部 95 によって上半部及び下半部に二等分される。切開部 95 は第 1 副画素電極 190a の右辺に入口を有している。切開部 95 の入口は間隙 94 の上部斜線部 91 及び下部斜線部 93 と各々実質的に平行な一対の斜辺を有している。間隙 94 及び切開部 95 は維持電極線 131 に対してほぼ反転対称をなす。30

【0117】

この時、分けられた部分の数または切開部の数は画素の大きさ、画素電極 190 の横辺と縦辺との長さ比、液晶層 3 の種類や特性など設計要素によって変わる。以下、説明の便宜のために間隙 94 も切開部であると表現する。

また、第 1 副画素電極 190a は第 1 ゲート線 121a と重畠し、第 2 副画素電極 190b は第 1 及び第 2 ゲート線 121a、121b 全てと重畠し、第 1 ゲート線 121a は画素電極 190 の上半部中心辺りを通過する。

【0118】

遮蔽電極 88 はデータ線 171 に沿って延在しており、データ線 171 を完全に覆う。遮蔽電極 88 には共通電圧が印加されるが、このために保護膜 180 及びゲート絶縁膜 140 の接触孔（図示せず）を通じて維持電極線 131 に連結されるか、薄膜トランジスタ表示板 100 から共通電極表示板 200 に共通電圧を伝達する短絡点（図示せず）に連結されることもできる。この時、開口率の減少が最少になるように遮蔽電極 88 と画素電極 190 との間の距離を最少にするのが好ましい。40

【0119】

このように共通電圧が印加される遮蔽電極 88 をデータ線 171 の上部に配置すれば、遮蔽電極 88 がデータ線 171 と画素電極 190 との間、及びデータ線 171 と共通電極 270 との間で形成される電界を遮断して画素電極 190 の電圧歪曲やデータ線 171 が伝達するデータ電圧の信号遅延が減少する。

また、画素電極 190 及び遮蔽電極 88 の短絡を防止するためにこれらの間に距離を置

かなければならぬので、画素電極 190 がデータ線 171 からもっと遠くなつてこれらの間の寄生容量が減少する。さらに、液晶層 3 の誘電率が保護膜 180 の誘電率より高いので、データ線 171 と遮蔽電極 88 との間の寄生容量が遮蔽電極 88 がない場合のデータ線 171 と共通電極 270 との間の寄生容量に比べて小さい。

#### 【0120】

それだけでなく、画素電極 190 及び遮蔽電極 88 が同一層で作られるので、これらの間の距離が一定に維持され、そのためにこれらの間の寄生容量が一定である。画素電極 190 とデータ線 171 との間の寄生容量が依然として分割露光過程で分割された露光領域によって変わることもあるが、画素電極 190 とデータ線 171 との間の寄生容量が相対的に減少するので、全体の寄生容量はほぼ一定であるといえる。従つて、ステッチ欠陥を 10 最少化することができる。

#### 【0121】

接触補助部材 81a、81b、82 は接触孔 181a、181b、182 を通じてゲート線 121a、121b の端部 129a、129b 及びデータ線 171 の端部 179 と各々連結される。接触補助部材 81a、81b、82 はゲート線 121a、121b の端部 129a、129b 及びデータ線 171 の各端部 179 と外部装置との接着性を補完してこれらを保護する役割を果たす。

#### 【0122】

ゲート駆動部 400a、400b またはデータ駆動部 500 が組立体 300 上に集積される場合には、ゲート線 121a、121b またはデータ線 171 が延在してこれらと直接連結されることもできる。この場合には、接触補助部材 81a、81b、82 がゲート線 121a、121b またはデータ線 171 とこれら駆動部 400a、400b、500 を連結するなどに用いられる。

#### 【0123】

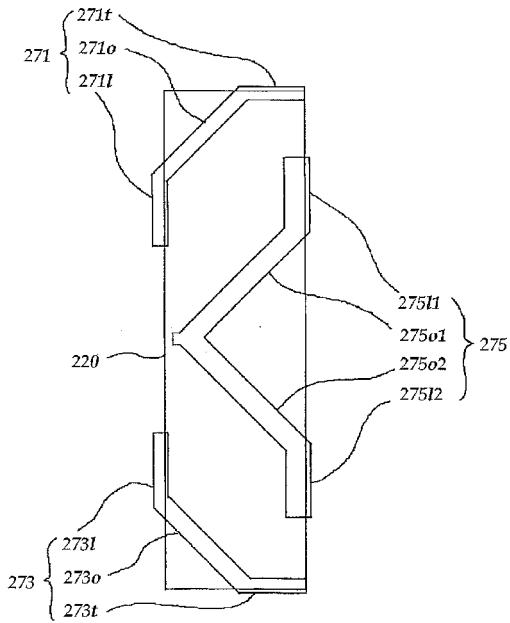

次に、図 20 乃至図 24 を参照して上部表示板 200 について説明する。

透明なガラスまたはプラスチックなどで作られた絶縁基板 210 上に光漏れを防止するためのブラックマトリックスという遮光部材 220 が形成されている。遮光部材 220 は画素電極 190 と対向して画素電極 190 とほぼ同一な形態を有する複数の開口部を有している。これとは違つて、遮光部材 220 はデータ線 171 に対応する部分及び薄膜トランジスタに対応する部分で構成されることもできる。しかし、遮光部材 220 は画素電極 190 及び薄膜トランジスタ Qa、Qb 付近での光漏れを遮断するために多様な形態を有することができる。

#### 【0124】

基板 210 上にはまた複数のカラーフィルタ 230 が形成されている。カラーフィルタ 230 は遮光部材 220 で囲まれた領域内にほとんど位置し、画素電極 190 に沿つて縦方向に長く延在することができる。カラーフィルタ 230 は赤色、緑色、及び青色などの基本色のうちの一つを表示することができる。

カラーフィルタ 230 及び遮光部材 220 上には、カラーフィルタ 230 が露出されることを防止し、平坦面を提供するための蓋膜 250 が形成されている。

#### 【0125】

蓋膜 250 の上には ITO、IZO などの透明な導電体などで構成される共通電極 270 が形成されている。

共通電極 270 は複数の切開部 271、273、275 の集合を有する。

一つの切開部の集合 271、273、275 は一つの画素電極 190 と対向して上部切開部 271、中央切開部 272、及び下部切開部 273 を含む。切開部 271、273、275 各々は画素電極 190 の隣接切開部 94、95 の間または切開部 94 と画素電極 190 の斜辺との間に配置されている。また、各切開部 271、273、275 は間隙 94 の上部斜線部 91 または下部斜線部 93 と平行に延在した少なくとも一つの斜線部 271o、273o、275o1、275o2 を含み、維持電極線 131 に対してほぼ反転対称である。

10

20

30

40

50

## 【0126】

上部及び下部切開部 271、273 各々はほぼ画素電極 190 の左側辺で上側または下側辺に向かって延在した斜線部 2710、2730、そして斜線部 2710、2730 の各端から画素電極 190 の辺に沿って辺と重畠しながら延在して斜線部 2710、2730 と鈍角をなす横部 271t、273t 及び縦部 2711、2731 を含む。

中央切開部 275 はほぼ画素電極 190 の左側辺中央から斜めに画素電極 190 の右側辺に向かって延在した一対の斜線部 27501、27502、そして斜線部 27501、27502 の各端から画素電極 190 の右側辺に沿って右側辺と重畠しながら延在して斜線部 27501、27502 と鈍角をなす縦部 27511、27512 を含む。

## 【0127】

切開部 271、273、275 の数爻は設計要素によって変わることがあって、遮光部材 220 が切開部 271、273、275 と重畠して切開部 271、273、275 付近の光漏れを遮断することができる。

表示板 100、200 の内側面には配向膜 (alignement layer) 11、21 が塗布されていてこれらは垂直配向膜であり得る。

## 【0128】

表示板 100、200 の外側面には偏光子 (polarizer) 12、22 が備えられているが、二つの偏光子 12、22 の偏光軸は直交して切開部 94、95 及び切開部 271、273、275 の斜線部とほぼ 45° の角度をなすのが好ましい。反射型液晶表示装置の場合には二つの偏光子 12、22 のうちの一つを省略できる。

本実施例による液晶表示板組立体は液晶層 3 の遅延を補償するための位相遅延膜 (retardation film) (図示せず) をさらに含むことができる。液晶表示板組立体はまた、偏光子 12、22、位相遅延膜、表示板 100、200 及び液晶層 3 に光を供給する照明部 (backlight unit) (図示せず) を含むことができる。

## 【0129】

液晶層 3 は負の誘電率異方性を有し、液晶分子は電界がない時その長軸が二つの表示板 100、200 の表面に対して実質的に垂直をなすように配向されている。したがって、入射光は直交偏光子 12、22 を通過できず、遮断される。

共通電極 270 に共通電圧を印加して画素電極 190 にデータ電圧を印加すれば表示板 100、200 の表面にほとんど垂直である電場 (電界) が生成される。[ここからは画素電極 190 と共通電極 270 をひっくるめて電場生成電極という。] 液晶分子は電場に応答してその長軸が電場の方向に垂直をなすように方向を変えようとする。

## 【0130】

電場生成電極 190、270 の切開部 94、95、271、273、275 と画素電極 190 の辺は電場を歪曲して液晶分子の傾斜方向を決定する水平成分を作りだす。電場の水平成分は切開部 94、95、271、273、275 の辺と画素電極 190 の辺にほとんど垂直である。

そのために電場は表示板 100、200 の表面に垂直である方向に対して傾いた方向を指す。液晶分子は電場に応答してその長軸が電場の方向に垂直をなすように方向を変えようとするが、この時切開部 94、95、271、273、275 及び画素電極 190 の辺付近の電場は液晶分子の長軸方向と並んでいなく一定の角度をなしているので液晶分子の長軸方向と電場がなす平面上で移動距離が短い方向に液晶分子が回転する。

## 【0131】

図 21 を参考にすれば、一つの切開部集合 94、95、271、273、275 は画素電極 190 を複数の副領域 (sub-area) に分け、各副領域は画素電極 190 の主辺と斜角をなす二つの主辺 (primary edge) を有する。各副領域の主辺は偏光子 12、22 の偏光軸と約 45° をなし、これは光効率を最大にするためである。

各副領域上の液晶分子はほとんど主辺に垂直である方向に傾くので、傾く方向を選び出せば、ほぼ四つの方向である。このように液晶分子が傾く方向を多様にすると液晶表示装置の基準視野角が大きくなる。

10

20

30

40

50

## 【0132】

切開部 94、95、271、273、275 の模様及び配置は多様に変更することができる。

少なくとも一つの切開部 94、95、271、273、275 は突起 (protrusion) (図示せず) や陥没部 (depression) (図示せず) に代替することができる。突起は有機物または無機物で作ることができて電場生成電極 190、270 の上のまたは下に配置される。

## 【0133】

では本発明の他の実施例による液晶表示装置に対して図 25 及び図 26 を参照して説明する。

図 25 は本発明の実施例による液晶表示装置のブロック図であり、図 26 は本発明の実施例による液晶表示装置の一つの画素に対する等価回路図である。

図 25 に示したように、本発明の一つの実施例による液晶表示装置も液晶表示板組立体 300、ゲート駆動部 490、データ駆動部 590、階調電圧生成部 800 及び信号制御部 600 を含む。

## 【0134】

図 25 に示したように、液晶表示板組立体 300 は複数のゲート線  $G_1 - G_n$ 、複数対のデータ線  $D_{1-2m}$  及び複数の画素  $P_X$  を含み、ゲート線  $G_1 - G_n$  の数爻が以前の実施例より少ない代わりにデータ線  $D_{1-2m}$  の数爻が以前の実施例の 2 倍である。一対のデータ線  $D_{1-2m}$  は一つの画素列を中心に左右に位置する。

図 25 及び図 26 に示したように本実施例による液晶表示装置の各画素  $P_X$  は二つの副画素  $P_Xa$ 、 $P_Xb$  を含む。二つの副画素  $P_Xa$ 、 $P_Xb$  のうちの一つ  $P_Xa$  (以下、第 1 副画素とする) はゲート線及び右側データ線に連結されたスイッチング素子  $Qa$  と液晶キャパシタ  $C_{1ca}$  及びストレージキャパシタ  $C_{sta}$  を含み、他の副画素  $P_Xb$  (以下、第 2 副画素とする) はゲート線及び左側データ線に連結されたスイッチング素子  $Qb$  と液晶キャパシタ  $C_{1cb}$  及びストレージキャパシタ  $C_{stb}$  を含む。

## 【0135】

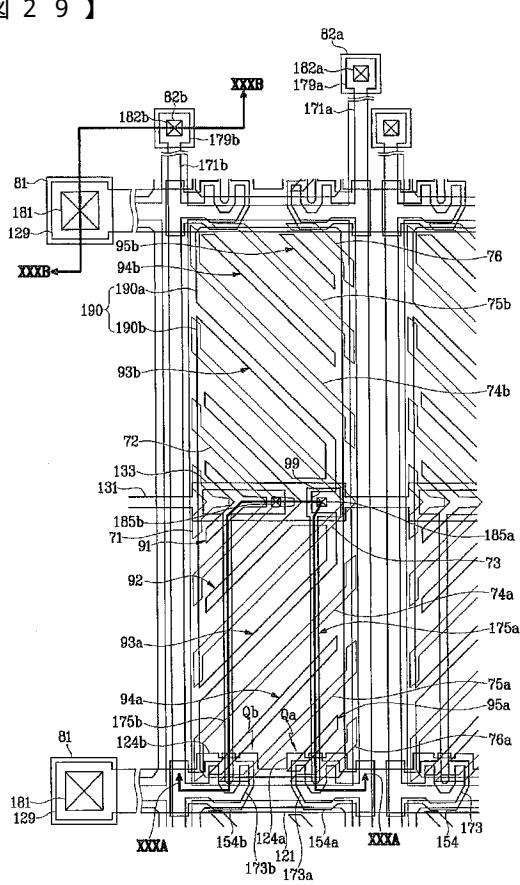

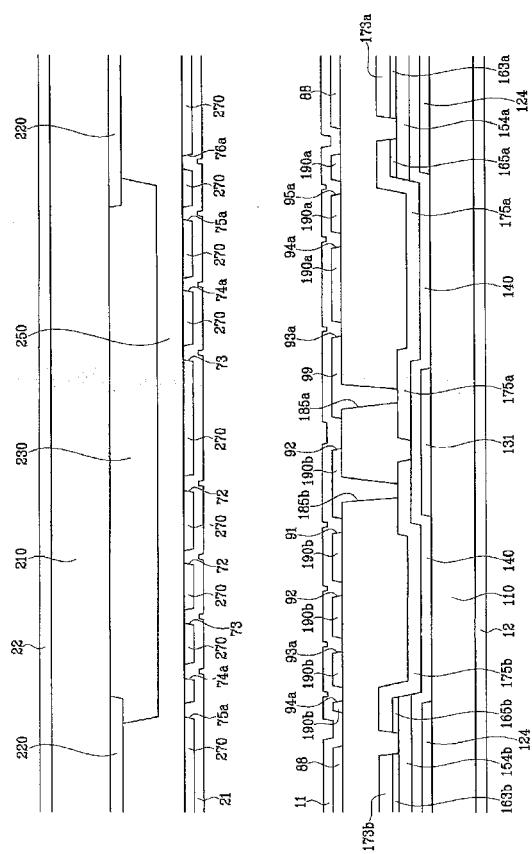

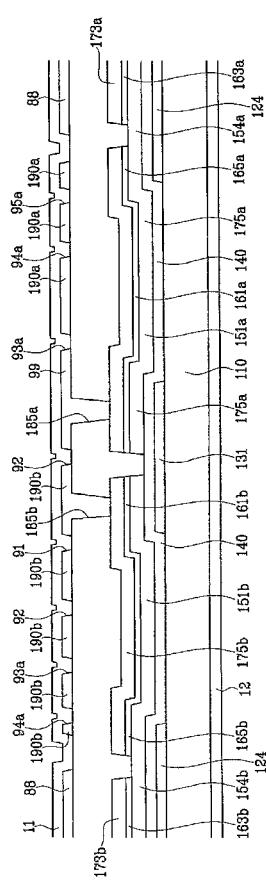

以下、このような図 25 及び図 26 に示した液晶表示装置の例に対し図 27 乃至図 30b を参照して詳細に説明する。

図 27 は本発明の一つの実施例による液晶表示板組立体用薄膜トランジスタ表示板の配置図であり、図 28 は本発明の一つの実施例による液晶表示板組立体用共通電極表示板の配置図であり、図 29 は図 27 の薄膜トランジスタ表示板と図 28 の共通電極表示板を含む液晶表示板組立体の配置図であり、図 30a 及び図 30b は各々図 29 の液晶表示板組立体を  $XXXa-XXXa$  線及び  $XXXb-XXXb$  線に沿って切断した断面図である。

## 【0136】

まず、図 27、図 30a 及び図 30b を参照して薄膜トランジスタ表示板 100 に対して詳細に説明する。

透明なガラスなどからなる絶縁基板 110 上に複数のゲート線 121 と複数の維持電極線 131 が形成されている。各ゲート線 121 は複数のゲート電極 (gate electrode) 124 と広い端部 129 を含む。それぞれの維持電極線 131 は下上に拡張された長方形の維持電極 133 を含む。維持電極線 131 は隣接した二つのゲート線 121 の間に位置し、二つのゲート線 121 からほぼ等距離である。

## 【0137】

ゲート線 121 及び維持電極線 131 上にはゲート絶縁膜 (gate insulating layer) 140 が形成されている。

ゲート絶縁膜 140 上には複数の島型半導体 154a、154b が形成されている。それぞれの島型半導体 154a、154b は主にゲート電極 124 の上部に位置する。

半導体 154a、154b 上には各々複数の島型抵抗性接触部材 (ohmic contact) 163a、163b、165a、165b が形成されている。二つの島型抵抗性接触部材 163a、163b、165a、165b は対をなして半導体 154a、154b

10

20

30

40

50

4 b 上に各々配置されていて、ゲート電極 124 を中心に互いに対向する。

【0138】

抵抗接触部材 163a、163b、165a、165b 及びゲート絶縁膜 140 上には複数対のデータ線 (data line) 171a、171b と複数のドレーン電極 (drain electrode) 175a、175b が形成されている。

各データ線 171a、171b は U 字型のソース電極 (source electrode) 173a、173b と広い端部 179a、179b を含む。各ドレーン電極 175a、175b は広い端部と棒状端部を含み、広い端部は維持電極 133 と重畳する。ドレーン電極 175a、175b の拡張部の辺は維持電極 133 の辺と実質的に平行する。

【0139】

データ線 171a、171b 及びドレーン電極 175a、175b と露出された半導体 154a、154b 部分の上には保護膜 (passivation layer) 180 が形成されている。

保護膜 180 にはドレーン電極 175a、175b 及びデータ線 171a、171b の端部 179a、179b を各々露出する複数の接触孔 (contact hole) 185a、185b、182a、182b が形成されており、保護膜 180 とゲート絶縁膜 140 にはゲート線 121 の端部 129 を露出する複数の接触孔 181 が形成されている。

【0140】

保護膜 180 上には第 1 及び第 2 副画素電極 190a、190b を各々含む複数の画素電極 190 と複数の遮蔽電極 (shielding electrode) 88 及び複数の接触補助部材 (contact assistant) 81、82a、82b が形成されている。

第 2 副画素電極 190b の面積は第 1 副画素電極 190a の面積より大きくて、約 2:1 の面積比を有するのが好ましい。低いデータ電圧、つまり、低階調のデータ電圧の印加で副画素 PXb の液晶分子は副画素 PXa の液晶分子より相対的に側面視認性に影響をあまり与えない初期状態程度の配列を維持するので、この副画素電極 190b の面積が広くなることによって側面視認性が向上する。特に、第 2 副画素電極 190b と第 1 副画素電極 190a の面積比が約 2:1 である場合、側面視認性に最も効果的である。

【0141】

一对の第 1 及び第 2 副画素電極 190a、190b はデータ線 171a、171b 及びゲート線 121 で囲まれた領域内にほとんど存在して境界のほとんどがゲート線 121 及びデータ線 171a、171b と平行して長方形をなす。第 1 及び第 2 副画素電極 190a、190b は互いに分離されていて、第 1 副画素電極 190a は第 2 副画素電極 190b を中心に上部及び下部に位置して互いに連結されている二つの部分からなっていて、第 2 副画素電極 190b は第 1 副画素電極 190a の二つの部分の間に挟まれて、第 1 及び第 2 画素電極 190a、190b は互いに噛み合った形態である。

【0142】

第 1 及び第 2 画素電極 190a、190b の四つの角は面取りされていて、面取りされた斜辺はゲート線 121 に対して約 45° の角度をなす。各第 2 画素電極 190b の右側二つの角部は残り二つの角部より長い斜辺を有していて、中心付近から左に拡張された拡張部を有している。

一对の第 1 及び第 2 副画素 190a、190b は一つの画素電極 190 をなす。

【0143】

画素電極 190 は中央切開部 91、92、下部切開部 93a、94a、95a 及び上部切開部 93b、94b、95b を有し、画素電極 190 はこれら切開部 91、92、93a、93b、94a、94b、95a、95b によって複数の領域に分割される。切開部 91、92、93a、93b、94a、94b、95a、95b は維持電極線 131 の横中心線に対しどんどん反転対称をなして、第 1 及び第 2 副画素電極 190a、190b は対向する二つの切開部 93a、93b 及びこれらを連結する切開連結部 99 を通じて分離されている。

10

20

30

40

50

## 【0144】

下部及び上部切開部 93a、93b、94a、94b、95a、95b はほぼ画素電極 190 の左側辺、左側角部、上側辺及び下側辺から右側辺に斜めに延在していて、維持電線 131 に分ける下半部と上半部に各々位置している。下部及び上部切開部 93a-95b はゲート線 121 に対して約 45° の角度をなして互いに垂直に延在している。

中央切開部 91、92 は下部切開部 93a、94a、95a と上部切開部 93b、94b、95b に各々ほとんど平行な一対の分枝からなる。中央切開部 91、92 は中央から横方向に延在した横部を有し、内側に位置する中央切開部 92 の横部は切開連結部 99 と連結されている。

## 【0145】

したがって、画素電極 190 の上半面と下半面は切開部 91-95b によって各々六個の領域に分けられる。この時、領域の数爻または切開部の数爻は画素の大きさ、画素電極の横辺と縦辺の長さ比、液晶層 3 の種類や特性など設計要素によって変わる。

画素電極 190 はまた、隣接するゲート線 121 またはデータ線 171a、171b と重畠して開口率 (aperture ratio) を高めている。

## 【0146】

接触補助部材 81、82a、82b は接触孔 181、182a、182b を通じてゲート線 121 の端部 129 及びデータ線 171a、171b の端部 179a、179b と各々連結される。

遮蔽電極 88 はデータ線 171a、171b 及びゲート線 121 に沿って延在していてデータ線 171a、171b 上部に位置する部分はデータ線 171a、171b を完全に覆って、ゲート線 121 上部に位置する部分はゲート線 121 の幅より小さい幅を有してゲート線 121 の境界線の内に位置する。隣接した二つのデータ線 171b、171a は完全に遮蔽電極 88 によって覆われている。しかし、その幅を調節してデータ線 171a、171b より小さいこともあって、ゲート線 121 の境界線の外に位置する境界線を有することができる。

## 【0147】

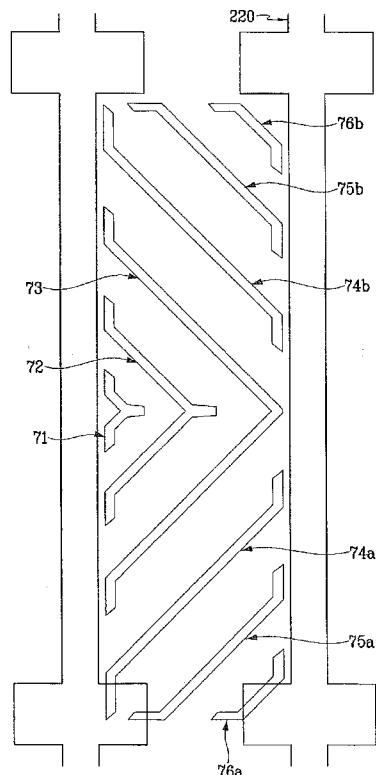

次に、図 28 及び図 30b を参照して、共通電極表示板 200 について説明する。

絶縁基板 210 上に遮光部材 220 が形成されている。遮光部材 220 はデータ線 171a、171b に対応する部分と薄膜トランジスタ Qa、Qb に対応する部分からなる。これとは異なって遮光部材 220 は画素電極 190 と対向して画素電極 190 とほとんど同一な模様の複数の開口部を有することができる。

## 【0148】

基板 210 上にはまた、複数のカラーフィルタ 230 が形成されており、カラーフィルタ 230 及び遮光部材 220 上には蓋膜 250 が形成されている。

蓋膜 250 の上には共通電極 270 が形成されており、共通電極 270 は複数の対の切開部 71-76b 集合を有する。

一対の切開部 71-76b は一つの画素電極 190 と対向して中央切開部 71-73、下部切開部 74a、75a、76a 及び上部切開部 74b、75b、76b を含む。切開部 71-76b 各々は隣接した画素電極 190 の切開部 91-95b の間または周縁切開部 95a、95b と画素電極 190 の斜辺の間に配置されている。また、各切開部 71-76b は画素電極 190 の切開部 91-95b と平行に延在した少なくとも一つの斜線部を含む。

## 【0149】

下部及び上部切開部 74a-76b 各々はほぼ画素電極 190 の右側辺から左側、下側または上側辺に向かって延在した斜線部、そして斜線部の各端から画素電極 190 の辺に沿って辺と重畠しながら延在して斜線部と鈍角をなす横部及び縦部を含む。

中央切開部 71-73 はほぼ画素電極 190 の左側辺から横部に延在した中央横部、この中央横部の端から中央横部と斜角をなして画素電極 190 の左側辺に向かって延在した一対の斜線部、そして斜線部の各端から画素電極 190 の左側辺に沿って左側辺と重畠し

10

20

30

40

50

ながら延在して斜線部と鈍角をなす縦断縦部を含む。

【0150】

切開部 71-76b の数爻は設計要素によって変わることができ、遮光部材 220 が切開部 71-76b と重畳して切開部 71-76b 付近の光漏れを遮断することができる。

共通電極 270 と遮蔽電極 88 に同一な共通電圧が印加されるので両者には電界がほとんどない。したがって、共通電極 270 と遮蔽電極 88 の間に位置した液晶分子は初期垂直配向状態をそのまま維持するのでこの部分に入射された光は透過されず、遮断される。

【0151】

少なくとも一つの切開部 91-95b、71-76b は突起や陥没部に代替することができて、切開部 91-95b、71-76b の模様及び配置は変更することができる。

表示板 100、200 の内側面には液晶分子を配向する配向膜 11、21 が各々塗布されている。配向膜 11、21 は水平配向膜であり得る。

表示板 100、200 の外側面には直交偏光板 12、22 が備えられているが、二つの偏光板 12、22 の透過軸は直交してこのうち、一つの透過軸（または吸収軸）は横方向と並んでいる。反射型液晶表示装置の場合には二つの偏光板 12、22 のうちの一つを省略できる。

【0152】

液晶層 3 は負の誘電率異方性を有して液晶層 3 の液晶分子 310 は電界がない状態でその長軸が二つの表示板の表面に対して垂直をなすように配向されている。

このような本発明の一つの実施例による液晶表示装置用薄膜トランジスタ表示板は一つの画素電極 190 をなす二つの副画素電極 190a、190b に各々連結されている薄膜トランジスタ Qa、Qb が形成されており、これら薄膜トランジスタ Qa、Qb に各々連結されているデータ線 171a、171b が形成されている。これによって、二つの副画素 Pxa、Pxb には別個のデータ信号が各々印加される。

【0153】

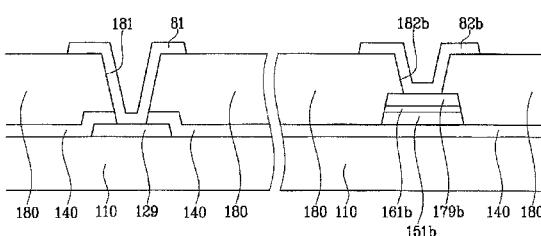

次に、図 31 乃至図 32b を参照して本発明の他の実施例による液晶表示装置用薄膜トランジスタ表示板について詳細に説明する。

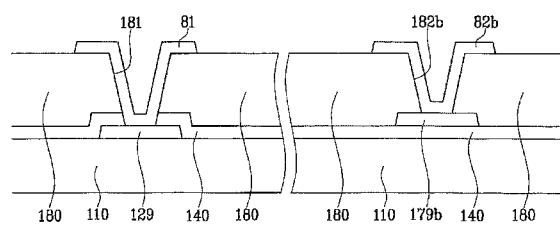

図 31 は本発明の他の実施例による液晶表示装置用薄膜トランジスタ表示板の配置図であり、図 32a は図 31 に示した薄膜トランジスタ表示板を XXXIIa-XXXXIIa 線に沿って切断した断面図であり、図 32b は図 31 に示した薄膜トランジスタ表示板を XXXIIb-XXXXIIb 線に沿って切断した断面図である。

【0154】

図 31 乃至図 32b に示したように、本実施例による液晶表示装置用薄膜トランジスタ表示板の層状構造はほとんど図 29 乃至図 30b に示した液晶表示装置用薄膜トランジスタ表示板の層状構造と同一である。つまり、基板 110 上にゲート電極 124 を含む複数のゲート線 121 及び維持電極 133 を含む複数の維持電極線 131 が形成されており、その上にゲート絶縁膜 140、突出部 154a、154b を含む半導体 151a、151b、突出部 163a、163b を含む抵抗性接触部材 161a、161b、165a、165b が順次に形成されている。抵抗性接触部材 161a、161b、165a、165b 及びゲート絶縁膜 140 上には複数のソース電極 173a、173b を含む複数のデータ線 171a、171b、複数のドレーン電極 175 が形成されていてその上に保護膜 180 が形成されている。

【0155】

保護膜 180 及び/またはゲート絶縁膜 140 には複数の接触孔 181、182a、182b、185a、185b が形成されており、保護膜 180 上には複数の副画素電極 90a、90b を含んで切開部 91-95b を有する複数の画素電極 190 と遮蔽電極 88、複数の接触補助部材 81、82a、82b が形成されている。そして保護膜 180 上には配向膜 11 が形成されている。

【0156】

しかし、図 29 乃至図 30b に示した薄膜トランジスタ表示板とは異なって、半導体 1

10

20

30

40

50

51a、151bは薄膜トランジスタQa、Qbが各々位置する突出部154a、154bを除けばデータ線171a、171b、ドレーン電極175a、175b及びその下部の抵抗性接触部材161a、161b、165a、165bと実質的に同一な平面形態を有している。具体的には、線状半導体151a、151bはデータ線171a、171b及びドレーン電極175a、175bとその下部の抵抗性接触部材161a、161b、165a、165bの下に存在する部分の以外にもソース電極173a、173bとドレーン電極175a、175bの間にこれらに遮られないで露出された部分を有している。

### 【0157】

このような薄膜トランジスタ表示板100を本発明の一つの実施例によって製造する方法ではデータ線171a、171b、ドレーン電極175a、175b、半導体151及び抵抗性接触部材161a、161b、165a、165bを一回の写真工程として形成する。

このような写真工程で使用する感光膜は位置によって厚さが異なって、特に厚さが薄くなる順に第1部分と第2部分を含む。第1部分はデータ線171a、171b及びドレーン電極175a、175bが占める配線領域に位置し、第2部分は薄膜トランジスタのチャンネル領域に位置する。

### 【0158】

位置によって感光膜の厚さを異ならせる方法としていろいろあり得るが、例えば、光マスクに投光領域(light transmitting area)及び遮光領域(light blocking area)の他に半透明領域(translucent area)を備える方法がある。半透明領域にはスリット(slit)パターン、格子パターン(lattice pattern)または透過率が中間であるか厚さが中間である薄膜が備わる。スリットパターンを使用する時には、スリットの幅やスリットの間の間隔が写真工程に使用する露光器の分解能(resolution)より小さいのが好ましい。他の例としてはリフローが可能な感光膜を使用する方法がある。つまり、投光領域と遮光領域のみを有する通常の露光マスクにリフローが可能な感光膜を形成した後、リフローさせて感光膜が残留しない領域に流れるようにすることによって薄い部分を形成することである。

### 【0159】

このようにすると一回の写真工程を減らすことができるので製造方法が簡単になる。

次に、このような液晶表示装置では信号制御部600が一つの行の画素PXに二つの副画素PXa、PXbに関する画像データDATを全て出力し、データ駆動部590は一対のデータ線を通して二つの副画素PXa、PXbに同時にデータ電圧を印加する。

したがってゲート駆動部490及びデータ駆動部590の動作周期は1水平周期となる。

### 【0160】

では本発明の実施例による反転形態に対して図25と共に図33を参照して詳細に説明する。

図33は本発明の実施例によって、列反転を実現する時、画素電極の極性状態を示した図面である。

図33でデータ駆動部590においての反転は列反転であり、一つのデータ線に流れるデータ電圧は1フレーム内、常に同一極性であり隣接した二つのデータ線に流れるデータ電圧は反対極性である。

### 【0161】

このようなデータ駆動部590の列反転によって、図33に示したように、一つの画素電極190をなす第1及び第2副画素電極190a、190bの極性は反転であり、第1副画素電極190a同士は同一極性を有し、第2副画素電極190b同士も同一極性を有する。例えば、図33に示したように、副画素電極190aは1フレーム内(-)極性を有するようになって、副画素電極190bは1フレーム内(+)極性を有するようになる。

10

20

30

40

50

## 【0162】

これによって、データ駆動部590は列反転であるが、一つの画素電極190に( - )極性と( + )極性が共に存在するので縦線模様のような画質不良がなくなる。また、同一な色相を示す画素の極性状態が全て同一であるので、同一色相の画素間の極性差による画質不良がなくなる。さらに、一つのデータ線を通じて流れるデータ電圧の極性がフレーム別にのみ反転するので、所定行ごとにデータ電圧の極性が反転する時、発生する液晶の応答速度遅延やデータ線の信号遅延が大きく減る。

## 【0163】

このように二つの副画素電圧を所望の水準に正確に合わせることによって、視認性を向上し、開口率を高め、透過率を向上させる。

10

以上で本発明の好ましい実施例について詳細に説明したが本発明の権利範囲はこれに限定されず、請求範囲で定義している本発明の基本概念を利用した当業者の多様な変形及び改良形態も本発明の権利範囲に属することである。

## 【図面の簡単な説明】

## 【0164】

【図1】本発明の一実施形態による液晶表示装置のブロック図である。

【図2】本発明の一実施形態による液晶表示装置の二つの副画素に対する等価回路図である。

20

【図3a】本発明の実施形態による液晶表示装置のブロック図である。

【図3b】本発明の実施形態による液晶表示装置のブロック図である。

【図3c】本発明の実施形態による液晶表示装置のブロック図である。

【図4a】本発明の実施形態による液晶表示装置の一画素に対する等価回路図である。

【図4b】本発明の実施形態による液晶表示装置の一画素に対する等価回路図である。

【図5a】本発明の実施形態による階調電圧生成部とデータ駆動部の多様な例を示したブロック図である。

【図5b】本発明の実施形態による階調電圧生成部とデータ駆動部の多様な例を示したブロック図である。

30

【図5c】本発明の実施形態による階調電圧生成部とデータ駆動部の多様な例を示したブロック図である。

【図6】本発明の一実施形態による基準電圧変更回路と電圧生成抵抗列のブロック図である。

40

【図7a】本発明の一実施形態による液晶表示装置のガンマ曲線を示したグラフである。

【図7b】本発明の一実施形態による液晶表示装置の入力階調に対する階調電圧を示したグラフである。

【図8a】本発明の実施形態による液晶表示装置の信号波形を時間によって示した図面である。

【図8b】本発明の実施形態による液晶表示装置の信号波形を時間によって示した図面である。

【図8c】本発明の実施形態による液晶表示装置の信号波形を時間によって示した図面である。

40

【図9】本発明の他の実施形態による液晶表示装置のブロック図である。

【図10】本発明の一実施形態による階調電圧生成部のブロック図である。

【図11】本発明の他の実施形態による液晶表示装置の階調電圧生成部のブロック図である。

【図12】図9乃至図11に示した液晶表示装置に使用される多様な信号の波形図である。

【図13】本発明の実施形態による液晶表示装置のブロック図である。

【図14】図13に示した液晶表示装置に使用される多様な信号の波形図である。

【図15】本発明の他の実施形態による液晶表示装置のブロック図である。

【図16】本発明の他の実施形態による液晶表示装置の一画素の等価回路図である。

50

【図17a】本発明の一実施形態による液晶表示装置の概略的な画素配置とデータ電圧の極性を示した図面である。

【図17b】図17aに示した液晶表示装置における各副画素の極性を示した表である。

【図18】図17aに示した液晶表示装置に使用される各種信号の波形図である。

【図19】本発明の一実施形態による下部表示板の配置図である。

【図20】本発明の一実施形態による上部表示板の配置図である。

【図21】図19の下部表示板と図20の上部表示板とを含む液晶表示板組立体の配置図である。

【図22】図21の液晶表示板組立体をX X I I - X X I I線に沿って切断した断面図である。

【図23】図21の液晶表示板組立体をX X I I I - X X I I I線に沿って切断した断面図である。

【図24】本発明の他の実施形態による液晶表示板組立体の配置図である。

【図25】本発明の他の実施形態による液晶表示装置のブロック図である。

【図26】図25に示した液晶表示装置の一画素に対する等価回路図である。

【図27】本発明の他の実施形態による液晶表示装置用薄膜トランジスタ表示板の配置図である。

【図28】本発明の他の実施形態による液晶表示装置用共通電極表示板の配置図である。

【図29】図27の薄膜トランジスタ表示板と図28の共通電極表示板を含む液晶表示板組立体の配置図である。

【図30a】各々図29の液晶表示板組立体をX X X a - X X X a線及びX X X b - X X X b線に沿って切断した断面図である。

【図30b】各々図29の液晶表示板組立体をX X X a - X X X a線及びX X X b - X X X b線に沿って切断した断面図である。

【図31】本発明の他の実施形態による薄膜トランジスタ表示板の配置図である。

【図32a】図31に示した薄膜トランジスタ表示板をI X a - I X a'線に沿って切断した断面図である。

【図32b】図31に示した薄膜トランジスタ表示板をI X b - I X b'線に沿って切断した断面図である。

【図33】図25乃至図32に示した液晶表示装置で列反転を実現する時の画素電極の極性状態を示した図面である。

【符号の説明】

【0165】

3 液晶層

11、21 配向膜

12、22 偏光子

71 - 76b、91 - 95、271 - 275 切開部

81、82a、82b 接触補助部材

88 遮蔽電極

100、200 表示板

110、210 絶縁基板

121、121a、121b、129、129a、129b ゲート線

124、124a、124b ゲート電極

126 結合電極

133、137、137a、137b 維持電極

140 絶縁膜

151、151a、151b、154a、154b 半導体

171、171a、171b、179、179a、179b データ線

175a、175b、177a、177b ドレイン電極

180 保護膜

10

20

30

40

50

181、181a、181b、182、182a、182b、185a、185b、186、187a、187b 接触孔

190 画素電極

190a、190b 副画素電極

220 遮光部材

230 カラーフィルタ

250 蓋膜

270 共通電極

271、273、275 切開部

300 液晶表示板組立体

310 液晶分子

400、400a、400b、410、420、430、440、440a、440b

10

500、590 データ駆動部

600 信号制御部

800、900 階調電圧生成部

【図1】

【図2】

【図3 a】

【図3 b】

【図3 c】

【図4 a】

【図 4 b】

【図 5 a】

【図6】

【図 5 b】

【 図 5 c 】

【 図 7 a 】

【 7 b 】

【図 8 a】

【図 8 b】

【図 8 c】

【図 9】

【図 10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17 a】

【図17 b】

|   |   |   |

|---|---|---|

| + | - | + |

| - | + | - |

| + | - | + |

| - | + | - |

| + | - | + |

| - | + | - |

| + | - | + |

| - | + | - |

【図18】

【 図 1 9 】

【 図 2 0 】

### 【 図 2 1 】

【 図 2 2 】

【 図 2 3 】

【図24】

【 図 25 】

【 図 2 6 】

【 図 27 】

【 図 2 8 】

【 図 29 】

【図30a】

【図30b】

【図31】

【図32a】

【図32b】

【図33】

## フロントページの続き

| (51)Int.Cl. | F I     | テーマコード(参考)   |

|-------------|---------|--------------|

|             | G 0 9 G | 3/20 6 2 2 D |

|             | G 0 9 G | 3/20 6 2 3 C |

|             | G 0 9 G | 3/20 6 2 3 F |

|             | G 0 9 G | 3/20 6 2 1 A |

|             | G 0 9 G | 3/20 6 1 2 F |

|             | G 0 9 G | 3/20 6 2 4 C |

|             | G 0 9 G | 3/20 6 2 1 B |

(72)発明者 金 相 淑

大韓民国ソウル市江南区道谷2洞タワーパレスF棟3104号

(72)発明者 金 東 奎

大韓民国京畿道龍仁市豊徳川洞三星5次アパート523棟1305号

(72)発明者 文 勝 煥

大韓民国京畿道龍仁市上 ヒョン 洞マンヒョンマウル2団地現代6次アパート205棟1504号

(72)発明者 李 昇 祐

大韓民国ソウル市衿川区始興2洞266番地冠岳山碧山タウン519棟1601号

(72)発明者 白 承 淑

大韓民国ソウル市冠岳区南 ヒョン 洞602-55番地302号

F ターム(参考) 2H093 NA16 NB07 NB11 NB21 NC09 NC11 NC31 NC34 ND10 ND15

ND58 NF03

5C006 AC24 AC25 AC26 AF42 AF71 AF82 BB16 BC03 BC12 BF24

BF34 BF37 BF43 FA16 FA22

5C080 AA10 BB05 DD05 EE29 FF11 JJ02 JJ03 JJ04 JJ05 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP2006139288A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2006-06-01 |

| 申请号            | JP2005329431                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2005-11-14 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| [标]发明人         | 金相洙<br>金東奎<br>文勝煥<br>李昇祐<br>白承洙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 金相洙<br>金東奎<br>文勝煥<br>李昇祐<br>白承洙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| CPC分类号         | G09G3/3648 G02F2001/134345 G09G3/2074 G09G3/3406 G09G3/3614 G09G3/3696 G09G2300/0426 G09G2300/0443 G09G2300/0447 G09G2300/0823 G09G2310/0251 G09G2310/0281 G09G2320/0209 G09G2320/0247 G09G2320/028 G09G2320/064                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G02F1/133.505 G09G3/20.642.A G09G3/20.622.C G09G3/20.622.D G09G3/20.623.C G09G3/20.623.F G09G3/20.621.A G09G3/20.612.F G09G3/20.624.C G09G3/20.621.B G11C19/00 G11C19/00.J                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NB07 2H093/NB11 2H093/NB21 2H093/NC09 2H093/NC11 2H093/NC31 2H093/NC34 2H093/ND10 2H093/ND15 2H093/ND58 2H093/NF03 5C006/AC24 5C006/AC25 5C006/AC26 5C006/AF42 5C006/AF71 5C006/AF82 5C006/BB16 5C006/BC03 5C006/BC12 5C006/BF24 5C006/BF34 5C006/BF37 5C006/BF43 5C006/FA16 5C006/FA22 5C080/AA10 5C080/BB05 5C080/DD05 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 2H093/NC35 2H093/NC40 2H193/ZA01 2H193/ZA04 2H193/ZA08 2H193/ZA19 2H193/ZC12 2H193/ZC13 2H193/ZC16 2H193/ZC34 2H193/ZC36 2H193/ZF24 2H193/ZH40 2H193/ZQ04 2H193/ZQ11 5B074/AA10 5B074/CA01 |         |            |

| 优先权            | 1020040092607 2004-11-12 KR<br>1020040098028 2004-11-26 KR<br>1020050002543 2005-01-11 KR<br>1020050004526 2005-01-18 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 其他公开文献         | JP5000124B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

**摘要(译)**

要解决的问题：精确匹配两个垂直相邻像素的形状，精确匹配像素的开口率，防止两个像素的电气和光学特性发生变化，并形成V形像素电极。当设置切口部分时，其中不出现水平条纹或垂直条纹的液晶显示装置。布置成矩阵并且包括第一和第二子像素的像素PX连接到第一子像素Px<sub>a</sub>，并且连接到传输第一选通信号的第一栅极线GL<sub>a</sub>，并且连接到第二子像素Px<sub>b</sub>。第二栅极线GL<sub>b</sub>用于传输第二栅极信号，数据线DL与第一栅极线和第二栅极线交叉并连接至第一子像素和第二子像素，用于传输数据电压。施加到每个像素的第一和第二子像素的数据电压的大小彼此不同，并且是从一个图像信息获得的。[选择图]图4a