(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-163943

(P2004-163943A)

(43) 公開日 平成16年6月10日(2004.6.10)

(51) Int.Cl.<sup>7</sup>

G02F 1/1343

G02F 1/1333

G09F 9/30

G09F 9/35

F 1

G02F 1/1343

G02F 1/1333 500

G09F 9/30 338

G09F 9/35

テーマコード(参考)

2H090

2H092

5C094

審査請求 未請求 請求項の数 4 O L (全 12 頁)

(21) 出願番号 特願2003-380247 (P2003-380247)

(22) 出願日 平成15年11月10日 (2003.11.10)

(31) 優先権主張番号 2002-070706

(32) 優先日 平成14年11月14日 (2002.11.14)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

大韓民国京畿道水原市靈通区梅灘洞 416

(74) 代理人 100094145

弁理士 小野 由己男

(74) 代理人 100106367

弁理士 稲積 朋子

(72) 発明者 柳在鎮

大韓民国京畿道廣州郡五浦面陽役1里69

2番地

(72) 発明者 李仲熙

大韓民国京畿道水原市八達区望浦洞694

番地望浦マウル現代 1次アイパーク10

9棟802号

最終頁に続く

(54) 【発明の名称】 液晶表示装置用薄膜トランジスタ基板

## (57) 【要約】

【課題】 本発明は、視認性に優れた多重ドメイン液晶表示装置及びそれに用いられるトランジスタ基板を提供することを目的とする。

【解決手段】 絶縁基板、絶縁基板上に第1方向に形成されている第1信号線、絶縁基板上に第2方向に形成されていて第1信号線と絶縁されて交差している第2信号線、第1信号線及び第2信号線に連結されている第1薄膜トランジスタ、第1薄膜トランジスタが連結されている第1信号線及び第2信号線に連結されている第2薄膜トランジスタ、第1薄膜トランジスタに連結されている第1画素電極、第2薄膜トランジスタに連結されている第2画素電極を含み、第1薄膜トランジスタの第1ドレーン電極及びゲート電極の間に形成される第1静電容量、第2薄膜トランジスタの第2ドレーン電極及びゲート電極の間に形成される第2静電容量が互いに異なる薄膜トランジスタ基板を提供する。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

絶縁基板と、

前記絶縁基板上に第1方向に形成されている第1信号線と、

前記絶縁基板上に第2方向に形成されて、前記第1信号線と絶縁されて交差している第2信号線と、

前記第1信号線及び前記第2信号線に連結されている第1薄膜トランジスタと、

前記第1薄膜トランジスタが連結されている前記第1信号線及び前記第2信号線に連結されている第2薄膜トランジスタと、

前記第1薄膜トランジスタに連結されている第1画素電極と、

前記第2薄膜トランジスタに連結されている第2画素電極とを含み、

前記第1薄膜トランジスタの第1ドレーン電極及びゲート電極の間に形成される第1静電容量と、前記第2薄膜トランジスタの第2ドレーン電極及びゲート電極の間に形成される第2静電容量とが互いに異なる薄膜トランジスタ基板。

**【請求項 2】**

請求項1に記載の薄膜トランジスタ基板と、

前記薄膜トランジスタ基板と対向する基準電極基板と、

前記基準電極基板上に形成されている基準電極と、

前記薄膜トランジスタ基板と前記基準電極基板との間に注入されている液晶物質とを含む液晶表示装置。

**【請求項 3】**

絶縁基板と、

前記絶縁基板上に横方向に形成されているゲート線及び前記ゲート線に連結されているゲート電極を含むゲート配線と、

前記ゲート配線を覆うゲート絶縁膜と、

前記ゲート電極上部の前記ゲート絶縁膜上に形成されている半導体層と、

前記ゲート絶縁膜上に縦方向に形成されているデータ線、前記データ線と連結されて前記半導体層上にまで延びているソース電極、前記半導体層上に前記ソース電極と対向している第1及び第2ドレーン電極とを含むデータ配線と、

前記データ配線上に形成されて前記第1及び第2ドレーン電極の一部をそれぞれ露出する第1及び第2接触孔を有する保護膜と、

前記保護膜上に形成されて前記第1接触孔を通じて前記第1ドレーン電極と連結される第1画素電極と、

前記保護膜上に形成されて前記第2接触孔を通じて前記第2ドレーン電極と連結される第2画素電極とを含み、

前記ゲート電極及び前記第1ドレーン電極が重なる面積と前記ゲート電極及び前記第2ドレーン電極が重なる面積とが互いに異なるように形成されている液晶表示装置用薄膜トランジスタ基板。

**【請求項 4】**

前記ソース電極は、第1及び第2ソース電極に分離されて形成されている請求項3に記載の液晶表示装置用薄膜トランジスタ基板。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、液晶表示装置及びそれに用いられる基板に関し、特に視野角が改善された液晶表示装置及びそれに用いられる基板に関するものである。

**【背景技術】****【0002】**

一般に液晶表示装置は、基準電極と色フィルターなどが形成されている上部基板と、画素電極及び薄膜トランジスタなどが形成されている下部基板との間に液晶物質を注入する

10

20

20

30

40

50

。そして、基準電極と画素電極に互いに異なる電位を印加することによって電界を形成して液晶分子の配列を変更させ、これによって光の透過率を調節することで画像を表現する装置である。ところが液晶表示装置は、視野角及び側面視認性が悪いことが大きな短所である。このような短所を解決するために、視野角を広くするための様々な方案が開発されているが、その中でも液晶分子を上下基板に対し垂直に配向して画素電極とその対向電極である基準電極とに一定の切開パターンを形成する方法や、突起を形成する方法が有力視されている。

#### 【0003】

切開パターンを形成する方法は、画素電極と基準電極とにそれぞれ切開パターンを形成し、これらの切開パターンによって形成されるフリンジフィールド ( fringe field ) を利用して液晶の傾斜方向を 4 方向に均等に分散させることで視野角を確保する方法である。突起を形成する方法は、上下基板上に形成されている画素電極と基準電極上にそれぞれ突起を形成して、その突起によって歪曲される電場を利用して液晶分子の横たわる方向を調節する方式である。

#### 【0004】

そして、切開パターンや突起によって分割されるドメインは、液晶の横たわる方向によつていくつかの種類に分類される。一般には 4 方向それぞれに対して一種類ずつ 4 種類に分けられる。この場合、下部基板と傾斜した液晶の長軸とがなす角度を傾斜角 ( tilt angle ) とすれば、同一な印加電圧に対して互いに異なるドメインの液晶分子の傾斜角は同一であるので、ドメインの光学的特性の補償率が低く、側面視認性に問題がある。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0005】

本発明は、前記の問題を解決するために視認性に優れた多重ドメイン液晶表示装置及びそれに用いられるトランジスタ基板を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0006】

前記目的を達成するために本発明の薄膜トランジスタ基板は、絶縁基板と、前記絶縁基板上に第 1 方向に形成されている第 1 信号線と、前記絶縁基板上に第 2 方向に形成されて前記第 1 信号線と絶縁されて交差している第 2 信号線と、前記第 1 信号線及び前記第 2 信号線に連結されている第 1 薄膜トランジスタと、前記第 1 薄膜トランジスタが連結されている前記第 1 信号線及び前記第 2 信号線に連結されている第 2 薄膜トランジスタ、前記第 1 薄膜トランジスタに連結されている第 1 画素電極、及び前記第 2 薄膜トランジスタに連結されている第 2 画素電極とを含み、前記第 1 薄膜トランジスタの第 1 ドレーン電極及びゲート電極の間に形成される第 1 静電容量と、前記第 2 薄膜トランジスタの第 2 ドレーン電極及びゲート電極の間に形成される第 2 静電容量とは互いに異なる。また、前記目的を達成するために本発明の液晶表示装置は、前記薄膜トランジスタ基板と、前記薄膜トランジスタ基板と対向する基準電極基板と、前記基準電極基板上に形成されている基準電極、及び前記薄膜トランジスタ基板と前記基準電極基板の間に注入されている液晶物質を含む。

#### 【0007】

さらに、前記目的を達成するために本発明の液晶表示装置用薄膜トランジスタ基板は、絶縁基板と、前記絶縁基板上に横方向に形成されるゲート線と前記ゲート線に連結されているゲート電極を含むゲート配線と、前記ゲート配線を覆うゲート絶縁膜と、前記ゲート電極上部の前記ゲート絶縁膜上に形成される半導体層と、前記ゲート絶縁膜上に縦方向に形成されているデータ線と、前記データ線と連結されて前記半導体層上にまで延びているソース電極と、前記半導体層上に前記ソース電極と対向している第 1 及び第 2 ドレーン電極を含むデータ配線と、前記データ配線上に形成されて前記第 1 及び第 2 ドレーン電極の一部をそれぞれ露出させる第 1 及び第 2 接触孔を有する保護膜と、前記保護膜上に形成さ

10

20

30

40

50

れて前記第1接触孔を通じて前記第1ドレーン電極と連結される第1画素電極と、前記保護膜上に形成されて前記第2接触孔を通じて前記第2ドレーン電極と連結される第2画素電極とを含み、前記ゲート電極及び前記第1ドレーン電極が重なる面積と前記ゲート電極及び前記第2ドレーン電極が重なる面積が互いに異なるように形成されている。そして、前記ソース電極は第1及び第2ソース電極に分離して形成されている。

【発明の効果】

【0008】

本発明による液晶表示装置用トランジスタ基板は、サブ画素領域間にキックバック現象による電圧下落値を互いに異なることによって、サブ画素領域間に差別電圧の印加を可能にし、視野角を改善することができる。

10

【発明を実施するための最良の形態】

【0009】

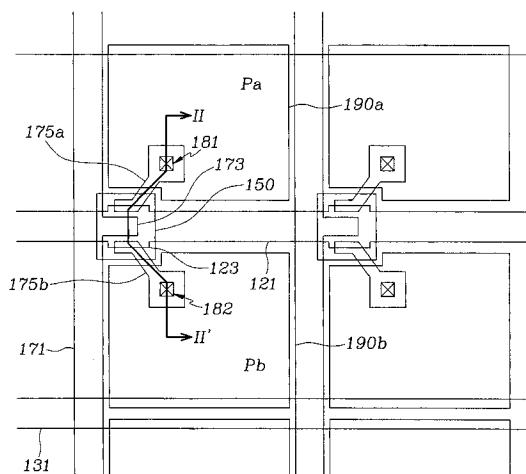

以下、添付した図面を参照して本発明による好ましい一実施例を詳細に説明する。図1は、本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板の配置図であり、図2は図1のI—I—I—I'線による断面図であり、図3は図1の薄膜トランジスタ基板を適用した液晶表示装置の等価回路図である。

【0010】

図1及び図2に示されるように、ガラスなどの透明な絶縁基板110上にゲート配線121、123と維持電極線131が形成されている。ゲート配線121、123は横方向に伸びているゲート線121を含み、ゲート線121にゲート電極123が連結されている。

20

【0011】

維持電極線131はゲート線121と並んで形成されており、図示していないが枝線を有することもできる。ゲート配線121、123と維持電極線131は、ゲート絶縁膜140で覆われており、ゲート絶縁膜140上には非晶質シリコンで構成される半導体層150が形成されている。半導体層150は、ゲート電極123と重なって薄膜トランジスタのチャンネル部を形成する。半導体層150の上には、リンなどのN型不純物が高濃度にドーピングされた非晶質シリコンで構成される抵抗性接触層163、165a、165bが形成されている。

【0012】

前記接触層163、165a、165b及びゲート絶縁膜140上には、データ配線171、173、175a、175bが形成されている。データ配線171、173、175a、175bは、データ線171とこれに連結されたソース電極173及びこれらと分離された第1及び第2ドレーン電極175a、175bを含む。ソース電極173は、ゲート電極123上部にデータ線171から突出しており、第1及び第2ドレーン電極175a、175bは、ソース電極173の両側にそれぞれ配置されて、それぞれの一端はゲート線121を中心に両側に位置する第1及び第2画素領域(Pa、Pb)の内側に伸びている。ここで、抵抗性接触層163、165a、165bは、半導体層150とデータ配線171、173、175a、175bが重なる部分にのみ形成されている。

30

【0013】

前記ゲート線121と第1及び第2ドレーン電極175a、175bの間には静電容量が形成される。この静電容量は、ゲート線121と第1及び第2ドレーン電極175a、175bが重なる面積とほぼ比例して増減する。

40

【0014】

本発明の実施例では、第1ドレーン電極175aとゲート線121が重なる面積が第2ドレーン電極175bとゲート線121が重なる面積に比べて大きくなるように調節することによって、ゲート線121と第1ドレーン電極175aの間に形成される静電容量がゲート線121と第2ドレーン電極175bとの間に形成される静電容量に比べて大きくなるように調節できる。これは、後述する第1のサブ画素領域に印加される電界を、第2のサブ画素領域に印加される電界より所定値分低くするためのものである。

50

## 【0015】

データ配線 171、173、175a、175b の上には、保護膜 180 が形成されている。前記保護膜 180 は、第1及び第2ドレーン電極 175a、175b の一端をそれぞれ露出する第1及び第2接触孔 181、182 を有する。

## 【0016】

保護膜 180 の上には、第1接触孔 181 と第2接触孔 182 を通じて第1ドレーン電極 175a 及び第2ドレーン電極 175b とそれぞれ連結されている第1及び第2画素電極 190a、190b が形成されている。画素電極 190a、190b は、ITO または IZO などの透明な導電物質で構成される。そして、維持電極線 131 には、画素電極 190a、190b と対向する基準電極の電位が印加されるのが普通である。従って、第1画素電極 190a が形成された領域を第1のサブ画素領域 (Pa) とし、第2の画素電極 190b が形成された領域を第2サブ画素領域 (Pb) とすれば、一つの画素領域は2つのサブ画素領域から構成されることになる。

## 【0017】

このような薄膜トランジスタ基板を使用する液晶表示装置は、次のような構造を有する。このような薄膜トランジスタ基板に対向して基準電極基板が、所定の間隔を置いて配置されており、薄膜トランジスタ基板と基準電極基板との間には液晶物質が注入されている。そして、基準電極基板には、薄膜トランジスタ基板の画素電極との間で液晶容量を形成する基準電極が形成されている。その他にも、基準電極基板上には補償フィルムが付着されており、二つの偏光板が薄膜トランジスタ基板と基準電極基板の外側に配置されている。

## 【0018】

以上のように本発明では、一つの画素領域当り一つのソース電極 173 と2つのドレーン電極 175a、175b が形成されており、一つの画素領域当り画素電極 190a、190b が2つずつ形成されている。ところが、二つのドレーン電極 175a、175b がゲート線 121 と重なる面積が異なることによって一つの画素領域内に位置する二つの画素電極 190a、190b に印加される電圧の間に少しの差が生ずる。このような差は、画素電極電圧のキックバック現象によって発生し、液晶表示装置の視認性を改善する効果がある。以下、キックバック現象と視認性改善効果について詳細に検討する。

## 【0019】

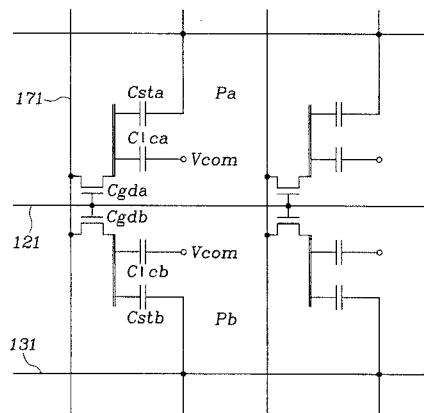

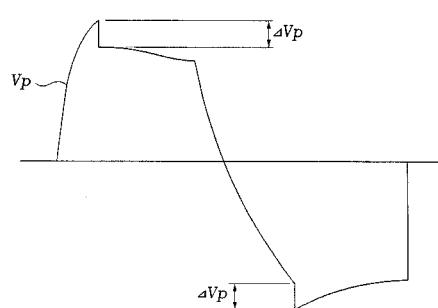

データ線を通じて第1、2サブ画素領域 (Pa、Pb) に印加される電圧にはキックバック現象が発生する。図4に示すように、キックバック現象とは、データ線を通じて第1、2サブ画素領域 (Pa、Pb) に印加されたデータ電圧 (Vd) が時間経過につれてゆっくり下落する場合、データ電圧の印加初期に発生する急激な電圧下落現象をいう。図4の Vp がキックバック現象による電圧下落値を示している。このようなキックバック現象は、ゲート電極 123 と第1、2ドレーン電極 175a、175b との間に形成された寄生容量によって発生する。従って、第1、2サブ画素領域 (Pa、Pb) には、初期データ電圧と Vp の差に該当する電圧のみが印加される。

## 【0020】

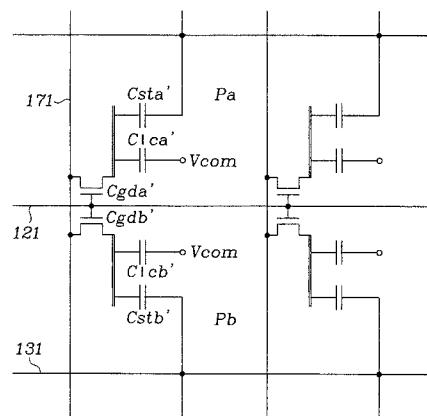

図3の C1ca は、第1画素電極 190a と基準電極との間に形成される液晶容量、Csta は維持電極線と第1画素電極 190a との間で形成される保持容量、C1cb は第2画素電極 190b と基準電極との間に形成される液晶容量、Cstb は維持電極線と第2画素電極 190b との間で形成される保持容量、Cgda はゲート電極 123 と第1ドレーン電極 175a との間に形成される寄生容量、Cgdb はゲート電極 123 と第2ドレーン電極 175b との間に形成される寄生容量を示す。ここで、キックバック現象によって下落する電圧値は次式のようである。

## 【0021】

【数1】

$$\Delta V_{p\alpha} = V_g \times \frac{C_{gda}}{Clca + Csta + Cgda} \quad \dots \dots (1)$$

数式(1)の  $V_{p\alpha}$  は、第1サブ画素領域( $P_\alpha$ )に印加される電圧のキックバック現象による電圧下落値をいう。 $V_g$  はゲート線121に印加される電圧を意味する。

【0022】

【数2】

$$\Delta V_{pb} = V_g \times \frac{Cgdb}{Clcb + Cstb + Cgdb} \quad \dots \dots (2)$$

10

数式2の  $V_{pb}$  は、第2サブ画素領域( $P_b$ )に印加される電圧のキックバック現象による電圧下落値をいう。数式(1)及び(2)に示すように、キックバック現象による電圧下落値は  $C_{gda}$  または  $C_{gdb}$  によって調整可能である。このような  $C_{gda}$  または  $C_{gdb}$  は、ゲート電極123と第1、2ドレーン電極175a、175bとの重畠面積によって決まる。

【0023】

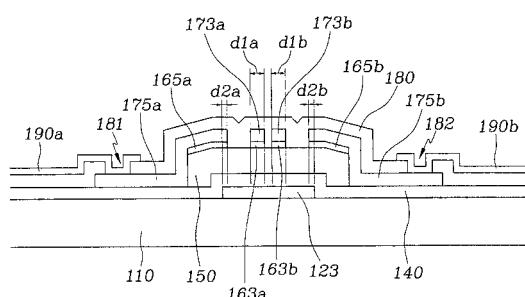

図2に示すように、ゲート電極123とソース電極173が重なる幅を  $d_1$ 、ゲート電極123と第1ドレーン電極175aが重なる幅を  $d_{2a}$ 、ゲート電極123と第2ドレーン電極175bが重なる幅を  $d_{2b}$  と定義する。 $C_{gda}$  または  $C_{gdb}$  は、 $d_{2a}$ 、 $d_{2b}$ を調節することによって変更できる。静電容量は二つの電極の重畠面積に比例するので、 $d_{2a}$ を増やせば  $C_{gda}$  が増加し、 $d_{2b}$ を増やせば  $C_{gdb}$  が増加する。

【0024】

そして、数式(1)及び(2)のように、 $C_{gda}$ の増加によって  $V_{p\alpha}$  が増加し、 $C_{gdb}$ の増加によって  $V_{pb}$  が増加する。従って、 $d_{2a}$ 、 $d_{2b}$ を調節することによって、第1サブ画素領域( $P_\alpha$ )に印加される電圧と第2サブ画素領域( $P_b$ )に印加される電圧を互いに異ならせることができ。つまり、 $d_{2a}$ 、 $d_{2b}$ を調節して  $C_{gda}$ を  $C_{gdb}$ より大きくすれば、キックバック現象による電圧下落値である  $V_{p\alpha}$  と  $V_{pb}$  の間には  $V_{p\alpha} > V_{pb}$  の関係が成立する。従って、第1サブ画素領域  $P_\alpha$  には第2サブ画素領域  $P_b$  より低い電圧が印加される。

30

【0025】

このようなキックバック現象による電圧下落値である  $V_{p\alpha}$  と  $V_{pb}$  は、残像やフリッカー現象を発生させてるので最少化するのが好ましい。シミュレーションの結果、データ電圧が10Vの時、キックバック現象による電圧下落値は0.8乃至0.9Vであり、実際測定した結果は0.5乃至1.0Vであった。

【0026】

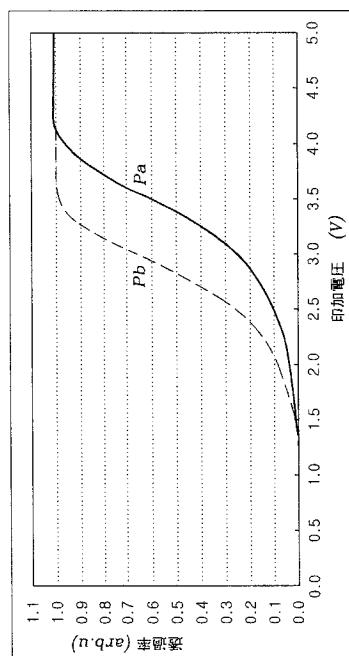

このように、第1サブ画素領域( $P_\alpha$ )に第2サブ画素領域( $P_b$ )より低い電圧が印加されれば、視野角側面にどんな現象が発生するかについてVA(Vertical alignment)モードを例に検討する。第1サブ画素領域( $P_\alpha$ )と第2サブ画素領域( $P_b$ )との間には印加される電圧が異なるので、二つのサブ画素領域( $P_\alpha$ 、 $P_b$ )間に位置する液晶分子の傾斜角が互いに異なる。従って、図5に示すように、印加された電圧に対する透過率の関係曲線、つまりV-T曲線は互いに異なる。これで、二つの領域( $P_\alpha$ 、 $P_b$ )の光学的特性が互いに効果的に補償されて視野角が広くなる。つまり、2つのサブ画素領域に印加する電圧を異ならせることで光透過特性を異ならせる。さらに、キックバック電圧を積極的に活用して同一のサブ画素領域でも反転時と非反転時で光透過特性を異ならせ、視認性の視角依存性を軽減する。特に、視野角の限界点付近で有効である。

40

【0027】

より具体的には、二つのサブ画素領域( $P_\alpha$ 、 $P_b$ )間に位置する液晶分子の傾斜角が

50

互いに異なることで視野角が改善される。VAモードを例に挙げて説明すると、印加電圧がなければ、液晶分子の液晶軸が画面に対して垂直になり印加電圧が小さければ、僅かながら液晶軸の平行成分が発生して垂直成分が減少し、印加電圧が大きければ、更に画面に対する平行成分が多く垂直成分が少なくなる。よって、両サブ画素領域の一方は印加電圧が小さく傾斜角が大きいが、他方は印加電圧が大きく傾斜角が小さくなる。そのため、隣接した第1および第2サブ画素領域に互いに異なる電圧が印加されると、高輝度のサブ画素領域と低輝度のサブ画素領域とが組み合わされ、両サブ画素領域の位相（またはRetardation）が互いに補償されて液晶パネルの正面から見る光の量と正面から外れた地点から見る光の量との差が減少し、視野角が向上する。

## 【0028】

10

TNモードの場合も同様に両サブ画素領域の位相が互いに補償されて視野角が向上する。TNモードでは、特に視野角限界付近での階調特性劣化については、特定の視角での入力電圧変化に対する輝度変化特性の急速な劣化が軽減される。つまり、特定視角で輝度反転を生じる限界輝度では、高輝度サブ画素領域が輝度反転になつても、低輝度サブ画素領域は正しく動作し、低輝度サブ画素領域が反転を生じる視角になつて初めて全面的に輝度反転になり、結果的に視野角が広がる。

## 【0029】

これは、VAモードだけでなくTN（Twisted nematic）モードやOCB（Optical compensated bend）モードなどにも同じように適用される。また、ドット反転方式だけでなくライン反転方式にも適用できる。さらに、画素領域の分割方法も縦方向の分割のみならず、差流分割や斜め分割にも適用可能である。

20

## 【0030】

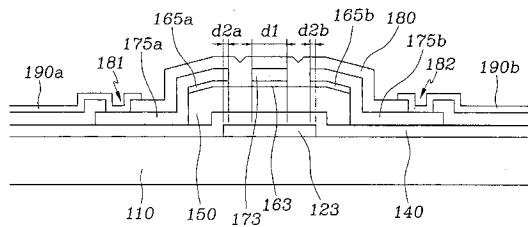

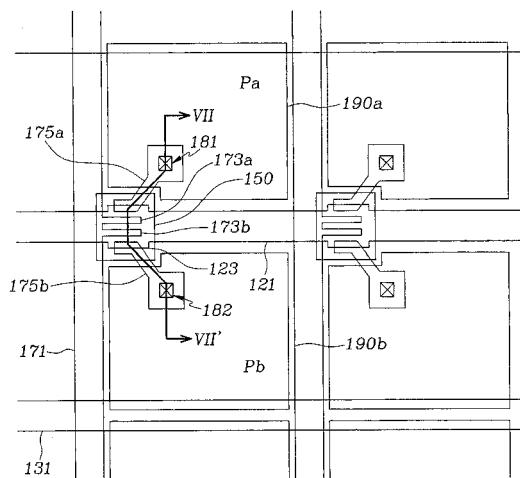

次は、本発明の第2実施例による液晶表示装置について説明する。本発明の第2実施例による液晶表示装置用トランジスタ基板が図6に示されている。ここで、前記図面と同じ符号となっているものは同じ機能の同じ部材である。

## 【0031】

図6は、本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板の配置図であり、図7は図6のVII-VII'線による断面図であり、図8は図6の薄膜トランジスタ基板を適用した液晶表示装置の等価回路図である。図6及び図7に示すように、接触層163、165a、165b及びゲート絶縁膜140上には、データ配線171、173a、173b、175a、175bが形成されている。データ配線171、173a、173b、175a、175bは、データ線171とこれに連結された第1及び第2ソース電極173a、173bとこれらと分離された第1及び第2ドレーン電極175a、175bを含む。第1及び第2ソース電極173a、173bは、互いに所定間隔を置いてゲート電極123上部にデータ線171から突出しており、第1及び第2ドレーン電極175a、175bの一側端はそれぞれ第1及び第2ソース電極173a、173bの一側に配置されて、それぞの他側端はゲート線121を中心にして両側に位置する第1及び第2画素領域（Pa、Pb）の内側に延びている。

30

## 【0032】

このように第1薄膜トランジスタは、ゲート電極123と、第1ソース電極173a及び第1ドレーン電極175aから構成されて、第2薄膜トランジスタはゲート電極123と、第2ソース電極173b及び第2ドレーン電極175bから構成される。ここで、抵抗性接触層163、165a、165bは、半導体層150とデータ配線171、173a、173b、175a、175bが重なる部分にのみ形成されている。ここで、ゲート線121と第1及び第2ドレーン電極175a、175bとの間には静電容量が形成される。この静電容量はゲート線121と第1及び第2ドレーン電極175a、175bが重なる面積にほぼ比例して増減する。本発明の実施例では、第1ドレーン電極175aとゲート線121が重なる面積が、第2ドレーン電極175bとゲート線121が重なる面積に比べて大きくすることによって、ゲート線121と第1ドレーン電極175aとの間に形成される静電容量が、ゲート線121と第2ドレーン電極175bとの間に形成される

40

50

静電容量より大きくなるように調節できる。これは、後述するように、第1サブ画素領域に印加される電界を第2サブ画素領域に印加される電界に比べて所定値分低くするためである。

### 【0033】

保護膜180の上には、第1接触孔181と第2接触孔182を通じて、第1ドレーン電極175a及び第2ドレーン電極175bとそれぞれ連結されている第1及び第2画素電極190a、190bが形成されている。第1及び第2薄膜トランジスタには、それぞれ第1画素電極190aと第2画素電極190bが連結されている。従って、第1画素電極190aが形成された領域を第1サブ画素領域(Pa)とし、第2画素電極190bが形成された領域を第2サブ画素領域(Pb)とすれば、一つの画素領域は2つのサブ画素領域から構成されることになる。

### 【0034】

前記のように、本発明による第2実施例の液晶表示装置用薄膜トランジスタ基板には、一つの画素領域当たり2つの画素電極190a、190bと2つの薄膜トランジスタが形成されている。ところが、2つの薄膜トランジスタのそれぞれのドレーン電極175a、175bがゲート線121と重なる面積を異ならすことによって、一つの画素領域内に位置する二つの画素電極190a、190bに印加される電圧の間には少しの差が発生する。このような差は、画素電極電圧のキックバック現象によって発生し、液晶表示装置の視認性を改善する効果がある。以下、キックバック現象と視認性改善効果について詳細に検討する。

### 【0035】

一つのデータ線171を基準にすると、一つのゲート線121がONになれば二つの薄膜トランジスタ(TFT)チャンネルがONになり、これを通じて第1及び第2画素電極190a、190bに電圧が印加される。しかし、データ線171を通じて第1、2サブ画素領域(Pa、Pb)に印加される電圧にはキックバック現象が発生する。このようなキックバック現象は、ゲート電極123と第1、2ドレーン電極175a、175bの間に形成された寄生容量によって発生する。従って、第1、2サブ画素領域(Pa、Pb)には初期データ電圧とVpの差の分の電圧のみが実際に印加される。

### 【0036】

図8でC1caは、第1画素電極190aと基準電極の間に形成される液晶容量、Cstaは維持電極線と第1画素電極190aの間に形成される保持容量、C1cbは第2画素電極190bと基準電極の間に形成される液晶容量、Cstbは維持電極線と第2画素電極190bの間に形成される保持容量、Cgda'はゲート電極123と第1ドレーン電極175aとの間に形成される寄生容量、Cgdb'はゲート電極123と第2ドレーン電極175bとの間に形成される寄生容量を示す。ここで、キックバック現象によって下落する電圧値は次の通りである。

### 【0037】

#### 【数3】

$$\Delta Vp'a' = Vg \times \frac{Cgda'}{Clca + Csta + Cgda'} \quad \dots \dots (3)$$

式(3)のVp'a'は、第1サブ画素領域(Pa)に印加される電圧のキックバック現象による電圧下落値をいう。Vgはゲート線に印加される電圧を意味する。

### 【0038】

#### 【数4】

$$\Delta Vpb' = Vg \times \frac{Cgdb'}{Clcb + Cstb + Cgdb'} \quad \dots \dots (4)$$

数式(4)の  $V_{pb}'$  は、第2サブ画素領域( $P_b$ )に印加される電圧のキックバック現象による電圧下落値をいう。数式(3)及び(4)に示すように、キックバック現象による電圧下落値は  $C_{gda}'$  または  $C_{gdb}'$  によって調整可能である。このような  $C_{gda}'$  または  $C_{gdb}'$  は、ゲート電極123及び第1、2ドレーン電極175a、175bとの重なる面積によって決定される。

#### 【0039】

図7に示すように、ゲート電極123と第1ソース電極173aが重なる幅を  $d_{1a}$ 、ゲート電極123と第2ソース電極173bが重なる幅を  $d_{1b}$ 、ゲート電極123と第1ドレーン電極175aが重なる幅を  $d_{2a}$ 、ゲート電極123と第2ドレーン電極175bが重なる幅を  $d_{2b}$  と定義する。 $C_{gda}'$  及び  $C_{gdb}'$  は  $d_{2a}$ 、 $d_{2b}$  を調節することによって変更できる。二つの電極間の静電容量は重なる面積に比例するので、 $d_{2a}$  を増やせば  $C_{gda}'$  が増加し、 $d_{2b}$  を増やせば  $C_{gdb}'$  が増加する。

#### 【0040】

そして、数式(3)及び(4)に示すように、 $C_{gda}'$  の増加によって  $V_{pa}'$  が増加し、 $C_{gdb}'$  の増加によって  $V_{pb}'$  が増加する。従って、 $d_{2a}$ 、 $d_{2b}$  を調節することによって第1サブ画素領域( $P_a$ )に印加される電圧と第2サブ画素領域( $P_b$ )に印加される電圧を互いに異ならせることができる。つまり、 $d_{2a}$ 、 $d_{2b}$  を調節して  $C_{gda}'$  を  $C_{gdb}'$  より大きくすれば、キックバック現象による電圧下落値である  $V_{pa}'$  と  $V_{pb}'$  の間に  $V_{pa}' > V_{pb}'$  の関係が成立する。よって、第1サブ画素領域( $P_a$ )には第2サブ画素領域( $P_b$ )より低い電圧が印加される。

#### 【0041】

このように、第1サブ画素領域( $P_a$ )に第2サブ画素領域( $P_b$ )より低い電圧が印加される際に視野角側面にどんな現象が発生するかについて検討する。第1サブ画素領域( $P_a$ )と第2サブ画素領域( $P_b$ )との間には、印加される電圧が異なるので二つのサブ画素領域( $P_a$ 、 $P_b$ )内に位置する液晶分子の傾斜角が互いに異なる。従って、図5に示すように、印加された電圧に対する透過率の関係曲線、つまりV-T曲線は互いに異なる。これによって、二つの領域( $P_a$ 、 $P_b$ )の光学的特性が互いに効果的に補償されて視野角が広くなる。

#### 【0042】

添付した図面に示される一実施例を参照して本発明について説明したが、これは例に過ぎず、当該技術分野における通常の知識を有する者ならば様々な変形や均等な他の実施例を実施することができる。従って、本発明の保護範囲は添付の請求範囲によって決まるべきである。

#### 【図面の簡単な説明】

#### 【0043】

【図1】本発明の第1実施例による液晶表示装置用薄膜トランジスタ基板の配置図である。

【図2】図1のII-II'線による断面図である。

【図3】図1の薄膜トランジスタ基板を適用した液晶表示装置用トランジスタ基板の等価回路図である。

【図4】キックバック現象によるデータ電圧の下落を示すものである。

【図5】印加された電圧に対する透過率の関係曲線である。

【図6】本発明の第2実施例による液晶表示装置用トランジスタ基板の配置図である。

【図7】図6のVI-VII'線による断面図である。

【図8】図6の薄膜トランジスタ基板を適用した液晶表示装置用トランジスタ基板の等価回路図である。

#### 【符号の説明】

#### 【0044】

123 ゲート電極

173a 第1ソース電極

10

20

30

40

50

- |         |            |

|---------|------------|

| 1 7 3 b | 第 2 ソース電極  |

| 1 7 5 a | 第 1 ドレーン電極 |

| 1 7 5 b | 第 2 ドレーン電極 |

| 1 9 0 a | 第 1 画素電極   |

| 1 9 0 b | 第 2 画素電極   |

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 損 廷 昊

大韓民国ソウル市江南区三成2洞ハンソルアパート102棟504号

(72)発明者 巖 允 成

大韓民国京畿道龍仁市水枝邑上 ヒョン 里双龍アパート216棟1702号

F ターム(参考) 2H090 JB02 KA05 KA07 KA14 LA01 LA03 LA04

2H092 GA11 JA34 JA37 JA41 JB22 JB31 NA01 NA25 PA01 PA06

QA07 QA09 QA13

5C094 AA12 AA48 BA03 BA43 CA19 DA13 DB05 EA04 ED14 FA01

FA02

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于液晶显示器件的薄膜晶体管基板                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP2004163943A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2004-06-10 |

| 申请号            | JP2003380247                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2003-11-10 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| [标]发明人         | 柳在鎮<br>李仲熙<br>損廷昊<br>嚴允成                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 柳在鎮<br>李仲熙<br>損廷昊<br>嚴允成                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G02F1/1333 G02F1/1343 G02F1/136 G02F1/1362 G02F1/1368 G09F9/30 G09F9/35 H01L27/12<br>H01L27/13                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| CPC分类号         | G02F1/1368 G02F1/13624 G02F2001/134345 H01L27/1255                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| FI分类号          | G02F1/1343 G02F1/1333.500 G09F9/30.338 G09F9/35                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 2H090/JB02 2H090/KA05 2H090/KA07 2H090/KA14 2H090/LA01 2H090/LA03 2H090/LA04 2H092<br>/GA11 2H092/JA34 2H092/JA37 2H092/JA41 2H092/JB22 2H092/JB31 2H092/NA01 2H092/NA25<br>2H092/PA01 2H092/PA06 2H092/QA07 2H092/QA09 2H092/QA13 5C094/AA12 5C094/AA48 5C094<br>/BA03 5C094/BA43 5C094/CA19 5C094/DA13 5C094/DB05 5C094/EA04 5C094/ED14 5C094/FA01<br>5C094/FA02 2H092/JB46 2H190/JB02 2H190/KA05 2H190/KA07 2H190/KA14 2H190/LA01 2H190<br>/LA03 2H190/LA04 |         |            |

| 优先权            | 1020020070706 2002-11-14 KR                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

### 摘要(译)

本发明的目的是提供一种具有优异的可见性的多域液晶显示装置和用于其的晶体管基板。解决方案：绝缘基板，在第一方向上形成在绝缘基板上的第一信号线和在第二方向上形成在绝缘基板上的第二信号线，以便与第一信号线绝缘并相交。信号线，连接至第一信号线和第二信号线的第一薄膜晶体管，连接至第一信号线的第二薄膜晶体管和连接至第一薄膜晶体管的第二信号线，第一薄膜晶体管连接到第二薄膜晶体管的第一像素电极，连接到第二薄膜晶体管的第二像素电极，在第一薄膜晶体管的第一漏极和栅极之间形成的第一电容，提供一种薄膜晶体管基板，该薄膜晶体管基板在第二漏极和第二漏极之间形成有不同的第二电容。[选择图]图2