特開2001 - 215469

(P2001 - 215469A)

(43)公開日 平成13年8月10日(2001.8.10)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I           | テマコード (参考)      |

|--------------------------|------|---------------|-----------------|

| G 0 2 F 1/133            | 550  | G 0 2 F 1/133 | 550 2 H 0 9 3   |

| G 0 9 G 3/20             | 611  | G 0 9 G 3/20  | 611 A 5 C 0 0 6 |

|                          | 622  |               | 622 D 5 C 0 8 0 |

|                          | 3/36 |               | 3/36            |

審査請求 有 請求項の数 40 L (全 15数)

(21)出願番号 特願2000 - 28079(P2000 - 28079)

(22)出願日 平成12年2月4日(2000.2.4)

(71)出願人 000004237

日本電気株式会社

東京都港区芝五丁目7番1号

(72)発明者 奥苑 登

東京都港区芝五丁目7番1号 日本電気株式会社内

(72)発明者 古賀 弘一

東京都港区芝五丁目7番1号 日本電気株式会社内

(74)代理人 100108578

弁理士 高橋 詔男 (外3名)

最終頁に続く

(54)【発明の名称】 液晶表示装置

**(57)【要約】**

**【課題】** 複数ライン反転駆動により低消費電力であつて、回路構成を複雑化させずに横縞を防止できる液晶表示装置を提供する。

**【解決手段】** 液晶セルの書き込み電圧極性を複数ライン毎に反転させた場合、極性が反転するnラインではドレインラインの充電が必要となってドレインライン波形の立ち上がりが鈍る(t3 ~ t4)。一方、n+1ラインではnラインの書き込みでドレインラインが充電されるため波形鈍りは生じない(t8 ~ t9)。このため、両ラインで液晶セルの書き込み状態に違いが出て横縞となる。そこで、クロック信号VCKの立ち上がり(t1)で出力イネーブル信号/VOEを“H”として、本来“H”になるはずのゲートラインを“L”にしたまま所定時間Aが経過してから“H”として(t4)液晶セルの書き込みを開始させる。こうすることで、波形鈍りの期間に書き込みが行われず、書き込み状態が全てのラインで同一となって横縞は生じない。

**【特許請求の範囲】**

【請求項1】 液晶セルとスイッチ手段を備えた画素が走査線とデータ線の交差位置に配置され、前記走査線に駆動信号を供給して前記スイッチ手段をオンオフする走査線駆動手段と、映像データに対応した書き込み信号を前記データ線及び前記スイッチ手段から前記液晶セルに供給するデータ線駆動手段とを有し、前記書き込み信号の極性を複数の走査線毎に反転させる液晶表示装置において、

前記走査線駆動手段は、前記書き込み信号の極性が反転する走査線について、前記データ線駆動手段が前記データ線の電圧の極性とは逆極性の書き込み信号の供給を該データ線に対して開始してから所定時間後より前記駆動信号を供給し、該走査線と同じ極性の書き込み信号が供給される後続の走査線について、前記書き込み信号の極性が反転する走査線について前記駆動信号が供給される時間と同じ時間だけ前記駆動信号を供給することを特徴とする液晶表示装置。

【請求項2】 液晶セルとスイッチ手段を備えた画素が走査線とデータ線の交差位置に配置され、前記走査線に駆動信号を供給して前記スイッチ手段をオンオフする走査線駆動手段と、映像データに対応した書き込み信号を前記データ線及び前記スイッチ手段から前記液晶セルに供給するデータ線駆動手段とを有し、前記書き込み信号の極性を複数の走査線毎に反転させる液晶表示装置において、

前記走査線駆動手段は、同じ極性の書き込み信号が供給される複数の走査線のうち、前記書き込み信号の極性が反転する走査線以外の後続の走査線について、前記書き込み信号の極性が反転する走査線について前記駆動信号が供給される時間よりも所定時間短かい時間だけ前記駆動信号を供給することを特徴とする液晶表示装置。

【請求項3】 液晶セルとスイッチ手段を備えた画素が走査線とデータ線の交差位置に配置され、前記走査線に駆動信号を供給して前記スイッチ手段をオンオフする走査線駆動手段と、映像データに対応した書き込み信号を前記データ線及び前記スイッチ手段から前記液晶セルに供給するデータ線駆動手段とを有し、前記書き込み信号の極性を複数の走査線毎に反転させる液晶表示装置において、

前記走査線駆動手段及び前記データ線駆動手段は、前記書き込み信号の極性が反転する走査線については、前記映像データが供給されない無効期間の範囲内で決められた一定時間だけ1水平期間よりも長い期間内でそれぞれ前記駆動信号及び前記書き込み信号を供給し、該走査線と同じ極性の書き込み信号が供給される後続の走査線については、前記一定時間だけ1水平期間よりも短かい期間内でそれぞれ前記駆動信号及び前記書き込み信号を供給することを特徴とする液晶表示装置。

【請求項4】 前記走査線駆動手段は、前記駆動電圧

を前記走査線に供給するか否かを制御するための出力イネーブル信号に従って、前記駆動信号を供給する期間を調整するようにしたことを特徴とする請求項1乃至3の何れかの項記載の液晶表示装置。

**【発明の詳細な説明】**

**【0001】**

【発明の属する技術分野】本発明はドットマトリクス構成の液晶表示装置に関し、特に、液晶セルに印加する書き込み電圧の極性を複数の走査線（ライン）毎に反転させるようにしたアクティブマトリクス型の液晶表示装置に関するものである。

**【0002】**

【従来の技術】一般的に用いられている液晶表示装置としては、STN（Super Twisted Nematic）型のものやTFT（Thin Film Transistor；薄膜トランジスタ）型のものなどが代表的である。このうち、STN型の液晶表示装置では単純マトリクス駆動を行っている。すなわち、単純マトリクス駆動では、スイッチング素子を設けることなく電極と液晶とで液晶パネルを構成し、マトリクス状に配置された各画素の液晶を走査信号に同期して直接時分割駆動している。

【0003】一方、TFT型の液晶表示装置ではアクティブマトリクス駆動を行っている。すなわち、アクティブマトリクス駆動では、TFT等の能動素子から成るスイッチング素子を画素毎に配置することで、オン画素とオフ画素を分離しつつオン画素に印加する電圧を保持可能として、マトリクス状に配置された各画素の液晶を走査信号に同期して時分割駆動している。このようにすることで、コントラストやレスポンス等が良好で高画質かつ大容量表示を容易に実現できることから、最近ではアクティブマトリクス型の液晶表示装置が主流になってきている。

【0004】そこでこれ以後は、アクティブマトリクス型の液晶表示装置を前提として話を進める。まず、液晶表示装置では線順次駆動を行っており、画面最上辺の走査線から最下辺の走査線に向かって走査線を順に駆動してゆくことで1画面分の映像を表示している。なお、この1画面を一般にフレーム（フィールドとも言う）と呼んでいる。また液晶表示装置では、液晶セルを駆動するにあたって、液晶材料が劣化してしまわないように、液晶セルに印加する書き込み電圧の極性を所定期間毎に反転させて交流駆動するようにしている。

【0005】ここで、書き込み電圧の極性を反転させるタイミングとしてはフレーム単位で行う場合、走査線単位で行う場合、画素（ドット）単位で行う場合があり、それぞれフレーム反転駆動、ライン反転駆動、ドット反転駆動と呼んでいる。このうち、フレーム反転駆動は最も基本的な駆動手法であって、各画素に印加する書き込み電圧の極性をフレーム毎に変えてやるものである。つまり、あるフレームで特定の画素を正極性で駆動したの

であれば、1フレーム分の駆動を行った次のフレームで再びこの画素を駆動するときには負極性で駆動するというものである。

【0006】一方、ライン反転駆動およびドット反転駆動は各フレーム内でも極性を反転させるようにしたものである。このうちのライン反転駆動（正確には、1ライン反転駆動）によると、或る走査線を正極性で駆動したのであれば、この走査線の直下にある次の走査線については負極性で駆動し、さらに次の走査線については再び正極性で駆動することになる。一方、ドット反転駆動は各走査線上の画素毎に極性を反転させるものであって、互いに隣接する2個の液晶セルを単位として書き込み電圧の極性が交互に切り替わってゆくものである。

10

#### 【0007】

【発明が解決しようとする課題】ところで、書き込み電圧の極性を反転させた場合、この書き込み電圧を液晶セルに供給するためのドレインラインを負極性の電圧から正極性の電圧に充電し、あるいは、これとは逆に正極性の電圧から負極性の電圧に放電する必要がある。このため、ライン反転駆動を行うとドレインラインの充放電が頻繁に行われて消費電力が大きくなってしまう。とりわけ、上述したように1走査線毎に書き込み電圧の極性を反転させるようにすると消費電力の増大が顕著である。

20

【0008】一方、フレーム反転駆動にすれば消費電力を低減できるが、この場合には1フレームの期間にわたって同一極性の電圧が液晶セルに保持され続けるため、TFTの漏れ電流によって画素の表示階調が乱れるといった別の問題が生じてしまう。こうしたことから、最近では折衷案として、複数ライン毎に書き込み電圧の極性を反転させる「複数ライン反転駆動」が採用されてきている。しかしながら、こうした複数ライン反転駆動にも以下に述べるような問題がある。

30

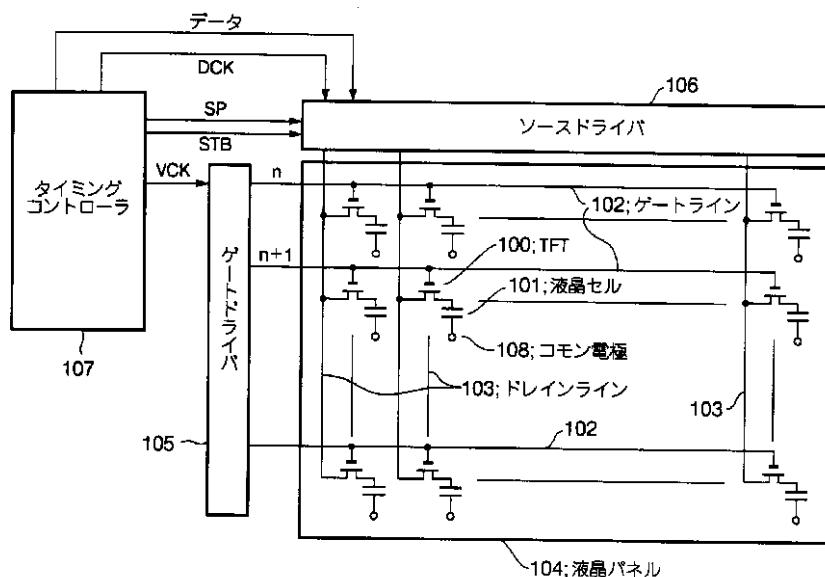

【0009】ここで、図9は従来の技術による液晶表示装置の構成の要部を示しており、ここでは従来の問題点を説明するために必要な事項についてのみ説明する。まず、図中のTFT100、液晶セル101は個々の画素を構成している。各画素は、行方向（走査線方向）に走る複数のゲートライン102と列方向に走る複数のドレインライン103が交差する位置に配列され、これらによつて液晶パネル104を形成している。

40

【0010】ゲートドライバ105は、ゲートライン102に駆動電圧を順次供給してゆくことで各ゲートラインに接続されたTFT100の導通状態を制御している。また、ソースドライバ106は書き込み電圧をドレインライン103に供給することで、ゲートドライバ105の駆動するTFT100を通じて各液晶セル101に書き込みを行う。さらに、タイミングコントローラ107は各種の制御信号をゲートドライバ105及びソースドライバ106に送出する。なお、液晶セル101の一端が接続されたコモン電極108には一定電圧が印加

50

されている。

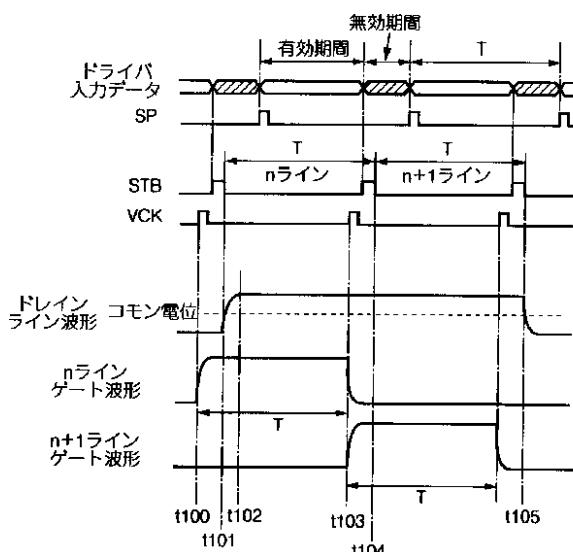

【0011】次に、図10は図9に示した液晶表示装置で2ライン反転駆動を行ったときのタイミング波形を示したものである。図中、クロック信号VCKはゲートドライバ105がゲートライン102を順次活性化させるためのものである。また、ラッチパルス信号STBは、ソースドライバ106が取り込んだ1走査線分の映像データをドレインライン103へ送出するためのタイミング信号である。そしてここでは、図10に示したタイミングに対応したフレームの直前のフレームにおいて、n番目及びn+1番目の走査線に何れも負極性の書き込み電圧が印加されていたものとする。なお、n番目の走査線（ゲートライン）をこれ以後の説明では単に「nライン」と呼ぶこととし、これ以外の走査線についても同様とする。

【0012】まず、時刻t100でクロック信号VCKが立ち上ると、「nラインゲート波形」で示した駆動電圧をnラインへ印加してこのゲートラインに接続された画素を選択する。次に、時刻t101でラッチパルス信号STBが立ち下がると、nライン上の映像データに対応した書き込み電圧をドレインライン103に印加して、このnラインに接続された液晶セル101への書き込みを開始する。

20

【0013】ところが、この場合は書き込み電圧の極性が反転した直後であって、液晶セル101の容量に加えてドレインライン103の持つ容量を充電（なお、正極性の書き込み電圧から負極性の書き込み電圧へ遷移する場合には放電）しなければならない。このため、ドレインライン103の電圧が負極性の書き込み電圧から徐々に正極性の書き込み電圧へと立ち上がってゆき、時刻t102になってようやく電圧の上昇が止まる。

30

【0014】その後、画面上の1水平期間に相当する時間Tが時刻t100から経過して時刻t103になると、nラインに対して駆動電圧が印加されなくなって、その代わりに「n+1ラインゲート波形」で示された駆動電圧がn+1ラインへ印加されるようになる。次に、時刻t104でラッチパルス信号STBが立ち下がると、nラインの場合と同様にして、映像データに対応した書き込み電圧がドレインライン103へ供給されるようになる。

40

【0015】もっとも、この時点ではnラインへの書き込みによってドレインライン103が既に正極性の電圧に充電されている。このため、n+1ラインでは液晶セル101の容量だけを充電（放電）すれば良くなり、ドレインライン波形はほぼ同電位のままのフラットな波形となる。そして、時刻t104から時間Tが経過した時刻t105でラッチパルス信号STBが立ち下がると、n+2ラインへの書き込みのためにドレインライン3が正極性の電圧から負極性の電圧に遷移する。

50

【0016】以上のように、nラインではドレインライ

ン103の持つ容量を充電するための時間が余分にかかるため、ドレインライン波形の立ち上がり部分で波形鈍りが生じてしまう（時刻t101～t102）。一方、n+1ラインではドレインライン103の持つ容量を充電する必要がないことから、nラインのときのようにドレインライン波形に波形鈍りが生じることもなくなる（時刻t104～）。

【0017】こうした相違にも拘わらず、従来の液晶表示装置では各ゲートラインを同じように駆動しており、各走査線における書き込み期間が常に一定時間Tとなっている。このため、例えばnラインとn+1ラインとは液晶セル101への書き込み状態が異なってくる。というのも、n+1ラインに接続された液晶セルの保持電圧は、書き込み期間が十分であるため、ソースドライバ106が出力する映像データに対応した電圧まで到達する。一方、nラインに接続された液晶セルの保持電圧は、波形鈍りの影響で実質的な書き込み期間が十分確保されなくなって、映像データに対応した電圧まで達しない。

【0018】ここで、液晶セルの保持電圧が下がるとそれだけ画素の輝度も低くなるため、nラインの輝度はn+1ラインの輝度よりも下がってしまう。こうした現象が他の走査線でも生じるため、画素の輝度が1走査線毎に違ってきて画面上で横筋（横縞）となって現れてくる。このことは、液晶表示装置を高解像度にして1水平期間（時間T）を短くすればするほど、ドレインライン波形における立ち上がり部分の影響が無視しえなくなるため、それだけ横縞も顕著になってくる。

【0019】ところで、特開平9-15560号公報（以下「公知例」という）では、書き込み電圧の極性が反転する走査線について、1水平期間の長さをこれ以外の走査線のものよりも広げている。こうすると、同極性での書き込みの場合と反対の極性での書き込みの場合とで書き込み状態の差が減少して、横縞の発生も緩和されるものと考えられる。

【0020】しかしながら、上記公知例のように1水平期間の長さそのものを変えるには、液晶表示装置内で基準となるクロック信号（以下「基準クロック信号」という）の周期を可変させなければならない。しかるに、一般的な液晶表示装置では1水平期間が一定であることを前提として回路設計が行われている。したがって、基準クロック信号の周期を可変にしてしまうと、回路構成（特に、図9に示したタイミングコントローラ107に相当する回路ブロック）が複雑化してしまうのは避けがたい。

【0021】また、上記公知例のすると次のような問題もある。すなわち上記公知例では、書き込み電圧の極性が反転する走査線についてはその水平走査期間を所定の時間幅だけ広げている。しかし、1フレーム内の走査線の本数は一定かつ不变であることから、広げた時間幅を

補償するにはこれ以外の走査線の水平走査期間を縮めてやらなければいけない。例えば、上記公知例では3走査線毎に書き込み電圧の極性を反転させているため、3本の走査線のうちの2本の走査線についてそれぞれ水平走査期間を狭める必要がある。

【0022】ここで、水平走査期間が短縮されても同じ画素数分の映像データを液晶セルへ書き込むためには、映像データを取り込むためのクロック信号（以下「データ取り込みクロック信号」という）の周波数を上げてやる必要がある。ところが、上記公知例では書き込み電圧の極性が反転する走査線の水平走査期間を1.1倍～1.4倍程度にまで広げている。このため、装置内の各部（特に、図9に示したタイミングコントローラ107及びソースドライバ106に相当する回路ブロック）について動作周波数をかなりの程度上げねばならず、回路設計やレイアウト設計を行う上での障害となる。のみならず、動作周波数が上がることでEMI（Electro-Magnetic Interference；電磁妨害）ノイズの対策といったことが必要になるのは必定である。

【0023】本発明は上記の点に鑑みてなされたものであって、その目的は、複数ライン反転駆動によって消費電力が低く、しかも、タイミングコントローラ等の回路構成を複雑化させることなく横縞の発生を防止して高画質表示が可能な液晶表示装置を提供することにある。

#### 【0024】

【課題を解決するための手段】以上の課題を解決するために、請求項1記載の発明は、液晶セルとスイッチ手段を備えた画素が走査線とデータ線の交差位置に配置され、前記走査線に駆動信号を供給して前記スイッチ手段をオンオフする走査線駆動手段と、映像データに対応した書き込み信号を前記データ線及び前記スイッチ手段から前記液晶セルに供給するデータ線駆動手段とを有し、前記書き込み信号の極性を複数の走査線毎に反転させる液晶表示装置において、前記走査線駆動手段は、前記書き込み信号の極性が反転する走査線について、前記データ線駆動手段が前記データ線の電圧の極性とは逆極性の書き込み信号の供給を該データ線に対して開始してから所定時間後より前記駆動信号を供給し、該走査線と同じ極性の書き込み信号が供給される後続の走査線について、前記書き込み信号の極性が反転する走査線について前記駆動信号が供給される時間と同じ時間だけ前記駆動信号を供給することを特徴としている。

【0025】また、請求項2記載の発明は、液晶セルとスイッチ手段を備えた画素が走査線とデータ線の交差位置に配置され、前記走査線に駆動信号を供給して前記スイッチ手段をオンオフする走査線駆動手段と、映像データに対応した書き込み信号を前記データ線及び前記スイッチ手段から前記液晶セルに供給するデータ線駆動手段とを有し、前記書き込み信号の極性を複数の走査線毎に反転させる液晶表示装置において、前記走査線駆動手段

は、同じ極性の書き込み信号が供給される複数の走査線のうち、前記書き込み信号の極性が反転する走査線以外の後続の走査線について、前記書き込み信号の極性が反転する走査線について前記駆動信号が供給される時間よりも所定時間短かい時間だけ前記駆動信号を供給することを特徴としている。また、請求項3記載の発明は、液晶セルとスイッチ手段を備えた画素が走査線とデータ線の交差位置に配置され、前記走査線に駆動信号を供給して前記スイッチ手段をオンオフする走査線駆動手段と、映像データに対応した書き込み信号を前記データ線及び前記スイッチ手段から前記液晶セルに供給するデータ線駆動手段とを有し、前記書き込み信号の極性を複数の走査線毎に反転させる液晶表示装置において、前記走査線駆動手段及び前記データ線駆動手段は、前記書き込み信号の極性が反転する走査線については、前記映像データが供給されない無効期間の範囲内で決められた一定時間だけ1水平期間よりも長い期間内でそれぞれ前記駆動信号及び前記書き込み信号を供給し、該走査線と同じ極性の書き込み信号が供給される後続の走査線については、前記一定時間だけ1水平期間よりも短かい期間内でそれぞれ前記駆動信号及び前記書き込み信号を供給することを特徴としている。

【0026】また、請求項4記載の発明は、請求項1乃至3の何れかの項記載の発明において、前記走査線駆動手段は、前記駆動電圧を前記走査線に供給するか否かを制御するための出力イネーブル信号に従って、前記駆動信号を供給する期間を調整するようにしたことを特徴としている。

#### 【0027】

【発明の実施の形態】以下、図面を参照して本発明の実施形態について順次説明してゆく。

##### 〔第1実施形態〕

###### (1) 構成の説明

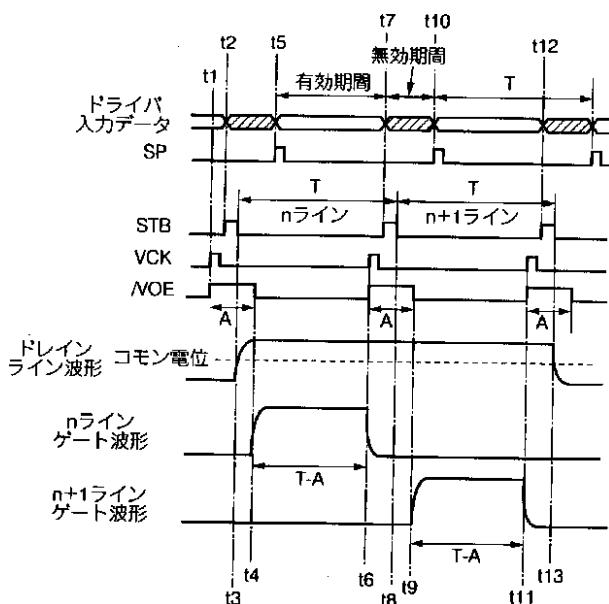

図1は本実施形態による液晶表示装置の構成の要部を示したものである。図中の符号1は液晶パネルであって、行方向に走るゲートライン $2_n$ 、ゲート $2_{n+1}$ 、…、 $2_{n+m}$ および列方向に走るドレインライン $3_1$ 、…、 $3_m$ がそれぞれ配線されている。

【0028】このうち、各ゲートラインはそれぞれ走査線に対応している。また、ドレインライン $3_1$ には液晶パネル1上で画面表示を行うための映像データが供給される。このため、ドレインライン $3_1$ はデータ線などと呼ばれることがある。そして、ゲートライン及びドレインラインが互いに交差する位置には画素がマトリクス状に配置されている。

【0029】これらの各画素はTFT4および液晶セル5によって構成されている。このうち、TFT4のゲート端子、ドレイン端子、ソース端子はそれぞれゲートライン $2_n$ 等、ドレインライン $3_1$ 、液晶セル5の一端に接続されている。一方、液晶セル5はその一端がTFT4

10 のソース端子に接続され、その他端がコモン電極6に接続されている。この液晶セル5は1ドット分の表示を行うほか、ソースドライバ9（後述）からドレンライン3を通じて供給される書き込み電圧を保持するための容量を構成している。

【0030】ここで、液晶セル5を通過する光の透過率は印加される書き込み電圧のレベルに応じて変化するため、この性質を利用して書き込み電圧のレベルを適宜変えてやれば、画素の輝度を所望の状態に設定することができる。また、コモン電極6には一定電圧として例えば7Vが印加されており、この一定電圧を基準にして液晶セル5に対する書き込み電圧の極性（正極性または負極性）が定まる。例えば本実施形態では、正極性の書き込み電圧を8~13V、負極性の書き込み電圧を1~6Vとしており、各極性においてコモン電極6の電位7Vからの差電圧（1V~6V）の範囲内で画素の輝度を変えられる。

【0031】そして、何れかのゲートラインに駆動電圧を印加してこれに接続されたTFT4をオンさせれば、ドレンライン3を通じて供給される映像データの書き込み電圧が、各TFT4に接続された液晶セル5の容量に印加されて該容量に電荷が書き込まれてゆく。また、ゲートラインに駆動電圧が印加されなくなってTFT4がオフしても、液晶セル5は再び書き込みが行われるまでの1フレームの期間中は書き込み電圧を保持しており、この保持電圧によって液晶パネル1上の表示が継続的に行われる。

【0032】なお、液晶パネル1は対向する2枚のガラス基板を備えており、これらガラス基板の間に液晶が封入されている。そして一方のガラス基板には、TFT4が配置されるとともにゲートライン $2_n$ 等およびドレンライン3が配線されている。また、他方のガラス基板にはフィルタとコモン電極6が配置されており、液晶表示装置がカラーであればフィルタとしてRGBの3原色のカラーフィルタが設けられる。ここで、本明細書では液晶パネル1の解像度がSXGA（Super eXtended Graphics Array）規格（1280ドット×1024ドット）に準拠しており、フレーム周波数が60Hzであるとして話を進める。したがって、ドレンライン3はRGB各色について1280本、ゲートラインは1024本となる。

【0033】次に、ゲートドライバ7は走査線方向の駆動を受け持っており、タイミングコントローラ8（後述）から供給されるクロック信号VCKに同期して、パルス状の駆動電圧（以下「ゲートパルス信号」という）をゲートライン $2_n$ 等に順番に供給してこれらゲートラインを線順次駆動する。したがって、ゲートドライバ7が各ゲートラインにゲートパルス信号を印加している期間（つまり、ゲートパルス信号のパルス幅）が、液晶セル5に対する書き込み期間となる。

【0034】また、ゲートドライバ7はタイミングコントローラ8から供給される出力イネーブル信号/V<sub>O E</sub>に応じて、ゲートライン2n等へゲートパルス信号を供給するかどうかを制御している。すなわち、出力イネーブル信号/V<sub>O E</sub>がローレベル（以後は“L”と略記する）であればゲートドライバ7はゲートライン2n等へゲートパルス信号を印加し、出力イネーブル信号/V<sub>O E</sub>がハイレベル（以後は“H”と略記する）であればゲートパルス信号を印加しない。なお、記号「/」は反転信号であることを意味する。

【0035】次に、タイミングコントローラ8はドットクロック信号DCK、ラッチパルス信号STB、クロック信号VCK、出力イネーブル信号/V<sub>O E</sub>、映像データをそれぞれ生成し、これらをゲートドライバ7及びソースドライバ9に送出することによって液晶パネル1における画面表示を制御するようにしている。なお、これら信号のタイミングの詳細については動作説明の際に明らかにするので、ここでは詳しく説明しない。

【0036】次に、ソースドライバ9はシフトレジスタ、ラッチ及びドライバ回路（いずれも図示を省略）を内蔵している。なお、これらシフトレジスタ等は何れも1走査線分の映像データ（ここでは1280ドット分）に対応した構成となっている。そしてソースドライバ9は、タイミングコントローラ8から供給されるスタートパルス信号SP及びドットクロック信号DCKに基づいて、スタートパルス信号SPに与えられたパルスの立ち上がり時点からドットクロック信号DCKに従って映像データを1画素ずつ順次シフトレジスタに取り込んでいく。

【0037】そして、ソースドライバ9は1走査線分の映像データを取り込んだ時点でシフトレジスタへの取り込みを停止させる。また、ソースドライバ9はタイミングコントローラ8からラッチパルス信号STBのパルスが供給された場合に、その立ち上がりに同期してシフトレジスタに取り込んでおいた全ての映像データを同時にラッチへ転送する。さらに、ソースドライバ9はラッチパルス信号STBの立ち下がりに同期して、ラッチに転送された映像データを液晶セル5に対する書き込み電圧に変換してドレンインライン3へ同時に送出する。

【0038】ここで、本発明の各実施形態による液晶表示装置は複数ライン反転駆動かつドット反転駆動を行っており、こうした駆動態様を「複数ラインドット反転駆動」と呼んでいる。例えば2ラインドット反転駆動を行う場合は、図2に示したような書き込み電圧の極性で個々の画素を駆動することになる。同図は、液晶パネル1の左上隅の近傍について、或る1フレーム内で各画素に書き込まれた映像データの電圧の極性を示したものである。図示したように、nラインについては左端の画素から順に正極性、負極性の電圧が繰り返し書き込まれ、n+1ラインについてもnラインと全く同様の極性の電圧

が書き込まれる。

【0039】一方、n+2ラインおよびn+3ラインについてはnライン及びn+1ラインと正反対の極性の電圧が書き込まれており、左端の画素から負極性、正極性の電圧が繰り返し書きされている。そして、n+4ライン以降はnライン～n+3ラインと同様の書き込みが繰り返されてゆく。そして、図2に示したフレームの次のフレームでは、いま述べたのと極性が正反対の電圧を順次書き込んでゆく。例えば、nライン及びn+1ラインについては左端の画素から順に負極性、正極性の電圧が繰り返し書きされてゆくことになる。

【0040】(2)動作の説明

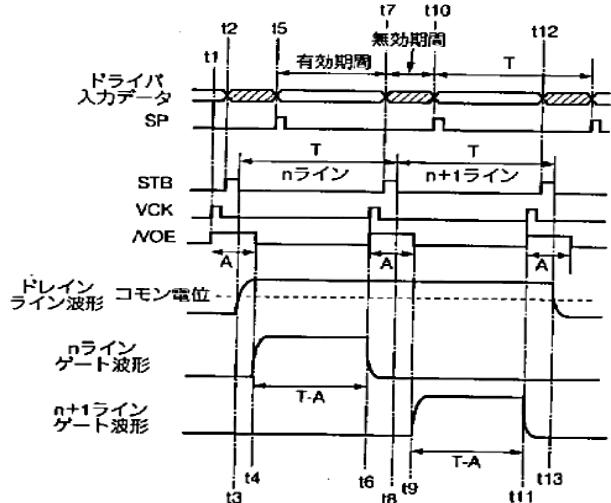

次に、本実施形態による液晶表示装置の動作を図3のタイミングチャートに沿って説明する。図3は図2に示したような2ラインドット反転駆動を行った場合について示したものである。また、図3ではドレンインライン波形の図示を簡単にするために画面上でベタ表示を行った場合について示してあり、このことはこれ以後に参照する図面でも同様である。そして本実施形態においても、直前のフレームではnライン及びn+1ラインの何れもが負極性の書き込み電圧で駆動されており、図3に示したタイミングのフレームではこれら両ラインが何れも正極性の書き込み電圧で駆動されるものとする。

【0041】図3において、「ドライバ入力データ」はタイミングコントローラ8からソースドライバ9に供給される映像データであって、1水平期間に相当する時間T（上述したSXGA, 60Hzの場合では15.6μs）を周期として1走査線分の映像データが供給される。ここで、1水平期間は有効期間および無効期間（INVALID期間とも言う）から構成されており、例えば有効期間は11.9μs、無効期間は3.7μsである。そして、有効期間は実際に映像データが供給される期間であり、また、1走査線上にある1280ドットの映像データをこの有効期間内に取り込むために、上述したドットクロックDCKの周波数は約108MHzに設定している。

【0042】一方、無効期間はCRT（Cathode Ray Tube）ディスプレイ等で用いられている水平帰線消去期間に相当するものであって、液晶表示装置では本来必要な期間ではあるが、CRTディスプレイ等との互換性をとるために設けてある。そして、スタートパルス信号SPに与えられたパルスの立ち上がりが有効期間の始まりであって、この有効期間が終了した時点から無効期間が始まる。また、スタートパルス信号SPの立ち上がりから時間Tだけ経過して再びスタートパルス信号SPにパルスが与えられるようになると新たな有効期間が始まる。

【0043】さて、まず時刻t1以前ではソースドライバ9がnラインの映像データをドットクロック信号DCKに従って取り込んでいる。そして時刻t1になるとタ

タイミングコントローラ8はクロック信号VCKにパルスを発生させる。すると、ゲートドライバ7はクロック信号VCKの立ち上がりに同期してゲートパルス信号をソフトさせる。

【0044】これによって、本来であればゲートドライバ7はゲートライン2nに供給する駆動電圧を立ち上げることになる。ところがこの場合、タイミングコントローラ8は出力イネーブル信号/VOEとして時間Aの幅を持ったパルスを同時刻t1から発生させている。このため、ゲートドライバ7はゲートライン2nに対するゲートパルス信号の供給を停止して、図3に示したようにnラインゲート波形を“L”のまま維持する。

【0045】次に、時刻t2でタイミングコントローラ8はラッチパルス信号STBにパルスを発生させる。このとき、タイミングコントローラ8からソースドライバ9に供給される映像データは有効期間から無効期間に移行するため、ソースドライバ9は映像データをシフトレジスタへ取り込むのを止めて、これらnライン上の映像データをシフトレジスタからラッチへ転送する。なお、クロック信号VCKが立ち上がってからゲートライン波形が立ち下がりきるまでにはある程度の時間を要する（例えば、時刻t6以降のnラインゲート波形を参照）。このため、クロック信号VCKの立ち上がりをラッチパルス信号STBの立ち下がりよりも前にしておかないと、次のラインの映像データを取り込んでしまう。こうしたことから、図3では若干の余裕を持たせて、クロック信号VCKの立ち下がりをラッチパルス信号STBの立ち上がりよりも一定時間だけ前にしている。

【0046】次に、時刻t3でタイミングコントローラ8がラッチパルス信号STBを立ち下げるとき、この立ち下がりに同期して、ソースドライバ9内のドライバ回路はラッチ内の映像データに対応した正極性の書き込み電圧をドレンインライン3へ送出する。ここで、この時点までドレンインライン3は負極性の書き込み電圧になっていたため、正極性の書き込み電圧が新たに印加されることでドレンインライン3の持つ容量に対する充電が始まる。この結果、図3に示したようにドレンインライン波形が時刻t3から徐々に立ち上がってゆき、時刻t4になるとドレンインライン3の電圧がソースドライバ9から出力された書き込み電圧に達する。

【0047】一方、タイミングコントローラ8は、時刻t1から予め決めておいた時間Aが経過するのを監視しており、これに対応した時刻t4で出力イネーブル信号/VOEのレベルを“L”に戻す。これにより、ゲートドライバ7はゲートライン2nに対するゲートパルス信号の印加を開始させるため、図3に示したように「nラインゲート波形」が立ち上がる。その結果、ゲートライン2nに接続されたTFT4が何れもオンとなって、これらTFTに接続された液晶セル5に対してドレンインライン3から供給される正極性の書き込み電圧で書き込み

が行われる。

【0048】ここで、時間Aはドレンインライン波形が負極性の書き込み電圧から正極性の書き込み電圧に立ち上がるまでの時間と同じ、あるいは、これを越える時間に決めておく。理論的には、時間Aの値をソースドライバ9の駆動能力、ソースドライバ9にかかる液晶パネル1の負荷（ドレンインライン3の抵抗や容量）などに基づいて算出可能である。しかしながら、液晶パネル1やソースドライバ9の特性には装置毎にバラツキがあるため、時間Aを計算のみによって精度良く求めることは一般に困難である。

【0049】そこで、実際には時間Aの値を評価によって求めている。そのために、液晶表示装置の外部から時間Aの値を可変できるようにタイミングコントローラ8を構成しておく。そして、液晶表示装置を実際に動作させて所定のパターン（例えば全画面がベタ）を液晶パネル1上に表示させながら、時間Aを微調整して画面上で横筋が発生するかどうかを目視で確認して、横筋が消えたときの時間Aを求めるようにしている。

【0050】なお、図3ではドレンインライン波形が立ち上がりきったところ（時刻t4）を出力イネーブル信号/VOEの立ち下がりに一致させている。しかし、出力イネーブル信号/VOEが時刻t4よりも早めに（すなわち、ドレンインライン波形が立ち上がりきった辺りで）立ち下がっても、目視で評価した結果として横筋が目立たないのであれば何ら問題はない。ちなみに、出力イネーブル信号/VOEの立ち下がりを時刻t4よりも後にもしても良いが、時間Aを長くすればするほど液晶セル5に十分書き込みが行われなくなって輝度が低下する。したがって、時間Aは横筋が消える最小値の時間とすることが望ましい。

【0051】ここで、図4はSXGA, 60MHzで2ラインドット反転駆動を実施した場合について横筋の程度の目視確認結果を示したものである。液晶セル5に127階調の階調表示を行う場合、時間Aが0μsでは薄い横筋が認められるのに対して、時間Aを1.26, 2.5, 5.0μsにすることで何れの場合にも横筋はなくなる。こうしたことから、127階調表示では時間Aの最終値を1.26μsに決定すれば良い。一方、63階調表示を行う場合には時間Aを1.26μsとしても薄い横筋が発生するため、横筋がなくなる2.5μsを時間Aの最終値に決定すれば良い。

【0052】次に、図3に示した時刻t5になるとタイミングコントローラ8はスタートパルス信号SPにパルスを発生させるが、このパルスの立ち上がりに同期して有効期間に入るためソースドライバ9に対して映像データが供給されるようになる。そこで、ソースドライバ9はドットクロック信号DCKに従って映像データを順次シフトレジスタに取り込んでゆく。次に、時刻t6になると、タイミングコントローラ8は時刻t1と同様にク

ロック信号VCK及び出力イネーブル信号/VOEを立ち上げる。

【0053】これにより、ゲートドライバ7はゲートパルス信号をシフトさせてゲートライン2nに対するゲートパルス信号の供給を停止させる結果、図3のようにnラインゲート波形が立ち下がって、ゲートライン2nに接続された液晶セル5への書き込みが終了する。以上のように、書き込み電圧の極性が反転する走査線では、時間(T-A)だけ液晶セル5に書き込みが行われるようになる。そして、この後はn+1ラインについても、nラインのとき(時刻t1~t6)とほぼ同様の動作が時刻t6~t11で行われる。

【0054】すなわち、時刻t6で出力イネーブル信号/VOEが立ち上がるため、ゲートドライバ7はゲートライン2n+1へゲートパルス信号を印加しないようになる。次に、時刻t7でラッチパルス信号STBが立ち上るとn+1ライン上の映像データの取り込みが停止し、時刻t8でラッチパルス信号STBが立ち下がるとそれまでに取り込まれたn+1ラインの映像データに対応する書き込み電圧がドレインライン3に印加されるようになる。ここで、n+1ラインではドレインライン3が既に正極性の書き込み電圧で充電されており、時刻t8~t9では時刻t3~t4のようなドレインライン波形の立ち上がりは存在しない。

【0055】次に、時刻t9で出力イネーブル信号/VOEが立ち下がると、ゲートライン2n+1にゲートパルス信号が印加されるようになって当該ゲートラインに接続された液晶セル5に対する書き込みが始まる。この後は、時刻t10でn+2ラインの映像データの取り込みが始まる。また、時刻t11でゲートパルス信号がシフトしてゲートライン2n+1に対するゲートパルス信号の供給が停止してこれに接続された液晶セル5への書き込みが終了する。以上のように、n+1ラインについても時間(T-A)だけ書き込みが行われることになる。

【0056】こうして同時刻t11で2走査線分の書き込みが終了すると、この後はn+2ライン以降の走査線についてもnライン及びn+1ラインと同様にして書き込みが行われてゆく。ここで、本実施形態では2ラインドット反転駆動を行っているため、図3の時刻t13に示したようにn+2ラインではドレインライン3が負極性の書き込み電圧で駆動され、図3に示したようにドレインライン波形が正極性の書き込み電圧から負極性の書き込み電圧に遷移する。なお、n+2ライン及びn+3ラインにおける書き込み動作は、ドレインライン波形が負極性の書き込み電圧になる以外はnライン及びn+1ラインと同じである。

【0057】以上のように本実施形態によると、書き込み電圧の極性が反転する走査線では、ドレインライン3の立ち上がり又は立ち下がり期間においてゲートライン

へ駆動電圧が印加されないように、ゲートドライバ7の出力をマスクしている。そして、ドレインライン波形が立ち上がりきって平坦になった時点で、ゲートラインにゲートパルス信号を印加して液晶セル5に対する書き込みを開始させている。また、同極性で書き込みが行われるこれ以降の各走査線では、書き込み電圧の極性が反転する走査線と同じだけの書き込み期間をとるようにしている。

【0058】こうすることによって、同じ極性で書き込まれる全ての走査線について液晶セル5に対する書き込み状態を等しくできる。このため、液晶セル5に印加される書き込み電圧が全ての走査線につき同一となるため、走査線間で輝度差がなくなって横縞が発生することも無くなる。さらに、これまでの液晶表示装置(図9を参照)と比べた場合、本実施形態では出力イネーブル信号/VOEの生成論理をタイミングコントローラ8に設けるほか、ゲートドライバ7が出力イネーブル信号/VOEに従って各ゲートラインへ書き込み電圧を供給するかどうかを制御するための論理を設けるだけで良い。

【0059】なお、上述した説明では2ラインドット反転駆動について例示したが、3ライン以上の複数ラインドット反転駆動を行う場合であっても同様の動作となる。すなわち、同じ極性の書き込み電圧で駆動される3番目の走査線以後では、2番目の走査線と同じくドレインライン3が既に同じ極性で充放電されている。したがって、図3に示した時刻t6~t11における2番目の走査線と同様の動作が3番目の走査線以後でも行われることになる。

【0060】〔第2実施形態〕本実施形態による液晶表示装置の基本的な構成は第1実施形態(図1を参照)と同じであって、本実施形態ではタイミングコントローラ8における信号のタイミング制御が第1実施形態と異なっている。そこで以下、液晶表示装置の具体的動作を説明するが、本実施形態では2ラインドット反転駆動の場合と3ライン以上のラインドット反転駆動とでは動作が若干異なる。

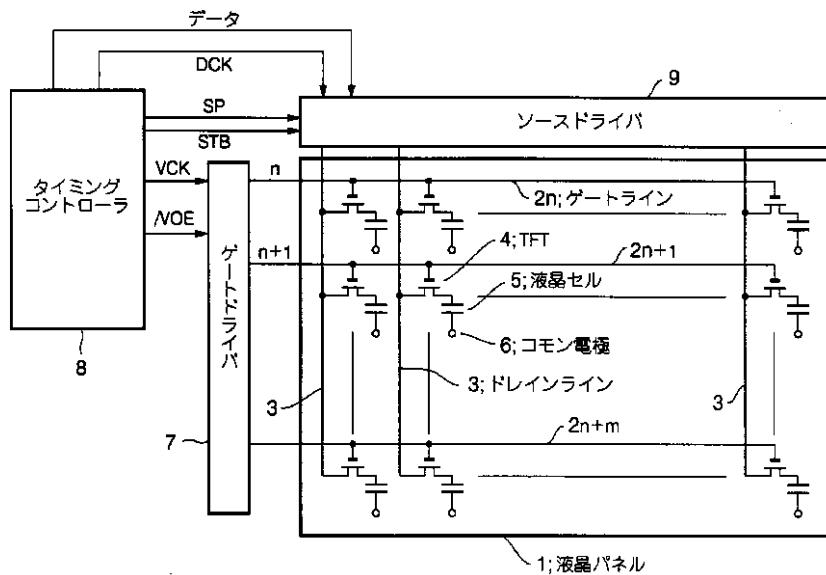

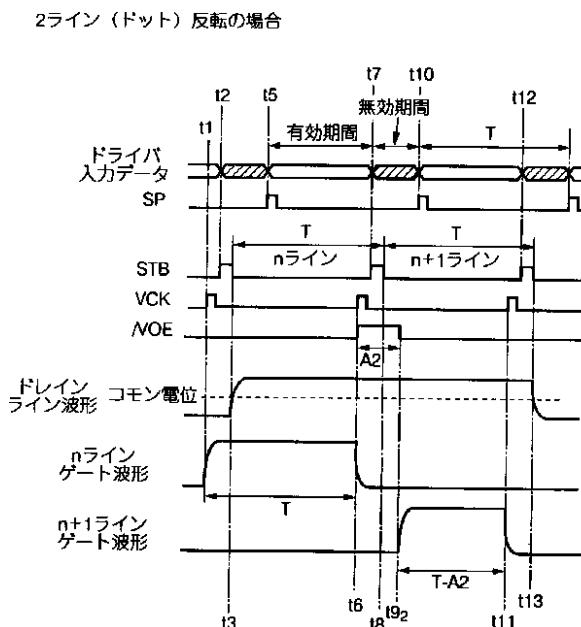

#### 【0061】(1) 2ラインドット反転駆動

そこでまず図5のタイミングチャートを参考して2ラインドット反転駆動の動作を説明する。なお、図5では図3に示した時刻に対応するものについて同一の時刻を付けている。また本実施形態でも、図5に示したタイミングの直前のフレームでは、nライン及びn+1ラインが何れも負極性の書き込み電圧によって駆動されていたものとする。

【0062】まず、時刻t1になるとタイミングコントローラ8はクロック信号VCKにパルスを発生させる。しかし、この場合は第1実施形態と違ってタイミングコントローラ8は同時刻t1で出力イネーブル信号/VOEにパルスを発生させない。このため、ゲートドライバ7はクロック信号VCKの立ち上がりに同期してゲート

パルス信号をシフトさせ、ゲートライン $2n$ に対してゲートパルス信号を供給する結果、ゲートライン $2n$ の電圧が同時刻 $t_1$ から立ち上がる。もっとも、この時点でソースドライバ9は $n$ ラインの映像データを取り込んでいる最中であって、ドレインライン3には $n-1$ ラインの映像データに対応した負極性の書き込み電圧が印加された状態になっている。

【0063】次に、時刻 $t_2$ 以降における $n$ ラインの書き込み動作は第1実施形態のものと概ね同じである。すなわち、時刻 $t_2$ でラッチパルス信号STBが立ち上がり映像データの取り込みが停止し、時刻 $t_3$ でラッチパルス信号STBが立ち下がると、 $n$ ラインの映像データに対応した正極性の書き込み電圧がドレインライン3へ供給される。この場合、本実施形態では既に時刻 $t_1$ でゲートライン $2n$ にゲートパルス信号が供給されているため、ゲートライン $2n$ に対応した液晶セル5に対して同時刻 $t_3$ から書き込みが始まる。

【0064】次に、時刻 $t_5$ でスタートパルス信号SPが立ち上ると $n+1$ ラインの映像データの取り込みが始まる。そして、時刻 $t_1$ から時間Tが経過した時刻 $t_6$ になると、タイミングコントローラ8は再びクロック信号VCKにパルスを発生させる。ただし、このときには $n$ ラインの場合とは違ってタイミングコントローラ8は出力イネーブル信号/VOEにもパルスを発生させる。

【0065】このため、ゲートドライバ7はゲートパルス信号をシフトさせてゲートライン $2n$ に対するゲートパルス信号の供給を止めるほか、ゲートライン $2n+1$ に対してゲートパルス信号を供給することもしない。こうして、同時刻 $t_6$ でゲートライン $2n$ に対応する液晶セル5への書き込みは終了する。以上のように、本実施形態では、書き込み電圧の極性が反転する走査線における書き込み期間は時間Tとなる。

【0066】そしてこれ以後は第1実施形態における $n+1$ ラインのときの動作と同様のことが行われる。ただし、本実施形態では出力イネーブル信号/VOEのパルス幅として時間Aの代わりに時間A2を用いており、 $n+1$ ラインゲート波形が立ち上がる時刻を図3に示した時刻 $t_9$ ではなく時刻 $t_{9_2}$ としてある。なお、この時間A2の値は第1実施形態における時間Aと同様にして、横縞のない画面となる最小値を目視で確認しながら求めめておく。そして、時刻 $t_7$ でラッチパルス信号STBが立ち上ると $n+1$ ラインの映像データの取り込み動作が停止し、時刻 $t_8$ でラッチパルス信号STBが立ち下がると同ラインの映像データに対応した書き込み電圧をドレインライン3に供給する。

【0067】次に、時刻 $t_6$ から時間A2が経過した時刻 $t_{9_2}$ でタイミングコントローラ8が出力イネーブル信号/VOEを立ち下げる時刻 $t_{9_2}$ はゲートドライバ7はゲートライン $2n+1$ へゲートパルス信号を印加して液晶セ

ル5への書き込みを開始させる。そしてこの後は、時刻 $t_{11}$ でクロック信号VCKが立ち上がって $n+1$ ゲートライン波形が立ち下がるまでゲートライン $2n+1$ に対する書き込みを継続する。以上のように、 $n+1$ ラインについては書き込み期間が時間(T-A2)となる。なお、時刻 $t_{11}$ からは $n+2$ ライン以降に対する書き込みとなるが、例えば $n+2$ ライン及び $n+3$ ラインの書き込み動作は、ドレインライン波形が負極性の書き込み電圧になる以外は $n$ ライン及び $n+1$ ラインと同じである。

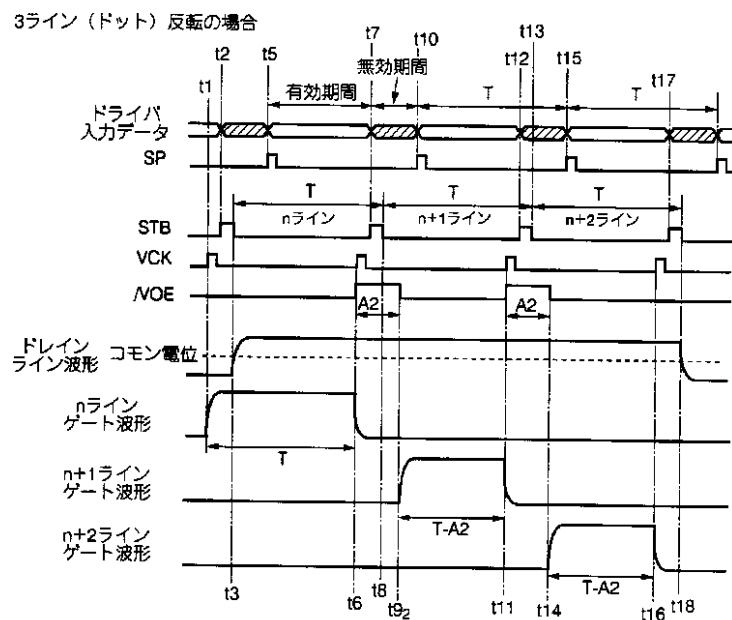

【0068】(2) 3ラインドット反転駆動

次に、図6のタイミングチャートを参照しながら3ラインドット反転駆動の場合について具体的な動作を説明する。なお、図6では図5に示した時刻に対応するものについては同一の時刻を付けている。3ラインドット反転駆動の場合も、図6の時刻 $t_1 \sim t_{11}$ における動作は図5に示したこれら時間帯の動作と全く同じである。

【0069】そして、時刻 $t_{11} \sim t_{18}$ では $n+2$ ラインに対して同じ正極性の書き込み電圧による書き込み動作が実施されるが、この期間中の動作は、書き込み対象が $n+1$ ラインではなく $n+2$ ラインである点を除いて図5に示した時刻 $t_6 \sim t_{13}$ の動作と同じである。要するに、書き込み電圧の極性が反転する走査線以外の走査線では、ドレインライン3が既に正極性の書き込み電圧に充電されているため、何れについても書き込み期間を時間(T-A2)とすれば良い。このことは4ライン以上のラインドット反転駆動を行う場合も同様である。

【0070】以上のように本実施形態では、ドレインラインの立ち上がりによる影響で $n$ ラインにおける書き込みが不十分となっている分、これと同じ極性の書き込み電圧で駆動される $n+1$ ライン以降の走査線については書き込み期間を均等に短くしている。そのため例えば2ラインドット反転駆動では、 $n+1$ ラインの書き込みにおいて、ゲートライン $2n+1$ に供給するゲートパルス信号の立ち上げタイミングを出力イネーブル信号/VOEによって時間A2だけ遅らせている。こうすることで、全ての走査線に対して同一の書き込み状態とすることが可能となり、走査線間の輝度差による横筋が発生しなくなる。

【0071】また本実施形態では、 $n$ ラインの書き込み期間を従来の液晶表示装置と同じく1水平期間に相当する時間Tのままとし、これに合わせて $n+1$ ライン以降の書き込み期間を変更するようにしている。つまり、横筋の発生しない範囲内で書き込み期間を最大にしているため、書き込み期間を縮めたことによる輝度の低下を最小限に抑えることができる。さらに本実施形態では、第1実施形態と同じく、これまでの液晶表示装置(図9を参照)の構成に対して若干の追加・変更を行うことで実現できるという利点がある。

【0072】〔第3実施形態〕本実施形態による液晶表示装置の基本的な構成も第1実施形態(図1を参照)と同じであって、第2実施形態と同じくタイミングコントローラ8における信号のタイミング制御が第1実施形態と異なっている。そこで以下、本実施形態による液晶表示装置の具体的な動作を説明するが、本実施形態でも2ラインドット反転駆動の場合と3ライン以上のラインドット反転駆動とでは動作が若干異なっている。

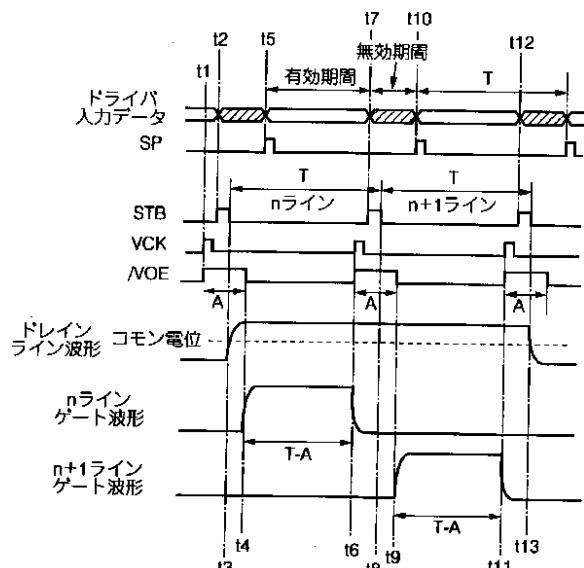

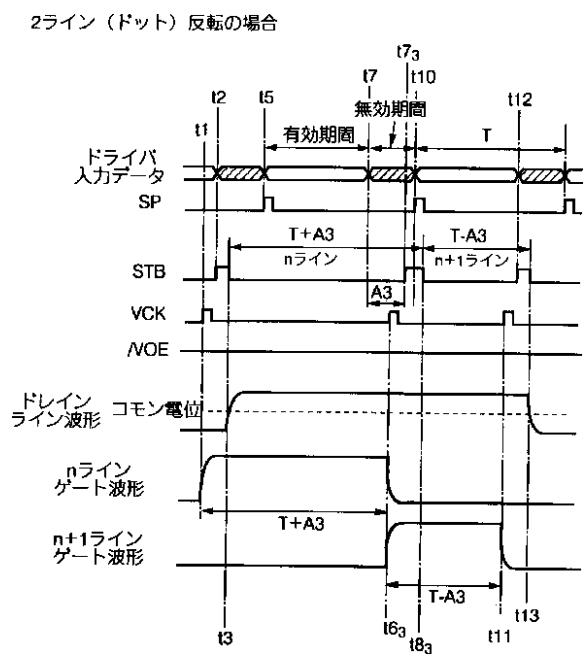

#### 【0073】(1) 2ラインドット反転駆動

まず図7のタイミングチャートを参照して2ラインドット反転駆動の場合について具体的動作を説明する。なお、図7において図3(第1実施形態)又は図5(第2実施形態)に示した時刻に対応するものについては同一の時刻を付けている。また本実施形態でも、図7に示したタイミングの直前のフレームにおいて、nライン及びn+1ラインが何れも負極性の書き込み電圧で駆動されていたものとする。さらに、2ラインドット反転駆動では出力イネーブル信号/V<sub>O E</sub>を使用しないことから、タイミングコントローラ8は出力イネーブル信号/V<sub>O E</sub>を常時“L”に維持している。

【0074】まず、時刻t<sub>1</sub>～t<sub>5</sub>における動作は第2実施形態における同期間内の動作と同じであって、この時刻t<sub>5</sub>よりも後の動作が第2実施形態と異なっている。すなわち、タイミングコントローラ8は時刻t<sub>1</sub>から時間Tが経過してもクロック信号V<sub>C K</sub>にパルスを発生させない。同様に、タイミングコントローラ8は時刻t<sub>2</sub>から時間Tが経過して時刻t<sub>7</sub>になっても、ラッチパルス信号S<sub>T B</sub>にパルスを発生させない。このため時刻t<sub>7</sub>では、ソースドライバ9に入力されるデータが無効期間に切り替わってn+1ラインの映像データの取り込みが停止する動作のみが行われる。

【0075】次に、時刻t<sub>1</sub>から時間(T+A<sub>3</sub>)が経過して時刻t<sub>6</sub><sub>3</sub>になると、タイミングコントローラ8は第1実施形態や第2実施形態のときよりも時間A<sub>3</sub>だけ遅れてクロック信号V<sub>C K</sub>にパルスを発生させる。ここで、時間A<sub>3</sub>の値は0～A<sub>3</sub>(無効期間の時間幅)の範囲内で可変となっている。また、時間A<sub>3</sub>の値は上述した各実施形態における時間A<sub>1</sub>や時間A<sub>2</sub>と同じく、横縞のない画面となるように目視で確認しながらその最小値を上記範囲内で決定すれば良い。

【0076】そして時刻t<sub>6</sub><sub>3</sub>でクロック信号V<sub>C K</sub>が立ち上ると、ゲートドライバ7はゲートパルス信号をシフトさせてゲートライン2nに対するゲートパルス信号の供給を停止させる。こうして本実施形態ではnラインの書き込み時間が時間(T+A<sub>3</sub>)となる。そして、上述のように出力イネーブル信号/V<sub>O E</sub>は常時“L”であることから、ゲートドライバ7は時刻t<sub>6</sub><sub>3</sub>でゲートライン2n+1へのゲートパルス信号の供給を開始させる。次に、時刻t<sub>7</sub>から時間A<sub>3</sub>が経過して時刻t<sub>7</sub><sub>3</sub>になった時点でタイミングコントローラ8は

50 ラッチパルス信号S<sub>T B</sub>を発生させる。

【0077】これによって、ソースドライバ9はラッチパルス信号S<sub>T B</sub>の立ち上がりに同期して、時刻t<sub>7</sub>までにシフトレジスタへ取り込んでおいたn+1ラインの映像データをラッチに転送する。次に、時刻t<sub>10</sub>でタイミングコントローラ8がスタートパルス信号S<sub>P</sub>を発生させることによって、ソースドライバ9はn+2ラインの映像データの取り込みを開始させる。なお、時間A<sub>3</sub>を無効期間の範囲内に制限しているため、ラッチパルス信号S<sub>T B</sub>の立ち上がりがスタートパルス信号S<sub>P</sub>の立ち上がりよりも後になることはない。したがって、ソースドライバ9内では、シフトレジスタの内容をラッチに転送してから、新たな映像データをシフトレジスタに取り込むことができる。

【0078】次に、時刻t<sub>3</sub>から時間(T+A<sub>3</sub>)が経過して時刻t<sub>8</sub><sub>3</sub>になると、タイミングコントローラ8は第1実施形態や第2実施形態のときよりも時間A<sub>3</sub>だけ遅れてラッチパルス信号S<sub>T B</sub>を立ち下げる。これにより、ソースドライバ9はn+1ラインの映像データに20 対応した書き込み電圧をドレインライン3に供給するようになる。このとき、ゲートライン2n+1には既に時刻t<sub>6</sub><sub>3</sub>からゲートパルス信号が印加されているため、同時刻t<sub>8</sub><sub>3</sub>からゲートライン2n+1に対応する液晶セル5への書き込みが開始される。

【0079】そして、これ以後の動作は第1実施形態や第2実施形態と同様である。すなわち、時刻t<sub>11</sub>でクロック信号V<sub>C K</sub>が立ち上るとゲートライン2n+1に対するゲートパルス信号の供給が停止して、当該ゲートラインに対する書き込みが終了する。こうして本実施形態ではn+1ラインの書き込み時間が時間(T-A<sub>3</sub>)となる。この後、時刻t<sub>12</sub>でラッチパルス信号S<sub>T B</sub>が立ち上ると、n+2ラインの映像データの取り込みが停止し、時刻t<sub>13</sub>でラッチパルス信号S<sub>T B</sub>が立ち下ると、n+2ラインの映像データに対応した負極性の書き込み電圧がドレインライン3に供給される。

#### 【0080】(2) 3ラインドット反転駆動

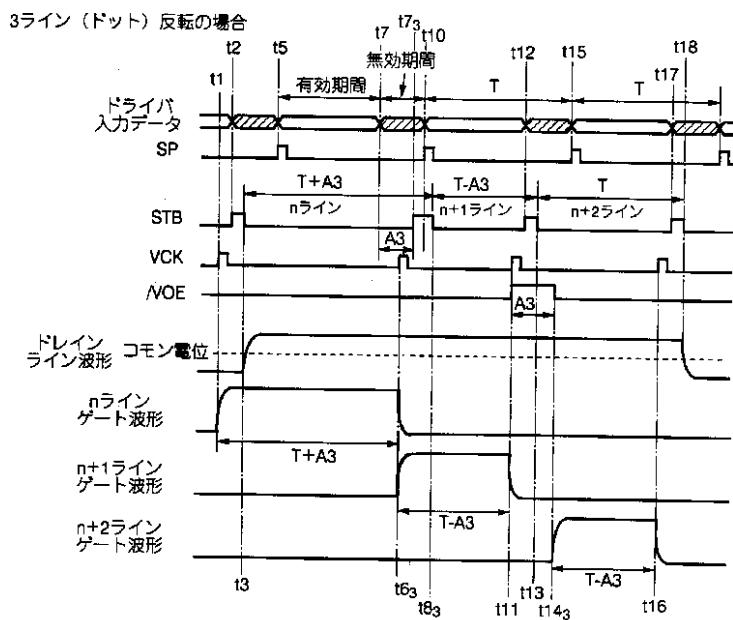

次に、図8のタイミングチャートを参照して3ラインドット反転駆動について具体的動作を説明する。なお、図8では図6(第2実施形態)又は図7に示した時刻に対応するものについては同一の時刻を付けている。この場合も、時刻t<sub>1</sub>～t<sub>13</sub>における動作は、以下に述べる点を除いて図7に示した同期間内の動作と同じである。

【0081】すなわち、この場合には時刻t<sub>11</sub>でクロック信号V<sub>C K</sub>が立ち上ると同時に、タイミングコントローラ8は出力イネーブル信号/V<sub>O E</sub>を“H”にする。このようにするのは、n+2ラインの書き込み時間をn+1ラインと同じ時間(T-A<sub>3</sub>)にするためである。これによって、ゲートドライバ7はゲートライン2n+1へのゲートパルス信号の供給を停止させてn+1ラインに対する書き込みを終了させるほか、ゲート

イン $2n+2$ （図示省略）に対してもゲートパルス信号を供給しないようにする。

【0082】そして、時刻 $t_{11}$ から時間A3が経過して時刻 $t_{14}$ になった時点では、タイミングコントローラ8は出力イネーブル信号/VOEを立ち下げる。これによって、ゲートドライバ7はゲートライン $2n+2$ に対してゲートパルス信号を供給するようになる。このときには、既に時刻 $t_{13}$ で $n+2$ ラインの映像データに対応した正極性の書き込み電圧がドレインライン3に印加されているため、同時に $t_{14}$ でゲートライン $2n+2$ に対応した液晶セル5への書き込みが始まる。次に、時刻 $t_{15}$ でスタートパルス信号STPが立ち上がりと $n+3$ ラインの映像データの取り込みが始まる。

【0083】そして、これ以後の動作は $n+1$ ラインとほぼ同様である。すなわち、時刻 $t_{16}$ でクロック信号VCKが立ち上がりことでゲートライン $2n+2$ に対するゲートパルス信号の供給が停止し、ゲートライン $2n+3$ （図示省略）に対してゲートパルス信号が供給されるようになる。この後、時刻 $t_{17}$ においてラッチパルス信号STBが立ち上がりことで $n+3$ ラインの映像データの取り込みが停止し、時刻 $t_{18}$ においてラッチパルス信号STBが立ち下がることで $n+3$ ラインの映像データに対応した負極性の書き込み電圧がドレインライン3に供給される。このように、3ライン以上のラインドット反転駆動の場合、 $n+2$ ライン以降のラインでは、 $n+1$ ラインと書き込み状態を同一にするためにゲートラインに供給されるゲートパルス信号の立ち上がりを時間A3だけ遅延させている。

【0084】以上の通りであって、第1実施形態や第2実施形態ではクロック信号VCKおよびラッチパルス信号STBの周期が一定時間Tであった。これに対し、本実施形態では $n$ ラインと $n+1$ ライン以降のラインとの間では、クロック信号VCK及びラッチパルス信号STBの周期を連動して変えるようにしている。すなわち、ドレインライン波形の立ち上がり期間が含まれる $n$ ラインでは書き込み期間を長くとり、ドレインライン波形がフラットな $n+1$ ライン以降のラインでは書き込み期間を短くしている。こうすることで、書き込み電圧の極性が反転する走査線とそれ以降の走査線とで書き込み状態を同一にすることができる。このため、走査線間で輝度差がなくなって横筋の発生を防止することができる。

【0085】また、本実施形態では、クロック信号VCK及びラッチパルス信号STBの周期を伸縮するときの可変範囲をドライバ入力データの無効期間内に收めるような制限を課している。ここで、もし仮に何らの制約も付けずにこれら信号の周期を可変できるようにすると、無効期間の範囲外となった期間だけ有効期間が短くなってしまう。このため、本来の有効期間（11.9μs）よりも短時間（例えば10μs）で1水平期間分の映像データを取り込まねばならなくなる。それには、ドット

10 10 20 30

クロック信号の周波数を高めねばならないため、〔発明が解決しようとする課題〕で述べたような問題が生じてしまう。これに対し、本実施形態では、第1実施形態や第2実施形態と同じ有効期間内に全ての映像データを取り込むことができ、ドットクロック信号DCKの周波数をいっさい変更する必要がない。

【0086】さらに本実施形態によると、2ラインドット反転駆動を行うのであれば、ラッチパルス信号STB及びクロック信号VCKのタイミングを調整するだけ良い。このため、タイミングコントローラの構成を若干変更することで実現可能となる。また、この場合には出力イネーブル信号/VOEのタイミングを制御する必要がないため、タイミングコントローラ8の制御が簡単になるという利点もある。一方、3ライン以上のラインドット反転駆動を行う場合にも、出力イネーブル信号/VOEの生成論理をタイミングコントローラ8に設けるとともに、出力イネーブル信号/VOEに従って駆動電圧を各ゲートラインへ供給するかどうかを制御する論理をゲートドライバ7に設けるだけで良い。

【0087】〔変形例〕

(1) 上述した各実施形態では、複数ラインドット反転駆動を前提にして説明したが、単なる複数ライン反転駆動であっても本発明を全く同様に適用することができる。

(2) また、上述した説明ではTFTを用いた構成を前提として説明を行っていたが、TFTの代わりにMIM（Metal Insulator Metal）ダイオードを用いた構成を採用しても良い。このほか、個々の液晶セルに対して外部に保持容量を並列的に設けた構成などにも本発明を同様に適用することができる。

(3) さらに、上述した各実施形態では、ゲートラインおよびドレインラインにそれぞれ駆動信号および書き込み電圧を時間Tだけ供給する従来構成（図10を参照）を前提として、この従来構成に対して本発明を適用する場合を説明した。しかし、駆動信号および書き込み電圧を供給する時間は必ずしも時間Tでなくとも良く、例えば時間Tよりも所定時間だけ短い時間（T-）の間だけ駆動信号および書き込み電圧を供給する構成を前提として、本発明を適用するようにしても良い。

【0088】

【発明の効果】以上説明したように、請求項1記載の発明によれば、書き込み信号の極性が反転する走査線では、データ線の電圧の極性とは逆極性の書き込み信号の供給が開始されてから所定時間後より該データ線へ駆動信号を供給し、これ以外の後続の走査線でも、書き込み信号の極性が反転する走査線について駆動信号が供給される時間と同じ時間だけ駆動信号を供給している。これにより、データ線の電圧波形における鈍り部分をマスクできるため、液晶セルに対する書き込み状態を全ての走査線で同一にすることができる。したがって、走査線間

50

の輝度差による横縞が発生することが無くなつて表示品位が向上する。

【0089】また、請求項2記載の発明によれば、書き込み信号の極性が反転する走査線以外の後続の走査線において、書き込み信号の極性が反転する走査線について駆動信号が供給される時間よりも所定時間短かい時間だけ駆動信号を供給している。これにより、液晶セルに対する書き込み状態を全ての走査線で同一にすることができるため、走査線間の輝度差による横縞が発生することが無くなつて表示品位が向上する。また、書き込み信号の極性が反転する走査線については駆動信号を供給する時間を短かくしていないため、それだけ輝度を低下させずに済むことになる。また、請求項3記載の発明によれば、書き込み信号の極性が反転する走査線では、無効期間の範囲内にある一定時間だけ1水平期間よりも長い期間内で駆動信号及び書き込み信号を供給し、これ以外の後続の走査線では上記一定時間だけ1水平期間よりも短かい期間内で駆動信号及び書き込み信号を供給するようにしている。これにより、液晶セルに対する書き込み状態を全ての走査線で同一にすることができるため、走査線間の輝度差による横縞が発生することが無くなつて表示品位が向上する。また、駆動信号及び書き込み信号を供給する期間を無効期間の範囲内で伸縮させているため、データ線駆動手段が映像データを取り込むためのドットクロック信号の周波数を変更するなどの必要が全くない。

【0090】なお、請求項1乃至4記載の発明において、目視による評価で画面に横縞が認められなくなるように、駆動信号又は書き込み信号が供給される期間を調整することで、液晶表示装置内の各部の特性にバラツキがあつても柔軟な調整が可能となるため、目視で横縞が認識できない範囲で可能な限り輝度を上げることが可能となる。

#### 【図面の簡単な説明】

【図1】 本発明の各実施形態による液晶表示装置の

要部の構成を示したブロック図である。

【図2】 2ラインドット反転駆動を行つた場合に、或る1フレーム内で各画素に書き込まれた映像データの電圧の極性を示した説明図である。

【図3】 本発明の第1実施形態による液晶表示装置の動作を2ラインドット反転駆動の場合について示したタイミングチャートである。

【図4】 SXGA規格、フレーム周波数60MHzで2ラインドット反転駆動を実施した場合について横筋の程度の確認結果を示した図表である。

【図5】 本発明の第2実施形態による液晶表示装置の動作を2ラインドット反転駆動の場合について示したタイミングチャートである。

【図6】 同実施形態による液晶表示装置の動作を3ラインドット反転駆動の場合について示したタイミングチャートである。

【図7】 本発明の第3実施形態による液晶表示装置の動作を2ラインドット反転駆動の場合について示したタイミングチャートである。

【図8】 同実施形態による液晶表示装置の動作を3ラインドット反転駆動の場合について示したタイミングチャートである。

【図9】 従来の技術による液晶表示装置の要部の構成を示したブロック図である。

【図10】 従来の技術による液晶表示装置の動作を2ラインドット反転駆動の場合について示したタイミングチャートである。

#### 【符号の説明】

1...液晶パネル、2...n, 2n+1...ゲートライン、3...ドレインライン、4...TFT、5...液晶セル、6...コモン電極、7...ゲートドライバ、8...タイミングコントローラ、9...ソースドライバ、DCK...ドットクロック信号、SP...スタートパルス信号、STB...ラッチパルス信号、VCK...クロック信号、VOE...出力イネーブル信号

【図2】

|     |   |   |   |   |   |   |  |

|-----|---|---|---|---|---|---|--|

| n   | 正 | 負 | 正 | 負 | 正 | 負 |  |

| n+1 | 正 | 負 | 正 | 負 | 正 | 負 |  |

| n+2 | 負 | 正 | 負 | 正 | 負 | 正 |  |

| n+3 | 負 | 正 | 負 | 正 | 負 | 正 |  |

| n+4 | 正 | 負 | 正 | 負 | 正 | 負 |  |

| n+5 | 正 | 負 | 正 | 負 | 正 | 負 |  |

【図4】

| VOEマスク時間A [μs] | 127階調 | 63階調 |

|----------------|-------|------|

| 0              | △     | △    |

| 1.26           | ○     | △    |

| 2.5            | ○     | ○    |

| 5.0            | ○     | ○    |

○:横筋なし △:横筋あるが薄い ×:横筋あり

【図1】

【図3】

【図5】

【図6】

【図7】

【図10】

【図8】

【図9】

フロントページの続き

Fターム(参考) 2H093 NA32 NA36 NA45 NB16 NC16

ND09 ND39

5C006 AC22 AC27 AF42 AF71 BB16

BC03 FA22 FA41 FA47 FA48

5C080 AA10 BB05 DD05 DD22 DD26

EE29 FF11 JJ02 JJ04 JJ05

|             |                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)     | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 公开(公告)号     | <a href="#">JP2001215469A</a>                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2001-08-10 |

| 申请号         | JP2000028079                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2000-02-04 |

| 申请(专利权)人(译) | NEC公司                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人      | 奥苑登<br>古賀弘一                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人         | 奥苑 登<br>古賀 弘一                                                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号      | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                       |         |            |

| CPC分类号      | G09G3/3614 G09G3/3648 G09G2320/0204 G09G2320/0223                                                                                                                                                                                                                                                                                                                 |         |            |

| FI分类号       | G02F1/133.550 G09G3/20.611.A G09G3/20.622.D G09G3/36                                                                                                                                                                                                                                                                                                              |         |            |

| F-TERM分类号   | 2H093/NA32 2H093/NA36 2H093/NA45 2H093/NB16 2H093/NC16 2H093/ND09 2H093/ND39 5C006 /AC22 5C006/AC27 5C006/AF42 5C006/AF71 5C006/BB16 5C006/BC03 5C006/FA22 5C006/FA41 5C006/FA47 5C006/FA48 5C080/AA10 5C080/BB05 5C080/DD05 5C080/DD22 5C080/DD26 5C080 /EE29 5C080/FF11 5C080/JJ02 5C080/JJ04 5C080/JJ05 2H093/NA16 2H193/ZC02 2H193/ZC20 2H193/ZC26 2H193/ZD32 |         |            |

| 其他公开文献      | <a href="#">JP3428550B2</a>                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接        | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                         |         |            |

### 摘要(译)

解决的问题：提供一种液晶显示装置，该液晶显示装置通过多线反转驱动而具有低功耗，并且能够在不使电路结构复杂的情况下防止水平条纹。当液晶单元的写入电压的极性每多条线反转时，漏极线需要在极性反转的n条线中充电，并且漏极线波形的上升变钝（t3至t4）。另一方面，在n+1行中，由于漏极线通过写入n线而被充电（t8至t9），因此波形不会钝化。因此，在两条线之间液晶单元的写入状态不同，导致水平条纹。因此，输出使能信号/VOE在时钟信号VCK的上升沿（t1）处被设置为“H”，并且在经过预定时间A之后将应为“H”的栅极线设置为“L”时将“H”设置为“H”。（T4）开始液晶单元的写入。通过这样做，在波形钝化时段期间不执行写入，所有行的写入状态相同，并且不会出现水平条纹。