(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4609970号

(P4609970)

(45) 発行日 平成23年1月12日(2011.1.12)

(24) 登録日 平成22年10月22日(2010.10.22)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

G02F 1/1368

G02F 1/133 (2006.01)

G02F 1/133 550

G09F 9/30 (2006.01)

G09F 9/30 338

請求項の数 4 (全 16 頁)

(21) 出願番号 特願2001-9325 (P2001-9325)

(22) 出願日 平成13年1月17日 (2001.1.17)

(65) 公開番号 特開2002-214643 (P2002-214643A)

(43) 公開日 平成14年7月31日 (2002.7.31)

審査請求日 平成18年1月5日 (2006.1.5)

審判番号 不服2009-12759 (P2009-12759/J1)

審判請求日 平成21年7月14日 (2009.7.14)

(73) 特許権者 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(72) 発明者 豊島 剛

東京都八王子市石川町2951番地の5

カシオ計算機株式会社 八王子研究所内

(72) 発明者 佐々木 和広

東京都八王子市石川町2951番地の5

カシオ計算機株式会社 八王子研究所内

(72) 発明者 両澤 克彦

東京都八王子市石川町2951番地の5

カシオ計算機株式会社 八王子研究所内

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素がマトリクス状に配置された表示領域を有するアクティブマトリクス型の液晶表示装置であって、

互いに平行となるように前記表示領域に延伸配置された複数の走査ラインと、

前記各走査ラインと交差するように延伸配置された複数のデータラインと、

前記各走査ラインと平行となるように且つ前記各データラインと交差するように、前記表示領域とは異なる領域に延伸配置された複数のダミーラインと、

前記画素毎に形成され、ゲート電極が前記走査ラインの何れかに接続された複数の画素トランジスタと、

少なくとも一つの薄膜トランジスタにおける半導体層が前記各画素トランジスタの半導体層と同層に形成され、前記複数の走査ラインの数と前記複数のダミーラインの数との合計に等しい出力段数を有し、前記各出力段に前記各走査ライン及び前記各ダミーラインの何れか一つが接続され、前記各走査ライン及び前記各ダミーラインに選択信号を出力するシフトレジスタと、を備え、

前記各ダミーラインは、前記シフトレジスタから該ダミーラインに選択信号を出力する際の負荷が前記シフトレジスタから前記走査ラインに選択信号を出力する際の負荷と等しくなるように負荷容量または負荷抵抗が形成されているとともに、隣接するダミーラインとの配線間隔が前記走査ラインの配線間隔よりも短く配置されていることを特徴とする液晶表示装置。

**【請求項 2】**

前記各ダミーラインは、前記各走査ラインに供給される選択信号よりも後に選択信号が供給されるように前記シフトレジスタに接続されていることを特徴とする請求項 1 に記載の液晶表示装置。

**【請求項 3】**

前記半導体層がアモルファスシリコン層であることを特徴とする請求項 1 または 2 に記載の液晶表示装置。

**【請求項 4】**

前記各ダミーラインはライン幅が前記各走査ラインのライン幅と異なるように形成されていることを特徴とする請求項 1 から 3 の何れかに記載の液晶表示装置。 10

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、アクティブマトリクス型の液晶表示装置に関する。

**【0002】****【従来の技術】**

TFT 液晶表示装置は、アクティブ素子としての TFT (Thin Film Transistor) を画素毎に設け、この TFT のオン / オフによって画素容量へデータを書き込むことによって、所望の画像を表示するものである。このように所望の画像を表示させるために、通常、TFT 液晶表示素子は、ゲートドライバとドレインドライバからなる駆動回路によって構成される。 20

**【0003】**

ゲートドライバは、TFT 液晶表示素子のゲートラインを 1 ラインずつ順次選択していくものであり、シフトレジスタが広く用いられている。ゲートドライバを構成するシフトレジスタとして、例えば、特開 2000-35772 号公報に記載されているように、TFT から各段が構成されたものが知られている。このシフトレジスタでは、各段の動作は、その前後の段における回路動作の影響を受ける。

**【0004】**

シフトレジスタの各段から液晶表示素子のゲートラインに出力された出力信号は、このゲートライン及びこれに接続された TFT、画素容量、補償容量が形成する、分布定数的な特定を有する回路によって減衰されることとなる。従って、各ゲートライン及びそこに接続された素子による分布定数的な特性を有する回路が、シフトレジスタの回路動作にも影響を及ぼすこととなる。 30

**【0005】**

ところが、上記公報において、シフトレジスタの段数は、TFT 液晶表示素子の表示画素のライン数と同じだけ設けられるものとなっていたため、最後の段の回路動作は、他の段とは異なり、後ろの段の回路動作による影響を受けない。従って、最後の段の回路動作は、それ以前の段の回路動作に対して微妙な差異が生じてしまう。さらに、長期間の駆動を行っていると、その微妙な差異が徐々に前の段にも波及していくことも考えられ、ゲートドライバを構成するシフトレジスタの動作が不安定になってしまうという問題があった。 40

**【0006】****【発明が解決しようとする課題】**

本発明は、上記従来技術の問題点を解消するためになされたものであり、ドライバとして適用されるシフトレジスタを安定動作させることを可能とした液晶表示装置を提供することを目的とする。

**【0008】****【課題を解決するための手段】**

上記目的を達成するため、本発明の液晶表示装置は、

複数の画素がマトリクス状に配置された表示領域を有するアクティブマトリクス型の液晶表示装置であって、 50

互いに平行となるように前記表示領域に延伸配置された複数の走査ラインと、前記各走査ラインと交差するように延伸配置された複数のデータラインと、前記各走査ラインと平行となるように且つ前記各データラインと交差するように、前記表示領域とは異なる領域に延伸配置された複数のダミーラインと、

前記画素毎に形成され、ゲート電極が前記走査ラインの何れかに接続された複数の画素トランジスタと、

少なくとも一つの薄膜トランジスタにおける半導体層が前記各画素トランジスタの半導体層と同層に形成され、前記複数の走査ラインの数と前記複数のダミーラインの数との合計に等しい出力段数を有し、前記各出力段に前記各走査ライン及び前記各ダミーラインの何れか一つが接続され、前記各走査ライン及び前記各ダミーラインに選択信号を出力するシフトレジスタと、を備え。10

前記各ダミーラインは、前記シフトレジスタから該ダミーラインに選択信号を出力する際の負荷が前記シフトレジスタから前記走査ラインに選択信号を出力する際の負荷と等しくなるように負荷容量または負荷抵抗が形成されているとともに、隣接するダミーラインとの配線間隔が前記走査ラインの配線間隔よりも短く配置されていることを特徴とする。

#### 【0009】

上記液晶表示装置では、ゲートドライバを安定して動作させることが可能となる。

#### 【0010】

前記各ダミーラインは、前記各走査ラインに供給される選択信号よりも後に選択信号が供給されるように前記シフトレジスタに接続されていてもよい。20

#### 【0011】

前記半導体層はアモルファスシリコン層とすることができます。

#### 【0012】

前記各ダミーラインは、隣接するダミーラインとの配線間隔が前記走査ラインの配線間隔よりも短く配置されていてもよい。

#### 【0013】

前記各ダミーラインはライン幅が前記各走査ラインのライン幅と異なるように形成され

ていてもよい。

#### 【0022】

#### 【発明の実施の形態】

以下、添付図面を参照して、本発明の実施の形態について説明する。

#### 【0023】

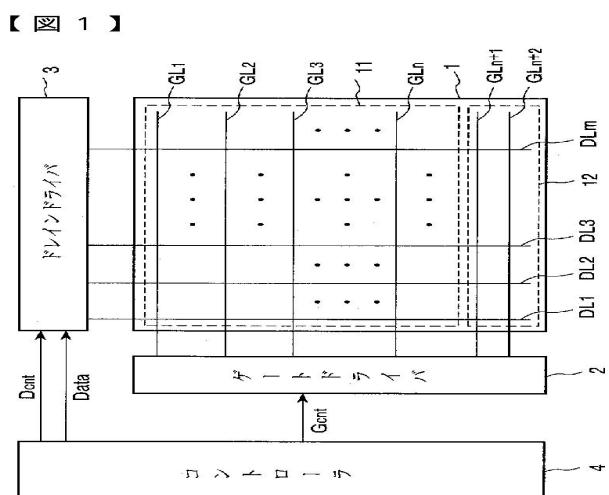

図1は、この実施の形態にかかる液晶表示装置の構成を、等価回路図を以て示す図である。図示するように、この液晶表示装置は、液晶表示素子1と、ゲートドライバ2と、ドレインドライバ3と、コントローラ4とから構成されている。

#### 【0024】

液晶表示素子1は、画素基板とコモン基板との間に液晶を封入して構成されるものであり、表示領域11と、ダミー素子領域12とを備えている。画素基板上には、表示領域11に配されたn本のゲートラインGL1～GLnと、ダミー素子領域12に配され、ゲートラインGL1～GLnと同一材料からなり、ゲートラインGL1～GLnと一括してパターニング形成された2本のダミーゲートライン（ダミー走査ライン）GLn+1、GLn+2とが、主走査方向（図では、横方向）に伸延して互いに平行に形成されている。また、m本のドレインラインDL1～DLmが、表示領域11及びダミー素子領域12をまたがって副走査方向（図では、縦方向）に伸延して互いに平行に形成されている。40

#### 【0025】

画素基板には、表示領域11においてゲートラインGL1～GLnとドレインラインDL1～DLmの交差位置に対応して形成されたマトリクス状の画素をそれぞれ構成するTFT、画素電極等が設けられている（詳細は後述）。また、ダミー素子領域12において、ダミー素子が設けられている（詳細は後述）。画素基板では、これらTFT、画素電極、ダミー素子の上に配向膜が形成されている。一方、コモン基板上には、コモン電極と配向

50

20

30

40

50

膜とが形成されているが、コモン電極は、表示領域 11 の範囲にのみ形成されている。

#### 【0026】

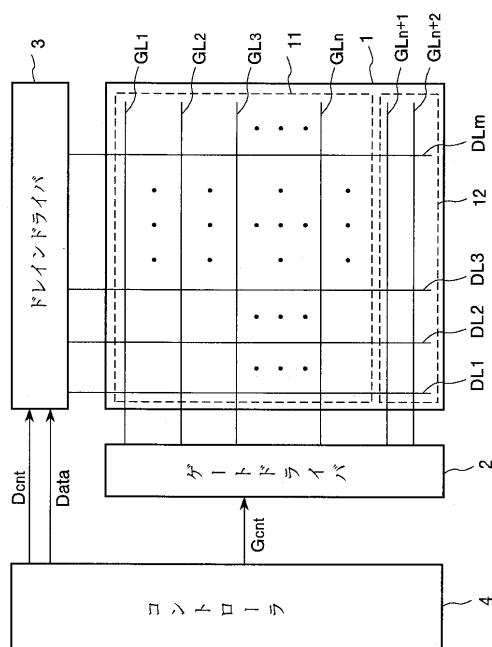

図 2 (a) は、表示領域 11 に形成された各画素の構造を示す図である。図では、画素基板上に形成されたもののみを示しているが、実際にはこれにコモン基板のコモン電極が対向している。また、電極や配線を構成する金属層の間には絶縁層が形成されているが、図では省略している。図 2 (b) は、各画素の等価回路（横方向に隣接する 2 画素分）を示す図である。

#### 【0027】

表示領域 11において画素基板上の 1 番下の層には、金属材料からなるゲートライン GL (GL1 ~ GLn) と、ゲートライン GL と一緒に形成された TFT111 のゲート電極 G が形成されている。また、補償容量 113 を形成するための補償電極 CE と、補償電極 CE に定電圧を供給する補償電極 CL と一緒に形成される。ゲート電極 G の上には、SiN からなるゲート絶縁膜を介して、アモルファスシリコンによって構成され、TFT111 の半導体層を形成するアモルファスシリコン半導体層 a - Si が形成されている。半導体層の両側には、不純物層を介してソース電極 S 及びドレイン電極 D が設けられ、ソース電極 S は、透明の ITO (Indium Tin Oxide) からなり、画素容量 112 を形成するための透明電極 TE と接続されている。

10

#### 【0028】

ドレイン電極 D は、ゲートライン GL の延在方向と直交する方向に延在するデータライン DL (DL1 ~ DLm) と一緒に形成されている。そして、これら TFT111 上に再び SiN からなる絶縁保護膜が形成され、そしてその上に配向膜が設けられることとなる。透明電極 TE は、少なくとも部分的に重なり合うように対向する位置にある補償電極 CE と、この補償電極 CE との間のゲート絶縁膜と同じ膜とでコンデンサを構成すると共に補償容量 113 を形成し、対向する位置にあるコモン基板側のコモン電極の間の液晶をコンデンサとしたと共に画素容量 112 を形成する。

20

#### 【0029】

このようにして形成される構造により、各画素においては、ゲートライン GL による配線抵抗 114 と、配線抵抗 114 にゲートが接続されたアクティブ素子としての TFT111 と、TFT111 のドレインに並列に接続された画素容量 112 と補償容量 113 とから回路が構成されることとなる。そして、ゲートライン GL1 ~ GLn のそれについて、このような各画素の回路が主走査方向の画素数分だけ接続された分布定数的な特性を有する電気回路が負荷として構成されることとなる。

30

#### 【0030】

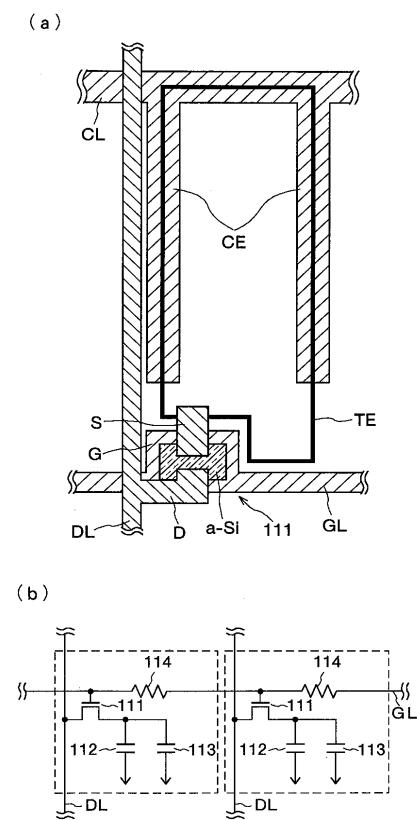

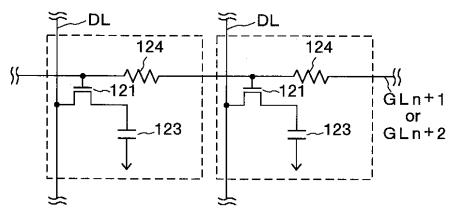

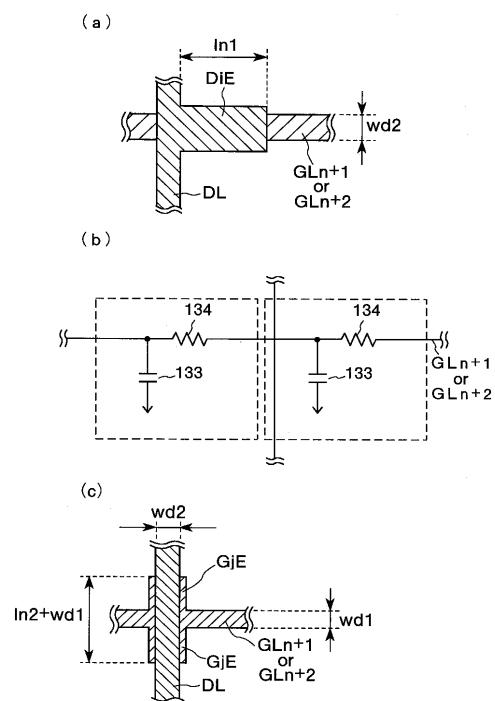

図 3 (a) は、ダミー素子領域 12 に形成された各ダミー素子の構造を示す図である。このダミー素子には、表示領域 11 の画素と異なり、コモン電極は対向していない。もっとも、この図においても、電極や配線を構成する金属層の間に形成されている絶縁層は省略している。図 3 (b) は、各ダミー素子の等価回路（横方向に隣接する 2 つ分）を示す図である。

#### 【0031】

ダミー素子領域 12 において画素基板上の 1 番下の層には、ゲートライン (GLn+1, GLn+2) と、ゲートライン GL と一緒に形成された TFT121 のゲート電極 G とが形成されている。また、ダミー容量 123 を形成するためのダミー容量電極 DiE (i は 1 ~ m のいずれか) と、ダミー容量電極 DiE に定電圧を供給するダミー容量電極ライン Dil と一緒に形成される。これらは、表示領域 11 のゲートライン GL 等と同じ金属材料で、同一プロセスにおいて形成されている。

40

#### 【0032】

ゲート電極 G の上には、アモルファスシリコンによって構成され、TFT121 の半導体層を形成するアモルファスシリコン半導体層 a - Si が形成されている。これらの上に、透明の SiN からなる絶縁層が形成され、さらにその上に、ITO からなり、ダミー容量電極 DiE と共にダミー容量 123 を形成する透明電極 TE が形成されている。これらも

50

、表示領域11における対応するものと、同一の材料で同一プロセスにおいて形成されている。

#### 【0033】

その上に、再びSiNからなるゲート絶縁層が形成され、さらにその上に、金属材料からなるデータラインDL(DL1～DLm:表示領域11のものと同一)と、データラインDLと一体に形成されたTFT121のドレイン電極Dと、TFT121のソース電極Sとが形成されている。ソース電極Sと透明電極TEとは、コンタクトホールを介して接続されている。そして、この上に再びSiNからなる絶縁保護膜が形成される。

#### 【0034】

ダミー容量123は、ダミー容量電極DiEと、透明電極TEと、ダミー容量電極DiEと透明電極TEとの間のゲート絶縁膜と同一の膜と、から構成され、このようにして形成される構造により、ダミーゲートラインGLによる配線抵抗124と、配線抵抗124にゲートが接続されたアクティブ素子としてのTFT121と、TFT121のドレインに接続されたダミー容量123からなるダミー素子が構成されることとなる。

10

#### 【0035】

TFT121は、形状、寸法、及びデータラインDLやゲートラインGLとの相対的位置がTFT111と全く同じため、TFT121における、接続されたデータラインDLとの間に生じる寄生容量やゲート-ドレイン間の寄生容量は、TFT111における、接続されたデータラインDLとの間に生じる寄生容量やゲート-ドレイン間の寄生容量に等しい。ダミー容量123は、表示領域11における画素容量112と補償容量113との合成容量に等しくなるように形成されている。そして、ゲートラインGLn+1、GLn+2のそれぞれについて、このようなダミー素子が主走査方向の画素数分だけ接続された分布定数的な特性を有する電気回路が負荷として構成されるが、これらはGL1～GLnのそれぞれの負荷と同じ特性を有するものとなる。

20

#### 【0036】

ゲートドライバ2は、詳細を後述するシフトレジスタによって構成され、コントローラ4からの制御信号群Gcntに従って、ゲートラインGL1～GLn+1に順次ハイレベルの選択信号を出力する。ドレインドライバ3は、コントローラ4からの制御信号群Dcntに従って、同じくコントローラ4から供給される画像データ信号Dataを1ライン分蓄積し、所定のタイミングでドレインラインDL1～DLmに出力する。なお、ゲートドライバ2のa-Si又はp-Siからなる半導体層を有するTFT201～206は、画素基板上に、液晶表示素子1の表示領域11のTFT111及びダミー素子領域12のTFT121と同一プロセスで形成される。コントローラ4は、ゲートドライバ2に制御信号群Gcntを供給すると共に、ドレインドライバ3に制御信号群Dcntと画像データ信号Dataとを供給する。

30

#### 【0037】

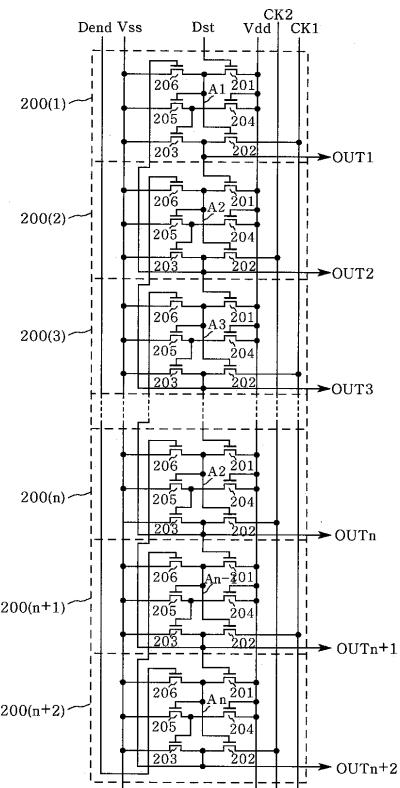

図4は、ゲートドライバ2を構成するシフトレジスタの回路構成を示す図である。図示するように、このシフトレジスタは、表示領域11に配されたn本のゲートラインGL1～GLnと、ダミー素子領域12に配された2本のゲートラインGLn+1、GLn+2とにそれぞれ対応するn+2個の段200(1)～200(n+2)から構成されている。

40

#### 【0038】

制御信号群Gcntに含まれる信号として、コントローラ4からクロック信号CK1、CK2、スタート信号Dst、終了信号Den、正の電圧レベルを有する電源電圧Vdd、及び負の電圧レベルを有する基準電圧Vssが供給されている。各段200(1)～200(n+2)の構成はほぼ同じであるため、1番目の段200(1)を例に採って説明すると、当該段内には、6個のnチャネル型の電界効果トランジスタであるTFT201～206が形成されている。

#### 【0039】

TFT201のゲートには、スタート信号Dstが供給され、ドレインには、電源電圧Vddが常時供給されている。TFT201のソースは、TFT202のゲートと、TFT

50

205のゲートとに接続されている。このTFT201のソース、TFT202のゲート及びTFT205のゲートで囲まれた配線を、ノードA1と呼ぶ（なお、2段目以降は、それぞれA2～An+2とする）。ハイレベルのスタート信号Dstが供給されてTFT201がオンすると、ノードA1に電荷が蓄積される。

#### 【0040】

TFT202のドレインには、クロック信号CK1が供給され、TFT202がオンしている際に、クロック信号CK1のレベルがほぼそのまま出力信号OUTとして、そのソースから1番目のゲートラインGL1に出力される。また、TFT202のソースは、TFT203のドレインに接続されている。

#### 【0041】

TFT204のゲートとドレインとには、電源電圧Vddが供給され、常にオン状態となっている。TFT204は、電源電圧Vddを供給する際の負荷として機能し、そのソースから電源電圧VddをほぼそのままTFT205のドレインに供給する。TFT204は、TFT以外の抵抗素子などに置き換えることも可能である。TFT205のソースには、基準電圧Vssが供給されており、TFT205がオンした際に、TFT204のソースとTFT205のドレインとの間に蓄積された電荷を放出させる。

#### 【0042】

TFT206のゲートには、次の段である2番目の段200(2)の出力信号OUT2が供給される。TFT206のドレインはノードA1に接続されており、ソースには基準電圧Vssが供給されている。出力信号OUT2がハイレベルとなるとTFT206がオンし、ノードA1に蓄積されている電荷を放出させる。

#### 【0043】

他の奇数番目の段200(3), 200(5), …, 200(n+1)の構成は、TFT201のゲートに前の段の出力信号OUT2, OUT4, …, OUTnが供給される以外は、1番目の段200(1)と同じである。最後の段以外の偶数番目の段200(2), 200(4), …, 200(n)の構成は、TFT201のゲートに前の段の出力信号OUT1, OUT3, …, OUTnが供給され、TFT202のドレインにクロック信号CK2が供給される以外は、1番目の段200(1)と同じである。最後の段200(n+2)の構成は、TFT201のゲートに前の段の出力信号OUTn+1が供給され、TFT206のゲートに制御信号群Gcntに含まれる終了信号Endが供給される以外は、1番目の段200(1)と同じである。

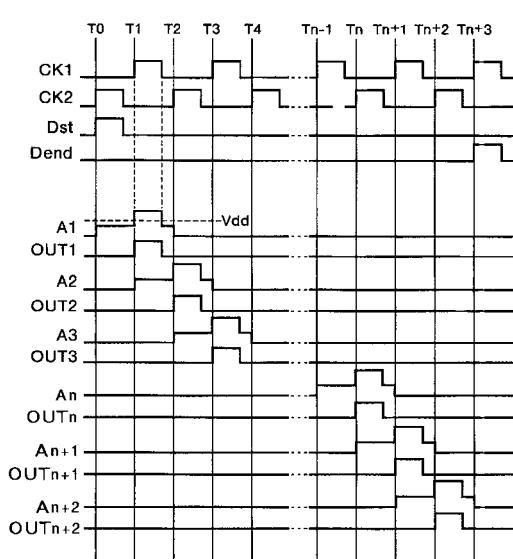

#### 【0044】

以下、この実施の形態にかかる液晶表示装置における動作について説明する。図5は、ゲートドライバ2を構成するシフトレジスタの動作を示すタイミングチャートである。このタイミングチャートにおいて、Tの期間が、液晶表示素子1における1水平期間となる。また、各水平期間において、ドレインドライバ3は、コントローラ4からの制御信号群Dcntに従って、当該水平期間の次の水平期間に対応する1ライン分の画像データ信号Dataを取り込んでいる。

#### 【0045】

まず、タイミングT0からタイミングT1までの間でスタート信号Dstがハイレベルとなり、1番目の段200(1)のTFT201がオンし、1番目の段200(1)のノードA1に電荷が蓄積される。これにより、TFT202, 205がオンし、TFT203がオフする。次に、タイミングT1においてクロック信号CK1がハイレベルに変化すると、この信号のレベルがほぼそのまま出力信号OUT1として表示領域11の1番目のゲートラインGL1に出力される。

#### 【0046】

ゲートラインGL1に出力された出力信号OUT1は、ゲートラインGL1及びこれに直接的または間接的に接続された各素子が構成する回路によって減衰されるが、ゲートラインGL1に接続された全てのTFT111をオン状態とするのに十分なレベルがある。ゲートラインGL1に接続された各TFT111がオンしているタイミングで、ドレインド

10

20

30

40

50

ライバ3は、ゲートラインGL1に対応する画素の画像データ信号をドレインラインDL1～DLmにそれぞれ出力する。これにより、ゲートラインGL1に対応する画素容量112に画像データ信号が書き込まれるが、補償容量113を設けたことによってTFT111に起因する減衰を小さく抑えることができる。

#### 【0047】

また、タイミングT1からT2の間でハイレベルの出力信号OUT1が2番目の段200(2)のTFT201に供給されると、2番目の段200(2)のノードA2に電荷が蓄積され、TFT202、205がオンし、TFT203がオフする。次に、タイミングT2においてクロック信号CK2がハイレベルに変化すると、この信号のレベルがほぼそのまま出力信号OUT2として表示領域11の2番目のゲートラインGL2に出力される。

10

#### 【0048】

ゲートラインGL2に出力された出力信号OUT2により、上記と同様にしてゲートラインGL2に接続された全てのTFT111がオン状態となり、ドレインドライバ3からドレインラインDL1～DLmに出力された画像データ信号がゲートラインGL2に対応する画素容量112に書き込まれる。出力信号OUT2は、また、1番目の段200(1)のTFT206に供給され、TFT206をオン状態とさせることにより、1番目の段200(1)のノードA1に蓄積された電荷を放出させる。このとき、出力信号OUT2のゲートラインGL2の出力による減衰の影響を、1番目の段200(1)のTFT206も受けることとなる。

#### 【0049】

20

タイミングT3以降も同様の動作を繰り返し、タイミングTn-1からTnの間で前の段の出力信号がn番目の段200(n)のTFT201に供給されると、n番目の段200(n)のノードAnに電荷が蓄積され、TFT202、205がオンし、TFT203がオフする。次に、タイミングTnにおいてクロック信号CK2がハイレベルに変化すると、この信号のレベルがほぼそのまま出力信号OUTnとして表示領域11のn番目のゲートラインGLnに出力される。

#### 【0050】

30

ゲートラインGLnに出力された出力信号OUTnにより、上記と同様にしてゲートラインGLnに接続された全てのTFT111がオン状態となり、ドレインドライバ3からドレインラインDL1～DLmに出力された画像データ信号がゲートラインGLnに対応する画素容量112に書き込まれる。出力信号OUTnは、また、n-1番目の段200(n-1)のTFT206に供給され、TFT206をオン状態とさせることにより、n-1番目の段200(n-1)のノードAn-1に蓄積された電荷を放出させる。

#### 【0051】

40

さらに、タイミングTnからTn+1の間で出力信号OUTnがn+1番目の段200(n+1)のTFT201に供給されることにより、n+1番目の段200(n+1)のノードAn+1に電荷が蓄積され、TFT202、205がオンし、TFT203がオフする。次に、タイミングTn+1においてクロック信号CK1がハイレベルに変化すると、この信号のレベルがほぼそのまま出力信号OUTn+1としてダミー素子領域12のn+1番目(ダミー素子領域12に限れば1番目)のゲートラインGLn+1に出力される。

#### 【0052】

ゲートラインGLn+1に出力された出力信号OUTn+1により、ゲートラインGLn+1に接続された全てのTFT121がオン状態となる。これにより、ゲートラインGLn+1及びこれに直接的または間接的に接続された素子が構成する負荷は、上記したゲートラインGL1～GLnのものと同等になる。出力信号OUT2は、ゲートラインGLn+1及びこれに接続された素子からなる負荷によって減衰されながら、n番目の段200(n)のTFT206に供給され、TFT206をオン状態とさせることにより、n番目の段200(n)のノードAnに蓄積された電荷を放出させる。

#### 【0053】

また、タイミングTn+1からTn+2の間では出力信号OUTn+1がn+2番目の段

50

200 (n + 2) の TFT201 に供給され、n + 2 番目の段 200 (n + 2) のノード An + 2 に電荷が蓄積される。そして、タイミング Tn + 2 においてクロック信号 CK2 がハイレベルに変化すると、この信号のレベルがほぼそのまま出力信号 OUTn + 2 としてダミー素子領域 12 の n + 2 番目（ダミー素子領域 12 に限れば 2 番目）のゲートライン GLn + 2 に出力される。出力信号 OUTn + 2 は、ゲートライン GLn + 2 及びこれに接続された素子からなる負荷によって減衰されながら、n + 1 番目の段 200 (n + 1) の TFT206 に供給され、n + 1 番目の段 200 (n + 1) のノード An + 1 に蓄積された電荷を放出させる。

#### 【0054】

さらに、タイミング Tn + 3 になると、コントローラ 4 からの制御信号群 Gcnt としてハイレベルの終了信号 Dend が n + 2 番目の段 200 (n + 2) の TFT206 に供給され、TFT206 がオンする。これにより、n + 2 番目の段 200 (n + 2) のノード An + 2 に蓄積された電荷が放出される。以下、垂直期間毎に上記のような動作を繰り返していく。

10

#### 【0055】

以上説明したように、この実施の形態にかかる液晶表示装置では、液晶表示素子 1 において表示領域 11 の外側にダミー素子領域 12 を設けている。ダミー素子領域 12 には、表示領域 11 の各ゲートライン GL1 ~ GLn 及びこれに直接または間接に接続される素子による負荷と同じ分布定数的な特性を有する負荷が、ゲートライン GLn + 1、GLn + 2 のそれぞれについて構成されることとなる。そして、ゲートドライバ 2 を構成するシフトレジスタは、ダミー素子領域 12 にあるゲートライン GLn + 1、GLn + 2 についても同じように走査している。

20

#### 【0056】

このため、ゲートライン GLn + 1、GLn + 2 のそれぞれの負荷並びにトランジスタ構成がゲートライン GL1 ~ GLn のそれぞれの負荷並びにトランジスタ構成と等しいので、ゲートライン GLn + 1、GLn + 2 にそれぞれ供給される信号、電圧として、ゲートライン GL1 ~ GLn にそれぞれ供給される所定の振幅の信号 CK1、CK2 や電圧 Vdd、Vss を利用することができる。また、ダミー段 200 (n + 1)、200 (n + 2) 用に新たな電圧値や振幅の信号を設定する必要がないので電圧生成回路及び配線設計を簡素化することができる。そして、表示領域 11 で最終のゲートライン GLn に対応するシフトレジスタの n + 1、n + 2 番目のダミー段 200 (n + 1)、200 (n + 2) が安定に動作できるので、n 番目の段 200 (n) も、それより前の段と同様の動作特性を有するものとなり、画像の表示のために必要なシフトレジスタの動作を安定化させることができる。

30

#### 【0057】

また、ダミー素子領域 12 に形成されている各ダミー素子 120 は、表示領域 11 に形成されている各画素の画素容量 112 と補償容量 113 との合成容量に等しいダミー容量 123 を有している。ダミー容量 123 は、表示のために必要なものではないので画素開口率を考慮する必要がなく、同一の基板上にあるため画素容量 112 よりも電極間の間隔が小さいので、画素容量 112 よりも必要な面積を小さくすることができる。このため、ダミー素子領域 12 に表示領域 11 の各ゲートライン GL1 ~ GLn の負荷と同等の負荷を形成するために必要となる面積を小さくすることができ、表示領域 11 の面積を相対的に大きくすることができる。

40

#### 【0058】

本発明は、上記の実施の形態に限られず、種々の変形、応用が可能である。以下、本発明に適用可能な上記の実施の形態の変形態様について説明する。

#### 【0059】

上記の実施の形態では、ダミー素子領域 12 におけるゲートライン GLn + 1、GLn + 2 は、表示領域 11 におけるゲートライン GL1 ~ GLn と同じ幅に構成して配線抵抗 124 が配線抵抗 114 と同じ抵抗値を有するものとし、画素容量 112 と補償容量 113

50

の合成容量に等しいダミー容量 123 を形成することで、ダミー素子 120 を構成するものとしていた。しかしながら、ダミー素子 120 の構成はこれに限られるものではない。

#### 【0060】

図 6 (a) は、ダミー素子の他の構造を示す図である。このダミー素子にもコモン電極は対向していない。また、この図においても、電極や配線を構成する金属層の間に形成されている絶縁層は省略している。図 6 (b) は、各ダミー素子の等価回路（横方向に隣接する 2 つ分）を示す図である。すなわち、各ダミー容量 133 は、図 2 (a) に示す画素を有する液晶表示装置において、TFT111 のゲートライン GL との寄生容量、ドレインライン DL との寄生容量からなる TFT (アクティブ素子) 111 の寄生容量と、画素容量 112 の容量と、補償容量 113 の容量と、の合成容量となるように設定されている。

10

#### 【0061】

この場合には、ダミー素子領域 12 において画素基板上の 1 番下の層には、ゲートライン GL 1 ~ GL n と同一材料からなり、ゲートライン GL 1 ~ GL n と一緒にパターニング形成され、各ゲートライン GL 1 ~ GL n とそれぞれ等しい容量の 2 本のダミーゲートライン GL n + 1、GL n + 2 が形成されている。ゲートライン GL の上には、SiN からなる絶縁層が 1 層以上形成され、その上にデータライン DL (DL 1 ~ DL m : 表示領域 11 のものと同一) と、各データライン DL には、各データライン DL と一緒に形成され、ダミーゲートライン GL n + 1、GL n + 2 に向けて突出するダミー容量電極 DiE (i は 1 ~ m のいずれか) が形成されている。ダミー容量電極 DiE とダミーゲートライン GL n + 1、GL n + 2 との重なり部分によってダミー容量 133 が形成される。すなわち、各データライン DL i (i は 1 ~ m のいずれか) は、ダミーゲートライン GL と交差する箇所毎にでダミー容量電極 DiE と接続されている。

20

#### 【0062】

このように形成される構造により、ダミーゲートライン GL n + 1、GL n + 2 のダミー容量電極 DiE と重ならない部分による配線抵抗 134 と、これに接続されたダミー容量 133 とからなるダミー素子が構成されることとなる。配線抵抗 134 の抵抗値とダミー容量 133 の容量値とは、ダミーゲートライン GL n + 1、GL n + 2 の幅 w d 1 とダミー容量電極 DiE の長さ l n 1 を調整することによって、調整される。そして、ダミーゲートライン GL n + 1、GL n + 2 のそれについて、このようなダミー素子が主走査方向の画素数分だけ接続された負荷が構成されるが、これらはゲートライン GL 1 ~ GL n のそれぞれの負荷と同等の分布定数的な電気特性を有するものとなる。

30

#### 【0063】

これによっても、ゲートドライバ 2 を構成するシフトレジスタの n 番目の段 200 (n) を、それより前の段と同様に安定して動作させることができるとなる。また、以上のような構成を有するダミー素子は、上記の実施の形態で示したダミー素子よりも、さらに小さく構成することが可能となる。このため、液晶表示素子 1 における表示領域 11 の面積の割合を、上記の実施の形態よりもさらに大きくすることが可能となる。

#### 【0064】

上記の実施の形態では、ダミー素子領域 12 には、2 本のゲートライン GL n + 1、GL n + 2 を設けるものとしていた。しかしながら、任意の数のゲートラインをダミー素子領域 12 に付加するものとすることができる。ダミー素子領域 12 におけるゲートラインの数を多くすれば多くのほど、ゲートドライバ 2 を構成するシフトレジスタを安定動作させることができ、少なくすれば少なくするほど、表示領域 11 の面積比を大きくすることができます。ここで、ダミー素子領域 12 にどれくらいの数のゲートラインを形成するかは、回路の安定動作と表示領域の面積との間のバランスによって選ぶことができる。

40

#### 【0065】

また、上記実施の形態で示した図 6 (a) のダミー容量電極 DiE の代わりに図 6 (c) に示すように、ダミーゲートライン GL n + 1、GL n + 2 と一緒に設けられたダミー容量電極 GjE (j は 1 ~ m のいずれか) としてもよい。すなわち、ダミーゲートライン GL n + 1、GL n + 2 のそれぞれは、データライン DL 1、DL 2、DL 3、……、D

50

$L_m$ と交差する箇所毎に設けられたダミー容量電極 G<sub>1</sub>E、G<sub>2</sub>E、G<sub>3</sub>E、……、G<sub>m</sub>Eと接続されている。ここでデータライン D<sub>L</sub>の幅の長さを w<sub>d2</sub>とし、ダミー容量電極 G<sub>j</sub>E の縦方向 (D<sub>L</sub> データラインの延在方向) の長さを l<sub>n2</sub>とすると、ダミー容量電極 G<sub>j</sub>E におけるデータライン D<sub>L</sub>との重なり部分の面積 (w<sub>d2</sub> × l<sub>n2</sub>) は、上記実施の形態における面積 (w<sub>d1</sub> × l<sub>n1</sub>) に等しいように設計されている。

#### 【0066】

なお、ダミー容量電極 G<sub>j</sub>E は、ダミーゲートライン G<sub>L</sub> に跨って 2 箇所に設けられているが、上記のような面積に設定されれば、図 6 (a) のようにどちらか一方のみに設けてもよい。同様に、図 6 (a) に示すダミー容量電極 D<sub>i</sub>E は、データライン D<sub>L</sub> に跨って横方向 (ダミーゲートライン G<sub>L</sub> の延在方向) の 2 箇所に設けてもよい。

10

#### 【0067】

また、上記各実施形態では液晶表示装置について説明したが、ゲートドライバ 2 の構成を撮像素子のゲートドライバに応用することができる。

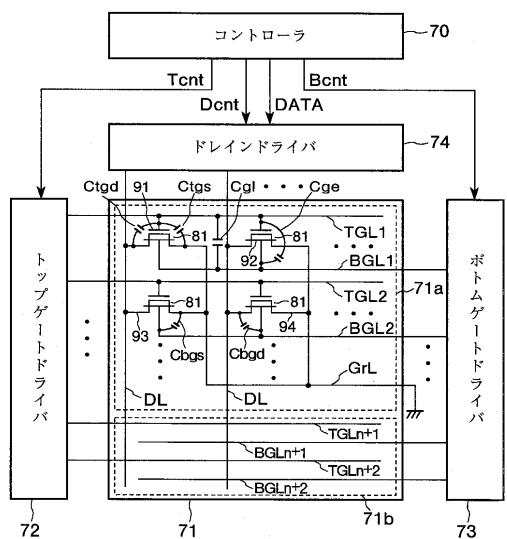

#### 【0068】

図 7 は、第 3 の実施の形態における、フォトセンサとしてダブルゲートトランジスタを適用した撮像素子を有する撮像装置の構成を示すブロック図である。この撮像装置は、例えば指紋センサとして使用されるもので、図示するように、コントローラ 70、撮像素子 71、トップゲートドライバ 72、ボトムゲートドライバ 73 及びドレインドライバ 74 から構成されている。

#### 【0069】

トップゲートドライバ 72 は、撮像素子領域 71a に設けられたトップゲートライン T<sub>G</sub><sub>L1</sub> ~ T<sub>G</sub><sub>Ln</sub> と接続され、ダミー素子領域 71b に設けられたダミートップゲートライン T<sub>G</sub><sub>Ln+1</sub>、T<sub>G</sub><sub>Ln+2</sub> と接続され、図 4 に示すシフトレジスタと同一の構成からなる。一方、ボトムゲートドライバ 73 は、撮像素子領域 71a に設けられたボトムゲートライン B<sub>G</sub><sub>L1</sub> ~ B<sub>G</sub><sub>Ln</sub> と接続され、ダミー素子領域 71b に設けられたダミーボトムゲートライン B<sub>G</sub><sub>Ln+1</sub>、B<sub>G</sub><sub>Ln+2</sub> と接続され、図 4 に示すシフトレジスタと同一の構成からなる。

20

#### 【0070】

撮像素子 71 は、マトリクス状に配置された複数のダブルゲートトランジスタ 81 で構成される。ダブルゲートトランジスタ 81 のトップゲート電極 91 はトップゲートライン T<sub>G</sub><sub>L</sub> に、ボトムゲート電極 92 はボトムゲートライン B<sub>G</sub><sub>L</sub> に、ドレイン電極 93 はドレインライン D<sub>L</sub> に、ソース電極 94 は接地されたグラウンドライン G<sub>r</sub><sub>L</sub> にそれぞれ接続されている。撮像素子 71 の下方には、ダブルゲートトランジスタ 81 の半導体層を励起する波長域の光は発光するバックライトが載置されている。

30

#### 【0071】

このような各トップゲートライン T<sub>G</sub><sub>L1</sub> ~ T<sub>G</sub><sub>Ln</sub> の合成容量は、接続されたダブルゲートトランジスタ 81 における、トップゲート電極 91 とドレイン電極 93 との間の寄生容量 C<sub>tgd</sub>、トップゲート電極 91 とソース電極 94 との間の寄生容量 C<sub>tgs</sub>、トップゲート電極 91 とボトムゲート電極 92 との間の寄生容量 C<sub>gde</sub>、並びにトップゲートライン T<sub>G</sub><sub>L</sub> とボトムゲートライン B<sub>G</sub><sub>L</sub> との間の重なり容量 C<sub>g1</sub> の和となる。各ダミートップゲートライン (ダミー走査ライン) T<sub>G</sub><sub>Ln+1</sub>、G<sub>Ln+2</sub> は、各トップゲートライン T<sub>G</sub><sub>L1</sub> ~ T<sub>G</sub><sub>Ln</sub> の上記合成容量と等しくなるように、交差するドレインライン D<sub>L</sub> との間の重なり面積を、図 6 (a) 又は図 6 (c) のようにすることで設定されている。

40

#### 【0072】

そして、各ボトムゲートライン B<sub>G</sub><sub>L1</sub> ~ B<sub>G</sub><sub>Ln</sub> の合成容量は、接続されたダブルゲートトランジスタ 81 における、ボトムゲート電極 91 とドレイン電極 93 との間の寄生容量 C<sub>bgd</sub>、ボトムゲート電極 91 とソース電極 94 との間の寄生容量 C<sub>bgs</sub>、ボトムゲート電極 91 とボトムゲート電極 92 との間の寄生容量 C<sub>ge</sub>、並びにボトムゲートライン B<sub>G</sub><sub>L</sub> とボトムゲートライン B<sub>G</sub><sub>L</sub> との間の重なり容量 C<sub>g1</sub> の和となる。各ダミー

50

ボトムゲートライン(ダミー走査ライン)B G L<sub>n+1</sub>、G L<sub>n+2</sub>は、各ボトムゲートラインB G L<sub>1</sub>～B G L<sub>n</sub>の上記合成容量と等しくなるように、交差するドレインラインD Lとの間の重なり面積を、図6(a)又は図6(c)のようにすることで設定されている。

#### 【0073】

撮像素子71を構成するダブルゲートトランジスタ81は、トップゲート電極91に印加されている電圧が+25(V)で、ボトムゲート電極92に印加されている電圧が0(V)であると、トップゲート電極91と半導体層との間に配置される窒化シリコンからなるゲート絶縁膜と半導体層とに蓄積されている正孔が吐出され、リセットされる。ダブルゲートトランジスタ81は、ソース、ドレイン電極93、94間に0(V)で、トップゲート電極91に印加されている電圧が-15(V)で、ボトムゲート電極92に印加されている電圧が0(V)となり、半導体層への光の入射によって発生した正孔-電子対のうちの正孔が上記半導体層及び上記ゲート絶縁膜に蓄積されるフォトセンス状態となる。この所定期間に蓄積される正孔の量は光量に依存している。10

#### 【0074】

フォトセンス状態において、バックライトがダブルゲートトランジスタ81に向け光を照射するが、このままではダブルゲートトランジスタ81の半導体層の下方の位置するボトムゲート電極92が遮光するので半導体層には十分なキャリアが生成されない。このとき、ダブルゲートトランジスタ81上方の絶縁膜上に指を載置すると、指の凹部(指紋形状を決める溝にあたる)の直下にあたるダブルゲートトランジスタ81の半導体層には、絶縁膜等で反射された光があまり入射されない。20

#### 【0075】

このように光の入射量が少なくて十分な量の正孔が半導体層内に蓄積されずに、トップゲート電極91に印加されている電圧が-15(V)で、ボトムゲート電極92に印加されている電圧が+10(V)となると、半導体層内に空乏層が広がり、nチャネルがピンチオフされ、半導体層が高抵抗となる。一方、フォトセンス状態において指の凸部(指の溝と溝の間の山)の直下にあたるダブルゲートトランジスタ81の半導体層には、絶縁膜等で反射された光が入射され十分な量の正孔が半導体層内に蓄積された状態で、このような電圧が印加された場合は、蓄積されている正孔がトップゲート電極91に引き寄せられて保持されることにより、半導体層のボトムゲート電極92側にnチャネルが形成され、半導体層が低抵抗となる。これらの読み出し状態における半導体層の抵抗値の違いが、ドレインラインD Lの電位の変化となって現れる。30

#### 【0076】

トップゲートドライバ72は、撮像素子71のトップゲートラインT G Lに接続され、コントローラ70からの制御信号群T c n tに従って、各トップゲートラインT G Lに+25(V)または-15(V)の信号を選択的に出力する。トップゲートドライバ72は、出力信号のレベルの相違、これに応じた入力信号のレベルの相違、並びに出力信号及び入力信号の位相の違いを除き、上記したゲートドライバ52を構成するシフトレジスタと実質的に同一の構成を有している。40

#### 【0077】

ボトムゲートドライバ73は、撮像素子71のボトムゲートラインB G Lに接続され、コントローラ70からの制御信号群B c n tに従って、各ボトムゲートラインB G Lに+10(V)または0(V)の信号を出力する。ボトムゲートドライバ73は、出力信号のレベルの相違、これに応じた入力信号のレベルの相違、並びに出力信号及び入力信号の位相の違いを除き、上記したゲートドライバ52を構成するシフトレジスタと実質的に同一の構成を有している。40

#### 【0078】

ドレインドライバ74は、撮像素子71のドレインラインD Lに接続され、コントローラ70からの制御信号群D c n tに従って、後述する所定の期間において全てのドレインラインD Lに定電圧(+10(V))を出力し、電荷をプリチャージさせる。ドレインドライバ50

イバ74は、プリチャージの後の所定の期間においてダブルゲートトランジスタ81の半導体層に光の入射、非入射に応じてチャネルが形成されているか否かによって変化する各ドレインラインDLの電位を読み出し、画像データDATAとしてコントローラ70に供給する。

#### 【0079】

コントローラ70は、制御信号群Cnt、Bcntによってそれぞれトップゲートドライバ72、ボトムゲートドライバ73を制御して、両ドライバ72、73からライン毎に所定のタイミングで所定レベルの信号を出力させる。これにより、撮像素子71の各ラインを順次リセット状態、フォトセンス状態、読み出し状態とさせる。コントローラ70は、また、制御信号群Dcntによりドレインドライバ74にドレインラインDLの電位変化を読み出させ、画像データDATAとして順次取り込んでいく。10

#### 【0080】

上記の各実施の形態では、本発明のアクティブ素子としてTFTを適用した場合を例として説明したが、MIM(Metal Insulator Metal)等の他のアクティブ素子も適用することができる。また、液晶表示素子や撮像素子と同一の基板上にゲートドライバ、ドレインドライバが形成された電子装置だけでなく、別途形成され、液晶表示素子や撮像素子に取り付けられた電子装置にも本発明を適用することができる。

#### 【0081】

なお、上記各実施の形態では、ダミー素子領域12のゲートラインGLn+1、GLn+2のそれぞれの負荷の一部として補償容量が設けられているが、表示領域11に配されたn本のゲートラインGL1～GLnにそれぞれ接続された画素に補償電極CEが設けられていない構造でのダミー素子領域12のゲートラインGLn+1、GLn+2のそれぞれの負荷は、上記各実施の形態でのダミー素子領域12のゲートラインGLn+1、GLn+2のそれぞれの負荷から各画素の補償容量が除かれたものに相当するように設定すればよい。20

#### 【0082】

なお、上記各実施の形態では、ダミー素子領域12のゲートラインGLn+1、GLn+2の2本を設けたが、ゲートラインGLn+1の1本のみとし、ゲートドライバ2も段200(1)～200(n+1)とした構成にしてもよい。

#### 【0083】

##### 【発明の効果】

以上説明したように、本発明によれば、走査ドライバによる画素の走査を安定して行うことができるようになる。

#### 【0084】

また、画素容量と補償容量の合成容量と等しい容量を形成したり、走査ラインとデータラインの一方に容量電極を設けて所定の容量を形成したりすることにより、表示領域外に設ける負荷の面積を小さくすることができ、相対的に表示領域の面積を大きくすることができる。

#### 【図面の簡単な説明】

【図1】本発明の実施の形態にかかる液晶表示装置の構成を示す図である。40

【図2】(a)は、図1の表示領域に形成された各画素の構造を示す図であり、(b)は、その等価回路図である。

【図3】(a)は、図1のダミー素子領域に形成された各ダミー素子の構造を示す図であり、(b)は、その等価回路図である。

【図4】図1のゲートドライバを構成するシフトレジスタの回路構成を示す図である。

【図5】図4のシフトレジスタの動作を示すタイミングチャートである。

【図6】(a)は、ダミー素子の他の構造を示す図であり、(b)は、その等価回路図であり、(c)は、ダミー素子のさらに他の構造を示す図である。

【図7】本発明の実施の形態にかかる撮像装置の構成を示すブロック図である。

#### 【符号の説明】

10

30

40

50

1 . . . 液晶表示素子、2 . . . ゲートドライバ、3 . . . ドレインドライバ、4 . . . コントローラ、11 . . . 表示領域、12 . . . ダミー素子領域、110 . . . 画素、111 . . . TFT、112 . . . 画素容量、113 . . . 補償容量、114 . . . 配線抵抗、120 . . . ダミー素子、121 . . . TFT、123 . . . ダミー容量、124 . . . 配線抵抗、133 . . . ダミー容量、134 . . . 配線抵抗、200 . . . 段、201 ~ 206 . . . TFT

【図1】

【図2】

【図3】

(b)

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

合議体

審判長 吉野 公夫

審判官 右田 昌士

審判官 田部 元史

(56)参考文献 特開平02-157826 (JP, A)

特開平09-311667 (JP, A)

特開平09-005780 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1368

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP4609970B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2011-01-12 |

| 申请号            | JP2001009325                                                                                                                                                                                                                                                                                                                                                                                                                                 | 申请日     | 2001-01-17 |

| [标]申请(专利权)人(译) | 卡西欧计算机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 卡西欧计算机有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 当前申请(专利权)人(译)  | 卡西欧计算机有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 豊島剛<br>佐々木和広<br>両澤克彦                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 发明人            | 豊島 剛<br>佐々木 和広<br>両澤 克彦                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G02F1/1368 G02F1/133 G09F9/30 G09G G09G3/26 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| CPC分类号         | G09G3/3688 G09G3/3648 G09G2310/0232 G09G2320/0223 G09G2320/0233                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| F1分类号          | G02F1/1368 G02F1/133.550 G09F9/30.338 G11C19/00 G11C19/00.J G11C19/00.K G11C19/28.D<br>G11C19/28.230                                                                                                                                                                                                                                                                                                                                         |         |            |

| F-Term分类号      | 2H092/JA25 2H092/JA26 2H092/JA34 2H092/JA37 2H092/JA41 2H092/JB22 2H092/JB31 2H092/JB68 2H092/NA07 2H092/NA11 2H093/NC22 2H093/NC34 2H093/NC35 2H093/NC62 2H093/ND34 2H093/ND37 2H093/ND58 2H192/AA24 2H192/BC31 2H192/CB05 2H192/CC02 2H192/CC04 2H192/DA12 2H192/FA02 2H193/ZA04 2H193/ZA07 2H193/ZF23 2H193/ZF24 2H193/ZH40 5B074/AA10 5B074/CA01 5B074/DA01 5C094/AA53 5C094/BA03 5C094/BA43 5C094/CA19 5C094/EA04 5C094/EA07 5C094/FB19 |         |            |

| 其他公开文献         | JP2002214643A                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

## 摘要(译)

要解决的问题：放置一个移位寄存器，用作稳定操作的液晶显示元件的驱动器。解决方案：在液晶显示元件1的显示区域11中，m & n个n像素以矩阵排列，(n)栅极线GL1至GLn在主扫描方向上延伸，(m)数据线DL1至DLm在垂直方向上延伸扫描方向排列在一个基板上。由各个栅极线GL1至GLn组成的电路和诸如TFT，像素电容器和直接或间接连接的补偿电容器的元件具有诸如分布常数的电特性。液晶显示元件1I产生栅极线GLn+1和GLn+2，栅极线GLn+1和GLn+2构成为具有分布常数等电特性以及显示区域11的栅极线GL1至GLn。栅极驱动器2选择在选择显示区域11中的栅极线GLn之后的水平时段中的虚设元件区域12中的栅极线GLn+1。