(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4593094号

(P4593094)

(45) 発行日 平成22年12月8日(2010.12.8)

(24) 登録日 平成22年9月24日(2010.9.24)

(51) Int.Cl.

F 1

|             |               |                  |             |               |             |

|-------------|---------------|------------------|-------------|---------------|-------------|

| <b>G02F</b> | <b>1/1368</b> | <b>(2006.01)</b> | <b>GO2F</b> | <b>1/1368</b> |             |

| <b>G09F</b> | <b>9/30</b>   | <b>(2006.01)</b> | <b>GO9F</b> | <b>9/30</b>   | <b>338</b>  |

| <b>H01L</b> | <b>29/417</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>29/50</b>  | <b>M</b>    |

| <b>H01L</b> | <b>21/336</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>29/78</b>  | <b>616K</b> |

| <b>H01L</b> | <b>29/786</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>29/78</b>  | <b>617J</b> |

請求項の数 16 (全 20 頁) 最終頁に続く

(21) 出願番号

特願2003-297575 (P2003-297575)

(22) 出願日

平成15年8月21日(2003.8.21)

(65) 公開番号

特開2005-72135 (P2005-72135A)

(43) 公開日

平成17年3月17日(2005.3.17)

審査請求日

平成16年9月2日(2004.9.2)

審判番号

不服2008-1629 (P2008-1629/J1)

審判請求日

平成20年1月21日(2008.1.21)

(73) 特許権者 000004237

日本電気株式会社

東京都港区芝五丁目7番1号

(74) 代理人 100095407

弁理士 木村 満

(72) 発明者 橋本 宣明

神奈川県川崎市中原区下沼部1753番地

NEC液晶テクノロジー株式会社内

(72) 発明者 木村 茂

神奈川県川崎市中原区下沼部1753番地

NEC液晶テクノロジー株式会社内

(72) 発明者 鈴木 聖二

神奈川県川崎市中原区下沼部1753番地

NEC液晶テクノロジー株式会社内

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

薄膜トランジスタ(TFT)が形成されたTFT基板と、ブラックマトリックスが形成された対向基板と、前記TFT基板と前記対向基板との間に挟まれた液晶層と、前記TFT基板の背面に配設されたバックライトとを備える液晶表示装置において、

前記TFTは、順次に形成されたゲート電極、ゲート絶縁膜、半導体層及びオーミックコンタクト層と、該オーミックコンタクト層上に形成されたソース電極及びドレイン電極と、を備え、前記オーミックコンタクト層の前記ソース電極と前記ドレイン電極との間に対応する領域に離間部が形成され、該離間部に対応する前記半導体層にチャネルが形成されており、

前記対向基板には、平面的に見て前記TFTのチャネルを被覆する遮光膜が形成されており、

前記TFTのチャネルと前記バックライトとの間に、前記TFTのチャネルを遮光する遮光層を有しており、

前記TFTのチャネルは、画素電極側の縁部のチャネル長のみが、チャネル中央部分のチャネル長に比して長いことを特徴とする液晶表示装置。

## 【請求項2】

前記TFTのゲート電極が前記TFTのチャネルと前記バックライトとの間に形成されており、該TFTのゲート電極が前記遮光層を兼ねる、請求項1に記載の液晶表示装置。

## 【請求項3】

10

20

前記チャネルを含むTFTの半導体層がアモルファスシリコンで形成されている、請求項1又は2に記載の液晶表示装置。

**【請求項4】**

前記チャネルを挟んで相互に対向するソース電極の縁部とドレイン電極の縁部とが、チャネルに関して非対称に形成されている、請求項1～3の何れか一に記載の液晶表示装置。

**【請求項5】**

前記チャネルの双方の縁部は、チャネル長が階段状に拡がる部分を有する、請求項1～4の何れか一に記載の液晶表示装置。

**【請求項6】**

前記チャネルは、前記チャネルの中央部から前記双方の縁部に向かって湾曲して拡がる、請求項1～3の何れか一に記載の液晶表示装置。

**【請求項7】**

薄膜トランジスタ(TFT)が形成されたTFT基板と、少なくとも前記TFTのチャネルを遮蔽するブラックマトリックスが形成された対向基板と、前記TFT基板と前記対向基板との間に挟まれた液晶層と、前記TFT基板の背面に配設されたバックライトとを備える液晶表示装置を製造する方法において、

前記TFT基板を形成する工程が、

TFTのゲート電極と、ゲート絶縁膜と、半導体層と、オームックコンタクト層とを順次に形成する工程と、

前記半導体層及びオームックコンタクト層をパターニングする工程と、

前記パターニングされたオームックコンタクト層上に、ソース電極及びドレイン電極を形成する工程と、

前記ソース電極及びドレイン電極をマスクとして、前記ソース電極とドレイン電極の間に対応する領域の前記オームックコンタクト層を除去することによって、前記半導体層を露出させてチャネル領域を形成する工程とを順次に備え、

前記チャネル領域の画素電極側の縁部のみのチャネル長を、チャネル領域の中央部分のチャネル長に比して長く形成することを特徴とする液晶表示装置の製造方法。

**【請求項8】**

薄膜トランジスタ(TFT)が形成されたTFT基板と、少なくとも前記TFTのチャネルを遮蔽するブラックマトリックスが形成された対向基板と、前記TFT基板と前記対向基板との間に挟まれた液晶層と、前記TFT基板の背面に配設されたバックライトとを備える液晶表示装置を製造する方法において、

前記TFT基板を形成する工程が、

TFTのゲート電極と、ゲート絶縁膜と、半導体層と、オームックコンタクト層と、金属層とを順次に形成する工程と、

前記金属層上にレジスト層を形成し、該レジスト層を、所定の波長を有する光源を用い、ソース電極パターン、ドレイン電極パターン、及び、前記ソース電極パターンとドレイン電極パターンとの間に配設される露光解像限界以下のパターンを有するマスクを介して露光し、前記ソース電極パターンと前記ドレイン電極パターンとの間に對応する領域の膜厚が、前記ソース電極パターン及びドレイン電極パターンに對応する領域の膜厚に比して薄いレジストパターンを形成する工程と、

前記レジストパターンを用いて、前記金属層、オームックコンタクト層、及び、半導体層をパターニングする工程と、

前記レジストパターンを所定の膜厚まで残して除去するレジスト一部除去工程と、

前記レジスト一部除去工程後のレジストパターンをマスクとし、前記金属層をパターニングしてソース電極及びドレイン電極を形成する工程と、

前記ソース電極及びドレイン電極をマスクとして、前記ソース電極とドレイン電極の間に対応する領域の前記オームックコンタクト層を除去することによって、前記半導体層を露出させてチャネル領域を形成する工程とを順次に備え、

10

20

30

40

50

前記チャネル領域の少なくとも一方の縁部のチャネル長を、チャネル領域の中央部分のチャネル長に比して長く形成することを特徴とする液晶表示装置の製造方法。

【請求項 9】

前記露光解像限界以下のパターンは、露光解像限界以下のスリットパターンとして構成される、請求項8に記載の液晶表示装置の製造方法。

【請求項 10】

前記スリットパターンの長辺方向の長さが、前記ソース電極パターン及びドレイン電極パターンの相互に対向する辺よりも長い、請求項9に記載の液晶表示装置の製造方法。

【請求項 11】

前記露光解像限界以下のパターンは、露光限界解像以下のハシゴ状パターンとして構成される、請求項8に記載の液晶表示装置の製造方法。 10

【請求項 12】

前記露光解像限界以下のパターンは、露光限界解像以下のドットパターンとして構成される、請求項8に記載の液晶表示装置の製造方法。

【請求項 13】

前記レジスト一部除去工程では、R I E - D E 装置により、前記レジストパターンを所定の膜厚まで残して除去する、請求項8 ~ 12の何れか一に記載の液晶表示装置の製造方法。

【請求項 14】

前記レジスト一部除去工程では、U V アッシャーにより、前記レジストパターンを所定の膜厚まで残して除去する、請求項8 ~ 13の何れか一に記載の液晶表示装置の製造方法。 20

【請求項 15】

前記TFTの双方のチャネル縁部のチャネル長を、前記チャネル中央部分のチャネル長よりも長く形成する、請求項8 ~ 12の何れか一に記載の液晶表示装置の製造方法。

【請求項 16】

前記チャネルを含むTFTの半導体層をアモルファスシリコンで形成する、請求項7 ~ 15の何れか一に記載の液晶表示装置の製造方法。

【発明の詳細な説明】

【技術分野】

30

【0001】

本発明は、液晶表示装置及びその製造方法に関し、更に詳しくは、薄膜トランジスタを有する液晶表示装置及びその製造方法に関する。

【背景技術】

【0002】

能動素子である薄膜トランジスタ(TFT)をスイッチング素子として使用するアクティブマトリクス型液晶表示装置が普及している。 TFTの半導体層には種々の材料が用いられているが、液晶表示装置では、多結晶シリコンを半導体層として用いたポリシリコン(p-Si) TFTや、非晶質シリコンを半導体層として用いたアモルファスシリコン(a-Si) TFTが一般的である。 p-Si TFTとa-Si TFTとを比較すると、a-Si TFTは、製造工程が少なく、また低温プロセスでの製造が可能である。 40

【0003】

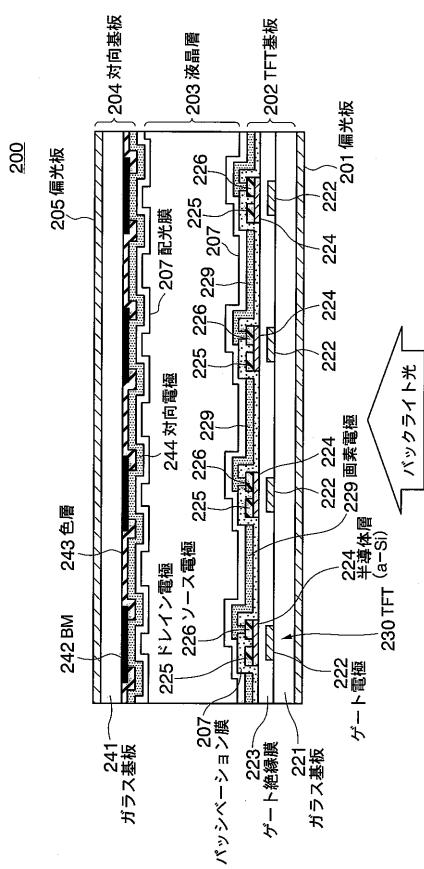

図15は、a-Si TFTを用いた、一般的な液晶表示装置の液晶パネルの断面を示している。液晶パネル200では、TFT基板202と対向基板204とが液晶層203を挟んで対向しており、各基板面には配向膜207が液晶層203との間に形成される。 TFT基板202の背面側であるバックライト光源側には第1偏光板201が配置され、対向基板204の表示面側には第2偏光板205が配置される。第1偏光板201と第2偏光板205とは、例えば、偏光方向が互いに90度異なる。

【0004】

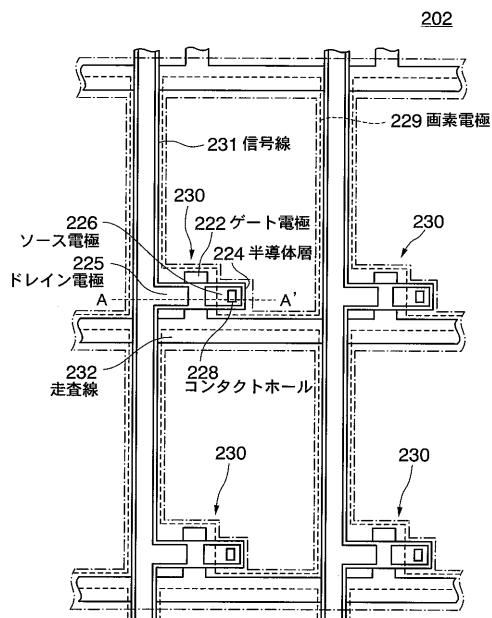

図16は、上記TFT基板202の一部を、対向基板204側から見た平面図として示

50

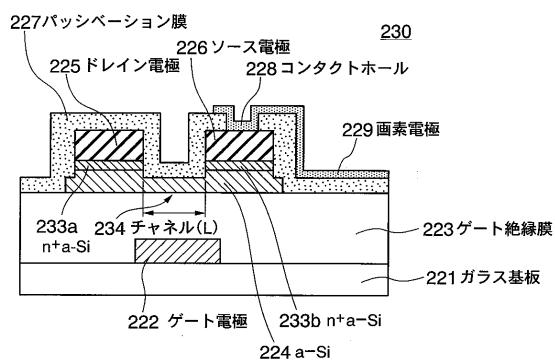

している。TFT基板202では、信号線231と走査線232とが格子状に配線され、その交点付近には、TFT230が形成される。TFT230のドレイン電極225は、信号線231から突き出た電極として構成され、ゲート電極222は、走査線232から突き出た電極として構成される。図17は、図16のB-B'断面に相当する、一般的なTFTの断面を示している。同図に示すような断面構造を有するTFTは、例えば特許第3152193号公報に記載された技術を適用して得られる。

#### 【0005】

一般に、p-Si TFTでは、ゲート電極、ドレイン電極、及び、ソース電極が、p-Si層の一方の側に形成されるコプラナ構造が採用され、a-Si TFTでは、ゲート電極222と、ドレイン電極225及びソース電極226とが、半導体層224を挟んで対向するスタガ構造が採用されることが多い。図17では、TFT230を、ゲート電極222が半導体層224の下層側に配置される逆スタガ構造で形成しているが、ゲート電極222が半導体層224の上層側に配置される順スタガ構造で形成することもできる。10

#### 【0006】

ドレイン電極225は、オーミックコンタクト層233aを介して半導体層224と接し、ソース電極226は、オーミックコンタクト層233bを介して半導体層224と接する。ソース電極226は、コンタクトホール228を介して画素電極229に接続される。同図に示すTFT230は、チャネルエッチング型TFTとして構成され、ドレイン電極225とその下層のオーミックコンタクト層233aとが同じサイズで形成され、ソース電極226とその下層のオーミックコンタクト層233bとが同じサイズで形成される。20

#### 【0007】

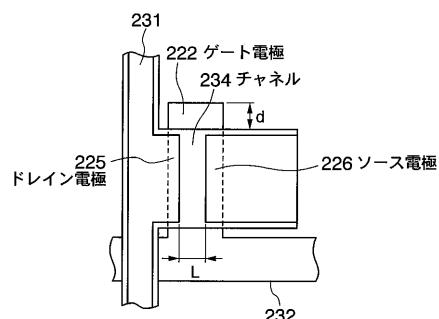

TFT230では、ゲート電極222の上層の、ドレイン電極225側のオーミックコンタクト層233aのソース電極226側の端部の位置から、ソース電極226側のオーミックコンタクト層233bのドレイン電極225側の端部の位置までの間の半導体層224が、チャネル領域234を構成する。逆スタガのTFT230では、ゲート電極222は、遮光膜を兼ね、バックライト光源側からチャネル領域234に侵入する光を遮光する。図18は、図16に示すTFT230の1つを拡大して示している。ドレイン電極225及びソース電極226は、チャネル領域234を挟んで対向する辺が、互いに平行であり、チャネル領域234のチャネル長Lは、チャネル幅方向の位置によらず、一定の長さに形成される。30

#### 【0008】

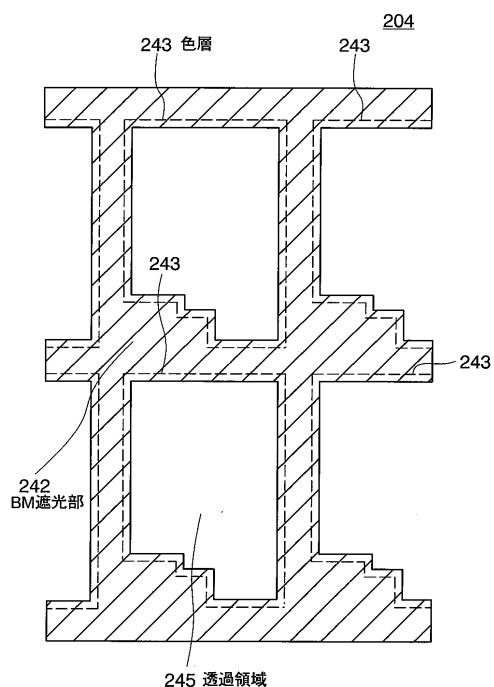

図19は、図16に示すTFT基板202と空間的に重なる対向基板204の一部を平面図として示している。同図に示すように、対向基板204上のブラックマトリクス242は、TFT230、信号線231、及び、走査線232と空間的に重なる位置に形成され、バックライト光源側から入射する光を遮光し、透過領域255を区画する。透過領域255からの光の出射量は、液晶層203を、TFT230の画素電極229と、対向基板の対向電極244とによって制御することで、コントロールされる。透過領域255には、例えばR、G、Bの3色の色層243が設けられ、画像のカラー表示を可能としている。40

【特許文献1】特許第3152193号公報

【発明の開示】

【発明が解決しようとする課題】

#### 【0009】

ところで、ブラックマトリクス242は、反射率が低い材料で形成されてはいるものの、対向基板204(図15)に入射した光の一部は、ブラックマトリクス242で反射して、TFT基板202側に向かう。この反射光の一部は、ゲート電極222とドレイン電極225又はソース電極226との間で多重反射し、チャネル領域234に侵入する。TFT230では、チャネル領域234(図18)のチャネル幅方向の両端の領域が、光が侵入しやすい領域である。チャネル領域234を構成する半導体層224に光が入射する50

と、TFT230にリーク電流が発生してスイッチング特性が悪化し、液晶表示装置における表示品質が低下してしまう。

#### 【0010】

例えば、ブラックマトリクス242で反射した光による光リーク電流を低減できる技術として、図15で対向基板204に配置されるブラックマトリクス242及び色層243をTFT基板202に積層する構成を採用する技術がある。この技術では、TFT230とブラックマトリクス242の間の距離を狭めることで、ブラックマトリクス242で反射した光による光リーク電流を低減することができる。しかし、この技術では、TFT基板202とブラックマトリクス242及び色層243とを連続して形成する必要があるため、技術的課題が多い。

10

#### 【0011】

一方、TFT230では、上記したブラックマトリクスでの反射光だけでなく、バックライト光源側からTFT基板202に入射する光の一部も、チャネル領域234に侵入する。これは、ゲート電極222によって、チャネル領域234に侵入する光を完全に遮光することができないためである。特に、チャネル領域234の画素電極229(図16)側の縁部では、チャネル領域234に近接して走査線232が配線されないため、走査線232側の縁部に比して光の侵入量が大きくなる。チャネル領域234の画素電極229側の縁部では、ゲート電極222の図18に示す突き出し量dをある程度大きくとることで、光の侵入を防いでいる。

#### 【0012】

20

しかし、対向基板204に形成されるブラックマトリクス242はTFT230と空間的に重なる位置に形成されることから、ゲート電極222の突き出し量dを大きくとり、TFT230の形成領域が広くなると、その分だけ透過領域255が狭くなる。液晶表示装置では、透過領域255を広くとることで、輝度等の表示品質を向上させることができるために、透過領域255を広くとりたいという要求がある。しかし、従来の液晶表示装置では、上記した理由により、TFT230の形成領域を狭くして、透過領域255を広くすることができなかった。

#### 【0013】

本発明は、上記問題点を解消し、TFT形成領域を狭くした場合についても、光リーク電流の影響を低減できる薄膜トランジスタを有する液晶表示装置及びその製造方法を提供することを目的とする。

30

#### 【課題を解決するための手段】

#### 【0015】

上記目的を達成するために、本発明の液晶表示装置は、薄膜トランジスタ(TFT)が形成されたTFT基板と、ブラックマトリクスが形成された対向基板と、前記TFT基板と前記対向基板との間に挟まれた液晶層と、前記TFT基板の背面に配設されたバックライトとを備える液晶表示装置において、前記TFTは、順次に形成されたゲート電極、ゲート絶縁膜、半導体層及びオーミックコンタクト層と、該オーミックコンタクト層上に形成されたソース電極及びドレイン電極と、を備え、前記オーミックコンタクト層の前記ソース電極と前記ドレイン電極との間に対応する領域に離間部が形成され、該離間部に対応する前記半導体層にチャネルが形成されており、前記対向基板には、平面的に見て前記TFTのチャネルを被覆する遮光膜が形成されており、前記TFTのチャネルと前記バックライトとの間に、前記TFTのチャネルを遮光する遮光層を有しており、前記TFTのチャネルは、画素電極側の縁部のチャネル長のみが、チャネル中央部分のチャネル長に比して長いことを特徴とする。

40

#### 【0016】

本発明の液晶表示装置では、バックライト光源側から回り込んだ光、或いは、対向基板のブラックマトリクスで反射した光が入射しやすいため、光リーク電流の影響を受けやすいTFTのチャネル縁部の少なくとも一方が、チャネル中央部に比して長く設定されている。このため、チャネル縁部に光が入射した場合にも、光リーク電流の電流経路が長いた

50

めに光リーク電流を低減でき、光リーク電流がTFTのスイッチング特性に与える影響を低減できる。従って、表示品質が高い液晶表示装置を得ることができる。

#### 【0017】

従来のTFTでは、チャネル領域の画素電極側の縁部に侵入する光を低減するために、ゲート電極の突き出し量を小さく設定することができなかったが、本発明のTFTでは、チャネル領域の画素電極側の縁部のチャネル長を、チャネル中央部に比して長く設定する構成を採用するときには、ゲート電極の突き出し量を小さく設定することができる。この場合には、TFTが形成される領域の面積を狭くして、液晶表示装置の対向基板における透過領域を広くすることができ、液晶表示装置の表示品質を向上させることができる。なお、TFTのチャネルは、縁部が直線状に広がる形状であってもよく、湾曲して広がる形状であってもよく、或いは、階段状に広がる形状であってもよい。ソース電極とドレイン電極とは、互いに対向する縁部が対称な形状でなくてもよく、例えばドレイン電極をコの字状に形成することもできる。

TFTのチャネルは、ドレイン電極側の接触層のソース電極側の縁部の位置から、ソース電極側の接触層のドレイン電極側の縁部の位置までの間の真性半導体層によって形成される。TFTは、チャネルエッチ型であってもよく、或いは、チャネル保護型であってもよい。

#### 【0019】

本発明の液晶表示装置では、前記TFTのゲート電極が前記TFTの前記チャネルと前記パックライトとの間に形成されており、該TFTのゲート電極が前記遮光層を兼ねることが好ましい。

#### 【0020】

本発明の液晶表示装置では、前記チャネルを含むTFTの半導体層をアモルファスシリコンシリコンで形成することができる。

#### 【0021】

本発明の液晶表示装置のTFTでは、チャネル縁部のチャネル長が長く設定されることで、光リーク電流を低減できるため、例えば、光感度が高いアモルファスシリコンを用いてTFTを形成した場合についても、良好な特性を得ることができる。

#### 【0024】

本発明の液晶表示装置では、前記チャネルを挟んで相互に対向するソース電極の縁部とドレイン電極の縁部とが、チャネルに関して非対称に形成されている構成を採用することができ、前記チャネルの双方の縁部は、チャネル長が階段状に拡がる部分を有する構成を採用することができ、或いは、前記チャネルは、前記チャネルの中央部から前記双方の縁部に向かって湾曲して拡がる構成を採用することができる。

#### 【0025】

本発明の第1の視点のTFTの製造方法は、薄膜トランジスタ(TFT)が形成されたTFT基板と、少なくとも前記TFTのチャネルを遮蔽するブラックマトリックスが形成された対向基板と、前記TFT基板と前記対向基板との間に挟まれた液晶層と、前記TFT基板の背面に配設されたパックライトとを備える液晶表示装置を製造する方法において、前記TFT基板を形成する工程が、TFTのゲート電極と、ゲート絶縁膜と、半導体層と、オーミックコンタクト層とを順次に形成する工程と、前記半導体層及びオーミックコンタクト層をパターニングする工程と、前記パターニングされたオーミックコンタクト層上に、ソース電極及びドレイン電極を形成する工程と、前記ソース電極及びドレイン電極をマスクとして、前記ソース電極とドレイン電極の間に對応する領域の前記オーミックコンタクト層を除去することによって、前記半導体層を露出させてチャネル領域を形成する工程とを順次に備え、前記チャネル領域の画素電極側の縁部のみのチャネル長を、チャネル領域の中央部分のチャネル長に比して長く形成することを特徴とする。

#### 【0026】

本発明の第1の視点のTFTの製造方法では、半導体層及びオーミックコンタクト層をパターニングした後に、オーミックコンタクト層上にソース電極及びドレイン電極を形成

10

20

30

40

50

し、ソース電極及びドレイン電極を用いてオーミックコンタクト層を除去して半導体層を露出させ、チャネル領域を形成する。ソース電極及びドレイン電極の形成する工程において、それらの電極を所望の形状に形成することで、チャネル領域の少なくとも一方の縁部のチャネル長が、中央部に比して長いTFTを形成することができる。

#### 【0027】

本発明の第2の視点のTFTの製造方法は、薄膜トランジスタ(TFT)が形成されたTFT基板と、少なくとも前記TFTのチャネルを遮蔽するブラックマトリックスが形成された対向基板と、前記TFT基板と前記対向基板との間に挟まれた液晶層と、前記TFT基板の背面に配設されたパックライトとを備える液晶表示装置を製造する方法において、前記TFT基板を形成する工程が、TFTのゲート電極と、ゲート絶縁膜と、半導体層と、オーミックコンタクト層と、金属層とを順次に形成する工程と、前記金属層上にレジスト層を形成し、該レジスト層を、所定の波長を有する光源を用い、ソース電極パターン、ドレイン電極パターン、及び、前記ソース電極パターンとドレイン電極パターンとの間に配設される露光解像限界以下のパターンを有するマスクを介して露光し、前記ソース電極パターンと前記ドレイン電極パターンとの間に応する領域の膜厚が、前記ソース電極パターン及びドレイン電極パターンに対応する領域の膜厚に比して薄いレジストパターンを形成する工程と、前記レジストパターンを用いて、前記金属層、オーミックコンタクト層、及び、半導体層をパターニングする工程と、前記レジストパターンを所定の膜厚まで残して除去するレジスト一部除去工程と、前記レジスト一部除去工程後のレジストパターンをマスクとし、前記金属層をパターニングしてソース電極及びドレイン電極を形成する工程と、前記ソース電極及びドレイン電極をマスクとして、前記ソース電極とドレイン電極の間に応する領域の前記オーミックコンタクト層を除去することによって、前記半導体層を露出させてチャネル領域を形成する工程とを順次に備え、前記チャネル領域の少なくとも一方の縁部のチャネル長を、チャネル領域の中央部分のチャネル長に比して長く形成することを特徴とする。

#### 【0028】

本発明の第2の視点のTFTの製造方法では、レジストパターンを露光形成する際に、ソース電極パターン、ドレイン電極パターン、及び、ソース電極パターンとドレイン電極パターンとの間に配置される、短辺方向の幅が露光解像限界以下のパターンを有するマスクを使用する。このようなマスクを用いて形成されたレジストパターンは、ソース電極パターン及びドレイン電極パターンに対応する領域では、露光された光が透過せずに未露光となってレジスト膜厚が厚く形成され、ソース電極パターンとドレイン電極パターンとの間に応する領域では、露光された光が透過しきれずに半露光となって、レジスト膜厚が、未露光の領域に比して薄く形成される。また、上記した領域以外の露光領域では、レジスト膜厚が半露光領域に比して更に薄いか、或いは、レジストが除去される。このように形成したレジストパターンを用いて、半導体層までをエッチングすることで、例えば島状の半導体層を形成でき、その後、レジスト一部除去工程により、レジスト膜厚が薄い半露光領域のレジストパターンを除去したレジストパターンを用いてソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極を用いて、オーミックコンタクト層をエッチングすることで、チャネル領域を形成することができる。

#### 【0029】

また、レジストパターンの露光形成の際に、露光解像限界以下のパターンがソース電極パターンとドレイン電極パターンとの間に配置されることにより、互いに対向するソース電極部分を構成するレジストパターン、及び、ドレイン電極部分を構成するレジストパターンの縁部の端部では、中央部に比して多くの光が回り込み、半露光の領域の幅が中央部に比して広がる。これにより、ソース電極部分を構成するレジストパターン、及び、ドレイン電極部分を構成するレジストパターンは、互いに対向する辺が、端部における辺間の距離が中央部に比して長くなるような湾曲形状に形成され、チャネル領域の縁部の少なくとも一方のチャネル長が、チャネル領域の中央部に比して長いTFTを形成することができる。

10

20

30

40

50

**【0030】**

本発明の第1の視点のTFTの製造方法では、半導体層及びオームックコンタクト層をパターニングする際のレジストパターンを形成するためのマスクと、ソース電極及びドレイン電極を形成する際のレジストパターンを形成するためのマスクとの2枚のマスクが必要になる。本発明の第2の視点のTFTの製造方法では、TFTの半導体層及びオームックコンタクト層と、ソース電極及びドレイン電極とを、1枚のマスクを用いて形成したレジストパターンで形成することができ、本発明の第1の視点のTFTの製造方法に比して、マスクを1枚削減して、TFTの製造コストを低減できる。

**【0031】**

本発明の第2の視点のTFTの製造方法では、前記露光解像限界以下のパターンを、露光解像限界以下のスリットパターンとして構成することができ、前記スリットパターンの長辺方向の長さが、前記ソース電極パターン及びドレイン電極パターンの相互に対向する辺よりも長くなるようにすることができ、露光限界解像以下のハシゴ状パターンとして構成することができ、或いは、露光限界解像以下のドットパターンとして構成することができる。

10

**【0032】**

本発明の第2の視点のTFTの製造方法は、前記レジスト一部除去工程では、RIE-DE装置により、前記レジストパターンを所定の膜厚まで残して除去することができ、UVアッシャーにより、前記レジストパターンを所定の膜厚まで残して除去することができ、或いは、前記TFTの双方のチャネル縁部のチャネル長を、前記チャネル中央部分のチャネル長よりも長く形成することができる。

20

本発明の第1及び第2の視点のTFTの製造方法では、前記チャネルを含むTFTの半導体層をアモルファスシリコンで形成することができる。

**【発明の効果】****【0033】**

以上説明したように、本発明の液晶表示装置は、光リーク電流の影響を受けやすいTFTのチャネル縁部の少なくとも一方が、チャネル中央部に比して長く設定されているため、バックライト光源側から光が回り込み、対向基板のブラックマトリクスで反射した光がチャネルに入射したとしても、光リーク電流を低減でき、スイッチング特性が悪化しない。

30

**【0034】**

本発明の第1及び第2の視点のTFTの製造方法では、チャネル領域の少なくとも一方の縁部のチャネル長が、中央部に比して長いTFTを形成することができる。また、本発明の第2の視点のTFTの製造方法では、TFTを形成する際に使用するマスクを1枚削減でき、本発明の第1の視点のTFTの製造方法に比して、TFTの製造コストを低減できる。

**【発明を実施するための最良の形態】****【0035】**

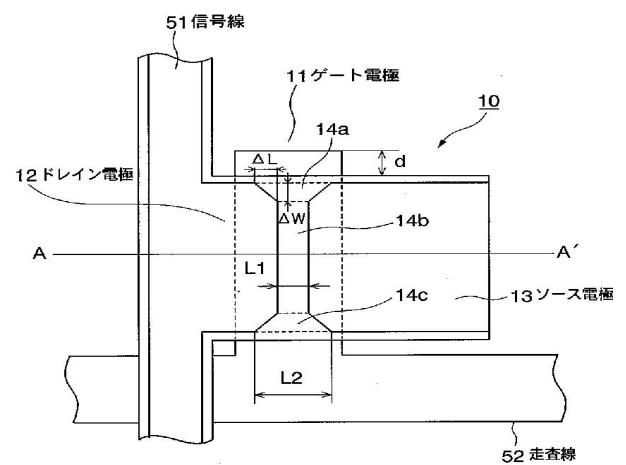

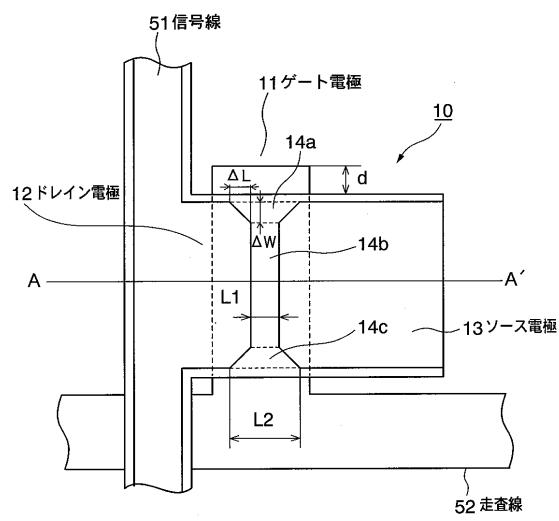

以下、図面を参照し、本発明の実施形態例に基づいて、本発明を更に詳細に説明する。図1は、本発明の第1実施形態例のTFTを平面図として示している。本実施形態例のTFT10は、ドレイン電極12、ソース電極13、及び、チャネル領域14の平面形状が、図18に示す従来のTFT230と相違する。TFT10は、図16に示すTFT230と同様に、信号線51と走査線52との交点付近に形成され、図17に示す一般的なTFTと同様な断面構造を有する。なお、図17に示す断面は、図1では、同図におけるA-A'断面に相当する。

40

**【0036】**

ドレイン電極12及びソース電極13は、それぞれ、チャネル領域14の画素電極側の縁部14a、及び、走査線側の縁部14cのチャネル長が、チャネル中央部14b側から外側に向かって長くなるように、互いに対向する辺の両端において、チャネル幅方向の両端の角が切り落とされた形状となっている。図1の例では、ドレイン電極12及びソース

50

電極 13 は、チャネル幅方向の両端の角が、互いに対向する辺からそれぞれの内側に向けて、底辺を W、高さを L とする直角三角形と同様な平面形状で切り落とされた形状となっている。チャネル中央部 14b では、チャネル長が、一定値 L1 となっており、チャネル領域の画素電極側の縁部 14a、及び、走査線 52 側の縁部 14c では、それぞれ、チャネル長が画素電極側又は走査線 52 側に向けて、L1 から L2 (= L1 + 2 × L) 向けて長くなっている。

#### 【0037】

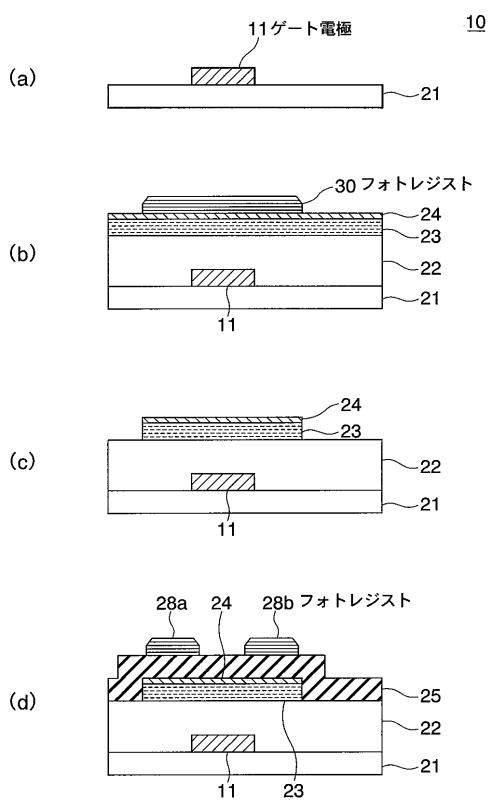

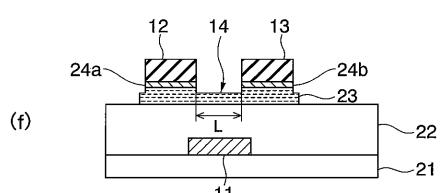

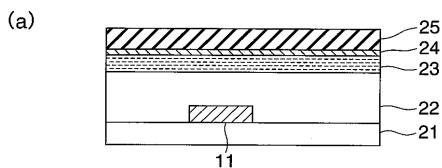

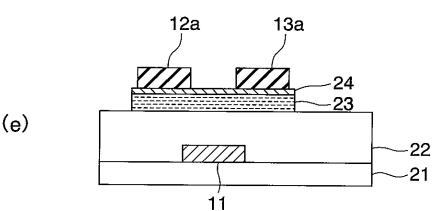

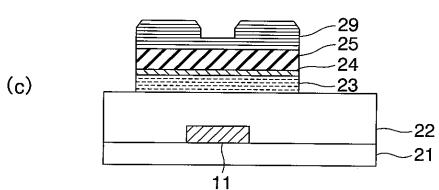

図 2(a) ~ (d)、及び、図 3(e) ~ (g) は、図 1 に示す TFT10 の断面を製造工程段階ごとに示している。TFT10(図 1) は、図 17 に示す断面構造と同様な構造を有し、以下のように形成される。ガラス基板 21 上に、第 1 導電膜を積層し、その第 1 導電膜を第 1 フォトレジストパターンを用いてエッチングし、所望の形状のゲート電極 11 を形成する(図 2(a))。ゲート絶縁膜 22、a-Si 層である半導体層 23、及び、n+a-Si 層であるオーミックコンタクト層 24 を積層し、オーミックコンタクト層 24 上に、第 2 フォトレジストパターン 30 を形成する(同図(b))。その第 2 フォトレジストパターン 30 を用いて、半導体層 23 及びオーミックコンタクト層 24 をエッチングし、半導体層 23 及びオーミックコンタクト層 24 を形成する(同図(c))。

#### 【0038】

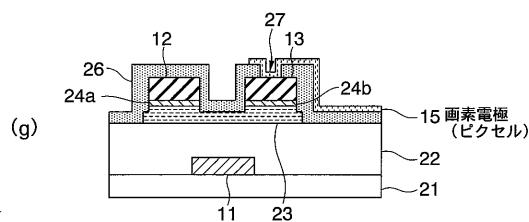

第 2 導電膜 25 を積層し、その上に、第 3 フォトレジストパターン 28 を形成する(図 2(d))。第 3 フォトレジストパターン 28 の一方である第 3 フォトレジストパターン 28a は、第 2 導電膜 25 をエッチングして得られるドレイン電極 12 が、図 1 に示す平面形状となるような形状に形成され、他方である第 3 フォトレジストパターン 28b は、ソース電極 13 が、図 1 に示す平面形状となるような形状に形成される。第 3 フォトレジストパターン 28 を用いて、第 2 導電膜 25 をエッチングし、図 1 に示す平面形状を有するドレイン電極 12 及びソース電極 13 を形成する(図 3(e))。

#### 【0039】

ドレイン電極 12 及びソース電極 13 を用いて、オーミックコンタクト層 24 及び半導体層 23 の一部をチャネルエッティングし、ゲート電極 11 の上層の、ドレイン電極 12 側のオーミックコンタクト層 24a のソース電極 13 側の端部の位置から、ソース電極 13 側のオーミックコンタクト層 24b のドレイン電極 12 側の端部の位置までのチャネル領域 14 を形成する。チャネル領域 14 の形成後に、パッシベーション膜 26 を積層し、そのパッシベーション膜 26 を第 4 フォトレジストパターンを用いてエッチングし、コンタクトホール 27 を形成する。ついで、透明導電膜を積層し、その透明導電膜を第 5 フォトレジストパターンを用いてエッティングし、画素電極 15 が形成される(図 3(g))。

#### 【0040】

本実施形態例では、チャネル領域 14 において、液晶表示装置に使用した際に、光の影響を受けやすい領域であるチャネル幅方向の双方の縁部 14a、14c におけるチャネル長を、チャネル中央部 14b におけるチャネル長に比して長く設定したため、それらの領域に光が侵入し、光リーク電流が発生した場合であっても、光リーク電流の電流経路が長く、光リーク電流が TFT10 のスイッチング特性に与える影響を低減できる。また、従来の TFT では、チャネル領域の画素電極側の縁部に侵入する光を低減するために、ゲート電極の突き出し量 d を小さく設定することができなかつたが、本実施形態例では、上記した理由により、ゲート電極の突き出し量 d を小さく設定することができ、TFT10 が形成される領域の面積を狭くして、対向基板(図 15)における透過領域(図 19)を広くすることにより、液晶表示装置の表示品質を向上させることができる。

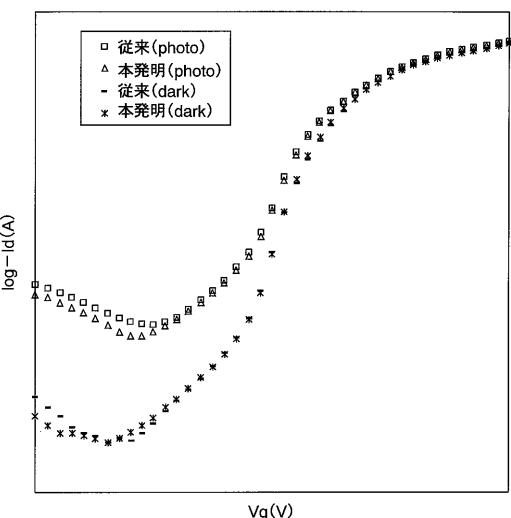

#### 【0041】

図 4 は、TFT におけるゲート電圧とドレイン電流との関係をグラフで示している。本発明者らは、TFT10 を試作し、バックライト装置を点灯した状態(photo)と、バックライト装置を点灯しない状態(dark)とのそれぞれについて、実験により、試作した TFT10 と従来の TFT230(図 18) の Vg - Id 特性を測定した。

#### 【0042】

10

20

30

40

50

なお、本実施形態例のTFT10では、チャネル幅Wを24μmに設定し、チャネル中央部14bにおけるチャネル長L1を6.0μmに設定した。また、チャネル領域の画素電極側の縁部14a、及び、走査線側の縁部14cでは、Wを3.0μmに設定し、Lを1.2に設定し、チャネル縁部から3μm以内のチャネル長の平均値、つまり、チャネル縁部から1.5μmの位置でのチャネル長を、チャネル長L1の120%である7.2μmに設定した。また、従来のTFT230では、チャネル幅Wを24μmに設定し、チャネル長Lを6.0μmに設定した。

#### 【0043】

図4に示すように、バックライト装置を点灯しない状態では、本実施形態例のTFT10と、従来のTFT230とは、ドレイン電流は、ほぼ同様に変化する。バックライト装置を点灯した状態では、本実施形態例のTFT10は、従来のTFT230に比して、光リーケ電流の影響が低減し、オフ電流の最小値を、従来のTFT230の約40%減少させることができた。また、本実施形態例のTFT10のオン電流は、従来のTFT230と同程度であった。実験により、本実施形態例のTFT10では、光の影響を受けやすい、チャネル縁部から3μm以内の位置におけるチャネル長を長く設定することで、光リーケ電流の影響を効果的に低減できると共に、従来のTFT230同程度のオン電流が得られることが確かめられた。

#### 【0044】

一般に、ドレイン電流は、チャネル幅Wとチャネル長Lの比(W/L)に比例して大きくなる。本実施形態例のTFT10では、光リーケ電流による影響をより低減させるために、チャネル領域の画素電極側の縁部14a、及び、走査線側の縁部14cにおける平均チャネル長を長くしていくと、オン電流の低下が無視できなくなる。このような場合には、チャネル中央部14bにおけるチャネル長L1を短くして、チャネル領域14全体での平均チャネル長の増加を抑えるなどして、所望のオン電流が得られるように設計するといい。

#### 【0045】

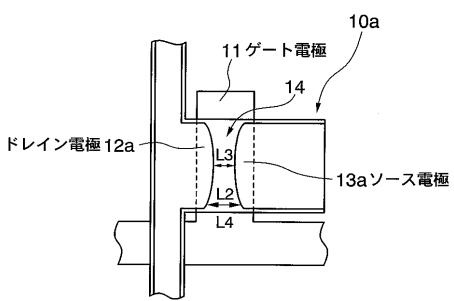

図5は、本発明の第2実施形態例のTFTを平面図として示している。本実施形態例のTFT10aは、ドレイン電極12a、ソース電極13a、及び、チャネル領域14の形状が、第1実施形態例と相違する。ドレイン電極12a及びソース電極13aは、互いに対向する辺が、中央部が膨らむように、湾曲した形状で形成され、チャネル領域14は、中央部でのチャネル長L3に比して、チャネル幅方向の縁部でチャネル長L4が長くなるように形成される。

#### 【0046】

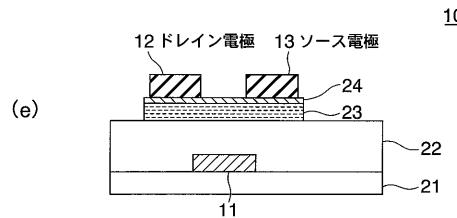

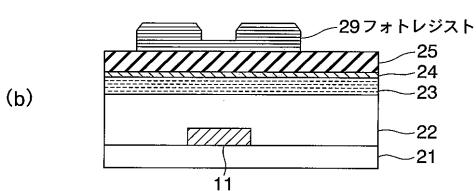

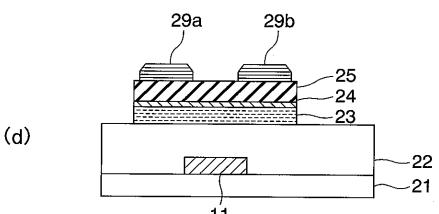

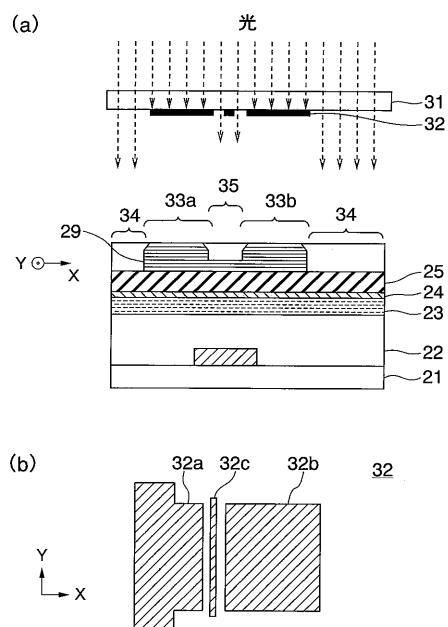

図6(a)及び(b)、並びに、図7(c)～(d)は、上記TFT10aの断面を、製造工程段階ごとに示している。上記TFT10aは、以下のように形成することもできる。ガラス基板21上に、ゲート電極11を形成し、ゲート絶縁膜22、a-Si層である半導体層23、n+a-Si層であるオーミックコンタクト層24、及び、第2導電膜25を積層し(図6(a))、その上に、フォトレジストパターン29を形成する(図6(b))。

#### 【0047】

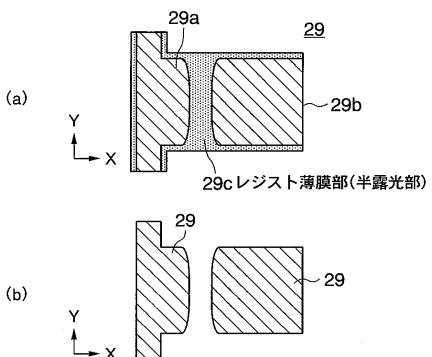

図8(a)は、図6(b)におけるフォトレジストパターン29の形成の様子を断面図として示し、図8(b)は、同図(a)のフォトマスク31に形成される遮光パターンの形状を平面図として示している。また、図9(a)は、図8(b)に示す遮光パターンを介して露光して得られるフォトレジストパターン29を平面図として示し、図9(b)は、同図(a)から半露光領域35に対応する領域を除去したフォトレジストパターン29を平面図として示している。以下、図8及び図9を参照し、フォトレジストパターン29の形成について説明する。

#### 【0048】

フォトマスク31(図8(a))には、同図(b)に示すような平面形状を有する遮光パターン32が形成される。遮光パターン32は、ドレイン電極用遮光パターン32a、

10

20

30

40

50

ソース電極用遮光パターン32b、及び、スリット遮光パターン32cを有する。ドレイン電極用遮光パターン32aは、最終的に図5に示す平面形状に形成されるドレイン電極12aに対応して形成され、ソース電極用遮光パターン32bは、最終的に図5に示す平面形状に形成されるソース電極13aに対応して形成される。スリット遮光パターン32cは、露光解像限界以下の遮光パターンとして構成され、ドレイン電極用遮光パターン32aとソース電極用遮光パターン32bとの間に配置される。スリット遮光パターン32cの短辺方向の幅は、レジスト材料の物性や、露光に用いる光の波長、レンズの開効率等の露光装置の光学系によって決まる露光解像限界以下の値に設定される。

#### 【0049】

第2導電膜25上にレジスト材料を塗布し、露光装置(図示せず)によって、フォトマスク31に所定波長の光を照射すると、照射された光の一部は、遮光パターン32で遮光される。これにより、レジスト材料には、光が照射されない未露光領域33と、光が照射される露光領域34とが形成される。ここで、ドレイン電極用遮光パターン32aとソース電極用遮光パターン32bの間には、スリット遮光パターン32cが形成されているものの、そのスリット遮光パターン32cの短辺方向の幅は露光解像限界以下であるために、照射された光が完全には透過されず、レジスト材料には、未露光領域33に比して光の照射量が多く、露光領域34に比して光の照射量が少ない半露光領域35が形成される。互いに対向するドレイン電極用遮光パターン32a及びソース電極用遮光パターン32bの縁部に対応する領域については、光の回り込みにより、両端での露光量が中央に比して多くなり、図9(a)に示すように、両端では、中央部に比して半露光領域35がX方向に広がる。

#### 【0050】

レジスト材料を露光した後に現像し、フォトレジストパターン29を形成する。露光領域34では、レジスト材料が除去され、第2導電膜25が表面に露出する。未露光領域33では、レジスト材料が除去されずに、所定の膜厚のフォトレジストパターン29が形成される。半露光領域35では、レジスト材料が、第2導電膜25が表面に露出しない程度に除去され、未露光領域33の所定膜厚に比して膜厚が薄いフォトレジストパターン29が形成される。言い換えると、フォトレジストパターン29は、未露光領域33と半露光領域35とで段差を有する断面形状に形成される。フォトレジストパターン29は、図9(a)に示すように、ドレイン電極用遮光パターン32aによる未露光領域33aに対応するドレイン電極用レジストパターン29aと、ソース電極用遮光パターン32bによる未露光領域33aに対応するソース電極用レジストパターン29bと、半露光領域35に対応するレジスト薄膜部29cと有する。

#### 【0051】

スリット遮光パターン32cは、図8(b)に示すように、長辺方向の長さが、互いに対向するドレイン電極用遮光パターン32a及びソース電極用遮光パターン32bの辺の長さに比して、長く設定されている。このスリット遮光パターン32cにより、互いに対向するドレイン電極用遮光パターン32a及びソース電極用遮光パターン32bの縁部のX方向の両端では、中央部に比して多くの光が回り込み、半露光領域35が、つまりは、レジスト薄膜部29cがY方向に広がって、互いに対向するドレイン電極用レジストパターン29a及びソース電極用レジストパターン29bの辺が、図9(a)に示すような湾曲した形状となる。

#### 【0052】

フォトレジストパターン29の平面形状は、半導体層23及オーミックコンタクト層24をエッティングする際に使用する第2フォトレジストパターン30(図2(b))と同様な形状に形成される。フォトレジストパターン29を用いて、半導体層23、オーミックコンタクト層24、及び、第2導電膜25をエッティングし、半導体層23、オーミックコンタクト層24、及び、第2導電膜25を形成する(図7(c))。フォトレジストパターン29を所望の膜厚となるように、アッシング除去し、レジスト薄膜部29cを除去する(図7(d))。

10

20

30

40

50

## 【0053】

上記アッシング除去には、R I E - D E 装置を使用することができ、或いは、U V アッシャーを使用することができる。R I E - D E 装置を使用する場合には、エッチング異方向性が優れているため、寸法制御性が向上でき、U V アッシャーを使用する場合には、工程の簡略化が可能である。アッシング除去により、図9(b)に示す平面形状を有するドレイン電極用レジストパターン29a及びソース電極用レジストパターン29bが残る。アッシング除去後のドレイン電極用レジストパターン29aとソース電極用レジストパターン29bの間の距離が、チャネル長を決定する。

## 【0054】

アッシング除去後に残ったドレイン電極用レジストパターン29a及びソース電極用レジストパターン29bを用いて、第2導電膜25をエッチングし、図5に示す平面形状を有するドレイン電極12a及びソース電極13aを形成する(図7(e))。その後、第1実施形態例におけるTFTの製造方法と同様に、ドレイン電極12及びソース電極13を用いて、オーミックコンタクト層24及び半導体層23の一部をチャネルエッチングし、パッシベーション膜26を積層し、コンタクトホール27を形成し、画素電極15を形成して、TFT10aが得られる。

10

## 【0055】

本実施形態例では、互いに対向する縁部が湾曲した平面形状に形成されるドレイン電極12a及びソース電極13aによって、チャネル領域14のチャネル幅方向の双方の縁部におけるチャネル長L4を、チャネル中央部におけるチャネル長L3に比して長く設定する。この場合にも、第1実施形態例と同様に、光リーキ電流がTFT10aのスイッチング特性に与える影響を低減でき、液晶表示装置の表示品質を向上させることができる。

20

## 【0056】

本実施形態例のTFT10aを、図6及び図7に示す本実施形態例の製造方法で形成するのに代えて、図2及び図3に示す第1実施形態例のTFT10と同様な製造方法を用いて形成することもできる。この場合には、図2(d)において、第3フォトレジストパターン28a及び28bを、それぞれ、図5に示すドレイン電極12a及びソース電極13aの形状に対応した平面形状でパターニングすればよい。しかし、第1実施形態例と同様な製造方法を用いてTFT10aを形成する場合には、第2フォトレジストパターン30をパターニングするためのマスクと、第3フォトレジストパターン28をパターニングするためのマスクとが必要になる。本実施形態例の製造方法を採用して、TFT10aを形成するときには、第1実施形態例と同様な製造方法を用いる場合に比べて、フォトレジストパターンをパターニングする際に使用するマスクを1枚削減して、製造コストを低減することができる。

30

## 【0057】

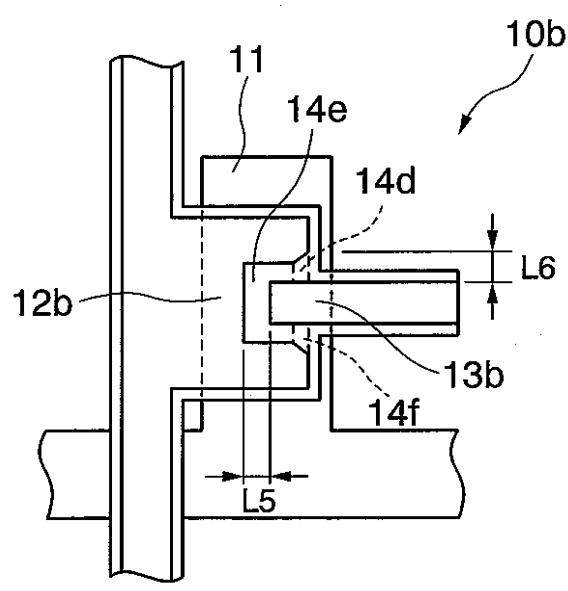

図10は、本発明の第3実施形態例のTFTを平面図として示している。本実施形態例のTFT10bは、ドレイン電極12b及びソース電極13bの形状が、第1実施形態例と相違する。ドレイン電極12bは、ソース電極13bを取り囲むように、平面形状がコの字状に形成される。ドレイン電極12bのチャネル領域14の両端側は、第1実施形態例におけるドレイン電極12と同様に、両端の角が切り落とされた形状と同様な形状となっている。チャネル領域14の画素電極側の縁部14d及び走査線側の縁部14fのチャネル長L6は、チャネル中央部14eのチャネル長L5に比して、長く設定される。

40

## 【0058】

本実施形態例のように、ドレイン電極12bとソース電極13bとがチャネル領域14を挟んで対称な平面形状に形成されない場合についても、チャネル領域の画素電極側の縁部14d及び走査線側の縁部14fのチャネル長L6を、チャネル中央部14eのチャネル長に比して長く設定することで、第1実施形態例と同様に、光リーキ電流がTFT10aのスイッチング特性に与える影響を低減でき、液晶表示装置の表示品質を向上させることができる。

## 【0059】

50

なお、上記実施形態例では、TFTが逆スタガ構造で形成される例について説明したが、スタガ構造には限定されない。また、逆スタガ構造に代えて、順スタガ構造を採用することもできる。この場合、チャネル領域に入射する光は、ゲート電極に代わり、半導体層の下層側に設けられた遮光膜で遮光される。上記実施形態例では、チャネル領域がチャネル幅方向に対称に形成され、チャネル領域の画素電極側の縁部のチャネル長と走査線側の縁部のチャネル長とが、同じ長さに設定される例について示したが、チャネル領域の画素電極側の縁部のチャネル長と走査線側の縁部のチャネル長とは、必ずしも同じ長さでなくともよい。例えば、光の回り込みが、チャネル領域の走査線側の縁部に比して多い、画素電極側の縁部のチャネル長を、走査線側の縁部のチャネル長に比して長く設定してもよい。また、ソース電極及びドレイン電極の平面形状は一例であり、上記実施形態例で採用した形状以外の形状を採用することもできる。

10

## 【0060】

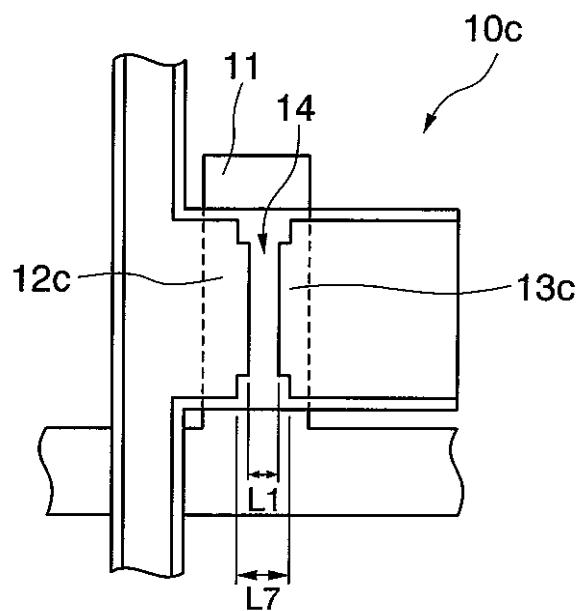

図11～図13は、それぞれ、チャネル縁部のチャネル長がチャネル中央部に比して長いTFTの別の例を示している。図1では、ドレイン電極及びソース電極の平面形状として、両端の角が切り落とされた形状と同様な形状を採用したが、これに代えて、図11に示すように、ドレイン電極及びソース電極の平面形状として、両端の角が階段状に切り落とされた形状と同様な形状を採用することもできる。この場合、チャネル縁部におけるチャネル長L7は、例えば、図1におけるチャネル縁部14a及び14cにおけるチャネル長の平均値と同じ値に設定することができる。

20

## 【0061】

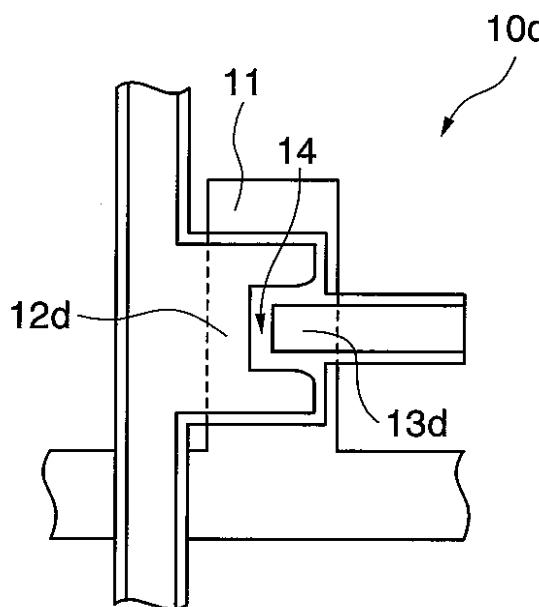

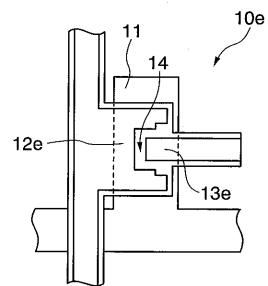

図10では、ドレイン電極の平面形状として、両端の角が切り落とされた形状を採用する例について示したが、これに代えて、図12に示すように、ドレイン電極の平面形状として、両端の角が湾曲した形状を採用することもできる。この場合、第2実施形態例で説明した、図6及び図7に示す工程を有するTFTの製造方法を採用することができる。または、図10に代えて、図13に示すように、図11の例と同様に、ドレイン電極の平面形状として、両端の角が階段状に切落された形状を採用することもできる。図11～図13に示す平面形状のドレイン電極及びソース電極の何れを採用する場合についても、チャネル縁部のチャネル長をチャネル中央部に比して長く設定することで、光リーキ電流がTFT10aのスイッチング特性に与える影響を低減することができる。

30

## 【0062】

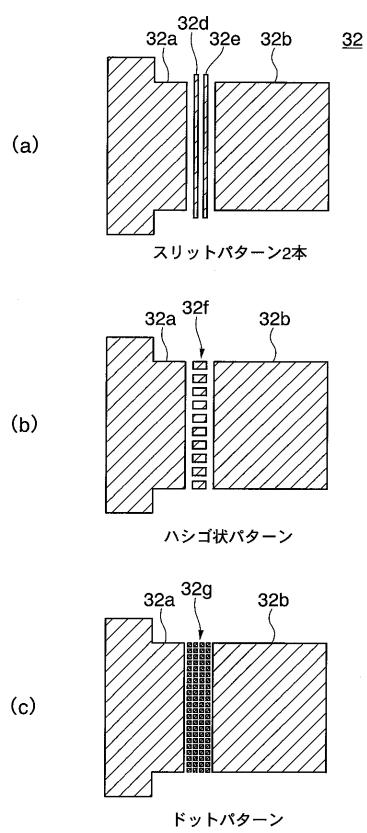

第2実施形態例では、図8(b)に示すような遮光パターン32によって、未露光領域33と半露光領域35とで段差を有するフォトトレジストパターン29を形成したが、ドレイン電極用遮光パターン32aと、ソース電極用遮光パターン32bとの間に配置される露光解像限界以下の遮光パターンは、図8(b)に示すスリット遮光パターン32cには限られない。図14(a)～(c)は、それぞれ、遮光パターン32の別の例を示している。図9に示すような形状のフォトトレジストパターン29は、図14(a)～(c)に示す遮光パターンを使用して形成することもできる。

## 【0063】

図14(a)に示す遮光パターン32は、ドレイン電極用遮光パターン32aと、ソース電極用遮光パターン32bとの間に、それぞれが露光解像限界以下の幅を有する2本のスリット遮光パターン32d、32eが配置されている。比較的、TFTのチャネル長Lが長いときや、露光解像度が高いときには、ドレイン電極用遮光パターン32aと、ソース電極用遮光パターン32bとの間に、図8(b)に示すような1本のスリット遮光パターン32cを配置するのに代えて、図14(a)に示すような2本のスリット遮光パターン32d、32eを配置して、フォトトレジストパターン29を形成するとよい。

40

## 【0064】

図14(b)に示す遮光パターン32は、ドレイン電極用遮光パターン32aと、ソース電極用遮光パターン32bとの間に、一列にならんだ複数の露光解像限界以下のパターンがハシゴ状パターン32fとして配置されている。また、同図(c)に示す遮光パターン32は、ドレイン電極用遮光パターン32aと、ソース電極用遮光パターン32bとの

50

間に、X方向及びY方向に配列された複数の露光解像限界以下のパターンがドットパターン32gとして配置されている。同図(b)に示すハシゴ状パターン32bを採用してフォトレジストパターン29を形成する場合には、露光時の露光スキャン方向、及び、現像時の現像方向によるレジスト形状のばらつきを抑制することができ、同図(c)に示すドットパターン32gを採用してフォトレジスト29を形成する場合には、ドレイン電極用遮光パターン32aと、ソース電極用遮光パターン32bとの間のレジスト薄膜部29c(図9)のレジスト膜厚の均一性を向上することができる。

#### 【0065】

以上、本発明をその好適な実施形態例に基づいて説明したが、本発明のTFTの製造方法及び液晶表示装置は、上記実施形態例にのみ限定されるものではなく、上記実施形態例の構成から種々の修正及び変更を施したものも、本発明の範囲に含まれる。

10

#### 【図面の簡単な説明】

#### 【0066】

【図1】本発明の第1実施形態例のTFTを示す平面図。

【図2】図2(a)～(d)は、それぞれ、TFT10の製造工程段階ごとに示す断面図。

【図3】図3(e)～(g)は、それぞれ、TFT10の製造工程段階ごとに示す断面図。

【図4】TFT10におけるゲート電圧とドレイン電流との関係を示すグラフ。

【図5】本発明の第2実施形態例のTFTを示す平面図。

20

【図6】図6(a)及び(b)は、それぞれ、TFT10aを製造工程段階ごとに示す断面図。

【図7】図7(c)～(e)は、それぞれ、TFT10aを製造工程段階ごとに示す断面図。

【図8】図8(a)は、図6(b)におけるフォトレジストパターン29の形成の様子を示す断面図、図8(b)は、同図(a)のフォトマスク31に形成される遮光パターンの形状を示す平面図。

【図9】図9(a)は、図8(b)に示す遮光パターンを介して露光して得られるフォトレジストパターン29を示す平面図、図9(b)は、同図(a)から半露光領域35に対応する領域を除去したフォトレジストパターン29を示す平面図。

30

【図10】本発明の第3実施形態例のTFTを示す平面図。

【図11】本発明のTFTの別の例を示す平面図。

【図12】本発明のTFTの別の例を示す平面図。

【図13】本発明のTFTの別の例を示す平面図。

【図14】(a)～(c)はそれぞれ、遮光パターン32の別の例を示す平面図。

【図15】a-Si TFTを用いた、一般的な液晶表示装置の液晶パネルを示す断面図。

【図16】TFT基板202の一部を示す平面図。

【図17】図16のA-A'断面に相当する、一般的なTFTの断面構造を示す断面図。

【図18】図16に示すTFT230の1つを拡大して示す平面図。

【図19】対向基板204の一部を示す平面図。

40

#### 【符号の説明】

#### 【0067】

10：薄膜トランジスタ(TFT)

11：ゲート電極

12：ドレイン電極

13：ソース電極

14：チャネル領域

15：画素電極

21：ガラス基板(絶縁基板)

22：ゲート酸化膜

50

- 2 3 : 半導体層

2 4 : オーミックコンタクト層

2 5 : 第 2 導電膜

2 6 : パッシベーション膜

2 7 : コンタクトホール

2 8、2 9、3 0 : フォトレジストパターン

3 1 : フォトマスク

3 2 : 遮光パターン

3 3 : 未露光領域

3 4 : 露光領域

3 5 : 半露光領域

10

【図 1】

【図 2】

【図3】

【図6】

10a

【図4】

Vg-Ig特性比較

【図5】

【図7】

10a

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【 図 1 4 】

【 図 15 】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(51)Int.Cl.

F I

|         |       |         |

|---------|-------|---------|

| H 0 1 L | 29/78 | 6 1 8 C |

| H 0 1 L | 29/78 | 6 1 9 B |

| H 0 1 L | 29/78 | 6 2 7 C |

合議体

審判長 河口 雅英

審判官 小川 将之

審判官 近藤 幸浩

(56)参考文献 特開平07-122754号公報( J P , A )

特開2003-068755号公報( J P , A )

特開平02-216870号公報( J P , A )

特開2001-324725号公報( J P , A )

特開2002-141512号公報( J P , A )

特開2002-261423号公報( J P , A )

(58)調査した分野(Int.Cl., DB名)

H01L29/786

H01L21/336

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP4593094B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2010-12-08 |

| 申请号            | JP2003297575                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 申请日     | 2003-08-21 |

| [标]申请(专利权)人(译) | NEC液晶技术株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | NEC LCD科技有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | NEC公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 橋本宜明<br>木村茂<br>鈴木聖二                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 橋本 宜明<br>木村 茂<br>鈴木 聖二                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G02F1/1368 G09F9/30 H01L29/417 H01L21/336 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| CPC分类号         | G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G02F1/1368 G09F9/30.338 H01L29/50.M H01L29/78.616.K H01L29/78.617.J H01L29/78.618.C<br>H01L29/78.619.B H01L29/78.627.C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 2H092/JA26 2H092/JA31 2H092/JA42 2H092/JA47 2H092/JB54 2H092/KA05 2H092/KA24 2H092/<br>/MA14 2H092/MA16 2H092/NA21 2H092/NA27 2H092/PA09 2H192/AA24 2H192/BC31 2H192/CB05<br>2H192/CB45 2H192/CB46 2H192/CC42 2H192/EA04 2H192/EA15 2H192/EA22 2H192/HA44 4M104<br>/AA09 4M104/BB01 4M104/CC01 4M104/DD62 4M104/FF11 4M104/FF13 4M104/GG09 4M104/GG10<br>4M104/GG14 5C094/AA25 5C094/AA43 5C094/AA48 5C094/BA03 5C094/BA43 5C094/CA19 5C094<br>/DA13 5C094/EA04 5C094/EB02 5C094/ED03 5C094/ED15 5F110/AA16 5F110/AA21 5F110/BB01<br>5F110/CC05 5F110/CC07 5F110/DD02 5F110/EE50 5F110/GG02 5F110/GG15 5F110/GG23 5F110<br>/GG28 5F110/GG29 5F110/HK09 5F110/HK16 5F110/HK21 5F110/HL07 5F110/NN44 5F110/QQ02 |         |            |

| 代理人(译)         | 木村充                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 助理审查员(译)       | 小川正幸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 其他公开文献         | JP2005072135A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

## 摘要(译)

LCD器件中的非晶硅TFT(薄膜晶体管)通过在源极的角落处形成倒角,与沟道的中心部分相比在TFT的沟道的两个边缘部分具有更大的沟道长度,以及漏电极。在两个边缘部分处的较大沟道长度减少了由入射到沟道上的转向光引起的泄漏电流。

【図1】