(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3639830号

(P3639830)

(45) 発行日 平成17年4月20日(2005.4.20)

(24) 登録日 平成17年1月21日(2005.1.21)

(51) Int.CI.<sup>7</sup>

F 1

|      |        |      |        |      |

|------|--------|------|--------|------|

| GO2F | 1/133  | GO2F | 1/133  | 525  |

| GO2F | 1/1343 | GO2F | 1/133  | 550  |

| GO2F | 1/1368 | GO2F | 1/1343 |      |

| GO9G | 3/20   | GO2F | 1/1368 |      |

| GO9G | 3/36   | GO9G | 3/20   | 611E |

請求項の数 13 (全 14 頁) 最終頁に続く

(21) 出願番号 特願2002-563069 (P2002-563069)

(86) (22) 出願日 平成13年12月25日 (2001.12.25)

(86) 國際出願番号 PCT/JP2001/011407

(87) 國際公開番号 WO2002/063383

(87) 國際公開日 平成14年8月15日 (2002.8.15)

審査請求日 平成15年7月9日 (2003.7.9)

(31) 優先権主張番号 特願2001-28602 (P2001-28602)

(32) 優先日 平成13年2月5日 (2001.2.5)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100086243

弁理士 坂口 博

(74) 代理人 100091568

弁理士 市位 嘉宏

(74) 代理人 100108501

弁理士 上野 剛史

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の基板と、第2の基板と、前記第1の基板及び前記第2の基板の間に封入された液晶材料とを有し、反転駆動により駆動される液晶表示装置において、

前記第1の基板上に、信号線と、走査線とを有し、前記信号線および前記走査線に接続されたスイッチング素子と、前記スイッチング素子に接続された画素電極と、前記液晶材料を駆動するための横方向電界を前記画素電極との間で生じる共通電極とを有する画素が複数個マトリクス状に設けられており、

前記第2の基板上に、ブラックマトリックス層、カラーフィルタ層、保護膜及び配向膜がこの順序で設けられており、

電源投入時に前記反転駆動により前記画素電極及び前記共通電極の間に生じるDC電圧成分の初期値を低下させるために、前記スイッチング素子に生じる寄生容量に起因する画素電極における表示電圧の減少を補償する突き抜け補償駆動を行うと共に、

前記画素電極と前記共通電極との間に、前記液晶材料、前記配向膜、前記保護膜、前記カラーフィルタ層を通過して前記ブラックマトリックス層に至り、再び、前記カラーフィルタ層、前記保護膜、前記配向膜及び前記液晶材料を通過して戻る電荷移動用の電界バスを備えることにより、前記DC電圧成分の値を前記初期値から更に減少させることを特徴とする液晶表示装置。

## 【請求項 2】

前記電源投入から画像が表示される時までに、フリッカを生じさせない許容値以下に前記

D C 電圧成分を減少させるために、

前記ブラックマトリックス層の抵抗率が、 $1 \times 10^0 \sim 1 \times 10^4$  • cm であり、

前記カラーフィルタ層の R の抵抗率が  $3 \times 10^1$  • cm であり、G の抵抗率が  $1 \times 10^1$  • cm であり、B の抵抗率が  $5 \times 10^1$  • cm であり、

前記保護膜の抵抗率が  $2.5 \times 10^1$  • cm 以下であり、

前記配向膜の抵抗率が、 $1.0 \times 10^1$  • cm である、

請求項 1 に記載の液晶表示装置。

**【請求項 3】**

前記ブラックマトリックス層の膜厚が  $1.5 \mu\text{m}$  であり、

前記カラーフィルタ層の膜厚が  $2.0 \mu\text{m}$  であり、

10

前記保護膜の膜厚が  $1.0 \mu\text{m}$  であり、

前記配向膜の膜厚が  $0.1 \mu\text{m}$  である、

請求項 2 に記載の液晶表示装置。

**【請求項 4】**

前記 D C 電圧成分の初期値は  $0.5 \text{ V}$  以下である、請求項 1 又は請求項 2 に記載の液晶表示装置。

**【請求項 5】**

前記 D C 電圧成分の許容値は  $0.15 \text{ V}$  である、請求項 2 に記載の液晶表示装置。

**【請求項 6】**

前記液晶表示装置は複数の走査線と複数の信号線とを有し、前記画素電極は前記複数の走査線の内の一つとの間で蓄積容量を形成する、請求項 1 に記載の液晶表示装置。

20

**【請求項 7】**

前記スイッチング素子は TFT 素子であり、

前記液晶表示装置が、前記複数の画素に表示信号を伝送する複数の信号線と、前記複数の

画素が有する TFT 素子のゲートにゲート信号を伝送する複数のゲート線とを有し、

蓄積容量が、前記画素電極と、前記複数のゲート線の内の一つであって前記画素電極に接続される TFT 素子に接続されたゲート線とは異なる他のゲート線との間に形成されている、

請求項 1 に記載の液晶表示装置。

**【請求項 8】**

30

前記突き抜け補償は、前記画素電極に接続される TFT 素子に接続された前記ゲート線のゲート信号の降下時に前記画素電極と前記ゲート線との間の寄生容量を介して生じる前記画素電極上の電位の変化を、前記他のゲート線のゲート信号の上昇変化分を前記蓄積容量を介して前記画素電極に印加することにより補償する、請求項 7 に記載の液晶表示装置。

**【請求項 9】**

第 1 の基板と、第 2 の基板と、前記第 1 の基板及び前記第 2 の基板の間に封入された液晶材料とを有し、反転駆動により駆動される液晶表示装置において、

前記第 1 の基板上に、複数の信号線と、複数のゲート線とを有し、前記複数の信号線の内の一つの信号線および前記複数のゲート線の内の一つのゲート線に接続された TFT 素子と、前記 TFT 素子に接続された画素電極と、前記液晶材料を駆動するための横方向電界を前記画素電極との間で生じる共通電極とを有する画素が複数個マトリクス状に設けられており、

40

前記第 2 の基板上に、ブラックマトリックス層、カラーフィルタ層、保護膜及び配向膜がこの順序で設けられており、

蓄積容量が、前記画素電極と前記複数のゲート線の内の他のゲート線との間に形成されており、

電源投入時に前記反転駆動により前記画素電極及び前記共通電極の間に生じる D C 電圧成分の初期値を低下させるために、前記一つのゲート線のゲート信号の降下時に、前記画素電極と前記一つのゲート線との間の寄生容量を介して生じる前記画素電極上の電位の変化を、前記他のゲート線のゲート信号の上昇変化分を前記蓄積容量を介して前記画素電極に

50

印加することにより補償する突き抜け補償駆動を行うと共に、

前記画素電極と前記共通電極との間に、前記液晶材料、前記配向膜、前記保護膜、前記カラーフィルタ層を通過して前記ブラックマトリックス層に至り、再び、前記カラーフィルタ層、前記保護膜、前記配向膜及び前記液晶材料を通過して戻る電荷移動用の電界パスを備えることにより、前記DC電圧成分の値を前記初期値から更に減少させ、

前記電源投入から画像が表示される時までに、フリッカを生じさせない許容値まで前記DC電圧成分を減少させるために、前記ブラックマトリックス層の抵抗率が、1E+00～1E+04・cmであり、前記保護膜の抵抗率が2.5E+15・cmであることを特徴とする液晶表示装置。

## 【請求項10】

10

前記電源投入から画像が表示される時までに、フリッカを生じさせない許容値以下に前記DC電圧成分を減少させるために、

前記カラーフィルタ層のRの抵抗率が3E+13・cmであり、Gの抵抗率が1E+13・cmであり、Bの抵抗率が5E+11・cmであり、

前記配向膜の抵抗率が、1.0E+15・cmである、

請求項9に記載の液晶表示装置。

## 【請求項11】

20

第1の基板と、第2の基板と、前記第1の基板及び前記第2の基板の間に封入された液晶材料とを有し、反転駆動により駆動され、THz駆動（Tは1秒間のフレームの数で自然数である）される液晶表示装置において、

前記第1の基板上に、信号線と、走査線とを有し、前記信号線および前記走査線に接続されたスイッチング素子と、前記スイッチング素子に接続された画素電極と、前記液晶材料を駆動するための横方向電界を前記画素電極との間で生じる共通電極とを有する画素が複数個マトリクス状に設けられており、

前記第2の基板上に、ブラックマトリックス層、カラーフィルタ層、保護膜及び配向膜がこの順序で設けられており、

電源投入時に前記反転駆動により前記画素電極及び前記共通電極の間に生じるDC電圧成分の初期値を低下させるために、前記スイッチング素子に生じる寄生容量に起因する画素電極における表示電圧の減少を補償する突き抜け補償駆動を行うと共に、

前記画素電極と前記共通電極との間に、前記液晶材料、前記配向膜、前記保護膜、前記カラーフィルタ層を通過して前記ブラックマトリックス層に至り、再び、前記カラーフィルタ層、前記保護膜、前記配向膜及び前記液晶材料を通過して戻る電荷移動用の電界パスを備えることにより、前記DC電圧成分の値を前記初期値から更に減少させ、

前記複数の画素は、フレーム毎に異なる電圧極性で駆動され、

前記複数の画素は、一つのフレームにおいて、第1の電圧極性で駆動される第1のグループの画素と、第2の電圧極性で駆動される第2のグループの画素とを有し、前記第1のグループの画素が最も輝度の小さい電圧値で駆動され、前記第2のグループの画素が所定の中間電圧値で駆動された場合、前記DC電圧成分が前記所定の許容値以下にあることにより、前記液晶表示からの透過光波形のT/2Hz成分の振幅を、THz成分の振幅の10倍以下とする、液晶表示装置。

## 【請求項12】

40

前記電源投入から画像が表示される時までに、フリッカを生じさせない許容値以下に前記DC電圧成分を減少させるために、

前記ブラックマトリックス層の抵抗率が、1E+00～1E+04・cmであり、

前記カラーフィルタ層のRの抵抗率が3E+13・cmであり、Gの抵抗率が1E+13・cmであり、Bの抵抗率が5E+11・cmであり、

前記保護膜の抵抗率が2.5E+15・cm以下であり、

前記配向膜の抵抗率が、1.0E+15・cmである、

請求項11に記載の液晶表示装置。

## 【請求項13】

10

20

30

40

50

前記スイッチング素子は TFT 素子であり、

前記液晶表示装置が、前記複数の画素に表示信号を伝送する複数の信号線と、前記複数の画素が有する TFT 素子のゲートにゲート信号を伝送する複数のゲート線とを有し、蓄積容量が、前記画素電極と、前記複数のゲート線の内の一つであって前記画素電極に接続される TFT 素子に接続されたゲート線とは異なる他のゲート線との間に形成されており、

前記突き抜け補償は、前記画素電極に接続される前記 TFT 素子に接続された前記ゲート線のゲート信号の降下時に前記画素電極と前記ゲート線との間の寄生容量を介して生じる前記画素電極上の電位の変化を、前記他のゲート線のゲート信号の上昇変化分を前記蓄積容量を介して前記画素電極に印加することにより補償を行う、

請求項 1 1 又は請求項 1 2 に記載の液晶表示装置。

#### 【発明の詳細な説明】

##### 技術分野

本発明は液晶表示装置に関するものであり、特に一つの基板上に画素電極と共に通電極とを有する IPS 型 (In Plane Switching) 液晶表示装置に関するものである。

##### 背景技術

パーソナルコンピュータや、その他各種モニター用の表示装置として、液晶表示装置の普及は目覚ましいものがある。この種の液晶表示装置は、一般に、液晶パネルの背面に、照明用の面状光源であるバックライトを配設し、所定の広がりを有する液晶面を全体として均一な明るさに照射することで、液晶パネルの液晶面に形成された画像を可視像化するよう構成されている。この液晶パネルは、2枚のガラス基板の間に充填された液晶に駆動電圧を印加することによって、液晶を駆動する構成となっている。液晶パネルは、このようにして液晶を駆動して液晶（分子）の向きを変えることにより、透過光の偏光を制御し、所望の画像を表示するのである。

ところで、従来、このような液晶パネルは、2枚のガラス基板の一方側と他方側にそれぞれ液晶駆動用の電極を設け、2枚のガラス基板を結ぶ方向、言い換えればガラス基板の基板面に略直交する方向の電界を生じさせ、これによって液晶を駆動する TN (twisted nematic) 方式が広く知られている。

しかしながら、このような方式の液晶パネルにおいては視野角が狭いため、これを改善する技術として、IPS (In Plane Switching: 横電界) 方式が知られている。これは、2枚のガラス基板の一方のみに配置した電極に駆動電圧を印加し、基板面に沿った水平方向（横方向）の電界を生じさせて液晶を駆動するものである。

液晶に DC 電圧が連続的に印加されづけると、液晶が劣化する。従って、TN 方式においても、IPS 方式においても、液晶に印加する電圧は、共通電位を基準として対称になるように設計される。

しかし、液晶表示パネルの製造公差のために、各製品毎に、同じ表示信号に対する画素電極と共に通電極との間の液晶に印加される電圧値が変化してしまう。このため、共通電位を基準とする液晶印加電圧の各極性の絶対値が非対称となる。これにより、液晶に印加される電圧が設計値から一方（共通電位を中心として + 側、もしくは - 側）にずれるので、画面がちらつくフリッカを発生させる。

以下に、具体例によってこのフリッカの発生を説明する。尚、これは、フリッカ発生の概念を説明するもので、必ずしも実際の製品に沿う正確なものではない。例えば、共通電位が 7.5 V 一定と設計されている場合に、12.5 V の電位を画素電極に設定した場合と、2.5 V の電位を画素電極に設定した場合では、同じ明るさで表示されるはずである。しかし、製造公差のために、実際に液晶に印加される電圧は、画素電極に 12.7 V と 2.7 V とを与えた場合の電圧となってしまう。これにより、+ 側に 0.2 V の直流成分が生ずる。12.7 V の方が、2.7 V よりも明るいので、フリッカが発生する。この電圧のズレは、主に、蓄積容量や寄生容量が製造公差によって設計値からずれることに起因する。

従来は、フリッカ調整機能を有する回路を制御回路基板上に設けることにより、この問題

10

20

30

40

50

を解決していた。液晶印加電圧の各極性の絶対値の非対称性を解消することにより、フリッカの発生を防ぐことができる。従来は、画素に与えられる電圧値を外部から変化させることによって、液晶印加電圧の各極性の絶対値の非対称性を解消していた。このように画素に与えられる電圧値を外部から変化させる方法として、従来、2つのものが知られている。

一つは、共通電位の値を外部から手動によって調整することにより、各極性の絶対値が共通電位に対して対称になるようにしていた。上記の例でいえば、共通電位を7.7Vにすることによって、各極性の絶対値を対称にすることができる。もう一つは、TFTのゲート電圧値を外部から手動によって変更することにより、フリッカ調整を行っていた。

しかし、上記のフリッカ調整回路の使用には、いくつかの問題があった。

10

第1に、製造公差による電圧値のずれは、製品毎に異なると同時に、一つの製品の面内においても生じている。例えば、画面の左側の画素と右側の画素との電圧値のずれは異なっている。したがって、外部から全ての画素に共通の共通電位やゲート電位を操作しても、この面内のはらつきを解消することはできなかった。

第2に、このようなフリッカ調整回路は部品点数の増大につながるので、液晶表示ディスプレイのコストを増加させる原因になっていた。

第3に、フリッカ調整の工程においては、人が外部から手動によって製品毎に調整を行っているので、この工程が製造スピードを悪化させる要因の一つとなっていた。

本発明はこのような技術的課題に基づいてなされたものであり、液晶表示装置製造後のフリッカ調整を不要とし得る、液晶表示装置を得ることを目的とする。

20

#### 発明の開示

本発明の発明者らは、上記課題について考察及び研究を行った結果、IPS型の液晶表示装置においては、フリッカ調整を不要とすることを見出しました。

つまり、共通電位を基準とする液晶印加電圧の各極性の絶対値が非対称となった場合、画素電極と共通電極との間には、一定の電圧値であるDC成分が存在している。このDC成分は、液晶材料に印加される定常的な電界とみなすことができる。IPS型液晶パネルにおいて、画素電極と共通電極との間は、容量と抵抗が並列に接続された回路としてモデル化することができる。従って、液晶内の方の電極側（例えば画素電極側）に+の電荷が存在し、もう一方の電極側（例えば共通電極側）に-の電荷が存在することにより、この電界が生じているとみなすことができる。

30

このDC成分が許容値以下であれば、フリッカ欠陥は生じない。従って、発明者らは、DC電圧成分が自動的に許容値以下に減少すれば、フリッカ調整を不要とすることを見出しました。

さらに、液晶表示装置においては、電源が投入されてから表示画面に画像が表示されるまでに、一定の時間がかかる。これは主に、バックライトの光源（例えば冷陰極管）が点灯するまでの時間に相当する。上記のDC成分が、この表示時間までの間に許容値以下に減少していれば、上記のフリッカ調整を不要とすることを見出しました。

これを可能とするには、2つの要素が満たされていることが必要である。一つは、電源投入時の初期DC成分が小さいことである。もう一つは、液晶材料に対するDC成分を生む電荷が、液晶パネル内を速く移動することである。

40

電荷の移動については、液晶材料内の移動のみならず、対向基板内の移動が極めて重要であることを見出した。これは、IPS型液晶表示装置においては、液晶材料の抵抗が横方向においてきわめて大きいことに起因すると考えられる。つまり、液晶材料内ののみを通過する電界においては、液晶材料の横方向抵抗が極めて大きいために、電荷が速く移動することができない。一方、縦方向の抵抗は、横方向に比較して十分小さい。一方の電極がられて、縦方向に液晶材料を通過する電界は、対向基板内を通過し、再び、液晶材料に戻って縦方向に通過し、もう一方の電極に入っていく。DC成分を減少させるためには、抵抗値の小さい電界パスが存在することが重要であると考えられる。この電界のパスにおいて、電荷が速く移動することができれば、所定時間内に許容値以下のDC成分とすることが可能となるからである。

50

しかし、上記のように、電荷の移動速度を確保するのみでは十分ではない。なぜなら、初期DC成分が大きい場合には、所定時間内に必要なDC成分値とすることができないからである。従って、初期DC成分を小さくし、さらに、高速な電荷移動が可能な液晶表示装置を構成することによって、初めてフリッカ調整を不要とすることができることを発明者は見出した。

尚、例えば、特開2000-66222、特開平10-133205、特開平7-159786などには、CF基板もしくはアレイ基板を構成する要素の物性値が記載されているが、いずれの先行技術にも、本発明の解決した課題、及びその解決手段について一切の開示がなされていない。

上記の知見に基づき、本発明の第1の態様の液晶表示装置は、第1の基板と、第2の基板と、前記第1及び第2の基板の間に封入された液晶材料と、を有する。液晶表示装置はマトリックス状に配置された複数の画素を有している。複数の画素のそれぞれは、前記第1の基板上に、スイッチング素子と、前記スイッチング素子に接続された画素電極と、前記画素電極との間で前記液晶材料に印加される電界を形成する共通電極と、を有している。液晶表示装置の電源投入直後に、画素電極と前記共通電極とは、初期DC電圧成分をその間に有し、液晶表示装置の電源投入後の所定時間において、DC電圧成分は前記初期値から許容値以下に自動的になっている。DC電圧成分が電源投入後の所定時間において許容値以下に自動的になっていることにより、画素内の電極に印加する電位を変更することによりフリッカ調整をすることが不要となる。

ここで、液晶表示装置とは、本発明の目的が達成される範囲において、2枚の対向基板の間に液晶を封入した液晶パネル、液晶パネルにドライバ回路やバックライト・ユニットを装着した液晶モジュール、最終製品としての液晶ディスプレイ等を含むものである。

第2の発明に係る液晶表示装置は、第1の液晶表示装置において、初期DC電圧成分は0.5V以下である。

第3の発明に係る液晶表示装置は、第1の液晶表示装置において、DC電圧成分許容値は0.15Vである。

第4の発明に係る液晶表示装置は、第1の液晶表示装置において、外部から画素内の電極に印加する電位を変更することによりフリッカ調整を行う回路を有していない。

第5の発明に係る液晶表示装置は、第1の液晶表示装置において、複数の走査線と複数の信号線とを有し、前記画素電極は走査線との間で蓄積容量を形成する。

第6の発明に係る液晶表示装置は、第1の基板と、第2の基板と、前記第1及び第2の基板の間に封入された液晶材料と、を有する。さらに、マトリックス状に配置された複数の画素を有している。複数の画素のそれぞれは、第1の基板上に、スイッチング素子と、前記スイッチング素子に接続された画素電極と、前記画素電極との間で前記液晶材料に印加される電界を形成する共通電極と、を有する。液晶表示装置の電源投入直後に、画素電極と前記共通電極とは、初期DC電圧成分をその間に有し、液晶表示装置の電源投入から5秒後において、DC電圧成分は前記初期値から0.15V以下に自動的になっている。

第7の発明に係る液晶表示装置は、第1、第5又は第6に記載の液晶表示装置において、スイッチング素子はTFTであり、TFTに与えられるゲート信号が落ちるとき蓄積容量を介して逆特性の補償信号を印加する補償駆動される。

第8の発明に係る液晶表示装置は、第7の発明に係る液晶表示装置において、第2の基板は、第1の樹脂層と、前記第1の樹脂層の内側に形成された第2の樹脂層とを有し、第1の樹脂層は、 $2.5E+15 [ \cdot cm ]$ 以下の抵抗率を有し、第2の樹脂層は、 $1E+00 \sim 1E+04 [ \cdot cm ]$ の抵抗率を有する。

第9の発明に係る液晶表示装置は、第7の発明に係る液晶表示装置において、第1の樹脂層は保護膜であり、第2の樹脂層はブラックマトリックス層である。

第10の発明に係る液晶表示装置は、第1の基板と、第2の基板と、前記第1及び第2の基板の間に封入された液晶材料と、を有し、THz駆動(Tは自然数)される。この液晶表示装置は、マトリックス状に配置された複数の画素を有する。複数の画素のそれぞれは、第1の基板上に、スイッチング素子と、前記スイッチング素子に接続された画素電極と

10

20

30

40

50

、前記画素電極との間で前記液晶材料に印加される電界を形成する共通電極と、を有する。複数の画素は、フレーム毎に異なる電圧極性で駆動され、一つのフレームにおいて、第1の電圧極性で駆動される第1のグループの画素と、第2の電圧極性で駆動される第2のグループの画素とを有している。液晶表示装置の電源投入直後に、画素電極と前記共通電極とは、初期DC電圧成分をその間に有し、液晶表示装置の電源投入後の所定時間において、DC電圧成分は許容値以下に自動的になっている。第1のグループの画素は最も輝度の小さい電圧値で駆動され、第2のグループの画素は所定の中間電圧値で駆動された場合、DC電圧成分が許容値以下にあることにより、液晶表示からの透過光波形のT/2Hz成分の振幅は、THz成分の振幅の10倍以下である。

第11の発明に係る液晶表示装置は、第10の発明に係る液晶表示装置において、スイッチング素子はTFT (Thin Film Transistor) であり、TFTに与えられるゲート信号が落ちるとき蓄積容量を介して逆特性の補償信号を印加する補償駆動される。10

第12の発明に係る液晶表示装置は、第10又は11の発明に係る液晶表示装置において、第2の基板は、第1の樹脂層と、前記第1の樹脂層の内側に形成された第2の樹脂層とを有している。前記第1の樹脂層は、 $2.5E+15 [ \cdot cm ]$ 以下の抵抗率を有している。前記第2の樹脂層は、 $1E+00 \sim 1E+04 [ \cdot cm ]$ の抵抗率を有する。

第13の発明に係る液晶表示装置は、第1又は10の発明に係る液晶表示装置において、電源投入後の所定時間は、電源を投入した後、液晶表示装置の表示画面に画像が映し出されるまでの時間である。

第14の発明に係る液晶表示装置は、第1又は10の発明に係る液晶表示装置において、前記電源投入後の所定時間は、前記電源を投入した5秒後である。20

第15の発明に係る液晶表示装置は、第1の基板と、第2の基板と、前記第1及び第2の基板の間に封入された液晶材料と、を有し、マトリックス状に配置された複数の画素を有する。複数の画素のそれぞれは、第1の基板上に、TFT素子と、前記スイッチング素子に接続された画素電極と、前記画素電極との間で前記液晶材料に印加する電界を形成する共通電極と、を有している。複数の画素のそれぞれは、第2の基板上に、 $2.5E+15 [ \cdot cm ]$ 以下の抵抗率を有する樹脂保護層と、前記保護層の内側に $1E+00 \sim 1E+04 [ \cdot cm ]$ の抵抗率を有する樹脂ブラックマトリックス層とを有している。液晶表示装置は、TFTに与えられるゲート信号が落ちるとき、蓄積容量を介して逆特性の補償信号を印加する補償駆動される。30

第16の発明に係る液晶表示装置は、第15発明に係る液晶表示装置において、複数の画素に表示信号を伝送する複数の信号線と、TFT素子のゲートにゲート信号を伝送する複数のゲート線とを有している。蓄積容量は、画素電極と前記複数のゲート線内の一つとの間に形成されている。

#### 【図面の簡単な説明】

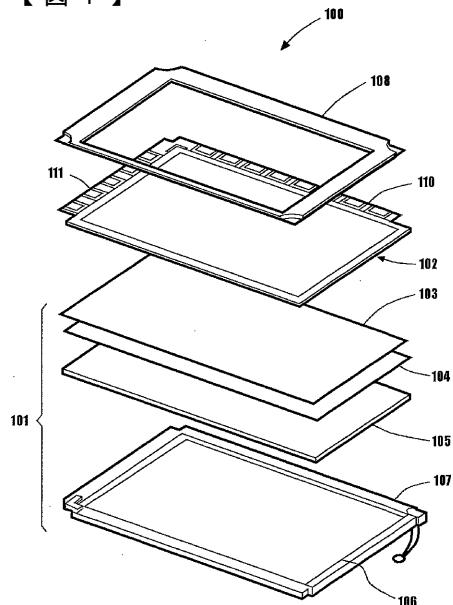

図1は、本実施形態における、液晶表示モジュールの構成を示す概略図である。

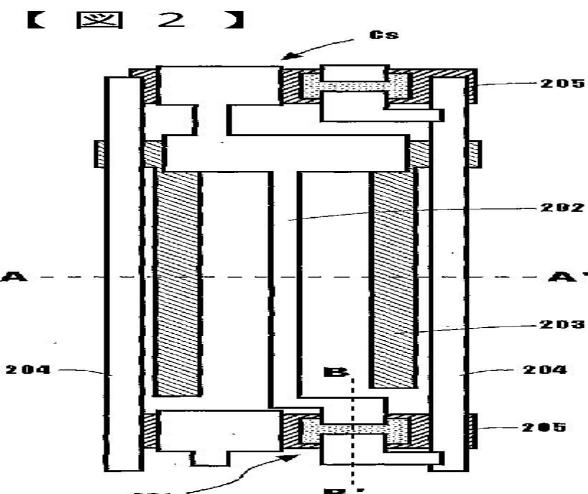

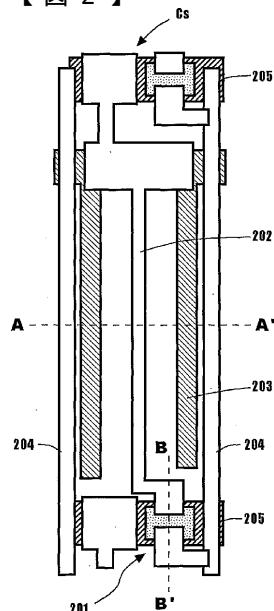

図2は、本実施形態における、画素の構成を示す概略図である。

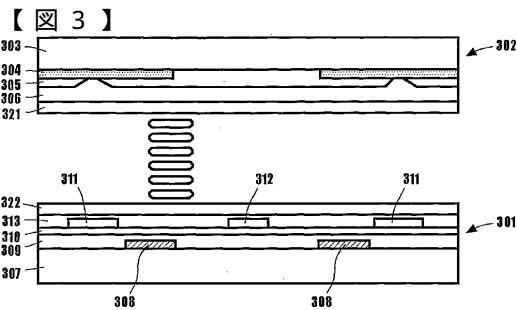

図3は、本実施形態における、画素の概略構成を示す断面図である。

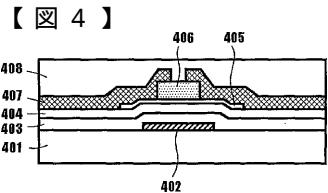

図4は、本実施形態における、画素のTFTの概略構成を示す断面図である。

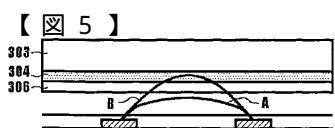

図5は、本実施形態における、DC成分による電界バスを説明する図である。40

図6は、本実施形態における、つきぬけ補償駆動を説明する、タイミング図である。

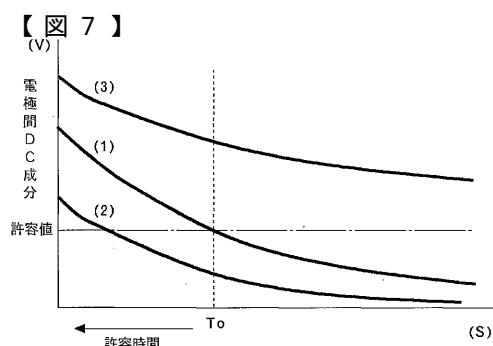

図7は、本発明に係る液晶表示装置と従来の液晶表示装置のDC成分の時間変化を説明する、図である。

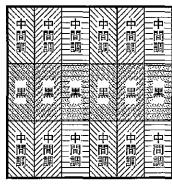

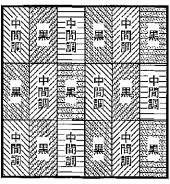

図8は、本実施形態における、フリッカ検査パターンを説明する図である。

#### 発明を実施するための最良の態様

以下にこの発明の一実施の形態における液晶表示装置を、図面に基づいて詳細に説明する。本実施形態は、IPS (In Plane Switching) 駆動方式の液晶表示装置である。本実施形態において、フリッカ調整を不要とした液晶表示装置について説明される。フリッカ調整機能を不要とするためには、初期DC成分を十分に小さくし、さらに、電荷が液晶パネル内を高速に移動できる構成でなければならない。本実施形態は、初期DC成分を小さく50

するための一つの技術として、突き抜け補償駆動方式を採用している。突き抜け補償駆動方式については、後に説明される。又、対向基板内の電荷の移動を容易にするために、対向基板の構成が好適化されている。

図1は、本実施の形態における液晶モジュールの全体構成を説明するための斜視図である。図1は、サイドライト型のバックライト・ユニットを有する液晶モジュール100の概略を示す、構成図である。図に於いて、101はバックライト・ユニット、102は駆動回路が取り付けられた液晶パネル（液晶セル）、103は光を拡散させ、液晶表示パネル面での明るさを均一にする拡散シートである。104は光を集光することにより、表示正面の輝度を向上させるプリズムシート、105は光源からの光を導き拡散させる導光板、106は導光板やプリズムシート等のバックライト・ユニット101の部品を収納するフレームである。10

液晶パネル102は、マトリックス状に配置された複数の画素から構成される表示領域とその外周領域である額縁領域とを有している。又、液晶パネル102は、アレイ回路が形成されたアレイ基板とその対向基板とを有し、その2つの基板の間に液晶が封入されている。107は光源としての冷陰極管、108は液晶セル102とバックライト・ユニット11を外側から保持、保護するベゼルである。拡散シート103、プリズムシート104、導光板105、フレーム106、そして冷陰極管107によって、バックライト・ユニット101を構成する。冷陰極管107はフレーム106の内側に配置されており、直接画面には記載されていない。尚、バックライト・ユニットとしては、他に、直下型のバックライト・ユニットが知られている。これは、液晶パネルの表示面の直下に1本もしくは複数本の光源を配置されている。20

表示領域内の各画素は、RGBいずれかの色表示を行う。もちろん、白黒ディスプレイにおいては、白と黒のいずれかの表示を行う。アレイ基板上の表示領域内には、複数の信号線とゲート線がマトリックス状に配設されている。信号線とゲート線とはお互いにほぼ直角に重なるように配設されている。各画素は、ドライバICから入力される表示信号電圧に基づき液晶に電界を印加する。このドライバICは、通常、TABによってアレイ基板に接続されるが、アレイ基板のガラス基板上に直接に設けられることもある。

通常、信号線用の複数のソース・ドライバIC110が、TFTアレイ基板のX軸側に設けられ、ゲート電圧を制御するゲート線用の複数のゲート・ドライバIC111が、Y軸側に設けられる。ソース・ドライバIC110から入力される電圧が、TFTのソース／ドレインを介して画素電極に送られ、画素電極と共に共通電極とが液晶に電界を印加する。この電圧を変えることにより液晶への印加電圧を変化させることができ、液晶の光の透過率を制御する。共通電極と共に共通電位を与える回路は、制御回路基板（不図示）上に構成される。30

図2は、本実施形態における画素構造を示す図である。図2において、201はスイッチング素子としてのアモルファス・シリコンTFT（Thin Film Transistor）、202はTFTのソース／ドレインに接続された画素電極、203は画素電極との間で液晶に電界を印加する共通電極、204はTFTに表示信号を伝送する信号線、205はTFTのゲートにゲート電圧を伝送するゲート線である。

ゲート線、信号線、そして共通電極は、典型的には、AlNdやMoWで形成されている。画素電極は、通常、AlやITO（Indium Tin Oxide）などで形成されている。40

画素電極の一部は、一つ上流の走査線と、絶縁体を介して重なり、蓄積容量を形成している。これは、いわゆる、Cs on gateと呼ばれる構成である。又、画素電極の別の一部は共通電極とも絶縁体層を介して重なっており、これは蓄積容量の一部を形成している。

画素は、X方向に伸びる2本のゲート線205と、Y方向に延びる2本の信号線204によって囲まれている。信号線204の内側には、くし歯形状を有する共通電極203が配置されている。2本の共通電極203の間に画素電極202が形成されている。画素電極202とその両側の共通電極203との間に於いて、基板面にほぼ平行な電界が形成される。

尚、画素電極と共に共通電極とは、上記の構成に限定されるものではない。例えば、画素電極50

をくし歯状に形成し、共通電極よかみ合うように配置することも可能である。あるいは、画素電極をくの字状の形に形成するなど、電極形状の様様な変更が可能である。又、共通電極を画素電極よりも上層に配置し、画素の開口部以外の全ての領域を覆うように配置することも可能である。画素電極と信号線との相互作用を防止するために、画素電極と信号線との間に共通電極が配置されることが好ましい。

図3は、図2におけるA-A'の断面図である。図3において、301は第1の基板であるアレイ基板、302は第2の基板であるカラーフィルタ基板である。

カラーフィルタ基板302は、ガラス基板303と、ガラス基板303の上に形成されたブラックマトリクス層(以下BM層)304と、BM層304の上に形成されたRGBのカラーフィルタ層(以下CF層)305と、CF層の上に形成された保護膜層306と、保護膜層の上に形成された配向膜321とを有している。BM層304はアクリル系の樹脂やエポキシ系の樹脂に黒色顔料を分散させたものが典型的に使用され、この顔料はカーボン材料である。BM層304は保護膜層306と一部で接触している。

CF層305は、アクリル系の樹脂やエポキシ系の樹脂に、赤、青、緑のいずれかの顔料を分散させたものが一般的である。保護膜306はアクリル系の樹脂やエポキシ系の樹脂を堆積したものが多く使われ、その内側の層を保護する機能と、その表面を平坦化する働きも有する。配向膜は通常、ポリイミド材料により構成され、液晶材料の無電界時の配向を制御する。本実施形態においては、対向基板としてCF基板を説明しているが、白黒の表示装置においては、対向基板からCF層が除かれる。

対向基板であるCF基板内の速い電荷の移動を実現するためには、保護膜306とBM層304の抵抗値が重要な要素の一つとなる。保護膜の抵抗率が十分に小さいと同時に、BM層の抵抗率も十分小さい必要がある。これは、液晶材料から配向膜を介して、保護膜、BM層、さらに保護膜と続く電界のパス(図5のB線)を考えた場合に、保護膜とBM層の両方の抵抗が十分に小さくななければ、電荷の移動速度を確保することができないからである。尚、BM層はカラー液晶ディスプレイにも白黒液晶ディスプレイにも使用されるので、汎用性が高い。又、CF層と異なり、顔料によって抵抗値を制御し安いという性格を有している。ただし、BM層の抵抗値が小さすぎると好ましくないので、BM層の抵抗値は所定に範囲内にあることが好ましい。クロムなどの金属を使用した極めて抵抗値の小さいBM層は好ましくない。

従って、BM層304の抵抗率は、好ましくは、 $1E+00 \sim 1E+04 [ \cdot \text{cm} ]$ である。BM層の膜厚は、例えば、約 $1.5 \mu\text{m}$ である。

CF層305の抵抗率は、例えば、RGBに対してそれぞれ、およそ、 $3E+13$ 、 $1E+13$ 、そして、 $5E+11 [ \cdot \text{cm} ]$ である。又、CF層の膜厚はおよそ $2.0 \mu\text{m}$ である。

保護膜層306の抵抗率は、好ましくは約 $2.5E+15 [ \cdot \text{cm} ]$ 以下であり、さらに好ましくは約 $8.5E+14 [ \cdot \text{cm} ]$ 以下である。保護膜層の膜厚は、例えば、およそ $1.0 \mu\text{m}$ である。

配向膜の抵抗率は、およそ $1.0E+15 [ \cdot \text{cm} ]$ 、膜厚は、およそ $0.1 \mu\text{m}$ とすることができる。

アレイ基板301は、下層から順に、ガラス基板307、共通電極308、酸化シリコン絶縁体層309、窒化シリコン絶縁体層310、信号線311及び画素電極312、窒化シリコン・パッシベーション層313、そして、配向膜322を有している。以下に各要素の寸法を例示する。例えば、共通電極308の厚さは、A1の場合はおよそ $0.3 \mu\text{m}$ であり、ITOの場合はおよそ $0.05 \mu\text{m}$ である。酸化シリコン層309の厚さは約 $0.4 \mu\text{m}$ 、窒化シリコン層310の厚さは約 $0.05 \mu\text{m}$ である。信号線311及び画素電極312の厚さは約 $0.3 \mu\text{m}$ であり、パッシベーション層313はおよそ $0.2 \mu\text{m}$ の厚さである。

アレイ基板とCF基板との間には液晶材料が封入されており、スペーサによって、2つの基板の間隔は、およそ $5 \mu\text{m}$ に維持される。

図4は、図1におけるB-B'の断面図であり、TFT201の構造を説明する図である

10

20

30

40

50

。図において、401はガラス基板、402はゲート線、403は酸化シリコン絶縁体層、404は窒化シリコン絶縁体層、405はアモルファス・シリコン層、406は窒化シリコン層、407はソース／ドレイン電極、408は窒化シリコンパッシベーション層である。この上に、配向膜が形成される。尚、TFTはトップゲート構造とすることもボトムゲート構造とすることも可能である。又、スイッチング素子としては、MIM(Metal Insulator Metal)などを利用することも可能である。

表示動作について説明する。走査線としてのゲート線は、ゲート・ドライバIC111から送られたゲート信号をTFTのゲートに伝送する。ゲート信号がONになるとTFTがON状態となり、データ・ドライバIC110から送信された表示信号が信号線とTFTのソース／ドレインを介して、画素電極202に送られる。共通電極203には共通電位が与えられており、画素電極と共通電極との間で電界が形成される。電界の強さを変化させることによって、液晶分子の向きを制御する。液晶分子は、基板にほぼ平行な面内においてその長軸の向きを変化させる。液晶材料内を通過する光の偏光は、液晶分子の複屈折性によって変化し、液晶分子の向きによって対向基板上の偏光板を通過する光の量が変化する。共通電位は、例えば、7.5Vに設計される。画素電極に与えられる電位は、例えば、最大13.5V、最小1.5Vに設計される。

液晶は交流で駆動される。つまり、フレーム毎に画素内の液晶に与える電圧の極性を+と-に反転させる。ここで電圧の極性とは、共通電位を基準として決定される。液晶の駆動方式としてはいくつかのものが知られており、ライン反転駆動やドット反転駆動が使用される。

ライン反転駆動とは、ゲート線ごとに表示電極に与える信号電圧の極性を反転させる駆動方法である。例えば、第1フレームの奇数行の画素行には+極性の電圧を与え、偶数行には、-極性の電圧を与える。第2フレームにおいては、奇数行の画素行には-極性の電圧を与え、偶数行には、+極性の電圧を与える。

ドット反転駆動とは、同一行(ゲート線)内において、画素毎に印加電圧の極性を反転させる駆動方式である。第1フレーム、奇数行において、奇数列(奇数番目の信号線)の画素には+極性の電圧を与え、偶数列の画素には-極性の電圧を与える。第1フレーム、偶数行において、奇数列の画素には-極性の電圧を与え、偶数列の画素には+極性の電圧を与える。第2フレームにおいては、各画素の電圧極性を反転させる。尚、共通電位を一定値に保持せずに、フレームの進行に従って変化させることも可能である。

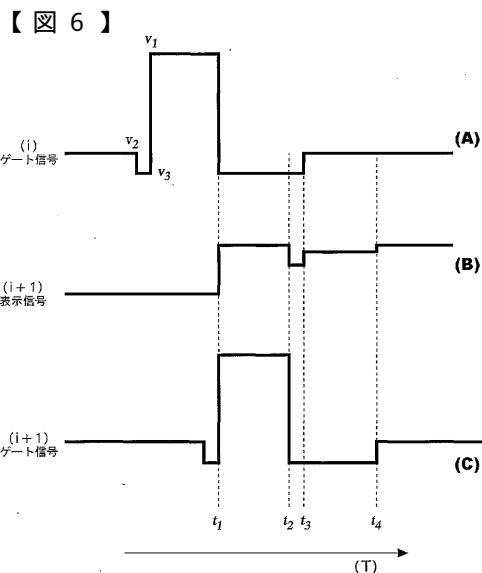

次に、つきぬけ補償駆動について説明する。図6は、ゲート信号と、液晶材料に印加される電圧の大きさとの関係を示す、タイミングチャートである。本実施形態においては、つきぬけ補償駆動方式が採用されている。液晶表示装置の画素においては、いくつかの寄生容量が存在する。その中で画素の駆動に大きな影響を及ぼすものに、ゲート線と画素電極(ゲートとソース。ここでは、画素電極側をソースと呼ぶ。)との間の寄生容量がある。これは、通常C<sub>gs</sub>(もしくはC<sub>gd</sub>)と呼ばれる。ゲート電位の変化は、このC<sub>gs</sub>を介して表示電圧の変化を生じさせる。突き抜け補償駆動は、TFTのゲート信号がLの論理レベルに落ちるときに、逆極性のパルスを蓄積容量を介して液晶材料に与える技術である。寄生容量C<sub>gs</sub>のため、ゲート電圧が落ちると、液晶材料に印加されている電圧値が減少する。画素電極と蓄積容量を形成する導体部に逆特性の信号を与えることにより、上記の減少分を補うことができる。

以下に、図6に従って、一つの画素の駆動動作を説明する。Aは、i番目のゲート線に与えられるゲート信号である。Bはi+1番目の画素行における1つの画素の液晶材料に印加される電圧の大きさである。Cはi+1番目のゲート線に与えられるゲート信号である。i+1番目の画素行における画素のTFTはi+1番目のゲート線によって制御される。X軸が時間の経過を表し、Y軸が信号の値を示している。ゲート信号は3つの電位、V1、V2、及びV3を有している。V1、V2、及びV3は、例えば、グランド電位を基準として、それぞれ、27V、-5V及び-9Vに設定される。

t<sub>1</sub>においてi+1番目のゲートの論理状態がH(ゲートON電圧、V1)になると、表示信号が信号線からTFTを介して画素電極に与えられる。この後、t<sub>2</sub>において、i+

10

20

30

40

50

1番目のゲートがLの論理状態（ゲートOFF電圧、V3）になる。このとき、ゲート電位がV1からV3に降下するので、ゲートとソース（画素電極）との間の寄生容量Cgsによって、表示電圧が降下する。t3において、i番目のゲート線の電位がV3からV2に上昇するので、ゲート線と画素電極との間の蓄積容量Csを介して、表示電圧が増加される。t4においてi+1番目のゲート電位がV3からV2に上昇する。この上昇は、寄生容量Cgsを介して表示電圧を上昇させる。実際の設計においては、寄生容量による電圧の降下及び上昇と、Csを介した上昇との和がゼロになるように設計される。

以上のような突き抜け補償駆動によって、寄生容量によって引き起こされる表示電圧の減少を補償することができる。同時に、画素電極と共通電極との間の初期DC電圧成分を、小さく抑えることが可能である。製造交差による表示電圧の変化は、寄生容量Cgsの変化に起因する部分が大きい。通常の駆動方式においては、寄生容量の変化の表示電圧の変化に対する寄与は、寄生容量の変化に対して画素全体の容量がどれほど変化したかにより決定される。一方、つきぬけ補償駆動においては、寄生容量の変化に対して蓄積容量Csがどれほど変化したかにより決定される。従って、突き抜け補償駆動によって、画素電極と共通電極との間の初期DC電圧成分を、小さく抑えることが可能となる。10

又、突き抜け補償駆動方式の液晶表示装置においては、製造交差による寄生容量と蓄積容量との変化による表示電圧の変化を、小さくするように設計することが可能である。このように設計することにより、上記の効果をさらに確かなものとすることができる。

尚、突き抜け補償駆動は、Csオングート構造を必須の要件としていない。例えば、Cs線をゲート線とは別に配設し、このCs線に上記の効果が得られる信号を与えることにより、突き抜け補償駆動を実現することができる。20

図7は従来の液晶表示ディスプレイと本発明による液晶表示ディスプレイとの、DC成分の変化を比較説明する図面である。図7において、Y軸は画素電極と共通電極との間のDC成分の値である。X軸は、電源がONにされた後の経過時間である。図において、(1)と(2)とは本発明に従う液晶表示装置におけるDC成分の変化を示すモデル曲線である。(3)は、従来の液晶表示装置におけるDC成分の変化を示すモデル曲線である。

すでに説明したように、画素電極と共通電極との間には、抵抗と容量が並列に接続されていると、モデル化される。従って、DC成分は電源投入直後の初期値から指數関数的に減少する。

図7から理解されるように、従来の液晶表示装置は、所定時間後に許容値以上のDC成分を有している。一方、本発明による液晶表示装置は、DC成分が所定時間内に許容値以下になるように構成されている。所定時間は、液晶表示ディスプレイの電源をONにしてから、表示画面に画像が表示されるまでの時間と設定することができる。この時間は通常、3~5秒、もしくはそれ以下の時間である。30

DC成分の許容値はフリッカの発生によって決定され、約0.15V以下が好ましい。さらに好ましくは約0.12V以下であり、最も好ましくは約0.08V以下である。あるいは、フリッカの発生は表示画面の特性から決定することができる。これは、画面に特定パターンの画像を表示して、特定周波数の光の波長を測定、比較することにより行う。

図8は、この特定パターンを説明する図である。図8において、(A)はドット反転駆動液晶表示装置のためのパターンである。(B)は、ライン反転駆動液晶表示装置のためのパターンである。赤、青、緑とは、各画素のCF層の色である。又、図8はノーマリ・ホワイト液晶表示装置の場合を説明している。黒の画素は、最も光の透過率が小さい電圧で駆動される。ノーマリブラックモードでは、最大駆動電圧値で駆動されている。中間調は、通常、最大駆動電圧値の50%の値で駆動されている。図から理解されるように、同じ極性の画素のグループは同じ電圧値で駆動され、異なる極性の画素のグループは異なる電圧値で駆動されている。ドット反転駆動においては、上下左右に隣接する画素(ドット)は、ことなる階調で表示を行う。ライン反転駆動においては、同じ行における画素は同じ階調で表示し、隣接する行の画素は、異なる階調で表示する。40

今、液晶表示装置が60Hzで駆動されている場合、表示装置に図8のパターンを表示さ50

せ、透過光波形の 60 Hz 成分の振幅と、30 Hz 成分の振幅とを比較する。選択される周波数は、THz で駆動される表示装置においては、THz と  $T/2\text{ Hz}$  である。THz 駆動の表示装置は、1 秒間に T フレームの画像を表示する。

透過光波形の 30 Hz 成分の振幅が、60 Hz 成分の振幅の 10 倍以下であることが好ましい。尚、2 ドット反転駆動液晶表示装置、2 ライン反転駆動液晶表示装置等、及びモノクロパネルにおいても、ルールは同じである。

同様のことは、インターレース駆動される液晶表示装置に関しててもあてはまる。インターレース駆動は、1 つのフレームを 2 つのフィールドに分けて表示する。一方のフィールドが奇数行の画素行を駆動し、もう一方のフィールドが偶数行の画素行を駆動する。各フィールドは、通常、ドット反転駆動もしくはライン反転駆動される。従って、各フィールドは、2 種類の駆動電圧極性を有する。特定パターンにおいて、一つのフィールド内の駆動されていない画素行は黒を表示する。駆動されている画素のうち、一方の極性の画素は黒を表示し、もう一方の極性の画素は中間調を表示する。1 つのフレーム内においては、例えば + 極性の画素は黒を表示し、- 極性の画素は中間調を表示する。

初期 DC 成分の値と減少率とは相補的関係にあるので、それぞれが特定の範囲を有することができる。初期 DC 成分が大きい場合は、減少率も大きくななければならない。しかし、減少率の大きさは限界があるので、初期 DC 成分の大きさもそれによって限定される。従って、初期 DC 成分は 0.5 V 以下であることが好ましい。さらに好ましくは、0.25 V 以下であり、最も好ましくは 0.2 V 以下である。本実施形態に従う液晶表示装置は、電源投入から約 1 秒後の画素電極と共に通電極との間の DC 成分を、0.04 ~ 0.06 V とすることが可能であり、この液晶表示装置はフリッカ欠陥を有していない。

尚、以上に説明したものは、本発明の一実施形態であり、本発明の技術的範囲は特許請求の範囲の記載に基づいて決定される。又、本発明の範囲内において、上記実施形態の要素を、変更、追加することは、当業者にとって明らかである。

【図 1】

【図 2】

**【図8】**

■赤 ■緑 ■青

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

G 0 9 G 3/20 6 7 0 D

G 0 9 G 3/36

(72) 発明者 竹中 敦

神奈川県大和市下鶴間1623番地14 日本アイ・ビー・エム株式会社 大和事業所内

(72) 発明者 池崎 充

神奈川県大和市下鶴間1623番地14 日本アイ・ビー・エム株式会社 大和事業所内

(72) 発明者 草深 薫

神奈川県大和市下鶴間1623番地14 日本アイ・ビー・エム株式会社 大和事業所内

審査官 右田 昌士

(56) 参考文献 特開2000-066222(JP, A)

特開平10-123482(JP, A)

特開平06-273720(JP, A)

国際公開第96/000408(WO, A1)

(58) 調査した分野(Int.Cl.<sup>7</sup>, DB名)

G02F 1/133

G02F 1/1343

G02F 1/1368

G09G 3/20

G09G 3/36

|                |                                                                                               |         |            |

|----------------|-----------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP3639830B2</a>                                                                   | 公开(公告)日 | 2005-04-20 |

| 申请号            | JP2002563069                                                                                  | 申请日     | 2001-12-25 |

| [标]申请(专利权)人(译) | 国际商业机器公司                                                                                      |         |            |

| 申请(专利权)人(译)    | 国际商业机器公司                                                                                      |         |            |

| 当前申请(专利权)人(译)  | 国际商业机器公司                                                                                      |         |            |

| [标]发明人         | 竹中敦<br>池崎充<br>草深薰                                                                             |         |            |

| 发明人            | 竹中 敦<br>池崎 充<br>草深 薰                                                                          |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G02F1/1343 G02F1/1368 G09G3/20                                             |         |            |

| CPC分类号         | G09G3/3648 G09G3/3614 G09G2300/0434 G09G2320/0204 G09G2320/0219 G09G2320/0247<br>G09G2330/026 |         |            |

| FI分类号          | G02F1/133.525 G02F1/133.550 G02F1/1343 G02F1/1368 G09G3/20.611.E G09G3/20.670.D G09G3/36      |         |            |

| 代理人(译)         | 坂口 博<br>上野武                                                                                   |         |            |

| 优先权            | 2001028602 2001-02-05 JP                                                                      |         |            |

| 其他公开文献         | <a href="#">JPWO2002063383A1</a>                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                     |         |            |

### 摘要(译)

提供一种液晶显示装置，其可以在制造液晶显示装置之后消除对闪烁调节的需要。本发明的液晶显示装置是IPS驱动系统的液晶显示装置。在液晶显示装置开启之后，像素电极和公共电极之间立即具有初始DC电压分量。这被认为是闪烁的原因。由于在电源接通之后DC电压分量在预定时间内自动等于或小于容许值，因此不必通过改变施加到像素中的电极的电位来调整闪烁。为此，初始DC分量应该足够小，此外，电荷应该能够在液晶面板中高速移动。作为用于减小初始DC分量的技术，采用了穿透补偿驱动方法。优化相对衬底的配置以促进电荷在相对衬底内的移动。