(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-193334

(P2007-193334A)

(43) 公開日 平成19年8月2日(2007.8.2)

(51) Int.CI.

G02F 1/1368 (2006.01)

G09F 9/30 (2006.01)

F 1

G02F 1/1368

G09F 9/30 338

テーマコード(参考)

2 H 0 9 2

5 C 0 9 4

審査請求 未請求 請求項の数 18 O L (全 12 頁)

(21) 出願番号 特願2007-7119 (P2007-7119)

(22) 出願日 平成19年1月16日 (2007.1.16)

(31) 優先権主張番号 10-2006-0004233

(32) 優先日 平成18年1月16日 (2006.1.16)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市八達区梅灘洞416

番地

(74) 代理人 100094145

弁理士 小野 由己男

(74) 代理人 100106367

弁理士 稲積 朋子

(72) 発明者 金 晶 日

大韓民国仁川廣域市南洞区萬壽一洞959

-3 東仁ビル ガ棟201号

最終頁に続く

(54) 【発明の名称】 液晶表示パネル及びその製造方法

## (57) 【要約】

## 【課題】

サブ画素配列構造の変更によってデータラインの数を減らしながらも開口率を十分に確保できる液晶パネル及びその製造方法を提供する。

## 【解決手段】

本発明は表示領域を構成する多数のサブ画素と、前記多数のサブ画素それぞれと接続された多数の薄膜トランジスタと、前記薄膜トランジスタと接続され前記サブ画素の長辺方向に沿って形成された多数のゲートラインと、前記薄膜トランジスタと接続され前記サブ画素の短辺方向に沿って形成された多数のデータラインと、前記短辺方向に沿って前記サブ画素を経由するように形成された多数のストレージラインと、前記多数のストレージラインの一側部と共に接続された第1共通ストレージラインと、前記多数のストレージラインの他側部と共に接続された第2共通ストレージラインを備える。

## 【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

表示領域を構成する多数のサブ画素と、

前記多数のサブ画素それぞれと接続された多数の薄膜トランジスタと、

前記薄膜トランジスタと接続され、前記サブ画素の長辺方向に沿って形成された多数のゲートラインと、

前記薄膜トランジスタと接続され、前記サブ画素の短辺方向に沿って形成された多数のデータラインと、

前記短辺方向に沿って前記サブ画素を横断するように形成された多数のストレージラインと、を備えることを特徴とする液晶パネル。

10

**【請求項 2】**

前記多数のストレージラインの一側部と共に接続された第1共通ストレージラインと、

前記多数のストレージラインの他側部と共に接続された第2共通ストレージラインと、

をさらに備えることを特徴とする請求項1に記載の液晶パネル。

**【請求項 3】**

前記多数のサブ画素には、赤、緑、青色のサブ画素のいずれかで構成され、

前記赤、緑、青色のサブ画素は前記データラインに沿って順番に反復的に配置されることを特徴とする請求項1に記載の液晶パネル。

**【請求項 4】**

前記第1及び第2共通ストレージラインは、前記ゲートラインと同じ第1金属層で形成され、前記ストレージラインは前記データラインと同じ第2金属層で形成されることを特徴とする請求項3に記載の液晶パネル。

20

**【請求項 5】**

前記第1共通ストレージラインと前記多数のストレージラインそれぞれを接続させる多数の第1コンタクト電極と、

前記第2共通ストレージラインと前記多数のストレージラインそれぞれを接続させる多数の第2コンタクト電極をさらに備えることを特徴とする請求項4に記載の液晶パネル。

30

**【請求項 6】**

前記第1及び第2コンタクト電極それぞれは、

前記共通ストレージライン及び前記ストレージラインをそれぞれ露出させるコンタクトホールを介して前記共通ストレージラインと前記ストレージラインを接続させる第3導電層で形成されることを特徴とする請求項5に記載の液晶パネル。

**【請求項 7】**

前記第1共通ストレージラインは、前記表示領域を取り囲む非表示領域のうち上側非表示領域を経て前記多数のストレージラインの上側部と接続され、

前記第2共通ストレージラインは下側非表示領域を経て前記多数のストレージラインの下側部と接続されることを特徴とする請求項4に記載の液晶パネル。

40

**【請求項 8】**

前記第2共通ストレージラインは、前記下側非表示領域で左側及び右側非表示領域に沿って前記上側非表示領域まで延びることを特徴とする請求項7に記載の液晶パネル。

**【請求項 9】**

前記第1共通ストレージラインの両端とそれぞれ接続された第1共通パッドと、

前記第2共通ストレージラインの両端とそれぞれ接続された第2共通パッドをさらに備えることを特徴とする請求項8に記載の液晶パネル。

**【請求項 10】**

前記第1及び第2共通ストレージラインの両端と共に接続された共通パッドをさらに備えることを特徴とする請求項8に記載の液晶パネル。

**【請求項 11】**

前記左側及び右側非表示領域に内蔵され前記多数のゲートラインを分割駆動するゲート駆動部をさらに備えることを特徴とする請求項9に記載の液晶パネル。

50

**【請求項 1 2】**

前記第2共通ストレージラインは前記ゲート駆動部の外郭側に経るように形成されることを特徴とする請求項11に記載の液晶パネル。

**【請求項 1 3】**

基板上にゲートライン及びデータラインと、該ゲートライン及びデータラインと接続される薄膜トランジスタを形成する段階と、

前記ゲートラインとデータラインの交差構造に限定され、前記ゲートラインと並んだ長辺と前記データラインと並んだ短辺を有する各サブ画素領域に前記薄膜トランジスタと接続された画素電極を形成する段階と、

前記画素電極を前記サブ画素領域の短辺方向に経るストレージラインを形成する段階と 10

、

前記ストレージラインの一側部と接続された第1共通ストレージラインと、前記ストレージラインの他側部と接続された第2共通ストレージラインを形成する段階と、を含むことを特徴とする液晶パネルの製造方法。

**【請求項 1 4】**

前記第1及び第2共通ストレージラインは前記ゲートラインと同じ第1金属層で、前記ストレージラインは前記データラインと同じ第2金属層で形成されることを特徴とする請求項13に記載の液晶パネルの製造方法。

**【請求項 1 5】**

前記第1共通ストレージラインと前記ストレージラインを接続させる第1コンタクト電極と、前記第2共通ストレージラインと前記ストレージラインを接続させる第2コンタクト電極を形成する段階をさらに含むことを特徴とする請求項14に記載の液晶パネルの製造方法。 20

**【請求項 1 6】**

前記第1及び第2コンタクト電極それぞれを形成する段階は、

前記共通ストレージライン及び前記ストレージラインをそれぞれ露出させるコンタクトホールを形成する段階と、

前記コンタクトホールを介して前記共通ストレージラインと前記ストレージラインを接続させる第3導電層で前記第1及び第2コンタクト電極を形成する段階を含むことを特徴とする請求項15に記載の液晶パネルの製造方法。 30

**【請求項 1 7】**

前記第1共通ストレージラインの両端とそれぞれ接続された第1共通パッドと、前記第2共通ストレージラインの両端とそれぞれ接続された第2共通パッドを形成する段階をさらに含むことを特徴とする請求項16に記載の液晶パネルの製造方法。

**【請求項 1 8】**

前記第1及び第2共通ストレージラインの両端と共に接続された共通パッドを形成する段階をさらに含むことを特徴とする請求項16に記載の液晶パネルの製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は液晶表示装置に関する。

**【背景技術】****【0002】**

液晶表示装置は液晶の電気的及び光学的特性を用いて映像を表示する。液晶表示装置は画素マトリックスを通じて画像を表示する液晶表示パネル(以下、液晶パネルと称する)と、液晶パネルを駆動する駆動回路とを備える。そして、液晶表示装置は液晶パネルが非発光素子なので液晶パネルの背面から光を供給するバックライトユニットを備える。このような液晶表示装置は移動通信端末機、携帯用コンピュータ、液晶TVなどのように小型表示装置から大型表示装置まで幅広く使われる。

**【0003】**

40

30

40

50

赤、緑、青サブ画素より構成された画素がマトリックス状に配列された液晶パネルは各サブ画素がデータ信号に応じて液晶配列状態を可変させてバックライトユニットから照射された光の透過率を調節することにより映像を表示する。この際、サブ画素はスイッチング素子である薄膜トランジスタを通じて画素電極に供給されたデータ信号と、共通電極に供給された共通電圧との電圧差を充電して液晶を駆動する。このような液晶パネルには薄膜トランジスタと接続されたゲートラインを駆動する多数のゲート集積回路(以下、I Cと称する)と、データラインを駆動する多数のデータI Cと、が接続される。データI Cはデジタルビデオデータをアナログデータ信号に変換すべきなので、ゲートI Cより複雑な回路構成を有する。

## 【0004】

10

最近、液晶パネルはコストダウンのためにデータI C数を減らすことができるよう、解像度は維持しつつデータライン数を減らす方向に発展しつつある。データライン数を減らす方法としてサブ画素の配列構造を変える方策が挙げられているが、この際、輝度及び画質が減少しないように開口率の確保を必要とする。

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0005】

そこで、本発明は従来の技術的課題を解決するために案出されたもので、その目的は開口率を十分に確保できる液晶パネル及びその製造方法を提供するところにある。

## 【課題を解決するための手段】

20

## 【0006】

そのため、本発明の実施例による液晶パネルは、表示領域を構成する多数のサブ画素と、前記多数のサブ画素それぞれと接続された多数の薄膜トランジスタと、前記薄膜トランジスタと接続され前記サブ画素の長辺方向に沿って形成された多数のゲートラインと、前記薄膜トランジスタと接続され前記サブ画素の短辺方向に沿って形成された多数のデータラインと、前記短辺方向に沿って前記サブ画素を経るように形成された多数のストレージラインと、を備える。

## 【0007】

以上のように、本発明に係る液晶パネル及びその製造方法は、R、G、Bサブ画素を垂直方向に配列してデータラインの数を減らす構造において、ストレージラインをデータラインと並んで形成して各サブ画素を短辺方向に経由させることによって、ストレージラインによる開口率減少を最小化して開口率を確保できるようになる。

前記多数のストレージラインの一側部と共に接続された第1共通ストレージラインと、前記多数のストレージラインの他側部と共に接続された第2共通ストレージラインを備える。

## 【0008】

30

前記多数のサブ画素に赤、緑、青色のサブ画素を含み、前記赤、緑、青色のサブ画素は前記データラインに沿って交代に反復的に配される。

前記第1及び第2共通ストレージラインは前記ゲートラインと同じ第1金属層で、前記ストレージラインは前記データラインと同じ第2金属層で形成される。

そして、本発明の液晶パネルは前記第1共通ストレージラインと前記多数のストレージラインそれぞれを接続させる多数の第1コンタクト電極と、前記第2共通ストレージラインと前記多数のストレージラインそれぞれを接続させる多数の第2コンタクト電極をさらに具備する。

## 【0009】

40

前記第1及び第2コンタクト電極それぞれは前記共通ストレージライン及び前記ストレージラインをそれぞれ露出させるコンタクトホールを介して前記共通ストレージラインと前記ストレージラインを接続させる第3導電層で形成される。

前記第1共通ストレージラインは前記表示領域を取り囲む非表示領域のうち上側非表示領域を経由して前記多数のストレージラインの上側部と接続され、前記第2共通ストレー

50

ジラインは下側非表示領域を経て前記多数のストレージラインの下側部と接続される。第1及び第2共通ストレージラインを多数のストレージラインの上下部と同時に接続させることにより、いずれか1本の共通ストレージラインが断線されても残り共通ストレージラインを介して多数のストレージラインに共通電圧を供給できるようになる。

#### 【0010】

前記第2共通ストレージラインは前記下側非表示領域で左側及び右側非表示領域に沿って前記上側非表示領域まで伸びる。

また、本発明の液晶パネルは前記第1共通ストレージラインの両端とそれぞれ接続された第1共通パッドと、前記第2共通ストレージラインの両端とそれぞれ接続された第2共通パッドをさらに備える。

10

#### 【0011】

一方、本発明の液晶パネルは前記第1及び第2共通ストレージラインの両端と共に接続された共通パッドをさらに備える。

また、本発明の液晶パネルは前記左側及び右側非表示領域に内蔵され前記多数のゲートラインを分割駆動するゲート駆動部をさらに備え、前記第2共通ストレージラインは前記ゲート駆動部の外郭側に経由するように形成される。

#### 【0012】

そして、本発明に係る液晶パネルの製造方法は、基板上にゲートライン及びデータラインと、そのゲートライン及びデータラインと接続された薄膜トランジスタを形成する段階と、前記ゲートラインとデータラインに交差構造に限定され前記ゲートラインと並んだ長辺と前記データラインと並んだ短辺を有する各サブ画素領域に前記薄膜トランジスタと接続された画素電極を形成する段階と、前記画素電極を前記サブ画素領域の短辺方向に経由するストレージラインを形成する段階と、前記ストレージラインの一側部と接続された第1共通ストレージラインと、前記ストレージラインの他側部と接続された第2共通ストレージラインを形成する段階を含む。

20

#### 【0013】

前記第1及び第2共通ストレージラインは、前記ゲートラインと同じ第1金属層で、前記ストレージラインは前記ストレージラインは前記データラインと同じ第2金属層で形成される。

また、本発明の液晶パネル製造方法は、前記第1共通ストレージラインと前記ストレージラインを接続させる第1コンタクト電極と、前記第2共通ストレージラインと前記ストレージラインを接続させる第2コンタクト電極を形成する段階をさらに含む。

30

#### 【0014】

前記第1及び第2コンタクト電極それぞれを形成する段階は、前記共通ストレージライン及び前記ストレージラインをそれぞれ露出させるコンタクトホールを形成する段階と、前記コンタクトホールを介して前記共通ストレージラインと前記ストレージラインを接続させる第3導電層で前記第1及び第2コンタクト電極を形成する段階を含む。

また、本発明の液晶パネル製造方法は、前記第1共通ストレージラインの両端とそれぞれ接続された第1共通パッドと、前記第2共通ストレージラインの両端とそれぞれ接続された第2共通パッドを形成する段階をさらに含む。

40

#### 【0015】

一方、本発明の液晶パネル製造方法は、前記第1及び第2共通ストレージラインの両端と共に接続された共通パッドを形成する段階をさらに含む。

#### 【発明の効果】

#### 【0016】

本発明によれば、開口率を十分に確保できる液晶パネル及びその製造方法を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0017】

以下、添付した図1ないし図5に基づき本発明の望ましい実施形態を詳述する。

50

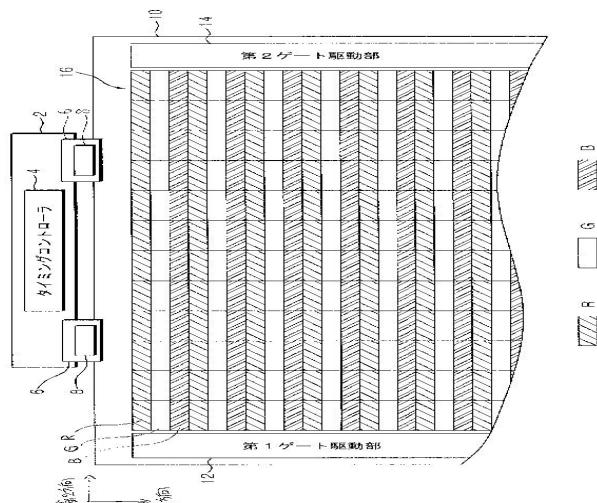

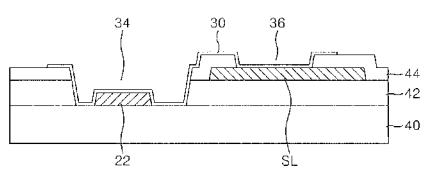

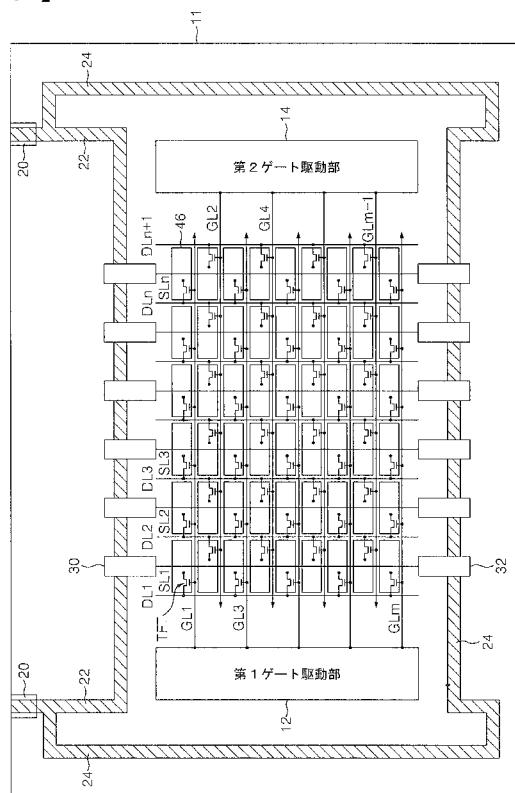

図1は本発明の実施形態による液晶表示装置の一部を概略的に示した平面図である。

図1に示された液晶表示装置は画像表示部16と、画像表示部16のゲートラインを駆動するゲート駆動部12、14が形成された液晶パネル10と、画像表示部16のデータラインを駆動するデータIC8が実装され印刷回路基板(以下、PCB:Printed Circuit Board)2と液晶パネル10との間に接続された回路フィルム6と、PCB2に実装されたタイミングコントローラ4とを備える。

#### 【0018】

液晶パネル10の画像表示部16は赤(R)、緑(G)、青(B)サブ画素で構成された多数の画素がマトリックス状に配列され画像を表示する。画像表示部16はR、G、Bサブ画素別に薄膜トランジスタが形成された薄膜トランジスタ基板と、カラーフィルタの形成されたカラーフィルタ基板と、が液晶を挟んで合わせられて形成される。薄膜トランジスタ基板には薄膜トランジスタと接続されたゲートライン及びデータラインと画素電極とがさらに形成される。画素電極と共に液晶を駆動する共通電極は、薄膜トランジスタ基板またはカラーフィルタ基板に形成される。R、G、Bサブ画素は垂直方向(図1中、第1方向)に交代に反復的に配列され、同色のサブ画素は水平方向(図1中、第2方向)のストライプ状に、つまり同一の行に位置するように配列される。言い換えれば、画像表示部16は、多数のRサブ画素で構成されたR水平ライン、多数のGサブ画素で構成されたG水平ライン、多数のBサブ画素で構成されたB水平ラインが垂直方向に交代に反復的に配列された構造を有する。そして、R、G、Bサブ画素は長辺が水平方向に、短辺が垂直方向に形成された直四角形を有する。

10

20

30

#### 【0019】

このように本発明の画像表示部16では、水平方向に長く形成されたR、G、Bサブ画素が垂直方向に反復的に配列されるため、垂直方向に長く形成されたR、G、Bサブ画素が水平方向に反復的に配列されていた従来の液晶パネルよりも、データライン数が1/3に減り、その結果データラインを駆動するデータIC8の数も減る。つまり、従来の液晶パネルの場合、垂直方向に長い、例えば3つのサブ画素が水平方向に沿って配置されるため、各サブ画素の画素電極46にデータ電圧を供給するためには、3本のデータラインが必要である。一方、本発明によれば、サブ画素が3つの場合、水平方向に長いサブ画素が垂直方向に沿って配置されるため、データラインを垂直方向に配置させることで、各サブ画素の画素電極46に共通にデータ電圧を供給することができる。よって、本発明のようにサブ画素を配置することで、従来よりもデータライン数を1/3に減らすことができる。

#### 【0020】

R、G、Bサブ画素の垂直方向配列にデータラインが減少するほどゲートラインが増加してゲート駆動部12、14のサイズが増加するが、ゲート駆動部12、14の回路構成がデータIC8より簡単なので製造コストを節減することができる。特に、非晶質シリコン(Amorphous Silicon)薄膜を用いた液晶パネル10にゲート駆動部12、14が内蔵されるので、製造コストは一層節減することができる。

40

#### 【0021】

第1及び第2ゲート駆動部12、14は画像表示部16の両側部に位置してゲートラインを分割駆動する。例えば、第1ゲート駆動部12は奇数ゲートラインを、第2ゲート駆動部14は偶数ゲートラインを駆動する。第1及び第2ゲート駆動部12、14は多数の薄膜トランジスタを含むシフトレジ斯特で構成されるため、液晶パネル10の薄膜トランジスタ基板に画像表示部16の薄膜トランジスタ及び多数の信号ラインと共に形成され、非表示領域に内蔵される。

#### 【0022】

画像表示部16のデータラインを分割駆動する多数のデータIC8それぞれは回路フィルム6上に実装され、回路フィルム6はACF(Anisotropic Conductive Film)を通じて液晶パネル10及びPCB2に取り付けられる。データIC8を実装した回路フィルム6としてはTCP(Tape Carrier Package)またはCOF(Chip On Film)が用いられる。これとは違って、データIC8は回路フィルム6を使用せず、液晶パネル10の薄膜トランジス

50

タ基板上にCOG (Chip On Glass)方式で直接に実装される場合もある。

#### 【0023】

PCB2に実装されたタイミングコントローラ4はデータIC8と第1及び第2ゲート駆動部12、14を制御する。タイミングコントローラ4からのデータ信号と多数のデータ制御信号はPCB2と回路フィルム6を経て各データIC8に供給され、多数のゲート制御信号はPCB2と回路フィルム6及び液晶パネル10の薄膜トランジスタ基板を経て第1及び第2ゲート駆動部12、14に供給される。

#### 【0024】

第1及び第2ゲート駆動部12、14はタイミングコントローラ4からのゲート制御信号と電源部(図示せず)からのゲートオン電圧及びゲートオフ電圧を用いて画像表示部16のゲートラインを順次駆動する。データIC8はタイミングコントローラ4からのデジタルデータをガンマ電圧部(図示せず)からのガンマ電圧を用いてアナログデータ信号に変換し、画像表示部16のゲートラインが駆動される各水平期間に同期してデータラインにアナログデータ信号を供給する。

#### 【0025】

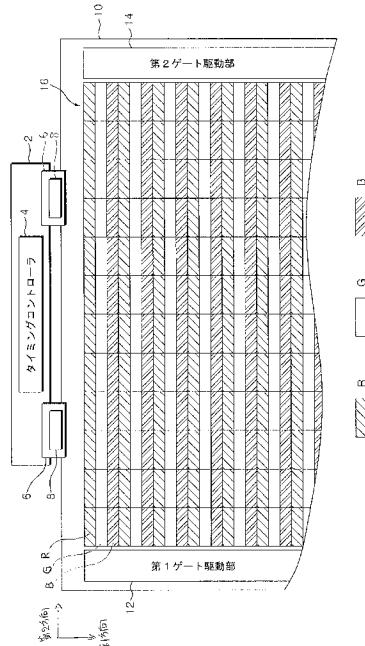

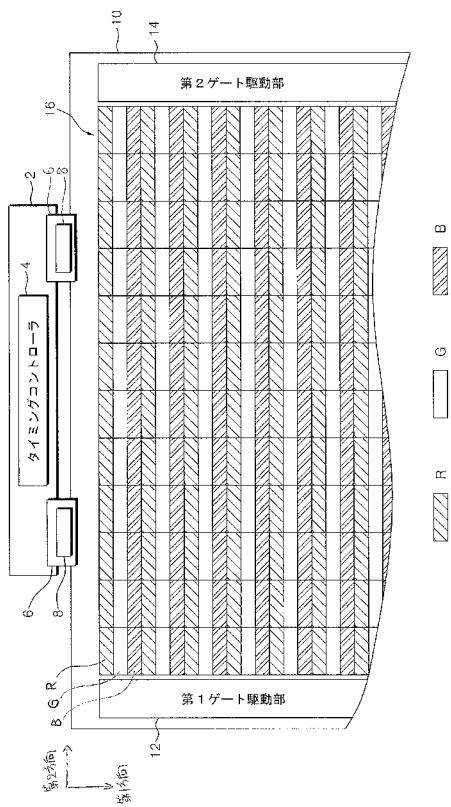

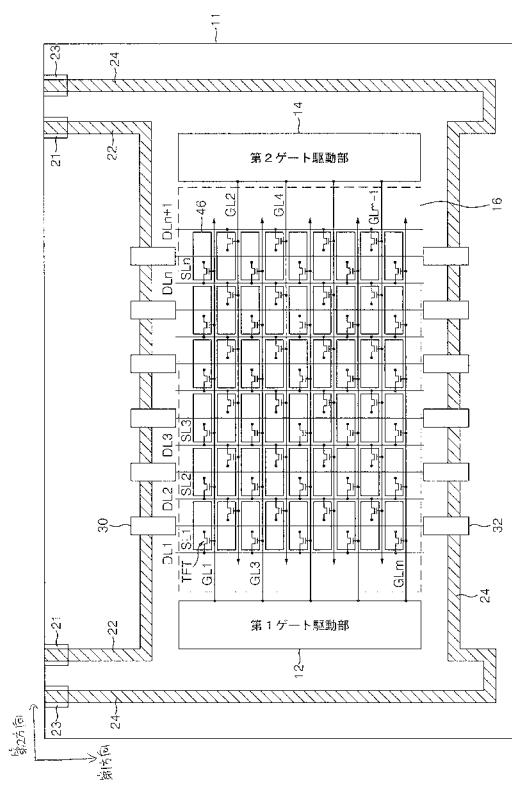

図2は図1に示された液晶パネルの薄膜トランジスタ基板を概略的に示した平面図である。

図2に示された薄膜トランジスタ基板11は図1に示された液晶パネル10の画像表示部16と対応する表示領域と、該表示領域を取り囲む非表示領域とに区分できる。薄膜トランジスタ基板11の表示領域にはゲートライン(GL1ないしGLm)とデータラインDL1ないしDLn+1が交差するような構造で形成され、その交差構造に限定された各サブ画素領域には後述の画素電極46と薄膜トランジスタ(TFT)が形成される。薄膜トランジスタ(TFT)はゲートライン(GL)からのゲート信号に応答してデータライン(DL)からのデータ信号を画素電極46に供給する。図1に示すように水平方向(第2方向)に長く形成されたR、G、Bサブ画素が垂直方向(第1方向)に反復的に配列されることによって、画素電極46は水平方向(第2方向)に長く、すなわち長辺が水平方向(第2方向)に位置し短辺が垂直方向(第1方向)に位置するように形成される。このような画素電極46はカラーフィルタ基板のカラーフィルタと共にサブ画素のサイズ及び形状を決める。

#### 【0026】

液晶劣化を防止するためにデータライン(DL1ないしDLn+1)に供給されるデータ信号の極性は一定周期に反転されるべきである。反転方法のうちドット反転方法は各サブ画素が水平及び垂直方向に隣接したサブ画素と反対の極性に駆動する方法であって最も優れた画質を提供する。しかし、ドット反転方法のためにはデータライン(DL1ないしDLn+1)に供給されるデータ信号がサブ画素単位で反転されるべきなので、データ信号のスイング幅及び駆動周波数が増加して消費電力面において不利な短所がある。この点を解決するため、データライン(DL1ないしDLn+1)と接続された薄膜トランジスタ(TFT)の接続方向を垂直方向に沿いつつ、各画素領域毎に交互に変える。例えば、奇数ゲートライン(GL1、GL3、…、GLn)と接続された奇数水平ラインの薄膜トランジスタ(TFT)は、図2中、データライン(DL1ないしDLn)の右側に位置した各画素領域の画素電極46と接続される。偶数ゲートライン(GL2、GL4、…、GLn)と接続された偶数水平ラインの薄膜トランジスタ(TFT)はデータライン(DL2ないしDLn+1)の左側に位置した各画素領域の画素電極46と接続される。これにより、データライン(DL1ないしDLn+1)それぞれに供給されるデータ信号の極性が、隣接したデータライン(DL)のデータ信号と反対になり、フレーム単位でだけ反転されても画素電極46は水平及び垂直方向に隣接した画素電極46と反対極性のデータ信号を充電してドット反転方式で駆動されうるようになる。

#### 【0027】

そして、薄膜トランジスタ基板11の表示領域には各サブ画素のストレージキャパシタ形成のためのストレージライン(SL11ないしSLn)それぞれがデータライン(DL1

10

20

30

40

50

ないし  $D L_n + 1$ ) と並んで形成される。また、ストレージライン ( $S L_1$  ないし  $S L_n$ ) はゲートライン ( $G L_1$  ないし  $G L_m$ ) と交差しつつ画素電極 4 6 を垂直(短辺)方向(第1方向)に経由するようになる。これにより、ストレージライン ( $S L_1$  ないし  $S L_n$ ) がゲートライン ( $G L_1$  ないし  $G L_m$ ) と並んで形成され画素電極 4 6 の水平(長辺)方向に重畠された場合より画素電極 4 6 との重畠面積が狭いので開口率を向上させることができる。つまり、画素電極 4 6 は、長辺が水平方向(第2方向)に位置し短辺が垂直方向(第1方向)に位置するように形成される。そのため、ストレージライン ( $S L_1$  ないし  $S L_n$ ) が垂直方向に沿って形成される方が、ストレージラインと画素電極 4 6 との重畠面積を小さくすることができる。

## 【0028】

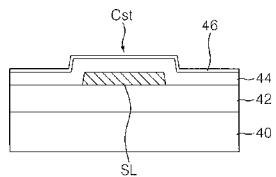

ストレージライン ( $S L_1$  ないし  $S L_n$ ) はデータライン ( $D L_1$  ないし  $D L_n + 1$ ) と同じマスク工程を通じてソース/ドレイン金属で形成される。言い換えれば、ストレージライン ( $S L$ ) は図3に示したようにゲート絶縁膜 4 2 上にソース/ドレイン金属で形成され、ゲート絶縁膜 4 2 は絶縁基板 4 0 上に形成される。これにより、各サブ画素のストレージキャパシタ ( $C_{st}$ ) は画素電極 4 6 が保護膜 4 4 を挟んでストレージライン ( $S L$ ) と重畠して形成される。

## 【0029】

図2に示すように、薄膜トランジスタ基板 1 1 の非表示領域のうち表示領域を挟んだ左側及び右側非表示領域にはゲートライン ( $G L_1$  ないし  $G L_n$ ) を分割駆動する第1及び第2ゲート駆動部 1 2、1 4 がそれぞれ形成される。例えば、左側非表示領域に位置する第1ゲート駆動部 1 2 は奇数ゲートライン ( $G L_1, G L_3, \dots, G L_{m-1}$ ) を駆動し、右側非表示領域に位置する第2ゲート駆動部 1 4 は偶数ゲートライン ( $G L_2, G L_4, \dots, G L_m$ ) を駆動する。このような第1及び第2ゲート駆動部 1 2、1 4 は多数の薄膜トランジスタで構成され、表示領域の薄膜トランジスタ (TFT) と共に形成される。

## 【0030】

また、薄膜トランジスタ基板 1 1 の画像表示部 1 6 を取り囲む非表示領域にはストレージライン ( $S L_1$  ないし  $S L_n$ ) と共に接続された第1及び第2共通ストレージライン 2 2、2 4 と、第1及び第2共通ストレージライン 2 2、2 4 とストレージライン ( $S L_1$  ないし  $S L_n$ ) それぞれを接続させる多数の第1及び第2コンタクト電極 3 0、3 2 が形成される。第1及び第2共通ストレージライン 2 2、2 4 はストレージライン ( $S L_1$  ないし  $S L_n$ ) の上端部及び下端部に同時に接続される。これにより、第1及び第2共通ストレージライン 2 2、2 4 のうちいずれか1つの共通ストレージラインが断線されると残り共通ストレージラインを介して共通電圧が供給できるので、第1及び第2共通ストレージライン 2 2、2 4 は互いのリダンダンシー (Redundancy) の役割を果たす。

## 【0031】

具体的に第1共通ストレージライン 2 2 は薄膜トランジスタ基板 1 1 の上側非表示領域に形成されストレージライン (( $S L_1$  ないし  $S L_n$ ) の上側部と第1コンタクト電極 3 0 を通じて共通接続される。また、第1共通ストレージライン 2 2 は上側非表示領域の両側に延びて二つの第1共通パッド 2 1 のそれぞれを通じて図1に示された一番目及び最後の回路フィルム 6 の出力パッドとそれぞれ接続される。これにより、第1共通ストレージライン 2 2 は図1に示した PCB 2 上に実装された電源部(図示せず)からの共通電圧を PCB 2 と回路フィルム 6 を経て供給されストレージライン ( $S L_1$  ないし  $S L_n$ ) に共通に供給するようになる。

## 【0032】

第2共通ストレージライン 2 4 は薄膜トランジスタ基板 1 1 の非表示領域のうち下側非表示領域に形成され、ストレージライン ( $S L_1$  ないし  $S L_n$ ) の下側部と第2コンタクト電極 3 2 を通じて共通接続される。また、第2共通ストレージライン 2 4 は下側非表示領域の両側に延びて屈曲され、左側及び右側非表示領域それぞれに沿って上側にさらに伸びて2つの第2共通パッド 2 3 それぞれを通じて図1に示された一番目及び最後の回路フィルム 6 の出力パッドとそれぞれ接続される。この際、第2共通ストレージライン 2 4 は左

10

20

30

40

50

側及び右側非表示領域において第1及び第2ゲート駆動部12、14の外郭に経由しつつ上側に延びる。従って、第2共通ストレージライン24は、図1に示されたPCB2上に実装された電源部(図示せず)からの共通電圧をPCB2と回路フィルム6を経て供給されストレージライン(SL1ないしSLn)に共通に供給する。

#### 【0033】

第1及び第2共通ストレージライン22、24は表示領域のゲートライン(GL)と共に同一なマスク工程によりゲート金属で形成され、第1及び第2コンタクト電極30、32は表示領域の画素電極46と共に同一なマスク工程により透明導電層で形成される。

例えば、第1コンタクト電極30は、図4に示したように、第1及び第2コンタクトホール34、36を介して第1共通ストレージライン22及びストレージライン(SL)と接続される。第1共通ストレージライン22は絶縁基板40上にゲート金属で形成され、その上にはゲート絶縁膜42が形成される。ストレージライン(SL)はゲート絶縁膜42上にソース/ドレイン金属で形成され、その上には保護膜44が形成される。第1コンタクトホール34は保護膜44及びゲート絶縁膜42を貫通して第1共通ストレージライン22の一部分を露出させ、第2コンタクトホール36は保護膜44を貫通してストレージライン(SL)の一部分を露出させる。保護膜44上に形成された第1コンタクト電極30は第1及び第2コンタクトホール34、36を経て第1共通ストレージライン22とストレージライン(SL)を接続させる。第2コンタクト電極32も図4に示された第1コンタクト電極30と同一な構造により第2共通ストレージライン24とストレージライン(SL)を接続させる。

#### 【0034】

そして、第1共通ストレージライン22と接続された第1共通パッド21と第2共通ストレージライン24と接続された第2共通パッド23は、図2に示したように互いに分離され、図1に示された回路フィルム6に設けられたそれぞれの出力パッドと接続される。

一方、第1及び第2共通ストレージライン22、24は図5に示したように1つの共通パッド20を介して図1に示された回路フィルム6に設けられた出力パッドと接続される場合もある。共通パッド20を介して1つの回路フィルム6に接続しつつ分離された第1及び第2共通ストレージライン22、24の間には多数のゲート駆動信号入力パッド(図示せず)が位置するようになる。多数のゲート駆動信号入力パッドはゲート駆動部12、14と接続された多数のゲート駆動信号供給ラインと接続され、図1に示されたPCB2上の電源部及びタイミングコントローラ4から回路フィルム6を経て供給された多数のゲート駆動信号をゲート駆動部12、14に供給するようになる。

#### 【0035】

このように本発明に係る液晶パネルは、水平方向(第2方向)に長く形成されたR、G、Bサブ画素を垂直方向(第1方向)に配列してデータラインの数を減らす。この際、R、G、Bサブ画素の長辺はゲートラインと平行に、短辺はデータラインと平行に形成し、ストレージラインをデータラインと平行に、すなわち短辺方向に各サブ画素を縦断するように形成することによって、ストレージラインによる開口率減少を最小化して開口率を確保できるようになる。

#### 【0036】

以上説明した内容を通じて当業者なら本発明の技術思想を逸脱しない範囲内で多様な変更及び修正ができることが分かる。従って、本発明の技術的範囲は明細書の詳細な説明に記載された内容に限られず、特許請求の範囲により定まるべきである。

#### 【図面の簡単な説明】

#### 【0037】

【図1】本発明の実施形態による液晶パネルの一部を示した図。

【図2】本発明の一実施形態による液晶パネルの薄膜トランジスタ基板を示した図。

【図3】図2に示したストレージラインの連結部をIII-III'線に沿って切断して示した断面図

10

20

30

40

50

【図4】図2に示した1つのサブ画素領域に形成されたストレージキャパシタを示した断面図。

【図5】本発明の他の実施形態による液晶パネルの薄膜トランジスタ基板を示した図。

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 金 東 奎

大韓民国京畿道龍仁市豊徳川二洞三星五次アパート523棟1305号

(72)発明者 権 英 根

大韓民国京畿道水原市靈通区網捕洞エルジーエックスアイ三次301棟1203号

F ターム(参考) 2H092 GA11 GA50 GA60 JA24 JA34 JB22 JB31 NA07 PA01 PA06

5C094 AA02 AA10 AA44 BA03 BA43 CA19 CA24 DB04 EA10

|                |                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示面板及其制造方法                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP2007193334A</a>                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2007-08-02 |

| 申请号            | JP2007007119                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2007-01-16 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 金晶日<br>金東奎<br>權英根                                                                                                                                                                                                                                                                                                                                               |         |            |

| 发明人            | 金晶日<br>金東奎<br>權英根                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | G02F1/1368 G09F9/30                                                                                                                                                                                                                                                                                                                                             |         |            |

| CPC分类号         | G02F1/134336 G02F1/13454 G02F1/136213 G02F1/136286                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G02F1/1368 G09F9/30.338                                                                                                                                                                                                                                                                                                                                         |         |            |

| F-TERM分类号      | 2H092/GA11 2H092/GA50 2H092/GA60 2H092/JA24 2H092/JA34 2H092/JB22 2H092/JB31 2H092/NA07 2H092/PA01 2H092/PA06 5C094/AA02 5C094/AA10 5C094/AA44 5C094/BA03 5C094/BA43 5C094/CA19 5C094/CA24 5C094/DB04 5C094/EA10 2H192/AA24 2H192/BC01 2H192/CC62 2H192/DA15 2H192/EA43 2H192/FA35 2H192/FA44 2H192/FA46 2H192/FB03 2H192/FB46 2H192/FB52 2H192/GA41 2H192/GD61 |         |            |

| 优先权            | 1020060004233 2006-01-16 KR                                                                                                                                                                                                                                                                                                                                     |         |            |

| 其他公开文献         | JP5382996B2<br>JP2007193334A5                                                                                                                                                                                                                                                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                       |         |            |

## 摘要(译)

[问题] 本发明提供一种液晶面板及其制造方法，该液晶面板可以通过改变子像素阵列结构来确保足够的开口率，同时减少数据线的数量。[解决方案] 本发明提供了形成显示区域的大量子像素，连接到大量子像素中的每一个的大量薄膜晶体管，以及连接到薄膜晶体管并沿着子像素的长边方向形成的大栅极。一条线，沿着子像素的短边方向形成的，连接到薄膜晶体管的多条数据线，以及形成为沿着短边方向穿过子像素的多条存储线。共同连接到多条存储线的一侧的第一公共存储线和共同连接到多条存储线的另一侧的第二公共存储线。[选型图]图1